多相クロック発生回路、及び多相クロック発生方法

【課題】回路規模の増加を抑えかつ出力信号のジッタ特性を低下させずに、複数の動作周波数に対応できる多相クロック発生回路を提供する。

【解決手段】多相クロック発生回路は、位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスと、リファレンスクロック信号の周波数に基づいて、複数の遅延パスのうち、リファレンスクロック信号の周波数に対応する遅延パスを選択するスイッチ部と、スイッチ部が選択した遅延パスにより、位相差が変更された複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間回路とを備える。

【解決手段】多相クロック発生回路は、位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスと、リファレンスクロック信号の周波数に基づいて、複数の遅延パスのうち、リファレンスクロック信号の周波数に対応する遅延パスを選択するスイッチ部と、スイッチ部が選択した遅延パスにより、位相差が変更された複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間回路とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、多相クロック発生回路、及び多相クロック発生方法に関する。

【背景技術】

【0002】

LSI間などでデジタル信号を送受信するためには、受信側で各データビットを正しいタイミングで判定する必要がある。そのため、データを送信する信号とは別にタイミング信号(クロック信号)を送信する信号線を設けることが多い。しかし、データ信号線に沿ってタイミング信号線を設ける必要があり、基板上の占有面積が増大するなどの問題が生じる。

【0003】

そこで、近年の高速シリアル伝送では、タイミング信号線を設けずに、送信側がデータ信号にタイミング信号を重畳して送信し、受信側がデータ信号のエッジ等を検出し、内部のリファレンスクロックの位相を調整することで、タイミング情報を再生している。このプロセスを、一般にクロック・データ・リカバリ(Clock Data Recovery:CDR)という。また、クロック・データ・リカバリのために受信側に設けられる回路をCDR回路という。

【0004】

CDR回路の主な構成方式には、位相同期(Phase-Locked Loop:PLL)方式、リングオシレータ方式、位相補間方式などがある。それぞれの方式には一長一短があるが、近年、伝送方式が向上するにつれて、位相補間方式を採用する事例が増えている(特許文献1)。

図11は、CDR回路に設けられる多相クロック発生回路9の構成例を示す回路図である。同図に示すように、多相クロック発生回路9は、4相−8相変換回路91と、位相選択回路92と、CDR制御回路93とを具備している。

【0005】

4相−8相変換回路91には、外部より基準のリファレンスクロックIN000と、リファレンスクロックIN000に対して、90°、180°、270°の位相差を有し、かつ同じ周波数を有するリファレンスクロックIN090、IN180、IN270が入力される。4相−8相変換回路91は、入力される4つのリファレンスクロックに基づいて、入力されるリファレンスクロックと同じ周波数を有し、位相が異なる8つのクロック信号OUT0〜OUT7を出力する。4相−8相変換回路91は、バッファ911−1〜911−4と、遅延バッファ912−1〜912−4と、位相補間回路(Phase Interpolator:PI)913−1〜913−4とを備えている。

【0006】

リファレンスクロックIN000、IN180は、バッファ911−1を介して、位相補間回路913−1と位相補間回路913−4とに入力される。また、リファレンスクロックIN000、IN180は、バッファ911−2及び遅延バッファ912−1、912−2を介して、位相補間回路913−1と位相補間回路913−2とに入力される。リファレンスクロックIN000、IN180は、遅延バッファ912−1、912−2を通過する際に45°の位相差に相当する遅延が加えられる。

【0007】

リファレンスクロックIN090、IN270は、バッファ911−3を介して、位相補間回路913−2と位相補間回路913−3とに入力される。また、リファレンスクロックIN090、IN270は、バッファ911−4及び遅延バッファ912−3、912−4を介して、位相補間回路913−3と位相補間回路913−4とに入力される。リファレンスクロックIN090、IN270は、遅延バッファ912−3、912−4を通過する際に45°の位相差に相当する遅延が加えられる。

【0008】

位相補間回路913−1〜913−4は、それぞれがバッファ911−1〜911−4及び遅延バッファ912−1〜912−4を介して入力されたリファレンスクロックを合成し、位相が異なる8つのクロック信号OUT0〜OUT7を出力する。

【0009】

位相選択回路92は、セレクタ回路921と、位相補間回路922−1〜922−4とを備えている。セレクタ回路921は、CDR制御回路93の制御に応じて、4相−8相変換回路91から入力される8つのクロック信号OUT0〜OUT7から、位相補間回路922−1〜922−4それぞれに入力するクロック信号の組合せを選択する。位相補間回路922−1〜922−4は、セレクタ回路921から入力された組合せのクロック信号を合成して、位相の異なる8つのクロック信号CLK000〜CLK315を出力する。

CDR制御回路93は、CDR回路において、サンプリングされたエッジサンプルとデータサンプルとに基づいて、位相選択回路92が出力するクロック信号CLK00〜CLK315の位相を制御する制御信号SELC、SELPを位相選択回路92に出力する。

【0010】

このように、多相クロック発生回路9は、2つの位相の異なる信号から中間的な位相を有する信号を生成する位相補間回路913−1〜913−4、922−1〜922−4の機能を利用した回路である。出力段の位相補間回路922−1〜922−4では、入力されるクロック信号の組合せにより、連続したクロックの位相を作り出している。

これらの位相補間回路では、入力される2つのクロック信号を合成して中間的な位相を有するクロック信号を生成しているため、位相補間回路を設計する際に定めた動作周波数に応じて、位相補間回路を構成するトランジスタのサイズ(幅(W)/長さ(L))と、位相補間回路に入力するクロック信号の立ち上がり及び立ち下がりに要する時間を最適化する必要があった。このため、一つの位相補間回路で複数の動作周波数に対応することが困難であった。

【0011】

これに対して、多相クロック発生回路9を動作周波数の高い方に合わせて設計を行い、低い動作周波数で用いる際には、後段に分周回路を設けることで対応をすることが行われていた。

図12は、複数の動作周波数に対応した多相クロック発生回路9Aの構成例を示す回路図である。同図に示すように、多相クロック発生回路9Aは、多相クロック発生回路9の後段に1/2分周回路94を設けた構成になっている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2011−097314号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、多相クロック発生回路に分周回路を追加する場合、8相クロック信号を出力する多相クロック発生回路では、8個分の分周回路が必要となり、回路の実装面積の増加や、消費電力の増加などを招いてしまうという問題があった。

また、位相補間回路の特徴として、一般的に、設計値の動作周波数に対して、入力するクロック信号の周波数を下げてしまうと、入力される2つのクロック信号の位相差が大きくなるために出力波形の歪みが大きくなり、最悪の場合、出力波形に段が生じジッタ特性が低下するなどの問題がある。

【0014】

図13は、位相補間回路における出力波形の歪みの例を示す波形図である。ここでは、位相補間回路における設計値の動作周波数が2.5[GHz]であり、出力信号の周波数(fout)を2.5[GHz]にした場合と、出力信号の周波数(fout)を1.25[GHz]にした場合とについて説明する。図13(B)は、図13(A)に対して入力する信号の波形をなまらせている。

図13(A)では、fout=1.25[GHz]とした場合に、信号変化の途中に段が生じていることが分かる。また、図13(B)では、信号変化の途中に生じる段を低減させるために信号の波形をなまらせているが、段は残りジッタ特性を低下させてしまっている。

【0015】

本発明は、上記問題を解決すべくなされたもので、その目的は、回路規模の増加を抑えかつ出力信号のジッタ特性を低下させずに、複数の動作周波数に対応できる多相クロック発生回路、及び多相クロック発生方法を提供することにある。

【課題を解決するための手段】

【0016】

上記問題を解決するために、本発明は、位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスと、前記リファレンスクロック信号の周波数に基づいて、前記複数の遅延パスのうち、前記リファレンスクロック信号の周波数に対応する遅延パスを選択するスイッチ部と、前記スイッチ部が選択した遅延パスにより、位相差が変更された前記複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間回路とを備えることを特徴とする多相クロック発生回路である。

【0017】

また、本発明は、位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスを備える多相クロック発生回路における多相クロック発生方法であって、前記リファレンスクロック信号の周波数に基づいて、前記複数の遅延パスのうち、前記リファレンスクロック信号の周波数に対応する遅延パスを選択する選択ステップと、前記選択ステップにおいて選択した遅延パスにより、位相差が変更された前記複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間ステップとを有することを特徴とする多相クロック発生方法である。

【発明の効果】

【0018】

この発明によれば、リファレンスクロック信号が取り得る周波数ごとに設けられた遅延パスのうち、入力されたリファレンスクロック信号の周波数に対応する遅延パスを選択し、選択した遅延パスを用いて位相を変更させたリファレンスクロック信号を位相補間回路に入力する。これにより、入力された複数のリファレンスクロック信号の周波数に応じた位相差を各リファレンスクロック信号に与えることで、位相補間回路に入力するリファレンスクロック信号の位相差を一定にすることができ、信号変化の途中で段が生じることを防ぎ、出力信号のジッタ特性の低下を抑制することができる。また、分周回路等を設けずに複数の周波数に対応することができるので、回路規模の増加を抑えることができる。

【図面の簡単な説明】

【0019】

【図1】本実施形態におけるCDR回路1の構成を示す概略ブロック図である。

【図2】本実施形態における多相クロック発生回路11の構成例を示す回路図である。

【図3】本実施形態における位相補間回路114−1〜114−4の構成例を示す回路図である。

【図4】本実施形態における位相補間回路152−1〜152−4のブロック図及び入出力波形図である。

【図5】本実施形態における位相補間回路152の構成例を示す回路図である。

【図6】本実施形態における多相クロック発生回路11が動作周波数2.5[GHz]において動作するときの状態を示す概略図である。

【図7】本実施形態における4相−8相変換回路11の入力信号及び出力信号の概要を示す図である。

【図8】本実施形態における制御信号(信号SELC、信号SELP)の組合せを示す図である。

【図9】本実施形態における位相選択回路150が出力するクロック出力信号の波形変化の概要を示す図である。

【図10】本実施形態における多相クロック発生回路11が動作周波数1.25[GHz]において動作するときの状態を示す概略図である。

【図11】CDR回路に設けられる多相クロック発生回路9の構成例を示す回路図である。

【図12】複数の動作周波数に対応した多相クロック発生回路9Aの構成例を示す回路図である。

【図13】位相補間回路における出力波形の歪みの例を示す波形図である。

【発明を実施するための形態】

【0020】

以下、図面を参照して、本発明の実施形態における多相クロック発生回路、及び多相クロック発生方法を説明する。

【0021】

図1は、本実施形態におけるCDR回路1の構成を示す概略ブロック図である。同図に示すように、CDR回路1には、外部からシリアルデータ及び周波数切替信号が入力され、受信側の装置に設けられたPLL回路2から4相のリファレンスクロック信号が入力される。4相のリファレンスクロック信号は、位相の基準となる1つのリファレンスクロック信号と、当該リファレンスクロック信号に対して90°、180°、270°の位相差を有する3つのリファレンスクロック信号とからなる。CDR回路1は、4相のレファレンスクロック信号、周波数切替信号、及びシリアルデータに基づいて、シリアルデータのエッジを検出し、シリアルデータに含まれるデータビットを読み出し、読み出したデータビットをリカバリデータとして出力する。周波数切替信号は、入力されるリファレンスクロック信号の周波数を示す信号である。

【0022】

CDR回路1は、多相クロック発生回路11と、サンプラー回路12と、CDR制御回路13とを具備している。

多相クロック発生回路11は、CDR制御回路13から入力される制御信号と、4相のリファレンスクロック信号と、周波数切替信号とに基づいて、4相のデータクロック信号及び4相のエッジクロック信号としての8相のクロック出力信号を生成する。

サンプラー回路12は、多相クロック発生回路11が生成された8相のクロック出力信号(リカバリクロック信号)を用いて、受信したシリアルデータをサンプリングし、エッジサンプルとデータサンプルとを出力する。データサンプルは、リカバリデータとして外部に出力される。

CDR制御回路13は、サンプラー回路12が出力するエッジサンプルとデータサンプルとに基づいて、シリアルデータをサンプリングするための最適なリカバリクロック信号の位相を決定する。また、CDR制御回路13は、決定した位相に一致するリカバリクロック信号が多相クロック発生回路11において生成されるように、制御信号を多相クロック発生回路11に出力する。

【0023】

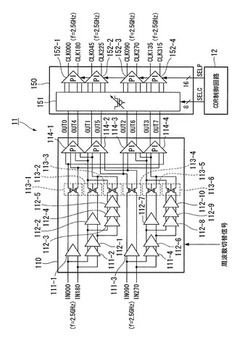

図2は、本実施形態における多相クロック発生回路11の構成例を示す回路図である。同図に示すように、多相クロック発生回路11は、4相−8相変換回路110と、位相選択回路150とを備えている。本実施形態では、多相クロック発生回路11が、2.5[GHz]の動作周波数と、1.25[GHz]の動作周波数との2つの動作周波数に対応する構成について説明する。

【0024】

4相−8相変換回路110は、入力される4相のリファレンスクロック信号及び周波数切替信号に基づいて、8相のクロック信号OUT0〜OUT7を出力する。以下、4相のリファレンスクロック信号のうち、基準とするクロックをクロック信号IN000といい、クロック信号IN000に対して90°、180°、270°の位相差を有するリファレンスクロック信号をクロック信号IN090、IN180、IN270という。

4相−8相変換回路110は、バッファ111−1〜111−4と、遅延バッファ112−1〜112−10と、スイッチ113−1〜113−6と、位相補間回路114−1〜114−4とを有している。なお、スイッチ113−1〜113−6は、P型チャネルMOSトランジスタを用いて構成したパススイッチであり、スイッチ部を構成している。

【0025】

バッファ111−1は、入力されるクロック信号IN000、IN180をスイッチ113−1に出力する。スイッチ113−1は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、バッファ111−1から入力されるクロック信号IN000、IN180を位相補間回路114−1と位相補間回路114−4とに出力し、オフの場合、バッファ111−1と、位相補間回路114−1及び位相補間回路114−4との間を遮断する。

【0026】

バッファ111−2は、入力されるクロック信号IN000、IN180を遅延バッファ112−1に出力する。遅延バッファ112−1は、バッファ111−2から入力されるクロック信号IN000、IN180に遅延を加えて、遅延を加えたクロック信号IN000、IN180を遅延バッファ112−2と遅延バッファ112−3とに出力する。

【0027】

遅延バッファ112−2は、遅延バッファ112−1から入力されるクロック信号IN000、IN180に更に遅延を加え、遅延を加えたクロック信号IN000、IN180をスイッチ113−2に出力する。スイッチ113−2は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、遅延バッファ112−2から入力されるクロック信号IN000、IN180を位相補間回路114−1及び位相補間回路114−2に出力し、オフの場合、遅延バッファ112−2と、位相補間回路114−1及び位相補間回路114−2との間を遮断する。

【0028】

遅延バッファ112−3は、遅延バッファ112−1から入力されるクロック信号IN000、IN180に更に遅延を加え、遅延を加えたクロック信号IN000、IN180を、遅延バッファ112−4、112−5を介してスイッチ113−3に出力する。スイッチ113−3は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、遅延バッファ112−5から入力されるクロック信号IN000、IN180を位相補間回路114−1及び位相補間回路114−2に出力し、オフの場合、遅延バッファ112−5と、位相補間回路114−1及び位相補間回路114−2との間を遮断する。

【0029】

バッファ111−3は、入力されるクロック信号IN090、IN270をスイッチ113−4に出力する。スイッチ113−4は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、バッファ111−3から入力されるクロック信号IN090、IN270を位相補間回路114−2と位相補間回路114−3とに出力し、オフの場合、バッファ111−3と、位相補間回路114−2及び位相補間回路114−3との間を遮断する。

【0030】

バッファ111−4は、入力されるクロック信号IN090、IN270を遅延バッファ112−6に出力する。遅延バッファ112−6は、バッファ111−4から入力されるクロック信号IN090、IN270に遅延を加えて、遅延を加えたクロック信号IN090、IN270を遅延バッファ112−7と遅延バッファ112−8とに出力する。

【0031】

遅延バッファ112−7は、遅延バッファ112−6から入力されるクロック信号IN090、IN270に更に遅延を加え、遅延を加えたクロック信号IN090、IN270をスイッチ113−5に出力する。スイッチ113−5は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、遅延バッファ112−7から入力されるクロック信号IN090、IN270を位相補間回路114−3及び位相補間回路114−4に出力し、オフの場合、遅延バッファ112−7と、位相補間回路114−3及び位相補間回路114−4との間を遮断する。

【0032】

遅延バッファ112−8は、遅延バッファ112−1から入力されるクロック信号IN090、IN270に更に遅延を加え、遅延を加えたクロック信号IN090、IN270を、遅延バッファ112−9、112−10を介してスイッチ113−6に出力する。スイッチ113−6は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、遅延バッファ112−10から入力されるクロック信号IN090、IN270を位相補間回路114−3及び位相補間回路114−4に出力し、オフの場合、遅延バッファ112−10と、位相補間回路114−3及び位相補間回路114−4との間を遮断する。

【0033】

バッファ111−1〜111−4は、CML(Current Mode Logic)で構成されたバッファであり、スイッチ113−1〜113−6におけるオン・オフを切り替える際に生じるスイッチングノイズの伝播を防止するために設けられている。なお、スイッチ113−1〜113−6のスイッチングノイズの影響が小さい場合は省略してもよい。

【0034】

遅延バッファ112−1〜112−10は、それぞれが同じ遅延量を有している。

バッファ111−2、遅延バッファ112−1、遅延バッファ112−2を経由して位相補間回路114−1及び位相補間回路114−2に到達する遅延パスは、2.5[GHz]の動作周波数に対して45°の位相に相当する遅延を、クロック信号IN000、IN180に加える。

バッファ111−2、遅延バッファ112−1、遅延バッファ112−3〜112−5を経由して位相補間回路114−1及び位相補間回路114−2に到達する遅延パスは、1.25[GHz]の動作周波数に対して45°の位相に相当する遅延を、クロック信号IN000、IN180に加える。

【0035】

バッファ111−4、遅延バッファ112−6、遅延バッファ112−7を経由して位相補間回路114−3及び位相補間回路114−4に到達する遅延パスは、2.5[GHz]の動作周波数に対して45°の位相に相当する遅延を、クロック信号IN090、IN270に加える。

バッファ111−4、遅延バッファ112−6、遅延バッファ112−8〜112−10を経由して位相補間回路114−3及び位相補間回路114−4に到達する遅延パスは、1.25[GHz]の動作周波数に対して45°の位相に相当する遅延を、クロック信号IN090、IN270に加える。

【0036】

スイッチ113−1〜113−6は、入力されるクロック信号IN000〜IN270の周波数が2.5[GHz]の場合、すなわち動作周波数が2.5[GHz]の場合、周波数切替信号により、スイッチ113−1、113−2、113−4、114−5がオンになり、スイッチ113−3、113−6がオフになる。これに対して、入力されるクロック信号IN000〜IN270の周波数が1.25[GHz]の場合、すなわち動作周波数が1.25[GHz]の場合、周波数切替信号により、スイッチ113−1、113−3、113−4、113−6がオンになり、スイッチ113−2、113−3がオフになる。

【0037】

位相補間回路114−1には、スイッチ113−1を介してクロック信号IN000、IN180が入力されると共に、スイッチ113−2又はスイッチ113−3を介して45°の遅延を加えられたクロック信号IN000、IN180が入力される。

位相補間回路114−1は、クロック信号IN000と、45°の遅延を加えられたクロック信号IN000とを合成し、クロック信号OUT0として出力する。また、位相補間回路114−1は、クロック信号IN180と、45°の遅延を加えられたクロック信号IN180とを合成し、クロック信号OUT4として出力する。

【0038】

位相補間回路114−2には、スイッチ113−2又はスイッチ113−3を介して45°の遅延を加えられたクロック信号IN000、IN180が入力されると共に、スイッチ113−4を介してクロック信号IN090、IN270が入力される。

位相補間回路114−2は、45°の遅延を加えられたクロック信号IN000と、クロック信号IN090とを合成し、クロック信号OUT1として出力する。また、位相補間回路114−2は、45°の遅延を加えられたクロック信号IN180と、クロック信号IN270とを合成し、クロック信号OUT5として出力する。

【0039】

位相補間回路114−3には、スイッチ113−4を介してクロック信号IN090、IN270が入力されると共に、スイッチ113−5又はスイッチ113−6を介して45°の遅延を加えられたクロック信号IN090、IN270が入力される。

位相補間回路114−3は、クロック信号IN90と、45°の遅延を加えられたクロック信号IN090とを合成し、クロック信号OUT2として出力する。また、位相補間回路114−3は、クロック信号IN270と、45°の遅延を加えられたクロック信号IN270とを合成し、クロック信号OUT6として出力する。

【0040】

位相補間回路114−4には、スイッチ113−5又はスイッチ113−6を介して45°の遅延を加えられたクロック信号IN090、IN270が入力されると共に、スイッチ113−1を介してクロック信号IN000、IN180が入力される。

位相補間回路114−4は、45°の遅延を加えられたクロック信号IN090と、クロック信号IN180とを合成し、クロック信号OUT3として出力する。また、位相補間回路114−4は、45°の遅延を加えられたクロック信号IN270と、クロック信号IN000とを合成し、クロック信号OUT7として出力する。

【0041】

図3は、本実施形態における位相補間回路114−1〜114−4の構成例を示す回路図である。同図に示すように、位相補間回路114−1〜114−4(以下、位相補間回路114という)は、N型チャネルのMOSトランジスタT1〜T4と、抵抗R1、R2と、電流源Ia、Ibとを有している。

MOSトランジスタT1、T3は、それぞれのドレインが共通に接続されて、抵抗R1を介して電源電位VDDに接続されている。MOSトランジスタT2、T4は、それぞれのドレインが共通に接続されて、抵抗R2を介して電源電位VDDに接続されている。

MOSトランジスタT1、T2は、それぞれのソースが共通に接続されて、電流源Iaを介して接地されている。MOSトランジスタT3、T4は、それぞれのソースが共通に接続されて、電流源Ibを介して接地されている。

【0042】

MOSトランジスタT1はゲートが入力端子Aに接続されている。MOSトランジスタT2はゲートが入力端子ABに接続されている。MOSトランジスタT3はゲートが入力端子Bに接続されている。MOSトランジスタT4はゲートが入力端子BBに接続されている。

MOSトランジスタT1、T3の共通接続されたドレインと抵抗R1との間に出力端子OUTBが接続されている。MOSトランジスタT2、T4の共通接続されたドレインと抵抗R2との間に出力端子OUTが接続されている。

【0043】

MOSトランジスタT1、T3のゲート幅とゲート長との比(W1/L1)と、MOSトランジスタT2、T4のゲート幅とゲート長との比(W2/L2)とは、予め定められた第1の比(例えば、6:4)になっている。また、電流源Iaと電流源Ibとが供給する電流も同様に、第1の比になっている。これにより、入力端子Aから入力される信号と、入力端子Bから入力される信号とが第1の比に基づいて合成され、出力端子OUTBか出力される。また、入力端子ABから入力される信号と、入力端子BBから入力される信号とが第1の比に基づいて合成され、出力端子OUTから出力される。

【0044】

例えば、位相補間回路114−1において、入力端子Aにはクロック信号IN000が入力され、入力端子Bには45°の遅延を加えられたクロック信号IN000が入力され、入力端子ABにはクロック信号IN180が入力され、入力端子BBには45°の遅延を加えられたクロック信号IN180が入力される。このとき、出力端子OUTBからクロック信号OUT0が出力され、出力端子OUTからクロック信号OUT4が出力される。なお、位相補間回路の動作原理については、例えば、参考文献1に記載されているので、ここでは詳細な説明を省略する(参考文献1:William J. Dally, John W. Poulton著、黒田忠広訳、「デジタルシステム工学 応用編」、丸善、平成15年3月、p.759−p.762)。

【0045】

上述の構成により、4相−8相変換回路110は、遅延バッファ112−1〜112−10がクロック信号IN000、IN090、IN180、IN270それぞれに対して45°の位相に対応する遅延を加えた信号を生成し、位相補間回路114−1〜114−4がクロック信号IN000、IN090、IN180、IN270と、45°の位相を有する4つのクロック信号とを波形合成することで、精度のよい8相のクロック信号OUT0〜OUT7を生成する。

【0046】

図2に戻って、多相クロック発生回路11の構成の説明を続ける。

位相選択回路150は、CDR制御回路13から入力される制御信号に基づいて、4相−8相変換回路110が出力するクロック信号OUT0〜OUT8からクロック出力信号CLK000〜CLK315を生成する。また、位相選択回路150は、セレクタ回路151と、位相補間回路152−1〜152−4とを有している。ここで、CDR制御回路13から入力される制御信号は、位相選択回路150を制御する信号SELCと、位相補間回路152−1〜152−4を制御する信号SELPとを含んでいる。

【0047】

セレクタ回路151は、CDR制御回路13から入力される信号SELCに基づいて、位相補間回路152−1〜152−4に対して、4相−8相変換回路110から出力されるクロック信号OUT0〜OUT8からクロック信号の4つの組合せを選択し、選択した4つの組合せのクロック信号を出力する。

【0048】

具体的な組合せとして、セレクタ回路151は、クロック信号OUT0、OUT4、OUT1、OUT5の組合せを位相補間回路152−1に出力し、クロック信号OUT1、OUT5、OUT2、OUT6の組合せを位相補間回路152−2に出力し、クロック信号OUT2、OUT6、OUT3、OUT7の組合せを位相補間回路152−3に出力し、クロック信号OUT3、OUT7、OUT4、OUT0の組合せを位相補間回路152−4に出力する。

すなわち、セレクタ回路151は、クロック信号OUT0、OUT4と、クロック信号OUT1、OUT5と、クロック信号OUT2、OUT6と、クロック信号OUT3、OUT7とから順に異なる4つのクロック信号の組合せを、信号SELCに基づいて選択し、選択した組合せを各位相補間回路152−1〜152−4に出力する。

【0049】

位相補間回路152−1〜152−4は、セレクタ回路151から入力される4つのクロック信号を、信号SELPに基づいて合成して出力する。

図4は、本実施形態における位相補間回路152−1〜152−4のブロック図及び入出力波形図である。図4(a)は、位相補間回路152−1〜152−4(以下、位相補間回路152という)を示すブロック図である。位相補間回路152は、2系統の位相の異なるクロック信号を入力し、入力されたクロック信号を補完し、中間の位相を作り出す回路である。図4(b)は、位相補間回路152の入力波形と出力波形との概要を示す図である。同図に示すように、位相補間回路152は、信号SELPの示す値に応じた比で、入力された信号Aと信号Bとを補完して、中間の位相の信号を作り出す。例えば、信号SELP[15:0]が(0/16)を示すとき、信号Aと信号Bとを1:0の比で合成する。すなわち、信号Aを出力する。また、信号SELP[15:0]が(7/16)を示すとき、信号Aと信号Bとを1:1の比で合成する。

【0050】

位相補間回路152は、セレクタ回路151によって45°位相がずれた信号が常に入力され、これらの中間位相(遅延)の信号を信号SELP[15:0]に応じて16段階で切り替えて出力する。位相補間回路152が出力する信号における位相の解像度は、16段階(ステップ)で設計した場合、2.8125°/ステップ(=45°÷16ステップ)である。CDR回路1に対するシリアルデータの伝送速度が10[Gbps]の場合、1UI(Unit Interval)が100[ps]であり、45°=50[ps]となり、3.125[ps/ステップ](=50[ps]÷16ステップ)の刻みでクロックの位相を微調整することができる。

位相補間回路152には、位相が45°異なるクロック信号を入力端子A(AB)と入力端子B(BB)とに入力し、信号SELP[15:0]から生成される制御ビット(SA、SB)により、選択された位相の信号が出力端子OUT(OUTB)から出力される。

【0051】

図5は、本実施形態における位相補間回路152の構成例を示す回路図である。同図に示すように、位相補間回路152は、N型チャネルのMOSトランジスタM1〜M4と、抵抗R3、R4と、スイッチ群SWa及び定電流源Uaからなる電流源aと、スイッチ群SWb及び定電流源Ubからなる電流源bとを有している。

MOSトランジスタM1、M3は、それぞれのドレインが共通に接続されて、抵抗R3を介して電源電位VDDに接続されている。MOSトランジスタM2、M4は、それぞれのドレインが共通に接続されて、抵抗R4を介して電源電位VDDに接続されている。

MOSトランジスタM1、M2は、それぞれのソースが共通に接続されて、電流源aを介して接地されている。MOSトランジスタM3、M4は、それぞれのソースが共通に接続されて、電流源bを介して接地されている。

【0052】

MOSトランジスタM1はゲートが入力端子Aに接続されている。MOSトランジスタM2はゲートが入力端子ABに接続されている。MOSトランジスタM3はゲートが入力端子Bに接続されている。MOSトランジスタM4はゲートが入力端子BBに接続されている。

MOSトランジスタM1、M3の共通接続されたドレインと抵抗R3との間に出力端子OUTBが接続されている。MOSトランジスタM2、M4の共通接続されたドレインと抵抗R4との間に出力端子OUTが接続されている。

【0053】

電流源aは、16個の単位電流源からなる定電流源Uaと、定電流源Uaが有する単位電流源のオン・オフを切り替える16個の電流スイッチからなる電流スイッチ群SWaとで構成されている。電流スイッチ群SWaの各電流スイッチと、制御ビットSB[15:0]の各ビットとは一対一に対応しており、それぞれの電流スイッチは対応する制御ビットの値が1のときにオンし、0のときにオフする。

電流源bは、電流源aと同様の構成を有しており、16個の単位電流源からなる定電流源Ubと、定電流源Ubが有する単位電流源のオン・オフを切り替える16個の電流スイッチからなる電流スイッチ群SWbとで構成されている。電流スイッチ群SWbの各電流スイッチと、制御ビットSA[15:0]の各ビットとは一対一に対応しており、それぞれの電流スイッチは対応する制御ビットの値が1のときにオンし、0のときにオフする。

【0054】

位相補間回路152において、電流源a側に流れる電流の振幅と、電流源b側に流れる電流の振幅とは制御ビットSA、SBによって制御され、2つの振幅の和は一定に保たれる。また、出力端子OUTの電位は、MOSトランジスタM2に流れる電流と、MOSトランジスタM4に流れる電流との和によって決定される。出力端子OUTBの電位は、MOSトランジスタM1に流れる電流と、MOSトランジスタM3に流れる電流との和によって決定される。したがって、入力端子A(AB)と入力端子B(BB)とに45°の位相差を有するクロック信号が入力されると、制御ビットSA、SBにより定まる位相のクロック信号が出力端子OUT(OUTB)から出力される。

ここで、本実施形態における信号SELP(制御ビットSA、SB)には、16ビットのサーモメータコードを用いる。これにより、電流スイッチ群SWaと電流スイッチ群SWbとにおいてオンになるスイッチの比で出力するクロック信号の位相を16段階で切り替えることができる。

【0055】

以下、多相クロック発生回路11の動作を説明する。

図6は、本実施形態における多相クロック発生回路11が動作周波数2.5[GHz]において動作するときの状態を示す概略図である。同図に示すように、多相クロック発生回路11には、基準のクロック信号IN000と、クロック信号IN000に対して90°、180°、270°の位相差を有するクロック信号IN090、IN180、IN270との4つのリファレンスクロック信号が入力される。このとき、図6に示すように、2.5[GHz]で動作させる場合、周波数切替信号によりスイッチ113−1、113−2、113−4、113−5をオンにし、スイッチ113−3、113−6をオフにする。

【0056】

このとき、バッファ111−2、遅延バッファ112−1、112−2を経由して45°の遅延を加えられたクロック信号IN000、IN180が位相補間回路114−1及び位相補間回路114−2に入力される。また、バッファ111−4、遅延バッファ112−6、112−7を経由して45°の遅延を加えられたクロック信号IN090、IN270が位相補間回路114−3及び位相補間回路114−4に入力される。

これにより、4相−8相変換回路110において、入力されたクロック信号IN000に対して、45°、135°、225°、315°の位相差を有するクロック信号が生成される。すなわち、4相のクロック信号から8相のクロック信号が生成される。

【0057】

図7は、本実施形態における4相−8相変換回路110の入力信号及び出力信号の概要を示す図である。同図において、横軸は時間を示し、縦軸は各クロック信号の振幅を示す。同図に示すように、4相−8相変換回路110から出力されるクロック信号OUT0〜OUT7は、それぞれの周波数が同じであると共に、入力されたクロック信号IN000〜IN270と同じ2.5[GHz]となる。このクロック信号OUT0〜OUT7がサンプリングクロックの基になる。

クロック信号OUT0を基準とした場合、入力されたリファレンスクロック信号において基準となるクロック信号IN000に対して、Δtの遅延を加えられたクロック信号OUT0が出力される。このクロック信号OUT0に対し、8分の1周期(T/8)ずつずれたクロック信号OUT1〜OUT7が出力される。

【0058】

位相選択回路150は、CDR制御回路13から出力された制御信号に基づいて、4相−8相変換回路110から出力されたクロック信号OUT0〜OUT7から、シリアルデータをサンプリングする際に用いるサンプリングクロックを生成し、クロック出力信号CLK000〜CLK315として出力する。

このとき、CDR制御回路13から出力される制御信号(信号SELC、信号SELP)は、図8に示すように変化する。図8は、本実施形態における制御信号(信号SELC、信号SELP)の組合せを示す図である。

【0059】

信号SELC=(00000011)、信号SELP=(00…0000)の組合せを初期状態とする。このとき、例えば、位相補間回路152−1には、入力端子Aから入力されるクロック信号OUT0と、入力端子Bから入力されるクロック信号OUT1であってクロック信号OUT0に対して45°の位相差を有するクロック信号OUT1とが入力される。位相補間回路152−1は、信号SELP=(00…0000)の示す値に応じて、入力端子Aの信号と、入力端子Bの信号とを16:0で合成して出力する。すなわち、クロック信号OUT0を出力する。

【0060】

位相補間回路152は、信号SELPにおける「1」の数が増えると、出力する信号における入力端子Bの信号の割合を増加させ、信号SELP=(11…1111)になると、入力端子Aの信号と、入力端子Bの信号とを0:16で合成した信号を出力する。CDR制御回路13は、信号SELP=(11…1111)をするタイミングで、信号SELCを(00000011)から(00000110)に変更する。

これにより、セレクタ回路151は、クロック信号OUT1、OUT5、OUT2、OUT6の組合せを位相補間回路152−1に出力し、クロック信号OUT2、OUT6、OUT3、OUT7の組合せを位相補間回路152−2に出力し、クロック信号OUT3、OUT7、OUT4、OUT0の組合せを位相補間回路152−3に出力し、クロック信号OUT4、OUT0、OUT5、OUT1の組合せを位相補間回路152−4に出力する。

【0061】

このように、位相選択回路150は、信号SELP[15:0]による1ステップごとの遅延変化と、16ステップごとに位相の組合せを切り替えることで、図9に示すように、クロック出力信号CLK000〜CLK315の位相(遅延)を360°に亘って、2.8125°刻みで切り替えることができる。図9には、本実施形態における位相選択回路150が出力するクロック出力信号の波形変化の概要が示されている。

また、出力クロックの位相を360°に亘って、2.8125°刻みで切り替える際、信号SELCと信号SELPとは、図8に示した組合せパターンで順に遷移する。

【0062】

図10は、本実施形態における多相クロック発生回路11が動作周波数1.25[GHz]において動作するときの状態を示す概略図である。同図に示すように、多相クロック発生回路11には、基準のクロック信号IN000と、クロック信号IN000に対して90°、180°、270°の位相差を有するクロック信号IN090、IN180、IN270との4つのリファレンスクロック信号が入力される。このとき、図8に示すように、1.25[GHz]で動作させる場合、周波数切替信号によりスイッチ113−1、113−3、113−4、113−6をオンにし、スイッチ113−2、113−5をオフにする。

【0063】

周波数切替信号に応じて、スイッチ113−1〜113−6を切り替えることにより、クロック信号IN000、IN180がバッファ111−2を介して位相補間回路114−1及び位相補間回路114−2に入力されるまでの遅延パスにおけるバッファの段数が、3段から5段に切り替えられる。これにより、クロック信号IN000、IN180に対して、1.25[GHz]における45°の位相に相当する100[ps]の遅延が加えられて、位相補間回路114−1及び位相補間回路114−2に入力される。同様に、クロック信号IN090、IN270に対して、1.25[GHz]における45°の位相に相当する100[ps]の遅延が加えられて、位相補間回路114−3及び位相補間回路114−4に入力される。

【0064】

このように、4相−8相変換回路110において、入力するクロック信号の周波数に応じて、内部に設けられている遅延パスを切り替えて用いることにより、クロック信号の周波数が1.25[GHz]である場合にも、クロック信号IN000に対して、45°、90°、135°、180°、225°、270°、315°の位相差を有するクロック信号を生成することができる。

【0065】

上述のように、本実施形態における多相クロック発生回路11は、伝送レート10[Gbps]で使用する周波数2.5[GHz]に最適化された遅延パス(バッファ111−2→遅延バッファ112−1→遅延バッファ112−2、及びバッファ111−4→遅延バッファ112−6→遅延バッファ112−7)を有する。また、多相クロック発生回路11は、伝送レート5[Gbps]で使用する周波数1.25[GHz]に最適化された遅延パス(バッファ111−2→遅延バッファ112−1→遅延バッファ112−3〜112−5、及びバッファ111−4→遅延バッファ112−6→遅延バッファ112−8〜112−10)を有する。

【0066】

多相クロック発生回路11は、外部より入力される周波数切替信号に基づいて、入力されるリファレンスクロック信号の周波数に応じて最適化された遅延パスからいずれかの遅延パスを選択することで、位相選択回路150の後段に分周回路や逓倍回路を設けることなく、複数のリファレンスクロック信号の周波数に対応した動作を行うことができる。

また、多相クロック発生回路11は、設計の際に定めた位相差を有するクロック信号を位相補間回路114及び位相補間回路152に入力することができ、位相補間回路114及び位相補間回路152の出力波形に段を生じさせることなく、複数の周波数に対応した動作を行うことができる。

【0067】

また、多相クロック発生回路11は、4相−8相変換回路110において、複数の遅延パスを有することにより回路が増加しているが、スイッチ113−1〜113−6を用いて、動作に不要な出力を遮断しているので、消費電力の増加をほぼゼロ(0)に抑えることができる。

このように、本実施形態の多相クロック発生回路11を用いることにより、位相補間回路を利用したクロック・データ・リカバリ回路に対する高速化及び幅広い動作周波数への対応の要求や、低消費電力や、面積増加の抑制などの要求を満たすことができる。

また、多相クロック発生回路11を具備したCDR回路1は、動作速度に応じた位相差を有する複数のサンプリングクロック信号(クロック出力信号)を用いることができ、SERDESなどの高速インターフェース回路の精度(速度)向上を図ることができる。

【0068】

なお、本実施形態において、4相のリファレンスクロック信号を8相のリファレンスクロック信号に変換する構成を説明した。しかし、これに限ることなく、2相のリファレンスクロック信号を4相のリファレンスクロック信号に変換する2:4の構成や、2:8、4:4、4:16などの変換を行う構成としてもよい。

また、本実施形態において、4相−8相変換回路110には、2つの周波数に合わせて最適化した遅延パスを設ける構成について説明したが、3つ以上の周波数に合わせて最適化した遅延パスを設けるようにしてもよい。

【符号の説明】

【0069】

1…CDR回路

2…PLL回路

9,9A,11…多相クロック発生回路

12…サンプラー回路

13…CDR制御回路

91,110…4相−8相変換回路

92,150…位相選択回路

93,93A…CDR制御回路

111−1,111−2,111−3,111−4,911−1,911−2,911−3,911−4…バッファ

112−1,112−2,112−3,112−4,112−5,112−6,112−7,112−8,112−9,112−10,912−1,912−2,912−3,912−4…遅延バッファ

113−1,113−2,113−3,113−4,113−5,113−6…スイッチ

114,114−1,114−2,114−3、114−4,152,152−1,152−2,152−3,152−4,913−1,913−2,913−3,913−4,922−1,922−2,922−3,922−4…位相補間回路

151,921…セレクタ回路

【技術分野】

【0001】

本発明は、多相クロック発生回路、及び多相クロック発生方法に関する。

【背景技術】

【0002】

LSI間などでデジタル信号を送受信するためには、受信側で各データビットを正しいタイミングで判定する必要がある。そのため、データを送信する信号とは別にタイミング信号(クロック信号)を送信する信号線を設けることが多い。しかし、データ信号線に沿ってタイミング信号線を設ける必要があり、基板上の占有面積が増大するなどの問題が生じる。

【0003】

そこで、近年の高速シリアル伝送では、タイミング信号線を設けずに、送信側がデータ信号にタイミング信号を重畳して送信し、受信側がデータ信号のエッジ等を検出し、内部のリファレンスクロックの位相を調整することで、タイミング情報を再生している。このプロセスを、一般にクロック・データ・リカバリ(Clock Data Recovery:CDR)という。また、クロック・データ・リカバリのために受信側に設けられる回路をCDR回路という。

【0004】

CDR回路の主な構成方式には、位相同期(Phase-Locked Loop:PLL)方式、リングオシレータ方式、位相補間方式などがある。それぞれの方式には一長一短があるが、近年、伝送方式が向上するにつれて、位相補間方式を採用する事例が増えている(特許文献1)。

図11は、CDR回路に設けられる多相クロック発生回路9の構成例を示す回路図である。同図に示すように、多相クロック発生回路9は、4相−8相変換回路91と、位相選択回路92と、CDR制御回路93とを具備している。

【0005】

4相−8相変換回路91には、外部より基準のリファレンスクロックIN000と、リファレンスクロックIN000に対して、90°、180°、270°の位相差を有し、かつ同じ周波数を有するリファレンスクロックIN090、IN180、IN270が入力される。4相−8相変換回路91は、入力される4つのリファレンスクロックに基づいて、入力されるリファレンスクロックと同じ周波数を有し、位相が異なる8つのクロック信号OUT0〜OUT7を出力する。4相−8相変換回路91は、バッファ911−1〜911−4と、遅延バッファ912−1〜912−4と、位相補間回路(Phase Interpolator:PI)913−1〜913−4とを備えている。

【0006】

リファレンスクロックIN000、IN180は、バッファ911−1を介して、位相補間回路913−1と位相補間回路913−4とに入力される。また、リファレンスクロックIN000、IN180は、バッファ911−2及び遅延バッファ912−1、912−2を介して、位相補間回路913−1と位相補間回路913−2とに入力される。リファレンスクロックIN000、IN180は、遅延バッファ912−1、912−2を通過する際に45°の位相差に相当する遅延が加えられる。

【0007】

リファレンスクロックIN090、IN270は、バッファ911−3を介して、位相補間回路913−2と位相補間回路913−3とに入力される。また、リファレンスクロックIN090、IN270は、バッファ911−4及び遅延バッファ912−3、912−4を介して、位相補間回路913−3と位相補間回路913−4とに入力される。リファレンスクロックIN090、IN270は、遅延バッファ912−3、912−4を通過する際に45°の位相差に相当する遅延が加えられる。

【0008】

位相補間回路913−1〜913−4は、それぞれがバッファ911−1〜911−4及び遅延バッファ912−1〜912−4を介して入力されたリファレンスクロックを合成し、位相が異なる8つのクロック信号OUT0〜OUT7を出力する。

【0009】

位相選択回路92は、セレクタ回路921と、位相補間回路922−1〜922−4とを備えている。セレクタ回路921は、CDR制御回路93の制御に応じて、4相−8相変換回路91から入力される8つのクロック信号OUT0〜OUT7から、位相補間回路922−1〜922−4それぞれに入力するクロック信号の組合せを選択する。位相補間回路922−1〜922−4は、セレクタ回路921から入力された組合せのクロック信号を合成して、位相の異なる8つのクロック信号CLK000〜CLK315を出力する。

CDR制御回路93は、CDR回路において、サンプリングされたエッジサンプルとデータサンプルとに基づいて、位相選択回路92が出力するクロック信号CLK00〜CLK315の位相を制御する制御信号SELC、SELPを位相選択回路92に出力する。

【0010】

このように、多相クロック発生回路9は、2つの位相の異なる信号から中間的な位相を有する信号を生成する位相補間回路913−1〜913−4、922−1〜922−4の機能を利用した回路である。出力段の位相補間回路922−1〜922−4では、入力されるクロック信号の組合せにより、連続したクロックの位相を作り出している。

これらの位相補間回路では、入力される2つのクロック信号を合成して中間的な位相を有するクロック信号を生成しているため、位相補間回路を設計する際に定めた動作周波数に応じて、位相補間回路を構成するトランジスタのサイズ(幅(W)/長さ(L))と、位相補間回路に入力するクロック信号の立ち上がり及び立ち下がりに要する時間を最適化する必要があった。このため、一つの位相補間回路で複数の動作周波数に対応することが困難であった。

【0011】

これに対して、多相クロック発生回路9を動作周波数の高い方に合わせて設計を行い、低い動作周波数で用いる際には、後段に分周回路を設けることで対応をすることが行われていた。

図12は、複数の動作周波数に対応した多相クロック発生回路9Aの構成例を示す回路図である。同図に示すように、多相クロック発生回路9Aは、多相クロック発生回路9の後段に1/2分周回路94を設けた構成になっている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2011−097314号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、多相クロック発生回路に分周回路を追加する場合、8相クロック信号を出力する多相クロック発生回路では、8個分の分周回路が必要となり、回路の実装面積の増加や、消費電力の増加などを招いてしまうという問題があった。

また、位相補間回路の特徴として、一般的に、設計値の動作周波数に対して、入力するクロック信号の周波数を下げてしまうと、入力される2つのクロック信号の位相差が大きくなるために出力波形の歪みが大きくなり、最悪の場合、出力波形に段が生じジッタ特性が低下するなどの問題がある。

【0014】

図13は、位相補間回路における出力波形の歪みの例を示す波形図である。ここでは、位相補間回路における設計値の動作周波数が2.5[GHz]であり、出力信号の周波数(fout)を2.5[GHz]にした場合と、出力信号の周波数(fout)を1.25[GHz]にした場合とについて説明する。図13(B)は、図13(A)に対して入力する信号の波形をなまらせている。

図13(A)では、fout=1.25[GHz]とした場合に、信号変化の途中に段が生じていることが分かる。また、図13(B)では、信号変化の途中に生じる段を低減させるために信号の波形をなまらせているが、段は残りジッタ特性を低下させてしまっている。

【0015】

本発明は、上記問題を解決すべくなされたもので、その目的は、回路規模の増加を抑えかつ出力信号のジッタ特性を低下させずに、複数の動作周波数に対応できる多相クロック発生回路、及び多相クロック発生方法を提供することにある。

【課題を解決するための手段】

【0016】

上記問題を解決するために、本発明は、位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスと、前記リファレンスクロック信号の周波数に基づいて、前記複数の遅延パスのうち、前記リファレンスクロック信号の周波数に対応する遅延パスを選択するスイッチ部と、前記スイッチ部が選択した遅延パスにより、位相差が変更された前記複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間回路とを備えることを特徴とする多相クロック発生回路である。

【0017】

また、本発明は、位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスを備える多相クロック発生回路における多相クロック発生方法であって、前記リファレンスクロック信号の周波数に基づいて、前記複数の遅延パスのうち、前記リファレンスクロック信号の周波数に対応する遅延パスを選択する選択ステップと、前記選択ステップにおいて選択した遅延パスにより、位相差が変更された前記複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間ステップとを有することを特徴とする多相クロック発生方法である。

【発明の効果】

【0018】

この発明によれば、リファレンスクロック信号が取り得る周波数ごとに設けられた遅延パスのうち、入力されたリファレンスクロック信号の周波数に対応する遅延パスを選択し、選択した遅延パスを用いて位相を変更させたリファレンスクロック信号を位相補間回路に入力する。これにより、入力された複数のリファレンスクロック信号の周波数に応じた位相差を各リファレンスクロック信号に与えることで、位相補間回路に入力するリファレンスクロック信号の位相差を一定にすることができ、信号変化の途中で段が生じることを防ぎ、出力信号のジッタ特性の低下を抑制することができる。また、分周回路等を設けずに複数の周波数に対応することができるので、回路規模の増加を抑えることができる。

【図面の簡単な説明】

【0019】

【図1】本実施形態におけるCDR回路1の構成を示す概略ブロック図である。

【図2】本実施形態における多相クロック発生回路11の構成例を示す回路図である。

【図3】本実施形態における位相補間回路114−1〜114−4の構成例を示す回路図である。

【図4】本実施形態における位相補間回路152−1〜152−4のブロック図及び入出力波形図である。

【図5】本実施形態における位相補間回路152の構成例を示す回路図である。

【図6】本実施形態における多相クロック発生回路11が動作周波数2.5[GHz]において動作するときの状態を示す概略図である。

【図7】本実施形態における4相−8相変換回路11の入力信号及び出力信号の概要を示す図である。

【図8】本実施形態における制御信号(信号SELC、信号SELP)の組合せを示す図である。

【図9】本実施形態における位相選択回路150が出力するクロック出力信号の波形変化の概要を示す図である。

【図10】本実施形態における多相クロック発生回路11が動作周波数1.25[GHz]において動作するときの状態を示す概略図である。

【図11】CDR回路に設けられる多相クロック発生回路9の構成例を示す回路図である。

【図12】複数の動作周波数に対応した多相クロック発生回路9Aの構成例を示す回路図である。

【図13】位相補間回路における出力波形の歪みの例を示す波形図である。

【発明を実施するための形態】

【0020】

以下、図面を参照して、本発明の実施形態における多相クロック発生回路、及び多相クロック発生方法を説明する。

【0021】

図1は、本実施形態におけるCDR回路1の構成を示す概略ブロック図である。同図に示すように、CDR回路1には、外部からシリアルデータ及び周波数切替信号が入力され、受信側の装置に設けられたPLL回路2から4相のリファレンスクロック信号が入力される。4相のリファレンスクロック信号は、位相の基準となる1つのリファレンスクロック信号と、当該リファレンスクロック信号に対して90°、180°、270°の位相差を有する3つのリファレンスクロック信号とからなる。CDR回路1は、4相のレファレンスクロック信号、周波数切替信号、及びシリアルデータに基づいて、シリアルデータのエッジを検出し、シリアルデータに含まれるデータビットを読み出し、読み出したデータビットをリカバリデータとして出力する。周波数切替信号は、入力されるリファレンスクロック信号の周波数を示す信号である。

【0022】

CDR回路1は、多相クロック発生回路11と、サンプラー回路12と、CDR制御回路13とを具備している。

多相クロック発生回路11は、CDR制御回路13から入力される制御信号と、4相のリファレンスクロック信号と、周波数切替信号とに基づいて、4相のデータクロック信号及び4相のエッジクロック信号としての8相のクロック出力信号を生成する。

サンプラー回路12は、多相クロック発生回路11が生成された8相のクロック出力信号(リカバリクロック信号)を用いて、受信したシリアルデータをサンプリングし、エッジサンプルとデータサンプルとを出力する。データサンプルは、リカバリデータとして外部に出力される。

CDR制御回路13は、サンプラー回路12が出力するエッジサンプルとデータサンプルとに基づいて、シリアルデータをサンプリングするための最適なリカバリクロック信号の位相を決定する。また、CDR制御回路13は、決定した位相に一致するリカバリクロック信号が多相クロック発生回路11において生成されるように、制御信号を多相クロック発生回路11に出力する。

【0023】

図2は、本実施形態における多相クロック発生回路11の構成例を示す回路図である。同図に示すように、多相クロック発生回路11は、4相−8相変換回路110と、位相選択回路150とを備えている。本実施形態では、多相クロック発生回路11が、2.5[GHz]の動作周波数と、1.25[GHz]の動作周波数との2つの動作周波数に対応する構成について説明する。

【0024】

4相−8相変換回路110は、入力される4相のリファレンスクロック信号及び周波数切替信号に基づいて、8相のクロック信号OUT0〜OUT7を出力する。以下、4相のリファレンスクロック信号のうち、基準とするクロックをクロック信号IN000といい、クロック信号IN000に対して90°、180°、270°の位相差を有するリファレンスクロック信号をクロック信号IN090、IN180、IN270という。

4相−8相変換回路110は、バッファ111−1〜111−4と、遅延バッファ112−1〜112−10と、スイッチ113−1〜113−6と、位相補間回路114−1〜114−4とを有している。なお、スイッチ113−1〜113−6は、P型チャネルMOSトランジスタを用いて構成したパススイッチであり、スイッチ部を構成している。

【0025】

バッファ111−1は、入力されるクロック信号IN000、IN180をスイッチ113−1に出力する。スイッチ113−1は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、バッファ111−1から入力されるクロック信号IN000、IN180を位相補間回路114−1と位相補間回路114−4とに出力し、オフの場合、バッファ111−1と、位相補間回路114−1及び位相補間回路114−4との間を遮断する。

【0026】

バッファ111−2は、入力されるクロック信号IN000、IN180を遅延バッファ112−1に出力する。遅延バッファ112−1は、バッファ111−2から入力されるクロック信号IN000、IN180に遅延を加えて、遅延を加えたクロック信号IN000、IN180を遅延バッファ112−2と遅延バッファ112−3とに出力する。

【0027】

遅延バッファ112−2は、遅延バッファ112−1から入力されるクロック信号IN000、IN180に更に遅延を加え、遅延を加えたクロック信号IN000、IN180をスイッチ113−2に出力する。スイッチ113−2は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、遅延バッファ112−2から入力されるクロック信号IN000、IN180を位相補間回路114−1及び位相補間回路114−2に出力し、オフの場合、遅延バッファ112−2と、位相補間回路114−1及び位相補間回路114−2との間を遮断する。

【0028】

遅延バッファ112−3は、遅延バッファ112−1から入力されるクロック信号IN000、IN180に更に遅延を加え、遅延を加えたクロック信号IN000、IN180を、遅延バッファ112−4、112−5を介してスイッチ113−3に出力する。スイッチ113−3は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、遅延バッファ112−5から入力されるクロック信号IN000、IN180を位相補間回路114−1及び位相補間回路114−2に出力し、オフの場合、遅延バッファ112−5と、位相補間回路114−1及び位相補間回路114−2との間を遮断する。

【0029】

バッファ111−3は、入力されるクロック信号IN090、IN270をスイッチ113−4に出力する。スイッチ113−4は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、バッファ111−3から入力されるクロック信号IN090、IN270を位相補間回路114−2と位相補間回路114−3とに出力し、オフの場合、バッファ111−3と、位相補間回路114−2及び位相補間回路114−3との間を遮断する。

【0030】

バッファ111−4は、入力されるクロック信号IN090、IN270を遅延バッファ112−6に出力する。遅延バッファ112−6は、バッファ111−4から入力されるクロック信号IN090、IN270に遅延を加えて、遅延を加えたクロック信号IN090、IN270を遅延バッファ112−7と遅延バッファ112−8とに出力する。

【0031】

遅延バッファ112−7は、遅延バッファ112−6から入力されるクロック信号IN090、IN270に更に遅延を加え、遅延を加えたクロック信号IN090、IN270をスイッチ113−5に出力する。スイッチ113−5は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、遅延バッファ112−7から入力されるクロック信号IN090、IN270を位相補間回路114−3及び位相補間回路114−4に出力し、オフの場合、遅延バッファ112−7と、位相補間回路114−3及び位相補間回路114−4との間を遮断する。

【0032】

遅延バッファ112−8は、遅延バッファ112−1から入力されるクロック信号IN090、IN270に更に遅延を加え、遅延を加えたクロック信号IN090、IN270を、遅延バッファ112−9、112−10を介してスイッチ113−6に出力する。スイッチ113−6は、周波数切替信号によりオンとオフとが切り替えられ、オンの場合、遅延バッファ112−10から入力されるクロック信号IN090、IN270を位相補間回路114−3及び位相補間回路114−4に出力し、オフの場合、遅延バッファ112−10と、位相補間回路114−3及び位相補間回路114−4との間を遮断する。

【0033】

バッファ111−1〜111−4は、CML(Current Mode Logic)で構成されたバッファであり、スイッチ113−1〜113−6におけるオン・オフを切り替える際に生じるスイッチングノイズの伝播を防止するために設けられている。なお、スイッチ113−1〜113−6のスイッチングノイズの影響が小さい場合は省略してもよい。

【0034】

遅延バッファ112−1〜112−10は、それぞれが同じ遅延量を有している。

バッファ111−2、遅延バッファ112−1、遅延バッファ112−2を経由して位相補間回路114−1及び位相補間回路114−2に到達する遅延パスは、2.5[GHz]の動作周波数に対して45°の位相に相当する遅延を、クロック信号IN000、IN180に加える。

バッファ111−2、遅延バッファ112−1、遅延バッファ112−3〜112−5を経由して位相補間回路114−1及び位相補間回路114−2に到達する遅延パスは、1.25[GHz]の動作周波数に対して45°の位相に相当する遅延を、クロック信号IN000、IN180に加える。

【0035】

バッファ111−4、遅延バッファ112−6、遅延バッファ112−7を経由して位相補間回路114−3及び位相補間回路114−4に到達する遅延パスは、2.5[GHz]の動作周波数に対して45°の位相に相当する遅延を、クロック信号IN090、IN270に加える。

バッファ111−4、遅延バッファ112−6、遅延バッファ112−8〜112−10を経由して位相補間回路114−3及び位相補間回路114−4に到達する遅延パスは、1.25[GHz]の動作周波数に対して45°の位相に相当する遅延を、クロック信号IN090、IN270に加える。

【0036】

スイッチ113−1〜113−6は、入力されるクロック信号IN000〜IN270の周波数が2.5[GHz]の場合、すなわち動作周波数が2.5[GHz]の場合、周波数切替信号により、スイッチ113−1、113−2、113−4、114−5がオンになり、スイッチ113−3、113−6がオフになる。これに対して、入力されるクロック信号IN000〜IN270の周波数が1.25[GHz]の場合、すなわち動作周波数が1.25[GHz]の場合、周波数切替信号により、スイッチ113−1、113−3、113−4、113−6がオンになり、スイッチ113−2、113−3がオフになる。

【0037】

位相補間回路114−1には、スイッチ113−1を介してクロック信号IN000、IN180が入力されると共に、スイッチ113−2又はスイッチ113−3を介して45°の遅延を加えられたクロック信号IN000、IN180が入力される。

位相補間回路114−1は、クロック信号IN000と、45°の遅延を加えられたクロック信号IN000とを合成し、クロック信号OUT0として出力する。また、位相補間回路114−1は、クロック信号IN180と、45°の遅延を加えられたクロック信号IN180とを合成し、クロック信号OUT4として出力する。

【0038】

位相補間回路114−2には、スイッチ113−2又はスイッチ113−3を介して45°の遅延を加えられたクロック信号IN000、IN180が入力されると共に、スイッチ113−4を介してクロック信号IN090、IN270が入力される。

位相補間回路114−2は、45°の遅延を加えられたクロック信号IN000と、クロック信号IN090とを合成し、クロック信号OUT1として出力する。また、位相補間回路114−2は、45°の遅延を加えられたクロック信号IN180と、クロック信号IN270とを合成し、クロック信号OUT5として出力する。

【0039】

位相補間回路114−3には、スイッチ113−4を介してクロック信号IN090、IN270が入力されると共に、スイッチ113−5又はスイッチ113−6を介して45°の遅延を加えられたクロック信号IN090、IN270が入力される。

位相補間回路114−3は、クロック信号IN90と、45°の遅延を加えられたクロック信号IN090とを合成し、クロック信号OUT2として出力する。また、位相補間回路114−3は、クロック信号IN270と、45°の遅延を加えられたクロック信号IN270とを合成し、クロック信号OUT6として出力する。

【0040】

位相補間回路114−4には、スイッチ113−5又はスイッチ113−6を介して45°の遅延を加えられたクロック信号IN090、IN270が入力されると共に、スイッチ113−1を介してクロック信号IN000、IN180が入力される。

位相補間回路114−4は、45°の遅延を加えられたクロック信号IN090と、クロック信号IN180とを合成し、クロック信号OUT3として出力する。また、位相補間回路114−4は、45°の遅延を加えられたクロック信号IN270と、クロック信号IN000とを合成し、クロック信号OUT7として出力する。

【0041】

図3は、本実施形態における位相補間回路114−1〜114−4の構成例を示す回路図である。同図に示すように、位相補間回路114−1〜114−4(以下、位相補間回路114という)は、N型チャネルのMOSトランジスタT1〜T4と、抵抗R1、R2と、電流源Ia、Ibとを有している。

MOSトランジスタT1、T3は、それぞれのドレインが共通に接続されて、抵抗R1を介して電源電位VDDに接続されている。MOSトランジスタT2、T4は、それぞれのドレインが共通に接続されて、抵抗R2を介して電源電位VDDに接続されている。

MOSトランジスタT1、T2は、それぞれのソースが共通に接続されて、電流源Iaを介して接地されている。MOSトランジスタT3、T4は、それぞれのソースが共通に接続されて、電流源Ibを介して接地されている。

【0042】

MOSトランジスタT1はゲートが入力端子Aに接続されている。MOSトランジスタT2はゲートが入力端子ABに接続されている。MOSトランジスタT3はゲートが入力端子Bに接続されている。MOSトランジスタT4はゲートが入力端子BBに接続されている。

MOSトランジスタT1、T3の共通接続されたドレインと抵抗R1との間に出力端子OUTBが接続されている。MOSトランジスタT2、T4の共通接続されたドレインと抵抗R2との間に出力端子OUTが接続されている。

【0043】

MOSトランジスタT1、T3のゲート幅とゲート長との比(W1/L1)と、MOSトランジスタT2、T4のゲート幅とゲート長との比(W2/L2)とは、予め定められた第1の比(例えば、6:4)になっている。また、電流源Iaと電流源Ibとが供給する電流も同様に、第1の比になっている。これにより、入力端子Aから入力される信号と、入力端子Bから入力される信号とが第1の比に基づいて合成され、出力端子OUTBか出力される。また、入力端子ABから入力される信号と、入力端子BBから入力される信号とが第1の比に基づいて合成され、出力端子OUTから出力される。

【0044】

例えば、位相補間回路114−1において、入力端子Aにはクロック信号IN000が入力され、入力端子Bには45°の遅延を加えられたクロック信号IN000が入力され、入力端子ABにはクロック信号IN180が入力され、入力端子BBには45°の遅延を加えられたクロック信号IN180が入力される。このとき、出力端子OUTBからクロック信号OUT0が出力され、出力端子OUTからクロック信号OUT4が出力される。なお、位相補間回路の動作原理については、例えば、参考文献1に記載されているので、ここでは詳細な説明を省略する(参考文献1:William J. Dally, John W. Poulton著、黒田忠広訳、「デジタルシステム工学 応用編」、丸善、平成15年3月、p.759−p.762)。

【0045】

上述の構成により、4相−8相変換回路110は、遅延バッファ112−1〜112−10がクロック信号IN000、IN090、IN180、IN270それぞれに対して45°の位相に対応する遅延を加えた信号を生成し、位相補間回路114−1〜114−4がクロック信号IN000、IN090、IN180、IN270と、45°の位相を有する4つのクロック信号とを波形合成することで、精度のよい8相のクロック信号OUT0〜OUT7を生成する。

【0046】

図2に戻って、多相クロック発生回路11の構成の説明を続ける。

位相選択回路150は、CDR制御回路13から入力される制御信号に基づいて、4相−8相変換回路110が出力するクロック信号OUT0〜OUT8からクロック出力信号CLK000〜CLK315を生成する。また、位相選択回路150は、セレクタ回路151と、位相補間回路152−1〜152−4とを有している。ここで、CDR制御回路13から入力される制御信号は、位相選択回路150を制御する信号SELCと、位相補間回路152−1〜152−4を制御する信号SELPとを含んでいる。

【0047】

セレクタ回路151は、CDR制御回路13から入力される信号SELCに基づいて、位相補間回路152−1〜152−4に対して、4相−8相変換回路110から出力されるクロック信号OUT0〜OUT8からクロック信号の4つの組合せを選択し、選択した4つの組合せのクロック信号を出力する。

【0048】

具体的な組合せとして、セレクタ回路151は、クロック信号OUT0、OUT4、OUT1、OUT5の組合せを位相補間回路152−1に出力し、クロック信号OUT1、OUT5、OUT2、OUT6の組合せを位相補間回路152−2に出力し、クロック信号OUT2、OUT6、OUT3、OUT7の組合せを位相補間回路152−3に出力し、クロック信号OUT3、OUT7、OUT4、OUT0の組合せを位相補間回路152−4に出力する。

すなわち、セレクタ回路151は、クロック信号OUT0、OUT4と、クロック信号OUT1、OUT5と、クロック信号OUT2、OUT6と、クロック信号OUT3、OUT7とから順に異なる4つのクロック信号の組合せを、信号SELCに基づいて選択し、選択した組合せを各位相補間回路152−1〜152−4に出力する。

【0049】

位相補間回路152−1〜152−4は、セレクタ回路151から入力される4つのクロック信号を、信号SELPに基づいて合成して出力する。

図4は、本実施形態における位相補間回路152−1〜152−4のブロック図及び入出力波形図である。図4(a)は、位相補間回路152−1〜152−4(以下、位相補間回路152という)を示すブロック図である。位相補間回路152は、2系統の位相の異なるクロック信号を入力し、入力されたクロック信号を補完し、中間の位相を作り出す回路である。図4(b)は、位相補間回路152の入力波形と出力波形との概要を示す図である。同図に示すように、位相補間回路152は、信号SELPの示す値に応じた比で、入力された信号Aと信号Bとを補完して、中間の位相の信号を作り出す。例えば、信号SELP[15:0]が(0/16)を示すとき、信号Aと信号Bとを1:0の比で合成する。すなわち、信号Aを出力する。また、信号SELP[15:0]が(7/16)を示すとき、信号Aと信号Bとを1:1の比で合成する。

【0050】

位相補間回路152は、セレクタ回路151によって45°位相がずれた信号が常に入力され、これらの中間位相(遅延)の信号を信号SELP[15:0]に応じて16段階で切り替えて出力する。位相補間回路152が出力する信号における位相の解像度は、16段階(ステップ)で設計した場合、2.8125°/ステップ(=45°÷16ステップ)である。CDR回路1に対するシリアルデータの伝送速度が10[Gbps]の場合、1UI(Unit Interval)が100[ps]であり、45°=50[ps]となり、3.125[ps/ステップ](=50[ps]÷16ステップ)の刻みでクロックの位相を微調整することができる。

位相補間回路152には、位相が45°異なるクロック信号を入力端子A(AB)と入力端子B(BB)とに入力し、信号SELP[15:0]から生成される制御ビット(SA、SB)により、選択された位相の信号が出力端子OUT(OUTB)から出力される。

【0051】

図5は、本実施形態における位相補間回路152の構成例を示す回路図である。同図に示すように、位相補間回路152は、N型チャネルのMOSトランジスタM1〜M4と、抵抗R3、R4と、スイッチ群SWa及び定電流源Uaからなる電流源aと、スイッチ群SWb及び定電流源Ubからなる電流源bとを有している。

MOSトランジスタM1、M3は、それぞれのドレインが共通に接続されて、抵抗R3を介して電源電位VDDに接続されている。MOSトランジスタM2、M4は、それぞれのドレインが共通に接続されて、抵抗R4を介して電源電位VDDに接続されている。

MOSトランジスタM1、M2は、それぞれのソースが共通に接続されて、電流源aを介して接地されている。MOSトランジスタM3、M4は、それぞれのソースが共通に接続されて、電流源bを介して接地されている。

【0052】

MOSトランジスタM1はゲートが入力端子Aに接続されている。MOSトランジスタM2はゲートが入力端子ABに接続されている。MOSトランジスタM3はゲートが入力端子Bに接続されている。MOSトランジスタM4はゲートが入力端子BBに接続されている。

MOSトランジスタM1、M3の共通接続されたドレインと抵抗R3との間に出力端子OUTBが接続されている。MOSトランジスタM2、M4の共通接続されたドレインと抵抗R4との間に出力端子OUTが接続されている。

【0053】

電流源aは、16個の単位電流源からなる定電流源Uaと、定電流源Uaが有する単位電流源のオン・オフを切り替える16個の電流スイッチからなる電流スイッチ群SWaとで構成されている。電流スイッチ群SWaの各電流スイッチと、制御ビットSB[15:0]の各ビットとは一対一に対応しており、それぞれの電流スイッチは対応する制御ビットの値が1のときにオンし、0のときにオフする。

電流源bは、電流源aと同様の構成を有しており、16個の単位電流源からなる定電流源Ubと、定電流源Ubが有する単位電流源のオン・オフを切り替える16個の電流スイッチからなる電流スイッチ群SWbとで構成されている。電流スイッチ群SWbの各電流スイッチと、制御ビットSA[15:0]の各ビットとは一対一に対応しており、それぞれの電流スイッチは対応する制御ビットの値が1のときにオンし、0のときにオフする。

【0054】

位相補間回路152において、電流源a側に流れる電流の振幅と、電流源b側に流れる電流の振幅とは制御ビットSA、SBによって制御され、2つの振幅の和は一定に保たれる。また、出力端子OUTの電位は、MOSトランジスタM2に流れる電流と、MOSトランジスタM4に流れる電流との和によって決定される。出力端子OUTBの電位は、MOSトランジスタM1に流れる電流と、MOSトランジスタM3に流れる電流との和によって決定される。したがって、入力端子A(AB)と入力端子B(BB)とに45°の位相差を有するクロック信号が入力されると、制御ビットSA、SBにより定まる位相のクロック信号が出力端子OUT(OUTB)から出力される。

ここで、本実施形態における信号SELP(制御ビットSA、SB)には、16ビットのサーモメータコードを用いる。これにより、電流スイッチ群SWaと電流スイッチ群SWbとにおいてオンになるスイッチの比で出力するクロック信号の位相を16段階で切り替えることができる。

【0055】

以下、多相クロック発生回路11の動作を説明する。

図6は、本実施形態における多相クロック発生回路11が動作周波数2.5[GHz]において動作するときの状態を示す概略図である。同図に示すように、多相クロック発生回路11には、基準のクロック信号IN000と、クロック信号IN000に対して90°、180°、270°の位相差を有するクロック信号IN090、IN180、IN270との4つのリファレンスクロック信号が入力される。このとき、図6に示すように、2.5[GHz]で動作させる場合、周波数切替信号によりスイッチ113−1、113−2、113−4、113−5をオンにし、スイッチ113−3、113−6をオフにする。

【0056】

このとき、バッファ111−2、遅延バッファ112−1、112−2を経由して45°の遅延を加えられたクロック信号IN000、IN180が位相補間回路114−1及び位相補間回路114−2に入力される。また、バッファ111−4、遅延バッファ112−6、112−7を経由して45°の遅延を加えられたクロック信号IN090、IN270が位相補間回路114−3及び位相補間回路114−4に入力される。

これにより、4相−8相変換回路110において、入力されたクロック信号IN000に対して、45°、135°、225°、315°の位相差を有するクロック信号が生成される。すなわち、4相のクロック信号から8相のクロック信号が生成される。

【0057】

図7は、本実施形態における4相−8相変換回路110の入力信号及び出力信号の概要を示す図である。同図において、横軸は時間を示し、縦軸は各クロック信号の振幅を示す。同図に示すように、4相−8相変換回路110から出力されるクロック信号OUT0〜OUT7は、それぞれの周波数が同じであると共に、入力されたクロック信号IN000〜IN270と同じ2.5[GHz]となる。このクロック信号OUT0〜OUT7がサンプリングクロックの基になる。

クロック信号OUT0を基準とした場合、入力されたリファレンスクロック信号において基準となるクロック信号IN000に対して、Δtの遅延を加えられたクロック信号OUT0が出力される。このクロック信号OUT0に対し、8分の1周期(T/8)ずつずれたクロック信号OUT1〜OUT7が出力される。

【0058】

位相選択回路150は、CDR制御回路13から出力された制御信号に基づいて、4相−8相変換回路110から出力されたクロック信号OUT0〜OUT7から、シリアルデータをサンプリングする際に用いるサンプリングクロックを生成し、クロック出力信号CLK000〜CLK315として出力する。

このとき、CDR制御回路13から出力される制御信号(信号SELC、信号SELP)は、図8に示すように変化する。図8は、本実施形態における制御信号(信号SELC、信号SELP)の組合せを示す図である。

【0059】

信号SELC=(00000011)、信号SELP=(00…0000)の組合せを初期状態とする。このとき、例えば、位相補間回路152−1には、入力端子Aから入力されるクロック信号OUT0と、入力端子Bから入力されるクロック信号OUT1であってクロック信号OUT0に対して45°の位相差を有するクロック信号OUT1とが入力される。位相補間回路152−1は、信号SELP=(00…0000)の示す値に応じて、入力端子Aの信号と、入力端子Bの信号とを16:0で合成して出力する。すなわち、クロック信号OUT0を出力する。

【0060】

位相補間回路152は、信号SELPにおける「1」の数が増えると、出力する信号における入力端子Bの信号の割合を増加させ、信号SELP=(11…1111)になると、入力端子Aの信号と、入力端子Bの信号とを0:16で合成した信号を出力する。CDR制御回路13は、信号SELP=(11…1111)をするタイミングで、信号SELCを(00000011)から(00000110)に変更する。

これにより、セレクタ回路151は、クロック信号OUT1、OUT5、OUT2、OUT6の組合せを位相補間回路152−1に出力し、クロック信号OUT2、OUT6、OUT3、OUT7の組合せを位相補間回路152−2に出力し、クロック信号OUT3、OUT7、OUT4、OUT0の組合せを位相補間回路152−3に出力し、クロック信号OUT4、OUT0、OUT5、OUT1の組合せを位相補間回路152−4に出力する。

【0061】

このように、位相選択回路150は、信号SELP[15:0]による1ステップごとの遅延変化と、16ステップごとに位相の組合せを切り替えることで、図9に示すように、クロック出力信号CLK000〜CLK315の位相(遅延)を360°に亘って、2.8125°刻みで切り替えることができる。図9には、本実施形態における位相選択回路150が出力するクロック出力信号の波形変化の概要が示されている。

また、出力クロックの位相を360°に亘って、2.8125°刻みで切り替える際、信号SELCと信号SELPとは、図8に示した組合せパターンで順に遷移する。

【0062】

図10は、本実施形態における多相クロック発生回路11が動作周波数1.25[GHz]において動作するときの状態を示す概略図である。同図に示すように、多相クロック発生回路11には、基準のクロック信号IN000と、クロック信号IN000に対して90°、180°、270°の位相差を有するクロック信号IN090、IN180、IN270との4つのリファレンスクロック信号が入力される。このとき、図8に示すように、1.25[GHz]で動作させる場合、周波数切替信号によりスイッチ113−1、113−3、113−4、113−6をオンにし、スイッチ113−2、113−5をオフにする。

【0063】

周波数切替信号に応じて、スイッチ113−1〜113−6を切り替えることにより、クロック信号IN000、IN180がバッファ111−2を介して位相補間回路114−1及び位相補間回路114−2に入力されるまでの遅延パスにおけるバッファの段数が、3段から5段に切り替えられる。これにより、クロック信号IN000、IN180に対して、1.25[GHz]における45°の位相に相当する100[ps]の遅延が加えられて、位相補間回路114−1及び位相補間回路114−2に入力される。同様に、クロック信号IN090、IN270に対して、1.25[GHz]における45°の位相に相当する100[ps]の遅延が加えられて、位相補間回路114−3及び位相補間回路114−4に入力される。

【0064】

このように、4相−8相変換回路110において、入力するクロック信号の周波数に応じて、内部に設けられている遅延パスを切り替えて用いることにより、クロック信号の周波数が1.25[GHz]である場合にも、クロック信号IN000に対して、45°、90°、135°、180°、225°、270°、315°の位相差を有するクロック信号を生成することができる。

【0065】

上述のように、本実施形態における多相クロック発生回路11は、伝送レート10[Gbps]で使用する周波数2.5[GHz]に最適化された遅延パス(バッファ111−2→遅延バッファ112−1→遅延バッファ112−2、及びバッファ111−4→遅延バッファ112−6→遅延バッファ112−7)を有する。また、多相クロック発生回路11は、伝送レート5[Gbps]で使用する周波数1.25[GHz]に最適化された遅延パス(バッファ111−2→遅延バッファ112−1→遅延バッファ112−3〜112−5、及びバッファ111−4→遅延バッファ112−6→遅延バッファ112−8〜112−10)を有する。

【0066】

多相クロック発生回路11は、外部より入力される周波数切替信号に基づいて、入力されるリファレンスクロック信号の周波数に応じて最適化された遅延パスからいずれかの遅延パスを選択することで、位相選択回路150の後段に分周回路や逓倍回路を設けることなく、複数のリファレンスクロック信号の周波数に対応した動作を行うことができる。

また、多相クロック発生回路11は、設計の際に定めた位相差を有するクロック信号を位相補間回路114及び位相補間回路152に入力することができ、位相補間回路114及び位相補間回路152の出力波形に段を生じさせることなく、複数の周波数に対応した動作を行うことができる。

【0067】

また、多相クロック発生回路11は、4相−8相変換回路110において、複数の遅延パスを有することにより回路が増加しているが、スイッチ113−1〜113−6を用いて、動作に不要な出力を遮断しているので、消費電力の増加をほぼゼロ(0)に抑えることができる。

このように、本実施形態の多相クロック発生回路11を用いることにより、位相補間回路を利用したクロック・データ・リカバリ回路に対する高速化及び幅広い動作周波数への対応の要求や、低消費電力や、面積増加の抑制などの要求を満たすことができる。

また、多相クロック発生回路11を具備したCDR回路1は、動作速度に応じた位相差を有する複数のサンプリングクロック信号(クロック出力信号)を用いることができ、SERDESなどの高速インターフェース回路の精度(速度)向上を図ることができる。

【0068】

なお、本実施形態において、4相のリファレンスクロック信号を8相のリファレンスクロック信号に変換する構成を説明した。しかし、これに限ることなく、2相のリファレンスクロック信号を4相のリファレンスクロック信号に変換する2:4の構成や、2:8、4:4、4:16などの変換を行う構成としてもよい。

また、本実施形態において、4相−8相変換回路110には、2つの周波数に合わせて最適化した遅延パスを設ける構成について説明したが、3つ以上の周波数に合わせて最適化した遅延パスを設けるようにしてもよい。

【符号の説明】

【0069】

1…CDR回路

2…PLL回路

9,9A,11…多相クロック発生回路

12…サンプラー回路

13…CDR制御回路

91,110…4相−8相変換回路

92,150…位相選択回路

93,93A…CDR制御回路

111−1,111−2,111−3,111−4,911−1,911−2,911−3,911−4…バッファ

112−1,112−2,112−3,112−4,112−5,112−6,112−7,112−8,112−9,112−10,912−1,912−2,912−3,912−4…遅延バッファ

113−1,113−2,113−3,113−4,113−5,113−6…スイッチ

114,114−1,114−2,114−3、114−4,152,152−1,152−2,152−3,152−4,913−1,913−2,913−3,913−4,922−1,922−2,922−3,922−4…位相補間回路

151,921…セレクタ回路

【特許請求の範囲】

【請求項1】

位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスと、

前記リファレンスクロック信号の周波数に基づいて、前記複数の遅延パスのうち、前記リファレンスクロック信号の周波数に対応する遅延パスを選択するスイッチ部と、

前記スイッチ部が選択した遅延パスにより、位相差が変更された前記複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間回路と

を備えることを特徴とする多相クロック発生回路。

【請求項2】

前記スイッチ部は、複数のパススイッチを有し、

前記パススイッチは、前記複数の遅延パスごとに設けられ、該遅延パスと前記位相補間回路との間を接続するか否かを切り替える

ことを特徴とする請求項1に記載に多相クロック発生回路。

【請求項3】

位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスを備える多相クロック発生回路における多相クロック発生方法であって、

前記リファレンスクロック信号の周波数に基づいて、前記複数の遅延パスのうち、前記リファレンスクロック信号の周波数に対応する遅延パスを選択する選択ステップと、

前記選択ステップにおいて選択した遅延パスにより、位相差が変更された前記複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間ステップと

を有することを特徴とする多相クロック発生方法。

【請求項1】

位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスと、

前記リファレンスクロック信号の周波数に基づいて、前記複数の遅延パスのうち、前記リファレンスクロック信号の周波数に対応する遅延パスを選択するスイッチ部と、

前記スイッチ部が選択した遅延パスにより、位相差が変更された前記複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間回路と

を備えることを特徴とする多相クロック発生回路。

【請求項2】

前記スイッチ部は、複数のパススイッチを有し、

前記パススイッチは、前記複数の遅延パスごとに設けられ、該遅延パスと前記位相補間回路との間を接続するか否かを切り替える

ことを特徴とする請求項1に記載に多相クロック発生回路。

【請求項3】

位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスを備える多相クロック発生回路における多相クロック発生方法であって、

前記リファレンスクロック信号の周波数に基づいて、前記複数の遅延パスのうち、前記リファレンスクロック信号の周波数に対応する遅延パスを選択する選択ステップと、

前記選択ステップにおいて選択した遅延パスにより、位相差が変更された前記複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間ステップと

を有することを特徴とする多相クロック発生方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−46271(P2013−46271A)

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願番号】特願2011−183290(P2011−183290)

【出願日】平成23年8月25日(2011.8.25)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願日】平成23年8月25日(2011.8.25)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

[ Back to top ]