大型電子部品の実装方法

【課題】 多層基板上に複数の接続端子を含む大型の電子部品を配置する場合が増加している。かかる基板のリフロー時における過熱・冷却を減ると、基板各層の熱膨張・熱収縮が異なるために基板が反り、大型の電子部品の接続端子が浮くことがある。この接続端子の浮き対策のため、大量の余剰はんだを基板上に配置すると他の部品との短絡の問題が生じていた。

【解決手段】 接続端子に対応するランドの一部を絶縁体であるソルダーレジストで覆う一方、かかるソルダーレジスト上にもクリームはんだを盛ってリフローを行う。クリームはんだの総量は変化しないが、ランド・接続端子間の接触面積が減るためはんだの盛り高さを確保できる。

【解決手段】 接続端子に対応するランドの一部を絶縁体であるソルダーレジストで覆う一方、かかるソルダーレジスト上にもクリームはんだを盛ってリフローを行う。クリームはんだの総量は変化しないが、ランド・接続端子間の接触面積が減るためはんだの盛り高さを確保できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はプリント配線基板上に大型電子部品の実装を行うための方法に関する。

【背景技術】

【0002】

ノートパソコンやPDA、携帯電話機、デジタルオーディオプレイヤーなど、個人が携帯する携帯情報端末は増加する一方である。また、個々の携帯情報端末の機能は高度化、複雑化している。このため基板上にはCPU(セントラルプロセッシングユニット)、DSP(デジタルシグナルプロセッサ)、CCD(チャージカップルドデバイス:電荷結合素子)、HDD(ハードディスクデバイス)といった大型の部品の実装を要求される。また従来基板上にパターン構成されていた無線回路や表示部制御デバイス等も1チップ化されることで実装コストの低減を図る動きも進んでいる。

【0003】

このように、基板上には大型の電子デバイスが実装される機会が多くなっている。一方で、このような傾向が進むことで新たな問題が新たに生じている。以下この問題について述べる。

【0004】

これらを含む電子部品の実装に際して基板上にはんだを印刷等して塗布して部品を配置したのち、リフローを行うことで部品を基板上に固定する。このリフロー時に、リフロー炉の炉中は摂氏140度以上に加熱され、その後放熱されるため、リフロー対象の基板は短時間に加熱、冷却されることとなる。このように加熱等されると、基板によっては大きなそりが発生する。一般的に用いられている多層基板は、必ずしも層ごとの熱膨張率、熱収縮率が同じではないためである。

【0005】

このそりが発生すると、以下のような問題が生じる。

【0006】

図8はそりが発生した際の基1上の大型電子部品2周辺の拡大図である。ここで大型電子部品2は2以上の大型電子部品接続端子5を有するものとする。

【0007】

基板1上には大型部品を実装するためのランド7が設けられている。リフロー前においては、このランド7上にはんだ6が盛られ、その上に大型電子部品接続端子5を配置する。その後加熱、冷却することではんだ6が溶融し大型電子部品接続端子5とランド7が電気的に固定されることとなる。

【0008】

しかし、図8のように加熱・冷却工程中に基板に「そり」が発生すると複数の大型電子部品接続端子5のうち一が固定される一方、別の一は「そり」により浮き4が発生し、はんだ6による接続ができない不具合が発生してしまう。

【0009】

この「そり」に接続不良を解決する対策として以下のようなものが存在する。

【0010】

特開2003−243818号公報には配線基板の半導体電子部品の実装部のそりに合わせて、配線基板のランドに形成されるはんだ高さを変化させることにより、配線基板のそりが大きくても確実に半導体電子部品の接続端子を半導体基板のランドに接続する思想が開示されている。

【0011】

【特許文献1】特開2003−243818号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

しかし特許文献1記載の発明ではランドの高さを決定する際に、事前にリフロー工程による基板のそりを事前計算若しくは現物にあわせて設計する必要がある。

【0013】

本発明は掛かる事前処理を行うことなく、「そり」による部品の浮き吸収できる方法を提供することにある。

【課題を解決するための手段】

【0014】

本発明に係る複数の接続端子を有する大型電子部品を接続する基板のランド構造は、ランドを2以上に分割するソルダーレジスト層を有することを特徴とする。

【0015】

またこの基板のランド構造のソルダーレジスト層はランド上に構成されることを特徴とする。

【0016】

本発明に係る複数の接続端子を有する大型電子部品の接続方法は、ランド上及びソルダーレジスト上にはんだを一体に塗布するステップと、塗布したはんだ上に大型部品の接続端子を載置するステップと、大型部品を載置した基板を加熱するステップからなることを特徴とする。

【0017】

さらにこの大型電子部品の接続方法は、加熱した前板を冷却するステップを含めても良い。

【発明の効果】

【0018】

本発明の構成を取ることで従来までの大型電子部品用ランドと同じはんだ供給量でも、はんだの高さの増加が可能となり、プリント配線基板がそった場合や、大型電子部品の接続端子の「浮き」が発生した場合でも、大型電子部品用ランドと大型電子部品接続端子との間の隙間がはんだで埋まり、電気的又は構造的に接続することが可能となる。

【発明を実施するための最良の形態】

【0019】

以下、本発明の実施の形態について図面を参照して説明する。

(実施例1)

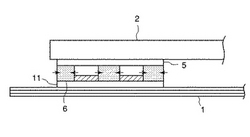

図1は本発明の第1の実施形態に用いるプリント配線基板1及びランド11を表す図面であり、一方、図2は従来用いられてきたプリント配線基板1等を表す図である。また図3はそのランド11周辺の断面図を、

プリント配線基板1は大型部品の実装対象になる基板である。リフロー時に発生するこのプリント配線基板1のそりが本発明の課題となる。

【0020】

ランド11は大型電子部品2の大型電子部品接続端子5をはんだで接続するための接続端子である。この端子を介してプリント配線基板1に配されたパターンと接続することで、回路を構成し、無線機能等を実現する。

【0021】

近隣部品用ランド12は大型部品近傍の小型部品を固定するためのランドである。

【0022】

従来、基板の「そり」に伴う大型電子部品接続端子5の浮きが発生する問題の解決策として、ランド11に載る「はんだ」の領域を大きく取るという解決策があった。

【0023】

従来の大型部品用はんだ開口部101はこの解決策を取った際のクリームはんだ印刷機により塗布された「はんだ」の領域を表すものである。このようにクリームはんだ印刷範囲を広く取ることで「そり」による浮きを補充するための「余剰はんだ」の塗布量を増やし、「そり」の量への対応を可能にする。クリームはんだ印刷機での作業は概略すると以下の通りである。最初にプリント配線基板1上に、ランドに対応する開口部を有した「はんだ」マスクを固定する。その後各開口部にクリームはんだを充填し、スキージといわれるハケで不要な「はんだ」を掻き取る。その後「はんだ」マスクを外すとはんだ層が形成される。すなわち、従来の大型部品用はんだ開口部101は「はんだ」マスクに大きな開口部を設けた際のその外延を表す。

【0024】

しかし、この従来の大型部品用はんだ開口部101を大きくすると、近隣部品用はんだ開口部102との距離が近接し、はんだの「漏れ」による回路の短絡が発生する可能性がある。

【0025】

これに対し、本発明においてはランド11にソルダーレジスト層13を2本入れている。ソルダーレジストとは「はんだ付け」に必要なランド以外のパターンなどに半田が付かないようにするコーティング材のことである。これをランド11内に設けることで、はんだ開口部を広げることなくプリント配線基板1上に余剰はんだを用意することが可能になる。このソルダーレジストはプリント配線基板1にも塗布され、不要な箇所に「はんだ」が付くことを防いでいる。

【0026】

図1のA−A断面を拡大して表したのが、図3のランド11周辺の拡大断面図である。

【0027】

プリント配線基板1は多層基板であることを示す(図では3層)。この層ごと素材の熱膨張率が相違することにより基板のそりが発生する。

【0028】

ランド11上にはソルダーレジスト層13が形成されていることがわかる。

【0029】

図3で表されたランド11に対してクリームはんだ印刷機によりはんだを印刷した際の断面図が図4である。

【0030】

はんだ層14はクリームはんだ印刷機により印刷された、「はんだ」の層である。前述のようにクリームはんだ印刷機を用いてペースト状のはんだを塗布したものである。この際に、ソルダーレジスト層13上にもクリームはんだを塗布しておくことで、従来の大型部品用はんだ開口部101の外延相当部に盛られる「余剰はんだ」の量を確保する。

【0031】

また、本図では「はんだ」の領域をランド11周辺に拡大している点で、従来のプリント配線基板1と同様の記載をしているが、これは特に無くてもよい。

【0032】

図4のはんだ塗布後のプリント配線基板1に大型電子部品2を配置し、リフローを行った後の図1のA−A断面を拡大したものが図5である。

【0033】

前述のソルダーレジスト層13はリフローされた場合に「はんだ」をはじく。従って、リフロー時の加熱によってソルダーレジスト層13上の「クリームはんだ」は両脇のソルダーレジスト層13が形成されていないランド11に移動する。

【0034】

また、図4で記載されたように、ランド11周辺に「はんだ」の塗布領域が拡大されている場合にも同様な挙動をする。すなわち基板上にもソルダーレジストが塗布されているので、過熱されると「はんだ」が流動性を持つと、表面張力によりランド11及び大型電子部品接続端子5方向に流れる(図5の矢印方向)。

【0035】

以上のようにランド11上にソルダーレジスト層13を設けると共に大型部品用はんだ開口部101を最小にすることで、恣意的にはんだの流動方向を誘導し近隣部品用ランド12に短絡しないようにする。あわせて「そり」によるランド11と大型電子部品接続端子5との距離が増したときに、ソルダーレジスト層13上に塗布された「余剰はんだ」を利用して隙間を埋め、接続不良が発生することを防止する。

【0036】

上述する実施例においてはランド11ごとにソルダーレジスト層13を2本引いているがこれに限定されるものではない。間隔を狭くして多数本のソルダーレジスト層13を設けても良い。また、このソルダーレジスト層13の形状は任意のものであっても良い。また、必ずしも「線」にこだわるものでなく、図6のように十字であっても良い。

【0037】

さらにソルダーレジストの代わりに同様の効果を有するシルクやポリイミド材をソルダーレジスト層13に適用しても良い。

【0038】

またプリント配線基板1以外にもフレキシブルプリント配線板や、リジッドフレキシブル配線板に用いても良い。

【0039】

加えてランド11上にソルダーレジスト層13を形成する方法以外にも、プリント配線基板1上に個別にランド11a乃至cを設け、プリント配線基板1中で相互に接続するようにしても良い。

【図面の簡単な説明】

【0040】

【図1】本発明に係るプリント配線基板1及びランド11を表す上面図である。

【図2】従来のプリント配線基板1及びランド11を表す上面図である。

【図3】はんだを印刷する前の本発明に係るランド11周辺の拡大断面図である。

【図4】はんだを印刷した後の本発明に係るランド11周辺の拡大断面図である。

【図5】リフロー後の本発明に係るランド11周辺の拡大断面図である。

【図6】ランド11上のソルダーレジスト層13の別のパターンを表した上面図である。

【図7】ランド11の異なる構成を表した断面図である。

【図8】本発明の課題であるプリント配線基板1のたわみを表す図である。

【符号の説明】

【0041】

1: プリント配線基板

2: 大型電子部品

11: ランド

12: 近隣部品用ランド

13: ソルダーレジスト層

【技術分野】

【0001】

本発明はプリント配線基板上に大型電子部品の実装を行うための方法に関する。

【背景技術】

【0002】

ノートパソコンやPDA、携帯電話機、デジタルオーディオプレイヤーなど、個人が携帯する携帯情報端末は増加する一方である。また、個々の携帯情報端末の機能は高度化、複雑化している。このため基板上にはCPU(セントラルプロセッシングユニット)、DSP(デジタルシグナルプロセッサ)、CCD(チャージカップルドデバイス:電荷結合素子)、HDD(ハードディスクデバイス)といった大型の部品の実装を要求される。また従来基板上にパターン構成されていた無線回路や表示部制御デバイス等も1チップ化されることで実装コストの低減を図る動きも進んでいる。

【0003】

このように、基板上には大型の電子デバイスが実装される機会が多くなっている。一方で、このような傾向が進むことで新たな問題が新たに生じている。以下この問題について述べる。

【0004】

これらを含む電子部品の実装に際して基板上にはんだを印刷等して塗布して部品を配置したのち、リフローを行うことで部品を基板上に固定する。このリフロー時に、リフロー炉の炉中は摂氏140度以上に加熱され、その後放熱されるため、リフロー対象の基板は短時間に加熱、冷却されることとなる。このように加熱等されると、基板によっては大きなそりが発生する。一般的に用いられている多層基板は、必ずしも層ごとの熱膨張率、熱収縮率が同じではないためである。

【0005】

このそりが発生すると、以下のような問題が生じる。

【0006】

図8はそりが発生した際の基1上の大型電子部品2周辺の拡大図である。ここで大型電子部品2は2以上の大型電子部品接続端子5を有するものとする。

【0007】

基板1上には大型部品を実装するためのランド7が設けられている。リフロー前においては、このランド7上にはんだ6が盛られ、その上に大型電子部品接続端子5を配置する。その後加熱、冷却することではんだ6が溶融し大型電子部品接続端子5とランド7が電気的に固定されることとなる。

【0008】

しかし、図8のように加熱・冷却工程中に基板に「そり」が発生すると複数の大型電子部品接続端子5のうち一が固定される一方、別の一は「そり」により浮き4が発生し、はんだ6による接続ができない不具合が発生してしまう。

【0009】

この「そり」に接続不良を解決する対策として以下のようなものが存在する。

【0010】

特開2003−243818号公報には配線基板の半導体電子部品の実装部のそりに合わせて、配線基板のランドに形成されるはんだ高さを変化させることにより、配線基板のそりが大きくても確実に半導体電子部品の接続端子を半導体基板のランドに接続する思想が開示されている。

【0011】

【特許文献1】特開2003−243818号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

しかし特許文献1記載の発明ではランドの高さを決定する際に、事前にリフロー工程による基板のそりを事前計算若しくは現物にあわせて設計する必要がある。

【0013】

本発明は掛かる事前処理を行うことなく、「そり」による部品の浮き吸収できる方法を提供することにある。

【課題を解決するための手段】

【0014】

本発明に係る複数の接続端子を有する大型電子部品を接続する基板のランド構造は、ランドを2以上に分割するソルダーレジスト層を有することを特徴とする。

【0015】

またこの基板のランド構造のソルダーレジスト層はランド上に構成されることを特徴とする。

【0016】

本発明に係る複数の接続端子を有する大型電子部品の接続方法は、ランド上及びソルダーレジスト上にはんだを一体に塗布するステップと、塗布したはんだ上に大型部品の接続端子を載置するステップと、大型部品を載置した基板を加熱するステップからなることを特徴とする。

【0017】

さらにこの大型電子部品の接続方法は、加熱した前板を冷却するステップを含めても良い。

【発明の効果】

【0018】

本発明の構成を取ることで従来までの大型電子部品用ランドと同じはんだ供給量でも、はんだの高さの増加が可能となり、プリント配線基板がそった場合や、大型電子部品の接続端子の「浮き」が発生した場合でも、大型電子部品用ランドと大型電子部品接続端子との間の隙間がはんだで埋まり、電気的又は構造的に接続することが可能となる。

【発明を実施するための最良の形態】

【0019】

以下、本発明の実施の形態について図面を参照して説明する。

(実施例1)

図1は本発明の第1の実施形態に用いるプリント配線基板1及びランド11を表す図面であり、一方、図2は従来用いられてきたプリント配線基板1等を表す図である。また図3はそのランド11周辺の断面図を、

プリント配線基板1は大型部品の実装対象になる基板である。リフロー時に発生するこのプリント配線基板1のそりが本発明の課題となる。

【0020】

ランド11は大型電子部品2の大型電子部品接続端子5をはんだで接続するための接続端子である。この端子を介してプリント配線基板1に配されたパターンと接続することで、回路を構成し、無線機能等を実現する。

【0021】

近隣部品用ランド12は大型部品近傍の小型部品を固定するためのランドである。

【0022】

従来、基板の「そり」に伴う大型電子部品接続端子5の浮きが発生する問題の解決策として、ランド11に載る「はんだ」の領域を大きく取るという解決策があった。

【0023】

従来の大型部品用はんだ開口部101はこの解決策を取った際のクリームはんだ印刷機により塗布された「はんだ」の領域を表すものである。このようにクリームはんだ印刷範囲を広く取ることで「そり」による浮きを補充するための「余剰はんだ」の塗布量を増やし、「そり」の量への対応を可能にする。クリームはんだ印刷機での作業は概略すると以下の通りである。最初にプリント配線基板1上に、ランドに対応する開口部を有した「はんだ」マスクを固定する。その後各開口部にクリームはんだを充填し、スキージといわれるハケで不要な「はんだ」を掻き取る。その後「はんだ」マスクを外すとはんだ層が形成される。すなわち、従来の大型部品用はんだ開口部101は「はんだ」マスクに大きな開口部を設けた際のその外延を表す。

【0024】

しかし、この従来の大型部品用はんだ開口部101を大きくすると、近隣部品用はんだ開口部102との距離が近接し、はんだの「漏れ」による回路の短絡が発生する可能性がある。

【0025】

これに対し、本発明においてはランド11にソルダーレジスト層13を2本入れている。ソルダーレジストとは「はんだ付け」に必要なランド以外のパターンなどに半田が付かないようにするコーティング材のことである。これをランド11内に設けることで、はんだ開口部を広げることなくプリント配線基板1上に余剰はんだを用意することが可能になる。このソルダーレジストはプリント配線基板1にも塗布され、不要な箇所に「はんだ」が付くことを防いでいる。

【0026】

図1のA−A断面を拡大して表したのが、図3のランド11周辺の拡大断面図である。

【0027】

プリント配線基板1は多層基板であることを示す(図では3層)。この層ごと素材の熱膨張率が相違することにより基板のそりが発生する。

【0028】

ランド11上にはソルダーレジスト層13が形成されていることがわかる。

【0029】

図3で表されたランド11に対してクリームはんだ印刷機によりはんだを印刷した際の断面図が図4である。

【0030】

はんだ層14はクリームはんだ印刷機により印刷された、「はんだ」の層である。前述のようにクリームはんだ印刷機を用いてペースト状のはんだを塗布したものである。この際に、ソルダーレジスト層13上にもクリームはんだを塗布しておくことで、従来の大型部品用はんだ開口部101の外延相当部に盛られる「余剰はんだ」の量を確保する。

【0031】

また、本図では「はんだ」の領域をランド11周辺に拡大している点で、従来のプリント配線基板1と同様の記載をしているが、これは特に無くてもよい。

【0032】

図4のはんだ塗布後のプリント配線基板1に大型電子部品2を配置し、リフローを行った後の図1のA−A断面を拡大したものが図5である。

【0033】

前述のソルダーレジスト層13はリフローされた場合に「はんだ」をはじく。従って、リフロー時の加熱によってソルダーレジスト層13上の「クリームはんだ」は両脇のソルダーレジスト層13が形成されていないランド11に移動する。

【0034】

また、図4で記載されたように、ランド11周辺に「はんだ」の塗布領域が拡大されている場合にも同様な挙動をする。すなわち基板上にもソルダーレジストが塗布されているので、過熱されると「はんだ」が流動性を持つと、表面張力によりランド11及び大型電子部品接続端子5方向に流れる(図5の矢印方向)。

【0035】

以上のようにランド11上にソルダーレジスト層13を設けると共に大型部品用はんだ開口部101を最小にすることで、恣意的にはんだの流動方向を誘導し近隣部品用ランド12に短絡しないようにする。あわせて「そり」によるランド11と大型電子部品接続端子5との距離が増したときに、ソルダーレジスト層13上に塗布された「余剰はんだ」を利用して隙間を埋め、接続不良が発生することを防止する。

【0036】

上述する実施例においてはランド11ごとにソルダーレジスト層13を2本引いているがこれに限定されるものではない。間隔を狭くして多数本のソルダーレジスト層13を設けても良い。また、このソルダーレジスト層13の形状は任意のものであっても良い。また、必ずしも「線」にこだわるものでなく、図6のように十字であっても良い。

【0037】

さらにソルダーレジストの代わりに同様の効果を有するシルクやポリイミド材をソルダーレジスト層13に適用しても良い。

【0038】

またプリント配線基板1以外にもフレキシブルプリント配線板や、リジッドフレキシブル配線板に用いても良い。

【0039】

加えてランド11上にソルダーレジスト層13を形成する方法以外にも、プリント配線基板1上に個別にランド11a乃至cを設け、プリント配線基板1中で相互に接続するようにしても良い。

【図面の簡単な説明】

【0040】

【図1】本発明に係るプリント配線基板1及びランド11を表す上面図である。

【図2】従来のプリント配線基板1及びランド11を表す上面図である。

【図3】はんだを印刷する前の本発明に係るランド11周辺の拡大断面図である。

【図4】はんだを印刷した後の本発明に係るランド11周辺の拡大断面図である。

【図5】リフロー後の本発明に係るランド11周辺の拡大断面図である。

【図6】ランド11上のソルダーレジスト層13の別のパターンを表した上面図である。

【図7】ランド11の異なる構成を表した断面図である。

【図8】本発明の課題であるプリント配線基板1のたわみを表す図である。

【符号の説明】

【0041】

1: プリント配線基板

2: 大型電子部品

11: ランド

12: 近隣部品用ランド

13: ソルダーレジスト層

【特許請求の範囲】

【請求項1】

複数の接続端子を有する大型電子部品を接続する基板のランド構造であって、

前記ランド上を2以上に分割するソルダーレジスト層を有することを特徴とする大型電子部品を接続する基板のランド構造。

【請求項2】

請求項1記載の基板のランド構造であって、

前記ソルダーレジスト層は前記ランド上に構成されることを特徴とする基板のランド構造。

【請求項3】

ソルダーレジスト層によって2以上に分割された接続用のランドを有する基板上に複数の接続端子を有する大型電子部品の接続方法であって、

前記ランド上及び前記ソルダーレジスト上にはんだを一体に塗布するステップと、

前記塗布したはんだ上に前記大型部品の接続端子を載置するステップと、

前記大型部品を載置した前記基板を加熱するステップからなる大型電子部品の接続方法。

【請求項4】

請求項3記載の大型電子部品の接続方法であって、

さらに加熱した前記基板を冷却するステップからなる大型電子部品の接続方法。

【請求項1】

複数の接続端子を有する大型電子部品を接続する基板のランド構造であって、

前記ランド上を2以上に分割するソルダーレジスト層を有することを特徴とする大型電子部品を接続する基板のランド構造。

【請求項2】

請求項1記載の基板のランド構造であって、

前記ソルダーレジスト層は前記ランド上に構成されることを特徴とする基板のランド構造。

【請求項3】

ソルダーレジスト層によって2以上に分割された接続用のランドを有する基板上に複数の接続端子を有する大型電子部品の接続方法であって、

前記ランド上及び前記ソルダーレジスト上にはんだを一体に塗布するステップと、

前記塗布したはんだ上に前記大型部品の接続端子を載置するステップと、

前記大型部品を載置した前記基板を加熱するステップからなる大型電子部品の接続方法。

【請求項4】

請求項3記載の大型電子部品の接続方法であって、

さらに加熱した前記基板を冷却するステップからなる大型電子部品の接続方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2006−344889(P2006−344889A)

【公開日】平成18年12月21日(2006.12.21)

【国際特許分類】

【出願番号】特願2005−171013(P2005−171013)

【出願日】平成17年6月10日(2005.6.10)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

【公開日】平成18年12月21日(2006.12.21)

【国際特許分類】

【出願日】平成17年6月10日(2005.6.10)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

[ Back to top ]