安全なメモリ区分を使用した安全な実行のための方法および装置

【課題】様々なタイプの脅威からコンピュータの実行の保全性を保証できるようにする。

【解決手段】検証実施命令を記憶するための不揮発性メモリと、安全区分223を有するシステム・メモリ220と、前記不揮発性メモリと前記システム・メモリ220に結合されたプロセッサ210とを備え、前記プロセッサ210は、ブートストラップ安全ロジック241を含むオンチップBIOS215と、前記オンチップBIOS215と前記システム・メモリ220に結合された実施ユニット211であって、前記ブートストラップ安全ロジック241により特定されるオペレーションを実施するように構成された前記実施ユニット211とを備え、前記オペレーションは前記不揮発性メモリから前記安全区分223へ前記検証実施命令242をコピーするステップと前記検証実施命令242の信頼性を検証するステップとを含む。

【解決手段】検証実施命令を記憶するための不揮発性メモリと、安全区分223を有するシステム・メモリ220と、前記不揮発性メモリと前記システム・メモリ220に結合されたプロセッサ210とを備え、前記プロセッサ210は、ブートストラップ安全ロジック241を含むオンチップBIOS215と、前記オンチップBIOS215と前記システム・メモリ220に結合された実施ユニット211であって、前記ブートストラップ安全ロジック241により特定されるオペレーションを実施するように構成された前記実施ユニット211とを備え、前記オペレーションは前記不揮発性メモリから前記安全区分223へ前記検証実施命令242をコピーするステップと前記検証実施命令242の信頼性を検証するステップとを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施態様は、プロセッサ内での安全な実行に関する。より詳細には、本発明は、安全なメモリ区分を使用した安全な実行のための方法および装置に関する。

【背景技術】

【0002】

コンピュータの接続性の著しい増大により、頑強なセキュリティ・インフラストラクチャの重要性が高まってきた。未許可アクセス(例えばインターネットからの)を防止するために、コンピュータ・システムのセキュリティ機能を使用することができる。インターネットに基づく商取引の利用を可能にするには、取引のプライバシーおよび保全性を維持する安全な実行環境が重要である。安全にされた実行環境はまた、ディジタル多用途ディスク(DVD)やコンパクト・ディスク−読取り専用メモリ(CD−ROM)などの媒体に記憶された発行されたソフトウェアまたはコンテンツ(例えば映画)に対するコピーを保護するのに用いることもできる。

【0003】

実行を安全なものとすることは、実行の保全性を保証し、コードおよびデータのプライバシーを保証することを含む。様々なタイプの脅威が、システムの保全性またはプライバシーを損なうことにつながる恐れがある。例えば、悪意あるソフトウェアが、オペレーティング・システムの脆弱性を利用することがある。ダイレクト・メモリ・アクセス・デバイスが、プロセッサのサポートなしで物理メモリを読み取れることがある。ロジック・アナライザを使用して、プロセッサとメモリの間のトラフィックが観察されることもある。また、プロセッサに備わるデバッグ・モードまたはプローブ・モードを利用した攻撃や、システム中のコンポーネントの接続性を物理的に変更して、コンポーネント間の通信を観察および変更する攻撃が行われることもある。また、攻撃者がハードウェアを異常な電圧、温度、または周波数にさらして、システムの実行を損なわせ、場合によってはハードウェアから外に秘密を「リーク」させる可能性もある。さらに、攻撃者がプロセス層を選択的に除去して、秘密を隠しているデバイス構造を露出させたり、イオン・ビームを使用してデバイス内部の信号フローを調べたりする可能性もある。

【0004】

公開鍵/秘密鍵暗号法に基づくものなど、いくつかのセキュリティ方式は、秘密にしておく必要のある秘密データまたはコードを使用する。いくつかの場合、使用されるエンコード・アルゴリズムは公開され、暗号法の強度は、鍵を秘密にしておくことにある。プログラムの制御フロー情報などの中間データは、明るみになれば秘密鍵が決定されやすくなる恐れがあるので、明るみにならないようにすべきである。これに関して、プロセッサ・アーキテクチャの条件付き割当て能力を用いて秘密データ上の分岐を除去することができる場合もあるが、この要件を満たすようにコードを設計することは困難である。適用例によっては、暗号強度の一部は、アルゴリズム自体のプライバシーにある。この場合、実行環境は、入力データおよびすべての中間結果に加えて実行コードさえも秘密に保たれることを保証する必要がある。

【0005】

いくつかのシステムでは、特別なセキュリティ・コプロセッサを使用して、ホスト・プロセッサのコードおよびデータを保護する。既知のシステムでは、例えば悪意あるソフトウェアやダイレクト・メモリ・アクセス・デバイスやロジック・アナライザを使用した攻撃、システム・デバッグ/プローブ・モードを利用した攻撃、またはハードウェアに変更を加えて秘密を暴く攻撃から、ホスト・プロセッサがホスト・プロセッサ内の秘密コードまたはデータ(例えば鍵)を保護するための、効果的な手段が提供されない。

【発明の概要】

【0006】

本発明の実施態様は、機密コードおよびデータを安全なメモリ区分に記憶することによって安全に実行できるようにする。機密コードおよびデータとしては、ネットワークを介して受信された伝送の信憑性および保全性を検証するのに使用されるコードおよびデータを含めることができ、また、DVDやCD−ROMなどの媒体に記憶されたコンテンツを含めることができる。安全なメモリ区分は、プロセッサの一般的なアドレス空間内のアドレス範囲としてアーキテクチャによって定義することができる。区分は、仮想メモリ位置または物理メモリ位置のアドレス範囲とすることができる。アドレス範囲は、基底アドレスおよび範囲によって指定することができる。安全なメモリ区分は、固定エントリ・ポイントを有することができる。他の実施態様では、機密コードおよびデータが暴かれないよう保護するために、機密コードおよびデータは、メモリに書き込む前にプロセッサ上のハードウェアによって暗号化し、プロセッサに再び読み込んだ後で暗号化解除する。本発明の様々な実施態様が、様々なレベルの脅威に対する保護を与える。各実施態様は、悪意あるソフトウェアやインテリジェントな入出力デバイスに基づく攻撃、ロジック・アナライザを使用した攻撃、プロセッサをソケットから外した後で保全性の損なわれたプラットフォーム中に配置することを含むハードウェア攻撃に対して、高度な保護を与える。

【図面の簡単な説明】

【0007】

【図1】本発明の一実施形態による、安全に実行できるコンピュータ・システムの部分ブロック図である。

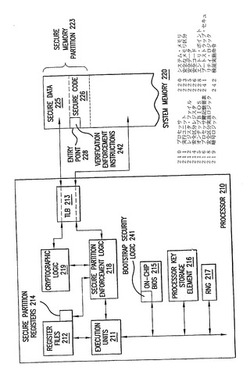

【図2】本発明の一実施形態による、安全な実行コンポーネントを有するプロセッサと、安全な区分を有するメモリとの部分ブロック図である。

【図3】仮想メモリ区分および物理メモリ区分の部分ブロック図である。

【図4】本発明の一実施形態による命令処理方法のフロー・チャートである。

【図5】本発明の一実施形態による別の命令処理方法のフロー・チャートである。

【発明を実施するための形態】

【0008】

図1は、本発明の一実施形態による、安全に実行できるコンピュータ・システムの部分ブロック図である。コンピュータ100はコンポーネント101を含み、このコンポーネント101は、プロセッサ110、チップセット102、システム・メモリ120、ネットワーク・インタフェース・カード103、不揮発性の大容量記憶域104、入出力(I/O)デバイス107、およびBIOS(basic input/output system)ROM108を備えることができる。プロセッサ110はチップセット102に結合することができる。「結合」という語は、直接接続、間接接続、間接通信などを含む。チップセット102もまた、システム・メモリ120、ネットワーク・インタフェース・カード103、不揮発性の大容量記憶域104、入出力デバイス107、およびBIOS ROM108に結合することができる。これらのデバイスは、システム・バスやPCI(peripheral component interface)バスなどのバスを介してチップセットに結合することができる。ネットワーク・インタフェース・カード103は、ネットワーク130に結合することができる。コンピュータ103はまた、コプロセッサやモデムなど、追加のコンポーネントを含むこともできる。

【0009】

プロセッサ110は、カリフォルニア州サンタクララのIntel Corp.製のPENTIUMクラス・プロセッサなどの汎用マイクロプロセッサとすることができる。別の実施形態では、プロセッサは、特定用途向け集積回路(IC)(ASIC)、コントローラ、マイクロコントローラなどとすることができる。チップセット102は、コンピュータ・システムのプロセッサと他のコンポーネントとの間でデータを転送するためのハブまたはコアとして働く1つまたは複数の集積回路チップとすることができる。一実施形態では、チップセット102は、「ノースブリッジ機能」として知られる機能を実施するメモリ・コントロール・ハブ(MCH)と、「サウスブリッジ機能」として知られる機能を実施する入出力コントローラ・ハブ(ICH)を含む。システム・メモリ120は、ダイナミック・ランダム・アクセス・メモリ(DRAM)やスタティック・ランダム・アクセス・メモリ(SRAM)など、ディジタル情報を記憶するように適合された任意のデバイス、またはこれらの任意の組合せである。一実施形態では、システム・メモリ120は揮発性メモリである。プロセッサ110、チップセット102、システム・メモリ120、およびBIOS ROM108は、コンピュータ100中のシステム・マザーボード上に装着することができる。

【0010】

ネットワーク・インタフェース・カード103は、標準的なネットワーク・プロトコルを使用して通信するためのロジックを含むことができる。ネットワーク130は、ローカル・エリアまたはワイド・エリア・コンピュータ・ネットワークとすることができ、例えばイントラネットやインターネットとすることができる。不揮発性の大容量記憶域104は、フラッシュ・メモリ、ハードディスク、光ディジタル記憶デバイス、電磁気記憶デバイス、DVD、CD−ROMなど、ディジタル情報を記憶するように適合された任意のデバイス、またはこれらの任意の組合せとすることができる。図1には、光記憶装置105およびフロッピー・ドライブ106を含むものとして、不揮発性の大容量記憶域104を示す。入出力デバイス107は、キーボード、マウス、表示画面、プリンタなど、またはこれらの任意の組合せとすることができる。BIOS ROM108は、キーボード、表示画面、ディスク・ドライブ、シリアル通信機構などの周辺デバイスを制御するためのコードを含むことができる。BIOS ROM108はまた、その他の様々な機能を実施するのに使用されるコードを含むこともできる。

【0011】

図2は、本発明の一実施形態による安全な実行コンポーネントを有するプロセッサと、安全な区分を有するメモリとの部分ブロック図である。図2には、例えば図1に示したコンピュータ・システム100などのコンピュータ・システムの一部であるプロセッサ210およびシステム・メモリ220が示してある。プロセッサ210およびシステム・メモリ220は、図1のプロセッサ110およびシステム・メモリ120と同じものとすることができる。プロセッサ210は、例えば図1のチップセット102などを介して、システム・メモリ220に結合することができる。

【0012】

プロセッサ210は、例えば算術論理ユニットなどの実行ユニット211を含むことができ、これはレジスタ・ファイル212に結合することができる。レジスタ・ファイル212は、汎用レジスタ、フラグ・レジスタ、命令ポインタ、インデックス・レジスタなど、またはこれらの組合せなど、複数のレジスタを含むことができる。レジスタ・ファイル212は、安全な区分レジスタ214を含むことができる。実行ユニット211は、オンチップBIOS(basic input/output system)215、プロセッサ・キー記憶要素216、および乱数生成器(RNG)ユニット217に結合することができる。オンチップBIOS215は、プロセッサがシステム・メモリ120など他のシステム・コンポーネントと通信するために使用する、焼き込まれたロジックを含むことができ、また、プロセッサが開始(ブートアップ)されるときに実行されるロジックを含むことができる。このロジックは、後述するようにブートストラップ・セキュリティ・ロジック241を含むことができる。さらに、オンチップBIOS215は、システム開始時にBIOS ROM108からシステム・メモリに命令をロードするためのロジック(例えばファームウェアやマイクロコードなど)を含むこともできる。プロセッサ鍵記憶要素216は、プロセッサ210が他のシステム・コンポーネントおよび他のコンピュータ・システムから受け取った情報を検証および認証するのに使用することのできる秘密鍵を含む。プロセッサ鍵は、プロセッサ鍵記憶要素216に焼き込むことができる。乱数生成器ユニット217は、任意のランダム化機能を使用するハードウェア乱数生成器とすることができる。一実施形態では、乱数生成器ユニット217は、物理デバイス中の統計的現象(例えば熱雑音)を利用して乱数を提供する。

【0013】

この実施形態では、実行ユニット211は、安全な区分実施ロジック218にも結合することができる。安全な区分実施ロジック218は、後述するように、メモリ中の安全区分を管理するためのロジックを含む。他の実施形態では、安全な区分実施ロジック218は、暗号ロジック219に結合される。暗号ロジック219は、安全区分に記憶される情報を暗号化し、安全区分から読み取られた情報を暗号化解除する。暗号ロジック219は、DES(Data Encryption Stanard)、RSA(Rivest−Shamir−Adleman)、DSS(Digital Signal Standard)暗号化などのアルゴリズムを実装したハードウェア・ロジックとすることができる。一実施形態では、暗号ロジック219は、プロセッサ鍵記憶要素216に記憶されたプロセッサ鍵ではなく、プラットフォーム特有の鍵を使用する。安全な区分実施ロジック218および暗号ロジック219は、アドレス変換バッファ(TLB)213に結合することができる。TLB213は、プロセッサ210のアドレス空間中の仮想アドレスを、システム・メモリ220中の物理アドレスおよびプロセッサ210からアクセスされる他のメモリ中の物理アドレスとマッチさせるのに使用することができる。

【0014】

図2にはまた、安全なメモリ区分223を含むシステム・メモリ220も示す。安全なメモリ区分223は、安全な区分中にあるコードからしかアクセスされない、物理メモリまたは仮想メモリのセクションとすることができる。一実施形態では、安全区分223は、2つの安全な区分レジスタ214によって決めることができる。例えば、安全区分223は、仮想メモリ中の安全区分の開始を指定する安全区分仮想アドレス基底レジスタと、安全区分のサイズを指定する安全区分仮想アドレス範囲レジスタとによって定義することができる。図2では、安全区分223は、システム・メモリ220中の物理アドレスにマッピングされた状態で示されている。安全なメモリ区分223は、安全なデータ・セクション225および安全なコード・セクション226を含むことができる。安全なコード・セクション226は、例えば信用できる検証実施命令242を記憶することができる。この命令242は、暗号アルゴリズムを適用し、ネットワークを介して受信された伝送(またはDVDやCD−ROMなどの媒体に記憶されたコンテンツ)の信憑性および保全性を検証するのに使用される。安全なデータ・セクション225は、秘密鍵や中間データ(例えばセキュリティ命令の制御フロー情報)など、安全コードによって使用されるデータを含むことができる。安全なコード・セクション226は、後述するように使用することのできるエントリ・ポイント228を有することができる。

【0015】

図2に示す実施形態は、次のように動作することができる。プロセッサ210は、プロセッサ・マイクロコードやオンチップBIOS検証ファームウェア・コード(図2にはブートストラップ・セキュリティ・ロジック241として示す)などのブートストラップ・セキュリティ・ロジックを使用して、BIOSコード(例えばBIOS ROM108中にある)を認証することにより、プラットフォームの保全性を保証する。次いで、安全なBIOS108は、チップセット中に他の保護機構があればその存在を妥当性検査する。一実施形態によれば、プロセッサ210がブートアップされるとき、プロセッサ210は、メモリを走査して安全区分のための位置を決定することにより、安全区分を生み出すことができる。次いでプロセッサは、安全区分基底レジスタおよび安全区分範囲レジスタをプログラムして、安全区分を定義することができる。これらのレジスタは、追記型レジスタとすることができる。他の実施形態では、他の機構を使用して安全区分を生み出すことができる。次いでプロセッサは、検証実施命令242、および鍵などの関連データを、システム・メモリ220中の安全なメモリ区分223にコピーすることができる。別の実施形態では、プロセッサのブートアップ中に、検証実施命令242をディスク・ドライブなど不揮発性の大容量記憶域から安全なメモリ区分223にコピーする。この実施形態では、プロセッサ210は、オンチップBIOS215に記憶されたセキュリティ・ロジック241と、プロセッサ鍵記憶要素216に記憶された鍵データを使用して、安全なメモリ区分223にコピーされた検証実施命令242およびデータの信憑性および保全性を検証することができる。この検証により、不揮発性メモリに記憶された検証実施命令242に、攻撃による破損または欠陥が生じているかどうかを判定することができる。ブートストラップ・セキュリティ・ロジック241をプロセッサに記憶し、検証実施命令242を不揮発性メモリに記憶することは、検証実施命令242をプロセッサ自体に焼き込むことよりも低コストであろう。

【0016】

一実施形態では、安全な区分実施ロジック218は、プロセッサ210によって行われるどんなメモリ・アクセスも監視する。このようなアクセスには、メモリに記憶された命令の実行や、メモリ中のデータに作用する命令の実行を含めることができる。命令は、メモリ中のある位置に記憶されたデータを読み取るとき、またはある位置にデータを書き込むときに、その位置でデータに作用する。この実施形態では、安全な区分実施ロジック218は、プロセッサ210によって各命令が実行される前に命令を調べることになる。命令が、区分エントリ・ポイント228以外の安全なメモリ区分223内の位置への分岐である場合は、安全な区分実施ロジックは、この命令を実施すべきでないと決定する。このような場合、区分実施ロジックは、トラップ・ハンドラにトラップすることができる。安全な区分実施ロジック218は、区分内のある位置から区分内の別の位置への分岐の実行は許可し、また、区分エントリ・ポイント228への分岐の実行は許可する。エントリ・ポイント228は、安全区分にジャンプしたソフトウェアの信憑性を検証する検証ルーチンの開始を含むことができる。したがって例えば、このルーチンは、未許可のまたは悪意あるプログラムが安全なコードを実行しないようにすることができる。さらに、エントリ・ポイントを安全なコード226へエンフォース(enforcing)することにより、安全な区分実施ロジック218は、未許可のまたは悪意あるコードが検証ルーチンをバイパスするのも防止する。他の実施形態では、命令が区分エントリ・ポイントに記憶されておらず、前に実行された命令が区分の開始の前の命令だったときは、安全な区分実施ロジックは、この命令を実行しないと決定する。したがって、区分エントリ・ポイント228が区分中の第1の命令でない場合、安全な区分実施ロジック218は、プロセッサがエントリ・ポイント以外のポイントで安全区分中に続けて進まないようにすることになる。

【0017】

この実施形態では、命令が安全区分外にあり、安全区分内の位置に作用(例えば読取りまたは書込み)しようとしているときは、安全な区分実施ロジックは、この命令を実行しないと決定する。したがって、安全なコード・セクション226中の信用できる命令だけが、安全なメモリ区分223の安全なデータ・セクション225内のデータに作用することができる。この実施形態では、安全区分中に位置するコードによってアクセスできることを除いては、安全データにアクセスすることはできない。他の実施形態では、安全区分中のコードは、安全区分外にあるデータにアクセスすることができる。別の実施形態では、この区分の安全なデータ・セクション225中のデータに作用しようとする命令が適切な読取り/書込み許可を有さない場合は、安全な区分実施ロジック218は、この命令を実行しないと決定することができる。別の実施形態では、安全区分外の命令が安全区分内の位置に作用しようとするときは、安全な区分実施ロジック218は、トラップ・ハンドラにトラップすることができる。また、命令が適切な読取り/書込み許可なしで安全なデータ・セクション中のデータに作用しようとするときも、トラップ・ハンドラにトラップすることができる。

【0018】

一実施形態では、安全なメモリ区分223は、仮想メモリ中の区分とすることができる。一実施形態では、プロセッサのアドレス空間は仮想メモリ・アドレス空間であり、すべての命令は、仮想アドレスでメモリをアドレス指定する。この実施形態では、安全区分は、プロセッサ210中で、仮想アドレス基底レジスタや仮想アドレス範囲レジスタなど、仮想アドレスによって指定される。安全区分を仮想アドレスで指定することにより、安全な区分実施ロジックはより早くパイプライン中に位置することができる。アドレス変換バッファ213が、これらの仮想アドレスを物理アドレスに変換することができる。安全区分についての仮想アドレスから物理アドレスへのマッピングは、信用できる機構を介して行うことができる。

【0019】

図3は、仮想メモリ区分および物理メモリ区分の部分ブロック図である。図3には、アプレット空間367およびカーネル空間365を有する仮想メモリ360を示す。アプレット空間367およびカーネル空間365は、物理メモリ320中の安全区分323にマッピングする。安全区分323中の情報は、不揮発性メモリ340中の安全な不揮発性空間345にスワップアウトすることができる。不揮発性メモリ340はフラッシュ・メモリとすることができる。一実施形態では、安全な不揮発性空間345は、安全区分323中のコードまたはデータのわずかな部分しか含まない。

【0020】

一実施形態では、検証実施命令242および関連データは、プロセッサ210からメモリに移行する間またはメモリに記憶されている間に暴かれないよう保護するために、暗号化された形で安全区分223に記憶される。この実施形態によれば、安全なコードおよびデータは、メモリ中の安全区分からプロセッサ210に転送された後で、実行ユニット211が作用できるように暗号ロジック219によって暗号化解除されることになる。反対に、安全なコードおよびデータがプロセッサ210からメモリ中の安全区分に転送される前には、暗号ロジック219によって暗号化されることになる。このようにすることで、安全なコードおよびデータは、例えばダイレクト・メモリ・アクセス、ロジック・アナライザ、イオン・ビームなどによる攻撃から保護されることになる。十分に強力な暗号化が用いられれば、攻撃者は、安全区分の内容を決定することができたとしても、安全なコードまたはデータを決定することはできないことになる。一実施形態では、安全なコードおよびデータは、例えばディフィー・ヘルマン・メソッドなどの共有暗号アルゴリズムを使用して暗号化および暗号化解除される。このような実施形態では、カバー鍵を使用してデータをカバーすることができ、このカバー鍵は共有されない。カバー鍵は、ブートアップ・ロジックによって生成することができる。他の実施形態では、1つのシステムがいくつかのプロセッサを有し、カバー鍵はシステム・プロセッサによって共有される。

【0021】

他の実施形態では、コンピュータ・システムは、ディスク・ドライブなど不揮発性の大容量記憶域中に安全区分を有する。不揮発性の大容量記憶域中の安全区分は、揮発性の大容量記憶域中の安全区分への追加的なものとすることができる。この実施形態によれば、不揮発性メモリ中の区分は、安全にされたコードによってのみアドレス指定可能である。

【0022】

乱数生成器217を使用して、暗号アルゴリズムの実施または新しい鍵の生成を行うことができる。プロセッサは、安全な不揮発性(NV)メモリを使用して、単調な値を最新のものに維持することができる。

【0023】

図4に、本発明の一実施形態による命令処理方法のフロー・チャートを示す。命令は、例えば、図1および2のプロセッサ110や210などのプロセッサによって実行されるアセンブリ言語命令とすることができる。実行前に、命令を調べる(401)。命令が仮想メモリ中の位置区分内の位置への未許可アクセスであるときは、この命令を実行しないと決定する。一実施形態では、命令が区分内の位置にあるデータに作用するものであり、命令が区分内に記憶されていないときは、この命令を実行しないと決定する(402)。他の実施形態では、命令が区分外の位置からの分岐であり、この分岐が区分内の位置への分岐であり、この分岐が区分エントリ・ポイントへの分岐でないときは、この命令を実行しないと決定する(403)。別の実施形態によれば、命令が区分エントリ・ポイントに記憶されておらず、前に実行された命令が区分の開始の直前の命令であったときは、この命令を実行しないと決定する(404)。命令を許可すると決定した場合は、命令を実行する(405)。例えば、命令が区分内のある位置から区分内の別の位置に分岐するとき、および命令が区分外の位置から区分エントリ・ポイントに分岐するときは、この命令を実行することができる。一実施形態によれば、この方法は、命令を実行しないと決定したときにトラップ・ハンドラにトラップすることを含む(406)。

【0024】

図5に、本発明の一実施形態による別の命令処理方法のフロー・チャートを示す。一実施形態によれば、暗号化された命令をメモリ中の安全区分からプロセッサに読み込む(501)。命令は、任意の暗号技術を用いて暗号化されたものとすることができる。読み込んだ命令は、例えば図2に示した暗号ロジック219を使用して暗号化解除する(502)。次いで、暗号化解除した命令を実行することができる。一実施形態では、安全区分からデータを読み取る命令の場合は(503)、安全区分からデータを読み取り、読み取ったデータを暗号化解除する(504)。別の実施形態では、安全区分中の位置にデータを書き込む命令の場合は(505)、データを暗号化し、暗号化したデータを安全区分に書き込む(506)。他の実施形態では、安全区分からデータを読み取る命令か、または安全区分中の位置にデータを書き込む命令かを決定することは、データの仮想アドレスを安全区分の境界と比較することを含む。

【0025】

セキュリティ特権レベル(SPL)

一実施形態では、2つの「セキュリティ特権レベル」を定義することができる。一方の特権レベルは、セキュリティ・カーネル特権レベルと呼び、これは、プリミティブなセキュリティ機能/サービスだけを実行するためのものとすることができる。第2の特権レベルは、プロセッサまたは第三者から供給されたセキュリティ・コードを実行するためのものと定義することができる。この第2の特権レベルは、アプレット特権レベルと呼ぶことができる。これらの新しいセキュリティ特権レベル(SPL)は、実行の特権レベルに関する既存の概念と直交することができる。したがってこの実施形態では、所与のアドレス範囲に対するアクセス(実行/読取り/書込み)特権は、現在特権レベル(CPL)だけでなく現在SPL(CSPL)とも相関関係になる。CSPLは、現在の実行に関連するセキュリティ特権レベルを示す。CSPLのデフォルト値は3とすることができる。この場合、CSPLが3のときは、実行モデルはデフォルト実行モデルと呼ぶことができる。CSPLがデフォルト以外の値を有するときは、実行モデルは「隠し実行」モデルの実行モデルと呼ぶ。

【0026】

2つの特権レベルは、SPL0(カーネルの場合)およびSPL1(アプレットの場合)と呼ぶことができる。複合特権レベルはリングx.yと呼ぶことができ、xは現在の実行についてのCPLであり、yは現在の実行についてのCSPLである。したがって、現在の実行の特権レベルが3.3である場合、これは現在のアプリケーションがデフォルト・リング3で実行されていることを意味する。しかし、現在特権レベルが3.0である場合は、実行についての現在特権レベルがリング3であり、アクセス権がセキュリティ・カーネル特権レベルに関連することを意味する。一実施形態では、実モードではCSPLは常に3であり、この場合、実モードでの隠し実行に対するサポートはない。

【0027】

カーネル特権レベル

アーキテクチャは、カーネル特権レベルで使用される新しい仮想アドレス範囲を定義することができる。新しい仮想アドレス範囲は、仮想アドレス基底レジスタ・カーネル(VABRk)および仮想アドレス範囲レジスタ・カーネル(VARRk)によって定義することができる。VABRkおよびVARRkによって定義する仮想アドレス範囲は、それに関連するカーネル・レベルのセキュリティ・アクセス権を有するように定義することができ、安全なカーネル空間、またはカーネルの安全なメモリ区分と呼ぶことができる。

【0028】

一実施形態では、安全なカーネル空間内のコードだけが、この空間で読取りまたは書込みを行うことができる。この場合、安全なカーネル空間内のデータおよびコードの保全性およびプライバシーがこの空間の外のコードによって損なわれることはない。他の実施形態では、安全なカーネル空間内のコードは、任意の仮想アドレス空間に対するデータの読取りおよび書込みを、そのようなアクセスが例えば既存のセグメンテーションおよびページング保護機構によって許される限り、行うことができる。他の実施形態では、セキュリティ・カーネル特権レベルにあるときだけ実行できる命令が定義される。別の実施形態では、カーネル仮想アドレス空間は自由に再配置可能である。別の実施形態では、安全区分のサイズは、ブートアップ時に固定され、一般のシステム・ソフトウェアの制御下にはない。例えば、プリOSファームウェアまたはオンチップ・マイクロコードだけが、仮想アドレス範囲レジスタに書き込むことができる。この場合、仮想アドレス範囲レジスタは、ソフトウェアによる書込みは全く不可能(プロセッサ・マイクロコードによって書き込まれる場合)とするか、またはリセット後に1度だけ書き込める(ファームウェアによって書き込まれる場合)とすることができる。

【0029】

別の実施形態では、安全なカーネル空間への固定エントリ・ポイントがあり、この空間の外から、このエントリ・ポイントに対する事前定義済みオフセット以外のオフセットまで安全なカーネル空間に分岐するのは違反である。デフォルトのセキュリティ特権を有するアドレス空間からは、固定エントリ・ポイントに入るのである限り、どんな制御転送機構を介しても安全なカーネル空間に入ることができる。他の実施形態では、カーネル・セキュリティ特権レベルにあるコードから要求されるカーネル・サービスは、要求元の現在特権レベルと相関関係にあるものとすることができる。この実施形態では、安全なカーネル空間へのエントリ・ポイントにあるコードは、呼出し元の現在特権レベルおよび現在のセキュリティ特権レベルを調べて、要求されているサービスが可能か否かを決定する。一実施形態では、安全カーネル・アドレス空間は、現在のセキュリティ特権レベルx.3を有する空間に、任意の制御転送機構を介して出ることができる。セキュリティ・カーネルが呼出し/リターン機構を使用してプログラム・フローを変更する場合、セキュリティ・カーネルは、その安全なスタック空間を管理し、かつ、安全なアプリケーション・スタック空間と安全でないアプリケーション・スタック空間との間の移行を管理することが必要な場合がある。

【0030】

アプレット特権レベル

アーキテクチャは、プロセッサの一般的な仮想アドレス空間内で新しい仮想アドレス範囲を定義することができる。この仮想アドレス範囲は、2つのレジスタすなわち仮想アドレス基底レジスタ・アプレット(VABRa)および仮想アドレス範囲レジスタ・アプレット(VARRa)によって定義することができる。VABRaおよびVARRaによって定義するアドレス範囲は、アプレット・レベルを有し、それに関連するセキュリティ・アクセス権を有することができ、安全なアプレット空間と呼ぶことができる。

【0031】

一実施形態では、アプレット・セキュリティ特権レベルに対応する仮想アドレス空間の場合、読取りおよび書込みアクセス権は、アプレットまたはカーネル・セキュリティ特権レベルを有するアドレス範囲内で実行されているコードに限定される。一実施形態では、安全なアプレット空間を定義するアプリケーションは、同じプロセスのコンテキストで、同じ現在特権レベルの安全なカーネル空間も定義しなければならない。一実施形態では、カーネルまたはアプレット隠し実行コード以外のコードは、安全なアプレット空間内で読取りまたは書込みを行うことができない。したがって、安全なアドレス空間内のデータまたはコードの保全性およびプライバシーが、セキュリティ・アクセス権を有さないコード(すなわち現在のセキュリティ特権レベル3)によって損なわれることはない。この実施形態では、安全なアプレット空間内のコードは、安全なカーネル・アドレス空間内ではデータの読取りまたは書込みを行うことはできず、安全なアプレット空間内のコードは、既存のセグメンテーションおよびページングおよび保護機構によって許される限り、安全なカーネル空間以外ならどんなアドレス範囲に対しても読取りおよび/または書込みを行うことができる。安全なアプレット空間は自由に再配置可能である。区分のサイズは、ブート時に固定することができ、一般のシステム・ソフトウェアの制御下にはない。この実施形態では、プリOSファームウェアまたはオンチップ・マイクロコードだけが、VARRaレジスタに書き込むことができる。したがって、レジスタVARRaは、ソフトウェアによる書込みは全く不可能(プロセッサ・マイクロコードによって書き込まれる場合)であるか、またはリセット後に1度だけ書き込める(ファームウェアによって書き込まれる場合)。

【0032】

一実施形態では、安全なアプレット空間には、安全なカーネル空間からしか入ることができない。この実施形態では、デフォルト・セキュリティ空間から安全なアプレット空間に分岐するのは違反とすることができるが、安全なカーネル空間から安全なアプレット空間へのエントリ・ポイントには制約はないものとすることができる。この実施形態では、デフォルト・セキュリティ特権を有するアドレス空間から安全なアプレット空間中の機能を呼び出すには、現在安全なアプレット空間内の機能の要求についての適切な「信任状」と共に、安全なカーネル空間中の固定エントリ・ポイントに制御を転送する必要がある。安全なアプレット・アドレス空間は、現在のセキュリティ特権レベル3を有する空間に、任意の制御転送機構を介して出ることができる。ただし、デフォルト・セキュリティを有する空間中の機能をアプレットが呼び出したい場合は、その安全なカーネル空間への機能呼出しを介してこれを行う。

【0033】

一実施形態では、安全なアプレット空間と安全なカーネル空間の間の移行は、デフォルト・セキュリティを有するアドレス空間と安全なカーネル空間の間の移行と同様だが、例外として、アプレットは、追加のセキュリティ・カーネル機能を呼び出すことができる。この実施形態では、安全なアプレット空間は、あらゆる割込みが安全なアプレット空間からの退出を引き起こすことを除いては、安全なアプレット空間内での制御転送のために任意の制御転送機構を使用することができる。安全なアプレット空間は、セキュリティ・カーネルが安全なアプレット空間の管理をサポートし、安全なアプリケーション・スタック空間と安全でないアプリケーション・スタック空間との間の移行をサポートする場合だけ、呼出し/リターン機構を使用することができる。

【0034】

安全な物理メモリ(RAMおよび不揮発性)区分

一実施形態では、セキュリティ拡張は、物理メモリ中の1つの「安全」区分を定義する。プロセッサがセキュリティ・カーネル特権レベルだけを実装している場合は、安全な物理空間のサイズは安全なカーネル空間のサイズ以上である。プロセッサがセキュリティ・カーネル特権レベルとアプレット特権レベルの両方をサポートする場合は、物理区分のサイズは、安全なカーネル空間と安全なアプレット空間の合計以上とすることができる。安全な物理メモリ区分は、物理アドレス基底レジスタ(PABR)および物理アドレス範囲レジスタ(PARR)によって定義することができる。一実施形態では、安全な物理メモリ区分の基底と範囲は両方とも、ブート時に固定され、したがって一般のシステム・ソフトウェアの制御下にはない。プリOSファームウェアだけがPABRまたはPARRレジスタに書き込むことができる。したがってこれらのレジスタは、リセット後に1度だけ書き込むことができる。

【0035】

物理アドレス区分は、仮想アドレス機構がイネーブルのとき(例えばプロセッサが保護モードで実行しているとき)、安全な仮想アドレス区分のための物理メモリを提供するのに使用することができる。仮想アドレス機構がディセーブルのとき(例えばプロセッサが実モードのとき)は、プロセッサ・ハードウェアは、安全な物理メモリ区分へのどんなアクセスも許可せず、この結果、実モードでの安全な物理区分へのアクセスはいずれも違反オペレーション・トラップとなる。

【0036】

一実施形態では、安全な物理メモリ区分は、プロセッサ・ダイ中の物理メモリとして、または同じパッケージ中の別個のダイとして、または外部システム・メモリの一部として提供することができる。安全な物理区分を外部システム・メモリとして実装する場合は、メモリ・コントローラもPABRおよびPARRと同様のレジスタの対を実装し、アドレス空間がDMAデバイスからアクセスを受けないようにすることが有利である。プリOS BIOSが、チップセット中に適切な保護機構があることを検証することができる。安全な物理メモリの一部は、不揮発性メモリに対応することができる。NV物理メモリ区分に使用される基底アドレスは、PABRと同じものとすることができる。追加の範囲レジスタとして、NVメモリ範囲レジスタすなわちNMRRがあってもよく、これは、安全なNVメモリ区分のサイズを定義するものであり、SPL0のコードによってしか書くことができない。安全なNVメモリ空間は、同じパッケージ中の別個のダイとしてあってもよく、外部コンポーネントの一部としてあってもよい。一実施形態では、このNVメモリへは、安全なカーネル空間で実行されているコードによって要求が開始された場合だけアクセス可能である。

【0037】

一実施形態では、安全なアドレス空間には4つのアーキテクチャ区分がある。すなわち、1)安全なアプレット空間、2)アプレットから要求されたセキュリティ・カーネル機能を実行するための、アプレット・アドレス空間に関連する安全な物理メモリ、3)カーネル・コードおよびデータのための安全な物理メモリ、4)安全なNVメモリである。アプレット空間のための安全な物理メモリと、アプレット実行に関連する安全なカーネル空間の一部とは、プロセスごとのリソースとすることができる。安全なカーネル空間は、安全なアプレット物理アドレス空間の内容、ならびに安全なアプレット・コードから呼び出されるセキュリティ・カーネル機能のために予約される安全なカーネル空間の一部の内容の、暗号化バージョンを保存する機能を実装することができる。安全なカーネル・アドレス空間はまた、安全なアプレット物理メモリと、アプレット空間に関連する安全なカーネル空間の一部とを復元する機能も実装することができる。これらの機能は、安全なアプレット物理メモリと、アプレット空間に関連するカーネル・メモリとを、いくつかのプロセス間で「仮想化」することを可能にする。スワップアウトされた状態の保全性は、スワップされた状態に関連するハッシュ値を、保存した状態のこのインスタンスに対応する「固有タグ」と共に安全なNVメモリに保持することによって提供することができる。

【0038】

一実施形態では、いくつかのカーネル機能を同時に実行することを可能にするのに十分な安全なカーネル空間物理メモリが提供され、実行の最中にセキュリティ・ドライバによって開始されたカーネル機能のスワップアウトを可能にすることは必要ない。他の実施形態では、セキュリティ機能の実行に割り振られた安全なカーネル空間が使用中になった後は、以後にカーネルのセキュリティ機能の要求があっても、前に実行されているセキュリティ機能が完了するまでブロックされる。

【0039】

プロセッサ鍵

一実施形態では、プロセッサは、固有IDに加えて秘密鍵/公開鍵の対も有することができる。この鍵の対は、RSA鍵の対、DSS鍵の対、または他の何らかの鍵の対とすることができるが、RSAが最も有利である。秘密鍵は、プロセッサ内部に「焼き込み」、特定のカーネルのセキュリティ機能でのみ使用できるものとすることができる。これらのセキュリティ機能は、特権レベルcp1.0(したがってカーネル・セキュリティ空間内)でのみ実行することができる。公開鍵もまた、関連する証明書と共にプロセッサ中に提供することができる。完全な秘密鍵と公開鍵のためにオンチップNV記憶域を提供することもできる。電源投入時にプロセッサが秘密鍵を明るみにすることなくオンチップ・マイクロコードまたはカーネル・コードを使用して完全な鍵を計算することができるような、公開鍵と秘密鍵を構成するのに十分なコンポーネントのための記憶域を提供すれば足りる。鍵の署名入りの値に対応する公開鍵証明書の部分もまた、オンチップNVメモリ中に提供すべきである。一実施形態では、RSA鍵の対は、1024ビットの秘密鍵の場合に、1344ビットの隠しNV記憶域をプロセッサ上に必要とする。すなわち、Pコンポーネント用に512ビット、Qコンポーネント用に512ビット、公開鍵証明書用に320ビットである(証明書中の署名がDSS署名であると仮定した場合)。

【0040】

秘密鍵と公開鍵に加えて、プロセッサは、オンチップNVセル中に56ビットのDES鍵を有することもできる(またはトリプルDESに対するサポートを有するべきである)。この鍵もまたプロセッサだけの秘密にしておくことができ、この鍵は、外部の安全な物理メモリに対して記憶/読取りを行うためのDES機能を実施するためだけに使用することができる。一実施形態では、プロセッサ特有のDES鍵ではなくプラットフォーム特有のDES鍵が使用される。

【0041】

セキュリティ特権レベルとプロセッサ・オペレーション・モードの対話

一実施形態では、デフォルトのプロセッサ実行と現在のセキュリティ特権レベルとの間に最小限の対話がある。他の実施形態では、仮想変換機構がオフのとき(すなわちプロセッサが実モードのとき)、CSPLは3(すなわちデフォルト・モード)にされ、安全な物理アドレス区分にアクセスするのは違反である。セキュリティ機能は、実モードまたは仮想モードではディセーブルとすることができる。この実施形態では、仮想変換機構がオンのとき(すなわちプロセッサが保護モードのとき)、安全な仮想アドレス区分へのアクセスに関するどんなTLBミスも、プロセッサが新しい変換アルゴリズムを使用して直接処理する。TLBミスは、TLBに関係するどんな障害も生じない。

【0042】

一実施形態では、安全なアドレス空間内でアクセス権がCSPLによってのみ制御されるように、安全なアドレス空間についての仮想−物理マッピングのためのページ変換エントリ・フォーマットを定義することができる。安全な仮想区分のいずれかからコードを実行するときは、性能監視機能がディセーブルになる。中断または外部割込みのせいで安全なカーネル空間または安全なアプレット空間の外に移行する場合があるときは、適切なレジスタを安全なカーネル空間内の事前定義済みのブロックに保存することができる。安全なアドレス空間内のデータを外部メモリに書き込む前にレジスタ中の一時的な値を保存するのに外部のシステム・メモリを使用することができる場合は、プロセッサは、プラットフォーム特有の「カバー鍵」を使用して、オンチップDESユニットで自動的にこの値を暗号化することができる。これらのレジスタを安全な物理メモリに保存した後、対応するプロセス・レジスタ値を、正当だが無意味ないくつかの値に変更することができる。例えば、EIPを何らかの正当な固定値に変更できることを除いては、ほとんどのデータ/アドレス・レジスタは、すべて「0」に変更することができる。

【0043】

セキュリティ・アドレス空間から外への移行は、オンチップ・マイクロコードによって、またはカーネルの安全な仮想アドレス区分内の割込み機構によって扱うことができる。安全な物理アドレス区分のために外部メモリが使用される場合、いくつかの実装形態では、プラットフォームの「カバー鍵」でDESを使用して命令ストリームの暗号化バージョンを安全な仮想アドレス区分からフェッチすることをサポートすることができる。

【0044】

一実施形態では、新しい安全移行(TSR)を定義することができる。この実施形態によれば、プログラム制御を他の空間から安全なカーネル空間に転送する制御転送機構はいずれも、呼出し元のCPLおよびCSPLをこのレジスタ中に提供する。安全なカーネル空間中のエントリ・ポイントにあるコードが、これらのビットおよび要求されているサービスを調べて、要求されているサービスを許可すべきか否かを決定することができる。例えば、いくつかのセキュリティ・サービスは、CPL0のコード(すなわちセキュリティ・ドライバ)からしか要求することができない。一実施形態では、TSRレジスタは、ハードウェアまたは安全なカーネル・コード(CSPL0)によってしか更新することができない。

【0045】

一実施形態では、安全なカーネル空間には固定エントリ・ポイントがある。この実施形態では、他のどんなオフセットへの分岐も違反である。レジスタの1つが、セキュリティ・アドレス空間またはアプリケーション・アドレス空間内で実行すべき機能番号を指定することができる。機能の中には、追加のパラメータを必要とするものもある。例えば、入力オペランドや、ターゲット・コード/データの暗号化解除に使用される鍵などである。一実施形態では、デフォルト・セキュリティ(CSPL3)を有するアドレス空間から安全なアプレット空間に制御を転送することは許されない。別の実施形態では、安全な物理空間についての「ライトバック」属性を選択するために、安全な仮想アドレス空間についてのキャッシュ制御ビットが事前定義される。

【0046】

セキュリティ命令

本発明の機能を実装するために、セキュリティ命令を設けることができる。これらの命令は、セキュリティ機能をサポートするのに必要な命令として分類することができ、あるいは、セキュリティ機能の性能または異なる特権レベル間の移行の性能を向上させるための命令として分類することができる。一実施形態では、最小限のネイティブ・セキュリティ機能では、実装形態がカーネル・セキュリティ特権レベルを「ロジック・アナライザ」脅威レベルでサポートすることが必要である。この機能レベルをサポートするのに使用することのできる命令は、(1)cp1.0特権レベルでプロセッサ秘密鍵を読み取る命令、(2)cp1.0特権レベルでプラットフォーム「カバー」鍵に、かつ別のモデル特有レジスタに書き込む命令、(3)いずれかのCPLまたはCSPLでプロセッサの公開鍵を証明書と共に読み取る命令、(4)いずれかのCPLまたはCSPLでRNGを読み取る命令である。

【0047】

その他の命令を定義して、実装形態を容易にし、異なるセキュリティ特権を有するアドレス空間の間の移行を促進することもできる。これらの命令には、次に現れる制御転送命令が実際に現在のセキュリティ特権レベルの変更を必要とすることを示すための分岐「ヒント」命令を含めることができる。この命令は、制御を安全なアプレット空間中のコードに転送する命令として実装することもでき、制御を安全なカーネル空間に転送する命令として実装することもでき、かつ/または、制御をデフォルトのセキュリティ特権レベルに転送する命令として実装することもできる。使用できる別の命令は、安全なNVメモリに記憶する命令である。この命令は、現在の記憶がNVメモリを対象としていることを設計のバックエンドではなくフロントエンドで知らせることにより、実装を補助することができる。

【0048】

ソフトウェア・モデル

セキュリティ・カーネル空間を実装するには、多くのオプションが可能である。一実施形態では、セキュリティ・カーネルは、セキュリティ機能を1つだけ実装することができる。他の実施形態では、セキュリティ・カーネルは、単に追加の機能をマクロコード中に実装するだけで、追加の機能をサポートすることができる。別の実施形態では、セキュリティ・カーネルは、セキュリティ・ドライバから1度に1つの機能が呼び出されることしか許可しないポリシーを実装することができる。この場合、いずれかの追加セキュリティ機能の実行を開始する前に、前のセキュリティ機能を完了すべきである。別の実施形態では、セキュリティ・カーネルは、そのリソース内で生きた機能を1つしかサポートできないが、セキュリティ・ドライバによって安全なカーネル空間を仮想化することができる。この手法は、部分的に実行された機能の状態を暗号化して、新たにロードされた機能に対して保全性チェックを実施する場合に、大きなオーバーヘッドにつながることがある。別の実施形態は、いくつかのセキュリティ機能が同時に生きられるだけの十分な空間を安全なカーネル空間に与え、この空間の「仮想化」はサポートしない。

【0049】

一実施形態では、CSPL3のアプリケーションがカーネルのセキュリティ機能を呼び出したいとき、このアプリケーションは、CPL0およびCSPL3で実行されているセキュリティ・ドライバを介して要求を出すべきである。性能の理由から、このアーキテクチャは、セキュリティ・ドライバを介した呼出しのオーバーヘッドなしにアプリケーションがそれに関連する安全なアプレット中の機能を呼び出せるようにすることができる。CSPL3のアプリケーションは、安全なカーネル空間へのエントリ・ポイントに対する制約が守られる限り、安全なカーネル空間を介してこのような要求を出すことができる。固定エントリ・ポイントにある安全なカーネル・コードが、呼出し元が指定のサービスを要求するのにふさわしい特権レベル(PLとSPLの両方)を有していたことを検証することを担う。このために、新しいレジスタとして移行状況レジスタ(TSR)を定義して、呼出し元のPLおよびSPLを安全なカーネル空間および安全なアプレット空間に提供することができる。

【0050】

性能の理由から、安全なアプレットが制御転送命令を介して制御をアプリケーションに転送して戻せるようにすることができる。実行のプライバシーを維持するために、アプレットは、セキュリティ・カーネルが安全なスタックに対するサポートを提供する場合だけ、制御をアプリケーションに転送する呼出し命令を使用すべきである。一実施形態では、呼出し元を検証するために安全なカーネル空間に負担を課すのではなく、アプリケーションから安全なアプレット空間への制御転送の要求は、セキュリティ・ドライバを介してのみ可能とすることができる。一実施形態では、インフラストラクチャはまた、エントリ・ポイントに対する制約が守られる限り、安全なアプレットが直接制御転送命令を介してカーネル空間中のセキュリティ機能を呼び出すことも可能にする。安全なカーネル空間は、生きたセキュリティ機能の呼出しを1度に1つサポートするのに十分な、現在安全なアプレットに関連する空間を提供するだけでよい。一実施形態では、どんなCPLおよびCSPLからでも安全なカーネル空間に入ることができるとしても、エントリ・ポイントにあるセキュリティ・カーネル・コードは、許可されたセキュリティ・カーネル・サービス要求だけしか所与のPLおよびSPLから出されないようにする。エントリ・ポイントにあるセキュリティ・カーネル・コードは、移行状況レジスタ(TSR)中の要求元の特権レベルを調べて、この決定を行うことができる。

【0051】

レジスタ

レジスタを使用して、安全区分機構を管理することができる。これらのレジスタには、安全カーネル仮想アドレス空間、アプレット仮想アドレス空間、物理アドレス空間、および不揮発性メモリ・アドレス空間のための、基底レジスタおよび範囲レジスタを含めることができる。また、様々なプロセッサ鍵にアクセスするためのレジスタを提供することもできる。これらには、プロセッサ秘密鍵のためのレジスタと、プロセッサ公開鍵およびそれに加えて証明書に対応する署名、ならびにプロセッサDES「カバー鍵」のためのレジスタを含めることができる。レジスタは読取り専用レジスタとすることができる。

【0052】

その他のレジスタには、セキュリティ・アドレス空間への移行のために呼出し元のPLおよびSPLを提供する移行状況レジスタを含めることができる。さらに、固有タグ番号レジスタが、隠し実行の特定インスタンスに割り当てられたタグ番号を保持することができる。中断セキュリティ特権レベル・レジスタを使用して、セキュリティ特権レベルを記録することができる。これらのレジスタは、読取り/書込みレジスタとすることができる。

【0053】

安全カーネル仮想アドレス空間および安全なアプレット仮想アドレス空間の管理

一実施形態では、安全なカーネル・アドレス空間および安全なアプレット・アドレス空間は、仮想−物理変換機構がイネーブルのときだけ定義される。セキュリティ機能は、安全な仮想アドレス区分を安全な物理メモリにマッピングすることを実現するために、OSのメモリ・マネージャに依拠しなくてもよい。安全な仮想アドレス区分と安全な物理区分との間に、固定マッピングを定義することができる。安全な仮想アドレス空間にはアクセス・フォールトおよびダーティ・フォールトへの対応がないものとすることができ、キャッシュ制御ビットを「ライトバック」モードに設定することができる。一実施形態では、安全な仮想アドレス空間と安全な物理アドレス空間との間にリンクを確立するのに、OSサービスは必要ない。他の実施形態では、これらの仮想アドレス区分にはページ・フォールトの概念がない。

【0054】

安全な仮想空間は、固定線形マッピングを用いて安全な物理空間にマッピングすることができる。ページ変換は、PABRレジスタおよびVARRkレジスタと相関関係にあるものとすることができる。アクセス権は事前定義することができる。これらのアクセス権は、あらゆるCPLで実行/読取り/書込み権を許可することができ、それにより、仮想安全区分はどんなCPLにあることもできる。この実施形態では、エントリ・ポイントにおけるセキュリティ・カーネル・コードによって安全なアドレス空間への移行が認められると、安全な区分内の所与の仮想アドレスに対するアクセス許可は、CSPLによってのみ制御される。

【0055】

一実施形態では、安全な仮想アドレス空間は自由に再配置可能である。この実施形態では、安全な仮想区分が再配置されたときは常に、再配置された安全な仮想区分に関する前の有効マッピングはすべて無効になる。このようにして、新しい安全な仮想区分への分岐が行われるときは常に、新しい有効TLBエントリが新しい区分に対して確立される。他の実施形態では、デフォルト・セキュリティを有する仮想アドレス空間のためのTLB機構は、これらのPTEに関する物理ページ・アドレスが安全な物理空間と重複しないことを保証するように強化される。重複の可能性があると、違反オペレーション・フォールトが引き起される恐れがある。

【0056】

割込み

一実施形態では、カーネル・アドレスとアプレット・アドレスの両方についての隠し実行が、ソフトウェアによって、かつ/または外部割込みを通して割込みを受けることがある。カーネルとアプレットのいずれかのセキュリティ特権レベルで隠し実行の途中だったかもしれないプロセスのコンテキストを保存できるようにするアーキテクチャ機構を設けることができる。プロセスがセキュリティ特権レベルのうちの1つで実行されている間にシングルステッピングによる割り込みを受けた場合でも、ハードウェア機構およびソフトウェア機構は、実行のプライバシーおよび保全性が脅威モデルまで維持されるようにすることができる。割込みの処理に使用される機構は、プロセッサ・アーキテクチャの機能に応じて決まる。一実施形態では、セキュリティ特権レベルで実行されているコードが割込みを受けた場合にセキュリティ問題に対処するルーチンを、既存の割込みマイクロコードに追加する。別の実施形態では、新しいセキュリティ割込みベクトル・テーブルを定義して、これらの割込みを処理する。この実施形態では、プログラムがセキュリティ特権レベルで実行されている間のどんな割込みも、安全なカーネル・アドレス空間中のハンドラに転送される。この安全な割込みハンドラは、クリティカルな機能を実施して、割り込まれたコードのプライバシーおよび保全性を保証し、次いで、関連するすべての正しい割込み状況情報と共に、分岐してデフォルトの割込みベクトルに戻る。

【0057】

セキュリティ・レベルの仕様

様々な実装形態が、様々な脅威レベルに対する保護を与えることができる。例えばいくつかの実装形態は、ソフトウェア、インテリジェント入出力、およびロジック・アナライザ(観察モードのみ)による攻撃だけに対して保護を与えることができ、他の実装形態は、イオン・ビーム攻撃からの脅威を含めて、あらゆる脅威モデルに対して保護を与えることができる。ある種類の脅威に対する保護能力が、セキュリティ・レベルを定義する。単純なハードウェア攻撃(プロセッサをソケットから外して、保全性の損なわれたプラットフォームに配置し、安全な物理空間を確立するための高保全性BIOSに対する信頼を欺くことを含む)に対する保護は、すべてのセキュリティ・レベルが実現すべきである。一実装形態では、プロセッサは、プロセッサ・マイクロコードまたはオンチップBIOS検証ファームウェア・コードを使用してBIOSを認証することにより、プラットフォームの保全性を保証する。この場合、BIOSコードは、必要なセキュリティ機能がチップセット中にあればその存在を妥当性検査することができる。

【0058】

セキュリティ・レベル1(SL−1)モデルの一実施形態では、安全な仮想アドレス区分をマッピングするための外部システム・メモリおよびシステムNV(フラッシュ)メモリの、保護された区分が使用される。一実施形態では、隠し実行のためのコードは、共通プラットフォーム鍵を使用して暗号化され、保護された物理メモリ中に暗号化された形で保持される。デバイスの秘密鍵に対して作用するいくつかの機能については、これらがデバイスの秘密鍵のビットに依存する分岐を有さないことを保証するための安全対策をとることができる。これは、条件付き移動命令を使用することによって、または予測機能を使用することによって達成することができる。一実施形態では、すべての中間計算データは、クリアな形でプロセッサ・レジスタおよびオンチップ・キャッシュ中だけに保持される。一実施形態では、安全なアドレス範囲中のデータを保護された外部物理メモリ区分に記憶する必要があるときは常に、出て行くデータをバス・インタフェース・ユニット中のDESユニットを使用して暗号化する。安全な物理アドレス空間から入ってきたデータおよびコードを暗号化解除するためには、別個のDESユニットがあってもよく、共通のDESユニットを共用してもよい。DESユニットは、少なくとも56ビットのDES鍵を使用すれば有利である。実装形態によっては、より大きな鍵を使用することもできる(トリプルDESが使用される場合)。

【0059】

セキュリティ・レベル1は、あらゆる隠し実行に対するロジック・アナライザ(観察モード)までのセキュリティ脅威に対処することができる。安全な物理空間中のコードが暗号化された形であるとき、外部バス信号をアクティブに変更してプロセッサ/プラットフォームの秘密にアクセスすることは非常に難しい。ただし、このセキュリティ・レベルは、このような攻撃に対してどんな保証も提供しない。他の実施形態では、耐タンパ性ソフトウェアを使用して「既知テキスト」攻撃をさらに困難にする。セキュリティ・レベル1モデルはまた、秘密データを解読するために実装プローブ・モードおよびデバッグ・フックを使用して実装特有の状態へのアクセスを得ることに対しても、何らかの保護を与えることができる。さらに、SL1モードは、プロセッサが誤って挙動するようにして秘密データへのアクセスを得る電圧および周波数タンパ技法に対しても、限られたいくらかの量の保護を採用することができる。

【0060】

SL−1モデルでは、物理メモリの安全な区分の保護は、仮想−物理変換機構、プロセッサ中でのDES暗号化、およびメモリ・コントローラ中の物理メモリ・タイプ・レジスタを介して提供することができる。SL−1モデルでは、秘密データのプライバシーは、プロセッサ記憶域内だけで秘密データに作用することによって保証することができる。安全な物理メモリ・アドレス範囲内のデータがバス上に書き出されるときは常に、データはBIU中のDESユニットを使用して暗号化される。システムによっては、安全な物理メモリとの間でデータ/コードを暗号化/暗号化解除するDESユニットは、プロセッサ特有の鍵ではなくプラットフォーム特有の鍵を使用することが望ましい。

【0061】

SL−1モデルでは、安全な物理アドレス空間中の外部コードおよびデータはすべてプラットフォーム鍵で暗号化しておくことができるので、ロジック・アナライザで外部バス信号を見るだけではコードまたはデータを解読することができない。プロセッサ/プラットフォーム秘密鍵は、より高レベルの脅威モデルまで保護することもできる。外部コードが暗号化されるので、機能の中のどの命令が秘密鍵にアクセスしているか、あるいはプロセッサが最終的に秘密データをクリアなメモリに書くように入来命令ビット・ストリームをどのように変形するかを知ることは、非常に難しい。SL−1モデルはまた、プロセッサ実装特有のデバッグおよびマシンチェック機構を使用して、また電圧および周波数タンパ技法を使用してプロセッサ/プラットフォームの秘密にアクセスすることに対しても、適度な量の保護を与える。

【0062】

セキュリティ・レベル2(SL−2)モデルの一実施形態は、安全な物理メモリ区分の少なくとも一部のためのオンチップ物理メモリを設けることによって、セキュリティ・レベルをSL−1よりも上げたものである。この場合、すべての安全なNVメモリ区分はやはりプラットフォーム中にある。揮発性の安全な物理メモリのいくつかもまたシステム・メモリ中にある場合がある。外部のシステム・メモリの一部である安全な揮発性メモリの部分に対する安全保護は、SL−1と同様である。SL−2セキュリティ・モデルでは、隠し実行に関するコードを、暗号化された形で外部メモリからダウンロードすることができる。次いで、このコードを暗号化解除して、プロセッサ・オンチップ・メモリを使用して保全性を検証することができる。次いで、暗号化解除したコードをプロセッサのオンチップ・メモリ外で実行する。あらゆる秘密データも、クリアな形でオンチップ・メモリに保持される。

【0063】

このモデルの一実施形態によれば、オンチップ・メモリは、セキュリティ・ドライバによって管理される共有プロセッサ・リソースである。オンチップ・メモリの一部は種々のプロセスによって共有することができる。オンチップ・メモリのこの共有部分を仮想化することは、ドライバによって行うことができる。オンチップ・メモリのこの部分を暗号化および保存する能力を与えるためのセキュリティ・カーネル機能を、ドライバに利用可能にすることができる。また、オンチップ物理メモリの、前に保存された部分を暗号化解除および復元するためのセキュリティ・カーネル機能を利用可能にすることもできる。外部NVメモリへの秘密データの記憶もまた、同じDESを使用して暗号化することができる。SL−2モデルは、プロセッサ実装特有のプローブ・モードまたはデバッグ・フックを用いた攻撃、ならびに電圧および周波数タンパによる攻撃に対して、より高レベルの保護を与えることもできる。

【0064】

SL−2モデルでは、物理揮発性メモリの安全区分の保護は、仮想−物理変換機構、オンチップ物理メモリによって提供することができ、また、外部システム・メモリの一部である安全な物理空間の部分に対するDES暗号化によって提供することができる。SL−2モデルは、SL−1モデルと比較して、デバイス/プラットフォームの秘密鍵とプロセッサの隠し実行との両方のセキュリティ・レベルを上げることができる。外部物理メモリ中のクリティカルなコードおよびデータがすべて暗号化された形で、かつクリアな形でオンチップ物理メモリ中に保持される場合、攻撃者は、ロジック・アナライザで外部バス信号を見るだけではコードまたはデータを解読することができない。また、オンチップ・メモリへのダウンロードの保全性がチェックされる場合、ロジック・アナライザを使用して外部バス信号をドライブすることによって隠し実行の保全性を損ねることはできない。SL−2モデルはまた、秘密鍵を解読するために実装プローブおよびデバッグ・フックを使用して実装特有の状態へのアクセスを得ることに対しても、より多くの保護を与えることができる。SL−2モデルはまた、プロセッサが誤って挙動するようにして秘密データへのアクセスを得る電圧および周波数タンパ技法に対しても、追加の保護を採用することができる。

【0065】

セキュリティ・レベル3(SL−3)モデルの一実施形態は、オンチップの安全なNVメモリを提供することにより、または安全なNVメモリ区分をプロセッサ・ダイと同じパッケージ内にもってくることにより、セキュリティ・レベルをSL−2よりも上げたものである。一実施形態では、揮発性および不揮発性メモリのいくつかは、やはりシステム・メモリおよびシステムNVメモリの一部として存在することができる。さらに、このセキュリティ・レベルは、実装デバッグ・フック、マシン・チェック・アーキテクチャ、および様々な実行タンパ技法の使用に対して、また放射線攻撃の使用に対して、より高レベルの保護を与えることもできる。実装形態によっては、イオン・ビーム攻撃を妨げるために、プロセッサおよびNVメモリ・シリコン上に、またプロセッサと安全なNVメモリ・ダイとの間の相互接続上に、保護ダイ・コーティングを施すこともできる。揮発性および不揮発性メモリの区分がシステム・リソース中にあるので、これらの実装は、少なくともSL−1レベルまでのセキュリティを与える。

【0066】

SL−3モデルの実施形態では、物理揮発性ならびにNVメモリの安全な区分の保護は、仮想−物理変換機構とオンチップ物理メモリの組合せによって行われる。このモデルは、プロセッサ記憶域内だけで秘密データに作用することにより、秘密データのプライバシーを保証する。このモデルは、SL−2モデルと比較して、デバイス/プラットフォーム秘密鍵とプロセッサ隠し実行との両方セキュリティ・レベルを上げることができる。SL−3モデルでは、隠し実行に関係するすべての記憶域を1つのパッケージ内にもってくることができる。これにより、計算エンジンと隠し実行のための記憶域との間でどんな内部信号も明るみになることはない。さらにこのモデルでは、オンチップ(または同一パッケージ)NVメモリもまた、ハードウェア再生攻撃に対して保護することができる。SL−3モデルは、実装特有プローブおよびデバッグ・フックによる秘密データのリークに対して、広範な保護を与えることができる。このモデルはまた、プロセッサを誤動作させて、場合により秘密データをクリアな形で外部バス上に書き出させることのできる様々なタンパ手法に対しても、保護を与えることができる。実装形態によっては、イオン・ビーム攻撃を用いて秘密データにアクセスすることができないように、プロセッサおよび秘密記憶領域の上に保護ダイ・コーティングを施すこともできる。

【0067】

安全なカーネル・アドレス空間内のマクロ機能

安全なカーネル・アドレス空間内に実装することのできるマクロ機能には、認証機能、鍵管理機能、埋込み検証カーネル、署名機能、検証機能、アプレット・ロード機能、暗号化保存アプレット、暗号化復元アプレット、アプレット空間中の機能呼出しがある。

【0068】

結び

本発明の実施形態は、安全なメモリ区分を使用した安全な実行のための方法および装置に関するものである。本発明は、ホスト・プロセッサのコードおよびデータを保護するための特別なセキュリティ・コプロセッサを有する従来システムに勝る、いくつかの利点を提供する。本発明は、コプロセッサが必要ないので、コスト効果がより大きい。さらに本発明は、より高性能な汎用プロセッサ中でセキュリティ・コードを実行することができるので、より高性能な解決法である。さらに本発明は、コプロセッサ・データ転送オーバーヘッドがないので、より効率的な解決法でもある。

【0069】

本明細書では、本発明のいくつかの実施形態について具体的に図示および/または記述している。ただし、本発明の修正および変形も、本発明の趣旨および意図される範囲を逸脱することなく、以上の教示によってカバーされ、頭記の特許請求の範囲内にあることは理解されるであろう。例えば、メモリ区分は、仮想メモリ中に実装しても物理メモリ中に実装してもよい。別の例として、各実施形態は、SL−1、SL−2、SL−3のいずれかのセキュリティ・モデルに適合する特徴を含んでいればよい。

【技術分野】

【0001】

本発明の実施態様は、プロセッサ内での安全な実行に関する。より詳細には、本発明は、安全なメモリ区分を使用した安全な実行のための方法および装置に関する。

【背景技術】

【0002】

コンピュータの接続性の著しい増大により、頑強なセキュリティ・インフラストラクチャの重要性が高まってきた。未許可アクセス(例えばインターネットからの)を防止するために、コンピュータ・システムのセキュリティ機能を使用することができる。インターネットに基づく商取引の利用を可能にするには、取引のプライバシーおよび保全性を維持する安全な実行環境が重要である。安全にされた実行環境はまた、ディジタル多用途ディスク(DVD)やコンパクト・ディスク−読取り専用メモリ(CD−ROM)などの媒体に記憶された発行されたソフトウェアまたはコンテンツ(例えば映画)に対するコピーを保護するのに用いることもできる。

【0003】

実行を安全なものとすることは、実行の保全性を保証し、コードおよびデータのプライバシーを保証することを含む。様々なタイプの脅威が、システムの保全性またはプライバシーを損なうことにつながる恐れがある。例えば、悪意あるソフトウェアが、オペレーティング・システムの脆弱性を利用することがある。ダイレクト・メモリ・アクセス・デバイスが、プロセッサのサポートなしで物理メモリを読み取れることがある。ロジック・アナライザを使用して、プロセッサとメモリの間のトラフィックが観察されることもある。また、プロセッサに備わるデバッグ・モードまたはプローブ・モードを利用した攻撃や、システム中のコンポーネントの接続性を物理的に変更して、コンポーネント間の通信を観察および変更する攻撃が行われることもある。また、攻撃者がハードウェアを異常な電圧、温度、または周波数にさらして、システムの実行を損なわせ、場合によってはハードウェアから外に秘密を「リーク」させる可能性もある。さらに、攻撃者がプロセス層を選択的に除去して、秘密を隠しているデバイス構造を露出させたり、イオン・ビームを使用してデバイス内部の信号フローを調べたりする可能性もある。

【0004】

公開鍵/秘密鍵暗号法に基づくものなど、いくつかのセキュリティ方式は、秘密にしておく必要のある秘密データまたはコードを使用する。いくつかの場合、使用されるエンコード・アルゴリズムは公開され、暗号法の強度は、鍵を秘密にしておくことにある。プログラムの制御フロー情報などの中間データは、明るみになれば秘密鍵が決定されやすくなる恐れがあるので、明るみにならないようにすべきである。これに関して、プロセッサ・アーキテクチャの条件付き割当て能力を用いて秘密データ上の分岐を除去することができる場合もあるが、この要件を満たすようにコードを設計することは困難である。適用例によっては、暗号強度の一部は、アルゴリズム自体のプライバシーにある。この場合、実行環境は、入力データおよびすべての中間結果に加えて実行コードさえも秘密に保たれることを保証する必要がある。

【0005】

いくつかのシステムでは、特別なセキュリティ・コプロセッサを使用して、ホスト・プロセッサのコードおよびデータを保護する。既知のシステムでは、例えば悪意あるソフトウェアやダイレクト・メモリ・アクセス・デバイスやロジック・アナライザを使用した攻撃、システム・デバッグ/プローブ・モードを利用した攻撃、またはハードウェアに変更を加えて秘密を暴く攻撃から、ホスト・プロセッサがホスト・プロセッサ内の秘密コードまたはデータ(例えば鍵)を保護するための、効果的な手段が提供されない。

【発明の概要】

【0006】

本発明の実施態様は、機密コードおよびデータを安全なメモリ区分に記憶することによって安全に実行できるようにする。機密コードおよびデータとしては、ネットワークを介して受信された伝送の信憑性および保全性を検証するのに使用されるコードおよびデータを含めることができ、また、DVDやCD−ROMなどの媒体に記憶されたコンテンツを含めることができる。安全なメモリ区分は、プロセッサの一般的なアドレス空間内のアドレス範囲としてアーキテクチャによって定義することができる。区分は、仮想メモリ位置または物理メモリ位置のアドレス範囲とすることができる。アドレス範囲は、基底アドレスおよび範囲によって指定することができる。安全なメモリ区分は、固定エントリ・ポイントを有することができる。他の実施態様では、機密コードおよびデータが暴かれないよう保護するために、機密コードおよびデータは、メモリに書き込む前にプロセッサ上のハードウェアによって暗号化し、プロセッサに再び読み込んだ後で暗号化解除する。本発明の様々な実施態様が、様々なレベルの脅威に対する保護を与える。各実施態様は、悪意あるソフトウェアやインテリジェントな入出力デバイスに基づく攻撃、ロジック・アナライザを使用した攻撃、プロセッサをソケットから外した後で保全性の損なわれたプラットフォーム中に配置することを含むハードウェア攻撃に対して、高度な保護を与える。

【図面の簡単な説明】

【0007】

【図1】本発明の一実施形態による、安全に実行できるコンピュータ・システムの部分ブロック図である。

【図2】本発明の一実施形態による、安全な実行コンポーネントを有するプロセッサと、安全な区分を有するメモリとの部分ブロック図である。

【図3】仮想メモリ区分および物理メモリ区分の部分ブロック図である。

【図4】本発明の一実施形態による命令処理方法のフロー・チャートである。

【図5】本発明の一実施形態による別の命令処理方法のフロー・チャートである。

【発明を実施するための形態】

【0008】

図1は、本発明の一実施形態による、安全に実行できるコンピュータ・システムの部分ブロック図である。コンピュータ100はコンポーネント101を含み、このコンポーネント101は、プロセッサ110、チップセット102、システム・メモリ120、ネットワーク・インタフェース・カード103、不揮発性の大容量記憶域104、入出力(I/O)デバイス107、およびBIOS(basic input/output system)ROM108を備えることができる。プロセッサ110はチップセット102に結合することができる。「結合」という語は、直接接続、間接接続、間接通信などを含む。チップセット102もまた、システム・メモリ120、ネットワーク・インタフェース・カード103、不揮発性の大容量記憶域104、入出力デバイス107、およびBIOS ROM108に結合することができる。これらのデバイスは、システム・バスやPCI(peripheral component interface)バスなどのバスを介してチップセットに結合することができる。ネットワーク・インタフェース・カード103は、ネットワーク130に結合することができる。コンピュータ103はまた、コプロセッサやモデムなど、追加のコンポーネントを含むこともできる。

【0009】

プロセッサ110は、カリフォルニア州サンタクララのIntel Corp.製のPENTIUMクラス・プロセッサなどの汎用マイクロプロセッサとすることができる。別の実施形態では、プロセッサは、特定用途向け集積回路(IC)(ASIC)、コントローラ、マイクロコントローラなどとすることができる。チップセット102は、コンピュータ・システムのプロセッサと他のコンポーネントとの間でデータを転送するためのハブまたはコアとして働く1つまたは複数の集積回路チップとすることができる。一実施形態では、チップセット102は、「ノースブリッジ機能」として知られる機能を実施するメモリ・コントロール・ハブ(MCH)と、「サウスブリッジ機能」として知られる機能を実施する入出力コントローラ・ハブ(ICH)を含む。システム・メモリ120は、ダイナミック・ランダム・アクセス・メモリ(DRAM)やスタティック・ランダム・アクセス・メモリ(SRAM)など、ディジタル情報を記憶するように適合された任意のデバイス、またはこれらの任意の組合せである。一実施形態では、システム・メモリ120は揮発性メモリである。プロセッサ110、チップセット102、システム・メモリ120、およびBIOS ROM108は、コンピュータ100中のシステム・マザーボード上に装着することができる。

【0010】

ネットワーク・インタフェース・カード103は、標準的なネットワーク・プロトコルを使用して通信するためのロジックを含むことができる。ネットワーク130は、ローカル・エリアまたはワイド・エリア・コンピュータ・ネットワークとすることができ、例えばイントラネットやインターネットとすることができる。不揮発性の大容量記憶域104は、フラッシュ・メモリ、ハードディスク、光ディジタル記憶デバイス、電磁気記憶デバイス、DVD、CD−ROMなど、ディジタル情報を記憶するように適合された任意のデバイス、またはこれらの任意の組合せとすることができる。図1には、光記憶装置105およびフロッピー・ドライブ106を含むものとして、不揮発性の大容量記憶域104を示す。入出力デバイス107は、キーボード、マウス、表示画面、プリンタなど、またはこれらの任意の組合せとすることができる。BIOS ROM108は、キーボード、表示画面、ディスク・ドライブ、シリアル通信機構などの周辺デバイスを制御するためのコードを含むことができる。BIOS ROM108はまた、その他の様々な機能を実施するのに使用されるコードを含むこともできる。

【0011】

図2は、本発明の一実施形態による安全な実行コンポーネントを有するプロセッサと、安全な区分を有するメモリとの部分ブロック図である。図2には、例えば図1に示したコンピュータ・システム100などのコンピュータ・システムの一部であるプロセッサ210およびシステム・メモリ220が示してある。プロセッサ210およびシステム・メモリ220は、図1のプロセッサ110およびシステム・メモリ120と同じものとすることができる。プロセッサ210は、例えば図1のチップセット102などを介して、システム・メモリ220に結合することができる。

【0012】

プロセッサ210は、例えば算術論理ユニットなどの実行ユニット211を含むことができ、これはレジスタ・ファイル212に結合することができる。レジスタ・ファイル212は、汎用レジスタ、フラグ・レジスタ、命令ポインタ、インデックス・レジスタなど、またはこれらの組合せなど、複数のレジスタを含むことができる。レジスタ・ファイル212は、安全な区分レジスタ214を含むことができる。実行ユニット211は、オンチップBIOS(basic input/output system)215、プロセッサ・キー記憶要素216、および乱数生成器(RNG)ユニット217に結合することができる。オンチップBIOS215は、プロセッサがシステム・メモリ120など他のシステム・コンポーネントと通信するために使用する、焼き込まれたロジックを含むことができ、また、プロセッサが開始(ブートアップ)されるときに実行されるロジックを含むことができる。このロジックは、後述するようにブートストラップ・セキュリティ・ロジック241を含むことができる。さらに、オンチップBIOS215は、システム開始時にBIOS ROM108からシステム・メモリに命令をロードするためのロジック(例えばファームウェアやマイクロコードなど)を含むこともできる。プロセッサ鍵記憶要素216は、プロセッサ210が他のシステム・コンポーネントおよび他のコンピュータ・システムから受け取った情報を検証および認証するのに使用することのできる秘密鍵を含む。プロセッサ鍵は、プロセッサ鍵記憶要素216に焼き込むことができる。乱数生成器ユニット217は、任意のランダム化機能を使用するハードウェア乱数生成器とすることができる。一実施形態では、乱数生成器ユニット217は、物理デバイス中の統計的現象(例えば熱雑音)を利用して乱数を提供する。

【0013】

この実施形態では、実行ユニット211は、安全な区分実施ロジック218にも結合することができる。安全な区分実施ロジック218は、後述するように、メモリ中の安全区分を管理するためのロジックを含む。他の実施形態では、安全な区分実施ロジック218は、暗号ロジック219に結合される。暗号ロジック219は、安全区分に記憶される情報を暗号化し、安全区分から読み取られた情報を暗号化解除する。暗号ロジック219は、DES(Data Encryption Stanard)、RSA(Rivest−Shamir−Adleman)、DSS(Digital Signal Standard)暗号化などのアルゴリズムを実装したハードウェア・ロジックとすることができる。一実施形態では、暗号ロジック219は、プロセッサ鍵記憶要素216に記憶されたプロセッサ鍵ではなく、プラットフォーム特有の鍵を使用する。安全な区分実施ロジック218および暗号ロジック219は、アドレス変換バッファ(TLB)213に結合することができる。TLB213は、プロセッサ210のアドレス空間中の仮想アドレスを、システム・メモリ220中の物理アドレスおよびプロセッサ210からアクセスされる他のメモリ中の物理アドレスとマッチさせるのに使用することができる。

【0014】

図2にはまた、安全なメモリ区分223を含むシステム・メモリ220も示す。安全なメモリ区分223は、安全な区分中にあるコードからしかアクセスされない、物理メモリまたは仮想メモリのセクションとすることができる。一実施形態では、安全区分223は、2つの安全な区分レジスタ214によって決めることができる。例えば、安全区分223は、仮想メモリ中の安全区分の開始を指定する安全区分仮想アドレス基底レジスタと、安全区分のサイズを指定する安全区分仮想アドレス範囲レジスタとによって定義することができる。図2では、安全区分223は、システム・メモリ220中の物理アドレスにマッピングされた状態で示されている。安全なメモリ区分223は、安全なデータ・セクション225および安全なコード・セクション226を含むことができる。安全なコード・セクション226は、例えば信用できる検証実施命令242を記憶することができる。この命令242は、暗号アルゴリズムを適用し、ネットワークを介して受信された伝送(またはDVDやCD−ROMなどの媒体に記憶されたコンテンツ)の信憑性および保全性を検証するのに使用される。安全なデータ・セクション225は、秘密鍵や中間データ(例えばセキュリティ命令の制御フロー情報)など、安全コードによって使用されるデータを含むことができる。安全なコード・セクション226は、後述するように使用することのできるエントリ・ポイント228を有することができる。

【0015】

図2に示す実施形態は、次のように動作することができる。プロセッサ210は、プロセッサ・マイクロコードやオンチップBIOS検証ファームウェア・コード(図2にはブートストラップ・セキュリティ・ロジック241として示す)などのブートストラップ・セキュリティ・ロジックを使用して、BIOSコード(例えばBIOS ROM108中にある)を認証することにより、プラットフォームの保全性を保証する。次いで、安全なBIOS108は、チップセット中に他の保護機構があればその存在を妥当性検査する。一実施形態によれば、プロセッサ210がブートアップされるとき、プロセッサ210は、メモリを走査して安全区分のための位置を決定することにより、安全区分を生み出すことができる。次いでプロセッサは、安全区分基底レジスタおよび安全区分範囲レジスタをプログラムして、安全区分を定義することができる。これらのレジスタは、追記型レジスタとすることができる。他の実施形態では、他の機構を使用して安全区分を生み出すことができる。次いでプロセッサは、検証実施命令242、および鍵などの関連データを、システム・メモリ220中の安全なメモリ区分223にコピーすることができる。別の実施形態では、プロセッサのブートアップ中に、検証実施命令242をディスク・ドライブなど不揮発性の大容量記憶域から安全なメモリ区分223にコピーする。この実施形態では、プロセッサ210は、オンチップBIOS215に記憶されたセキュリティ・ロジック241と、プロセッサ鍵記憶要素216に記憶された鍵データを使用して、安全なメモリ区分223にコピーされた検証実施命令242およびデータの信憑性および保全性を検証することができる。この検証により、不揮発性メモリに記憶された検証実施命令242に、攻撃による破損または欠陥が生じているかどうかを判定することができる。ブートストラップ・セキュリティ・ロジック241をプロセッサに記憶し、検証実施命令242を不揮発性メモリに記憶することは、検証実施命令242をプロセッサ自体に焼き込むことよりも低コストであろう。

【0016】

一実施形態では、安全な区分実施ロジック218は、プロセッサ210によって行われるどんなメモリ・アクセスも監視する。このようなアクセスには、メモリに記憶された命令の実行や、メモリ中のデータに作用する命令の実行を含めることができる。命令は、メモリ中のある位置に記憶されたデータを読み取るとき、またはある位置にデータを書き込むときに、その位置でデータに作用する。この実施形態では、安全な区分実施ロジック218は、プロセッサ210によって各命令が実行される前に命令を調べることになる。命令が、区分エントリ・ポイント228以外の安全なメモリ区分223内の位置への分岐である場合は、安全な区分実施ロジックは、この命令を実施すべきでないと決定する。このような場合、区分実施ロジックは、トラップ・ハンドラにトラップすることができる。安全な区分実施ロジック218は、区分内のある位置から区分内の別の位置への分岐の実行は許可し、また、区分エントリ・ポイント228への分岐の実行は許可する。エントリ・ポイント228は、安全区分にジャンプしたソフトウェアの信憑性を検証する検証ルーチンの開始を含むことができる。したがって例えば、このルーチンは、未許可のまたは悪意あるプログラムが安全なコードを実行しないようにすることができる。さらに、エントリ・ポイントを安全なコード226へエンフォース(enforcing)することにより、安全な区分実施ロジック218は、未許可のまたは悪意あるコードが検証ルーチンをバイパスするのも防止する。他の実施形態では、命令が区分エントリ・ポイントに記憶されておらず、前に実行された命令が区分の開始の前の命令だったときは、安全な区分実施ロジックは、この命令を実行しないと決定する。したがって、区分エントリ・ポイント228が区分中の第1の命令でない場合、安全な区分実施ロジック218は、プロセッサがエントリ・ポイント以外のポイントで安全区分中に続けて進まないようにすることになる。

【0017】

この実施形態では、命令が安全区分外にあり、安全区分内の位置に作用(例えば読取りまたは書込み)しようとしているときは、安全な区分実施ロジックは、この命令を実行しないと決定する。したがって、安全なコード・セクション226中の信用できる命令だけが、安全なメモリ区分223の安全なデータ・セクション225内のデータに作用することができる。この実施形態では、安全区分中に位置するコードによってアクセスできることを除いては、安全データにアクセスすることはできない。他の実施形態では、安全区分中のコードは、安全区分外にあるデータにアクセスすることができる。別の実施形態では、この区分の安全なデータ・セクション225中のデータに作用しようとする命令が適切な読取り/書込み許可を有さない場合は、安全な区分実施ロジック218は、この命令を実行しないと決定することができる。別の実施形態では、安全区分外の命令が安全区分内の位置に作用しようとするときは、安全な区分実施ロジック218は、トラップ・ハンドラにトラップすることができる。また、命令が適切な読取り/書込み許可なしで安全なデータ・セクション中のデータに作用しようとするときも、トラップ・ハンドラにトラップすることができる。

【0018】

一実施形態では、安全なメモリ区分223は、仮想メモリ中の区分とすることができる。一実施形態では、プロセッサのアドレス空間は仮想メモリ・アドレス空間であり、すべての命令は、仮想アドレスでメモリをアドレス指定する。この実施形態では、安全区分は、プロセッサ210中で、仮想アドレス基底レジスタや仮想アドレス範囲レジスタなど、仮想アドレスによって指定される。安全区分を仮想アドレスで指定することにより、安全な区分実施ロジックはより早くパイプライン中に位置することができる。アドレス変換バッファ213が、これらの仮想アドレスを物理アドレスに変換することができる。安全区分についての仮想アドレスから物理アドレスへのマッピングは、信用できる機構を介して行うことができる。

【0019】

図3は、仮想メモリ区分および物理メモリ区分の部分ブロック図である。図3には、アプレット空間367およびカーネル空間365を有する仮想メモリ360を示す。アプレット空間367およびカーネル空間365は、物理メモリ320中の安全区分323にマッピングする。安全区分323中の情報は、不揮発性メモリ340中の安全な不揮発性空間345にスワップアウトすることができる。不揮発性メモリ340はフラッシュ・メモリとすることができる。一実施形態では、安全な不揮発性空間345は、安全区分323中のコードまたはデータのわずかな部分しか含まない。

【0020】

一実施形態では、検証実施命令242および関連データは、プロセッサ210からメモリに移行する間またはメモリに記憶されている間に暴かれないよう保護するために、暗号化された形で安全区分223に記憶される。この実施形態によれば、安全なコードおよびデータは、メモリ中の安全区分からプロセッサ210に転送された後で、実行ユニット211が作用できるように暗号ロジック219によって暗号化解除されることになる。反対に、安全なコードおよびデータがプロセッサ210からメモリ中の安全区分に転送される前には、暗号ロジック219によって暗号化されることになる。このようにすることで、安全なコードおよびデータは、例えばダイレクト・メモリ・アクセス、ロジック・アナライザ、イオン・ビームなどによる攻撃から保護されることになる。十分に強力な暗号化が用いられれば、攻撃者は、安全区分の内容を決定することができたとしても、安全なコードまたはデータを決定することはできないことになる。一実施形態では、安全なコードおよびデータは、例えばディフィー・ヘルマン・メソッドなどの共有暗号アルゴリズムを使用して暗号化および暗号化解除される。このような実施形態では、カバー鍵を使用してデータをカバーすることができ、このカバー鍵は共有されない。カバー鍵は、ブートアップ・ロジックによって生成することができる。他の実施形態では、1つのシステムがいくつかのプロセッサを有し、カバー鍵はシステム・プロセッサによって共有される。

【0021】

他の実施形態では、コンピュータ・システムは、ディスク・ドライブなど不揮発性の大容量記憶域中に安全区分を有する。不揮発性の大容量記憶域中の安全区分は、揮発性の大容量記憶域中の安全区分への追加的なものとすることができる。この実施形態によれば、不揮発性メモリ中の区分は、安全にされたコードによってのみアドレス指定可能である。

【0022】

乱数生成器217を使用して、暗号アルゴリズムの実施または新しい鍵の生成を行うことができる。プロセッサは、安全な不揮発性(NV)メモリを使用して、単調な値を最新のものに維持することができる。

【0023】

図4に、本発明の一実施形態による命令処理方法のフロー・チャートを示す。命令は、例えば、図1および2のプロセッサ110や210などのプロセッサによって実行されるアセンブリ言語命令とすることができる。実行前に、命令を調べる(401)。命令が仮想メモリ中の位置区分内の位置への未許可アクセスであるときは、この命令を実行しないと決定する。一実施形態では、命令が区分内の位置にあるデータに作用するものであり、命令が区分内に記憶されていないときは、この命令を実行しないと決定する(402)。他の実施形態では、命令が区分外の位置からの分岐であり、この分岐が区分内の位置への分岐であり、この分岐が区分エントリ・ポイントへの分岐でないときは、この命令を実行しないと決定する(403)。別の実施形態によれば、命令が区分エントリ・ポイントに記憶されておらず、前に実行された命令が区分の開始の直前の命令であったときは、この命令を実行しないと決定する(404)。命令を許可すると決定した場合は、命令を実行する(405)。例えば、命令が区分内のある位置から区分内の別の位置に分岐するとき、および命令が区分外の位置から区分エントリ・ポイントに分岐するときは、この命令を実行することができる。一実施形態によれば、この方法は、命令を実行しないと決定したときにトラップ・ハンドラにトラップすることを含む(406)。

【0024】

図5に、本発明の一実施形態による別の命令処理方法のフロー・チャートを示す。一実施形態によれば、暗号化された命令をメモリ中の安全区分からプロセッサに読み込む(501)。命令は、任意の暗号技術を用いて暗号化されたものとすることができる。読み込んだ命令は、例えば図2に示した暗号ロジック219を使用して暗号化解除する(502)。次いで、暗号化解除した命令を実行することができる。一実施形態では、安全区分からデータを読み取る命令の場合は(503)、安全区分からデータを読み取り、読み取ったデータを暗号化解除する(504)。別の実施形態では、安全区分中の位置にデータを書き込む命令の場合は(505)、データを暗号化し、暗号化したデータを安全区分に書き込む(506)。他の実施形態では、安全区分からデータを読み取る命令か、または安全区分中の位置にデータを書き込む命令かを決定することは、データの仮想アドレスを安全区分の境界と比較することを含む。

【0025】

セキュリティ特権レベル(SPL)

一実施形態では、2つの「セキュリティ特権レベル」を定義することができる。一方の特権レベルは、セキュリティ・カーネル特権レベルと呼び、これは、プリミティブなセキュリティ機能/サービスだけを実行するためのものとすることができる。第2の特権レベルは、プロセッサまたは第三者から供給されたセキュリティ・コードを実行するためのものと定義することができる。この第2の特権レベルは、アプレット特権レベルと呼ぶことができる。これらの新しいセキュリティ特権レベル(SPL)は、実行の特権レベルに関する既存の概念と直交することができる。したがってこの実施形態では、所与のアドレス範囲に対するアクセス(実行/読取り/書込み)特権は、現在特権レベル(CPL)だけでなく現在SPL(CSPL)とも相関関係になる。CSPLは、現在の実行に関連するセキュリティ特権レベルを示す。CSPLのデフォルト値は3とすることができる。この場合、CSPLが3のときは、実行モデルはデフォルト実行モデルと呼ぶことができる。CSPLがデフォルト以外の値を有するときは、実行モデルは「隠し実行」モデルの実行モデルと呼ぶ。

【0026】

2つの特権レベルは、SPL0(カーネルの場合)およびSPL1(アプレットの場合)と呼ぶことができる。複合特権レベルはリングx.yと呼ぶことができ、xは現在の実行についてのCPLであり、yは現在の実行についてのCSPLである。したがって、現在の実行の特権レベルが3.3である場合、これは現在のアプリケーションがデフォルト・リング3で実行されていることを意味する。しかし、現在特権レベルが3.0である場合は、実行についての現在特権レベルがリング3であり、アクセス権がセキュリティ・カーネル特権レベルに関連することを意味する。一実施形態では、実モードではCSPLは常に3であり、この場合、実モードでの隠し実行に対するサポートはない。

【0027】

カーネル特権レベル

アーキテクチャは、カーネル特権レベルで使用される新しい仮想アドレス範囲を定義することができる。新しい仮想アドレス範囲は、仮想アドレス基底レジスタ・カーネル(VABRk)および仮想アドレス範囲レジスタ・カーネル(VARRk)によって定義することができる。VABRkおよびVARRkによって定義する仮想アドレス範囲は、それに関連するカーネル・レベルのセキュリティ・アクセス権を有するように定義することができ、安全なカーネル空間、またはカーネルの安全なメモリ区分と呼ぶことができる。

【0028】

一実施形態では、安全なカーネル空間内のコードだけが、この空間で読取りまたは書込みを行うことができる。この場合、安全なカーネル空間内のデータおよびコードの保全性およびプライバシーがこの空間の外のコードによって損なわれることはない。他の実施形態では、安全なカーネル空間内のコードは、任意の仮想アドレス空間に対するデータの読取りおよび書込みを、そのようなアクセスが例えば既存のセグメンテーションおよびページング保護機構によって許される限り、行うことができる。他の実施形態では、セキュリティ・カーネル特権レベルにあるときだけ実行できる命令が定義される。別の実施形態では、カーネル仮想アドレス空間は自由に再配置可能である。別の実施形態では、安全区分のサイズは、ブートアップ時に固定され、一般のシステム・ソフトウェアの制御下にはない。例えば、プリOSファームウェアまたはオンチップ・マイクロコードだけが、仮想アドレス範囲レジスタに書き込むことができる。この場合、仮想アドレス範囲レジスタは、ソフトウェアによる書込みは全く不可能(プロセッサ・マイクロコードによって書き込まれる場合)とするか、またはリセット後に1度だけ書き込める(ファームウェアによって書き込まれる場合)とすることができる。

【0029】

別の実施形態では、安全なカーネル空間への固定エントリ・ポイントがあり、この空間の外から、このエントリ・ポイントに対する事前定義済みオフセット以外のオフセットまで安全なカーネル空間に分岐するのは違反である。デフォルトのセキュリティ特権を有するアドレス空間からは、固定エントリ・ポイントに入るのである限り、どんな制御転送機構を介しても安全なカーネル空間に入ることができる。他の実施形態では、カーネル・セキュリティ特権レベルにあるコードから要求されるカーネル・サービスは、要求元の現在特権レベルと相関関係にあるものとすることができる。この実施形態では、安全なカーネル空間へのエントリ・ポイントにあるコードは、呼出し元の現在特権レベルおよび現在のセキュリティ特権レベルを調べて、要求されているサービスが可能か否かを決定する。一実施形態では、安全カーネル・アドレス空間は、現在のセキュリティ特権レベルx.3を有する空間に、任意の制御転送機構を介して出ることができる。セキュリティ・カーネルが呼出し/リターン機構を使用してプログラム・フローを変更する場合、セキュリティ・カーネルは、その安全なスタック空間を管理し、かつ、安全なアプリケーション・スタック空間と安全でないアプリケーション・スタック空間との間の移行を管理することが必要な場合がある。

【0030】

アプレット特権レベル

アーキテクチャは、プロセッサの一般的な仮想アドレス空間内で新しい仮想アドレス範囲を定義することができる。この仮想アドレス範囲は、2つのレジスタすなわち仮想アドレス基底レジスタ・アプレット(VABRa)および仮想アドレス範囲レジスタ・アプレット(VARRa)によって定義することができる。VABRaおよびVARRaによって定義するアドレス範囲は、アプレット・レベルを有し、それに関連するセキュリティ・アクセス権を有することができ、安全なアプレット空間と呼ぶことができる。

【0031】

一実施形態では、アプレット・セキュリティ特権レベルに対応する仮想アドレス空間の場合、読取りおよび書込みアクセス権は、アプレットまたはカーネル・セキュリティ特権レベルを有するアドレス範囲内で実行されているコードに限定される。一実施形態では、安全なアプレット空間を定義するアプリケーションは、同じプロセスのコンテキストで、同じ現在特権レベルの安全なカーネル空間も定義しなければならない。一実施形態では、カーネルまたはアプレット隠し実行コード以外のコードは、安全なアプレット空間内で読取りまたは書込みを行うことができない。したがって、安全なアドレス空間内のデータまたはコードの保全性およびプライバシーが、セキュリティ・アクセス権を有さないコード(すなわち現在のセキュリティ特権レベル3)によって損なわれることはない。この実施形態では、安全なアプレット空間内のコードは、安全なカーネル・アドレス空間内ではデータの読取りまたは書込みを行うことはできず、安全なアプレット空間内のコードは、既存のセグメンテーションおよびページングおよび保護機構によって許される限り、安全なカーネル空間以外ならどんなアドレス範囲に対しても読取りおよび/または書込みを行うことができる。安全なアプレット空間は自由に再配置可能である。区分のサイズは、ブート時に固定することができ、一般のシステム・ソフトウェアの制御下にはない。この実施形態では、プリOSファームウェアまたはオンチップ・マイクロコードだけが、VARRaレジスタに書き込むことができる。したがって、レジスタVARRaは、ソフトウェアによる書込みは全く不可能(プロセッサ・マイクロコードによって書き込まれる場合)であるか、またはリセット後に1度だけ書き込める(ファームウェアによって書き込まれる場合)。

【0032】

一実施形態では、安全なアプレット空間には、安全なカーネル空間からしか入ることができない。この実施形態では、デフォルト・セキュリティ空間から安全なアプレット空間に分岐するのは違反とすることができるが、安全なカーネル空間から安全なアプレット空間へのエントリ・ポイントには制約はないものとすることができる。この実施形態では、デフォルト・セキュリティ特権を有するアドレス空間から安全なアプレット空間中の機能を呼び出すには、現在安全なアプレット空間内の機能の要求についての適切な「信任状」と共に、安全なカーネル空間中の固定エントリ・ポイントに制御を転送する必要がある。安全なアプレット・アドレス空間は、現在のセキュリティ特権レベル3を有する空間に、任意の制御転送機構を介して出ることができる。ただし、デフォルト・セキュリティを有する空間中の機能をアプレットが呼び出したい場合は、その安全なカーネル空間への機能呼出しを介してこれを行う。

【0033】

一実施形態では、安全なアプレット空間と安全なカーネル空間の間の移行は、デフォルト・セキュリティを有するアドレス空間と安全なカーネル空間の間の移行と同様だが、例外として、アプレットは、追加のセキュリティ・カーネル機能を呼び出すことができる。この実施形態では、安全なアプレット空間は、あらゆる割込みが安全なアプレット空間からの退出を引き起こすことを除いては、安全なアプレット空間内での制御転送のために任意の制御転送機構を使用することができる。安全なアプレット空間は、セキュリティ・カーネルが安全なアプレット空間の管理をサポートし、安全なアプリケーション・スタック空間と安全でないアプリケーション・スタック空間との間の移行をサポートする場合だけ、呼出し/リターン機構を使用することができる。

【0034】

安全な物理メモリ(RAMおよび不揮発性)区分

一実施形態では、セキュリティ拡張は、物理メモリ中の1つの「安全」区分を定義する。プロセッサがセキュリティ・カーネル特権レベルだけを実装している場合は、安全な物理空間のサイズは安全なカーネル空間のサイズ以上である。プロセッサがセキュリティ・カーネル特権レベルとアプレット特権レベルの両方をサポートする場合は、物理区分のサイズは、安全なカーネル空間と安全なアプレット空間の合計以上とすることができる。安全な物理メモリ区分は、物理アドレス基底レジスタ(PABR)および物理アドレス範囲レジスタ(PARR)によって定義することができる。一実施形態では、安全な物理メモリ区分の基底と範囲は両方とも、ブート時に固定され、したがって一般のシステム・ソフトウェアの制御下にはない。プリOSファームウェアだけがPABRまたはPARRレジスタに書き込むことができる。したがってこれらのレジスタは、リセット後に1度だけ書き込むことができる。

【0035】

物理アドレス区分は、仮想アドレス機構がイネーブルのとき(例えばプロセッサが保護モードで実行しているとき)、安全な仮想アドレス区分のための物理メモリを提供するのに使用することができる。仮想アドレス機構がディセーブルのとき(例えばプロセッサが実モードのとき)は、プロセッサ・ハードウェアは、安全な物理メモリ区分へのどんなアクセスも許可せず、この結果、実モードでの安全な物理区分へのアクセスはいずれも違反オペレーション・トラップとなる。

【0036】

一実施形態では、安全な物理メモリ区分は、プロセッサ・ダイ中の物理メモリとして、または同じパッケージ中の別個のダイとして、または外部システム・メモリの一部として提供することができる。安全な物理区分を外部システム・メモリとして実装する場合は、メモリ・コントローラもPABRおよびPARRと同様のレジスタの対を実装し、アドレス空間がDMAデバイスからアクセスを受けないようにすることが有利である。プリOS BIOSが、チップセット中に適切な保護機構があることを検証することができる。安全な物理メモリの一部は、不揮発性メモリに対応することができる。NV物理メモリ区分に使用される基底アドレスは、PABRと同じものとすることができる。追加の範囲レジスタとして、NVメモリ範囲レジスタすなわちNMRRがあってもよく、これは、安全なNVメモリ区分のサイズを定義するものであり、SPL0のコードによってしか書くことができない。安全なNVメモリ空間は、同じパッケージ中の別個のダイとしてあってもよく、外部コンポーネントの一部としてあってもよい。一実施形態では、このNVメモリへは、安全なカーネル空間で実行されているコードによって要求が開始された場合だけアクセス可能である。

【0037】

一実施形態では、安全なアドレス空間には4つのアーキテクチャ区分がある。すなわち、1)安全なアプレット空間、2)アプレットから要求されたセキュリティ・カーネル機能を実行するための、アプレット・アドレス空間に関連する安全な物理メモリ、3)カーネル・コードおよびデータのための安全な物理メモリ、4)安全なNVメモリである。アプレット空間のための安全な物理メモリと、アプレット実行に関連する安全なカーネル空間の一部とは、プロセスごとのリソースとすることができる。安全なカーネル空間は、安全なアプレット物理アドレス空間の内容、ならびに安全なアプレット・コードから呼び出されるセキュリティ・カーネル機能のために予約される安全なカーネル空間の一部の内容の、暗号化バージョンを保存する機能を実装することができる。安全なカーネル・アドレス空間はまた、安全なアプレット物理メモリと、アプレット空間に関連する安全なカーネル空間の一部とを復元する機能も実装することができる。これらの機能は、安全なアプレット物理メモリと、アプレット空間に関連するカーネル・メモリとを、いくつかのプロセス間で「仮想化」することを可能にする。スワップアウトされた状態の保全性は、スワップされた状態に関連するハッシュ値を、保存した状態のこのインスタンスに対応する「固有タグ」と共に安全なNVメモリに保持することによって提供することができる。

【0038】

一実施形態では、いくつかのカーネル機能を同時に実行することを可能にするのに十分な安全なカーネル空間物理メモリが提供され、実行の最中にセキュリティ・ドライバによって開始されたカーネル機能のスワップアウトを可能にすることは必要ない。他の実施形態では、セキュリティ機能の実行に割り振られた安全なカーネル空間が使用中になった後は、以後にカーネルのセキュリティ機能の要求があっても、前に実行されているセキュリティ機能が完了するまでブロックされる。

【0039】

プロセッサ鍵

一実施形態では、プロセッサは、固有IDに加えて秘密鍵/公開鍵の対も有することができる。この鍵の対は、RSA鍵の対、DSS鍵の対、または他の何らかの鍵の対とすることができるが、RSAが最も有利である。秘密鍵は、プロセッサ内部に「焼き込み」、特定のカーネルのセキュリティ機能でのみ使用できるものとすることができる。これらのセキュリティ機能は、特権レベルcp1.0(したがってカーネル・セキュリティ空間内)でのみ実行することができる。公開鍵もまた、関連する証明書と共にプロセッサ中に提供することができる。完全な秘密鍵と公開鍵のためにオンチップNV記憶域を提供することもできる。電源投入時にプロセッサが秘密鍵を明るみにすることなくオンチップ・マイクロコードまたはカーネル・コードを使用して完全な鍵を計算することができるような、公開鍵と秘密鍵を構成するのに十分なコンポーネントのための記憶域を提供すれば足りる。鍵の署名入りの値に対応する公開鍵証明書の部分もまた、オンチップNVメモリ中に提供すべきである。一実施形態では、RSA鍵の対は、1024ビットの秘密鍵の場合に、1344ビットの隠しNV記憶域をプロセッサ上に必要とする。すなわち、Pコンポーネント用に512ビット、Qコンポーネント用に512ビット、公開鍵証明書用に320ビットである(証明書中の署名がDSS署名であると仮定した場合)。

【0040】

秘密鍵と公開鍵に加えて、プロセッサは、オンチップNVセル中に56ビットのDES鍵を有することもできる(またはトリプルDESに対するサポートを有するべきである)。この鍵もまたプロセッサだけの秘密にしておくことができ、この鍵は、外部の安全な物理メモリに対して記憶/読取りを行うためのDES機能を実施するためだけに使用することができる。一実施形態では、プロセッサ特有のDES鍵ではなくプラットフォーム特有のDES鍵が使用される。

【0041】

セキュリティ特権レベルとプロセッサ・オペレーション・モードの対話

一実施形態では、デフォルトのプロセッサ実行と現在のセキュリティ特権レベルとの間に最小限の対話がある。他の実施形態では、仮想変換機構がオフのとき(すなわちプロセッサが実モードのとき)、CSPLは3(すなわちデフォルト・モード)にされ、安全な物理アドレス区分にアクセスするのは違反である。セキュリティ機能は、実モードまたは仮想モードではディセーブルとすることができる。この実施形態では、仮想変換機構がオンのとき(すなわちプロセッサが保護モードのとき)、安全な仮想アドレス区分へのアクセスに関するどんなTLBミスも、プロセッサが新しい変換アルゴリズムを使用して直接処理する。TLBミスは、TLBに関係するどんな障害も生じない。

【0042】

一実施形態では、安全なアドレス空間内でアクセス権がCSPLによってのみ制御されるように、安全なアドレス空間についての仮想−物理マッピングのためのページ変換エントリ・フォーマットを定義することができる。安全な仮想区分のいずれかからコードを実行するときは、性能監視機能がディセーブルになる。中断または外部割込みのせいで安全なカーネル空間または安全なアプレット空間の外に移行する場合があるときは、適切なレジスタを安全なカーネル空間内の事前定義済みのブロックに保存することができる。安全なアドレス空間内のデータを外部メモリに書き込む前にレジスタ中の一時的な値を保存するのに外部のシステム・メモリを使用することができる場合は、プロセッサは、プラットフォーム特有の「カバー鍵」を使用して、オンチップDESユニットで自動的にこの値を暗号化することができる。これらのレジスタを安全な物理メモリに保存した後、対応するプロセス・レジスタ値を、正当だが無意味ないくつかの値に変更することができる。例えば、EIPを何らかの正当な固定値に変更できることを除いては、ほとんどのデータ/アドレス・レジスタは、すべて「0」に変更することができる。

【0043】

セキュリティ・アドレス空間から外への移行は、オンチップ・マイクロコードによって、またはカーネルの安全な仮想アドレス区分内の割込み機構によって扱うことができる。安全な物理アドレス区分のために外部メモリが使用される場合、いくつかの実装形態では、プラットフォームの「カバー鍵」でDESを使用して命令ストリームの暗号化バージョンを安全な仮想アドレス区分からフェッチすることをサポートすることができる。

【0044】

一実施形態では、新しい安全移行(TSR)を定義することができる。この実施形態によれば、プログラム制御を他の空間から安全なカーネル空間に転送する制御転送機構はいずれも、呼出し元のCPLおよびCSPLをこのレジスタ中に提供する。安全なカーネル空間中のエントリ・ポイントにあるコードが、これらのビットおよび要求されているサービスを調べて、要求されているサービスを許可すべきか否かを決定することができる。例えば、いくつかのセキュリティ・サービスは、CPL0のコード(すなわちセキュリティ・ドライバ)からしか要求することができない。一実施形態では、TSRレジスタは、ハードウェアまたは安全なカーネル・コード(CSPL0)によってしか更新することができない。

【0045】

一実施形態では、安全なカーネル空間には固定エントリ・ポイントがある。この実施形態では、他のどんなオフセットへの分岐も違反である。レジスタの1つが、セキュリティ・アドレス空間またはアプリケーション・アドレス空間内で実行すべき機能番号を指定することができる。機能の中には、追加のパラメータを必要とするものもある。例えば、入力オペランドや、ターゲット・コード/データの暗号化解除に使用される鍵などである。一実施形態では、デフォルト・セキュリティ(CSPL3)を有するアドレス空間から安全なアプレット空間に制御を転送することは許されない。別の実施形態では、安全な物理空間についての「ライトバック」属性を選択するために、安全な仮想アドレス空間についてのキャッシュ制御ビットが事前定義される。

【0046】

セキュリティ命令

本発明の機能を実装するために、セキュリティ命令を設けることができる。これらの命令は、セキュリティ機能をサポートするのに必要な命令として分類することができ、あるいは、セキュリティ機能の性能または異なる特権レベル間の移行の性能を向上させるための命令として分類することができる。一実施形態では、最小限のネイティブ・セキュリティ機能では、実装形態がカーネル・セキュリティ特権レベルを「ロジック・アナライザ」脅威レベルでサポートすることが必要である。この機能レベルをサポートするのに使用することのできる命令は、(1)cp1.0特権レベルでプロセッサ秘密鍵を読み取る命令、(2)cp1.0特権レベルでプラットフォーム「カバー」鍵に、かつ別のモデル特有レジスタに書き込む命令、(3)いずれかのCPLまたはCSPLでプロセッサの公開鍵を証明書と共に読み取る命令、(4)いずれかのCPLまたはCSPLでRNGを読み取る命令である。

【0047】

その他の命令を定義して、実装形態を容易にし、異なるセキュリティ特権を有するアドレス空間の間の移行を促進することもできる。これらの命令には、次に現れる制御転送命令が実際に現在のセキュリティ特権レベルの変更を必要とすることを示すための分岐「ヒント」命令を含めることができる。この命令は、制御を安全なアプレット空間中のコードに転送する命令として実装することもでき、制御を安全なカーネル空間に転送する命令として実装することもでき、かつ/または、制御をデフォルトのセキュリティ特権レベルに転送する命令として実装することもできる。使用できる別の命令は、安全なNVメモリに記憶する命令である。この命令は、現在の記憶がNVメモリを対象としていることを設計のバックエンドではなくフロントエンドで知らせることにより、実装を補助することができる。

【0048】

ソフトウェア・モデル

セキュリティ・カーネル空間を実装するには、多くのオプションが可能である。一実施形態では、セキュリティ・カーネルは、セキュリティ機能を1つだけ実装することができる。他の実施形態では、セキュリティ・カーネルは、単に追加の機能をマクロコード中に実装するだけで、追加の機能をサポートすることができる。別の実施形態では、セキュリティ・カーネルは、セキュリティ・ドライバから1度に1つの機能が呼び出されることしか許可しないポリシーを実装することができる。この場合、いずれかの追加セキュリティ機能の実行を開始する前に、前のセキュリティ機能を完了すべきである。別の実施形態では、セキュリティ・カーネルは、そのリソース内で生きた機能を1つしかサポートできないが、セキュリティ・ドライバによって安全なカーネル空間を仮想化することができる。この手法は、部分的に実行された機能の状態を暗号化して、新たにロードされた機能に対して保全性チェックを実施する場合に、大きなオーバーヘッドにつながることがある。別の実施形態は、いくつかのセキュリティ機能が同時に生きられるだけの十分な空間を安全なカーネル空間に与え、この空間の「仮想化」はサポートしない。

【0049】

一実施形態では、CSPL3のアプリケーションがカーネルのセキュリティ機能を呼び出したいとき、このアプリケーションは、CPL0およびCSPL3で実行されているセキュリティ・ドライバを介して要求を出すべきである。性能の理由から、このアーキテクチャは、セキュリティ・ドライバを介した呼出しのオーバーヘッドなしにアプリケーションがそれに関連する安全なアプレット中の機能を呼び出せるようにすることができる。CSPL3のアプリケーションは、安全なカーネル空間へのエントリ・ポイントに対する制約が守られる限り、安全なカーネル空間を介してこのような要求を出すことができる。固定エントリ・ポイントにある安全なカーネル・コードが、呼出し元が指定のサービスを要求するのにふさわしい特権レベル(PLとSPLの両方)を有していたことを検証することを担う。このために、新しいレジスタとして移行状況レジスタ(TSR)を定義して、呼出し元のPLおよびSPLを安全なカーネル空間および安全なアプレット空間に提供することができる。

【0050】

性能の理由から、安全なアプレットが制御転送命令を介して制御をアプリケーションに転送して戻せるようにすることができる。実行のプライバシーを維持するために、アプレットは、セキュリティ・カーネルが安全なスタックに対するサポートを提供する場合だけ、制御をアプリケーションに転送する呼出し命令を使用すべきである。一実施形態では、呼出し元を検証するために安全なカーネル空間に負担を課すのではなく、アプリケーションから安全なアプレット空間への制御転送の要求は、セキュリティ・ドライバを介してのみ可能とすることができる。一実施形態では、インフラストラクチャはまた、エントリ・ポイントに対する制約が守られる限り、安全なアプレットが直接制御転送命令を介してカーネル空間中のセキュリティ機能を呼び出すことも可能にする。安全なカーネル空間は、生きたセキュリティ機能の呼出しを1度に1つサポートするのに十分な、現在安全なアプレットに関連する空間を提供するだけでよい。一実施形態では、どんなCPLおよびCSPLからでも安全なカーネル空間に入ることができるとしても、エントリ・ポイントにあるセキュリティ・カーネル・コードは、許可されたセキュリティ・カーネル・サービス要求だけしか所与のPLおよびSPLから出されないようにする。エントリ・ポイントにあるセキュリティ・カーネル・コードは、移行状況レジスタ(TSR)中の要求元の特権レベルを調べて、この決定を行うことができる。

【0051】

レジスタ

レジスタを使用して、安全区分機構を管理することができる。これらのレジスタには、安全カーネル仮想アドレス空間、アプレット仮想アドレス空間、物理アドレス空間、および不揮発性メモリ・アドレス空間のための、基底レジスタおよび範囲レジスタを含めることができる。また、様々なプロセッサ鍵にアクセスするためのレジスタを提供することもできる。これらには、プロセッサ秘密鍵のためのレジスタと、プロセッサ公開鍵およびそれに加えて証明書に対応する署名、ならびにプロセッサDES「カバー鍵」のためのレジスタを含めることができる。レジスタは読取り専用レジスタとすることができる。

【0052】

その他のレジスタには、セキュリティ・アドレス空間への移行のために呼出し元のPLおよびSPLを提供する移行状況レジスタを含めることができる。さらに、固有タグ番号レジスタが、隠し実行の特定インスタンスに割り当てられたタグ番号を保持することができる。中断セキュリティ特権レベル・レジスタを使用して、セキュリティ特権レベルを記録することができる。これらのレジスタは、読取り/書込みレジスタとすることができる。

【0053】

安全カーネル仮想アドレス空間および安全なアプレット仮想アドレス空間の管理

一実施形態では、安全なカーネル・アドレス空間および安全なアプレット・アドレス空間は、仮想−物理変換機構がイネーブルのときだけ定義される。セキュリティ機能は、安全な仮想アドレス区分を安全な物理メモリにマッピングすることを実現するために、OSのメモリ・マネージャに依拠しなくてもよい。安全な仮想アドレス区分と安全な物理区分との間に、固定マッピングを定義することができる。安全な仮想アドレス空間にはアクセス・フォールトおよびダーティ・フォールトへの対応がないものとすることができ、キャッシュ制御ビットを「ライトバック」モードに設定することができる。一実施形態では、安全な仮想アドレス空間と安全な物理アドレス空間との間にリンクを確立するのに、OSサービスは必要ない。他の実施形態では、これらの仮想アドレス区分にはページ・フォールトの概念がない。

【0054】

安全な仮想空間は、固定線形マッピングを用いて安全な物理空間にマッピングすることができる。ページ変換は、PABRレジスタおよびVARRkレジスタと相関関係にあるものとすることができる。アクセス権は事前定義することができる。これらのアクセス権は、あらゆるCPLで実行/読取り/書込み権を許可することができ、それにより、仮想安全区分はどんなCPLにあることもできる。この実施形態では、エントリ・ポイントにおけるセキュリティ・カーネル・コードによって安全なアドレス空間への移行が認められると、安全な区分内の所与の仮想アドレスに対するアクセス許可は、CSPLによってのみ制御される。

【0055】

一実施形態では、安全な仮想アドレス空間は自由に再配置可能である。この実施形態では、安全な仮想区分が再配置されたときは常に、再配置された安全な仮想区分に関する前の有効マッピングはすべて無効になる。このようにして、新しい安全な仮想区分への分岐が行われるときは常に、新しい有効TLBエントリが新しい区分に対して確立される。他の実施形態では、デフォルト・セキュリティを有する仮想アドレス空間のためのTLB機構は、これらのPTEに関する物理ページ・アドレスが安全な物理空間と重複しないことを保証するように強化される。重複の可能性があると、違反オペレーション・フォールトが引き起される恐れがある。

【0056】

割込み

一実施形態では、カーネル・アドレスとアプレット・アドレスの両方についての隠し実行が、ソフトウェアによって、かつ/または外部割込みを通して割込みを受けることがある。カーネルとアプレットのいずれかのセキュリティ特権レベルで隠し実行の途中だったかもしれないプロセスのコンテキストを保存できるようにするアーキテクチャ機構を設けることができる。プロセスがセキュリティ特権レベルのうちの1つで実行されている間にシングルステッピングによる割り込みを受けた場合でも、ハードウェア機構およびソフトウェア機構は、実行のプライバシーおよび保全性が脅威モデルまで維持されるようにすることができる。割込みの処理に使用される機構は、プロセッサ・アーキテクチャの機能に応じて決まる。一実施形態では、セキュリティ特権レベルで実行されているコードが割込みを受けた場合にセキュリティ問題に対処するルーチンを、既存の割込みマイクロコードに追加する。別の実施形態では、新しいセキュリティ割込みベクトル・テーブルを定義して、これらの割込みを処理する。この実施形態では、プログラムがセキュリティ特権レベルで実行されている間のどんな割込みも、安全なカーネル・アドレス空間中のハンドラに転送される。この安全な割込みハンドラは、クリティカルな機能を実施して、割り込まれたコードのプライバシーおよび保全性を保証し、次いで、関連するすべての正しい割込み状況情報と共に、分岐してデフォルトの割込みベクトルに戻る。

【0057】

セキュリティ・レベルの仕様

様々な実装形態が、様々な脅威レベルに対する保護を与えることができる。例えばいくつかの実装形態は、ソフトウェア、インテリジェント入出力、およびロジック・アナライザ(観察モードのみ)による攻撃だけに対して保護を与えることができ、他の実装形態は、イオン・ビーム攻撃からの脅威を含めて、あらゆる脅威モデルに対して保護を与えることができる。ある種類の脅威に対する保護能力が、セキュリティ・レベルを定義する。単純なハードウェア攻撃(プロセッサをソケットから外して、保全性の損なわれたプラットフォームに配置し、安全な物理空間を確立するための高保全性BIOSに対する信頼を欺くことを含む)に対する保護は、すべてのセキュリティ・レベルが実現すべきである。一実装形態では、プロセッサは、プロセッサ・マイクロコードまたはオンチップBIOS検証ファームウェア・コードを使用してBIOSを認証することにより、プラットフォームの保全性を保証する。この場合、BIOSコードは、必要なセキュリティ機能がチップセット中にあればその存在を妥当性検査することができる。

【0058】

セキュリティ・レベル1(SL−1)モデルの一実施形態では、安全な仮想アドレス区分をマッピングするための外部システム・メモリおよびシステムNV(フラッシュ)メモリの、保護された区分が使用される。一実施形態では、隠し実行のためのコードは、共通プラットフォーム鍵を使用して暗号化され、保護された物理メモリ中に暗号化された形で保持される。デバイスの秘密鍵に対して作用するいくつかの機能については、これらがデバイスの秘密鍵のビットに依存する分岐を有さないことを保証するための安全対策をとることができる。これは、条件付き移動命令を使用することによって、または予測機能を使用することによって達成することができる。一実施形態では、すべての中間計算データは、クリアな形でプロセッサ・レジスタおよびオンチップ・キャッシュ中だけに保持される。一実施形態では、安全なアドレス範囲中のデータを保護された外部物理メモリ区分に記憶する必要があるときは常に、出て行くデータをバス・インタフェース・ユニット中のDESユニットを使用して暗号化する。安全な物理アドレス空間から入ってきたデータおよびコードを暗号化解除するためには、別個のDESユニットがあってもよく、共通のDESユニットを共用してもよい。DESユニットは、少なくとも56ビットのDES鍵を使用すれば有利である。実装形態によっては、より大きな鍵を使用することもできる(トリプルDESが使用される場合)。

【0059】

セキュリティ・レベル1は、あらゆる隠し実行に対するロジック・アナライザ(観察モード)までのセキュリティ脅威に対処することができる。安全な物理空間中のコードが暗号化された形であるとき、外部バス信号をアクティブに変更してプロセッサ/プラットフォームの秘密にアクセスすることは非常に難しい。ただし、このセキュリティ・レベルは、このような攻撃に対してどんな保証も提供しない。他の実施形態では、耐タンパ性ソフトウェアを使用して「既知テキスト」攻撃をさらに困難にする。セキュリティ・レベル1モデルはまた、秘密データを解読するために実装プローブ・モードおよびデバッグ・フックを使用して実装特有の状態へのアクセスを得ることに対しても、何らかの保護を与えることができる。さらに、SL1モードは、プロセッサが誤って挙動するようにして秘密データへのアクセスを得る電圧および周波数タンパ技法に対しても、限られたいくらかの量の保護を採用することができる。

【0060】

SL−1モデルでは、物理メモリの安全な区分の保護は、仮想−物理変換機構、プロセッサ中でのDES暗号化、およびメモリ・コントローラ中の物理メモリ・タイプ・レジスタを介して提供することができる。SL−1モデルでは、秘密データのプライバシーは、プロセッサ記憶域内だけで秘密データに作用することによって保証することができる。安全な物理メモリ・アドレス範囲内のデータがバス上に書き出されるときは常に、データはBIU中のDESユニットを使用して暗号化される。システムによっては、安全な物理メモリとの間でデータ/コードを暗号化/暗号化解除するDESユニットは、プロセッサ特有の鍵ではなくプラットフォーム特有の鍵を使用することが望ましい。

【0061】

SL−1モデルでは、安全な物理アドレス空間中の外部コードおよびデータはすべてプラットフォーム鍵で暗号化しておくことができるので、ロジック・アナライザで外部バス信号を見るだけではコードまたはデータを解読することができない。プロセッサ/プラットフォーム秘密鍵は、より高レベルの脅威モデルまで保護することもできる。外部コードが暗号化されるので、機能の中のどの命令が秘密鍵にアクセスしているか、あるいはプロセッサが最終的に秘密データをクリアなメモリに書くように入来命令ビット・ストリームをどのように変形するかを知ることは、非常に難しい。SL−1モデルはまた、プロセッサ実装特有のデバッグおよびマシンチェック機構を使用して、また電圧および周波数タンパ技法を使用してプロセッサ/プラットフォームの秘密にアクセスすることに対しても、適度な量の保護を与える。

【0062】

セキュリティ・レベル2(SL−2)モデルの一実施形態は、安全な物理メモリ区分の少なくとも一部のためのオンチップ物理メモリを設けることによって、セキュリティ・レベルをSL−1よりも上げたものである。この場合、すべての安全なNVメモリ区分はやはりプラットフォーム中にある。揮発性の安全な物理メモリのいくつかもまたシステム・メモリ中にある場合がある。外部のシステム・メモリの一部である安全な揮発性メモリの部分に対する安全保護は、SL−1と同様である。SL−2セキュリティ・モデルでは、隠し実行に関するコードを、暗号化された形で外部メモリからダウンロードすることができる。次いで、このコードを暗号化解除して、プロセッサ・オンチップ・メモリを使用して保全性を検証することができる。次いで、暗号化解除したコードをプロセッサのオンチップ・メモリ外で実行する。あらゆる秘密データも、クリアな形でオンチップ・メモリに保持される。

【0063】

このモデルの一実施形態によれば、オンチップ・メモリは、セキュリティ・ドライバによって管理される共有プロセッサ・リソースである。オンチップ・メモリの一部は種々のプロセスによって共有することができる。オンチップ・メモリのこの共有部分を仮想化することは、ドライバによって行うことができる。オンチップ・メモリのこの部分を暗号化および保存する能力を与えるためのセキュリティ・カーネル機能を、ドライバに利用可能にすることができる。また、オンチップ物理メモリの、前に保存された部分を暗号化解除および復元するためのセキュリティ・カーネル機能を利用可能にすることもできる。外部NVメモリへの秘密データの記憶もまた、同じDESを使用して暗号化することができる。SL−2モデルは、プロセッサ実装特有のプローブ・モードまたはデバッグ・フックを用いた攻撃、ならびに電圧および周波数タンパによる攻撃に対して、より高レベルの保護を与えることもできる。

【0064】

SL−2モデルでは、物理揮発性メモリの安全区分の保護は、仮想−物理変換機構、オンチップ物理メモリによって提供することができ、また、外部システム・メモリの一部である安全な物理空間の部分に対するDES暗号化によって提供することができる。SL−2モデルは、SL−1モデルと比較して、デバイス/プラットフォームの秘密鍵とプロセッサの隠し実行との両方のセキュリティ・レベルを上げることができる。外部物理メモリ中のクリティカルなコードおよびデータがすべて暗号化された形で、かつクリアな形でオンチップ物理メモリ中に保持される場合、攻撃者は、ロジック・アナライザで外部バス信号を見るだけではコードまたはデータを解読することができない。また、オンチップ・メモリへのダウンロードの保全性がチェックされる場合、ロジック・アナライザを使用して外部バス信号をドライブすることによって隠し実行の保全性を損ねることはできない。SL−2モデルはまた、秘密鍵を解読するために実装プローブおよびデバッグ・フックを使用して実装特有の状態へのアクセスを得ることに対しても、より多くの保護を与えることができる。SL−2モデルはまた、プロセッサが誤って挙動するようにして秘密データへのアクセスを得る電圧および周波数タンパ技法に対しても、追加の保護を採用することができる。

【0065】

セキュリティ・レベル3(SL−3)モデルの一実施形態は、オンチップの安全なNVメモリを提供することにより、または安全なNVメモリ区分をプロセッサ・ダイと同じパッケージ内にもってくることにより、セキュリティ・レベルをSL−2よりも上げたものである。一実施形態では、揮発性および不揮発性メモリのいくつかは、やはりシステム・メモリおよびシステムNVメモリの一部として存在することができる。さらに、このセキュリティ・レベルは、実装デバッグ・フック、マシン・チェック・アーキテクチャ、および様々な実行タンパ技法の使用に対して、また放射線攻撃の使用に対して、より高レベルの保護を与えることもできる。実装形態によっては、イオン・ビーム攻撃を妨げるために、プロセッサおよびNVメモリ・シリコン上に、またプロセッサと安全なNVメモリ・ダイとの間の相互接続上に、保護ダイ・コーティングを施すこともできる。揮発性および不揮発性メモリの区分がシステム・リソース中にあるので、これらの実装は、少なくともSL−1レベルまでのセキュリティを与える。

【0066】

SL−3モデルの実施形態では、物理揮発性ならびにNVメモリの安全な区分の保護は、仮想−物理変換機構とオンチップ物理メモリの組合せによって行われる。このモデルは、プロセッサ記憶域内だけで秘密データに作用することにより、秘密データのプライバシーを保証する。このモデルは、SL−2モデルと比較して、デバイス/プラットフォーム秘密鍵とプロセッサ隠し実行との両方セキュリティ・レベルを上げることができる。SL−3モデルでは、隠し実行に関係するすべての記憶域を1つのパッケージ内にもってくることができる。これにより、計算エンジンと隠し実行のための記憶域との間でどんな内部信号も明るみになることはない。さらにこのモデルでは、オンチップ(または同一パッケージ)NVメモリもまた、ハードウェア再生攻撃に対して保護することができる。SL−3モデルは、実装特有プローブおよびデバッグ・フックによる秘密データのリークに対して、広範な保護を与えることができる。このモデルはまた、プロセッサを誤動作させて、場合により秘密データをクリアな形で外部バス上に書き出させることのできる様々なタンパ手法に対しても、保護を与えることができる。実装形態によっては、イオン・ビーム攻撃を用いて秘密データにアクセスすることができないように、プロセッサおよび秘密記憶領域の上に保護ダイ・コーティングを施すこともできる。

【0067】

安全なカーネル・アドレス空間内のマクロ機能

安全なカーネル・アドレス空間内に実装することのできるマクロ機能には、認証機能、鍵管理機能、埋込み検証カーネル、署名機能、検証機能、アプレット・ロード機能、暗号化保存アプレット、暗号化復元アプレット、アプレット空間中の機能呼出しがある。

【0068】

結び

本発明の実施形態は、安全なメモリ区分を使用した安全な実行のための方法および装置に関するものである。本発明は、ホスト・プロセッサのコードおよびデータを保護するための特別なセキュリティ・コプロセッサを有する従来システムに勝る、いくつかの利点を提供する。本発明は、コプロセッサが必要ないので、コスト効果がより大きい。さらに本発明は、より高性能な汎用プロセッサ中でセキュリティ・コードを実行することができるので、より高性能な解決法である。さらに本発明は、コプロセッサ・データ転送オーバーヘッドがないので、より効率的な解決法でもある。

【0069】

本明細書では、本発明のいくつかの実施形態について具体的に図示および/または記述している。ただし、本発明の修正および変形も、本発明の趣旨および意図される範囲を逸脱することなく、以上の教示によってカバーされ、頭記の特許請求の範囲内にあることは理解されるであろう。例えば、メモリ区分は、仮想メモリ中に実装しても物理メモリ中に実装してもよい。別の例として、各実施形態は、SL−1、SL−2、SL−3のいずれかのセキュリティ・モデルに適合する特徴を含んでいればよい。

【特許請求の範囲】

【請求項1】

検証実施命令を記憶するための不揮発性メモリと、

安全区分を有するシステム・メモリと、そして

前記不揮発性メモリと前記システム・メモリに結合されたプロセッサと

を備え、

前記プロセッサは、

ブートストラップ安全ロジックを含むオンチップBIOSと、そして

前記オンチップBIOSと前記システム・メモリに結合された実施ユニットであって、前記ブートストラップ安全ロジックにより特定されるオペレーションを実施するように構成された前記実施ユニットと

を備え、

前記オペレーションは前記不揮発性メモリから前記安全区分へ前記検証実施命令をコピーするステップと前記検証実施命令の信頼性を検証するステップとを含む、

処理システム。

【請求項2】

前記プロセッサは、

キーを記憶するように構成されたキー記憶要素と、そして

前記実施ユニットと前記キー記憶要素に結合された暗号化ロジックであって、前記キーに基づいて前記検証実施命令を復号化するように構成された暗号化ロジックと

をさらに備える請求項1に記載の処理システム。

【請求項3】

前記暗号化ロジックはRSAアルゴリズムを実行する請求項2に記載の処理システム。

【請求項4】

前記キーがRSA秘密キーである請求項3に記載の処理システム。

【請求項5】

前記プロセッサは、前記実施ユニットに結合された安全区分実施ロジックであって、前記安全区分へのアクセスをモニターし、メモリ・アクセスを許可するか否かを決定するように構成された安全区分実施ロジックをさらに備える請求項1に記載の処理システム。

【請求項6】

前記プロセッサは、前記安全区分実施ロジックに結合され、仮想メモリ・アドレスを物理メモリ・アドレスに整合させるように構成されたTLBをさらに備える請求項5に記載の処理システム。

【請求項7】

前記システム・メモリはオンチップ物理メモリと外部システム・メモリを備え、前記プロセッサは仮想化することにより異なるプロセス間でオンチップ物理メモリを共有するように構成されている請求項1に記載の処理システム。

【請求項8】

前記プロセッサは前記外部システム・メモリに暗号化されたデータを記憶し、前記オンチップ物理メモリに復号化されたデータを記憶するように構成されている請求項1に記載の処理システム。

【請求項9】

第1のメモリから第2のメモリの安全区分に検証実施命令をコピーするために、オンチップBIOSに記憶されたブートストラップ安全ロジックを、前記プロセッサにより、実行するステップと、そして

その後、前記検証実施命令の信頼性を検証するステップと

を含む方法。

【請求項10】

前記プロセッサのキー記憶要素に記憶されたキーに基づいて前記検証実施命令を、前記暗号化ロジックにより、復号化するステップをさらに含む請求項9に記載の方法。

【請求項11】

前記暗号化ロジックはRSAアルゴリズムを実施する請求項10に記載の方法。

【請求項12】

前記キーはRSA秘密キーである請求項11に記載の方法。

【請求項13】

前記安全区分実施ロジックにより、前記安全区分へのアクセスをモニターし、メモリ・アクセスを許可するか否かを決定する請求項9に記載の方法。

【請求項14】

I/Oインタフェースと、ディスプレイ・デバイスと通信するように適応されたディスプレイ・コントローラと、スタンダード・ネットワーク・プロトコルを使用して通信するように適応されたネットワーク・インタフェースと、そしてオンチップ・メモリとを有するアプリケーション・プロセッサを含む処理システムを作動させるステップと、

不揮発性メモリに記憶された検証実施命令をシステム・メモリの安全区分にローディングするステップと、

プロセッサに含まれたオンチップBIOSに収容されたブートストラップ安全ロジックにより特定されるオペレーションを実行するステップであって、前記オペレーションが前記不揮発性メモリから前記安全区分に前記検証実施命令をコピーするステップと前記検証実施命令の信頼性を検証するステップを含む、ステップと

を含む方法。

【請求項15】

キー記憶要素内にRSA公開キーを記憶するステップと、

安全区分実施ロジックで前記安全区分へのアクセスをモニターするステップと、

前記安全区分実施ロジックでメモリ・アクセスを許可するか否かを決定するステップと、そして

仮想メモリ・アドレスを物理メモリ・アドレスにTLBで整合させるステップと

をさらに含む請求項14に記載の方法。

【請求項16】

前記不揮発性メモリはフラッシュ・メモリからなり、前記実行ユニットは演算ロジック・ユニットを含む、請求項14に記載の方法。

【請求項17】

1つまたは複数の安全区分レジスターにおいて前記システム・メモリの前記安全区分を定めるステップをさらに含む請求項14に記載の方法。

【請求項18】

前記安全区分実施ロジックでメモリ・アクセスを許可するか否かを決定するステップが、前記安全区分外のターゲット位置の分岐命令を検出するステップと、前記安全区分外に在る前記ターゲット位置に基づいて前記分岐命令を拒否するステップと、をさらに含む請求項15に記載の方法。

【請求項19】

前記暗号化ロジックが乱数発生器からなる請求項15に記載の方法。

【請求項1】

検証実施命令を記憶するための不揮発性メモリと、

安全区分を有するシステム・メモリと、そして

前記不揮発性メモリと前記システム・メモリに結合されたプロセッサと

を備え、

前記プロセッサは、

ブートストラップ安全ロジックを含むオンチップBIOSと、そして

前記オンチップBIOSと前記システム・メモリに結合された実施ユニットであって、前記ブートストラップ安全ロジックにより特定されるオペレーションを実施するように構成された前記実施ユニットと

を備え、

前記オペレーションは前記不揮発性メモリから前記安全区分へ前記検証実施命令をコピーするステップと前記検証実施命令の信頼性を検証するステップとを含む、

処理システム。

【請求項2】

前記プロセッサは、

キーを記憶するように構成されたキー記憶要素と、そして

前記実施ユニットと前記キー記憶要素に結合された暗号化ロジックであって、前記キーに基づいて前記検証実施命令を復号化するように構成された暗号化ロジックと

をさらに備える請求項1に記載の処理システム。

【請求項3】

前記暗号化ロジックはRSAアルゴリズムを実行する請求項2に記載の処理システム。

【請求項4】

前記キーがRSA秘密キーである請求項3に記載の処理システム。

【請求項5】

前記プロセッサは、前記実施ユニットに結合された安全区分実施ロジックであって、前記安全区分へのアクセスをモニターし、メモリ・アクセスを許可するか否かを決定するように構成された安全区分実施ロジックをさらに備える請求項1に記載の処理システム。

【請求項6】

前記プロセッサは、前記安全区分実施ロジックに結合され、仮想メモリ・アドレスを物理メモリ・アドレスに整合させるように構成されたTLBをさらに備える請求項5に記載の処理システム。

【請求項7】

前記システム・メモリはオンチップ物理メモリと外部システム・メモリを備え、前記プロセッサは仮想化することにより異なるプロセス間でオンチップ物理メモリを共有するように構成されている請求項1に記載の処理システム。

【請求項8】

前記プロセッサは前記外部システム・メモリに暗号化されたデータを記憶し、前記オンチップ物理メモリに復号化されたデータを記憶するように構成されている請求項1に記載の処理システム。

【請求項9】

第1のメモリから第2のメモリの安全区分に検証実施命令をコピーするために、オンチップBIOSに記憶されたブートストラップ安全ロジックを、前記プロセッサにより、実行するステップと、そして

その後、前記検証実施命令の信頼性を検証するステップと

を含む方法。

【請求項10】

前記プロセッサのキー記憶要素に記憶されたキーに基づいて前記検証実施命令を、前記暗号化ロジックにより、復号化するステップをさらに含む請求項9に記載の方法。

【請求項11】

前記暗号化ロジックはRSAアルゴリズムを実施する請求項10に記載の方法。

【請求項12】

前記キーはRSA秘密キーである請求項11に記載の方法。

【請求項13】

前記安全区分実施ロジックにより、前記安全区分へのアクセスをモニターし、メモリ・アクセスを許可するか否かを決定する請求項9に記載の方法。

【請求項14】

I/Oインタフェースと、ディスプレイ・デバイスと通信するように適応されたディスプレイ・コントローラと、スタンダード・ネットワーク・プロトコルを使用して通信するように適応されたネットワーク・インタフェースと、そしてオンチップ・メモリとを有するアプリケーション・プロセッサを含む処理システムを作動させるステップと、

不揮発性メモリに記憶された検証実施命令をシステム・メモリの安全区分にローディングするステップと、

プロセッサに含まれたオンチップBIOSに収容されたブートストラップ安全ロジックにより特定されるオペレーションを実行するステップであって、前記オペレーションが前記不揮発性メモリから前記安全区分に前記検証実施命令をコピーするステップと前記検証実施命令の信頼性を検証するステップを含む、ステップと

を含む方法。

【請求項15】

キー記憶要素内にRSA公開キーを記憶するステップと、

安全区分実施ロジックで前記安全区分へのアクセスをモニターするステップと、

前記安全区分実施ロジックでメモリ・アクセスを許可するか否かを決定するステップと、そして

仮想メモリ・アドレスを物理メモリ・アドレスにTLBで整合させるステップと

をさらに含む請求項14に記載の方法。

【請求項16】

前記不揮発性メモリはフラッシュ・メモリからなり、前記実行ユニットは演算ロジック・ユニットを含む、請求項14に記載の方法。

【請求項17】

1つまたは複数の安全区分レジスターにおいて前記システム・メモリの前記安全区分を定めるステップをさらに含む請求項14に記載の方法。

【請求項18】

前記安全区分実施ロジックでメモリ・アクセスを許可するか否かを決定するステップが、前記安全区分外のターゲット位置の分岐命令を検出するステップと、前記安全区分外に在る前記ターゲット位置に基づいて前記分岐命令を拒否するステップと、をさらに含む請求項15に記載の方法。

【請求項19】

前記暗号化ロジックが乱数発生器からなる請求項15に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−53898(P2012−53898A)

【公開日】平成24年3月15日(2012.3.15)

【国際特許分類】

【出願番号】特願2011−234826(P2011−234826)

【出願日】平成23年10月26日(2011.10.26)

【分割の表示】特願2002−508208(P2002−508208)の分割

【原出願日】平成13年6月7日(2001.6.7)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.フロッピー

【出願人】(591003943)インテル・コーポレーション (1,101)

【公開日】平成24年3月15日(2012.3.15)

【国際特許分類】

【出願日】平成23年10月26日(2011.10.26)

【分割の表示】特願2002−508208(P2002−508208)の分割

【原出願日】平成13年6月7日(2001.6.7)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.フロッピー

【出願人】(591003943)インテル・コーポレーション (1,101)

[ Back to top ]