定電圧電源回路

【課題】起動時や過負荷時に内部の消費電流を制限し、起動時においてオーバシュートの発生を抑制する。

【解決手段】定電圧電源回路は、誤差増幅部50と、出力用PMOS81を有する出力部80と、PMOS81に流れる負荷電流をモニタし、負荷電流に応じて誤差増幅部50のバイアス電流を増加させる負荷電流モニタ部60と、電流制限用の抵抗62を有し、負荷電流をモニタしてこの負荷電流に応じて誤差増幅部50のゲインを低下させるゲイン調整部70とを備えている。そのため、起動時や過負荷時にゲイン調整部70をリミッタ回路として動作するようになるため、起動時や過負荷時に内部の消費電流を制限できる。しかも、起動時においては、このリミッタ動作により、起動時の応答を遅くすることとなるため、オーバシュートの発生を抑制できる。

【解決手段】定電圧電源回路は、誤差増幅部50と、出力用PMOS81を有する出力部80と、PMOS81に流れる負荷電流をモニタし、負荷電流に応じて誤差増幅部50のバイアス電流を増加させる負荷電流モニタ部60と、電流制限用の抵抗62を有し、負荷電流をモニタしてこの負荷電流に応じて誤差増幅部50のゲインを低下させるゲイン調整部70とを備えている。そのため、起動時や過負荷時にゲイン調整部70をリミッタ回路として動作するようになるため、起動時や過負荷時に内部の消費電流を制限できる。しかも、起動時においては、このリミッタ動作により、起動時の応答を遅くすることとなるため、オーバシュートの発生を抑制できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路等に搭載される定電圧電源回路に関するものである。

【背景技術】

【0002】

図4は、従来の定電圧電源回路を示す回路図である。

この定電圧電源回路は、基準電圧Vrefと出力端子30から出力される出力電圧Voutに比例した電圧Vfbとの差分を増幅する誤差増幅部10と、この誤差増幅部10の出力側に接続され、誤差増幅部10の出力により制御されて出力端子30から出力する出力電圧Voutを一定に制御する出力部20とにより構成されている。

【0003】

誤差増幅部10は、電源電圧VCCノードに接続された負荷用のPチャネルMOSトランジスタ(以下「PMOS」という。)11,12と、このPMOS11,12に直列に接続され、基準電圧Vref及び電圧Vfbをそれぞれ入力して差動増幅する入力トランジスタであるNチャネルMOSトランジスタ(以下」「NMOS」という。)13,14と、このNMOS13,14とグランドGNDとの間に接続され、バイアス電圧Vbにより一定電流を流す定電流源用のNMOS15とを有する差動増幅器により構成されている。出力部20は、出力トランジスタであるPMOS21と分圧抵抗22,23とを有し、これらが電源電圧VCCノードとグランドGNDとの間に直列に接続されている。PMOS21と分圧抵抗22との接続点には、出力電圧Voutを出力する出力端子30が接続されている。

【0004】

一般には、急峻な負荷電流変動に対して出力電圧変動を抑制するために、容量値(例えば、数μF程度)のコンデンサ31を外部に接続して使用される。

【0005】

図5は、図4の定電圧電源回路における周波数特性を示す図である。

外部にコンデンサ31が接続された図4の回路構成の場合、定電圧電源回路の誤差増幅部10と出力部20の周波数特性は、図5に示すように、誤差増幅部10のポールよりも出力部20のポールが低周波域に存在する場合がある。2つのポールが存在する場合は、2つのポールが近い周波数域に存在すると、位相余裕がとれず、出力電圧Voutの発振を生じるおそれがあるため、十分に2つのポールを分離する必要がある。

【0006】

図5に示すように、出力部20のポールが低周波域にある場合には、出力部20のポールは、PMOS21を流れる負荷電流の大きさにより高周波側へ移動するため、このようなポール位置関係を持つ定電圧電源回路を安定動作させるには、負荷電流変動により出力部20のポールが変化しても位相余裕が十分とれるように、誤差増幅部10のポールを十分に高周波側に配置する必要があるが、そのためには誤差増幅部10のバイアス電流を大きくする等の対策が必要となる。しかし、大きな負荷電流駆動能力を必要とする用途では、出力部20のポールの高周波側への移動範囲が広がるため、誤差増幅部10のバイアス電流を大きくする対策だけでは、過大な電流を消費することとなり、おのずと限界がある。

【0007】

そこで、図4の定電圧源源回路において、動作開始時の出力電圧Voutの安定性及び過電流防止のために、下記の特許文献1に開示されているような負帰還回路を設ける対策が考えられる。

【0008】

更に、位相余裕をより確保するためには、下記の特許文献2に開示されているような負荷電流モニタ部を設ける対策が考えられる。

【0009】

図6は、特許文献2に記載された従来の他の定電圧電源回路を示す回路図である。

この定電圧電源回路では、図4の回路に、負荷電流モニタ部40が付加されている。負荷電流モニタ部40は、出力端子30の出力電流に比例したバイアス電流を誤差増幅部10へフィードバックすることで、高速応答と低消費電流を実現する回路であり、PMOS41及びNMOS42,43により構成されている。

【0010】

図7は、図6の定電圧電源回路において負荷電流が大きい場合の周波数特性を示す図である。

【0011】

図6に示す負荷電流モニタ部40を付加することにより、前述したように、出力部20のポールが誤差増幅部20のポールよりも低周波側にある場合、PMOS21に流れる負荷電流の増加に応じて誤差増幅部10のバイアス電流を増加させることができる。そのため、図7に示すように、誤差増幅部10のポールを負荷電流に応じて高周波側へ移動させることができる。

【0012】

従って、出力部20のポールと誤差増幅部10のポールが、共に負荷電流に応じて移動することにより、出力部20のポールと誤差増幅部10のポールの位置関係とを、全負荷電流範囲で十分な位相余裕を確保できるように設計すれば、負荷電流の大きさにより回路内部での消費電流を変化させることで、低消費電力化を図ることが可能になると共に安定に動作させることができる。

【0013】

【特許文献1】特開2007−233657号公報

【特許文献2】特開平3−158912号公報

【発明の開示】

【発明が解決しようとする課題】

【0014】

しかしながら、従来の図6の定電圧電源回路では、次のような課題があった。

図8は、図6の定電圧電源回路において負荷電流が小さい場合の周波数特性を示す図である。

【0015】

図6の負荷電流モニタ部40では、PMOS21に流れる負荷電流が小さい範囲において、PMOS21、及びこのPMOS21のゲート電圧をモニタするPMOS41のゲート・ソース間電圧Vgsの変化量が小さくなるため、負荷電流モニタ部40による誤差増幅部10のバイアス電流は、ほとんど増加しないことになる。

【0016】

このため、負荷電流が小さい時には、図8に示すように、出力部20の負荷電流増加に伴うポール移動量に対し、誤差増幅部10のポールがほとんど移動しないため、2つのポールが接近し位相余裕が低下する。この場合、PMOS41のゲート幅を大きくすることで、負荷電流に対する誤差増幅部10でのバイアス電流増加量を大きくし、誤差増幅部10のポール移動量を大きくすることは可能である。しかし、PMOS41のゲート幅を大きくすると、回路面積を大きくするだけでなく、負荷電流モニタ部40での消費電流が大きくなり、回路全体の消費電流が大きくなるため良策ではない。

【0017】

このように、負荷電流モニタ部40を付加した場合は、高速応答、且つ低消費電流という利点がある反面、負荷電流が小さい場合に位相余裕が低下する欠点の他に、起動時に出力電圧Voutのオーバシュート量が大きくなる虞れがあること、又、過負荷により出力電圧Voutがクランプすると、負荷電流モニタ部自体での電流消費が大きくなるという課題があった。

【課題を解決するための手段】

【0018】

本発明の定電圧電源回路は、バイアス電圧により流れるバイアス電流が供給され、基準電圧と出力端子から出力される出力電圧に対応する第1の電圧との差分を増幅する誤差増幅部と、前記出力端子と電源ノードとの間に接続され、前記誤差増幅部の出力により制御されて前記出力電圧を一定に制御する出力トランジスタと、前記出力トランジスタに流れる負荷電流をモニタし、前記負荷電流に応じて前記バイアス電流を増加させる負荷電流モニタ部と、前記負荷電流をモニタし、前記負荷電流に応じて前記誤差増幅部のゲインを低下させるゲイン調整部と、前記負荷電流モニタ回路内に設けられ、起動時あるいは過負荷時における前記負荷電流モニタ部の消費電流あるいは前記バイアス電流を制限する電流制限抵抗とを有することを特徴とする。

【発明の効果】

【0019】

本発明によれば、起動時や過負荷時にゲイン調整部をリミッタ回路として動作するようになるため、起動時や過負荷時に内部の消費電流を制限できる。しかも、起動時においては、このリミッタ動作により、起動時の応答を遅くすることとなるため、オーバシュートの発生を抑えることができる。

【発明を実施するための最良の形態】

【0020】

本発明を実施するための最良の形態は、以下の好ましい実施例の説明を添付図面と照らし合わせて読むと、明らかになるであろう。但し、図面はもっぱら解説のためのものであって、本発明の範囲を限定するものではない。

【実施例1】

【0021】

(実施例1の構成)

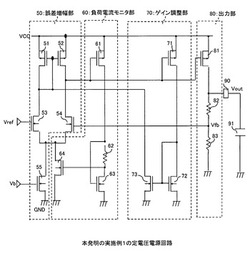

図1は、本発明の実施例1における定電圧電源回路を示す回路図である。

この定電圧電源回路は、例えば、半導体集積回路に搭載される回路であって、従来と同様の誤差増幅部50を有し、この誤差増幅部50の出力側に、従来とは異なる構成の負荷電流モニタ部60、新たに追加されたゲイン調整部70、及び従来と同様の出力部80が縦続接続され、更に、この出力部80の出力側に、出力電圧Voutを出力する出力端子90が接続されている。

【0022】

誤差増幅部50は、外部で発生するバイアス電圧Vbによりバイアス電流が流れ、外部で生成される基準電圧Vrefと出力電圧Voutに対応する第1の電圧(例えば、フィードバック電圧)Vfbとの差分を増幅する回路であり、負荷用のトランジスタ(例えば、PMOS)51,52と、第1及び第2の入力トランジスタ(例えば、NMOS)53,54と、バイアス電流を流す定電流源用の第1のトランジスタ(例えば、NMOS)55とにより構成されている。

【0023】

各PMOS51,52は、ソース端子(以下単に「ソース」という。)が電源電圧VCCノードに接続され、ゲート端子(以下単に「ゲート」という。)が相互に接続されている。各PMOS51,52のドレイン端子(以下単に「ドレイン」という。)には、各NMOS53,54のドレインがそれぞれ接続されている。NMOS53のゲートには、基準電圧Vrefが印加される。NMOS54のゲートには、出力電圧Voutに対応するフィードバック電圧Vfbが印加される。これらのNMOS53,54のソースは相互に接続され、この接続点にNMOS55のドレインが接続されている。NMOS55のソースはグランドGNDに接続され、このゲートに、外部で発生するバイアス電圧Vbが印加される。

【0024】

負荷電流モニタ部60は、出力部80に流れる負荷電流をモニタし、この負荷電流に応じて誤差増幅部50のバイアス電流を増加させる回路であり、負荷電流モニタ用の第3のトランジスタ(例えば、PMOS)61、電流制限用の抵抗62(例えば、シリコン基板上の層間絶縁膜内に埋め込まれた多結晶シリコンによる配線抵抗素子)、第4のトランジスタ(例えば、NMOS)63、及びバイアス電流調整用の第2のトランジスタ(例えば、NMOS)64により構成されている。

【0025】

PMOS61は、ソースが電源電圧VCCノードに接続され、ゲートがPMOS52のドレインに接続されている。PMOS61のドレインには、抵抗62を介してNMOS63のドレインが接続されると共に、NMOS63のゲートが接続され、このNMOS63のソースがグランドGNDに接続されている。NMOS63のソースには、NNOS64のゲートが接続され、このNMOS64のドレインがNMOS53,54のソースに共通に接続され、更に、NMOS64のソースがグランドGNDに接続されている。NMOS63及び64は、カレントミラー回路を構成している。

【0026】

ゲイン調整部70は、出力部80に流れる負荷電流をモニタし、この負荷電流に応じて誤差増幅部50のゲインを低下させる回路であり、負荷電流モニタ用のPMOS71と、NMOS72,73からなるカレントミラー回路とにより構成されている。

【0027】

PMOS71は、ソースが電源電圧VCCノードに接続され、ゲートがPMOS61のゲートに接続されている。PMOS71のドレインには、NMOS72のドレイン及びゲートとNMOS73のゲートとが接続され、これらのNMOS72,73のソースがグランドGNDに接続されている。NMOS73のドレインは、PMOS51のドレイン及びゲートとPMOS52のゲートとが接続されている。

【0028】

出力部80は、誤差増幅部50の出力電圧により制御されて出力電圧Voutを一定に制御する出力トランジスタ(例えば、負荷電流を流すPMOS)81と、出力電圧Voutを分圧してフィードバック電圧Vfbを生成する分圧抵抗82,83とにより構成されている。

【0029】

PMOS81は、ソースが電源電圧VCCノードに接続され、ゲートがPMOS52のドレイン及びPMOS61,71のゲートに接続されている。PMOS81のドレインには、分圧抵抗82,83及びグランドGNDが直列に接続されている。PMOS81及び分圧抵抗82の接続点には、出力端子90が接続されている。出力端子90には、例えば、安定化用のコンデンサ91が接続される。

【0030】

図2は、図1中のNMOS63箇所の回路図である。図3は、その図2の回路を有する定電圧電源回路において負荷電流が小さい場合の周波数特性を示す図である。

【0031】

本実施例1の定電圧電源回路は、図2に示すように、負荷電流モニタ部60におけるNMOS63箇所に抵抗62を持たない回路構成を基礎技術としている。そのため、先ず、抵抗62を持たない定電圧電源回路の動作1を、図3を参照しつつ説明した後、抵抗62を付加した図1の定電圧電源回路における動作2を説明する。

【0032】

(実施例1の動作1)

電源電圧VCC、基準電圧Vref、及びバイアス電圧Vbが印加されると、誤差増幅部50は、基準電圧Vrefと、出力電圧Voutを抵抗82,83で分圧したフィードバック電圧Vfbとの差分を増幅して、出力用PMOS81のゲート電圧を生成する。出力用PMOS81は、このゲート電圧により制御され、出力電圧Voutを一定に制御する。

【0033】

負荷電流モニタ部60のPMOS61は、出力用PMOS81に流れるドレイン電流をある比(例えば、1:1000等)でコピーし、NMOS63に供給する。NMOS63及び64は、カレントミラー回路を構成しており、NMOS63に供給された電流は、NMOS64にコピーされ、誤差増幅部50のバイアス電流となる。負荷電流モニタ部60は、出力用PMOS81のドレイン電流(負荷電流)が大きくなると、PMOS61によりコピーされ、NMOS63及び64のカレントミラー回路を介して誤差増幅部50のバイアス電流を増加させる。これにより、出力電圧Voutの応答を高速にすると共に、誤差増幅部50のポールを高周波側に移動させる。

【0034】

ゲイン調整部70は、負荷電流モニタ部60のPMOS61と同様に、PMOS71で出力用PMOS81のドレイン電流をコピーし、PMOS72に供給する。但し、PMOS61とPMOS71のゲート幅/ゲート長(W/L)比は、PMOS61をPMOS71より大きくし、PMOS81のドレイン電流に対し、(PMOS61のドレイン電流>PMOS71のドレイン電流)となるように設定しておく。

【0035】

PMOS72とNMOS73はカレントミラー回路を構成しており、PMOS72に供給された電流はコピーされ、モニタした電流分だけ誤差増幅部50のPMOS51のドレイン電流を吸い込む。

【0036】

誤差増幅部50において、基準電圧Vrefと、抵抗82,83によって出力電圧Voutを分圧したフィードバック電圧Vfbとが等しい状態であるとすると、誤差増幅部50の差動段を構成するNMOS53とNMOS54のドレイン電流は等しく、その電流は、NMOS55とNMOS64のドレイン電流の和の1/2になる。従来のようにゲイン調整部70がない場合は、NMOS53とPMOS51のドレイン電流、NMOS54とPMOS52のドレイン電流は等しくなり、バランスしている状態になる。本実施例1のようにゲイン調整部70を接続すると、PMOS51のドレイン電流は、NMOS53とNMOS73のドレイン電流の和になり、ゲイン調整部70がない場合に比べ、PMOS51のドレイン電流はNMOS73のドレイン電流分だけ増加する。これにより、誤差増幅部50の出力インピーダンスが低下し、図3に示すように、誤差増幅部50のゲインを低下させる共に、誤差増幅部50のポールを高周波側へ移動させる。

【0037】

従来のように、負荷電流モニタ部60のみで構成した場合には、負荷電流が小さい時に、誤差増幅部50のバイアス電流がほとんど増加しないため、出力部80のポールの移動量に対し、誤差増幅部50のポールが移動せず、ある負荷電流範囲で位相余裕が低下する問題があった。これに対し、本実施例1のように、ゲイン調整部70を付加することにより、誤差増幅部50のポールを高周波側へ移動させることにより、位相余裕の低下を防ぐことができる。

【0038】

一般に、誤差増幅部50のバイアス電流(NMOS55のドレイン電流)は、消費電流を抑えるためにできるだけ小さくする。負荷電流が小さい時には、負荷電流モニタ部60によるバイアス電流(NMOS64のドレイン電流)も小さいため、ゲイン調整部70のNMOS73による吸い込み電流は小さいが、誤差増幅部50のバイアス電流に対するNMOS73による吸い込み電流の割合が大きいため、負荷電流が小さい時には、ゲイン調整部70によるポール移動の効果が大きく現れる。

【0039】

一方、負荷電流が大きくなると、ゲイン調整部70によるNMOS73の吸い込み電流量が大きくなるが、負荷電流モニタ部60によるバイアス電流増加の割合が大きくなるため、負荷電流モニタ部60によるポール移動の効果が大きく現れる。

【0040】

本来の負荷電流モニタ部60の特徴であった、高速応答については、負荷電流が大きく変動した場合には、負荷電流モニタ部60による誤差増幅部50のバイアス電流増加が大きいため、図2の回路においてもその特徴はそのまま生かされる。又、ゲイン調整部70は、負荷電流モニタ部60と同様に、負荷電流に応じて吸い込み電流を調整する構成であるため、ゲイン調整部70を付加しても、内部での消費電流は十分に小さくできる。

【0041】

以上のように、図1の定電圧電源回路において、図2のように抵抗62を持たない回路構成によれば、ゲイン調整部70を付加することにより、本来、負荷電流モニタ部60が持っていた高速応答・低消費電流という特徴を残したまま、負荷電流が小さい時に安定性が劣化するという問題を改善できる。

【0042】

しかし、負荷電流モニタ部60は、高速応答、且つ低消費電流という利点がある反面、前述した負荷電流が小さい場合に位相余裕が低下する欠点の他に、起動時に出力電圧のオーバシュート量が大きくなる虞があること、又、過負荷等により出力電圧Voutがクランプすると、負荷電流モニタ部60自体での電流消費が大きくなるという問題が依然として残る。

【0043】

そこで、この点を改善するために、本実施例1では、図1に示すように、負荷電流モニタ部60に電流制限用の抵抗62を設けている。この動作2を以下説明する。

【0044】

(実施例1の動作2)

図1の定電圧電源回路において、起動時や過負荷時には出力用PMOS81に大きな電流が流れるため、PMOS81のドレイン電流をコピーする負荷電流モニタ部60のPMOS61のドレイン電流も大きくなる。しかし、抵抗62が挿入されているので、PMOS61のドレイン電流がある電流値以上になった時に、抵抗62の電圧降下により、NMOS63のソース・ドレイン間電圧が低くなる。これに伴い、NMOS64のゲート電圧が低くなるため、ドレイン電流が減少し、誤差増幅部50のバイアス電流が減少する。

【0045】

一方、ゲイン調整部70では、起動時や過負荷時には、PMOS71,72のドレイン電流が大きくなり、NMOS73による吸い込み電流が大きくなる。負荷電流モニタ部60によるバイアス電流が低下し、ゲイン調整部70の吸い込み電流が増加すると、ゲイン調整部70のみが機能することとなり、ゲイン調整部70による負帰還により出力用PMOS81のゲート電圧はある一定レベルに固定される。これは、ゲイン調整部70がリミッタとして動作していることを意味しており、この状態になると、PMOS81による出力電流が制限されるだけでなく、ゲイン調整部70での消費電流も制限されることになり、起動時・過負荷時に消費する電流を制限できることになる。

【0046】

(実施例1の効果)

本実施例1によれば、図1に示す回路構成とすることにより、起動時や過負荷時にゲイン調整部70をリミッタ回路として動作するようになるため、起動時や過負荷時に内部の消費電流を制限できる。しかも、起動時においては、このリミッタ動作により、起動時の応答を遅くすることとなるため、オーバシュートの発生を抑制できる。

【0047】

(変形例)

本発明は、上記実施例1に限定されず、種々の利用形態や変形が可能である。この利用形態や変形例としては、例えば、次の(a)〜(c)のようなものがある。

【0048】

(a) 実施例1では、NMOSトランジスタによる差動段をもつ誤差増幅部50を使用しているが、いかなる構成の誤差増幅部50であっても、誤差増幅部50及び出力トランジスタ(PMOS81)という回路構成であれば適用可能である。

【0049】

(b) 負荷電流モニタ部60の抵抗62の挿入場所は、過負荷状態における負荷電流モニタ部60の消費電流、あるいは誤差増幅部50のバイアス電流を制限するものであれば、図1の回路図以外の場所でも可能である。

【0050】

(c) 抵抗62の代わりに、MOSトランジスタ等を抵抗として使用することも可能である。

【図面の簡単な説明】

【0051】

【図1】本発明の実施例1における定電圧電源回路を示す回路図である。

【図2】図1中のNMOS63箇所の回路図である。

【図3】図2の回路を有する定電圧電源回路において負荷電流が小さい場合の周波数特性を示す図である。

【図4】従来の定電圧電源回路を示す回路図である。

【図5】図4の定電圧電源回路における周波数特性を示す図である。

【図6】従来の他の定電圧電源回路を示す回路図である。

【図7】図6の定電圧電源回路において負荷電流が大きい場合の周波数特性を示す図である。

【図8】図6の定電圧電源回路において負荷電流が小さい場合の周波数特性を示す図である。

【符号の説明】

【0052】

50 誤差増幅部

60 負荷電流モニタ部

62 抵抗

70 ゲイン調整部

80 出力部

【技術分野】

【0001】

本発明は、半導体集積回路等に搭載される定電圧電源回路に関するものである。

【背景技術】

【0002】

図4は、従来の定電圧電源回路を示す回路図である。

この定電圧電源回路は、基準電圧Vrefと出力端子30から出力される出力電圧Voutに比例した電圧Vfbとの差分を増幅する誤差増幅部10と、この誤差増幅部10の出力側に接続され、誤差増幅部10の出力により制御されて出力端子30から出力する出力電圧Voutを一定に制御する出力部20とにより構成されている。

【0003】

誤差増幅部10は、電源電圧VCCノードに接続された負荷用のPチャネルMOSトランジスタ(以下「PMOS」という。)11,12と、このPMOS11,12に直列に接続され、基準電圧Vref及び電圧Vfbをそれぞれ入力して差動増幅する入力トランジスタであるNチャネルMOSトランジスタ(以下」「NMOS」という。)13,14と、このNMOS13,14とグランドGNDとの間に接続され、バイアス電圧Vbにより一定電流を流す定電流源用のNMOS15とを有する差動増幅器により構成されている。出力部20は、出力トランジスタであるPMOS21と分圧抵抗22,23とを有し、これらが電源電圧VCCノードとグランドGNDとの間に直列に接続されている。PMOS21と分圧抵抗22との接続点には、出力電圧Voutを出力する出力端子30が接続されている。

【0004】

一般には、急峻な負荷電流変動に対して出力電圧変動を抑制するために、容量値(例えば、数μF程度)のコンデンサ31を外部に接続して使用される。

【0005】

図5は、図4の定電圧電源回路における周波数特性を示す図である。

外部にコンデンサ31が接続された図4の回路構成の場合、定電圧電源回路の誤差増幅部10と出力部20の周波数特性は、図5に示すように、誤差増幅部10のポールよりも出力部20のポールが低周波域に存在する場合がある。2つのポールが存在する場合は、2つのポールが近い周波数域に存在すると、位相余裕がとれず、出力電圧Voutの発振を生じるおそれがあるため、十分に2つのポールを分離する必要がある。

【0006】

図5に示すように、出力部20のポールが低周波域にある場合には、出力部20のポールは、PMOS21を流れる負荷電流の大きさにより高周波側へ移動するため、このようなポール位置関係を持つ定電圧電源回路を安定動作させるには、負荷電流変動により出力部20のポールが変化しても位相余裕が十分とれるように、誤差増幅部10のポールを十分に高周波側に配置する必要があるが、そのためには誤差増幅部10のバイアス電流を大きくする等の対策が必要となる。しかし、大きな負荷電流駆動能力を必要とする用途では、出力部20のポールの高周波側への移動範囲が広がるため、誤差増幅部10のバイアス電流を大きくする対策だけでは、過大な電流を消費することとなり、おのずと限界がある。

【0007】

そこで、図4の定電圧源源回路において、動作開始時の出力電圧Voutの安定性及び過電流防止のために、下記の特許文献1に開示されているような負帰還回路を設ける対策が考えられる。

【0008】

更に、位相余裕をより確保するためには、下記の特許文献2に開示されているような負荷電流モニタ部を設ける対策が考えられる。

【0009】

図6は、特許文献2に記載された従来の他の定電圧電源回路を示す回路図である。

この定電圧電源回路では、図4の回路に、負荷電流モニタ部40が付加されている。負荷電流モニタ部40は、出力端子30の出力電流に比例したバイアス電流を誤差増幅部10へフィードバックすることで、高速応答と低消費電流を実現する回路であり、PMOS41及びNMOS42,43により構成されている。

【0010】

図7は、図6の定電圧電源回路において負荷電流が大きい場合の周波数特性を示す図である。

【0011】

図6に示す負荷電流モニタ部40を付加することにより、前述したように、出力部20のポールが誤差増幅部20のポールよりも低周波側にある場合、PMOS21に流れる負荷電流の増加に応じて誤差増幅部10のバイアス電流を増加させることができる。そのため、図7に示すように、誤差増幅部10のポールを負荷電流に応じて高周波側へ移動させることができる。

【0012】

従って、出力部20のポールと誤差増幅部10のポールが、共に負荷電流に応じて移動することにより、出力部20のポールと誤差増幅部10のポールの位置関係とを、全負荷電流範囲で十分な位相余裕を確保できるように設計すれば、負荷電流の大きさにより回路内部での消費電流を変化させることで、低消費電力化を図ることが可能になると共に安定に動作させることができる。

【0013】

【特許文献1】特開2007−233657号公報

【特許文献2】特開平3−158912号公報

【発明の開示】

【発明が解決しようとする課題】

【0014】

しかしながら、従来の図6の定電圧電源回路では、次のような課題があった。

図8は、図6の定電圧電源回路において負荷電流が小さい場合の周波数特性を示す図である。

【0015】

図6の負荷電流モニタ部40では、PMOS21に流れる負荷電流が小さい範囲において、PMOS21、及びこのPMOS21のゲート電圧をモニタするPMOS41のゲート・ソース間電圧Vgsの変化量が小さくなるため、負荷電流モニタ部40による誤差増幅部10のバイアス電流は、ほとんど増加しないことになる。

【0016】

このため、負荷電流が小さい時には、図8に示すように、出力部20の負荷電流増加に伴うポール移動量に対し、誤差増幅部10のポールがほとんど移動しないため、2つのポールが接近し位相余裕が低下する。この場合、PMOS41のゲート幅を大きくすることで、負荷電流に対する誤差増幅部10でのバイアス電流増加量を大きくし、誤差増幅部10のポール移動量を大きくすることは可能である。しかし、PMOS41のゲート幅を大きくすると、回路面積を大きくするだけでなく、負荷電流モニタ部40での消費電流が大きくなり、回路全体の消費電流が大きくなるため良策ではない。

【0017】

このように、負荷電流モニタ部40を付加した場合は、高速応答、且つ低消費電流という利点がある反面、負荷電流が小さい場合に位相余裕が低下する欠点の他に、起動時に出力電圧Voutのオーバシュート量が大きくなる虞れがあること、又、過負荷により出力電圧Voutがクランプすると、負荷電流モニタ部自体での電流消費が大きくなるという課題があった。

【課題を解決するための手段】

【0018】

本発明の定電圧電源回路は、バイアス電圧により流れるバイアス電流が供給され、基準電圧と出力端子から出力される出力電圧に対応する第1の電圧との差分を増幅する誤差増幅部と、前記出力端子と電源ノードとの間に接続され、前記誤差増幅部の出力により制御されて前記出力電圧を一定に制御する出力トランジスタと、前記出力トランジスタに流れる負荷電流をモニタし、前記負荷電流に応じて前記バイアス電流を増加させる負荷電流モニタ部と、前記負荷電流をモニタし、前記負荷電流に応じて前記誤差増幅部のゲインを低下させるゲイン調整部と、前記負荷電流モニタ回路内に設けられ、起動時あるいは過負荷時における前記負荷電流モニタ部の消費電流あるいは前記バイアス電流を制限する電流制限抵抗とを有することを特徴とする。

【発明の効果】

【0019】

本発明によれば、起動時や過負荷時にゲイン調整部をリミッタ回路として動作するようになるため、起動時や過負荷時に内部の消費電流を制限できる。しかも、起動時においては、このリミッタ動作により、起動時の応答を遅くすることとなるため、オーバシュートの発生を抑えることができる。

【発明を実施するための最良の形態】

【0020】

本発明を実施するための最良の形態は、以下の好ましい実施例の説明を添付図面と照らし合わせて読むと、明らかになるであろう。但し、図面はもっぱら解説のためのものであって、本発明の範囲を限定するものではない。

【実施例1】

【0021】

(実施例1の構成)

図1は、本発明の実施例1における定電圧電源回路を示す回路図である。

この定電圧電源回路は、例えば、半導体集積回路に搭載される回路であって、従来と同様の誤差増幅部50を有し、この誤差増幅部50の出力側に、従来とは異なる構成の負荷電流モニタ部60、新たに追加されたゲイン調整部70、及び従来と同様の出力部80が縦続接続され、更に、この出力部80の出力側に、出力電圧Voutを出力する出力端子90が接続されている。

【0022】

誤差増幅部50は、外部で発生するバイアス電圧Vbによりバイアス電流が流れ、外部で生成される基準電圧Vrefと出力電圧Voutに対応する第1の電圧(例えば、フィードバック電圧)Vfbとの差分を増幅する回路であり、負荷用のトランジスタ(例えば、PMOS)51,52と、第1及び第2の入力トランジスタ(例えば、NMOS)53,54と、バイアス電流を流す定電流源用の第1のトランジスタ(例えば、NMOS)55とにより構成されている。

【0023】

各PMOS51,52は、ソース端子(以下単に「ソース」という。)が電源電圧VCCノードに接続され、ゲート端子(以下単に「ゲート」という。)が相互に接続されている。各PMOS51,52のドレイン端子(以下単に「ドレイン」という。)には、各NMOS53,54のドレインがそれぞれ接続されている。NMOS53のゲートには、基準電圧Vrefが印加される。NMOS54のゲートには、出力電圧Voutに対応するフィードバック電圧Vfbが印加される。これらのNMOS53,54のソースは相互に接続され、この接続点にNMOS55のドレインが接続されている。NMOS55のソースはグランドGNDに接続され、このゲートに、外部で発生するバイアス電圧Vbが印加される。

【0024】

負荷電流モニタ部60は、出力部80に流れる負荷電流をモニタし、この負荷電流に応じて誤差増幅部50のバイアス電流を増加させる回路であり、負荷電流モニタ用の第3のトランジスタ(例えば、PMOS)61、電流制限用の抵抗62(例えば、シリコン基板上の層間絶縁膜内に埋め込まれた多結晶シリコンによる配線抵抗素子)、第4のトランジスタ(例えば、NMOS)63、及びバイアス電流調整用の第2のトランジスタ(例えば、NMOS)64により構成されている。

【0025】

PMOS61は、ソースが電源電圧VCCノードに接続され、ゲートがPMOS52のドレインに接続されている。PMOS61のドレインには、抵抗62を介してNMOS63のドレインが接続されると共に、NMOS63のゲートが接続され、このNMOS63のソースがグランドGNDに接続されている。NMOS63のソースには、NNOS64のゲートが接続され、このNMOS64のドレインがNMOS53,54のソースに共通に接続され、更に、NMOS64のソースがグランドGNDに接続されている。NMOS63及び64は、カレントミラー回路を構成している。

【0026】

ゲイン調整部70は、出力部80に流れる負荷電流をモニタし、この負荷電流に応じて誤差増幅部50のゲインを低下させる回路であり、負荷電流モニタ用のPMOS71と、NMOS72,73からなるカレントミラー回路とにより構成されている。

【0027】

PMOS71は、ソースが電源電圧VCCノードに接続され、ゲートがPMOS61のゲートに接続されている。PMOS71のドレインには、NMOS72のドレイン及びゲートとNMOS73のゲートとが接続され、これらのNMOS72,73のソースがグランドGNDに接続されている。NMOS73のドレインは、PMOS51のドレイン及びゲートとPMOS52のゲートとが接続されている。

【0028】

出力部80は、誤差増幅部50の出力電圧により制御されて出力電圧Voutを一定に制御する出力トランジスタ(例えば、負荷電流を流すPMOS)81と、出力電圧Voutを分圧してフィードバック電圧Vfbを生成する分圧抵抗82,83とにより構成されている。

【0029】

PMOS81は、ソースが電源電圧VCCノードに接続され、ゲートがPMOS52のドレイン及びPMOS61,71のゲートに接続されている。PMOS81のドレインには、分圧抵抗82,83及びグランドGNDが直列に接続されている。PMOS81及び分圧抵抗82の接続点には、出力端子90が接続されている。出力端子90には、例えば、安定化用のコンデンサ91が接続される。

【0030】

図2は、図1中のNMOS63箇所の回路図である。図3は、その図2の回路を有する定電圧電源回路において負荷電流が小さい場合の周波数特性を示す図である。

【0031】

本実施例1の定電圧電源回路は、図2に示すように、負荷電流モニタ部60におけるNMOS63箇所に抵抗62を持たない回路構成を基礎技術としている。そのため、先ず、抵抗62を持たない定電圧電源回路の動作1を、図3を参照しつつ説明した後、抵抗62を付加した図1の定電圧電源回路における動作2を説明する。

【0032】

(実施例1の動作1)

電源電圧VCC、基準電圧Vref、及びバイアス電圧Vbが印加されると、誤差増幅部50は、基準電圧Vrefと、出力電圧Voutを抵抗82,83で分圧したフィードバック電圧Vfbとの差分を増幅して、出力用PMOS81のゲート電圧を生成する。出力用PMOS81は、このゲート電圧により制御され、出力電圧Voutを一定に制御する。

【0033】

負荷電流モニタ部60のPMOS61は、出力用PMOS81に流れるドレイン電流をある比(例えば、1:1000等)でコピーし、NMOS63に供給する。NMOS63及び64は、カレントミラー回路を構成しており、NMOS63に供給された電流は、NMOS64にコピーされ、誤差増幅部50のバイアス電流となる。負荷電流モニタ部60は、出力用PMOS81のドレイン電流(負荷電流)が大きくなると、PMOS61によりコピーされ、NMOS63及び64のカレントミラー回路を介して誤差増幅部50のバイアス電流を増加させる。これにより、出力電圧Voutの応答を高速にすると共に、誤差増幅部50のポールを高周波側に移動させる。

【0034】

ゲイン調整部70は、負荷電流モニタ部60のPMOS61と同様に、PMOS71で出力用PMOS81のドレイン電流をコピーし、PMOS72に供給する。但し、PMOS61とPMOS71のゲート幅/ゲート長(W/L)比は、PMOS61をPMOS71より大きくし、PMOS81のドレイン電流に対し、(PMOS61のドレイン電流>PMOS71のドレイン電流)となるように設定しておく。

【0035】

PMOS72とNMOS73はカレントミラー回路を構成しており、PMOS72に供給された電流はコピーされ、モニタした電流分だけ誤差増幅部50のPMOS51のドレイン電流を吸い込む。

【0036】

誤差増幅部50において、基準電圧Vrefと、抵抗82,83によって出力電圧Voutを分圧したフィードバック電圧Vfbとが等しい状態であるとすると、誤差増幅部50の差動段を構成するNMOS53とNMOS54のドレイン電流は等しく、その電流は、NMOS55とNMOS64のドレイン電流の和の1/2になる。従来のようにゲイン調整部70がない場合は、NMOS53とPMOS51のドレイン電流、NMOS54とPMOS52のドレイン電流は等しくなり、バランスしている状態になる。本実施例1のようにゲイン調整部70を接続すると、PMOS51のドレイン電流は、NMOS53とNMOS73のドレイン電流の和になり、ゲイン調整部70がない場合に比べ、PMOS51のドレイン電流はNMOS73のドレイン電流分だけ増加する。これにより、誤差増幅部50の出力インピーダンスが低下し、図3に示すように、誤差増幅部50のゲインを低下させる共に、誤差増幅部50のポールを高周波側へ移動させる。

【0037】

従来のように、負荷電流モニタ部60のみで構成した場合には、負荷電流が小さい時に、誤差増幅部50のバイアス電流がほとんど増加しないため、出力部80のポールの移動量に対し、誤差増幅部50のポールが移動せず、ある負荷電流範囲で位相余裕が低下する問題があった。これに対し、本実施例1のように、ゲイン調整部70を付加することにより、誤差増幅部50のポールを高周波側へ移動させることにより、位相余裕の低下を防ぐことができる。

【0038】

一般に、誤差増幅部50のバイアス電流(NMOS55のドレイン電流)は、消費電流を抑えるためにできるだけ小さくする。負荷電流が小さい時には、負荷電流モニタ部60によるバイアス電流(NMOS64のドレイン電流)も小さいため、ゲイン調整部70のNMOS73による吸い込み電流は小さいが、誤差増幅部50のバイアス電流に対するNMOS73による吸い込み電流の割合が大きいため、負荷電流が小さい時には、ゲイン調整部70によるポール移動の効果が大きく現れる。

【0039】

一方、負荷電流が大きくなると、ゲイン調整部70によるNMOS73の吸い込み電流量が大きくなるが、負荷電流モニタ部60によるバイアス電流増加の割合が大きくなるため、負荷電流モニタ部60によるポール移動の効果が大きく現れる。

【0040】

本来の負荷電流モニタ部60の特徴であった、高速応答については、負荷電流が大きく変動した場合には、負荷電流モニタ部60による誤差増幅部50のバイアス電流増加が大きいため、図2の回路においてもその特徴はそのまま生かされる。又、ゲイン調整部70は、負荷電流モニタ部60と同様に、負荷電流に応じて吸い込み電流を調整する構成であるため、ゲイン調整部70を付加しても、内部での消費電流は十分に小さくできる。

【0041】

以上のように、図1の定電圧電源回路において、図2のように抵抗62を持たない回路構成によれば、ゲイン調整部70を付加することにより、本来、負荷電流モニタ部60が持っていた高速応答・低消費電流という特徴を残したまま、負荷電流が小さい時に安定性が劣化するという問題を改善できる。

【0042】

しかし、負荷電流モニタ部60は、高速応答、且つ低消費電流という利点がある反面、前述した負荷電流が小さい場合に位相余裕が低下する欠点の他に、起動時に出力電圧のオーバシュート量が大きくなる虞があること、又、過負荷等により出力電圧Voutがクランプすると、負荷電流モニタ部60自体での電流消費が大きくなるという問題が依然として残る。

【0043】

そこで、この点を改善するために、本実施例1では、図1に示すように、負荷電流モニタ部60に電流制限用の抵抗62を設けている。この動作2を以下説明する。

【0044】

(実施例1の動作2)

図1の定電圧電源回路において、起動時や過負荷時には出力用PMOS81に大きな電流が流れるため、PMOS81のドレイン電流をコピーする負荷電流モニタ部60のPMOS61のドレイン電流も大きくなる。しかし、抵抗62が挿入されているので、PMOS61のドレイン電流がある電流値以上になった時に、抵抗62の電圧降下により、NMOS63のソース・ドレイン間電圧が低くなる。これに伴い、NMOS64のゲート電圧が低くなるため、ドレイン電流が減少し、誤差増幅部50のバイアス電流が減少する。

【0045】

一方、ゲイン調整部70では、起動時や過負荷時には、PMOS71,72のドレイン電流が大きくなり、NMOS73による吸い込み電流が大きくなる。負荷電流モニタ部60によるバイアス電流が低下し、ゲイン調整部70の吸い込み電流が増加すると、ゲイン調整部70のみが機能することとなり、ゲイン調整部70による負帰還により出力用PMOS81のゲート電圧はある一定レベルに固定される。これは、ゲイン調整部70がリミッタとして動作していることを意味しており、この状態になると、PMOS81による出力電流が制限されるだけでなく、ゲイン調整部70での消費電流も制限されることになり、起動時・過負荷時に消費する電流を制限できることになる。

【0046】

(実施例1の効果)

本実施例1によれば、図1に示す回路構成とすることにより、起動時や過負荷時にゲイン調整部70をリミッタ回路として動作するようになるため、起動時や過負荷時に内部の消費電流を制限できる。しかも、起動時においては、このリミッタ動作により、起動時の応答を遅くすることとなるため、オーバシュートの発生を抑制できる。

【0047】

(変形例)

本発明は、上記実施例1に限定されず、種々の利用形態や変形が可能である。この利用形態や変形例としては、例えば、次の(a)〜(c)のようなものがある。

【0048】

(a) 実施例1では、NMOSトランジスタによる差動段をもつ誤差増幅部50を使用しているが、いかなる構成の誤差増幅部50であっても、誤差増幅部50及び出力トランジスタ(PMOS81)という回路構成であれば適用可能である。

【0049】

(b) 負荷電流モニタ部60の抵抗62の挿入場所は、過負荷状態における負荷電流モニタ部60の消費電流、あるいは誤差増幅部50のバイアス電流を制限するものであれば、図1の回路図以外の場所でも可能である。

【0050】

(c) 抵抗62の代わりに、MOSトランジスタ等を抵抗として使用することも可能である。

【図面の簡単な説明】

【0051】

【図1】本発明の実施例1における定電圧電源回路を示す回路図である。

【図2】図1中のNMOS63箇所の回路図である。

【図3】図2の回路を有する定電圧電源回路において負荷電流が小さい場合の周波数特性を示す図である。

【図4】従来の定電圧電源回路を示す回路図である。

【図5】図4の定電圧電源回路における周波数特性を示す図である。

【図6】従来の他の定電圧電源回路を示す回路図である。

【図7】図6の定電圧電源回路において負荷電流が大きい場合の周波数特性を示す図である。

【図8】図6の定電圧電源回路において負荷電流が小さい場合の周波数特性を示す図である。

【符号の説明】

【0052】

50 誤差増幅部

60 負荷電流モニタ部

62 抵抗

70 ゲイン調整部

80 出力部

【特許請求の範囲】

【請求項1】

バイアス電圧によりバイアス電流が流れ、基準電圧と出力端子から出力される出力電圧に対応する第1の電圧との差分を増幅する誤差増幅部と、

前記出力端子と電源ノードとの間に接続され、前記誤差増幅部の出力により制御されて前記出力電圧を一定に制御する出力トランジスタと、

前記出力トランジスタに流れる負荷電流をモニタし、前記負荷電流に応じて前記バイアス電流を増加させる負荷電流モニタ部と、

前記負荷電流をモニタし、前記負荷電流に応じて前記誤差増幅部のゲインを低下させるゲイン調整部と、

前記負荷電流モニタ部内に設けられ、起動時あるいは過負荷時における前記負荷電流モニタ部の消費電流あるいは前記バイアス電流を制限する電流制限抵抗と、

を有することを特徴とする定電圧電源回路。

【請求項2】

前記誤差増幅部は、

前記基準電圧及び前記第1の電圧をそれぞれ入力して差動増幅する第1及び第2の入力トランジスタと、

前記バイアス電圧に基づき、前記第1及び第2の入力トランジスタに前記バイアス電流を流す定電流源用の第1のトランジスタと、

を有する差動増幅器により構成されていることを特徴とする請求項1記載の定電圧電源回路。

【請求項3】

前記負荷電流モニタ部は、

前記第1のトランジスタに対して並列に接続されたバイアス電流調整用の第2のトランジスタと、

前記出力トランジスタと共にカレントミラー回路を構成して前記負荷電流をモニタする第3のトランジスタと、

前記第3のトランジスタに対して直列に接続され、前記第2のトランジスタと共にカレントミラー回路を構成して、前記第3のトランジスタに流れる電流に対応した電流を、前記第2のトランジスタに流す第4のトランジスタと、

前記第4のトランジスタに対して直列に接続された前記電流制限抵抗と、

を有することを特徴とする請求項2記載の定電圧電源回路。

【請求項4】

前記第1の電圧は、前記出力電圧を抵抗で分圧して生成されることを特徴とする請求項1〜3のいずれか1項に記載の定電圧電源回路。

【請求項5】

前記出力端子には、安定化用コンデンサが接続されることを特徴とする請求項1〜4のいずれか1項に記載の定電圧電源回路。

【請求項6】

前記定電圧電源回路は、半導体集積回路に搭載されていることを特徴とする請求項1〜5のいずれか1項に記載の定電圧電源回路。

【請求項1】

バイアス電圧によりバイアス電流が流れ、基準電圧と出力端子から出力される出力電圧に対応する第1の電圧との差分を増幅する誤差増幅部と、

前記出力端子と電源ノードとの間に接続され、前記誤差増幅部の出力により制御されて前記出力電圧を一定に制御する出力トランジスタと、

前記出力トランジスタに流れる負荷電流をモニタし、前記負荷電流に応じて前記バイアス電流を増加させる負荷電流モニタ部と、

前記負荷電流をモニタし、前記負荷電流に応じて前記誤差増幅部のゲインを低下させるゲイン調整部と、

前記負荷電流モニタ部内に設けられ、起動時あるいは過負荷時における前記負荷電流モニタ部の消費電流あるいは前記バイアス電流を制限する電流制限抵抗と、

を有することを特徴とする定電圧電源回路。

【請求項2】

前記誤差増幅部は、

前記基準電圧及び前記第1の電圧をそれぞれ入力して差動増幅する第1及び第2の入力トランジスタと、

前記バイアス電圧に基づき、前記第1及び第2の入力トランジスタに前記バイアス電流を流す定電流源用の第1のトランジスタと、

を有する差動増幅器により構成されていることを特徴とする請求項1記載の定電圧電源回路。

【請求項3】

前記負荷電流モニタ部は、

前記第1のトランジスタに対して並列に接続されたバイアス電流調整用の第2のトランジスタと、

前記出力トランジスタと共にカレントミラー回路を構成して前記負荷電流をモニタする第3のトランジスタと、

前記第3のトランジスタに対して直列に接続され、前記第2のトランジスタと共にカレントミラー回路を構成して、前記第3のトランジスタに流れる電流に対応した電流を、前記第2のトランジスタに流す第4のトランジスタと、

前記第4のトランジスタに対して直列に接続された前記電流制限抵抗と、

を有することを特徴とする請求項2記載の定電圧電源回路。

【請求項4】

前記第1の電圧は、前記出力電圧を抵抗で分圧して生成されることを特徴とする請求項1〜3のいずれか1項に記載の定電圧電源回路。

【請求項5】

前記出力端子には、安定化用コンデンサが接続されることを特徴とする請求項1〜4のいずれか1項に記載の定電圧電源回路。

【請求項6】

前記定電圧電源回路は、半導体集積回路に搭載されていることを特徴とする請求項1〜5のいずれか1項に記載の定電圧電源回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2010−79653(P2010−79653A)

【公開日】平成22年4月8日(2010.4.8)

【国際特許分類】

【出願番号】特願2008−248062(P2008−248062)

【出願日】平成20年9月26日(2008.9.26)

【出願人】(308033711)OKIセミコンダクタ株式会社 (898)

【出願人】(591049893)株式会社 沖マイクロデザイン (127)

【Fターム(参考)】

【公開日】平成22年4月8日(2010.4.8)

【国際特許分類】

【出願日】平成20年9月26日(2008.9.26)

【出願人】(308033711)OKIセミコンダクタ株式会社 (898)

【出願人】(591049893)株式会社 沖マイクロデザイン (127)

【Fターム(参考)】

[ Back to top ]