定電流回路

【課題】出力する定電流の温度特性の傾きを広範囲に設定する。

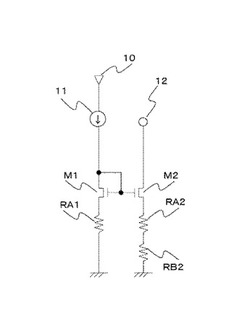

【解決手段】電流源11と、電流源11をドレインに接続する、ダイオード接続されるNchMOSトランジスタM1と、NchMOSトランジスタM1のソースと接地間に接続される第1の温度係数を持つ抵抗素子RA1と、ゲートをNchMOSトランジスタM1のゲートに接続するNchMOSトランジスタM2と、NchMOSトランジスタM2のソースと接地間に接続される第1の温度係数を持つ抵抗素子RA2および第2の温度係数を持つ抵抗素子RB2と、を備え、NchMOSトランジスタM2のドレインを出力端子12とする。

【解決手段】電流源11と、電流源11をドレインに接続する、ダイオード接続されるNchMOSトランジスタM1と、NchMOSトランジスタM1のソースと接地間に接続される第1の温度係数を持つ抵抗素子RA1と、ゲートをNchMOSトランジスタM1のゲートに接続するNchMOSトランジスタM2と、NchMOSトランジスタM2のソースと接地間に接続される第1の温度係数を持つ抵抗素子RA2および第2の温度係数を持つ抵抗素子RB2と、を備え、NchMOSトランジスタM2のドレインを出力端子12とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、定電流回路に関し、特に、出力電流の温度特性の制御技術に関する。

【背景技術】

【0002】

定電流回路は、集積回路などで広く用いられる。このような定電流回路は、出力電流に温度依存性が少ないことが求められ、温度係数の異なる抵抗素子を組み合わせることで構成されている。例えば、特許文献1に記載の定電流回路は、一定の電圧を抵抗体に印加して抵抗体に流れる電流を出力とする定電流回路であって、抵抗体を正の温度係数を持つ抵抗体と負の温度係数を持つ抵抗体とを直列接続して温度係数がキャンセルされるように構成されている。

【0003】

また、特許文献2には、抵抗の温度係数の大小、あるいはその正負にかかわらず、確実に平坦な温度特性を実現する定電流源回路が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平2−66613号公報

【特許文献2】特開2005−316530号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

以下の分析は本発明において与えられる。

【0006】

従来例の目的は、定電流出力の温度特性をキャンセルすることにあった。ところで、温度センサーなどの回路によっては、温度特性の傾きがより大きい方が都合の良い場合がある。しかしながら、従来例の定電流回路は、出力電流において平坦な温度特性を実現することを目的として構成されるので、このままでは、出力する定電流の温度特性の傾きを広範囲に設定することができず、温度センサーなどの回路に適用することができない。

【課題を解決するための手段】

【0007】

本発明の1つのアスペクト(側面)に係る定電流回路は、電流源と、電流源をドレインに接続する、ダイオード接続される第1の第1導電型トランジスタと、第1の第1導電型トランジスタのソースと接地間に接続される第1の温度係数を持つ第1の抵抗素子と、ゲートを第1の第1導電型トランジスタのゲートに接続する第2の第1導電型トランジスタと、第2の第1導電型トランジスタのソースと接地間に接続される第2の温度係数を持つ第2の抵抗素子と、を備え、第2の第1導電型トランジスタのドレインを電流出力端とする。

【発明の効果】

【0008】

本発明によれば、異なる温度係数をもつ抵抗素子によって、出力する定電流の温度特性の傾きを広範囲に設定することができる。

【図面の簡単な説明】

【0009】

【図1】本発明の第1の実施例に係る定電流回路の回路図である。

【図2】定電流回路の各抵抗素子の値を変更した場合の出力電流の温度特性を示す図である。

【図3】本発明の第2の実施例に係る定電流回路の回路図である。

【図4】本発明の第3の実施例に係る定電流回路の回路図である。

【発明を実施するための形態】

【0010】

本発明の実施形態に係る定電流回路は、電流源(図1の11)と、電流源をドレインに接続する、ダイオード接続される第1の第1導電型トランジスタ(図1のM1)と、第1の第1導電型トランジスタのソースと接地間に接続される第1の温度係数を持つ第1の抵抗素子(図1のRA1)と、ゲートを第1の第1導電型トランジスタのゲートに接続する第2の第1導電型トランジスタ(図1のM2)と、第2の第1導電型トランジスタのソースと接地間に接続される第2の温度係数を持つ第2の抵抗素子(図1のRB2)と、を備え、第2の第1導電型トランジスタのドレインを電流出力端(図1の12)とする。

【0011】

定電流回路において、第2の第1導電型トランジスタのソースと接地間に、第2の抵抗素子と直列に第1の温度係数を持つ第3の抵抗素子(図1のRA2)をさらに備えるようにしてもよい。

【0012】

定電流回路において、第1の第1導電型トランジスタのソースと接地間に、第1の抵抗素子と直列に第2の温度係数を持つ第4の抵抗素子(図4のRB1)をさらに備えるようにしてもよい。

【0013】

定電流回路において、第1および第2の抵抗素子は、可変抵抗素子(図4のRA5、RB5)であってもよい。

【0014】

定電流回路において、第2の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を並列または直列形態で接続するようにしてもよい。

【0015】

定電流回路において、第1の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を並列または直列形態で接続するようにしてもよい。

【0016】

定電流回路において、第2の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を直並列組み合わせた形態で接続するようにしてもよい。

【0017】

定電流回路において、第1の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を直並列組み合わせた形態で接続するようにしてもよい。

【0018】

定電流回路において、電流出力端にドレインを接続する、ダイオード接続される第1の第2導電型トランジスタ(図3のM3)と、第1の第2導電型トランジスタのソースと電源間に接続される第1の温度係数を持つ第5の抵抗素子(図3のRA3)と、ゲートを第1の第2導電型トランジスタのゲートに接続する第2の第2導電型トランジスタ(図3のM4)と、第2の第2導電型トランジスタのソースと電源間に接続される第2の温度係数を持つ第6の抵抗素子(図3のRB4)と、をさらに備え、第2の第2導電型トランジスタのドレインを他の電流出力端(図3の12)としてもよい。

【0019】

以上のような半導体装置によれば、抵抗素子の温度係数がそれぞれ異なるようにすることで、入力電流の温度特性と出力電流の温度特性に違いにより、正か負のいずれか一方しか持たない半導体プロセスにおいても正負任意の傾きを持つ温度特性の出力電流設定が可能となる。

【0020】

以下、実施例に即し、図面を参照して詳しく説明する。

【実施例1】

【0021】

図1は、本発明の第1の実施例に係る定電流回路の回路図である。図1において、定電流回路は、電流源11、NchMOSトランジスタM1、M2、抵抗素子RA1、RA2、RB2を備える。

【0022】

電流源11は、一方の端子を電源10と接続し、他方の端子をNchMOSトランジスタM1のゲートとドレインとに接続する。第一の温度係数を持つ抵抗素子RA1は、NchMOSトランジスタM1のソースとGND間に接続される。NchMOSトランジスタM2は、ゲートをNchMOSトランジスタM1のゲートと共通に接続し、ソースとGND間に第一の温度係数を持つ抵抗素子RA2および第二の温度係数を持つ抵抗素子RB2とを直列接続し、ドレインからドレイン電流を出力端子12へ出力する。

【0023】

NchMOSトランジスタM1、M2は、カレントミラーを構成する。抵抗素子RA1の温度係数と、抵抗素子RA2および抵抗素子RB2を合成した抵抗の温度係数とが異なるため、NchMOSトランジスタM1のソース電位とNchMOSトランジスタM2のソース電位との差が温度によって異なる。このため、NchMOSトランジスタM1のゲート・ソース間電圧Vgs1とNchMOSトランジスタM2のゲート・ソース間電圧Vgs2の差も温度によって異なってくる。したがって、電流源11からNchMOSトランジスタM1に流れ込む電流の温度特性と、NchMOSトランジスタM2のドレインから出力される電流の温度特性とは、異なる特性を示す。この場合、出力電流の温度特性の傾きは、RA2の抵抗値とRB2の抵抗値の割合によって正負任意に設定可能である。

【0024】

電流源11からNchMOSトランジスタM1を介して流れる電流によって生じる抵抗素子RA1の電圧を、50〜100[mV]程度以上になるように抵抗値を設定する。すなわち、MOSトランジスタのΔVtや、MOSトランジスタに流れる電流の変化分ΔIdsによるゲート電圧の変化分ΔVgsに対して、十分大きい電圧になるよう設定する。

【0025】

この時、NchMOSトランジスタM1、M2を電流源11から流れる電流に対して十分大きいgmとなるようしておけば、出力側の電流が多少変化してもNchMOSトランジスタM1のゲート・ソース間電圧Vgs1とNchMOSトランジスタM2のゲート・ソース間電圧Vgs2との差は、ほとんど変化しない。

【0026】

従って、NchMOSトランジスタM1、M2のディメンジョンを同じにすると共に、下記の(1)式で示すように抵抗値を設定した場合、NchMOSトランジスタM1、M2に流れる電流は、ほぼ同じとなる。

RA1抵抗値≒RA2抵抗値+RB2抵抗値 ・・・・(1)

【0027】

この場合、(2)式が成り立つ。

NchMOSトランジスタM1のソース電位≒NchMOSトランジスタM2のソース電位 ・・・・(2)

【0028】

また、下記の(3)、(4)式が成り立つ。

NchMOSトランジスタM1のソース電位≒電流源11の電流*(R1a*(1+dta*(T−25))) ・・・・(3)

NchMOSトランジスタM2のソース電位≒出力電流*(R2a*(1+dta*(T−25))+R2b*(1+dtb*(T−25))) ・・・・(4)

【0029】

上記の(2)、(3)、(4)式より、次式が得られる。

出力電流≒(電流源11の電流*(R1a*(1+dta*(T−25))))/(R2a*(1+dta*(T−25))+R2b*(1+dtb*(T−25))) ・・・・(5)

但し、R1a:RA1の25℃での抵抗値

R2a:RA2の25℃での抵抗値

R2b:RB2の25℃での抵抗値

dta:RA1、RA2の持つ抵抗の温度係数

dtb:RB2の持つ抵抗の温度係数

【0030】

(5)式において、出力電流の温度特性の違いが一番小さくなるのは、RA2=RA1、RB2=0Ωの時である。この場合、下記の(6)式に示すようになり、出力電流は、温度特性も含めて電流源11の電流と同じになる。

出力電流≒(電流源11の電流*(R1a*(1+dta*(T−25))))/(R2a*(1+dta*(T−25)))≒電流源11の電流 ・・・・(6)

【0031】

逆に、(5)式において、出力電流の温度特性の違いが一番大きくなるのは、RA2=0Ω、RB2=RA1の時である。この場合、下記の(7)式のようになる。

出力電流≒(電流源11の電流*(R1a*(1+dta*(T−25))))/(R2b*(1+dtb*(T−25)))≒電流源11の電流*((1+dta*(T−25))/(1+dtb*(T−25))) ・・・・(7)

【0032】

(7)式より、RA1およびRA2の抵抗の温度係数dtaとRB2の抵抗の温度係数dtbとの間に差がある場合、dta>dtbでは、温度が高くなるほど出力電流が大きくなり正の傾きをもった温度特性となる。逆に、dta<dtbでは、温度が高くなるほど出力電流が小さくなり負の傾きをもった温度特性となる。

【0033】

図2は、定電流回路の各抵抗素子の値を下記のように設定した場合の出力電流の温度特性を示す図である。

条件1:RA1=100KΩ(0.1[%/K])、RB2=100KΩ(0.4[%/K])

条件2:RA1=100KΩ(0.1[%/K])、RA2=50KΩ(0.1[%/K])、RB2=50KΩ(0.4[%/K])

条件3:RA1=100KΩ(0.4[%/K])、RB2=100KΩ(0.1[%/K])

条件4:RA1=100KΩ(0.4[%/K])、RA2=50KΩ(0.4[%/K])、RB2=50KΩ(0.1[%/K])

【0034】

以上説明したように、RA2の抵抗値とRB2の抵抗値の割合を適宜設定することで、出力電流の温度特性における傾きを正負任意に設定することができる。

【実施例2】

【0035】

図3は、本発明の第2の実施例に係る定電流回路の回路図である。図3において、図1と同一の符号は同一物を表し、その説明を省略する。第2の実施例の定電流回路は、図1の定電流回路の出力電流を入力とするPchMOSトランジスタM3とPchMOSトランジスタM4で構成されるカレントミラー回路を接続して備える。また、PchMOSトランジスタM3のソースと電源10の間に第一の温度係数を持つ抵抗素子RA3を備える。PchMOSトランジスタM4のソースと電源10間に第一の温度係数を持つ抵抗素子RA4と第二の温度係数を持つ抵抗素子RB4とを直列接続して備える。そして、PchMOSトランジスタM4のドレイン電流を出力端子12から出力する。なお、図1の抵抗素子RA2は省いている。

【0036】

以上のような定電流回路において、PchMOSトランジスタM3、M4、抵抗素子RA3、RA4、RB4からなる回路は、極性が異なるものの、図1のNchMOSトランジスタM1、M2、抵抗素子RA1、RA2、RB2からなる回路構成と同じであって同様に動作する。

【0037】

第2の実施例の定電流回路によれば、NchMOSトランジスタM1、M2を介して得られた出力電流の温度特性の傾きを、PchMOSトランジスタM3、M4を介して更に大きな傾きとすることが出来る。したがって、出力電流の温度特性の傾きを、より幅広い範囲で調整することが可能となる。

【実施例3】

【0038】

図4は、本発明の第3の実施例に係る定電流回路の回路図である。図4において、図1と同一の符号は同一物を表し、その説明を省略する。第3の実施例の定電流回路は、第1の実施例のNchMOSトランジスタM1のソースとGND間に第二の温度係数を持つ抵抗素子RB1と第一の温度係数を持つ可変抵抗素子RA5とを直列接続し、NchMOSトランジスタM2のソースとGND間に第一の温度係数を持つ抵抗素子RA2と第二の温度係数を持つ可変抵抗素子RB5とを直列接続し、NchMOSトランジスタM2のドレイン電流を出力端子12から出力する。

【0039】

このように定電流回路は、第二の温度係数を持つ可変抵抗素子RB5と第一の温度係数を持つ可変抵抗素子RA5とを有する。したがって、定電流回路を半導体集積回路に内蔵したような場合、外部のマイクロコンピュータなどのプログラムよって可変抵抗素子RA5、RB5の抵抗値を変更することで、出力電流の温度特性の傾きを適宜変更することが可能となる。

【0040】

なお、前述の特許文献等の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0041】

10 電源

11 電流源

12 出力端子

M1、M2 NchMOSトランジスタ

M3、M4 PchMOSトランジスタ

RA1〜RA4、RB1、RB2、RB4 抵抗素子

RA5、RB5 可変抵抗素子

【技術分野】

【0001】

本発明は、定電流回路に関し、特に、出力電流の温度特性の制御技術に関する。

【背景技術】

【0002】

定電流回路は、集積回路などで広く用いられる。このような定電流回路は、出力電流に温度依存性が少ないことが求められ、温度係数の異なる抵抗素子を組み合わせることで構成されている。例えば、特許文献1に記載の定電流回路は、一定の電圧を抵抗体に印加して抵抗体に流れる電流を出力とする定電流回路であって、抵抗体を正の温度係数を持つ抵抗体と負の温度係数を持つ抵抗体とを直列接続して温度係数がキャンセルされるように構成されている。

【0003】

また、特許文献2には、抵抗の温度係数の大小、あるいはその正負にかかわらず、確実に平坦な温度特性を実現する定電流源回路が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平2−66613号公報

【特許文献2】特開2005−316530号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

以下の分析は本発明において与えられる。

【0006】

従来例の目的は、定電流出力の温度特性をキャンセルすることにあった。ところで、温度センサーなどの回路によっては、温度特性の傾きがより大きい方が都合の良い場合がある。しかしながら、従来例の定電流回路は、出力電流において平坦な温度特性を実現することを目的として構成されるので、このままでは、出力する定電流の温度特性の傾きを広範囲に設定することができず、温度センサーなどの回路に適用することができない。

【課題を解決するための手段】

【0007】

本発明の1つのアスペクト(側面)に係る定電流回路は、電流源と、電流源をドレインに接続する、ダイオード接続される第1の第1導電型トランジスタと、第1の第1導電型トランジスタのソースと接地間に接続される第1の温度係数を持つ第1の抵抗素子と、ゲートを第1の第1導電型トランジスタのゲートに接続する第2の第1導電型トランジスタと、第2の第1導電型トランジスタのソースと接地間に接続される第2の温度係数を持つ第2の抵抗素子と、を備え、第2の第1導電型トランジスタのドレインを電流出力端とする。

【発明の効果】

【0008】

本発明によれば、異なる温度係数をもつ抵抗素子によって、出力する定電流の温度特性の傾きを広範囲に設定することができる。

【図面の簡単な説明】

【0009】

【図1】本発明の第1の実施例に係る定電流回路の回路図である。

【図2】定電流回路の各抵抗素子の値を変更した場合の出力電流の温度特性を示す図である。

【図3】本発明の第2の実施例に係る定電流回路の回路図である。

【図4】本発明の第3の実施例に係る定電流回路の回路図である。

【発明を実施するための形態】

【0010】

本発明の実施形態に係る定電流回路は、電流源(図1の11)と、電流源をドレインに接続する、ダイオード接続される第1の第1導電型トランジスタ(図1のM1)と、第1の第1導電型トランジスタのソースと接地間に接続される第1の温度係数を持つ第1の抵抗素子(図1のRA1)と、ゲートを第1の第1導電型トランジスタのゲートに接続する第2の第1導電型トランジスタ(図1のM2)と、第2の第1導電型トランジスタのソースと接地間に接続される第2の温度係数を持つ第2の抵抗素子(図1のRB2)と、を備え、第2の第1導電型トランジスタのドレインを電流出力端(図1の12)とする。

【0011】

定電流回路において、第2の第1導電型トランジスタのソースと接地間に、第2の抵抗素子と直列に第1の温度係数を持つ第3の抵抗素子(図1のRA2)をさらに備えるようにしてもよい。

【0012】

定電流回路において、第1の第1導電型トランジスタのソースと接地間に、第1の抵抗素子と直列に第2の温度係数を持つ第4の抵抗素子(図4のRB1)をさらに備えるようにしてもよい。

【0013】

定電流回路において、第1および第2の抵抗素子は、可変抵抗素子(図4のRA5、RB5)であってもよい。

【0014】

定電流回路において、第2の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を並列または直列形態で接続するようにしてもよい。

【0015】

定電流回路において、第1の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を並列または直列形態で接続するようにしてもよい。

【0016】

定電流回路において、第2の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を直並列組み合わせた形態で接続するようにしてもよい。

【0017】

定電流回路において、第1の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を直並列組み合わせた形態で接続するようにしてもよい。

【0018】

定電流回路において、電流出力端にドレインを接続する、ダイオード接続される第1の第2導電型トランジスタ(図3のM3)と、第1の第2導電型トランジスタのソースと電源間に接続される第1の温度係数を持つ第5の抵抗素子(図3のRA3)と、ゲートを第1の第2導電型トランジスタのゲートに接続する第2の第2導電型トランジスタ(図3のM4)と、第2の第2導電型トランジスタのソースと電源間に接続される第2の温度係数を持つ第6の抵抗素子(図3のRB4)と、をさらに備え、第2の第2導電型トランジスタのドレインを他の電流出力端(図3の12)としてもよい。

【0019】

以上のような半導体装置によれば、抵抗素子の温度係数がそれぞれ異なるようにすることで、入力電流の温度特性と出力電流の温度特性に違いにより、正か負のいずれか一方しか持たない半導体プロセスにおいても正負任意の傾きを持つ温度特性の出力電流設定が可能となる。

【0020】

以下、実施例に即し、図面を参照して詳しく説明する。

【実施例1】

【0021】

図1は、本発明の第1の実施例に係る定電流回路の回路図である。図1において、定電流回路は、電流源11、NchMOSトランジスタM1、M2、抵抗素子RA1、RA2、RB2を備える。

【0022】

電流源11は、一方の端子を電源10と接続し、他方の端子をNchMOSトランジスタM1のゲートとドレインとに接続する。第一の温度係数を持つ抵抗素子RA1は、NchMOSトランジスタM1のソースとGND間に接続される。NchMOSトランジスタM2は、ゲートをNchMOSトランジスタM1のゲートと共通に接続し、ソースとGND間に第一の温度係数を持つ抵抗素子RA2および第二の温度係数を持つ抵抗素子RB2とを直列接続し、ドレインからドレイン電流を出力端子12へ出力する。

【0023】

NchMOSトランジスタM1、M2は、カレントミラーを構成する。抵抗素子RA1の温度係数と、抵抗素子RA2および抵抗素子RB2を合成した抵抗の温度係数とが異なるため、NchMOSトランジスタM1のソース電位とNchMOSトランジスタM2のソース電位との差が温度によって異なる。このため、NchMOSトランジスタM1のゲート・ソース間電圧Vgs1とNchMOSトランジスタM2のゲート・ソース間電圧Vgs2の差も温度によって異なってくる。したがって、電流源11からNchMOSトランジスタM1に流れ込む電流の温度特性と、NchMOSトランジスタM2のドレインから出力される電流の温度特性とは、異なる特性を示す。この場合、出力電流の温度特性の傾きは、RA2の抵抗値とRB2の抵抗値の割合によって正負任意に設定可能である。

【0024】

電流源11からNchMOSトランジスタM1を介して流れる電流によって生じる抵抗素子RA1の電圧を、50〜100[mV]程度以上になるように抵抗値を設定する。すなわち、MOSトランジスタのΔVtや、MOSトランジスタに流れる電流の変化分ΔIdsによるゲート電圧の変化分ΔVgsに対して、十分大きい電圧になるよう設定する。

【0025】

この時、NchMOSトランジスタM1、M2を電流源11から流れる電流に対して十分大きいgmとなるようしておけば、出力側の電流が多少変化してもNchMOSトランジスタM1のゲート・ソース間電圧Vgs1とNchMOSトランジスタM2のゲート・ソース間電圧Vgs2との差は、ほとんど変化しない。

【0026】

従って、NchMOSトランジスタM1、M2のディメンジョンを同じにすると共に、下記の(1)式で示すように抵抗値を設定した場合、NchMOSトランジスタM1、M2に流れる電流は、ほぼ同じとなる。

RA1抵抗値≒RA2抵抗値+RB2抵抗値 ・・・・(1)

【0027】

この場合、(2)式が成り立つ。

NchMOSトランジスタM1のソース電位≒NchMOSトランジスタM2のソース電位 ・・・・(2)

【0028】

また、下記の(3)、(4)式が成り立つ。

NchMOSトランジスタM1のソース電位≒電流源11の電流*(R1a*(1+dta*(T−25))) ・・・・(3)

NchMOSトランジスタM2のソース電位≒出力電流*(R2a*(1+dta*(T−25))+R2b*(1+dtb*(T−25))) ・・・・(4)

【0029】

上記の(2)、(3)、(4)式より、次式が得られる。

出力電流≒(電流源11の電流*(R1a*(1+dta*(T−25))))/(R2a*(1+dta*(T−25))+R2b*(1+dtb*(T−25))) ・・・・(5)

但し、R1a:RA1の25℃での抵抗値

R2a:RA2の25℃での抵抗値

R2b:RB2の25℃での抵抗値

dta:RA1、RA2の持つ抵抗の温度係数

dtb:RB2の持つ抵抗の温度係数

【0030】

(5)式において、出力電流の温度特性の違いが一番小さくなるのは、RA2=RA1、RB2=0Ωの時である。この場合、下記の(6)式に示すようになり、出力電流は、温度特性も含めて電流源11の電流と同じになる。

出力電流≒(電流源11の電流*(R1a*(1+dta*(T−25))))/(R2a*(1+dta*(T−25)))≒電流源11の電流 ・・・・(6)

【0031】

逆に、(5)式において、出力電流の温度特性の違いが一番大きくなるのは、RA2=0Ω、RB2=RA1の時である。この場合、下記の(7)式のようになる。

出力電流≒(電流源11の電流*(R1a*(1+dta*(T−25))))/(R2b*(1+dtb*(T−25)))≒電流源11の電流*((1+dta*(T−25))/(1+dtb*(T−25))) ・・・・(7)

【0032】

(7)式より、RA1およびRA2の抵抗の温度係数dtaとRB2の抵抗の温度係数dtbとの間に差がある場合、dta>dtbでは、温度が高くなるほど出力電流が大きくなり正の傾きをもった温度特性となる。逆に、dta<dtbでは、温度が高くなるほど出力電流が小さくなり負の傾きをもった温度特性となる。

【0033】

図2は、定電流回路の各抵抗素子の値を下記のように設定した場合の出力電流の温度特性を示す図である。

条件1:RA1=100KΩ(0.1[%/K])、RB2=100KΩ(0.4[%/K])

条件2:RA1=100KΩ(0.1[%/K])、RA2=50KΩ(0.1[%/K])、RB2=50KΩ(0.4[%/K])

条件3:RA1=100KΩ(0.4[%/K])、RB2=100KΩ(0.1[%/K])

条件4:RA1=100KΩ(0.4[%/K])、RA2=50KΩ(0.4[%/K])、RB2=50KΩ(0.1[%/K])

【0034】

以上説明したように、RA2の抵抗値とRB2の抵抗値の割合を適宜設定することで、出力電流の温度特性における傾きを正負任意に設定することができる。

【実施例2】

【0035】

図3は、本発明の第2の実施例に係る定電流回路の回路図である。図3において、図1と同一の符号は同一物を表し、その説明を省略する。第2の実施例の定電流回路は、図1の定電流回路の出力電流を入力とするPchMOSトランジスタM3とPchMOSトランジスタM4で構成されるカレントミラー回路を接続して備える。また、PchMOSトランジスタM3のソースと電源10の間に第一の温度係数を持つ抵抗素子RA3を備える。PchMOSトランジスタM4のソースと電源10間に第一の温度係数を持つ抵抗素子RA4と第二の温度係数を持つ抵抗素子RB4とを直列接続して備える。そして、PchMOSトランジスタM4のドレイン電流を出力端子12から出力する。なお、図1の抵抗素子RA2は省いている。

【0036】

以上のような定電流回路において、PchMOSトランジスタM3、M4、抵抗素子RA3、RA4、RB4からなる回路は、極性が異なるものの、図1のNchMOSトランジスタM1、M2、抵抗素子RA1、RA2、RB2からなる回路構成と同じであって同様に動作する。

【0037】

第2の実施例の定電流回路によれば、NchMOSトランジスタM1、M2を介して得られた出力電流の温度特性の傾きを、PchMOSトランジスタM3、M4を介して更に大きな傾きとすることが出来る。したがって、出力電流の温度特性の傾きを、より幅広い範囲で調整することが可能となる。

【実施例3】

【0038】

図4は、本発明の第3の実施例に係る定電流回路の回路図である。図4において、図1と同一の符号は同一物を表し、その説明を省略する。第3の実施例の定電流回路は、第1の実施例のNchMOSトランジスタM1のソースとGND間に第二の温度係数を持つ抵抗素子RB1と第一の温度係数を持つ可変抵抗素子RA5とを直列接続し、NchMOSトランジスタM2のソースとGND間に第一の温度係数を持つ抵抗素子RA2と第二の温度係数を持つ可変抵抗素子RB5とを直列接続し、NchMOSトランジスタM2のドレイン電流を出力端子12から出力する。

【0039】

このように定電流回路は、第二の温度係数を持つ可変抵抗素子RB5と第一の温度係数を持つ可変抵抗素子RA5とを有する。したがって、定電流回路を半導体集積回路に内蔵したような場合、外部のマイクロコンピュータなどのプログラムよって可変抵抗素子RA5、RB5の抵抗値を変更することで、出力電流の温度特性の傾きを適宜変更することが可能となる。

【0040】

なお、前述の特許文献等の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0041】

10 電源

11 電流源

12 出力端子

M1、M2 NchMOSトランジスタ

M3、M4 PchMOSトランジスタ

RA1〜RA4、RB1、RB2、RB4 抵抗素子

RA5、RB5 可変抵抗素子

【特許請求の範囲】

【請求項1】

電流源と、

前記電流源をドレインに接続する、ダイオード接続される第1の第1導電型トランジスタと、

前記第1の第1導電型トランジスタのソースと接地間に接続される第1の温度係数を持つ第1の抵抗素子と、

ゲートを前記第1の第1導電型トランジスタのゲートに接続する第2の第1導電型トランジスタと、

前記第2の第1導電型トランジスタのソースと接地間に接続される第2の温度係数を持つ第2の抵抗素子と、

を備え、

前記第2の第1導電型トランジスタのドレインを電流出力端とすることを特徴とする定電流回路。

【請求項2】

前記第2の第1導電型トランジスタのソースと接地間に、前記第2の抵抗素子と直列に第1の温度係数を持つ第3の抵抗素子をさらに備えることを特徴とする請求項1記載の定電流回路。

【請求項3】

前記第1の第1導電型トランジスタのソースと接地間に、前記第1の抵抗素子と直列に第2の温度係数を持つ第4の抵抗素子をさらに備えることを特徴とする請求項1または2記載の定電流回路。

【請求項4】

前記第1および第2の抵抗素子は、可変抵抗素子であることを特徴とする請求項1乃至3のいずれか一に記載の定電流回路。

【請求項5】

前記第2の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を並列または直列形態で接続することを特徴とする請求項1記載の定電流回路。

【請求項6】

前記第1の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を並列または直列形態で接続することを特徴とする請求項1または5記載の定電流回路。

【請求項7】

前記第2の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を直並列組み合わせた形態で接続することを特徴とする請求項1記載の定電流回路。

【請求項8】

前記第1の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を直並列組み合わせた形態で接続することを特徴とする請求項1または7記載の定電流回路。

【請求項9】

前記電流出力端にドレインを接続する、ダイオード接続される第1の第2導電型トランジスタと、

前記第1の第2導電型トランジスタのソースと電源間に接続される第1の温度係数を持つ第5の抵抗素子と、

ゲートを前記第1の第2導電型トランジスタのゲートに接続する第2の第2導電型トランジスタと、

前記第2の第2導電型トランジスタのソースと電源間に接続される第2の温度係数を持つ第6の抵抗素子と、

をさらに備え、

前記第2の第2導電型トランジスタのドレインを他の電流出力端とすることを特徴とする請求項1乃至8のいずれか一に記載の定電流回路。

【請求項10】

請求項1乃至9のいずれか一に記載の定電流回路を備える半導体集積回路装置。

【請求項1】

電流源と、

前記電流源をドレインに接続する、ダイオード接続される第1の第1導電型トランジスタと、

前記第1の第1導電型トランジスタのソースと接地間に接続される第1の温度係数を持つ第1の抵抗素子と、

ゲートを前記第1の第1導電型トランジスタのゲートに接続する第2の第1導電型トランジスタと、

前記第2の第1導電型トランジスタのソースと接地間に接続される第2の温度係数を持つ第2の抵抗素子と、

を備え、

前記第2の第1導電型トランジスタのドレインを電流出力端とすることを特徴とする定電流回路。

【請求項2】

前記第2の第1導電型トランジスタのソースと接地間に、前記第2の抵抗素子と直列に第1の温度係数を持つ第3の抵抗素子をさらに備えることを特徴とする請求項1記載の定電流回路。

【請求項3】

前記第1の第1導電型トランジスタのソースと接地間に、前記第1の抵抗素子と直列に第2の温度係数を持つ第4の抵抗素子をさらに備えることを特徴とする請求項1または2記載の定電流回路。

【請求項4】

前記第1および第2の抵抗素子は、可変抵抗素子であることを特徴とする請求項1乃至3のいずれか一に記載の定電流回路。

【請求項5】

前記第2の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を並列または直列形態で接続することを特徴とする請求項1記載の定電流回路。

【請求項6】

前記第1の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を並列または直列形態で接続することを特徴とする請求項1または5記載の定電流回路。

【請求項7】

前記第2の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を直並列組み合わせた形態で接続することを特徴とする請求項1記載の定電流回路。

【請求項8】

前記第1の第1導電型トランジスタのソースと接地間に、それぞれ温度係数の異なる抵抗素子を直並列組み合わせた形態で接続することを特徴とする請求項1または7記載の定電流回路。

【請求項9】

前記電流出力端にドレインを接続する、ダイオード接続される第1の第2導電型トランジスタと、

前記第1の第2導電型トランジスタのソースと電源間に接続される第1の温度係数を持つ第5の抵抗素子と、

ゲートを前記第1の第2導電型トランジスタのゲートに接続する第2の第2導電型トランジスタと、

前記第2の第2導電型トランジスタのソースと電源間に接続される第2の温度係数を持つ第6の抵抗素子と、

をさらに備え、

前記第2の第2導電型トランジスタのドレインを他の電流出力端とすることを特徴とする請求項1乃至8のいずれか一に記載の定電流回路。

【請求項10】

請求項1乃至9のいずれか一に記載の定電流回路を備える半導体集積回路装置。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2010−165177(P2010−165177A)

【公開日】平成22年7月29日(2010.7.29)

【国際特許分類】

【出願番号】特願2009−6927(P2009−6927)

【出願日】平成21年1月15日(2009.1.15)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成22年7月29日(2010.7.29)

【国際特許分類】

【出願日】平成21年1月15日(2009.1.15)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]