実装構造体、および実装構造体の製造方法

【課題】 従来の実装構造体では、落下などに起因する衝撃に対しての要求される耐衝撃性を確保できない場合があった。

【解決手段】 基板表面1210に垂直な方向の凸部1510の厚さは、基板表面1210に垂直な方向のソルダレジスト1400の厚さより、10μm以上40μm以下の範囲で大きく、基板電極1311および1312の、基板表面1210の部分1220の側にある電極辺1321および1322の方向の、凸部1510の長さは、電極辺1321および1322の長さの80%以上120%以下であり、凸部1510と電極辺1321および1322との間の距離は、0mm以上0.7mm以下であり、凸部1510は、基板電極1311および1312の電極表面に面接触しないように形成されている、実装構造体1000である。

【解決手段】 基板表面1210に垂直な方向の凸部1510の厚さは、基板表面1210に垂直な方向のソルダレジスト1400の厚さより、10μm以上40μm以下の範囲で大きく、基板電極1311および1312の、基板表面1210の部分1220の側にある電極辺1321および1322の方向の、凸部1510の長さは、電極辺1321および1322の長さの80%以上120%以下であり、凸部1510と電極辺1321および1322との間の距離は、0mm以上0.7mm以下であり、凸部1510は、基板電極1311および1312の電極表面に面接触しないように形成されている、実装構造体1000である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子部品を電子回路基板に実装するための、実装構造体、および実装構造体の製造方法に関するものである。

【背景技術】

【0002】

導電性フィラーを構成するための半田粒子からなる半田と、粘度の調整などを行うためのフラックス成分と、を含む組成物であるクリーム半田などの導電性ペーストが、電子部品を電子回路基板に実装するために利用されている。

【0003】

近年、電子部品のパッケージサイズは、微細化される傾向にある。

【0004】

そのため、電子部品が実装される電子回路基板の基板表面に形成された基板電極の上に塗布された導電性ペーストが電子部品と接触する面積は、小さくなってきている。

【0005】

よって、落下などに起因する衝撃に対しての耐衝撃性を確保することは、必ずしも容易ではない。

【0006】

そこで、半田と、フラックス成分と、に加えて、エポキシ樹脂などの補強用の樹脂を含む導電性ペーストの開発が、半田接合部を補強する目的で進められている(たとえば、特許文献1参照)。

【0007】

ここで、従来の実装構造体1000pの模式的な断面図である図19を参照しながら、従来の実装構造体1000pの構成、およびその製造方法について説明する。

【0008】

以下の説明においては、三次元空間の直交座標系を定めるための、互いに直交する三本の数直線であるX軸、Y軸およびZ軸が利用される。

【0009】

基板表面1210の全体にあらかじめ形成されていた回路パターン用の銅箔の内、回路パターンに対応する部分以外の部分が除去され、基板電極1311および1312などの回路パターンが基板表面1210に形成される。

【0010】

回路パターンが前述の通り形成された基板表面1210の全体に塗布されたソルダレジスト用のインキの内、基板電極1311および1312などに対応する部分が除去され、ソルダレジスト1400が同部分を除いて基板表面1210に形成される。

【0011】

半田と、フラックス成分と、樹脂と、を含む導電性ペーストが基板電極1311および1312の上に塗布され、電子部品1100が塗布された導電性ペーストの上に載置される。

【0012】

導電性ペーストが塗布され、電子部品1100が載置された電子回路基板1200は、加熱される。

【0013】

すると、樹脂は半田と分離し、半田と分離した樹脂は半田によって形成された半田接合部1611および1612を+Z方向に濡れ上がって硬化し、半田接合部1611および1612を覆う樹脂補強部1710pが形成される。

【0014】

このようにして、半田接合部1611および1612による半田接合と、樹脂補強部1710pによる樹脂補強と、が同時に行われ、落下などに起因する衝撃に対しての耐衝撃性が確保された実装構造体1000pが得られる。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開2010−77271号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

しかしながら、前述した従来の実装構造体1000pでは、要求される耐衝撃性を確保できない場合があることが判明した。

【0017】

すなわち、導電性ペーストが加熱され、補強用の樹脂が半田と分離すると、半田と分離した樹脂は電子部品1100の部品下面1110の下側の空隙に優先的に充填されてしまう。

【0018】

これは、加熱された樹脂はその粘度が低くなるために比較的に高い流動性をもち、毛細管現象が発生するからである。

【0019】

そして、実質的に平坦なソルダレジスト1400のレジスト表面1410と、部品下面1110と、の間の距離(d)が通常30〜100μm程度はある前述した空隙の体積、したがって同空隙に充填されてしまう樹脂の量は、無視できない程度に大きいことがある。

【0020】

すると、半田と分離した樹脂が半田接合部1611および1612を+Z方向に十分に濡れ上がることができず、形成された樹脂補強部1710pのZ方向の高さ(Hp)が半田接合部1611および1612に比較して小さくなってしまう。

【0021】

結果的に、要求される耐衝撃性を確保できる樹脂補強部1710pが形成されない場合が、あった。

【0022】

本発明は、上述した従来の課題を考慮し、落下などに起因する衝撃に対してのより優れた耐衝撃性を確保することが可能な、実装構造体、および実装構造体の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0023】

第1の本発明は、電子回路基板の基板表面に形成された少なくとも二つの基板電極と、

電子部品をそれぞれの前記基板電極に接合する半田接合部と、

前記半田接合部を覆う樹脂補強部と、

前記基板表面に形成されたソルダレジストと、

前記電子部品の下側にあり前記基板電極に挟まれた、前記基板表面の部分に形成された凸部と、

を備え、

前記基板表面に垂直な方向の前記凸部の厚さは、前記基板表面に垂直な前記方向の前記ソルダレジストの厚さより、10μm以上40μm以下の範囲で大きく、

前記基板電極の、前記基板表面の前記部分の側にある電極辺の方向の、前記凸部の長さは、前記電極辺の長さの80%以上120%以下であり、

前記凸部と前記電極辺との間の距離は、0mm以上0.7mm以下であり、

前記凸部は、前記基板電極の電極表面に面接触しないように形成されている、実装構造体である。

【0024】

第2の本発明は、前記凸部の材料は、前記ソルダレジストの材料と異なる、第1の本発明の実装構造体である。

【0025】

第3の本発明は、前記基板表面の前記部分に形成された基板配線を備え、

前記凸部は、前記基板配線と、前記基板配線の上に形成された前記ソルダレジストと、によって構成されている、第1の本発明の実装構造体である。

【0026】

第4の本発明は、前記凸部の前記厚さは、前記ソルダレジストの前記厚さより、25μm以上の範囲で大きく、

前記凸部の前記長さは、前記電極辺の前記長さの100%以上であり、

前記凸部と前記電極辺との間の前記距離は、0.3mm以下である、第1の本発明の実装構造体である。

【0027】

第5の本発明は、少なくとも二つの基板電極を、電子回路基板の基板表面に形成する基板電極形成ステップと、

ソルダレジストを、前記基板表面に形成するソルダレジスト形成ステップと、

所定の部材を、前記基板電極に挟まれた、前記ソルダレジストのレジスト表面に形成する部材形成ステップと、

半田と、フラックス成分と、樹脂と、を含む導電性ペーストを、前記基板電極の上に塗布する導電性ペースト塗布ステップと、

電子部品を、前記塗布された導電性ペーストの上に載置する電子部品載置ステップと、

前記基板電極と、前記ソルダレジストと、前記部材と、が形成され、前記導電性ペーストが塗布され、前記電子部品が載置された前記電子回路基板を加熱する加熱ステップと、

を備えた、実装構造体の製造方法である。

【発明の効果】

【0028】

本発明により、落下などに起因する衝撃に対してのより優れた耐衝撃性を確保することが可能な、実装構造体、および実装構造体の製造方法を提供することができる。

【図面の簡単な説明】

【0029】

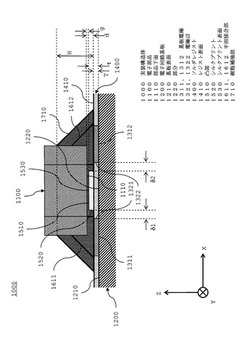

【図1】本発明における実施の形態1の実装構造体の模式的な断面図

【図2】本発明における実施の形態1の実装構造体の模式的な平面図

【図3】本発明における実施の形態2の実装構造体の模式的な断面図

【図4】本発明における実施の形態2の実装構造体の模式的な平面図

【図5】本発明における実施例1の実装構造体の模式的な平面図

【図6】本発明における実施例2の実装構造体の模式的な平面図

【図7】本発明における実施例3の実装構造体の模式的な平面図

【図8】本発明における実施例4の実装構造体の模式的な平面図

【図9】本発明における実施例5の実装構造体の模式的な平面図

【図10】本発明における実施例6の実装構造体の模式的な平面図

【図11】本発明における実施例7の実装構造体の模式的な平面図

【図12】本発明における実施例8の実装構造体の模式的な平面図

【図13】本発明における比較例1の実装構造体の模式的な平面図

【図14】本発明における比較例2の実装構造体の模式的な平面図

【図15】本発明における比較例3の実装構造体の模式的な平面図

【図16】本発明における比較例4の実装構造体の模式的な平面図

【図17】本発明における比較例5の実装構造体の模式的な平面図

【図18】本発明における実施例1〜8およびおよび比較例1〜5の実装構造体に対して行われた耐衝撃試験の結果を説明する説明図

【図19】従来の実装構造体の模式的な断面図

【発明を実施するための形態】

【0030】

以下、図面を参照しながら、本発明における実施の形態について詳細に説明する。

【0031】

(実施の形態1)

はじめに、本発明における実施の形態1の実装構造体の模式的な断面図である図1、および本発明における実施の形態1の実装構造体の模式的な平面図である図2を主として参照しながら、本実施の形態の実装構造体1000の構成について説明する。

【0032】

ここに、図2においては、電子部品1100などの図示が省略されている。

【0033】

実装構造体1000は、少なくとも二つの基板電極1311および1312と、半田接合部1611および1612と、樹脂補強部1710と、ソルダレジスト1400と、凸部1510と、を備えている。

【0034】

以下では、実装構造体1000の構成についてより具体的に説明する。

【0035】

基板電極1311および1312は、電子回路基板1200の基板表面1210に形成されている。

【0036】

半田接合部1611および1612は、電子部品1100をそれぞれの基板電極1311および1312に接合している。

【0037】

ここに、電子部品1100は、チップ部品などである。

【0038】

樹脂補強部1710は、半田接合部1611および1612を覆っている。

【0039】

なお、基板表面1210に垂直な方向(Z方向)の樹脂補強部1710の高さ(H)は、実質的に0.1mm以上である。

【0040】

ここに、ソルダレジスト1400は基板表面1210に直接的に形成されているので、高さ(H)は実質的に平坦なソルダレジスト1400のレジスト表面1410を基準として定義されている。

【0041】

ソルダレジスト1400は、基板表面1210に形成されている。

【0042】

ソルダレジスト1400は、後述の通りソルダレジスト用のインキを利用して形成された厚さ(T)30μm程度のレジストである。

【0043】

凸部1510は、電子部品1100の下側(−Z側)にあり基板電極1311および1312に挟まれた、基板表面1210の部分1220に形成されている。

【0044】

もちろん、後述されるように、凸部1510の長さ(λ)が電極辺1321および1322の長さ(L1およびL2)より大きい場合もあり、そのような場合には凸部1510の端部は電極辺1321および/または1322の端部よりも飛び出す。

【0045】

基板表面1210に垂直な方向(Z方向)の凸部1510の厚さ(τ)は、基板表面1210に垂直な方向(Z方向)のソルダレジスト1400の厚さ(T)より、実質的に10μm以上40μm以下の範囲で大きい。

【0046】

ここに、厚さτは、基板表面1210を基準として定義されている。

【0047】

より具体的には、凸部1510は、後述の通りシルクプリント用のインキを利用してレジスト表面1410に形成された厚さ(τ−T>0)10〜40μm程度の略直方体の形状を有するシルクプリント1520と、シルクプリント1520の−Z側にある厚さ(T)30μm程度のソルダレジスト1400と、で構成されている。

【0048】

したがって、シルクプリント1520のシルクプリント表面1530と、電子部品1100の部品下面1110と、の間のZ方向のギャップ(g)は、実質的に平坦なソルダレジスト1400のレジスト表面1410と、部品下面1110と、の間の距離(d)が40μm程度であれば、大きくても30μm程度しかない。

【0049】

ここに、凸部1510の厚さ(τ)とソルダレジスト1400の厚さ(T)との差(τ−T>0)が10μmより小さいと、部品下面1110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0050】

そして、凸部1510の厚さ(τ)とソルダレジスト1400の厚さ(T)との差(τ−T>0)が40μmより大きいと、導電性ペースト塗布ステップにおけるメタルマスクの面と基板電極1311および1312の電極表面との間に形成されるギャップが無視できなくなり、基板電極1311および1312の上に塗布された導電性ペーストの印刷形状が悪化してしまう恐れがある。

【0051】

なお、凸部1510の材料は、ソルダレジスト1400の材料と異なっているが、ソルダレジスト1400の材料と同じであってもよい。

【0052】

もちろん、凸部1510がシルクプリント1520と、ソルダレジスト1400と、で前述の通り構成されているので、凸部1510の材料は、シルクプリント1520の材料とソルダレジスト1400の材料とが異なっていれば、ソルダレジスト1400の材料と異なっていることになる。

【0053】

基板電極1311および1312の、基板表面1210の部分1220の側にある電極辺1321および1322の方向(Y方向)の、凸部1510の長さ(λ)は、電極辺1321および1322の長さ(L1およびL2)の実質的に80%以上120%以下である。

【0054】

もちろん、L1およびL2のように添数が異なる量は、以下の説明では特に断らない限り等しいが、必ずしも等しくなくてもよい(その他の量についても同様である)。

【0055】

ここに、凸部1510の長さ(λ)が電極辺1321および1322の長さ(L1およびL2)の80%より小さいと、部品下面1110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0056】

そして、凸部1510の長さ(λ)が電極辺1321および1322の長さ(L1およびL2)の120%より大きいと、凸部1510が隣接する電子部品(図示省略)のランド部分に接触してしまう恐れがある。

【0057】

凸部1510と電極辺1321および1322との間の距離(δ1およびδ2)は、実質的に0mm以上0.7mm以下である。

【0058】

凸部1510は、基板電極1311および1312の電極表面に面接触しないように形成されている。

【0059】

ここに、凸部1510と電極辺1321および1322との間の距離(δ1およびδ2)が0.7mmより大きいと、部品下面1110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0060】

もちろん、凸部1510が基板電極1311および1312の電極表面に面接触していないので、基板電極1311および1312の上に塗布された導電性ペーストの印刷形状が悪化し、導電性ペーストが電子部品1100と接触する面積が不十分になってしまう恐れはほとんどない。

【0061】

つぎに、図1および2を主として参照しながら、実装構造体1000の製造方法について説明する。

【0062】

以下では、基板電極形成ステップと、ソルダレジスト形成ステップと、シルクプリント形成ステップと、導電性ペースト塗布ステップと、電子部品載置ステップと、加熱ステップと、についてこの順番で具体的に説明する。

【0063】

もちろん、上記のステップは必ずしもこの順番で行われなくてもよく、たとえば、導電性ペースト塗布ステップはシルクプリント形成ステップが行われた後で行われてもよい。

【0064】

(基板電極形成ステップ)

少なくとも二つの基板電極1311および1312が、電子回路基板1200の基板表面1210に形成される。

【0065】

より具体的には、基板表面1210の全体にあらかじめ形成されていた回路パターン用の銅箔の内、回路パターンに対応する部分以外の部分がフォトリソグラフィなどにより除去され、基板電極1311および1312などの回路パターンが基板表面1210に形成される。

【0066】

(ソルダレジスト形成ステップ)

ソルダレジスト1400が、基板表面1210に形成される。

【0067】

より具体的には、回路パターンが前述の通り形成された基板表面1210の全体に塗布されたアクリル系またはエポキシアクレート系などの樹脂であるソルダレジスト用のインキの内、基板電極1311および1312などに対応する部分がフォトリソグラフィなどにより除去され、ソルダレジスト1400が同部分を除いて基板表面1210に厚さ(T)30μm程度のレジストとして形成される。

【0068】

もちろん、ソルダレジスト1400は、基板電極1311および1312などに対応する部分を少なくとも除いて基板表面1210に形成されていればよく、たとえば、基板電極1311および1312などに対応する部分およびその周辺の狭小部分を除いて基板表面1210に形成されていてもよい。

【0069】

(シルクプリント形成ステップ)

シルクプリント1520が、基板電極1311および1312に挟まれた、ソルダレジスト1400のレジスト表面1410に形成される。

【0070】

より具体的には、アクリル系またはエポキシアクレート系などの樹脂であるシルクプリント用のインキがスクリーン印刷法などにより塗布され、シルクプリント1520が厚さ(τ−T>0)10〜40μm程度のプリントとして形成される。

【0071】

(導電性ペースト塗布ステップ)

半田と、フラックス成分と、樹脂と、を含む導電性ペーストが、基板電極1311および1312の上に塗布される。

【0072】

より具体的には、導電性ペーストは、開口が基板電極1311および1312などの電極サイズに応じて形成された厚さ120μm程度のメタルマスクを用いるスクリーン印刷機を利用して、スクリーン印刷法などにより塗布される。

【0073】

(電子部品載置ステップ)

電子部品1100が、塗布された導電性ペーストの上に載置される。

【0074】

より具体的には、電子部品1100は、チップマウンタを利用して、導電性ペーストの上に載置される。

【0075】

(加熱ステップ)

基板電極1311および1312と、ソルダレジスト1400と、シルクプリント1520と、が形成され、導電性ペーストが塗布され、電子部品1100が載置された電子回路基板1200が、加熱される。

【0076】

より具体的には、導電性ペーストが塗布され、電子部品1100が載置された電子回路基板1200は、リフロー炉を利用して半田の融点以上である160℃で6分間加熱される。

【0077】

すると、樹脂は半田と分離し、半田と分離した樹脂は半田によって形成された半田接合部1611および1612を+Z方向に濡れ上がって硬化し、半田接合部1611および1612を覆う樹脂補強部1710が形成される。

【0078】

前述されたように、シルクプリント表面1530と部品下面1110との間のZ方向のギャップ(g)は大きくても30μm程度しかないので、部品下面1110の下側の空隙に充填されてしまう樹脂の量はそれほど多くない。

【0079】

したがって、樹脂が半田接合部1611および1612を+Z方向に十分に濡れ上がることができ、形成された樹脂補強部1710のZ方向の高さ(H)が半田接合部1611および1612に比較して小さくなる恐れはほとんどない。

【0080】

このようにして、半田接合部1611および1612による半田接合と、樹脂補強部1710による樹脂補強と、が同時に行われ、落下などに起因する衝撃に対しての耐衝撃性が確保された実装構造体1000が得られる。

【0081】

(実施の形態2)

つぎに、本発明における実施の形態2の実装構造体の模式的な断面図である図3、および本発明における実施の形態2の実装構造体の模式的な平面図である図4を主として参照しながら、本実施の形態の実装構造体2000の構成について説明する。

【0082】

ここに、図4においては、電子部品2100などの図示が省略されている。

【0083】

実装構造体2000は、少なくとも二つの基板電極1311および1312と、半田接合部2611および2612と、樹脂補強部2711および2712と、ソルダレジスト2400と、凸部2511および2512と、を備えている。

【0084】

実装構造体2000の構成は、前述の実装構造体1000の構成とつぎのような点で異なっている。

【0085】

実装構造体2000は、基板表面1210の部分1220に形成された基板配線2521および2522を備えている。

【0086】

凸部2511および2512は、基板配線2521および2522と、基板配線2521および2522の上に形成されたソルダレジスト2400と、によって構成されている。

【0087】

ここに、基板配線2521および2522は、Cu(銅)配線などである。

【0088】

以下では、実装構造体2000の構成についてより具体的に説明する。

【0089】

基板電極1311および1312は、電子回路基板1200の基板表面1210に形成されている。

【0090】

半田接合部2611および2612は、電子部品2100をそれぞれの基板電極1311および1312に接合している。

【0091】

ここに、電子部品2100は、基板電極1311および1312に接合された部品電極2111および2112などを有するSON(Small Outline No−lead)部品などである。

【0092】

樹脂補強部2711および2712は、半田接合部2611および2612を覆っている。

【0093】

もちろん、樹脂補強部2711および2712は、たとえば電子部品2100の−Z側で一つにつながっていてもよい。

【0094】

なお、基板表面1210に垂直な方向(Z方向)の樹脂補強部2711および2712の高さ(H1およびH2)は、実質的に0.1mm以上である。

【0095】

ここに、ソルダレジスト2400の一部は基板表面1210に直接的にではなく前述の通り基板配線2521および2522の上に形成されているので、高さ(H1およびH2)は基板表面1210に直接的に形成されている実質的に平坦なソルダレジスト2400のレジスト表面2410を基準として定義されている。

【0096】

ソルダレジスト2400は、基板表面1210に形成されている。

【0097】

ソルダレジスト2400は、後述の通りソルダレジスト用のインキを利用して形成された厚さ(T)30μm程度のレジストである。

【0098】

凸部2511および2512は、電子部品2100の下側(−Z側)にあり基板電極1311および1312に挟まれた、基板表面1210の部分1220に形成されている。

【0099】

もちろん、後述されるように、凸部2511および2512の長さ(λ1およびλ2)が電極辺1321および1322の長さ(L1およびL2)より大きい場合もあり、そのような場合には凸部2511および2512の端部は電極辺1321および/または1322の端部よりも飛び出す。

【0100】

そして、後述されるように、凸部2511および2512はソルダレジスト形成ステップにおいて自然に形成されるので、ソルダレジスト2400は実質的に平坦なソルダレジスト2400のレジスト表面2410から見て基板配線2521および2522の周辺の狭小部分で盛り上がる場合が多く、そのような場合には凸部2511および2512は同狭小部分に相当する部分だけやや大きくなる。

【0101】

基板表面1210に垂直な方向(Z方向)の凸部2511および2512の厚さ(τ1およびτ2)は、基板表面1210に垂直な方向(Z方向)のソルダレジスト2400の厚さ(T)より、実質的に10μm以上40μm以下の範囲で大きい。

【0102】

ここに、厚さτ1およびτ2は、基板表面1210を基準として定義されている。

【0103】

より具体的には、凸部2511および2512は、前述の通り基板表面1210に形成された厚さ(τi−T>0、i=1および2)25μm程度の略直方体の形状を有する基板配線2521および2522と、基板配線2521および2522の+Z側にある厚さ(T)30μm程度のソルダレジスト2400と、で構成されている。

【0104】

したがって、基板配線2521および2522の上に形成されているソルダレジスト2400のレジスト表面2410と、電子部品2100の部品下面2110と、の間のZ方向のギャップ(g)は、基板表面1210に直接的に形成されている実質的に平坦なソルダレジスト2400のレジスト表面2410と、部品下面2110と、の間の距離(d)が40μm程度であれば、大きくても15μm程度しかない。

【0105】

このように比較的に厚い基板配線2521および2522が基板電極1311および1312のかなり近くに設けられている場合などには、製造時に加熱された樹脂が部品下面2110の下側の空隙にまで達しないので、樹脂補強部2711および2712が一つにつながることさえない。

【0106】

ここに、凸部2511および2512の厚さ(τ1およびτ2)とソルダレジスト2400の厚さ(T)との差(τ−T>0)が10μmより小さいと、部品下面2110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0107】

そして、凸部2511および2512の厚さ(τ1およびτ2)とソルダレジスト2400の厚さ(T)との差(τ−T>0)が40μmより大きいと、導電性ペースト塗布ステップにおけるメタルマスクの面と基板電極1311および1312の電極表面との間に形成されるギャップが無視できなくなり、基板電極1311および1312の上に塗布された導電性ペーストの印刷形状が悪化してしまう恐れがある。

【0108】

基板電極1311および1312の、基板表面1210の部分1220の側にある電極辺1321および1322の方向(Y方向)の、凸部2511および2512の長さ(λ1およびλ2)は、電極辺1321および1322の長さ(L1およびL2)の実質的に80%以上120%以下である。

【0109】

ここに、凸部2511および2512の長さ(λ1およびλ2)が電極辺1321および1322の長さ(L1およびL2)の80%より小さいと、部品下面2110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0110】

そして、凸部2511および2512の長さ(λ1およびλ2)が電極辺1321および1322の長さ(L1およびL2)の120%より大きいと、凸部2511および2512が隣接する電子部品(図示省略)のランド部分に接触してしまう恐れがある。

【0111】

凸部2511および2512と電極辺1321および1322との間の距離(δ1およびδ2)は、実質的に0mm以上0.7mm以下である。

【0112】

凸部2511および2512は、基板電極1311および1312の電極表面に面接触しないように形成されている。

【0113】

ここに、凸部2511および2512と電極辺1321および1322との間の距離(δ1およびδ2)が0.7mmより大きいと、部品下面2110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0114】

もちろん、凸部2511および2512が基板電極1311および1312の電極表面に面接触していないので、基板電極1311および1312の上に塗布された導電性ペーストの印刷形状が悪化し、導電性ペーストが電子部品2100と接触する面積が不十分になってしまう恐れはほとんどない。

【0115】

つぎに、図3および4を主として参照しながら、実装構造体2000の製造方法について説明する。

【0116】

以下では、基板電極形成ステップと、ソルダレジスト形成ステップと、導電性ペースト塗布ステップと、電子部品載置ステップと、加熱ステップと、についてこの順番で具体的に説明する。

【0117】

(基板電極形成ステップ)

少なくとも二つの基板電極1311および1312が、電子回路基板1200の基板表面1210に形成される。

【0118】

より具体的には、基板表面1210の全体にあらかじめ形成されていた回路パターン用の銅箔の内、回路パターンに対応する部分以外の部分がフォトリソグラフィなどにより除去され、基板電極1311および1312、ならびに基板配線2521および2522などの回路パターンが基板表面1210に形成される。

【0119】

(ソルダレジスト形成ステップ)

ソルダレジスト2400が、基板表面1210に形成される。

【0120】

より具体的には、回路パターンが前述の通り形成された基板表面1210の全体に塗布されたアクリル系またはエポキシアクレート系などの樹脂であるソルダレジスト用のインキの内、基板電極1311および1312などに対応する部分がフォトリソグラフィなどにより除去され、ソルダレジスト2400が同部分を除いて基板表面1210に厚さ(T)30μm程度のレジストとして形成される。

【0121】

そして、凸部2511および2512が、前述の通り基板表面1210に形成された厚さ(τi−T>0、i=1および2)25μm程度の基板配線2521および2522に対応するレジスト表面2410の突起物として形成される。

【0122】

もちろん、ソルダレジスト2400は、基板電極1311および1312などに対応する部分を少なくとも除いて基板表面1210に形成されていればよく、たとえば、基板電極1311および1312などに対応する部分およびその周辺の狭小部分を除いて基板表面1210に形成されていてもよい。

【0123】

(導電性ペースト塗布ステップ)

半田と、フラックス成分と、樹脂と、を含む導電性ペーストが、基板電極1311および1312の上に塗布される。

【0124】

より具体的には、導電性ペーストは、開口が基板電極1311および1312などの電極サイズに応じて形成された厚さ120μm程度のメタルマスクを用いるスクリーン印刷機を利用して、スクリーン印刷法などにより塗布される。

【0125】

(電子部品載置ステップ)

電子部品2100が、塗布された導電性ペーストの上に載置される。

【0126】

より具体的には、電子部品2100は、チップマウンタを利用して、導電性ペーストの上に載置される。

【0127】

(加熱ステップ)

基板電極1311および1312と、ソルダレジスト2400と、が形成され、導電性ペーストが塗布され、電子部品2100が載置された電子回路基板1200が、加熱される。

【0128】

より具体的には、導電性ペーストが塗布され、電子部品2100が載置された電子回路基板1200は、リフロー炉を利用して半田の融点以上である160℃で6分間加熱される。

【0129】

すると、樹脂は半田と分離し、半田と分離した樹脂は半田によって形成された半田接合部2611および2612を+Z方向に濡れ上がって硬化し、半田接合部2611および2612を覆う樹脂補強部2711および2712が形成される。

【0130】

前述されたように、基板配線2521および2522の上に形成されているソルダレジスト2400のレジスト表面2410と、部品下面2110と、の間のZ方向のギャップ(g)は大きくても15μm程度しかないので、部品下面2110の下側の空隙に充填されてしまう樹脂の量はそれほど多くない。

【0131】

さらに、比較的に厚い基板配線2521および2522が基板電極1311および1312のかなり近くに設けられている場合などには、加熱された樹脂が部品下面2110の下側の空隙にまで達しないので、充填されてしまう樹脂の量は無視できる程度に小さく、樹脂補強部2711および2712が一つにつながることさえない。

【0132】

したがって、樹脂が半田接合部2611および2612を+Z方向に十分に濡れ上がることができ、形成された樹脂補強部2711および2712のZ方向の高さ(H1およびH2)が半田接合部2611および2612に比較して小さくなる恐れはほとんどない。

【0133】

このようにして、半田接合部2611および2612による半田接合と、樹脂補強部2711および2712による樹脂補強と、が同時に行われ、落下などに起因する衝撃に対しての耐衝撃性が確保された実装構造体2000が得られる。

【0134】

なお、本実施の形態の半田は、Sn(錫)系、Sn−Bi(ビスマス)系、Sn−In(インジウム)系、Sn−Bi−In系、Sn−Ag(銀)系、Sn−Cu(銅)系、Sn−Ag−Cu系、Sn−Ag−Bi系、Sn−Cu−Bi系、Sn−Ag−Cu−Bi系、Sn−Ag−In系、Sn−Cu−In系、Sn−Ag−Cu−In系、およびSn−Ag−Cu−Bi−In系などの所定の合金組成を有する合金を、単独で、またはいくつか組み合わせて混合物として利用することで構成されている。

【0135】

また、本実施の形態の樹脂は、ビスフェノール型エポキシ樹脂、多官能エポキシ樹脂、可撓性エポキシ樹脂、臭素化エポキシ樹脂、グリシジルエステル型エポキシ樹脂、および高分子型エポキシ樹脂などを、単独で、またはいくつか組み合わせて利用することで構成されている。より具体的には、上記のエポキシ樹脂は、ビスフェノールA型エポキシ樹脂、ビスフェノールF型エポキシ樹脂、ビスフェノールS型エポキシ樹脂、ビフェニル型エポキシ樹脂、ナフタレン型エポキシ樹脂、フェノールノボラック型エポキシ樹脂、およびクレゾールノボラック型エポキシ樹脂、ならびにこれらを変性させたエポキシ樹脂などを、単独で、またはいくつか組み合わせて利用することで構成されている。

【0136】

なお、導電性ペーストの使用環境および/または用途に応じ前述されたエポキシ樹脂と組み合わせて利用される硬化剤は、チオール系化合物、変性アミン系化合物、多官能フェノール系化合物、イミダゾール系化合物、および酸無水物系化合物などを、単独で、またはいくつか組み合わせて利用することで構成されている。

【0137】

また、必要に応じて利用される粘度調整/チクソ性付与添加剤は、無機系である、シリカ、およびアルミナ、ならびに有機系である、固形のエポキシ樹脂、低分子量のアマイド、ポリエステル系樹脂、およびヒマシ油の有機誘導体などを、単独で、またはいくつか組み合わせて利用することで構成されている。

【0138】

要するに、本実施の形態の導電性ペーストの組成については、多くの有用な変形例が考えられる。

【実施例】

【0139】

以下では、つぎの第一から第三の条件が全て満足されていれば、優れた耐衝撃性を確保できることが実験的に裏付けられている点について説明する。

【0140】

(1a)凸部の厚さは、ソルダレジストの厚さより、10μm以上40μm以下の範囲で大きい。

【0141】

(2a)凸部の長さは、電極辺の長さの80%以上120%以下である。

【0142】

(3a)凸部と電極辺との間の距離は、0mm以上0.7mm以下である。

【0143】

さらに、より厳しいつぎの第一から第三の条件が全て満足されていれば、より優れた耐衝撃性を確保することができることも、明らかになる。

【0144】

(1b)凸部の厚さは、ソルダレジストの厚さより、25μm以上の範囲で大きい。

【0145】

(2b)凸部の長さは、電極辺の長さの100%以上である。

【0146】

(3b)凸部と電極辺との間の距離は、0.3mm以下である。

【0147】

なお、凸部の厚さは、凸部が複数の材料で構成されている場合などには、全体的な厚さを部品下面の下側の空隙への樹脂の充填が抑制されるようにある程度は大きくすることが有意義である。

【0148】

もちろん、導電性ペースト塗布ステップにおけるメタルマスクの面と基板電極の電極表面との間に形成されるギャップが無視できなくなり、基板電極の上に塗布された導電性ペーストの印刷形状が悪化してしまう恐れがあるので、凸部の厚さが大きすぎることは前述の通り望ましくない。

【0149】

また、凸部の長さは、複数の凸部が設けられている場合などには、全体的な長さを部品下面の下側の空隙への樹脂の充填が抑制されるようにある程度は大きくすることが有意義である。

【0150】

もちろん、凸部が隣接する電子部品のランド部分に接触してしまう恐れがあるので、凸部の長さが大きすぎることは前述の通り望ましくない。

【0151】

たとえば、後述されるように、電極辺の長さは1.7mm程度であり、電子部品は3216サイズチップ部品であって隣接する電子部品の間の間隔は0.3〜0.5mm程度であるという具体例がある。このような具体例においては、凸部の各端部が電極辺の各端部よりも電極辺の長さの10%に相当する0.17(=1.7×10/100)mm程度だけ飛び出しているとしても、凸部は隣接する電子部品のランド部分に接触しない。要するに、凸部の長さが電極辺の長さの120(=100+10×2)%以下であれば、凸部が隣接する電子部品のランド部分に接触してしまう恐れはほとんどない。

【0152】

また、凸部と電極辺との間の距離は、凸部と電極辺それぞれとの間の距離が異なる場合などには、最大の距離を部品下面の下側の空隙への樹脂の充填が抑制されるようにある程度は小さくすることが有意義である。

【0153】

もちろん、基板電極の上に塗布された導電性ペーストの印刷形状が悪化し、導電性ペーストが電子部品と接触する面積が不十分になってしまう恐れがあるので、凸部が基板電極の電極表面に面接触することは前述の通り望ましくない。

【0154】

つぎに、図5〜17を主として参照しながら、実施例1〜8および比較例1〜5の実装構造体の構成について説明する。

【0155】

なお、図5〜17は、本発明における実施例1〜8および比較例1〜5の実装構造体の模式的な平面図である。

【0156】

ここに、図5〜17においては、電子部品1100(図1参照)などの図示が省略されている。

【0157】

はじめに、実施例1〜8および比較例1〜5に全て共通の事項について説明を行う。

【0158】

まず、電子部品1100(図1参照)は、3216サイズのチップ抵抗などの3216サイズチップ部品である。

【0159】

電子回路基板1200は、厚さ0.8mm程度のFR−4(Flame Retardant Type 4)基板を利用することで構成されている。

【0160】

電極辺1321および1322の長さ(L1およびL2)は、1.7mm程度である。

【0161】

より具体的には、基板電極1311および1312は同様な略直方体の形状を有し、電子回路基板1200の横の方向、すなわちX方向の、基板電極1311および1312の幅(W)は1.2mm程度であり、電子回路基板1200の奥行きの方向、すなわちY方向の、基板電極1311および1312の長さ(L=Li、i=1および2)は1.7mm程度である。

【0162】

そして、このように同様な略直方体の形状を有する基板電極1311と基板電極1312との間の距離(D)は、1.8mm程度である。

【0163】

ここで、導電性ペーストの組成について説明する。

【0164】

半田は、Sn58Bi半田を利用することで構成されている。

【0165】

エポキシ樹脂は、ビスフェノールF型エポキシ樹脂(商品名「エピコート806」、三菱化学製)を利用することで構成されている。

【0166】

硬化剤は、イミダゾール系硬化剤(商品名「キュアゾール2P4MZ」、四国化成製)を利用することで構成されている。

【0167】

粘度調整/チクソ性付与添加剤は、ヒマシ油系チクソ剤(商品名「THIXCIN R」、エレメンティス・ジャパン製)を利用することで構成されている。

【0168】

前述されたように、導電性ペーストは厚さ120μm程度のメタルマスクを用いるスクリーン印刷機を利用して基板電極1311および1312の上に塗布され、電子部品1100がチップマウンタを利用して塗布された導電性ペーストの上に載置され、電子回路基板1200がリフロー炉を利用して160℃で6分間加熱される。

【0169】

このようにして、半田接合と樹脂補強とが同時に行われる。

【0170】

つぎに、実施例1〜8および比較例1〜5にそれぞれ個別の事項について説明を行う。

【0171】

(実施例1)

図5を主として参照しながら、本実施例の実装構造体1000aの構成について説明する。

【0172】

凸部1510aは、レジスト表面1410aに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1520aと、シルクプリント1520aの−Z側にある厚さ30μm程度のソルダレジスト1400aと、で構成されている。

【0173】

したがって、凸部1510aの厚さは、ソルダレジスト1400aの厚さより、10μm程度大きい。

【0174】

ここに、シルクプリント1520aと、ソルダレジスト1400aと、の厚さを加算することで得られた、凸部1510aの全体的な厚さが考えられている(以下同様である)。

【0175】

実質的に平坦なソルダレジスト1400aのレジスト表面1410aと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0176】

凸部1510aの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0177】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1510aの幅(ω)は、1.2mm程度である。

【0178】

凸部1510aと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.3mm程度である。

【0179】

(実施例2)

図6を主として参照しながら、本実施例の実装構造体1000bの構成について説明する。

【0180】

凸部1511bおよび1512bは、それぞれ、レジスト表面1410bに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1521bおよび1522bと、シルクプリント1521bおよび1522bの−Z側にある厚さ30μm程度のソルダレジスト1400bと、で構成されている。

【0181】

実質的に平坦なソルダレジスト1400bのレジスト表面1410bと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0182】

凸部1511bおよび1512bそれぞれの長さ(λ1およびλ2)は、近接する電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0183】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1511bおよび1512bそれぞれの幅(ω1およびω2)は、0.5mm程度である。

【0184】

凸部1511bおよび1512bそれぞれと、近接する電極辺1321および1322それぞれと、の間の距離(δ1およびδ2)は、0.2mm程度である。

【0185】

(実施例3)

図7を主として参照しながら、本実施例の実装構造体2000aの構成について説明する。

【0186】

凸部2510aは、基板表面1210に形成された厚さ25μm程度の略直方体の形状を有する基板配線2520aと、基板配線2520aの+Z側にある厚さ30μm程度のソルダレジスト2400aと、で構成されている。

【0187】

基板表面1210に直接的に形成されている実質的に平坦なソルダレジスト2400aのレジスト表面2410aと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0188】

凸部2510aの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0189】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部2510aの幅(ω)は、1.2mm程度である。

【0190】

凸部2510aと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.3mm程度である。

【0191】

(実施例4)

図8を主として参照しながら、本実施例の実装構造体2000bの構成について説明する。

【0192】

凸部2511bおよび2512bは、それぞれ、基板表面1210に形成された厚さ25μm程度の略直方体の形状を有する基板配線2521bおよび2522bと、基板配線2521bおよび2522bの+Z側にある厚さ30μm程度のソルダレジスト2400bと、で構成されている。

【0193】

基板表面1210に直接的に形成されている実質的に平坦なソルダレジスト2400bのレジスト表面2410bと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0194】

凸部2511bおよび2512bそれぞれの長さ(λ1およびλ2)は、近接する電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0195】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部2511bおよび2512bそれぞれの幅(ω1およびω2)は、0.5mm程度である。

【0196】

凸部2511bおよび2512bそれぞれと、近接する電極辺1321および1322それぞれと、の間の距離(δ1およびδ2)は、0.2mm程度である。

【0197】

(実施例5)

図9を主として参照しながら、本実施例の実装構造体3000aの構成について説明する。

【0198】

凸部3510aは、レジスト表面3410aに形成された厚さ10〜15μm程度の略直方体の形状を有するシルクプリント3521aと、シルクプリント3521aの−Z側にあり、基板配線3522aの+Z側にある厚さ30μm程度のソルダレジスト3400aと、基板表面1210に形成された厚さ25〜30μm程度の略直方体の形状を有する基板配線3522aと、で構成されている。

【0199】

したがって、凸部3510aの厚さは、ソルダレジスト3400aの厚さより、35(=10+25)〜45(=15+30)μmの中間値である40μm程度大きい。

【0200】

ここに、前述されたように、凸部が複数の材料で構成されており、シルクプリント3521aと、ソルダレジスト3400aと、基板配線3522aと、の厚さを加算することで得られた、凸部3510aの全体的な厚さが考えられている。

【0201】

基板表面1210に直接的に形成されている実質的に平坦なソルダレジスト3400aのレジスト表面3410aと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0202】

凸部3510aの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0203】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部3510aの幅(ω)は、1.2mm程度である。

【0204】

凸部3510aと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.3mm程度である。

【0205】

(実施例6)

図10を主として参照しながら、本実施例の実装構造体1000cの構成について説明する。

【0206】

凸部1510cは、レジスト表面1410cに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1520cと、シルクプリント1520cの−Z側にある厚さ30μm程度のソルダレジスト1400cと、で構成されている。

【0207】

実質的に平坦なソルダレジスト1400cのレジスト表面1410cと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0208】

凸部1510cの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0209】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1510cの幅(ω)は、0.4mm程度である。

【0210】

凸部1510cと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.7mm程度である。

【0211】

(実施例7)

図11を主として参照しながら、本実施例の実装構造体1000dの構成について説明する。

【0212】

凸部1511d、1512d、1513dおよび1514dは、それぞれ、レジスト表面1410dに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1521d、1522d、1523dおよび1524dと、シルクプリント1521d、1522d、1523dおよび1524dの−Z側にある厚さ30μm程度のソルダレジスト1400dと、で構成されている。

【0213】

実質的に平坦なソルダレジスト1400dのレジスト表面1410dと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0214】

凸部1511d、1512d、1513dおよび1514dそれぞれの長さ(λ1、λ2、λ3およびλ4)は、近接する電極辺1321および1322それぞれの長さ(L1およびL2)の40%程度である。

【0215】

したがって、凸部1511d、1512d、1513dおよび1514dの長さは、電極辺1321および1322の長さ(L1およびL2)の80(=40+40)%程度である。

【0216】

ここに、複数の凸部が設けられており、凸部1511d、1512d、1513dおよび1514dの合併の、電極辺1321および1322それぞれへの射影の長さを算出することで得られた、凸部1511d、1512d、1513dおよび1514dの全体的な長さが考えられている。

【0217】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1511d、1512d、1513dおよび1514dそれぞれの幅(ω1、ω2、ω3およびω4)は、0.15mm程度である。

【0218】

凸部1511d、1512d、1513dおよび1514dそれぞれと、近接する電極辺1321および1322それぞれと、の間の距離(δ1、δ2、δ3およびδ4)は、0.7mm程度である。

【0219】

(実施例8)

図12を主として参照しながら、本実施例の実装構造体1000eの構成について説明する。

【0220】

凸部1511eおよび1512eは、それぞれ、レジスト表面1410eに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1521eおよび1522eと、シルクプリント1521eおよび1522eの−Z側にある厚さ30μm程度のソルダレジスト1400eと、で構成されている。

【0221】

実質的に平坦なソルダレジスト1400eのレジスト表面1410eと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0222】

凸部1511eおよび1512eそれぞれの長さ(λ1およびλ2)は、近接する電極辺1321および1322それぞれの長さ(L1およびL2)の80%程度である。

【0223】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1511eおよび1512eそれぞれの幅(ω1およびω2)は、0.15mm程度である。

【0224】

凸部1511eおよび1512eそれぞれと、近接する電極辺1321および1322それぞれと、の間の距離(δ1およびδ2)は、0.7mm程度である。

【0225】

(比較例1)

図13を主として参照しながら、本比較例の実装構造体4000aの構成について説明する。

【0226】

凸部が、実装構造体4000aにおいては設けられていない。

【0227】

実質的に平坦なソルダレジスト4400aのレジスト表面4410aと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0228】

(比較例2)

図14を主として参照しながら、本比較例の実装構造体1000fの構成について説明する。

【0229】

凸部1510fは、レジスト表面1410fに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1520fと、シルクプリント1520fの−Z側にある厚さ30μm程度のソルダレジスト1400fと、で構成されている。

【0230】

実質的に平坦なソルダレジスト1400fのレジスト表面1410fと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0231】

凸部1510fの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0232】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1510fの幅(ω)は、0.5mm程度である。

【0233】

凸部1510fと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、1.1mmおよび0.2mm程度である。

【0234】

したがって、凸部1510fと電極辺1321および1322との間の距離は、1.1(=Max(1.1,0.2))mm程度である。

【0235】

ここに、凸部と電極辺それぞれとの間の距離が異なっており、凸部1510fと電極辺1321および1322それぞれとの間の距離の最大値を算出することで得られた、凸部1510fと電極辺1321および1322それぞれとの間の最大の距離が考えられている。

【0236】

(比較例3)

図15を主として参照しながら、本比較例の実装構造体1000gの構成について説明する。

【0237】

凸部1510gは、レジスト表面1410gに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1520gと、シルクプリント1520gの−Z側にある厚さ30μm程度のソルダレジスト1400gと、で構成されている。

【0238】

実質的に平坦なソルダレジスト1400gのレジスト表面1410gと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0239】

凸部1510gの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0240】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1510gの幅(ω)は、0.2mm程度である。

【0241】

凸部1510gと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.8mm程度である。

【0242】

(比較例4)

図16を主として参照しながら、本比較例の実装構造体1000hの構成について説明する。

【0243】

凸部1510hは、レジスト表面1410hに形成された厚さ5μm程度の略直方体の形状を有するシルクプリント1520hと、シルクプリント1520hの−Z側にある厚さ30μm程度のソルダレジスト1400hと、で構成されている。

【0244】

実質的に平坦なソルダレジスト1400hのレジスト表面1410hと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0245】

凸部1510hの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0246】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1510hの幅(ω)は、1.2mm程度である。

【0247】

凸部1510hと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.3mm程度である。

【0248】

(比較例5)

図17を主として参照しながら、本比較例の実装構造体1000iの構成について説明する。

【0249】

凸部1511iおよび1512iは、それぞれ、レジスト表面1410iに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1521iおよび1522iと、シルクプリント1521iおよび1522iの−Z側にある厚さ30μm程度のソルダレジスト1400iと、で構成されている。

【0250】

実質的に平坦なソルダレジスト1400iのレジスト表面1410iと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0251】

凸部1511iおよび1512iそれぞれの長さ(λ1およびλ2)は、近接する電極辺1321および1322それぞれの長さ(L1およびL2)の70%程度である。

【0252】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1511iおよび1512iそれぞれの幅(ω1およびω2)は、0.15mm程度である。

【0253】

凸部1511iおよび1512iそれぞれと、近接する電極辺1321および1322それぞれと、の間の距離(δ1およびδ2)は、0.7mm程度である。

【0254】

これら実施例1〜8および比較例1〜5の実装構造体についての耐衝撃試験は、樹脂補強部の高さ、せん断強度および破壊落下回数を測定することで行われた。

【0255】

なお、上記の樹脂補強部の高さは、実装構造体の半田接合部の断面をSEM(Scanning Electron Microscope)を利用して観察し、実質的に平坦なソルダレジストのレジスト表面とほぼ同一面内にある基板電極の電極表面を基準として樹脂の半田接合部への濡れ上がり高さをつながっている部分ごとに測定することにより、測定された。

【0256】

また、上記のせん断強度は、電子部品の長手方向と垂直な方向から幅1.5mm程度のステンレス製のツールを利用して1mm/sec程度の速度でせん断力を与え、半田接合部が破壊したときの荷重を測定することにより、測定された。

【0257】

また、上記の破壊落下回数は、実装構造体を重さ110g程度の筐体に固定し、高さ1.5m程度の場所から自由落下させ、電子部品が剥離するまでの落下回数を測定することにより、測定された。

【0258】

さて、以下では、耐衝撃試験の結果について説明する。

【0259】

なお、図18は、本発明における実施例1〜8およびおよび比較例1〜5の実装構造体に対して行われた耐衝撃試験の結果を説明する説明図である。

【0260】

耐衝撃試験評価は、つぎのように定義される“×”、“△”、“○”および“◎”の四段階で与えられている。

【0261】

破壊落下回数が20回以下であるとき、耐衝撃試験評価は“×”である。

【0262】

破壊落下回数が21〜99回であるとき、耐衝撃試験評価は“△”である。

【0263】

破壊落下回数が100回以上であり、せん断強度が13kgf未満であるとき、耐衝撃試験評価は“○”である。

【0264】

破壊落下回数が100回以上であり、せん断強度が13kgf以上であるとき、耐衝撃試験評価は“○”である。

【0265】

耐衝撃試験評価が“◎”または“○”である実施例の実装構造体は、樹脂補強部の高さが0.1mm以上であって、破壊落下回数が100回以上であり、実際の製品への使用に好適であるといえる。

【0266】

さて、実施例1、2および6〜8については、上記の第一から第三の条件(1a)〜(3a)が全て満足されており、耐衝撃試験評価が“○”である。

【0267】

そして、実施例3〜5については、上記のより厳しいつぎの第一から第三の条件(1b)〜(3b)が全て満足されており、耐衝撃試験評価が“◎”である。

【0268】

つまり、これらの実施例においては、凸部が設けられていることによる効果が十分に発揮され、導電性ペーストが加熱された際に発生する毛細管現象による部品下面の下側の空隙への樹脂の充填がかなり抑制されるので、樹脂の半田接合部への濡れ上がり高さが確保されると分析される。

【0269】

もちろん、このような凸部が設けられていることによる効果は、部品および基板電極についての形状および配置などによらずに発揮される。

【0270】

そして、比較例1〜5については、第一から第三の条件が全ては満足されておらず、耐衝撃試験評価が“△”または“×”である。

【0271】

なお、比較例4については、凸部の厚さの、ソルダレジストの厚さとの差に関する第一の条件が満足されていない。

【0272】

また、比較例5については、凸部の長さの、電極辺の長さとの比に関する第二の条件が満足されていない。

【0273】

また、比較例2および3については、凸部と電極辺との間の距離に関する第三の条件が満足されていない。

【産業上の利用可能性】

【0274】

本発明における実装構造体、および実装構造体の製造方法は、落下などに起因する衝撃に対してのより優れた耐衝撃性を確保することが可能であり、たとえば電子部品を電子回路基板に実装するために有用である。

【符号の説明】

【0275】

1000 実装構造体

1100 電子部品

1110 部品下面

1200 電子回路基板

1210 基板表面

1220 部分

1311、1312 基板電極

1321、1322 電極辺

1400 ソルダレジスト

1410 レジスト表面

1510 凸部

1520 シルクプリント

1530 シルクプリント表面

1611、1612 半田接合部

1710 樹脂補強部

【技術分野】

【0001】

本発明は、電子部品を電子回路基板に実装するための、実装構造体、および実装構造体の製造方法に関するものである。

【背景技術】

【0002】

導電性フィラーを構成するための半田粒子からなる半田と、粘度の調整などを行うためのフラックス成分と、を含む組成物であるクリーム半田などの導電性ペーストが、電子部品を電子回路基板に実装するために利用されている。

【0003】

近年、電子部品のパッケージサイズは、微細化される傾向にある。

【0004】

そのため、電子部品が実装される電子回路基板の基板表面に形成された基板電極の上に塗布された導電性ペーストが電子部品と接触する面積は、小さくなってきている。

【0005】

よって、落下などに起因する衝撃に対しての耐衝撃性を確保することは、必ずしも容易ではない。

【0006】

そこで、半田と、フラックス成分と、に加えて、エポキシ樹脂などの補強用の樹脂を含む導電性ペーストの開発が、半田接合部を補強する目的で進められている(たとえば、特許文献1参照)。

【0007】

ここで、従来の実装構造体1000pの模式的な断面図である図19を参照しながら、従来の実装構造体1000pの構成、およびその製造方法について説明する。

【0008】

以下の説明においては、三次元空間の直交座標系を定めるための、互いに直交する三本の数直線であるX軸、Y軸およびZ軸が利用される。

【0009】

基板表面1210の全体にあらかじめ形成されていた回路パターン用の銅箔の内、回路パターンに対応する部分以外の部分が除去され、基板電極1311および1312などの回路パターンが基板表面1210に形成される。

【0010】

回路パターンが前述の通り形成された基板表面1210の全体に塗布されたソルダレジスト用のインキの内、基板電極1311および1312などに対応する部分が除去され、ソルダレジスト1400が同部分を除いて基板表面1210に形成される。

【0011】

半田と、フラックス成分と、樹脂と、を含む導電性ペーストが基板電極1311および1312の上に塗布され、電子部品1100が塗布された導電性ペーストの上に載置される。

【0012】

導電性ペーストが塗布され、電子部品1100が載置された電子回路基板1200は、加熱される。

【0013】

すると、樹脂は半田と分離し、半田と分離した樹脂は半田によって形成された半田接合部1611および1612を+Z方向に濡れ上がって硬化し、半田接合部1611および1612を覆う樹脂補強部1710pが形成される。

【0014】

このようにして、半田接合部1611および1612による半田接合と、樹脂補強部1710pによる樹脂補強と、が同時に行われ、落下などに起因する衝撃に対しての耐衝撃性が確保された実装構造体1000pが得られる。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開2010−77271号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

しかしながら、前述した従来の実装構造体1000pでは、要求される耐衝撃性を確保できない場合があることが判明した。

【0017】

すなわち、導電性ペーストが加熱され、補強用の樹脂が半田と分離すると、半田と分離した樹脂は電子部品1100の部品下面1110の下側の空隙に優先的に充填されてしまう。

【0018】

これは、加熱された樹脂はその粘度が低くなるために比較的に高い流動性をもち、毛細管現象が発生するからである。

【0019】

そして、実質的に平坦なソルダレジスト1400のレジスト表面1410と、部品下面1110と、の間の距離(d)が通常30〜100μm程度はある前述した空隙の体積、したがって同空隙に充填されてしまう樹脂の量は、無視できない程度に大きいことがある。

【0020】

すると、半田と分離した樹脂が半田接合部1611および1612を+Z方向に十分に濡れ上がることができず、形成された樹脂補強部1710pのZ方向の高さ(Hp)が半田接合部1611および1612に比較して小さくなってしまう。

【0021】

結果的に、要求される耐衝撃性を確保できる樹脂補強部1710pが形成されない場合が、あった。

【0022】

本発明は、上述した従来の課題を考慮し、落下などに起因する衝撃に対してのより優れた耐衝撃性を確保することが可能な、実装構造体、および実装構造体の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0023】

第1の本発明は、電子回路基板の基板表面に形成された少なくとも二つの基板電極と、

電子部品をそれぞれの前記基板電極に接合する半田接合部と、

前記半田接合部を覆う樹脂補強部と、

前記基板表面に形成されたソルダレジストと、

前記電子部品の下側にあり前記基板電極に挟まれた、前記基板表面の部分に形成された凸部と、

を備え、

前記基板表面に垂直な方向の前記凸部の厚さは、前記基板表面に垂直な前記方向の前記ソルダレジストの厚さより、10μm以上40μm以下の範囲で大きく、

前記基板電極の、前記基板表面の前記部分の側にある電極辺の方向の、前記凸部の長さは、前記電極辺の長さの80%以上120%以下であり、

前記凸部と前記電極辺との間の距離は、0mm以上0.7mm以下であり、

前記凸部は、前記基板電極の電極表面に面接触しないように形成されている、実装構造体である。

【0024】

第2の本発明は、前記凸部の材料は、前記ソルダレジストの材料と異なる、第1の本発明の実装構造体である。

【0025】

第3の本発明は、前記基板表面の前記部分に形成された基板配線を備え、

前記凸部は、前記基板配線と、前記基板配線の上に形成された前記ソルダレジストと、によって構成されている、第1の本発明の実装構造体である。

【0026】

第4の本発明は、前記凸部の前記厚さは、前記ソルダレジストの前記厚さより、25μm以上の範囲で大きく、

前記凸部の前記長さは、前記電極辺の前記長さの100%以上であり、

前記凸部と前記電極辺との間の前記距離は、0.3mm以下である、第1の本発明の実装構造体である。

【0027】

第5の本発明は、少なくとも二つの基板電極を、電子回路基板の基板表面に形成する基板電極形成ステップと、

ソルダレジストを、前記基板表面に形成するソルダレジスト形成ステップと、

所定の部材を、前記基板電極に挟まれた、前記ソルダレジストのレジスト表面に形成する部材形成ステップと、

半田と、フラックス成分と、樹脂と、を含む導電性ペーストを、前記基板電極の上に塗布する導電性ペースト塗布ステップと、

電子部品を、前記塗布された導電性ペーストの上に載置する電子部品載置ステップと、

前記基板電極と、前記ソルダレジストと、前記部材と、が形成され、前記導電性ペーストが塗布され、前記電子部品が載置された前記電子回路基板を加熱する加熱ステップと、

を備えた、実装構造体の製造方法である。

【発明の効果】

【0028】

本発明により、落下などに起因する衝撃に対してのより優れた耐衝撃性を確保することが可能な、実装構造体、および実装構造体の製造方法を提供することができる。

【図面の簡単な説明】

【0029】

【図1】本発明における実施の形態1の実装構造体の模式的な断面図

【図2】本発明における実施の形態1の実装構造体の模式的な平面図

【図3】本発明における実施の形態2の実装構造体の模式的な断面図

【図4】本発明における実施の形態2の実装構造体の模式的な平面図

【図5】本発明における実施例1の実装構造体の模式的な平面図

【図6】本発明における実施例2の実装構造体の模式的な平面図

【図7】本発明における実施例3の実装構造体の模式的な平面図

【図8】本発明における実施例4の実装構造体の模式的な平面図

【図9】本発明における実施例5の実装構造体の模式的な平面図

【図10】本発明における実施例6の実装構造体の模式的な平面図

【図11】本発明における実施例7の実装構造体の模式的な平面図

【図12】本発明における実施例8の実装構造体の模式的な平面図

【図13】本発明における比較例1の実装構造体の模式的な平面図

【図14】本発明における比較例2の実装構造体の模式的な平面図

【図15】本発明における比較例3の実装構造体の模式的な平面図

【図16】本発明における比較例4の実装構造体の模式的な平面図

【図17】本発明における比較例5の実装構造体の模式的な平面図

【図18】本発明における実施例1〜8およびおよび比較例1〜5の実装構造体に対して行われた耐衝撃試験の結果を説明する説明図

【図19】従来の実装構造体の模式的な断面図

【発明を実施するための形態】

【0030】

以下、図面を参照しながら、本発明における実施の形態について詳細に説明する。

【0031】

(実施の形態1)

はじめに、本発明における実施の形態1の実装構造体の模式的な断面図である図1、および本発明における実施の形態1の実装構造体の模式的な平面図である図2を主として参照しながら、本実施の形態の実装構造体1000の構成について説明する。

【0032】

ここに、図2においては、電子部品1100などの図示が省略されている。

【0033】

実装構造体1000は、少なくとも二つの基板電極1311および1312と、半田接合部1611および1612と、樹脂補強部1710と、ソルダレジスト1400と、凸部1510と、を備えている。

【0034】

以下では、実装構造体1000の構成についてより具体的に説明する。

【0035】

基板電極1311および1312は、電子回路基板1200の基板表面1210に形成されている。

【0036】

半田接合部1611および1612は、電子部品1100をそれぞれの基板電極1311および1312に接合している。

【0037】

ここに、電子部品1100は、チップ部品などである。

【0038】

樹脂補強部1710は、半田接合部1611および1612を覆っている。

【0039】

なお、基板表面1210に垂直な方向(Z方向)の樹脂補強部1710の高さ(H)は、実質的に0.1mm以上である。

【0040】

ここに、ソルダレジスト1400は基板表面1210に直接的に形成されているので、高さ(H)は実質的に平坦なソルダレジスト1400のレジスト表面1410を基準として定義されている。

【0041】

ソルダレジスト1400は、基板表面1210に形成されている。

【0042】

ソルダレジスト1400は、後述の通りソルダレジスト用のインキを利用して形成された厚さ(T)30μm程度のレジストである。

【0043】

凸部1510は、電子部品1100の下側(−Z側)にあり基板電極1311および1312に挟まれた、基板表面1210の部分1220に形成されている。

【0044】

もちろん、後述されるように、凸部1510の長さ(λ)が電極辺1321および1322の長さ(L1およびL2)より大きい場合もあり、そのような場合には凸部1510の端部は電極辺1321および/または1322の端部よりも飛び出す。

【0045】

基板表面1210に垂直な方向(Z方向)の凸部1510の厚さ(τ)は、基板表面1210に垂直な方向(Z方向)のソルダレジスト1400の厚さ(T)より、実質的に10μm以上40μm以下の範囲で大きい。

【0046】

ここに、厚さτは、基板表面1210を基準として定義されている。

【0047】

より具体的には、凸部1510は、後述の通りシルクプリント用のインキを利用してレジスト表面1410に形成された厚さ(τ−T>0)10〜40μm程度の略直方体の形状を有するシルクプリント1520と、シルクプリント1520の−Z側にある厚さ(T)30μm程度のソルダレジスト1400と、で構成されている。

【0048】

したがって、シルクプリント1520のシルクプリント表面1530と、電子部品1100の部品下面1110と、の間のZ方向のギャップ(g)は、実質的に平坦なソルダレジスト1400のレジスト表面1410と、部品下面1110と、の間の距離(d)が40μm程度であれば、大きくても30μm程度しかない。

【0049】

ここに、凸部1510の厚さ(τ)とソルダレジスト1400の厚さ(T)との差(τ−T>0)が10μmより小さいと、部品下面1110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0050】

そして、凸部1510の厚さ(τ)とソルダレジスト1400の厚さ(T)との差(τ−T>0)が40μmより大きいと、導電性ペースト塗布ステップにおけるメタルマスクの面と基板電極1311および1312の電極表面との間に形成されるギャップが無視できなくなり、基板電極1311および1312の上に塗布された導電性ペーストの印刷形状が悪化してしまう恐れがある。

【0051】

なお、凸部1510の材料は、ソルダレジスト1400の材料と異なっているが、ソルダレジスト1400の材料と同じであってもよい。

【0052】

もちろん、凸部1510がシルクプリント1520と、ソルダレジスト1400と、で前述の通り構成されているので、凸部1510の材料は、シルクプリント1520の材料とソルダレジスト1400の材料とが異なっていれば、ソルダレジスト1400の材料と異なっていることになる。

【0053】

基板電極1311および1312の、基板表面1210の部分1220の側にある電極辺1321および1322の方向(Y方向)の、凸部1510の長さ(λ)は、電極辺1321および1322の長さ(L1およびL2)の実質的に80%以上120%以下である。

【0054】

もちろん、L1およびL2のように添数が異なる量は、以下の説明では特に断らない限り等しいが、必ずしも等しくなくてもよい(その他の量についても同様である)。

【0055】

ここに、凸部1510の長さ(λ)が電極辺1321および1322の長さ(L1およびL2)の80%より小さいと、部品下面1110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0056】

そして、凸部1510の長さ(λ)が電極辺1321および1322の長さ(L1およびL2)の120%より大きいと、凸部1510が隣接する電子部品(図示省略)のランド部分に接触してしまう恐れがある。

【0057】

凸部1510と電極辺1321および1322との間の距離(δ1およびδ2)は、実質的に0mm以上0.7mm以下である。

【0058】

凸部1510は、基板電極1311および1312の電極表面に面接触しないように形成されている。

【0059】

ここに、凸部1510と電極辺1321および1322との間の距離(δ1およびδ2)が0.7mmより大きいと、部品下面1110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0060】

もちろん、凸部1510が基板電極1311および1312の電極表面に面接触していないので、基板電極1311および1312の上に塗布された導電性ペーストの印刷形状が悪化し、導電性ペーストが電子部品1100と接触する面積が不十分になってしまう恐れはほとんどない。

【0061】

つぎに、図1および2を主として参照しながら、実装構造体1000の製造方法について説明する。

【0062】

以下では、基板電極形成ステップと、ソルダレジスト形成ステップと、シルクプリント形成ステップと、導電性ペースト塗布ステップと、電子部品載置ステップと、加熱ステップと、についてこの順番で具体的に説明する。

【0063】

もちろん、上記のステップは必ずしもこの順番で行われなくてもよく、たとえば、導電性ペースト塗布ステップはシルクプリント形成ステップが行われた後で行われてもよい。

【0064】

(基板電極形成ステップ)

少なくとも二つの基板電極1311および1312が、電子回路基板1200の基板表面1210に形成される。

【0065】

より具体的には、基板表面1210の全体にあらかじめ形成されていた回路パターン用の銅箔の内、回路パターンに対応する部分以外の部分がフォトリソグラフィなどにより除去され、基板電極1311および1312などの回路パターンが基板表面1210に形成される。

【0066】

(ソルダレジスト形成ステップ)

ソルダレジスト1400が、基板表面1210に形成される。

【0067】

より具体的には、回路パターンが前述の通り形成された基板表面1210の全体に塗布されたアクリル系またはエポキシアクレート系などの樹脂であるソルダレジスト用のインキの内、基板電極1311および1312などに対応する部分がフォトリソグラフィなどにより除去され、ソルダレジスト1400が同部分を除いて基板表面1210に厚さ(T)30μm程度のレジストとして形成される。

【0068】

もちろん、ソルダレジスト1400は、基板電極1311および1312などに対応する部分を少なくとも除いて基板表面1210に形成されていればよく、たとえば、基板電極1311および1312などに対応する部分およびその周辺の狭小部分を除いて基板表面1210に形成されていてもよい。

【0069】

(シルクプリント形成ステップ)

シルクプリント1520が、基板電極1311および1312に挟まれた、ソルダレジスト1400のレジスト表面1410に形成される。

【0070】

より具体的には、アクリル系またはエポキシアクレート系などの樹脂であるシルクプリント用のインキがスクリーン印刷法などにより塗布され、シルクプリント1520が厚さ(τ−T>0)10〜40μm程度のプリントとして形成される。

【0071】

(導電性ペースト塗布ステップ)

半田と、フラックス成分と、樹脂と、を含む導電性ペーストが、基板電極1311および1312の上に塗布される。

【0072】

より具体的には、導電性ペーストは、開口が基板電極1311および1312などの電極サイズに応じて形成された厚さ120μm程度のメタルマスクを用いるスクリーン印刷機を利用して、スクリーン印刷法などにより塗布される。

【0073】

(電子部品載置ステップ)

電子部品1100が、塗布された導電性ペーストの上に載置される。

【0074】

より具体的には、電子部品1100は、チップマウンタを利用して、導電性ペーストの上に載置される。

【0075】

(加熱ステップ)

基板電極1311および1312と、ソルダレジスト1400と、シルクプリント1520と、が形成され、導電性ペーストが塗布され、電子部品1100が載置された電子回路基板1200が、加熱される。

【0076】

より具体的には、導電性ペーストが塗布され、電子部品1100が載置された電子回路基板1200は、リフロー炉を利用して半田の融点以上である160℃で6分間加熱される。

【0077】

すると、樹脂は半田と分離し、半田と分離した樹脂は半田によって形成された半田接合部1611および1612を+Z方向に濡れ上がって硬化し、半田接合部1611および1612を覆う樹脂補強部1710が形成される。

【0078】

前述されたように、シルクプリント表面1530と部品下面1110との間のZ方向のギャップ(g)は大きくても30μm程度しかないので、部品下面1110の下側の空隙に充填されてしまう樹脂の量はそれほど多くない。

【0079】

したがって、樹脂が半田接合部1611および1612を+Z方向に十分に濡れ上がることができ、形成された樹脂補強部1710のZ方向の高さ(H)が半田接合部1611および1612に比較して小さくなる恐れはほとんどない。

【0080】

このようにして、半田接合部1611および1612による半田接合と、樹脂補強部1710による樹脂補強と、が同時に行われ、落下などに起因する衝撃に対しての耐衝撃性が確保された実装構造体1000が得られる。

【0081】

(実施の形態2)

つぎに、本発明における実施の形態2の実装構造体の模式的な断面図である図3、および本発明における実施の形態2の実装構造体の模式的な平面図である図4を主として参照しながら、本実施の形態の実装構造体2000の構成について説明する。

【0082】

ここに、図4においては、電子部品2100などの図示が省略されている。

【0083】

実装構造体2000は、少なくとも二つの基板電極1311および1312と、半田接合部2611および2612と、樹脂補強部2711および2712と、ソルダレジスト2400と、凸部2511および2512と、を備えている。

【0084】

実装構造体2000の構成は、前述の実装構造体1000の構成とつぎのような点で異なっている。

【0085】

実装構造体2000は、基板表面1210の部分1220に形成された基板配線2521および2522を備えている。

【0086】

凸部2511および2512は、基板配線2521および2522と、基板配線2521および2522の上に形成されたソルダレジスト2400と、によって構成されている。

【0087】

ここに、基板配線2521および2522は、Cu(銅)配線などである。

【0088】

以下では、実装構造体2000の構成についてより具体的に説明する。

【0089】

基板電極1311および1312は、電子回路基板1200の基板表面1210に形成されている。

【0090】

半田接合部2611および2612は、電子部品2100をそれぞれの基板電極1311および1312に接合している。

【0091】

ここに、電子部品2100は、基板電極1311および1312に接合された部品電極2111および2112などを有するSON(Small Outline No−lead)部品などである。

【0092】

樹脂補強部2711および2712は、半田接合部2611および2612を覆っている。

【0093】

もちろん、樹脂補強部2711および2712は、たとえば電子部品2100の−Z側で一つにつながっていてもよい。

【0094】

なお、基板表面1210に垂直な方向(Z方向)の樹脂補強部2711および2712の高さ(H1およびH2)は、実質的に0.1mm以上である。

【0095】

ここに、ソルダレジスト2400の一部は基板表面1210に直接的にではなく前述の通り基板配線2521および2522の上に形成されているので、高さ(H1およびH2)は基板表面1210に直接的に形成されている実質的に平坦なソルダレジスト2400のレジスト表面2410を基準として定義されている。

【0096】

ソルダレジスト2400は、基板表面1210に形成されている。

【0097】

ソルダレジスト2400は、後述の通りソルダレジスト用のインキを利用して形成された厚さ(T)30μm程度のレジストである。

【0098】

凸部2511および2512は、電子部品2100の下側(−Z側)にあり基板電極1311および1312に挟まれた、基板表面1210の部分1220に形成されている。

【0099】

もちろん、後述されるように、凸部2511および2512の長さ(λ1およびλ2)が電極辺1321および1322の長さ(L1およびL2)より大きい場合もあり、そのような場合には凸部2511および2512の端部は電極辺1321および/または1322の端部よりも飛び出す。

【0100】

そして、後述されるように、凸部2511および2512はソルダレジスト形成ステップにおいて自然に形成されるので、ソルダレジスト2400は実質的に平坦なソルダレジスト2400のレジスト表面2410から見て基板配線2521および2522の周辺の狭小部分で盛り上がる場合が多く、そのような場合には凸部2511および2512は同狭小部分に相当する部分だけやや大きくなる。

【0101】

基板表面1210に垂直な方向(Z方向)の凸部2511および2512の厚さ(τ1およびτ2)は、基板表面1210に垂直な方向(Z方向)のソルダレジスト2400の厚さ(T)より、実質的に10μm以上40μm以下の範囲で大きい。

【0102】

ここに、厚さτ1およびτ2は、基板表面1210を基準として定義されている。

【0103】

より具体的には、凸部2511および2512は、前述の通り基板表面1210に形成された厚さ(τi−T>0、i=1および2)25μm程度の略直方体の形状を有する基板配線2521および2522と、基板配線2521および2522の+Z側にある厚さ(T)30μm程度のソルダレジスト2400と、で構成されている。

【0104】

したがって、基板配線2521および2522の上に形成されているソルダレジスト2400のレジスト表面2410と、電子部品2100の部品下面2110と、の間のZ方向のギャップ(g)は、基板表面1210に直接的に形成されている実質的に平坦なソルダレジスト2400のレジスト表面2410と、部品下面2110と、の間の距離(d)が40μm程度であれば、大きくても15μm程度しかない。

【0105】

このように比較的に厚い基板配線2521および2522が基板電極1311および1312のかなり近くに設けられている場合などには、製造時に加熱された樹脂が部品下面2110の下側の空隙にまで達しないので、樹脂補強部2711および2712が一つにつながることさえない。

【0106】

ここに、凸部2511および2512の厚さ(τ1およびτ2)とソルダレジスト2400の厚さ(T)との差(τ−T>0)が10μmより小さいと、部品下面2110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0107】

そして、凸部2511および2512の厚さ(τ1およびτ2)とソルダレジスト2400の厚さ(T)との差(τ−T>0)が40μmより大きいと、導電性ペースト塗布ステップにおけるメタルマスクの面と基板電極1311および1312の電極表面との間に形成されるギャップが無視できなくなり、基板電極1311および1312の上に塗布された導電性ペーストの印刷形状が悪化してしまう恐れがある。

【0108】

基板電極1311および1312の、基板表面1210の部分1220の側にある電極辺1321および1322の方向(Y方向)の、凸部2511および2512の長さ(λ1およびλ2)は、電極辺1321および1322の長さ(L1およびL2)の実質的に80%以上120%以下である。

【0109】

ここに、凸部2511および2512の長さ(λ1およびλ2)が電極辺1321および1322の長さ(L1およびL2)の80%より小さいと、部品下面2110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0110】

そして、凸部2511および2512の長さ(λ1およびλ2)が電極辺1321および1322の長さ(L1およびL2)の120%より大きいと、凸部2511および2512が隣接する電子部品(図示省略)のランド部分に接触してしまう恐れがある。

【0111】

凸部2511および2512と電極辺1321および1322との間の距離(δ1およびδ2)は、実質的に0mm以上0.7mm以下である。

【0112】

凸部2511および2512は、基板電極1311および1312の電極表面に面接触しないように形成されている。

【0113】

ここに、凸部2511および2512と電極辺1321および1322との間の距離(δ1およびδ2)が0.7mmより大きいと、部品下面2110の下側の空隙への樹脂の浸透を十分に抑制できない恐れがある。

【0114】

もちろん、凸部2511および2512が基板電極1311および1312の電極表面に面接触していないので、基板電極1311および1312の上に塗布された導電性ペーストの印刷形状が悪化し、導電性ペーストが電子部品2100と接触する面積が不十分になってしまう恐れはほとんどない。

【0115】

つぎに、図3および4を主として参照しながら、実装構造体2000の製造方法について説明する。

【0116】

以下では、基板電極形成ステップと、ソルダレジスト形成ステップと、導電性ペースト塗布ステップと、電子部品載置ステップと、加熱ステップと、についてこの順番で具体的に説明する。

【0117】

(基板電極形成ステップ)

少なくとも二つの基板電極1311および1312が、電子回路基板1200の基板表面1210に形成される。

【0118】

より具体的には、基板表面1210の全体にあらかじめ形成されていた回路パターン用の銅箔の内、回路パターンに対応する部分以外の部分がフォトリソグラフィなどにより除去され、基板電極1311および1312、ならびに基板配線2521および2522などの回路パターンが基板表面1210に形成される。

【0119】

(ソルダレジスト形成ステップ)

ソルダレジスト2400が、基板表面1210に形成される。

【0120】

より具体的には、回路パターンが前述の通り形成された基板表面1210の全体に塗布されたアクリル系またはエポキシアクレート系などの樹脂であるソルダレジスト用のインキの内、基板電極1311および1312などに対応する部分がフォトリソグラフィなどにより除去され、ソルダレジスト2400が同部分を除いて基板表面1210に厚さ(T)30μm程度のレジストとして形成される。

【0121】

そして、凸部2511および2512が、前述の通り基板表面1210に形成された厚さ(τi−T>0、i=1および2)25μm程度の基板配線2521および2522に対応するレジスト表面2410の突起物として形成される。

【0122】

もちろん、ソルダレジスト2400は、基板電極1311および1312などに対応する部分を少なくとも除いて基板表面1210に形成されていればよく、たとえば、基板電極1311および1312などに対応する部分およびその周辺の狭小部分を除いて基板表面1210に形成されていてもよい。

【0123】

(導電性ペースト塗布ステップ)

半田と、フラックス成分と、樹脂と、を含む導電性ペーストが、基板電極1311および1312の上に塗布される。

【0124】

より具体的には、導電性ペーストは、開口が基板電極1311および1312などの電極サイズに応じて形成された厚さ120μm程度のメタルマスクを用いるスクリーン印刷機を利用して、スクリーン印刷法などにより塗布される。

【0125】

(電子部品載置ステップ)

電子部品2100が、塗布された導電性ペーストの上に載置される。

【0126】

より具体的には、電子部品2100は、チップマウンタを利用して、導電性ペーストの上に載置される。

【0127】

(加熱ステップ)

基板電極1311および1312と、ソルダレジスト2400と、が形成され、導電性ペーストが塗布され、電子部品2100が載置された電子回路基板1200が、加熱される。

【0128】

より具体的には、導電性ペーストが塗布され、電子部品2100が載置された電子回路基板1200は、リフロー炉を利用して半田の融点以上である160℃で6分間加熱される。

【0129】

すると、樹脂は半田と分離し、半田と分離した樹脂は半田によって形成された半田接合部2611および2612を+Z方向に濡れ上がって硬化し、半田接合部2611および2612を覆う樹脂補強部2711および2712が形成される。

【0130】

前述されたように、基板配線2521および2522の上に形成されているソルダレジスト2400のレジスト表面2410と、部品下面2110と、の間のZ方向のギャップ(g)は大きくても15μm程度しかないので、部品下面2110の下側の空隙に充填されてしまう樹脂の量はそれほど多くない。

【0131】

さらに、比較的に厚い基板配線2521および2522が基板電極1311および1312のかなり近くに設けられている場合などには、加熱された樹脂が部品下面2110の下側の空隙にまで達しないので、充填されてしまう樹脂の量は無視できる程度に小さく、樹脂補強部2711および2712が一つにつながることさえない。

【0132】

したがって、樹脂が半田接合部2611および2612を+Z方向に十分に濡れ上がることができ、形成された樹脂補強部2711および2712のZ方向の高さ(H1およびH2)が半田接合部2611および2612に比較して小さくなる恐れはほとんどない。

【0133】

このようにして、半田接合部2611および2612による半田接合と、樹脂補強部2711および2712による樹脂補強と、が同時に行われ、落下などに起因する衝撃に対しての耐衝撃性が確保された実装構造体2000が得られる。

【0134】

なお、本実施の形態の半田は、Sn(錫)系、Sn−Bi(ビスマス)系、Sn−In(インジウム)系、Sn−Bi−In系、Sn−Ag(銀)系、Sn−Cu(銅)系、Sn−Ag−Cu系、Sn−Ag−Bi系、Sn−Cu−Bi系、Sn−Ag−Cu−Bi系、Sn−Ag−In系、Sn−Cu−In系、Sn−Ag−Cu−In系、およびSn−Ag−Cu−Bi−In系などの所定の合金組成を有する合金を、単独で、またはいくつか組み合わせて混合物として利用することで構成されている。

【0135】

また、本実施の形態の樹脂は、ビスフェノール型エポキシ樹脂、多官能エポキシ樹脂、可撓性エポキシ樹脂、臭素化エポキシ樹脂、グリシジルエステル型エポキシ樹脂、および高分子型エポキシ樹脂などを、単独で、またはいくつか組み合わせて利用することで構成されている。より具体的には、上記のエポキシ樹脂は、ビスフェノールA型エポキシ樹脂、ビスフェノールF型エポキシ樹脂、ビスフェノールS型エポキシ樹脂、ビフェニル型エポキシ樹脂、ナフタレン型エポキシ樹脂、フェノールノボラック型エポキシ樹脂、およびクレゾールノボラック型エポキシ樹脂、ならびにこれらを変性させたエポキシ樹脂などを、単独で、またはいくつか組み合わせて利用することで構成されている。

【0136】

なお、導電性ペーストの使用環境および/または用途に応じ前述されたエポキシ樹脂と組み合わせて利用される硬化剤は、チオール系化合物、変性アミン系化合物、多官能フェノール系化合物、イミダゾール系化合物、および酸無水物系化合物などを、単独で、またはいくつか組み合わせて利用することで構成されている。

【0137】

また、必要に応じて利用される粘度調整/チクソ性付与添加剤は、無機系である、シリカ、およびアルミナ、ならびに有機系である、固形のエポキシ樹脂、低分子量のアマイド、ポリエステル系樹脂、およびヒマシ油の有機誘導体などを、単独で、またはいくつか組み合わせて利用することで構成されている。

【0138】

要するに、本実施の形態の導電性ペーストの組成については、多くの有用な変形例が考えられる。

【実施例】

【0139】

以下では、つぎの第一から第三の条件が全て満足されていれば、優れた耐衝撃性を確保できることが実験的に裏付けられている点について説明する。

【0140】

(1a)凸部の厚さは、ソルダレジストの厚さより、10μm以上40μm以下の範囲で大きい。

【0141】

(2a)凸部の長さは、電極辺の長さの80%以上120%以下である。

【0142】

(3a)凸部と電極辺との間の距離は、0mm以上0.7mm以下である。

【0143】

さらに、より厳しいつぎの第一から第三の条件が全て満足されていれば、より優れた耐衝撃性を確保することができることも、明らかになる。

【0144】

(1b)凸部の厚さは、ソルダレジストの厚さより、25μm以上の範囲で大きい。

【0145】

(2b)凸部の長さは、電極辺の長さの100%以上である。

【0146】

(3b)凸部と電極辺との間の距離は、0.3mm以下である。

【0147】

なお、凸部の厚さは、凸部が複数の材料で構成されている場合などには、全体的な厚さを部品下面の下側の空隙への樹脂の充填が抑制されるようにある程度は大きくすることが有意義である。

【0148】

もちろん、導電性ペースト塗布ステップにおけるメタルマスクの面と基板電極の電極表面との間に形成されるギャップが無視できなくなり、基板電極の上に塗布された導電性ペーストの印刷形状が悪化してしまう恐れがあるので、凸部の厚さが大きすぎることは前述の通り望ましくない。

【0149】

また、凸部の長さは、複数の凸部が設けられている場合などには、全体的な長さを部品下面の下側の空隙への樹脂の充填が抑制されるようにある程度は大きくすることが有意義である。

【0150】

もちろん、凸部が隣接する電子部品のランド部分に接触してしまう恐れがあるので、凸部の長さが大きすぎることは前述の通り望ましくない。

【0151】

たとえば、後述されるように、電極辺の長さは1.7mm程度であり、電子部品は3216サイズチップ部品であって隣接する電子部品の間の間隔は0.3〜0.5mm程度であるという具体例がある。このような具体例においては、凸部の各端部が電極辺の各端部よりも電極辺の長さの10%に相当する0.17(=1.7×10/100)mm程度だけ飛び出しているとしても、凸部は隣接する電子部品のランド部分に接触しない。要するに、凸部の長さが電極辺の長さの120(=100+10×2)%以下であれば、凸部が隣接する電子部品のランド部分に接触してしまう恐れはほとんどない。

【0152】

また、凸部と電極辺との間の距離は、凸部と電極辺それぞれとの間の距離が異なる場合などには、最大の距離を部品下面の下側の空隙への樹脂の充填が抑制されるようにある程度は小さくすることが有意義である。

【0153】

もちろん、基板電極の上に塗布された導電性ペーストの印刷形状が悪化し、導電性ペーストが電子部品と接触する面積が不十分になってしまう恐れがあるので、凸部が基板電極の電極表面に面接触することは前述の通り望ましくない。

【0154】

つぎに、図5〜17を主として参照しながら、実施例1〜8および比較例1〜5の実装構造体の構成について説明する。

【0155】

なお、図5〜17は、本発明における実施例1〜8および比較例1〜5の実装構造体の模式的な平面図である。

【0156】

ここに、図5〜17においては、電子部品1100(図1参照)などの図示が省略されている。

【0157】

はじめに、実施例1〜8および比較例1〜5に全て共通の事項について説明を行う。

【0158】

まず、電子部品1100(図1参照)は、3216サイズのチップ抵抗などの3216サイズチップ部品である。

【0159】

電子回路基板1200は、厚さ0.8mm程度のFR−4(Flame Retardant Type 4)基板を利用することで構成されている。

【0160】

電極辺1321および1322の長さ(L1およびL2)は、1.7mm程度である。

【0161】

より具体的には、基板電極1311および1312は同様な略直方体の形状を有し、電子回路基板1200の横の方向、すなわちX方向の、基板電極1311および1312の幅(W)は1.2mm程度であり、電子回路基板1200の奥行きの方向、すなわちY方向の、基板電極1311および1312の長さ(L=Li、i=1および2)は1.7mm程度である。

【0162】

そして、このように同様な略直方体の形状を有する基板電極1311と基板電極1312との間の距離(D)は、1.8mm程度である。

【0163】

ここで、導電性ペーストの組成について説明する。

【0164】

半田は、Sn58Bi半田を利用することで構成されている。

【0165】

エポキシ樹脂は、ビスフェノールF型エポキシ樹脂(商品名「エピコート806」、三菱化学製)を利用することで構成されている。

【0166】

硬化剤は、イミダゾール系硬化剤(商品名「キュアゾール2P4MZ」、四国化成製)を利用することで構成されている。

【0167】

粘度調整/チクソ性付与添加剤は、ヒマシ油系チクソ剤(商品名「THIXCIN R」、エレメンティス・ジャパン製)を利用することで構成されている。

【0168】

前述されたように、導電性ペーストは厚さ120μm程度のメタルマスクを用いるスクリーン印刷機を利用して基板電極1311および1312の上に塗布され、電子部品1100がチップマウンタを利用して塗布された導電性ペーストの上に載置され、電子回路基板1200がリフロー炉を利用して160℃で6分間加熱される。

【0169】

このようにして、半田接合と樹脂補強とが同時に行われる。

【0170】

つぎに、実施例1〜8および比較例1〜5にそれぞれ個別の事項について説明を行う。

【0171】

(実施例1)

図5を主として参照しながら、本実施例の実装構造体1000aの構成について説明する。

【0172】

凸部1510aは、レジスト表面1410aに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1520aと、シルクプリント1520aの−Z側にある厚さ30μm程度のソルダレジスト1400aと、で構成されている。

【0173】

したがって、凸部1510aの厚さは、ソルダレジスト1400aの厚さより、10μm程度大きい。

【0174】

ここに、シルクプリント1520aと、ソルダレジスト1400aと、の厚さを加算することで得られた、凸部1510aの全体的な厚さが考えられている(以下同様である)。

【0175】

実質的に平坦なソルダレジスト1400aのレジスト表面1410aと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0176】

凸部1510aの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0177】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1510aの幅(ω)は、1.2mm程度である。

【0178】

凸部1510aと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.3mm程度である。

【0179】

(実施例2)

図6を主として参照しながら、本実施例の実装構造体1000bの構成について説明する。

【0180】

凸部1511bおよび1512bは、それぞれ、レジスト表面1410bに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1521bおよび1522bと、シルクプリント1521bおよび1522bの−Z側にある厚さ30μm程度のソルダレジスト1400bと、で構成されている。

【0181】

実質的に平坦なソルダレジスト1400bのレジスト表面1410bと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0182】

凸部1511bおよび1512bそれぞれの長さ(λ1およびλ2)は、近接する電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0183】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1511bおよび1512bそれぞれの幅(ω1およびω2)は、0.5mm程度である。

【0184】

凸部1511bおよび1512bそれぞれと、近接する電極辺1321および1322それぞれと、の間の距離(δ1およびδ2)は、0.2mm程度である。

【0185】

(実施例3)

図7を主として参照しながら、本実施例の実装構造体2000aの構成について説明する。

【0186】

凸部2510aは、基板表面1210に形成された厚さ25μm程度の略直方体の形状を有する基板配線2520aと、基板配線2520aの+Z側にある厚さ30μm程度のソルダレジスト2400aと、で構成されている。

【0187】

基板表面1210に直接的に形成されている実質的に平坦なソルダレジスト2400aのレジスト表面2410aと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0188】

凸部2510aの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0189】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部2510aの幅(ω)は、1.2mm程度である。

【0190】

凸部2510aと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.3mm程度である。

【0191】

(実施例4)

図8を主として参照しながら、本実施例の実装構造体2000bの構成について説明する。

【0192】

凸部2511bおよび2512bは、それぞれ、基板表面1210に形成された厚さ25μm程度の略直方体の形状を有する基板配線2521bおよび2522bと、基板配線2521bおよび2522bの+Z側にある厚さ30μm程度のソルダレジスト2400bと、で構成されている。

【0193】

基板表面1210に直接的に形成されている実質的に平坦なソルダレジスト2400bのレジスト表面2410bと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0194】

凸部2511bおよび2512bそれぞれの長さ(λ1およびλ2)は、近接する電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0195】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部2511bおよび2512bそれぞれの幅(ω1およびω2)は、0.5mm程度である。

【0196】

凸部2511bおよび2512bそれぞれと、近接する電極辺1321および1322それぞれと、の間の距離(δ1およびδ2)は、0.2mm程度である。

【0197】

(実施例5)

図9を主として参照しながら、本実施例の実装構造体3000aの構成について説明する。

【0198】

凸部3510aは、レジスト表面3410aに形成された厚さ10〜15μm程度の略直方体の形状を有するシルクプリント3521aと、シルクプリント3521aの−Z側にあり、基板配線3522aの+Z側にある厚さ30μm程度のソルダレジスト3400aと、基板表面1210に形成された厚さ25〜30μm程度の略直方体の形状を有する基板配線3522aと、で構成されている。

【0199】

したがって、凸部3510aの厚さは、ソルダレジスト3400aの厚さより、35(=10+25)〜45(=15+30)μmの中間値である40μm程度大きい。

【0200】

ここに、前述されたように、凸部が複数の材料で構成されており、シルクプリント3521aと、ソルダレジスト3400aと、基板配線3522aと、の厚さを加算することで得られた、凸部3510aの全体的な厚さが考えられている。

【0201】

基板表面1210に直接的に形成されている実質的に平坦なソルダレジスト3400aのレジスト表面3410aと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0202】

凸部3510aの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0203】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部3510aの幅(ω)は、1.2mm程度である。

【0204】

凸部3510aと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.3mm程度である。

【0205】

(実施例6)

図10を主として参照しながら、本実施例の実装構造体1000cの構成について説明する。

【0206】

凸部1510cは、レジスト表面1410cに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1520cと、シルクプリント1520cの−Z側にある厚さ30μm程度のソルダレジスト1400cと、で構成されている。

【0207】

実質的に平坦なソルダレジスト1400cのレジスト表面1410cと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0208】

凸部1510cの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0209】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1510cの幅(ω)は、0.4mm程度である。

【0210】

凸部1510cと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.7mm程度である。

【0211】

(実施例7)

図11を主として参照しながら、本実施例の実装構造体1000dの構成について説明する。

【0212】

凸部1511d、1512d、1513dおよび1514dは、それぞれ、レジスト表面1410dに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1521d、1522d、1523dおよび1524dと、シルクプリント1521d、1522d、1523dおよび1524dの−Z側にある厚さ30μm程度のソルダレジスト1400dと、で構成されている。

【0213】

実質的に平坦なソルダレジスト1400dのレジスト表面1410dと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0214】

凸部1511d、1512d、1513dおよび1514dそれぞれの長さ(λ1、λ2、λ3およびλ4)は、近接する電極辺1321および1322それぞれの長さ(L1およびL2)の40%程度である。

【0215】

したがって、凸部1511d、1512d、1513dおよび1514dの長さは、電極辺1321および1322の長さ(L1およびL2)の80(=40+40)%程度である。

【0216】

ここに、複数の凸部が設けられており、凸部1511d、1512d、1513dおよび1514dの合併の、電極辺1321および1322それぞれへの射影の長さを算出することで得られた、凸部1511d、1512d、1513dおよび1514dの全体的な長さが考えられている。

【0217】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1511d、1512d、1513dおよび1514dそれぞれの幅(ω1、ω2、ω3およびω4)は、0.15mm程度である。

【0218】

凸部1511d、1512d、1513dおよび1514dそれぞれと、近接する電極辺1321および1322それぞれと、の間の距離(δ1、δ2、δ3およびδ4)は、0.7mm程度である。

【0219】

(実施例8)

図12を主として参照しながら、本実施例の実装構造体1000eの構成について説明する。

【0220】

凸部1511eおよび1512eは、それぞれ、レジスト表面1410eに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1521eおよび1522eと、シルクプリント1521eおよび1522eの−Z側にある厚さ30μm程度のソルダレジスト1400eと、で構成されている。

【0221】

実質的に平坦なソルダレジスト1400eのレジスト表面1410eと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0222】

凸部1511eおよび1512eそれぞれの長さ(λ1およびλ2)は、近接する電極辺1321および1322それぞれの長さ(L1およびL2)の80%程度である。

【0223】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1511eおよび1512eそれぞれの幅(ω1およびω2)は、0.15mm程度である。

【0224】

凸部1511eおよび1512eそれぞれと、近接する電極辺1321および1322それぞれと、の間の距離(δ1およびδ2)は、0.7mm程度である。

【0225】

(比較例1)

図13を主として参照しながら、本比較例の実装構造体4000aの構成について説明する。

【0226】

凸部が、実装構造体4000aにおいては設けられていない。

【0227】

実質的に平坦なソルダレジスト4400aのレジスト表面4410aと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0228】

(比較例2)

図14を主として参照しながら、本比較例の実装構造体1000fの構成について説明する。

【0229】

凸部1510fは、レジスト表面1410fに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1520fと、シルクプリント1520fの−Z側にある厚さ30μm程度のソルダレジスト1400fと、で構成されている。

【0230】

実質的に平坦なソルダレジスト1400fのレジスト表面1410fと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0231】

凸部1510fの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0232】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1510fの幅(ω)は、0.5mm程度である。

【0233】

凸部1510fと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、1.1mmおよび0.2mm程度である。

【0234】

したがって、凸部1510fと電極辺1321および1322との間の距離は、1.1(=Max(1.1,0.2))mm程度である。

【0235】

ここに、凸部と電極辺それぞれとの間の距離が異なっており、凸部1510fと電極辺1321および1322それぞれとの間の距離の最大値を算出することで得られた、凸部1510fと電極辺1321および1322それぞれとの間の最大の距離が考えられている。

【0236】

(比較例3)

図15を主として参照しながら、本比較例の実装構造体1000gの構成について説明する。

【0237】

凸部1510gは、レジスト表面1410gに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1520gと、シルクプリント1520gの−Z側にある厚さ30μm程度のソルダレジスト1400gと、で構成されている。

【0238】

実質的に平坦なソルダレジスト1400gのレジスト表面1410gと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0239】

凸部1510gの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0240】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1510gの幅(ω)は、0.2mm程度である。

【0241】

凸部1510gと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.8mm程度である。

【0242】

(比較例4)

図16を主として参照しながら、本比較例の実装構造体1000hの構成について説明する。

【0243】

凸部1510hは、レジスト表面1410hに形成された厚さ5μm程度の略直方体の形状を有するシルクプリント1520hと、シルクプリント1520hの−Z側にある厚さ30μm程度のソルダレジスト1400hと、で構成されている。

【0244】

実質的に平坦なソルダレジスト1400hのレジスト表面1410hと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0245】

凸部1510hの長さ(λ)は、電極辺1321および1322それぞれの長さ(L1およびL2)と同程度である。

【0246】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1510hの幅(ω)は、1.2mm程度である。

【0247】

凸部1510hと電極辺1321および1322それぞれとの間の距離(δ1およびδ2)は、0.3mm程度である。

【0248】

(比較例5)

図17を主として参照しながら、本比較例の実装構造体1000iの構成について説明する。

【0249】

凸部1511iおよび1512iは、それぞれ、レジスト表面1410iに形成された厚さ10μm程度の略直方体の形状を有するシルクプリント1521iおよび1522iと、シルクプリント1521iおよび1522iの−Z側にある厚さ30μm程度のソルダレジスト1400iと、で構成されている。

【0250】

実質的に平坦なソルダレジスト1400iのレジスト表面1410iと、部品下面1110(図1参照)と、の間の距離は、40μm程度である。

【0251】

凸部1511iおよび1512iそれぞれの長さ(λ1およびλ2)は、近接する電極辺1321および1322それぞれの長さ(L1およびL2)の70%程度である。

【0252】

そして、電子回路基板1200の横の方向、すなわちX方向の、凸部1511iおよび1512iそれぞれの幅(ω1およびω2)は、0.15mm程度である。

【0253】

凸部1511iおよび1512iそれぞれと、近接する電極辺1321および1322それぞれと、の間の距離(δ1およびδ2)は、0.7mm程度である。

【0254】

これら実施例1〜8および比較例1〜5の実装構造体についての耐衝撃試験は、樹脂補強部の高さ、せん断強度および破壊落下回数を測定することで行われた。

【0255】

なお、上記の樹脂補強部の高さは、実装構造体の半田接合部の断面をSEM(Scanning Electron Microscope)を利用して観察し、実質的に平坦なソルダレジストのレジスト表面とほぼ同一面内にある基板電極の電極表面を基準として樹脂の半田接合部への濡れ上がり高さをつながっている部分ごとに測定することにより、測定された。

【0256】

また、上記のせん断強度は、電子部品の長手方向と垂直な方向から幅1.5mm程度のステンレス製のツールを利用して1mm/sec程度の速度でせん断力を与え、半田接合部が破壊したときの荷重を測定することにより、測定された。

【0257】

また、上記の破壊落下回数は、実装構造体を重さ110g程度の筐体に固定し、高さ1.5m程度の場所から自由落下させ、電子部品が剥離するまでの落下回数を測定することにより、測定された。

【0258】

さて、以下では、耐衝撃試験の結果について説明する。

【0259】

なお、図18は、本発明における実施例1〜8およびおよび比較例1〜5の実装構造体に対して行われた耐衝撃試験の結果を説明する説明図である。

【0260】

耐衝撃試験評価は、つぎのように定義される“×”、“△”、“○”および“◎”の四段階で与えられている。

【0261】

破壊落下回数が20回以下であるとき、耐衝撃試験評価は“×”である。

【0262】

破壊落下回数が21〜99回であるとき、耐衝撃試験評価は“△”である。

【0263】

破壊落下回数が100回以上であり、せん断強度が13kgf未満であるとき、耐衝撃試験評価は“○”である。

【0264】

破壊落下回数が100回以上であり、せん断強度が13kgf以上であるとき、耐衝撃試験評価は“○”である。

【0265】

耐衝撃試験評価が“◎”または“○”である実施例の実装構造体は、樹脂補強部の高さが0.1mm以上であって、破壊落下回数が100回以上であり、実際の製品への使用に好適であるといえる。

【0266】

さて、実施例1、2および6〜8については、上記の第一から第三の条件(1a)〜(3a)が全て満足されており、耐衝撃試験評価が“○”である。

【0267】

そして、実施例3〜5については、上記のより厳しいつぎの第一から第三の条件(1b)〜(3b)が全て満足されており、耐衝撃試験評価が“◎”である。

【0268】

つまり、これらの実施例においては、凸部が設けられていることによる効果が十分に発揮され、導電性ペーストが加熱された際に発生する毛細管現象による部品下面の下側の空隙への樹脂の充填がかなり抑制されるので、樹脂の半田接合部への濡れ上がり高さが確保されると分析される。

【0269】

もちろん、このような凸部が設けられていることによる効果は、部品および基板電極についての形状および配置などによらずに発揮される。

【0270】

そして、比較例1〜5については、第一から第三の条件が全ては満足されておらず、耐衝撃試験評価が“△”または“×”である。

【0271】

なお、比較例4については、凸部の厚さの、ソルダレジストの厚さとの差に関する第一の条件が満足されていない。

【0272】

また、比較例5については、凸部の長さの、電極辺の長さとの比に関する第二の条件が満足されていない。

【0273】

また、比較例2および3については、凸部と電極辺との間の距離に関する第三の条件が満足されていない。

【産業上の利用可能性】

【0274】

本発明における実装構造体、および実装構造体の製造方法は、落下などに起因する衝撃に対してのより優れた耐衝撃性を確保することが可能であり、たとえば電子部品を電子回路基板に実装するために有用である。

【符号の説明】

【0275】

1000 実装構造体

1100 電子部品

1110 部品下面

1200 電子回路基板

1210 基板表面

1220 部分

1311、1312 基板電極

1321、1322 電極辺

1400 ソルダレジスト

1410 レジスト表面

1510 凸部

1520 シルクプリント

1530 シルクプリント表面

1611、1612 半田接合部

1710 樹脂補強部

【特許請求の範囲】

【請求項1】

電子回路基板の基板表面に形成された少なくとも二つの基板電極と、

電子部品をそれぞれの前記基板電極に接合する半田接合部と、

前記半田接合部を覆う樹脂補強部と、

前記基板表面に形成されたソルダレジストと、

前記電子部品の下側にあり前記基板電極に挟まれた、前記基板表面の部分に形成された凸部と、

を備え、

前記基板表面に垂直な方向の前記凸部の厚さは、前記基板表面に垂直な前記方向の前記ソルダレジストの厚さより、10μm以上40μm以下の範囲で大きく、

前記基板電極の、前記基板表面の前記部分の側にある電極辺の方向の、前記凸部の長さは、前記電極辺の長さの80%以上120%以下であり、

前記凸部と前記電極辺との間の距離は、0mm以上0.7mm以下であり、

前記凸部は、前記基板電極の電極表面に面接触しないように形成されている、実装構造体。

【請求項2】

前記凸部の材料は、前記ソルダレジストの材料と異なる、請求項1記載の実装構造体。

【請求項3】

前記基板表面の前記部分に形成された基板配線を備え、

前記凸部は、前記基板配線と、前記基板配線の上に形成された前記ソルダレジストと、によって構成されている、請求項1記載の実装構造体。

【請求項4】

前記凸部の前記厚さは、前記ソルダレジストの前記厚さより、25μm以上の範囲で大きく、

前記凸部の前記長さは、前記電極辺の前記長さの100%以上であり、

前記凸部と前記電極辺との間の前記距離は、0.3mm以下である、請求項1記載の実装構造体。

【請求項5】

少なくとも二つの基板電極を、電子回路基板の基板表面に形成する基板電極形成ステップと、

ソルダレジストを、前記基板表面に形成するソルダレジスト形成ステップと、

所定の部材を、前記基板電極に挟まれた、前記ソルダレジストのレジスト表面に形成する部材形成ステップと、

半田と、フラックス成分と、樹脂と、を含む導電性ペーストを、前記基板電極の上に塗布する導電性ペースト塗布ステップと、

電子部品を、前記塗布された導電性ペーストの上に載置する電子部品載置ステップと、

前記基板電極と、前記ソルダレジストと、前記部材と、が形成され、前記導電性ペーストが塗布され、前記電子部品が載置された前記電子回路基板を加熱する加熱ステップと、

を備えた、実装構造体の製造方法。

【請求項1】

電子回路基板の基板表面に形成された少なくとも二つの基板電極と、

電子部品をそれぞれの前記基板電極に接合する半田接合部と、

前記半田接合部を覆う樹脂補強部と、

前記基板表面に形成されたソルダレジストと、

前記電子部品の下側にあり前記基板電極に挟まれた、前記基板表面の部分に形成された凸部と、

を備え、

前記基板表面に垂直な方向の前記凸部の厚さは、前記基板表面に垂直な前記方向の前記ソルダレジストの厚さより、10μm以上40μm以下の範囲で大きく、

前記基板電極の、前記基板表面の前記部分の側にある電極辺の方向の、前記凸部の長さは、前記電極辺の長さの80%以上120%以下であり、

前記凸部と前記電極辺との間の距離は、0mm以上0.7mm以下であり、

前記凸部は、前記基板電極の電極表面に面接触しないように形成されている、実装構造体。

【請求項2】

前記凸部の材料は、前記ソルダレジストの材料と異なる、請求項1記載の実装構造体。

【請求項3】

前記基板表面の前記部分に形成された基板配線を備え、

前記凸部は、前記基板配線と、前記基板配線の上に形成された前記ソルダレジストと、によって構成されている、請求項1記載の実装構造体。

【請求項4】

前記凸部の前記厚さは、前記ソルダレジストの前記厚さより、25μm以上の範囲で大きく、

前記凸部の前記長さは、前記電極辺の前記長さの100%以上であり、

前記凸部と前記電極辺との間の前記距離は、0.3mm以下である、請求項1記載の実装構造体。

【請求項5】

少なくとも二つの基板電極を、電子回路基板の基板表面に形成する基板電極形成ステップと、

ソルダレジストを、前記基板表面に形成するソルダレジスト形成ステップと、

所定の部材を、前記基板電極に挟まれた、前記ソルダレジストのレジスト表面に形成する部材形成ステップと、

半田と、フラックス成分と、樹脂と、を含む導電性ペーストを、前記基板電極の上に塗布する導電性ペースト塗布ステップと、

電子部品を、前記塗布された導電性ペーストの上に載置する電子部品載置ステップと、

前記基板電極と、前記ソルダレジストと、前記部材と、が形成され、前記導電性ペーストが塗布され、前記電子部品が載置された前記電子回路基板を加熱する加熱ステップと、

を備えた、実装構造体の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2012−227180(P2012−227180A)

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願番号】特願2011−90449(P2011−90449)

【出願日】平成23年4月14日(2011.4.14)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願日】平成23年4月14日(2011.4.14)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]