実装構造

【課題】回路設計において高い自由度を得つつ、鳴きを低減することができる実装構造を提供することである。

【解決手段】電子部品10が回路基板50上に実装されている実装構造1。ランド54a,54bは、基板本体52上に設けられ、外部電極12a,12bのそれぞれとはんだ60a,60bにより接続されている。ランド電極54a,54bからはんだ60a,60bの頂上までの高さH1は、ランド電極54a,54bから回路基板50の最も近くに位置するコンデンサ導体32dが端面S3から露出している部分までの高さH2の1.27倍以下である。

【解決手段】電子部品10が回路基板50上に実装されている実装構造1。ランド54a,54bは、基板本体52上に設けられ、外部電極12a,12bのそれぞれとはんだ60a,60bにより接続されている。ランド電極54a,54bからはんだ60a,60bの頂上までの高さH1は、ランド電極54a,54bから回路基板50の最も近くに位置するコンデンサ導体32dが端面S3から露出している部分までの高さH2の1.27倍以下である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、実装構造に関し、より特定的には、コンデンサ等の電子部品が基板上に実装されている実装構造に関する。

【背景技術】

【0002】

誘電体層とコンデンサ導体とが積層されてなる電子部品では、電子部品に交流電圧が印加されると、電圧によって誘電体層に電界誘起歪みが発生する。このような電界誘起歪みは、電子部品が実装されている基板を振動させ、「鳴き」と呼ばれる振動音を発生させる。このような「鳴き」を低減するための従来の電子部品に関連する発明としては、例えば、特許文献1に記載の積層セラミックコンデンサの回路基板実装方法が知られている。

【0003】

特許文献1に記載の積層セラミックコンデンサの回路基板実装方法では、回路基板の表面と裏面に同等仕様のコンデンサが配置されている。これにより、一方のコンデンサから回路基板に伝達した振動と他方のコンデンサから回路基板に伝達した振動とが打ち消し合う。その結果、「鳴き」が低減される。

【0004】

しかしながら、特許文献1に記載の積層セラミックコンデンサの回路基板実装方法では、二つのコンデンサを回路基板の両面に実装する必要があるので、回路設計の自由度が低くなるという問題があった。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−232030号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

そこで、本発明の目的は、回路設計において高い自由度を得つつ、鳴きを低減することができる実装構造を提供することである。

【課題を解決するための手段】

【0007】

本発明の第1の形態である実装構造は、電子部品が基板上に実装されている実装構造であって、前記電子部品は、複数の誘電体層が積層されて構成されている積層体であって、前記基板に対向し、かつ、積層方向の一方側に位置する実装面、並びに、互いに対向する第1の端面及び第2の端面を有する直方体状の積層体と、前記誘電体層と共に積層されることによってコンデンサを形成し、かつ、前記第1の端面又は前記第2の端面に引き出されている複数のコンデンサ導体と、前記第1の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第1の外部電極と、前記第2の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第2の外部電極と、を備えており、前記基板は、基板本体と、前記基板本体上に設けられている第1のランド電極及び第2のランド電極であって、前記第1の外部電極及び前記第2の外部電極のそれぞれと導電性材料により接続されている第1のランド電極及び第2のランド電極と、を備えており、前記第1のランド電極又は前記第2のランド電極から前記導電性材料の頂上までの高さは、前記第1のランド電極又は前記第2のランド電極から前記コンデンサ導体が前記第1の端面又は前記第2の端面から露出している部分までの最短距離の1.27倍以下であること、を特徴とする。

【0008】

本発明の第2の形態である実装構造は、電子部品が基板上に実装されている実装構造であって、前記電子部品は、複数の誘電体層が積層されて構成されている積層体であって、前記基板に対向し、かつ、積層方向と直交する方向の一方側に位置する実装面、並びに、互いに対向する第1の端面及び第2の端面を有する直方体状の積層体と、前記誘電体層と共に積層されることによってコンデンサを形成し、かつ、前記第1の端面又は前記第2の端面に引き出されている複数のコンデンサ導体と、前記第1の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第1の外部電極と、前記第2の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第2の外部電極と、を備えており、前記基板は、基板本体と、前記基板本体上に設けられている第1のランド電極及び第2のランド電極であって、前記第1の外部電極及び前記第2の外部電極のそれぞれと導電性材料により接続されている第1のランド電極及び第2のランド電極と、を備えており、前記第1のランド電極は、第1のランド部及び第2のランド部に分割されており、前記第1のランド部及び前記第2のランド部は、前記基板本体の法線方向から平面視したときに、前記第1の端面の中心とは重なっておらず、前記導電性材料は、前記基板本体の法線方向から平面視したときに、前記第1の端面の中心とは重なっていないこと、を特徴とする。

【0009】

前記第1の形態である実装構造においては、第1のランド電極又は第2のランド電極から導電性材料の頂上までの高さは、第1のランド電極又は第2のランド電極からコンデンサ導体が第1の端面又は第2の端面から露出している部分までの最短距離の1.27倍以下であるため、コンデンサ導体が設けられている積層体部分において発生した振動の伝搬媒体である導電性材料が、最も振動する部分から離れることになり、振動が回路基板に伝搬されにくくなる。

【0010】

また、前記第2の形態である実装構造においては、第1のランド部及び第2のランド部は、基板本体の法線方向から平面視したときに、第1の端面の中心とは重なっておらず、導電性材料は、基板本体の法線方向から平面視したときに、第1の端面の中心とは重なっていないため、コンデンサ導体が設けられている積層体部分において発生した振動の伝搬媒体であるランド電極及び導電性材料が、最も振動する部分とは接合されておらず、振動が回路基板に伝搬されにくくなる。

【発明の効果】

【0011】

本発明によれば、一つの電子部品のみで振動を緩衝することができるため、回路設計において高い自由度を得つつ、鳴きを低減することができる。

【図面の簡単な説明】

【0012】

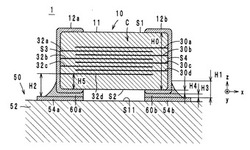

【図1】第1の実施形態である実装構造の断面構造図である。

【図2】第1の実施形態である実装構造を平面視した図である。

【図3】第1の実施形態を構成する電子部品の外観斜視図である。

【図4】図3の電子部品の積層体の分解斜視図である。

【図5】第1の実施形態において、電子部品が振動している様子を示した図である。

【図6】音圧レベルの測定装置の構成図である。

【図7】第1の実施形態における実験結果を示したグラフである。

【図8】第1の変形例である実装構造の断面構造図である。

【図9】第2の変形例である実装構造を構成する電子部品の断面構造図である。

【図10】第3の変形例である実装構造を平面視した図である。

【図11】第3の変形例における実験結果を示したグラフである。

【図12】第2の実施形態である実装構造の断面構造図である。

【図13】第2の実施形態である実装構造をz軸方向の正方向側から平面視した図である。

【図14】第2の実施形態において、電子部品が振動している様子を示した図である。

【図15】第2の実施形態における実験結果を示したグラフである。

【発明を実施するための形態】

【0013】

以下に、本発明に係る実装構造について添付図面を参照しながら説明する。なお、各図面においては、同じ部材、部分に関しては共通の符号を付し、重複する説明は省略する。

【0014】

(第1の実施形態、図1〜図7参照)

(実装構造の構成)

まず、第1の実施形態である実装構造1について図1〜図4を参照しながら説明する。この実装構造1は、図1及び図2に示すように、電子部品10及び回路基板50を備えている。電子部品10は、チップコンデンサであり、回路基板50上に実装されている。また、電子部品10は、図3及び図4にも示すように、積層体11、外部電極12(12a,12b)及びコンデンサ導体30(30a〜30d),32(32a〜32d)を備えている。以下では、積層体11の積層方向をz軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の長辺が延在している方向をx軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の短辺が延在している方向をy軸方向と定義する。

【0015】

積層体11は、図3に示すように、z軸方向の両端に位置している上面S1及び底面S2、互いに対向している端面S3,S4、並びに、互いに対向している側面S5,S6を有する直方体状をなしている。積層体11は、面取りが施されることにより角及び稜線において丸みを帯びた形状をなしている。以下では、積層体11において、z軸方向の正方向側に位置する面を上面S1とし、z軸方向の負方向側に位置する面を底面S2とする。また、x軸方向の負方向側に位置する面を端面S3とし、x軸方向の正方向側に位置する面を端面S4とする。また、y軸方向の正方向側に位置する面を側面S5とし、y軸方向の負方向側に位置する面を側面S6とする。底面S2は、電子部品10が回路基板50に実装される際に、該回路基板50と対向する実装面である。

【0016】

積層体11は、図4に示すように、複数のセラミック層(誘電体層)17(17a〜17n)がz軸方向の正方向側から負方向側へとこの順に並ぶように積層されることにより構成されている。セラミック層17は、長方形状をなしており、誘電体セラミックにより作製されている。以下では、セラミック層17のz軸方向の正方向側の主面を表面と称し、セラミック層17のz軸方向の負方向側の主面を裏面と称す。

【0017】

積層体11の上面S1は、z軸方向の最も正方向側に設けられているセラミック層17aの表面により構成されている。積層体11の底面S2は、z軸方向の最も負方向側に設けられているセラミック層17nの裏面により構成されている。また、端面S3は、セラミック層17a〜17nのx軸方向の負方向側の短辺が連なることによって構成されている。端面S4は、セラミック層17a〜17nのx軸方向の正方向側の短辺が連なることによって構成されている。側面S5は、セラミック層17a〜17nのy軸方向の正方向側の長辺が連なることによって構成されている。側面S6は、セラミック層17a〜17nのy軸方向の負方向側の長辺が連なることによって構成されている。

【0018】

コンデンサ導体30a〜30d,32a〜32dは、セラミック層17と共に積層されることによって、セラミック層17を介して互いに対向している。

【0019】

コンデンサ導体30a〜30dは、それぞれ、図4に示すように、セラミック層17d,17f,17h,17jの表面上に設けられており、積層体11に内蔵されている。コンデンサ導体30a〜30dは、長方形状をなしており、セラミック層17d,17f,17h,17jのx軸方向の正方向側の短辺に引き出されている。これにより、コンデンサ導体30a〜30dは、図1に示すように、端面S4(第1の端面)に引き出されている。

【0020】

コンデンサ導体32a〜32dは、それぞれ、図4に示すように、セラミック層17e,17g,17i,17kの表面上に設けられており、積層体11に内蔵されている。コンデンサ導体32a〜32dは、長方形状をなしており、セラミック層17e,17g,17i,17kのx軸方向の負方向側の短辺に引き出されている。これにより、コンデンサ導体32a〜32dは、図1に示すように、端面S3(第2の端面)に引き出されている。コンデンサ導体30a〜30dとコンデンサ導体32a〜32dとは、z軸方向から平面視したときに、重なり合っている。これにより、コンデンサ導体30,32間にはコンデンサCが形成されている。

【0021】

外部電極12a(第2の外部電極)は、端面S3を覆っていると共に、上面S1、底面S2及び側面S5,S6とに折り返されている。即ち、外部電極12aは、端面S3と上面S1、底面S2及び側面S5,S6とに跨って設けられている。また、外部電極12aは、コンデンサ導体32a〜32dに接続されている。より詳細には、外部電極12aは、コンデンサ導体32a〜32dが端面S3から露出している部分を覆うように、積層体11の端面S3の全面を覆っている。

【0022】

外部電極12b(第1の外部電極)は、端面S4を覆っていると共に、上面S1、底面S2及び側面S5,S6とに折り返されている。即ち、外部電極12bは、端面S4と上面S1、底面S2及び側面S5,S6とに跨って設けられている。また、外部電極12bは、コンデンサ導体30a〜30dに接続されている。より詳細には、外部電極12bは、コンデンサ導体30a〜30dが端面S4から露出している部分を覆うように、積層体11の端面S4の全面を覆っている。

【0023】

回路基板50は、表面及び内部に図示しない回路を有している多層基板であり、基板本体52及びランド電極54(54a,54b)を備えている。基板本体52は、複数の絶縁体層が積層されて構成されており、主面S11を有している。主面S11は、図1に示すように、基板本体52のz軸方向の正方向側の主面である。

【0024】

ランド電極54は、基板本体52の主面S11上に設けられており、外部電極12a,12bのそれぞれと導電性材料(はんだ60a,60b)により接続されている。より詳細には、ランド電極54a,54bは、z軸方向から平面視したときに、図2に示すように、長方形状をなしており、x軸方向の負方向側から正方向側へとこの順に並んでいる。

【0025】

外部電極12a,12bは、それぞれ、図1及び図2に示すように、ランド電極54a,54b上に載置され、はんだ60a,60bにより電気的に接続された状態でランド電極54a,54bに固定されている。ここで、はんだ60a,60bはそれぞれ、図1に示すように、外部電極12a,12bとランド電極54a,54bとの間の隙間を埋めていると共に、外部電極12a,12bの側面S3,S4を覆っている部分に沿ってz軸方向の正方向側に向かって延びている。

【0026】

ところで、実装構造1は、鳴きを低減すると共に、回路設計の自由度を向上させるために以下に説明する構造を有している。まず、ランド電極54a,54bのz軸方向の正方向側の面(上面)からはんだ60a,60bの頂上までの高さをH1と定義する。はんだ60a,60bの頂上とは、外部電極12a,12bの側面S3,S4上に延びているはんだ60a,60bのz軸方向の正方向側の端部を意味している。また、高さとは、z軸方向における距離を意味している。以下では、ランド電極54a,54bのz軸方向の正方向側の面(上面)からはんだ60a,60bの頂上までの高さH1をはんだフィレット高さともいう。更に、ランド電極54a,54bからコンデンサ導体30a〜30d,32a〜32dが端面S3,S4から露出している部分までの最短距離をH2とする。H2は、換言すれば、ランド電極54a,54bから回路基板50の最も近くに位置するコンデンサ導体32dが端面S3から露出している部分までの高さである。このとき、H1は、H2の1.27倍以下である。

【0027】

(電子部品の製造方法)

次に、電子部品10の製造方法について説明する。なお、図面は、図3及び図4を参照する。

【0028】

まず、BaTiO3等のセラミック粉末に対して、バインダ及び有機溶剤を加えてボールミルに投入し、湿式調合を行って、セラミックスラリーを得る。得られたセラミックスラリーをドクターブレード法により、キャリアシート上にシート状に形成して乾燥させ、セラミック層17となるべきセラミックグリーンシートを作製する。セラミック層17となるべきセラミックグリーンシートの厚さは、焼成後のセラミック層の厚さが0.5μm以上10μm以下となる厚さであることが好ましい。なお、セラミック粉末の主成分は、CaTiO3,SrTiO3,CaZrO3等であってもよい。また、セラミック粉末の副成分として、Mn化合物、Mg化合物、Si化合物、Co化合物、Ni化合物、希土類化合物等が添加されていてもよい。

【0029】

次に、セラミック層17となるべきセラミックグリーンシート上に、導電性材料からなるペーストをスクリーン印刷法で塗布することにより、コンデンサ導体30,32を形成する。導電性材料からなるペーストは、金属粉末に、有機バインダ及び有機溶剤が加えられたものである。金属粉末は、例えば、Ni、Cu、Ag、Pd、Ag−Pd合金、Au等である。焼成後のコンデンサ導体30,32の厚さは、0.3μm以上2.0μm以下であることが好ましい。

【0030】

次に、セラミック層17となるべきセラミックグリーンシートを積層して未焼成のマザー積層体を得る。この後、未焼成のマザー積層体に対して、プレスを施す。

【0031】

次に、未焼成のマザー積層体を所定寸法にカットして、複数の未焼成の積層体11を得る。この後、積層体11の表面に、バレル研磨加工等の研磨加工を施す。

【0032】

次に、未焼成の積層体11を焼成する。焼成温度は、例えば、1200〜1300℃である。

【0033】

次に、積層体11に外部電極12を形成する。具体的には、周知のディップ法やスリット工法等により、積層体11の表面にCu、Ni、Ag、Pd、Ag−Pd合金、Au等を含有する導電性ペーストを塗布する。そして、下地電極を焼付けを行って、下地電極を形成する。下地電極上には、Niめっき及びSnめっきを施す。これにより、外部電極12が形成される。以上の工程により、電子部品10が完成する。

【0034】

以上のように製造された電子部品10は、回路基板50上に実装される。基板本体52は、例えば、ガラスエポキシ等からなる絶縁体層が複数積層されて構成されている。また、ランド電極54は、Cuからなる下地電極にめっきが施されて構成されている。実装時には、ランド電極54にはんだペーストを塗布する。次に、底面S2が基板本体52の主面S11と対向するように、ランド電極54上に外部電極12をセットする。この際、底面S2と主面S11とは平行になっていることが好ましい。この後、リフロー工程を行ってはんだペーストを溶融させた後、はんだペーストを固化させる。これにより、電子部品10が回路基板50上に実装される。

【0035】

なお、はんだペーストには、例えば、Sn−Pb共晶はんだや、Sn−Ag−Cu等の鉛フリーはんだを用いることが可能である。また、はんだ60の代わりに導電性接着剤が用いられてもよい。

【0036】

(効果)

以上の実装構造1によれば、以下に説明するように、回路設計において高い自由度を得つつ、鳴きを低減することができる。図5は、実装構造1において、電子部品10が振動している様子を示した図である。

【0037】

特許文献1に記載の積層セラミックコンデンサの回路基板実装方法では、鳴きの低減のために、二つのコンデンサが回路基板の両面に実装されているので、回路設計の自由度が低くなるという問題があった。

【0038】

そこで、実装構造1では、ランド電極54a,54bのz軸方向の正方向側の面からはんだ60a,60bの頂上までの高さ(フィレット高さ)H1は、ランド電極54a,54bから回路基板50の最も近くに位置するコンデンサ導体32dが端面S3から露出している部分までの高さH2の1.27倍以下とされている。これにより、実装構造1は、以下に説明するように、電子部品10を二つ用いることなく、鳴きの低減を実現できる。

【0039】

より詳細には、実装構造1では、コンデンサ導体30,32が設けられている部分において発生した振動がはんだ60及びランド電極54を伝搬されることによって、回路基板50が振動して鳴きが発生する。図5に示すように、電子部品10は、端面S3,S4のz軸方向の中心に近づくにしたがって大きく振動する。そこで、実装構造1では、振動の伝搬経路となっているはんだ60は、振動源である端面S3,S4のz軸方向の中心から離されている。これにより、電子部品10において発生した振動が回路基板50に伝搬されにくくなる。その結果、実装構造1では、鳴きが低減される。

【0040】

(実験)

本願発明者は、実装構造1が奏する効果をより明確にするために、以下に説明する実験を行った。具体的には、本願発明者は、以下に説明する第1の試料群及び第2の試料群を作製した。なお、第1の試料群及び第2の試料群では、以下の条件に示すように、フィレット高さH1を複数種類に変更した。

【0041】

第1の試料群の条件

回路基板のサイズ:100mm×40mm×1.6mm

電子部品の外形寸法:1.75mm×0.95mm×0.91mm

電子部品の容量:22μF

セラミック層の厚み:0.94μm

コンデンサ導体の厚み:0.58μm

コンデンサ導体の枚数:491

積層体の高さH0(図1参照):0.87mm

フィレット高さ:0.08mm、0.16mm、0.32mm、0.5mm、0.6mm、0.8mmの6種類

外部電極とランド電極との隙間H3(図1参照):0.05mm

外部電極の厚みH4(図1参照):20μm

回路基板の最も近くに位置する外部電極から積層体の底面までの距離(外層厚)H5(図1参照):56μm

【0042】

なお、第1の試料群では、ランド電極から回路基板の最も近くに位置するコンデンサ導体が端面から露出している部分までの高さH2は、H3、H4及びH5の合計(126μm)である。

【0043】

第2の試料群の条件

回路基板のサイズ:100mm×40mm×1.6mm

電子部品の外形寸法:2.11mm×1.35mm×1.31mm

電子部品の容量:47μF

セラミック層の厚み:0.94μm

コンデンサ導体の厚み:0.62μm

コンデンサ導体の枚数:671

積層体の高さH0(図1参照):1.26mm

フィレット高さ:0.08mm、0.21mm、0.4mm、0.75mm、1.2mmの5種類

外部電極とランド電極との隙間H3(図1参照):0.05mm

外部電極の厚みH4(図1参照):25μm

回路基板の最も近くに位置する外部電極から積層体の底面までの距離(外層厚)H5(図1参照):90μm

【0044】

なお、第2の試料群では、ランド電極から回路基板の最も近くに位置するコンデンサ導体が端面から露出している部分までの高さH2は、H3、H4及びH5の合計(165μm)である。

【0045】

以上のように構成された第1の試料群及び第2の試料群を用いて、音圧レベルの抑制量を測定した。図6は、音圧レベルの測定装置71の構成図である。

【0046】

本願発明者は、実装構造1(第1の試料群及び第2の試料群)を無響箱73内に設置し、電子部品10に対して、3kHzの周波数及び1Vppの電圧を有する交流電圧を印加した。そして、その際に発生する鳴きを集音マイク74で集音し、集音計76及びFETアナライザ78(株式会社小野測器製 CF−5220)で集音された音の音圧レベルを測定した。集音マイク74は、回路基板50から3mmだけ離して設置した。図7は、実験結果を示したグラフである。縦軸は、音圧レベルの抑制量を示し、横軸は、H1/H2の値を示している。音圧レベルの抑制量とは、H1/H2=8のときの音圧レベルに対する抑制量である。

【0047】

図7によれば、第1の試料群及び第2の試料群共に、H1/H2が1.27以下である場合には、H1/H2が1.27より大きい場合に比べて、音圧レベルの抑制量が飛躍的に大きくなっていることが分かる。よって、本実験によれば、H1をH2の1.27倍以下とすることによって、鳴きを低減できることが理解できる。

【0048】

(第1の変形例、図8参照)

以下に、第1の変形例である実装構造1aについて図面を参照しながら説明する。図8は、第1の変形例である実装構造1aの断面構造図である。

【0049】

本実装構造1aと前記実装構造1との相違点は、コンデンサ導体30,32の位置である。より詳細には、実装構造1aのコンデンサ導体30,32は、実装構造1のコンデンサ導体30,32よりもz軸方向の正方向側に位置している。即ち、底面S2とコンデンサ導体32dとの距離は、上面S1とコンデンサ導体30aとの距離よりも大きい。これにより、実装構造1aでは実装構造1よりも、ランド電極54a,54bから回路基板50の最も近くに位置するコンデンサ導体32dが端面S3から露出している部分までの高さH2が大きくなる。その結果、実装構造1aでは実装構造1よりもH1/H2が小さくなる。よって、実装構造1aでは、より効果的に鳴きが低減される。

【0050】

(第2の変形例、図9参照)

次に、第2の変形例である実装構造1bについて図面を参照しながら説明する。図9(A),(B)はそれぞれ実装構造1bに用いられる電子部品10bを示している。

【0051】

前記第1の変形例で用いられている電子部品1aでは、底面S2とコンデンサ導体32dとの距離を、上面S1とコンデンサ導体30aとの距離よりも大きくしているため、つまり、下側の外層部分が上側の外層部分よりも厚く、非対称になるため、電子部品10aの製造工程においてマザー積層体としたときに、熱が加わるとマザー積層体が全体的に反ってしまい、加工できなくなるおそれがある。

【0052】

そこで、本第2の変形例である実装構造1bでは、適宜枚数のダミー導体31を、底面S2とコンデンサ導体32dとの間のセラミック層に設けるようにした。ダミー導体31は、図9(A)に示すように、x軸方向の中央部分で分離され、両端部が外部電極12a,12bに接続されていてもよく、あるいは、図9(B)に示すように、外部電極12a,12bとは接続されることなく、x軸方向の中央部分に電気的には絶縁状態で配置されていてもよい。また、ダミー導体31は、外部電極12a,12bいずれかのみと接続されていてもよい。

【0053】

第2の変形例によれば、積層体11において、比較的厚みのあるセラミック層のみからなる下側の外層部分にダミー導体31を設けため、該外層部分が硬くなり、積層体11が反ってしまう不具合を解消できる。

【0054】

(第3の変形例、図10及び図11参照)

以下に、第3の変形例である実装構造1cについて図面を参照しながら説明する。図10は、第3の変形例である実装構造1cを平面視した図である。

【0055】

本実装構造1cと前記実装構造1との相違点は、ランド電極54の構造である。実装構造1cでは、ランド電極54aは、ランド部70a,72aに分割されている。ランド部70a,72aは、長方形状をなしており、y軸方向の負方向側から正方向側へとこの順に並んでいる。そして、ランド部70a,72aはそれぞれ、z軸方向(基板本体50の法線方向)から平面視したときに、積層体11の隣り合う角と重なっている。より詳細には、ランド部70a,72aは、z軸方向から平面視したときに、積層体11のx軸方向の負方向側の短辺の両端に位置する角と重なっている。ランド部70a,72aはそれぞれ、はんだ61a,62aを介して外部電極12aに接続されている。

【0056】

但し、ランド部70a,72aは、z軸方向から平面視したときに、端面S3の中心(対角線の交点)と重なっていない。よって、はんだ61a,62aは、z軸方向から平面視したときに、端面S3の中心とは重なっていない。

【0057】

また、ランド電極54bは、ランド部70b,72bに分割されている。ランド部70b,72bは、長方形状をなしており、y軸方向の負方向側から正方向側へとこの順に並んでいる。そして、ランド部70b,72bはそれぞれ、z軸方向(基板本体50の法線方向)から平面視したときに、積層体11の隣り合う角と重なっている。より詳細には、ランド部70b,72bは、z軸方向から平面視したときに、積層体11のx軸方向の正方向側の短辺の両端に位置する角と重なっている。ランド部70b,72bはそれぞれ、はんだ61b,62bを介して外部電極12bに接続されている。

【0058】

但し、ランド部70b,72bは、z軸方向から平面視したときに、端面S4の中心(対角線の交点)と重なっていない。よって、はんだ61b,62bは、z軸方向から平面視したときに、端面S4の中心とは重なっていない。

【0059】

実装構造1cは、以下に説明するように、前記実装構造1よりも鳴きを低減できる。実装構造1cでは、ランド電極54はそれぞれ、ランド部70,72に分割されている。これにより、実装構造1cにおいて外部電極12とランド電極54とがはんだ61,62により接続されている面積は、実装構造1において外部電極12とランド電極54とがはんだ60により接続されている面積よりも小さくなる。その結果、実装構造1cでは、実装構造1よりも、電子部品10で発生した振動が回路基板50に伝達されにくくなる。その結果、実装構造1cでは、実装構造1よりも鳴きが低減される。

【0060】

また、電子部品10に交流電圧が印加されると、端面S3,S4の中心(対角線の交点)が大きく振動する。そのため、端面S3,S4の中心の直下がランド電極54に固定されていると、電子部品10から回路基板50に振動が伝わりやすい。そこで、電子部品10では、ランド電極54がランド部70,72に分割されている。ランド部70,74は、z軸方向から平面視したときに、端面S3,S4の中心とは重なっていない。よって、はんだ61,62は、z軸方向から平面視したときに、端面S3,S4の中心とは重なっていない。これにより、電子部品10から回路基板50に振動が伝わることが抑制されている。

【0061】

本願発明者は、実装構造1cが奏する効果をより明確にするために、以下に説明する実験を行った。より詳細には、本願発明者は、以下に説明する第1のサンプル及び第2のサンプルを作製し、第1のサンプル及び第2のサンプルの電子部品10に対して1Vppの電圧を有する交流電圧を印加し、周波数を変化させながら音圧を測定した。

【0062】

第1のサンプルは、図1に示す実装構造1である。第2のサンプルは、図10に示す実装構造1cである。図11は、実験結果を示したグラフである。縦軸は、音圧レベルを示し、横軸は、周波数を示している。

【0063】

図11によれば、第1のサンプルの音圧レベルよりも第2のサンプルの音圧レベルの方が小さくなっていることが分かる。即ち、ランド電極54が分割されることによって、鳴きが低減されていることが理解できる。

【0064】

(第2の実施形態、図12〜図15参照)

以下に、第2の実施形態である実装構造2について図面を参照しながら説明する。図12は、第2の実施形態である実装構造2の断面構造図である。図13は、図12の実装構造2をz軸方向の正方向側から平面視した図である。

【0065】

本実装構造2と前記実装構造1との相違点は、電子部品10の向きである。実装構造2では、積層方向と直交する方向の一方側に位置する側面S5が実装面である。本第2の実施形態では、積層方向をy軸方向と定義する。また、積層体11をy軸方向から平面視したときに、積層体11の長辺が延在している方向をx軸方向と定義する。積層体11をy軸方向から平面視したときに、積層体11の短辺が延在している方向をz軸方向と定義する。

【0066】

また、図13に示すように、実装構造2では、ランド電極54aは、ランド部70a,72aに分割されている。ランド部70a,72aは、長方形状をなしており、y軸方向の負方向側から正方向側へとこの順に並んでいる。そして、ランド部70a,72aはそれぞれ、z軸方向(基板本体50の法線方向)から平面視したときに、積層体11の隣り合う角と重なっている。より詳細には、ランド部70a,72aは、z軸方向から平面視したときに、積層体11のx軸方向の負方向側の短辺の両端に位置する角と重なっている。ランド部70a,72aはそれぞれ、はんだ61a,62aを介して外部電極12aに接続されている。

【0067】

但し、ランド部70a,72aは、z軸方向から平面視したときに、端面S3の中心(対角線の交点)と重なっていない。よって、はんだ61a,62aは、z軸方向から平面視したときに、端面S3の中心とは重なっていない。

【0068】

また、ランド電極54bは、ランド部70b,72bに分割されている。ランド部70b,72bは、長方形状をなしており、y軸方向の負方向側から正方向側へとこの順に並んでいる。そして、ランド部70b,72bはそれぞれ、z軸方向(基板本体50の法線方向)から平面視したときに、積層体11の隣り合う角と重なっている。より詳細には、ランド部70b,72bは、z軸方向から平面視したときに、積層体11のx軸方向の正方向側の短辺の両端に位置する角と重なっている。ランド部70b,72bはそれぞれ、はんだ61b,62bを介して外部電極12bに接続されている。

【0069】

但し、ランド部70b,72bは、z軸方向から平面視したときに、端面S4の中心(対角線の交点)と重なっていない。よって、はんだ61b,62bは、z軸方向から平面視したときに、端面S4の中心とは重なっていない。

【0070】

(効果)

以上の実装構造2によれば、以下に説明するように、回路設計において高い自由度を得つつ、鳴きを低減することができる。図14は、実装構造2において、電子部品10が振動している様子を示した図である。

【0071】

実装構造2では、電子部品10に交流電圧が印加されると、図14に示すように、端面S3,S4の中心(対角線の交点)が大きく振動する。そのため、端面S3,S4の中心の直下(z軸方向の負方向側)がランド電極54に固定されていると、電子部品10から回路基板50に振動が伝わりやすい。そこで、実装構造2では、ランド電極54がランド部70,72に分割されている。ランド部70,72は、z軸方向から平面視したときに、振動源である端面S3,S4の中心とは重なっていない。よって、はんだ61,62は、z軸方向から平面視したときに、振動源である端面S3,S4の中心とは重なっていない。即ち、実装構造2では、振動の伝搬経路となっているはんだ61,62は、振動源である端面S3,S4の中心から離されている。これにより、電子部品10において発生した振動が回路基板50に伝搬されにくくなる。その結果、実装構造2では、鳴きが低減される。

【0072】

本願発明者は、実装構造2が奏する効果をより明確にするために、以下に説明する実験を行った。より詳細には、本願発明者は、以下に説明する第3のサンプル及び第4のサンプルを作製し、第3のサンプル及び第4のサンプルの電子部品10に対して1Vppの電圧を有する交流電圧を印加し、周波数を変化させながら音圧を測定した。

【0073】

第3のサンプルは、図12に示す実装構造2である。第4のサンプルは、図12及び図14に示す実装構造2において、ランド電極54が分割されていない回路基板に電子部品10が図12に示すように実装された実装構造である。図15は、実験結果を示したグラフである。縦軸は、音圧レベルを示し、横軸は、周波数を示している。

【0074】

図15によれば、第4のサンプルの音圧レベルよりも第3のサンプルの音圧レベルの方が小さくなっていることが分かる。これにより、実装構造2において、ランド電極54が分割されることによって、鳴きが低減されていることが理解できる。

【0075】

(他の実施形態)

なお、本発明に係る実装構造は、前記実施形態に限定するものではなく、その要旨の範囲内で種々に変更することができる。

【0076】

特に、前記第2実施形態(図12〜図15参照)において、二つのランド部に分割されているランド電極54a,54bは、いずれか一方のみが分割されているだけであってもよい。

【産業上の利用可能性】

【0077】

以上のように、本発明は、電子部品の実装構造に有用であり、特に、回路設計において高い自由度を得つつ、鳴きを低減することができる点で優れている。

【符号の説明】

【0078】

C コンデンサ

S1 上面

S2 底面

S3,S4 端面

S5,S6 側面

1,1a〜1c,2 実装構造

10 電子部品

11 積層体

12a,12b 外部電極

17a〜17n セラミック層

30a〜30d,32a〜32d コンデンサ導体

50 回路基板

52 基板本体

54a,54b ランド電極

60a,60b,61a,61b,62a,62b はんだ

70a,70b,72a,72b ランド部

【技術分野】

【0001】

本発明は、実装構造に関し、より特定的には、コンデンサ等の電子部品が基板上に実装されている実装構造に関する。

【背景技術】

【0002】

誘電体層とコンデンサ導体とが積層されてなる電子部品では、電子部品に交流電圧が印加されると、電圧によって誘電体層に電界誘起歪みが発生する。このような電界誘起歪みは、電子部品が実装されている基板を振動させ、「鳴き」と呼ばれる振動音を発生させる。このような「鳴き」を低減するための従来の電子部品に関連する発明としては、例えば、特許文献1に記載の積層セラミックコンデンサの回路基板実装方法が知られている。

【0003】

特許文献1に記載の積層セラミックコンデンサの回路基板実装方法では、回路基板の表面と裏面に同等仕様のコンデンサが配置されている。これにより、一方のコンデンサから回路基板に伝達した振動と他方のコンデンサから回路基板に伝達した振動とが打ち消し合う。その結果、「鳴き」が低減される。

【0004】

しかしながら、特許文献1に記載の積層セラミックコンデンサの回路基板実装方法では、二つのコンデンサを回路基板の両面に実装する必要があるので、回路設計の自由度が低くなるという問題があった。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−232030号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

そこで、本発明の目的は、回路設計において高い自由度を得つつ、鳴きを低減することができる実装構造を提供することである。

【課題を解決するための手段】

【0007】

本発明の第1の形態である実装構造は、電子部品が基板上に実装されている実装構造であって、前記電子部品は、複数の誘電体層が積層されて構成されている積層体であって、前記基板に対向し、かつ、積層方向の一方側に位置する実装面、並びに、互いに対向する第1の端面及び第2の端面を有する直方体状の積層体と、前記誘電体層と共に積層されることによってコンデンサを形成し、かつ、前記第1の端面又は前記第2の端面に引き出されている複数のコンデンサ導体と、前記第1の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第1の外部電極と、前記第2の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第2の外部電極と、を備えており、前記基板は、基板本体と、前記基板本体上に設けられている第1のランド電極及び第2のランド電極であって、前記第1の外部電極及び前記第2の外部電極のそれぞれと導電性材料により接続されている第1のランド電極及び第2のランド電極と、を備えており、前記第1のランド電極又は前記第2のランド電極から前記導電性材料の頂上までの高さは、前記第1のランド電極又は前記第2のランド電極から前記コンデンサ導体が前記第1の端面又は前記第2の端面から露出している部分までの最短距離の1.27倍以下であること、を特徴とする。

【0008】

本発明の第2の形態である実装構造は、電子部品が基板上に実装されている実装構造であって、前記電子部品は、複数の誘電体層が積層されて構成されている積層体であって、前記基板に対向し、かつ、積層方向と直交する方向の一方側に位置する実装面、並びに、互いに対向する第1の端面及び第2の端面を有する直方体状の積層体と、前記誘電体層と共に積層されることによってコンデンサを形成し、かつ、前記第1の端面又は前記第2の端面に引き出されている複数のコンデンサ導体と、前記第1の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第1の外部電極と、前記第2の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第2の外部電極と、を備えており、前記基板は、基板本体と、前記基板本体上に設けられている第1のランド電極及び第2のランド電極であって、前記第1の外部電極及び前記第2の外部電極のそれぞれと導電性材料により接続されている第1のランド電極及び第2のランド電極と、を備えており、前記第1のランド電極は、第1のランド部及び第2のランド部に分割されており、前記第1のランド部及び前記第2のランド部は、前記基板本体の法線方向から平面視したときに、前記第1の端面の中心とは重なっておらず、前記導電性材料は、前記基板本体の法線方向から平面視したときに、前記第1の端面の中心とは重なっていないこと、を特徴とする。

【0009】

前記第1の形態である実装構造においては、第1のランド電極又は第2のランド電極から導電性材料の頂上までの高さは、第1のランド電極又は第2のランド電極からコンデンサ導体が第1の端面又は第2の端面から露出している部分までの最短距離の1.27倍以下であるため、コンデンサ導体が設けられている積層体部分において発生した振動の伝搬媒体である導電性材料が、最も振動する部分から離れることになり、振動が回路基板に伝搬されにくくなる。

【0010】

また、前記第2の形態である実装構造においては、第1のランド部及び第2のランド部は、基板本体の法線方向から平面視したときに、第1の端面の中心とは重なっておらず、導電性材料は、基板本体の法線方向から平面視したときに、第1の端面の中心とは重なっていないため、コンデンサ導体が設けられている積層体部分において発生した振動の伝搬媒体であるランド電極及び導電性材料が、最も振動する部分とは接合されておらず、振動が回路基板に伝搬されにくくなる。

【発明の効果】

【0011】

本発明によれば、一つの電子部品のみで振動を緩衝することができるため、回路設計において高い自由度を得つつ、鳴きを低減することができる。

【図面の簡単な説明】

【0012】

【図1】第1の実施形態である実装構造の断面構造図である。

【図2】第1の実施形態である実装構造を平面視した図である。

【図3】第1の実施形態を構成する電子部品の外観斜視図である。

【図4】図3の電子部品の積層体の分解斜視図である。

【図5】第1の実施形態において、電子部品が振動している様子を示した図である。

【図6】音圧レベルの測定装置の構成図である。

【図7】第1の実施形態における実験結果を示したグラフである。

【図8】第1の変形例である実装構造の断面構造図である。

【図9】第2の変形例である実装構造を構成する電子部品の断面構造図である。

【図10】第3の変形例である実装構造を平面視した図である。

【図11】第3の変形例における実験結果を示したグラフである。

【図12】第2の実施形態である実装構造の断面構造図である。

【図13】第2の実施形態である実装構造をz軸方向の正方向側から平面視した図である。

【図14】第2の実施形態において、電子部品が振動している様子を示した図である。

【図15】第2の実施形態における実験結果を示したグラフである。

【発明を実施するための形態】

【0013】

以下に、本発明に係る実装構造について添付図面を参照しながら説明する。なお、各図面においては、同じ部材、部分に関しては共通の符号を付し、重複する説明は省略する。

【0014】

(第1の実施形態、図1〜図7参照)

(実装構造の構成)

まず、第1の実施形態である実装構造1について図1〜図4を参照しながら説明する。この実装構造1は、図1及び図2に示すように、電子部品10及び回路基板50を備えている。電子部品10は、チップコンデンサであり、回路基板50上に実装されている。また、電子部品10は、図3及び図4にも示すように、積層体11、外部電極12(12a,12b)及びコンデンサ導体30(30a〜30d),32(32a〜32d)を備えている。以下では、積層体11の積層方向をz軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の長辺が延在している方向をx軸方向と定義する。積層体11をz軸方向から平面視したときに、積層体11の短辺が延在している方向をy軸方向と定義する。

【0015】

積層体11は、図3に示すように、z軸方向の両端に位置している上面S1及び底面S2、互いに対向している端面S3,S4、並びに、互いに対向している側面S5,S6を有する直方体状をなしている。積層体11は、面取りが施されることにより角及び稜線において丸みを帯びた形状をなしている。以下では、積層体11において、z軸方向の正方向側に位置する面を上面S1とし、z軸方向の負方向側に位置する面を底面S2とする。また、x軸方向の負方向側に位置する面を端面S3とし、x軸方向の正方向側に位置する面を端面S4とする。また、y軸方向の正方向側に位置する面を側面S5とし、y軸方向の負方向側に位置する面を側面S6とする。底面S2は、電子部品10が回路基板50に実装される際に、該回路基板50と対向する実装面である。

【0016】

積層体11は、図4に示すように、複数のセラミック層(誘電体層)17(17a〜17n)がz軸方向の正方向側から負方向側へとこの順に並ぶように積層されることにより構成されている。セラミック層17は、長方形状をなしており、誘電体セラミックにより作製されている。以下では、セラミック層17のz軸方向の正方向側の主面を表面と称し、セラミック層17のz軸方向の負方向側の主面を裏面と称す。

【0017】

積層体11の上面S1は、z軸方向の最も正方向側に設けられているセラミック層17aの表面により構成されている。積層体11の底面S2は、z軸方向の最も負方向側に設けられているセラミック層17nの裏面により構成されている。また、端面S3は、セラミック層17a〜17nのx軸方向の負方向側の短辺が連なることによって構成されている。端面S4は、セラミック層17a〜17nのx軸方向の正方向側の短辺が連なることによって構成されている。側面S5は、セラミック層17a〜17nのy軸方向の正方向側の長辺が連なることによって構成されている。側面S6は、セラミック層17a〜17nのy軸方向の負方向側の長辺が連なることによって構成されている。

【0018】

コンデンサ導体30a〜30d,32a〜32dは、セラミック層17と共に積層されることによって、セラミック層17を介して互いに対向している。

【0019】

コンデンサ導体30a〜30dは、それぞれ、図4に示すように、セラミック層17d,17f,17h,17jの表面上に設けられており、積層体11に内蔵されている。コンデンサ導体30a〜30dは、長方形状をなしており、セラミック層17d,17f,17h,17jのx軸方向の正方向側の短辺に引き出されている。これにより、コンデンサ導体30a〜30dは、図1に示すように、端面S4(第1の端面)に引き出されている。

【0020】

コンデンサ導体32a〜32dは、それぞれ、図4に示すように、セラミック層17e,17g,17i,17kの表面上に設けられており、積層体11に内蔵されている。コンデンサ導体32a〜32dは、長方形状をなしており、セラミック層17e,17g,17i,17kのx軸方向の負方向側の短辺に引き出されている。これにより、コンデンサ導体32a〜32dは、図1に示すように、端面S3(第2の端面)に引き出されている。コンデンサ導体30a〜30dとコンデンサ導体32a〜32dとは、z軸方向から平面視したときに、重なり合っている。これにより、コンデンサ導体30,32間にはコンデンサCが形成されている。

【0021】

外部電極12a(第2の外部電極)は、端面S3を覆っていると共に、上面S1、底面S2及び側面S5,S6とに折り返されている。即ち、外部電極12aは、端面S3と上面S1、底面S2及び側面S5,S6とに跨って設けられている。また、外部電極12aは、コンデンサ導体32a〜32dに接続されている。より詳細には、外部電極12aは、コンデンサ導体32a〜32dが端面S3から露出している部分を覆うように、積層体11の端面S3の全面を覆っている。

【0022】

外部電極12b(第1の外部電極)は、端面S4を覆っていると共に、上面S1、底面S2及び側面S5,S6とに折り返されている。即ち、外部電極12bは、端面S4と上面S1、底面S2及び側面S5,S6とに跨って設けられている。また、外部電極12bは、コンデンサ導体30a〜30dに接続されている。より詳細には、外部電極12bは、コンデンサ導体30a〜30dが端面S4から露出している部分を覆うように、積層体11の端面S4の全面を覆っている。

【0023】

回路基板50は、表面及び内部に図示しない回路を有している多層基板であり、基板本体52及びランド電極54(54a,54b)を備えている。基板本体52は、複数の絶縁体層が積層されて構成されており、主面S11を有している。主面S11は、図1に示すように、基板本体52のz軸方向の正方向側の主面である。

【0024】

ランド電極54は、基板本体52の主面S11上に設けられており、外部電極12a,12bのそれぞれと導電性材料(はんだ60a,60b)により接続されている。より詳細には、ランド電極54a,54bは、z軸方向から平面視したときに、図2に示すように、長方形状をなしており、x軸方向の負方向側から正方向側へとこの順に並んでいる。

【0025】

外部電極12a,12bは、それぞれ、図1及び図2に示すように、ランド電極54a,54b上に載置され、はんだ60a,60bにより電気的に接続された状態でランド電極54a,54bに固定されている。ここで、はんだ60a,60bはそれぞれ、図1に示すように、外部電極12a,12bとランド電極54a,54bとの間の隙間を埋めていると共に、外部電極12a,12bの側面S3,S4を覆っている部分に沿ってz軸方向の正方向側に向かって延びている。

【0026】

ところで、実装構造1は、鳴きを低減すると共に、回路設計の自由度を向上させるために以下に説明する構造を有している。まず、ランド電極54a,54bのz軸方向の正方向側の面(上面)からはんだ60a,60bの頂上までの高さをH1と定義する。はんだ60a,60bの頂上とは、外部電極12a,12bの側面S3,S4上に延びているはんだ60a,60bのz軸方向の正方向側の端部を意味している。また、高さとは、z軸方向における距離を意味している。以下では、ランド電極54a,54bのz軸方向の正方向側の面(上面)からはんだ60a,60bの頂上までの高さH1をはんだフィレット高さともいう。更に、ランド電極54a,54bからコンデンサ導体30a〜30d,32a〜32dが端面S3,S4から露出している部分までの最短距離をH2とする。H2は、換言すれば、ランド電極54a,54bから回路基板50の最も近くに位置するコンデンサ導体32dが端面S3から露出している部分までの高さである。このとき、H1は、H2の1.27倍以下である。

【0027】

(電子部品の製造方法)

次に、電子部品10の製造方法について説明する。なお、図面は、図3及び図4を参照する。

【0028】

まず、BaTiO3等のセラミック粉末に対して、バインダ及び有機溶剤を加えてボールミルに投入し、湿式調合を行って、セラミックスラリーを得る。得られたセラミックスラリーをドクターブレード法により、キャリアシート上にシート状に形成して乾燥させ、セラミック層17となるべきセラミックグリーンシートを作製する。セラミック層17となるべきセラミックグリーンシートの厚さは、焼成後のセラミック層の厚さが0.5μm以上10μm以下となる厚さであることが好ましい。なお、セラミック粉末の主成分は、CaTiO3,SrTiO3,CaZrO3等であってもよい。また、セラミック粉末の副成分として、Mn化合物、Mg化合物、Si化合物、Co化合物、Ni化合物、希土類化合物等が添加されていてもよい。

【0029】

次に、セラミック層17となるべきセラミックグリーンシート上に、導電性材料からなるペーストをスクリーン印刷法で塗布することにより、コンデンサ導体30,32を形成する。導電性材料からなるペーストは、金属粉末に、有機バインダ及び有機溶剤が加えられたものである。金属粉末は、例えば、Ni、Cu、Ag、Pd、Ag−Pd合金、Au等である。焼成後のコンデンサ導体30,32の厚さは、0.3μm以上2.0μm以下であることが好ましい。

【0030】

次に、セラミック層17となるべきセラミックグリーンシートを積層して未焼成のマザー積層体を得る。この後、未焼成のマザー積層体に対して、プレスを施す。

【0031】

次に、未焼成のマザー積層体を所定寸法にカットして、複数の未焼成の積層体11を得る。この後、積層体11の表面に、バレル研磨加工等の研磨加工を施す。

【0032】

次に、未焼成の積層体11を焼成する。焼成温度は、例えば、1200〜1300℃である。

【0033】

次に、積層体11に外部電極12を形成する。具体的には、周知のディップ法やスリット工法等により、積層体11の表面にCu、Ni、Ag、Pd、Ag−Pd合金、Au等を含有する導電性ペーストを塗布する。そして、下地電極を焼付けを行って、下地電極を形成する。下地電極上には、Niめっき及びSnめっきを施す。これにより、外部電極12が形成される。以上の工程により、電子部品10が完成する。

【0034】

以上のように製造された電子部品10は、回路基板50上に実装される。基板本体52は、例えば、ガラスエポキシ等からなる絶縁体層が複数積層されて構成されている。また、ランド電極54は、Cuからなる下地電極にめっきが施されて構成されている。実装時には、ランド電極54にはんだペーストを塗布する。次に、底面S2が基板本体52の主面S11と対向するように、ランド電極54上に外部電極12をセットする。この際、底面S2と主面S11とは平行になっていることが好ましい。この後、リフロー工程を行ってはんだペーストを溶融させた後、はんだペーストを固化させる。これにより、電子部品10が回路基板50上に実装される。

【0035】

なお、はんだペーストには、例えば、Sn−Pb共晶はんだや、Sn−Ag−Cu等の鉛フリーはんだを用いることが可能である。また、はんだ60の代わりに導電性接着剤が用いられてもよい。

【0036】

(効果)

以上の実装構造1によれば、以下に説明するように、回路設計において高い自由度を得つつ、鳴きを低減することができる。図5は、実装構造1において、電子部品10が振動している様子を示した図である。

【0037】

特許文献1に記載の積層セラミックコンデンサの回路基板実装方法では、鳴きの低減のために、二つのコンデンサが回路基板の両面に実装されているので、回路設計の自由度が低くなるという問題があった。

【0038】

そこで、実装構造1では、ランド電極54a,54bのz軸方向の正方向側の面からはんだ60a,60bの頂上までの高さ(フィレット高さ)H1は、ランド電極54a,54bから回路基板50の最も近くに位置するコンデンサ導体32dが端面S3から露出している部分までの高さH2の1.27倍以下とされている。これにより、実装構造1は、以下に説明するように、電子部品10を二つ用いることなく、鳴きの低減を実現できる。

【0039】

より詳細には、実装構造1では、コンデンサ導体30,32が設けられている部分において発生した振動がはんだ60及びランド電極54を伝搬されることによって、回路基板50が振動して鳴きが発生する。図5に示すように、電子部品10は、端面S3,S4のz軸方向の中心に近づくにしたがって大きく振動する。そこで、実装構造1では、振動の伝搬経路となっているはんだ60は、振動源である端面S3,S4のz軸方向の中心から離されている。これにより、電子部品10において発生した振動が回路基板50に伝搬されにくくなる。その結果、実装構造1では、鳴きが低減される。

【0040】

(実験)

本願発明者は、実装構造1が奏する効果をより明確にするために、以下に説明する実験を行った。具体的には、本願発明者は、以下に説明する第1の試料群及び第2の試料群を作製した。なお、第1の試料群及び第2の試料群では、以下の条件に示すように、フィレット高さH1を複数種類に変更した。

【0041】

第1の試料群の条件

回路基板のサイズ:100mm×40mm×1.6mm

電子部品の外形寸法:1.75mm×0.95mm×0.91mm

電子部品の容量:22μF

セラミック層の厚み:0.94μm

コンデンサ導体の厚み:0.58μm

コンデンサ導体の枚数:491

積層体の高さH0(図1参照):0.87mm

フィレット高さ:0.08mm、0.16mm、0.32mm、0.5mm、0.6mm、0.8mmの6種類

外部電極とランド電極との隙間H3(図1参照):0.05mm

外部電極の厚みH4(図1参照):20μm

回路基板の最も近くに位置する外部電極から積層体の底面までの距離(外層厚)H5(図1参照):56μm

【0042】

なお、第1の試料群では、ランド電極から回路基板の最も近くに位置するコンデンサ導体が端面から露出している部分までの高さH2は、H3、H4及びH5の合計(126μm)である。

【0043】

第2の試料群の条件

回路基板のサイズ:100mm×40mm×1.6mm

電子部品の外形寸法:2.11mm×1.35mm×1.31mm

電子部品の容量:47μF

セラミック層の厚み:0.94μm

コンデンサ導体の厚み:0.62μm

コンデンサ導体の枚数:671

積層体の高さH0(図1参照):1.26mm

フィレット高さ:0.08mm、0.21mm、0.4mm、0.75mm、1.2mmの5種類

外部電極とランド電極との隙間H3(図1参照):0.05mm

外部電極の厚みH4(図1参照):25μm

回路基板の最も近くに位置する外部電極から積層体の底面までの距離(外層厚)H5(図1参照):90μm

【0044】

なお、第2の試料群では、ランド電極から回路基板の最も近くに位置するコンデンサ導体が端面から露出している部分までの高さH2は、H3、H4及びH5の合計(165μm)である。

【0045】

以上のように構成された第1の試料群及び第2の試料群を用いて、音圧レベルの抑制量を測定した。図6は、音圧レベルの測定装置71の構成図である。

【0046】

本願発明者は、実装構造1(第1の試料群及び第2の試料群)を無響箱73内に設置し、電子部品10に対して、3kHzの周波数及び1Vppの電圧を有する交流電圧を印加した。そして、その際に発生する鳴きを集音マイク74で集音し、集音計76及びFETアナライザ78(株式会社小野測器製 CF−5220)で集音された音の音圧レベルを測定した。集音マイク74は、回路基板50から3mmだけ離して設置した。図7は、実験結果を示したグラフである。縦軸は、音圧レベルの抑制量を示し、横軸は、H1/H2の値を示している。音圧レベルの抑制量とは、H1/H2=8のときの音圧レベルに対する抑制量である。

【0047】

図7によれば、第1の試料群及び第2の試料群共に、H1/H2が1.27以下である場合には、H1/H2が1.27より大きい場合に比べて、音圧レベルの抑制量が飛躍的に大きくなっていることが分かる。よって、本実験によれば、H1をH2の1.27倍以下とすることによって、鳴きを低減できることが理解できる。

【0048】

(第1の変形例、図8参照)

以下に、第1の変形例である実装構造1aについて図面を参照しながら説明する。図8は、第1の変形例である実装構造1aの断面構造図である。

【0049】

本実装構造1aと前記実装構造1との相違点は、コンデンサ導体30,32の位置である。より詳細には、実装構造1aのコンデンサ導体30,32は、実装構造1のコンデンサ導体30,32よりもz軸方向の正方向側に位置している。即ち、底面S2とコンデンサ導体32dとの距離は、上面S1とコンデンサ導体30aとの距離よりも大きい。これにより、実装構造1aでは実装構造1よりも、ランド電極54a,54bから回路基板50の最も近くに位置するコンデンサ導体32dが端面S3から露出している部分までの高さH2が大きくなる。その結果、実装構造1aでは実装構造1よりもH1/H2が小さくなる。よって、実装構造1aでは、より効果的に鳴きが低減される。

【0050】

(第2の変形例、図9参照)

次に、第2の変形例である実装構造1bについて図面を参照しながら説明する。図9(A),(B)はそれぞれ実装構造1bに用いられる電子部品10bを示している。

【0051】

前記第1の変形例で用いられている電子部品1aでは、底面S2とコンデンサ導体32dとの距離を、上面S1とコンデンサ導体30aとの距離よりも大きくしているため、つまり、下側の外層部分が上側の外層部分よりも厚く、非対称になるため、電子部品10aの製造工程においてマザー積層体としたときに、熱が加わるとマザー積層体が全体的に反ってしまい、加工できなくなるおそれがある。

【0052】

そこで、本第2の変形例である実装構造1bでは、適宜枚数のダミー導体31を、底面S2とコンデンサ導体32dとの間のセラミック層に設けるようにした。ダミー導体31は、図9(A)に示すように、x軸方向の中央部分で分離され、両端部が外部電極12a,12bに接続されていてもよく、あるいは、図9(B)に示すように、外部電極12a,12bとは接続されることなく、x軸方向の中央部分に電気的には絶縁状態で配置されていてもよい。また、ダミー導体31は、外部電極12a,12bいずれかのみと接続されていてもよい。

【0053】

第2の変形例によれば、積層体11において、比較的厚みのあるセラミック層のみからなる下側の外層部分にダミー導体31を設けため、該外層部分が硬くなり、積層体11が反ってしまう不具合を解消できる。

【0054】

(第3の変形例、図10及び図11参照)

以下に、第3の変形例である実装構造1cについて図面を参照しながら説明する。図10は、第3の変形例である実装構造1cを平面視した図である。

【0055】

本実装構造1cと前記実装構造1との相違点は、ランド電極54の構造である。実装構造1cでは、ランド電極54aは、ランド部70a,72aに分割されている。ランド部70a,72aは、長方形状をなしており、y軸方向の負方向側から正方向側へとこの順に並んでいる。そして、ランド部70a,72aはそれぞれ、z軸方向(基板本体50の法線方向)から平面視したときに、積層体11の隣り合う角と重なっている。より詳細には、ランド部70a,72aは、z軸方向から平面視したときに、積層体11のx軸方向の負方向側の短辺の両端に位置する角と重なっている。ランド部70a,72aはそれぞれ、はんだ61a,62aを介して外部電極12aに接続されている。

【0056】

但し、ランド部70a,72aは、z軸方向から平面視したときに、端面S3の中心(対角線の交点)と重なっていない。よって、はんだ61a,62aは、z軸方向から平面視したときに、端面S3の中心とは重なっていない。

【0057】

また、ランド電極54bは、ランド部70b,72bに分割されている。ランド部70b,72bは、長方形状をなしており、y軸方向の負方向側から正方向側へとこの順に並んでいる。そして、ランド部70b,72bはそれぞれ、z軸方向(基板本体50の法線方向)から平面視したときに、積層体11の隣り合う角と重なっている。より詳細には、ランド部70b,72bは、z軸方向から平面視したときに、積層体11のx軸方向の正方向側の短辺の両端に位置する角と重なっている。ランド部70b,72bはそれぞれ、はんだ61b,62bを介して外部電極12bに接続されている。

【0058】

但し、ランド部70b,72bは、z軸方向から平面視したときに、端面S4の中心(対角線の交点)と重なっていない。よって、はんだ61b,62bは、z軸方向から平面視したときに、端面S4の中心とは重なっていない。

【0059】

実装構造1cは、以下に説明するように、前記実装構造1よりも鳴きを低減できる。実装構造1cでは、ランド電極54はそれぞれ、ランド部70,72に分割されている。これにより、実装構造1cにおいて外部電極12とランド電極54とがはんだ61,62により接続されている面積は、実装構造1において外部電極12とランド電極54とがはんだ60により接続されている面積よりも小さくなる。その結果、実装構造1cでは、実装構造1よりも、電子部品10で発生した振動が回路基板50に伝達されにくくなる。その結果、実装構造1cでは、実装構造1よりも鳴きが低減される。

【0060】

また、電子部品10に交流電圧が印加されると、端面S3,S4の中心(対角線の交点)が大きく振動する。そのため、端面S3,S4の中心の直下がランド電極54に固定されていると、電子部品10から回路基板50に振動が伝わりやすい。そこで、電子部品10では、ランド電極54がランド部70,72に分割されている。ランド部70,74は、z軸方向から平面視したときに、端面S3,S4の中心とは重なっていない。よって、はんだ61,62は、z軸方向から平面視したときに、端面S3,S4の中心とは重なっていない。これにより、電子部品10から回路基板50に振動が伝わることが抑制されている。

【0061】

本願発明者は、実装構造1cが奏する効果をより明確にするために、以下に説明する実験を行った。より詳細には、本願発明者は、以下に説明する第1のサンプル及び第2のサンプルを作製し、第1のサンプル及び第2のサンプルの電子部品10に対して1Vppの電圧を有する交流電圧を印加し、周波数を変化させながら音圧を測定した。

【0062】

第1のサンプルは、図1に示す実装構造1である。第2のサンプルは、図10に示す実装構造1cである。図11は、実験結果を示したグラフである。縦軸は、音圧レベルを示し、横軸は、周波数を示している。

【0063】

図11によれば、第1のサンプルの音圧レベルよりも第2のサンプルの音圧レベルの方が小さくなっていることが分かる。即ち、ランド電極54が分割されることによって、鳴きが低減されていることが理解できる。

【0064】

(第2の実施形態、図12〜図15参照)

以下に、第2の実施形態である実装構造2について図面を参照しながら説明する。図12は、第2の実施形態である実装構造2の断面構造図である。図13は、図12の実装構造2をz軸方向の正方向側から平面視した図である。

【0065】

本実装構造2と前記実装構造1との相違点は、電子部品10の向きである。実装構造2では、積層方向と直交する方向の一方側に位置する側面S5が実装面である。本第2の実施形態では、積層方向をy軸方向と定義する。また、積層体11をy軸方向から平面視したときに、積層体11の長辺が延在している方向をx軸方向と定義する。積層体11をy軸方向から平面視したときに、積層体11の短辺が延在している方向をz軸方向と定義する。

【0066】

また、図13に示すように、実装構造2では、ランド電極54aは、ランド部70a,72aに分割されている。ランド部70a,72aは、長方形状をなしており、y軸方向の負方向側から正方向側へとこの順に並んでいる。そして、ランド部70a,72aはそれぞれ、z軸方向(基板本体50の法線方向)から平面視したときに、積層体11の隣り合う角と重なっている。より詳細には、ランド部70a,72aは、z軸方向から平面視したときに、積層体11のx軸方向の負方向側の短辺の両端に位置する角と重なっている。ランド部70a,72aはそれぞれ、はんだ61a,62aを介して外部電極12aに接続されている。

【0067】

但し、ランド部70a,72aは、z軸方向から平面視したときに、端面S3の中心(対角線の交点)と重なっていない。よって、はんだ61a,62aは、z軸方向から平面視したときに、端面S3の中心とは重なっていない。

【0068】

また、ランド電極54bは、ランド部70b,72bに分割されている。ランド部70b,72bは、長方形状をなしており、y軸方向の負方向側から正方向側へとこの順に並んでいる。そして、ランド部70b,72bはそれぞれ、z軸方向(基板本体50の法線方向)から平面視したときに、積層体11の隣り合う角と重なっている。より詳細には、ランド部70b,72bは、z軸方向から平面視したときに、積層体11のx軸方向の正方向側の短辺の両端に位置する角と重なっている。ランド部70b,72bはそれぞれ、はんだ61b,62bを介して外部電極12bに接続されている。

【0069】

但し、ランド部70b,72bは、z軸方向から平面視したときに、端面S4の中心(対角線の交点)と重なっていない。よって、はんだ61b,62bは、z軸方向から平面視したときに、端面S4の中心とは重なっていない。

【0070】

(効果)

以上の実装構造2によれば、以下に説明するように、回路設計において高い自由度を得つつ、鳴きを低減することができる。図14は、実装構造2において、電子部品10が振動している様子を示した図である。

【0071】

実装構造2では、電子部品10に交流電圧が印加されると、図14に示すように、端面S3,S4の中心(対角線の交点)が大きく振動する。そのため、端面S3,S4の中心の直下(z軸方向の負方向側)がランド電極54に固定されていると、電子部品10から回路基板50に振動が伝わりやすい。そこで、実装構造2では、ランド電極54がランド部70,72に分割されている。ランド部70,72は、z軸方向から平面視したときに、振動源である端面S3,S4の中心とは重なっていない。よって、はんだ61,62は、z軸方向から平面視したときに、振動源である端面S3,S4の中心とは重なっていない。即ち、実装構造2では、振動の伝搬経路となっているはんだ61,62は、振動源である端面S3,S4の中心から離されている。これにより、電子部品10において発生した振動が回路基板50に伝搬されにくくなる。その結果、実装構造2では、鳴きが低減される。

【0072】

本願発明者は、実装構造2が奏する効果をより明確にするために、以下に説明する実験を行った。より詳細には、本願発明者は、以下に説明する第3のサンプル及び第4のサンプルを作製し、第3のサンプル及び第4のサンプルの電子部品10に対して1Vppの電圧を有する交流電圧を印加し、周波数を変化させながら音圧を測定した。

【0073】

第3のサンプルは、図12に示す実装構造2である。第4のサンプルは、図12及び図14に示す実装構造2において、ランド電極54が分割されていない回路基板に電子部品10が図12に示すように実装された実装構造である。図15は、実験結果を示したグラフである。縦軸は、音圧レベルを示し、横軸は、周波数を示している。

【0074】

図15によれば、第4のサンプルの音圧レベルよりも第3のサンプルの音圧レベルの方が小さくなっていることが分かる。これにより、実装構造2において、ランド電極54が分割されることによって、鳴きが低減されていることが理解できる。

【0075】

(他の実施形態)

なお、本発明に係る実装構造は、前記実施形態に限定するものではなく、その要旨の範囲内で種々に変更することができる。

【0076】

特に、前記第2実施形態(図12〜図15参照)において、二つのランド部に分割されているランド電極54a,54bは、いずれか一方のみが分割されているだけであってもよい。

【産業上の利用可能性】

【0077】

以上のように、本発明は、電子部品の実装構造に有用であり、特に、回路設計において高い自由度を得つつ、鳴きを低減することができる点で優れている。

【符号の説明】

【0078】

C コンデンサ

S1 上面

S2 底面

S3,S4 端面

S5,S6 側面

1,1a〜1c,2 実装構造

10 電子部品

11 積層体

12a,12b 外部電極

17a〜17n セラミック層

30a〜30d,32a〜32d コンデンサ導体

50 回路基板

52 基板本体

54a,54b ランド電極

60a,60b,61a,61b,62a,62b はんだ

70a,70b,72a,72b ランド部

【特許請求の範囲】

【請求項1】

電子部品が基板上に実装されている実装構造であって、

前記電子部品は、

複数の誘電体層が積層されて構成されている積層体であって、前記基板に対向し、かつ、積層方向の一方側に位置する実装面、並びに、互いに対向する第1の端面及び第2の端面を有する直方体状の積層体と、

前記誘電体層と共に積層されることによってコンデンサを形成し、かつ、前記第1の端面又は前記第2の端面に引き出されている複数のコンデンサ導体と、

前記第1の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第1の外部電極と、

前記第2の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第2の外部電極と、

を備えており、

前記基板は、

基板本体と、

前記基板本体上に設けられている第1のランド電極及び第2のランド電極であって、前記第1の外部電極及び前記第2の外部電極のそれぞれと導電性材料により接続されている第1のランド電極及び第2のランド電極と、

を備えており、

前記第1のランド電極又は前記第2のランド電極から前記導電性材料の頂上までの高さは、前記第1のランド電極又は前記第2のランド電極から前記コンデンサ導体が前記第1の端面又は前記第2の端面から露出している部分までの最短距離の1.27倍以下であること、

を特徴とする実装構造。

【請求項2】

前記第1のランド電極又は前記第2のランド電極から前記コンデンサ導体が前記第1の端面又は前記第2の端面から露出している部分までの最短距離は、該第1のランド電極又は該第2のランド電極から前記基板の最も近くに位置する前記コンデンサ導体が該第1の端面又は該第2の端面から露出している部分までの高さであること、

を特徴とする請求項1に記載の実装構造。

【請求項3】

前記第1のランド電極は、第1のランド部及び第2のランド部に分割されており、

前記第1のランド部及び前記第2のランド部は、前記基板本体の法線方向から平面視したときに、前記積層体の隣り合う角と重なっていること、

を特徴とする請求項1又は請求項2のいずれかに記載の実装構造。

【請求項4】

前記導電性材料は、はんだであること、

を特徴とする請求項1ないし請求項3のいずれかに記載の実装構造。

【請求項5】

前記実装面と該実装面に最も近い前記コンデンサ導体までの距離は、前記実装面と対向する面と該面に最も近い前記コンデンサ導体までの距離よりも大きいこと、

を特徴とする請求項1ないし請求項4のいずれかに記載の実装構造。

【請求項6】

前記実装面と該実装面に最も近い前記コンデンサ導体との間に、ダミー導体が設けられていること、

を特徴とする請求項5に記載の実装構造。

【請求項7】

電子部品が基板上に実装されている実装構造であって、

前記電子部品は、

複数の誘電体層が積層されて構成されている積層体であって、前記基板に対向し、かつ、積層方向と直交する方向の一方側に位置する実装面、並びに、互いに対向する第1の端面及び第2の端面を有する直方体状の積層体と、

前記誘電体層と共に積層されることによってコンデンサを形成し、かつ、前記第1の端面又は前記第2の端面に引き出されている複数のコンデンサ導体と、

前記第1の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第1の外部電極と、

前記第2の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第2の外部電極と、

を備えており、

前記基板は、

基板本体と、

前記基板本体上に設けられている第1のランド電極及び第2のランド電極であって、前記第1の外部電極及び前記第2の外部電極のそれぞれと導電性材料により接続されている第1のランド電極及び第2のランド電極と、

を備えており、

前記第1のランド電極は、第1のランド部及び第2のランド部に分割されており、

前記第1のランド部及び前記第2のランド部は、前記基板本体の法線方向から平面視したときに、前記第1の端面の中心とは重なっておらず、

前記導電性材料は、前記基板本体の法線方向から平面視したときに、前記第1の端面の中心とは重なっていないこと、

を特徴とする実装構造。

【請求項1】

電子部品が基板上に実装されている実装構造であって、

前記電子部品は、

複数の誘電体層が積層されて構成されている積層体であって、前記基板に対向し、かつ、積層方向の一方側に位置する実装面、並びに、互いに対向する第1の端面及び第2の端面を有する直方体状の積層体と、

前記誘電体層と共に積層されることによってコンデンサを形成し、かつ、前記第1の端面又は前記第2の端面に引き出されている複数のコンデンサ導体と、

前記第1の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第1の外部電極と、

前記第2の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第2の外部電極と、

を備えており、

前記基板は、

基板本体と、

前記基板本体上に設けられている第1のランド電極及び第2のランド電極であって、前記第1の外部電極及び前記第2の外部電極のそれぞれと導電性材料により接続されている第1のランド電極及び第2のランド電極と、

を備えており、

前記第1のランド電極又は前記第2のランド電極から前記導電性材料の頂上までの高さは、前記第1のランド電極又は前記第2のランド電極から前記コンデンサ導体が前記第1の端面又は前記第2の端面から露出している部分までの最短距離の1.27倍以下であること、

を特徴とする実装構造。

【請求項2】

前記第1のランド電極又は前記第2のランド電極から前記コンデンサ導体が前記第1の端面又は前記第2の端面から露出している部分までの最短距離は、該第1のランド電極又は該第2のランド電極から前記基板の最も近くに位置する前記コンデンサ導体が該第1の端面又は該第2の端面から露出している部分までの高さであること、

を特徴とする請求項1に記載の実装構造。

【請求項3】

前記第1のランド電極は、第1のランド部及び第2のランド部に分割されており、

前記第1のランド部及び前記第2のランド部は、前記基板本体の法線方向から平面視したときに、前記積層体の隣り合う角と重なっていること、

を特徴とする請求項1又は請求項2のいずれかに記載の実装構造。

【請求項4】

前記導電性材料は、はんだであること、

を特徴とする請求項1ないし請求項3のいずれかに記載の実装構造。

【請求項5】

前記実装面と該実装面に最も近い前記コンデンサ導体までの距離は、前記実装面と対向する面と該面に最も近い前記コンデンサ導体までの距離よりも大きいこと、

を特徴とする請求項1ないし請求項4のいずれかに記載の実装構造。

【請求項6】

前記実装面と該実装面に最も近い前記コンデンサ導体との間に、ダミー導体が設けられていること、

を特徴とする請求項5に記載の実装構造。

【請求項7】

電子部品が基板上に実装されている実装構造であって、

前記電子部品は、

複数の誘電体層が積層されて構成されている積層体であって、前記基板に対向し、かつ、積層方向と直交する方向の一方側に位置する実装面、並びに、互いに対向する第1の端面及び第2の端面を有する直方体状の積層体と、

前記誘電体層と共に積層されることによってコンデンサを形成し、かつ、前記第1の端面又は前記第2の端面に引き出されている複数のコンデンサ導体と、

前記第1の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第1の外部電極と、

前記第2の端面及び前記実装面に跨って設けられ、かつ、前記コンデンサ導体と接続されている第2の外部電極と、

を備えており、

前記基板は、

基板本体と、

前記基板本体上に設けられている第1のランド電極及び第2のランド電極であって、前記第1の外部電極及び前記第2の外部電極のそれぞれと導電性材料により接続されている第1のランド電極及び第2のランド電極と、

を備えており、

前記第1のランド電極は、第1のランド部及び第2のランド部に分割されており、

前記第1のランド部及び前記第2のランド部は、前記基板本体の法線方向から平面視したときに、前記第1の端面の中心とは重なっておらず、

前記導電性材料は、前記基板本体の法線方向から平面視したときに、前記第1の端面の中心とは重なっていないこと、

を特徴とする実装構造。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−65820(P2013−65820A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2012−133216(P2012−133216)

【出願日】平成24年6月12日(2012.6.12)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成24年6月12日(2012.6.12)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]