実装評価構造及び実装評価方法

【課題】 目視に頼ることなく、基板に対するチップの実装状態を三次元的に評価することができる実装評価構造及び実装評価方法を提供するものである。

【解決手段】 実装評価構造は、実装評価用基板10の実装面10aに配設される複数の第1の電極パターン30aと、当該各第1の電極パターン30aにそれぞれ対向して実装評価用チップ20の下面20aに配設される複数の第2の電極パターン30bと、からなる複数の静電容量部30を形成し、複数の静電容量部30における静電容量を比較し、当該比較結果に基づき、実装評価用基板10に対する実装評価用チップ20の実装状態を評価する。

【解決手段】 実装評価構造は、実装評価用基板10の実装面10aに配設される複数の第1の電極パターン30aと、当該各第1の電極パターン30aにそれぞれ対向して実装評価用チップ20の下面20aに配設される複数の第2の電極パターン30bと、からなる複数の静電容量部30を形成し、複数の静電容量部30における静電容量を比較し、当該比較結果に基づき、実装評価用基板10に対する実装評価用チップ20の実装状態を評価する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、フリップチップボンディング法によって、チップが基板に実装される状態を評価するための実装評価構造及び実装評価方法に関し、特に、フリップチップボンディングの実装機(以下、フリップチップボンダと称す)のボンディング精度を評価するための実装評価構造及び実装評価方法に関する。

【背景技術】

【0002】

従来のフリップチップ実装評価方法は、バンプ付きLSIチップを配線基板にフリップチップ実装する工程を評価する際、透明ガラスからなり且つ寸法形状が製品のLSIチップと同じダミーチップの片面に製品のバンプと同じバンプが製品のバンプ付きLSIチップと同じ配列で且つ同じバンプ下地金属膜を介して形成されたバンプ付きダミーチップを使用してフリップチップ実装のトライアルを行い、トライアル品のボンディング部分とその周辺をダミーチップを透して目視により観察することで、ボンディング位置精度、バンプ接続形状等をチェックする(例えば、特許文献1参照)。

【0003】

また、フリップチップボンダに関する技術分野に属するものではないが、静電容量に基づいてアライメント誤差を測定する素子も知られている。例えば、特許文献2では、下地絶縁層上にY方向に延びる下層導電膜が形成され、さらにその上に絶縁層が形成されている。絶縁層上に、下層導電膜に隣接し、かつY方向に延びる帯状の上層導電膜が形成されている。また、特許文献3に記載された従来のマスクとウェハ間の間隙測定装置は、マスクのウェハに対向する面側と、ウェハのマスクに対向する面側とのいずれか一方に、電極パターンを作成し、該電極パターンを含む静電容量形位置センサを備えている。

【特許文献1】特開2001−68514号公報

【特許文献2】特開2003−172601号公報

【特許文献3】特開昭63−107022号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、従来のフリップ実装評価方法は、目視によりフリップ実装工程の評価を行なうものであり、必ずしも精確ではなく、ボンディング部分の欠陥を見過ごしてしまう恐れがあるという課題があった。

【0005】

特に、従来のフリップ実装評価方法は、透明なダミーチップを透かしてのボンディング部分の目視確認により、ボンディング位置精度をチェックするものであり、x−y平面上の位置ずれ(二次元的な変位)はチェックできるのであるが、z方向の位置ずれ(三次元的な変位)はチェックすることができないという課題があった。

【0006】

なお、従来の半導体装置におけるアライメント誤差の測定素子は、ボンディング精度を評価するものではなく、フォトリソグラフィ技術を用いて加工したエッチングマスクの合わせずれ量(アライメント誤差)を測定するものである。すなわち、従来の測定素子によるアライメント誤差の測定は、層間絶縁膜で形成されるキャパシタ自体の容量値の変化で検出するため、z方向のずれ量を測定することができないという課題があった。

【0007】

ここで、複数のボールバンプをチップ上に形成した場合に、バンプ高さには、ばらつきが生じるものである。このため、チップが基板に実装され、チップと基板との平行度が保たれていたとしても、バンプ高さが最小値となるボールバンプの部分においては、当該ボールバンプを介してチップと基板とが接触(導通)していない場合があり得る。

【0008】

これに対し、従来のマスクとウェハ間の間隙測定装置は、対向する電極による静電容量に基づき、マスクとウェハ間の間隙を測定できるのであるが、この間隙測定装置の特徴を、フリップチップボンダに単に適用したのみでは、チップと基板との導通状態を評価するという思想に容易に想到できないものと考えられる。

【0009】

この発明は、上述のような課題を解決するためになされたもので、目視に頼ることなく、基板に対するチップの実装状態を三次元的に評価することができる実装評価構造及び実装評価方法を提供するものである。

【課題を解決するための手段】

【0010】

この発明に係る実装評価構造においては、基板に配設される複数の第1の電極パターンと、当該各第1の電極パターンにそれぞれ対向してチップに配設される複数の第2の電極パターンと、からなる複数の静電容量部を形成し、当該複数の静電容量部における静電容量を比較し、当該比較結果に基づき、前記基板に対する前記チップの実装状態を評価するものである。

【発明の効果】

【0011】

この発明に係る実装評価構造においては、基板に配設される複数の第1の電極パターンと、当該各第1の電極パターンにそれぞれ対向してチップに配設される複数の第2の電極パターンと、からなる複数の静電容量部を形成し、当該複数の静電容量部における静電容量を比較し、当該比較結果に基づき、前記基板に対する前記チップの実装状態を評価することにより、従来のフリップ実装評価方法のような光学的な測定ではなく、電気的な測定により、精確かつ短時間に、基板に対するチップの実装状態を評価することができる。

【発明を実施するための最良の形態】

【0012】

(本発明の第1の実施形態)

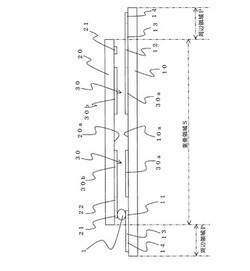

図1は第1の実施形態に係る実装評価用基板の概略構成を示す平面図、図2は第1の実施形態に係る実装評価用チップの概略構成を示す平面図、図3は図1に示す実装評価用基板及び図2に示す実装評価用チップのボンディング状態の矢視A−A線の断面図、図4はブリッジ回路を構成することによる測定方法を説明するための説明図、図5は応力評価用パターンの一例を示す平面図である。

【0013】

RS(reference substrate)である実装評価用基板10は、図1に示すように、後述する実装評価用チップ20のボールバンプ1に対応する複数のパッド(以下、第1のパッド11と称す)が実装面10aに配設され、実装評価用チップ20がフリップチップボンディング法によって実装される。

【0014】

なお、以下の説明においては、実装評価用基板10の実装面10aに実装評価用チップ20を実装した場合に、実装面10aにおける実装評価用チップ20の重畳する領域を重畳領域Sと称し、実装面10aにおける重畳領域S以外の領域を周辺領域Pと称して説明する。また、実装評価用基板10及び実装評価用チップ20を総称して、実装評価装置100と称す。

【0015】

また、本実施形態に係る実装評価用基板10は、基材として、平面形状を正方形とし、平面寸法を15.0mm×15.0mmとし、材質を石英ガラスとしたガラス基板を使用しているが、この仕様に限られるものではない。

【0016】

また、本実施形態に係る第1のパッド11は、平面形状を正方形とし、平面寸法を40μm×40μmとし、材質をAl−Si系合金とし、隣り合うパッド間の間隔を50μmとして、実装面10aの重畳領域Sの各辺に136個(合計544個)並設させているが、この仕様に限られるものではない。

【0017】

第1の電極パターン30aは、実装評価用基板10の実装面10aの重畳領域Sに配設され、重畳領域Sに配設される接続配線部(以下、第1の接続配線部12と称す)及び周辺領域Pに配設される引出配線部13を介して、実装面10aの周縁部に配設される外部端子14に接続されている。

【0018】

また、第1の電極パターン30aは、後述する第2の電極パターン30bに対向させて静電容量部30を形成するために、実装評価用基板10の実装面10aにおける所定の位置に配設される。特に、後述する本発明に係る作用効果を奏するためには、複数の静電容量部30が必要であるために、第1の電極パターン30aは、実装評価用基板10の実装面10aの重畳領域Sに複数配設させる。

【0019】

なお、本実施形態に係る第1の電極パターン30aは、平面形状を正方形とし、平面寸法を2.0mm×2.0mmとし、材質をAl−Si系合金として、実装面10aの重畳領域Sの各コーナー近傍に1つ(合計4つ)配設させているが、静電容量部30における所望の静電容量(例えば、測定装置の分解能である2pF)を得ることができるのであれば、この仕様に限られるものではない。

【0020】

外部端子14は、静電容量部30における静電容量を検出するための信号処理回路を備えた図示しない測定装置のプローブを当接させるために、実装評価用基板10の実装面10aにおいて露出させている。

【0021】

なお、本実施形態に係る外部端子14は、平面形状を長方形とし、平面寸法を1.5mm×0.7mmとし、材質をAl−Si系合金として、実装評価用基板10の実装面10aの各辺に10個(合計40個)並設させているが、この仕様に限られるものではない。

【0022】

また、本実施形態に係る複数の外部端子14は、隣り合う外部端子14の少なくとも片側の外部端子14が、グラウンド端子となるように配設することが好ましい。これにより、外部端子14である信号端子及びグラウンド端子に特性インピーダンスが整合された高周波プローブを接続することができ、第1の電極パターン30a及び第2の電極パターン30b間における正確な高周波インピーダンス測定を行なうことができる。

【0023】

なお、高周波プローブには、同軸構造とコプレーナ構造とがあり、特性インピーダンスは一般的に50Ωである。また、使用する測定装置と高周波プローブとによって測定可能な周波数帯域は異なるのであるが、例えば、高周波プローブとして、信号用電極とグラウンド用電極との間隔が0.5mm以下であるコプレーナ構造の高周波プローブを使用し、測定装置として、高周波ベクトルネットワークアナライザを使用すれば、20GHz程度までの高周波インピーダンス測定が可能となる。

【0024】

ちなみに、外部端子14である信号端子の近傍に、グラウンド端子を配設しない場合には、インピーダンス整合された高周波プローブを接続することができないために、高周波信号の反射損失及び挿入損失が大きく、正確な高周波インピーダンス測定が行なえない。この場合の測定可能な周波数の上限は、数10MHzが限界である。

【0025】

特に、2つの信号端子を挟んで両側にグラウンド端子をそれぞれ配設させることで、同時に4つの端子に接触できる、グランド−信号1−信号2−グランドの電極配置を持つ既存のコプレーナ高周波プローブを使用することが可能となる。これにより、1個のプローブに2本の信号線があるプローブが使用できるために、プローブを使用する本数は半減し、プローブの費用を削減できる。また、信号−グラウンドのみの電極配置を持つ既存のコプレーナ高周波プローブ(以下、単一線プローブと称す)を使用した場合と比較して、実装評価装置100に対するプローブ時間を半分に短縮することができる。また、2つの信号端子を同一のプローブで接触できるために、プローブと信号端子との機械的な接触位置が常に一定となり、単一線プローブで問題となる機械的な接触位置における不安定性に依存する測定の不安定状態を取り除くことができる。

【0026】

なお、本実施形態に係る実装評価用基板10は、図3に示すように、基材であるガラス基板上にAl−Si係合金の薄膜を成膜させ、所望の形状にパターニングすることで、第1の電極パターン30a、第1のパッド11、第1の接続配線部12、引出配線部13及び外部端子14を単層にて形成したものである。

【0027】

TEG(test element group)である実装評価用チップ20は、図2に示すように、下面20aの周縁部に沿って配設される複数のパッド(以下、第2のパッド21と称す)上に、複数のボールバンプ1がそれぞれ配設される。

【0028】

また、実装評価用チップ20は、ボールバンプ1が下面20aの中央領域には配置されず、周縁部近傍のみに配置される構成であり、周縁部における実装評価用基板10とのボンディング状態を評価するためのチップを利用している。

【0029】

なお、本実施形態に係る実装評価用チップ20は、基材として、平面形状を正方形とし、平面寸法を7.4mm×7.4mmとし、材質を石英ガラスとしたガラスチップを使用しているが、この仕様に限られるものではない。

【0030】

また、本実施形態に係る第2のパッド21は、平面形状を正方形とし、平面寸法を40μm×40μmとし、材質をAl−Si系合金とし、隣り合うパッド間の間隔を50μmとして、実装評価用チップ20の下面20aの各辺に136個(合計544個)並設させているが、この仕様に限られるものではない。

【0031】

第2の電極パターン30bは、実装評価用チップ20の下面20aに配設され、接続配線部(以下、第2の接続配線部22と称す)を介して第2のパッド21に接続されている。

また、第2の電極パターン30bは、実装評価用チップ20がフリップチップボンディング法によって実装評価用基板10に実装されることで、第2のパッド21上のボールバンプ1と実装評価用基板10上の第1のパッド11とが導通し、この第1のパッド11に接続する引出配線部13を介して外部端子14に接続される。

【0032】

また、第2の電極パターン30bは、第1の電極パターン30aに対向させて静電容量部30を形成するために、実装評価用チップ20の下面20aにおける所定の位置に配設される。特に、後述する本発明に係る作用効果を奏するためには、複数の静電容量部30が必要であるために、第2の電極パターン30bは、実装評価用チップ20の下面20aに複数配設させる。

【0033】

なお、本実施形態に係る第2の電極パターン30bは、平面形状を正方形とし、平面寸法を2.0mm×2.0mmとし、材質をAl−Si系合金として、実装評価用チップ20の下面20aの各コーナー近傍に1つ(合計4つ)配設させているが、静電容量部30における所望の静電容量(例えば、測定装置の分解能である2pF)を得ることができるのであれば、この仕様に限られるものではない。

【0034】

また、本実施形態に係る実装評価用チップ20は、図3に示すように、基材であるガラスチップ上にAl−Si係合金の薄膜を成膜させ、所望の形状にパターニングすることで、第2の電極パターン30b、第2のパッド21及び第2の接続配線部22を単層にて形成したものである。

【0035】

静電容量部30は、対向する第1の電極パターン30a及び第2の電極パターン30bを互いに同一の平面形状及び平面寸法とし、複数の静電容量部30(ここでは、4つの静電容量部30)の各第1の電極パターン30a及び各第2の電極パターン30bについても互いに同一の平面形状及び平面寸法としている。すなわち、全ての第1の電極パターン30a及び第2の電極パターン30bが同一の平面形状及び平面寸法としている。

【0036】

また、静電容量部30は、実装評価用基板10上に実装評価用チップ20が正常(実装評価用基板10と実装評価用チップ20とが略平行となる、正対した状態)にフリップチップボンディングされた場合に、実装評価用基板10に垂直な方向において、対向する第1の電極パターン30a及び第2の電極パターン30bが完全に重畳する構成である。

【0037】

すなわち、実装評価用基板10上に実装評価用チップ20が正常にフリップチップボンディングされた場合には、対向する第1の電極パターン30a及び第2の電極パターン30b間の距離が全ての静電容量部30において等しく、対向する第1の電極パターン30a及び第2の電極パターン30bの重畳する面積が全ての静電容量部30において等しいために、4つの静電容量部30における各静電容量は、全て等しい値となる。

【0038】

したがって、本実施形態に係る実装評価構造においては、複数の静電容量部30における各静電容量を測定し、全て等しい測定値であれば、実装評価用基板10上に実装評価用チップ20が正常にフリップチップボンディングされた実装状態であると判定できる。また、複数の静電容量部30における各静電容量が、全て等しい測定値でないならば、実装評価用基板10上に実装評価用チップ20が異常(傾斜した状態)にフリップチップボンディングされた実装状態であると判定できる。

【0039】

特に、本実施形態に係る実装評価構造においては、対向する第1の電極パターン30a及び第2の電極パターン30bの重畳する面積S、対向する第1の電極パターン30a及び第2の電極パターン30b間の誘電率ε、並びに、静電容量部30における静電容量Cの測定値に基づき、第1の電極パターン30a及び第2の電極パターン30b間の間隙dの値を算出する。そして、第1の電極パターン30a及び第2の電極パターン30b間の間隙dが、ボールバンプ1の形成における高さばらつきによるバンプ高さの最小値よりも小さい場合に、実装評価用チップ20と実装評価用基板10とが全てのボールバンプ1において接触状態(導通状態)であると判定できる。

【0040】

なお、本実施形態に係る実装評価装置100は、複数の静電容量部30を備えているのであれば、複数の静電容量部30における各静電容量の差分を算出することができるために、4つの静電容量部30を備える構成に限られるものではない。

【0041】

しかしながら、本実施形態に係る実装評価装置100が静電容量部30を2つだけ備えている場合には、この2つの静電容量部30を結んだ直線を回転軸として実装評価用チップ20が傾斜してフリップチップ実装された場合に、2つの静電容量部30における静電容量が等しい値となってしまうために、実装状態の異常を検出することができないことになる。

【0042】

したがって、本実施形態に係る実装評価装置100は、全ての静電容量部30が同一直線上に並設されない3つ以上の静電容量部30を備えていることが好ましい。

また、本実施形態に係る実装評価装置100は、4つの静電容量部30を備えることで、実装状態の評価にあたり、4つの静電容量部30を接続してブリッジ回路を構成させることが考えられる。

【0043】

この構成により、ブリッジ回路の一次側(一の対角)に電圧を与え、二次側(他の対角)の電圧を測定し、二次側の電圧が零(許容範囲を含む)である場合に、4つの静電容量部30における静電容量が平衡状態であるために、実装評価用基板10上に実装評価用チップ20が正常にフリップチップボンディングされた実装状態であると判定できる。

【0044】

なお、本実施形態に係る実装評価装置100は、ブリッジ回路を構成させるために、隣り合う静電容量部30を接続する配線パターン、ブリッジ回路の一次側(一の対角)に電圧を入力するための端子及び配線パターン、並びに、ブリッジ回路の二次側(他の対角)の電圧を測定するための端子及び配線パターンを、予め、実装評価用基板10の実装面10aに形成してもよい。

【0045】

なお、本実施形態に係る実装評価装置100は、静電容量部30の配置を特に限定するものではないが、実装評価用基板10の重畳領域S(実装評価用チップ20の下面20a)の各コーナー近傍に静電容量部30を配設することで、実装評価用チップ20が傾斜して実装された場合に、重畳領域Sの中央部分に静電容量部30を配設する場合と比較して、複数の静電容量部30における静電容量の差分が大きく検出でき、異常な実装状態を漏れなく検出できるために好ましい。

【0046】

つぎに、実装評価構造を用いた、実装評価用基板10に対する実装評価用チップ20の実装状態の評価方法について説明する。

まず、実装評価用チップ20及び実装評価用基板10は、ボンディング精度の検証の対象装置である図示しないフリップチップボンダに投入される。

【0047】

そして、実装評価用チップ20及び実装評価用基板10は、図示しないアライメントマークなどに基づき位置決めされ、実装評価用チップ20の第2のパッド21(ボールバンプ1)と実装評価用基板10の第1のパッド11とを対向して密着させ、熱及び圧力を加えて接合される。

【0048】

接合された実装評価用チップ20及び実装評価用基板10は、実装評価用基板10の外部端子14に図示しない測定装置のプローブが当接され、静電容量部30の対をなす第1の電極パターン30a及び第2の電極パターン30b間の静電容量を、4つの静電容量部30に対してそれぞれ測定される。なお、測定装置としては、Qメータ、LCRメーター又はインピーダンスアナライザなどの既存の測定装置を用いる。

【0049】

そして、4つの静電容量部30における静電容量の測定値に基づき、4つの静電容量部30の静電容量が全て等しい測定値であれば、実装評価用基板10に対して実装評価用チップ20が正常(正対した状態)に実装されていると判定する。

【0050】

これに対し、4つの静電容量部30における静電容量の測定値に基づき、4つの静電容量部30の静電容量が全て等しい測定値でないならば、実装評価用基板10に対して実装評価用チップ20が異常(傾斜した状態)に実装されていると判定する。

【0051】

なお、前述したように、4つの静電容量部30を接続してブリッジ回路を構成し、ブリッジ回路の一次側(一の対角)に電圧を与え、二次側(他の対角)の電圧を測定することによっても、実装評価用基板10に対する実装評価用チップ20の実装状態を評価することができる。

この場合には、例えば、図4に示すような回路構成にて、実装状態を評価することが考えられる。

【0052】

測定装置200は、プローブ201(201a〜201h)を外部端子14(14a〜14h)に当接させることで、4つの静電容量部30のうち、第1の静電容量部31の一の外部端子14a及び第4の静電容量部34の他の外部端子14h、第1の静電容量部31の他の外部端子14b及び第2の静電容量部32の一の外部端子14c、第2の静電容量部32の他の外部端子14d及び第3の静電容量部33の一の外部端子14e、第3の静電容量部33の他の外部端子14f及び第4の静電容量部34の一の外部端子14gをそれぞれ接続させ、ブリッジ回路2を構成する。

【0053】

また、第1の静電容量部31の外部端子14aと第4の静電容量部34の外部端子14hとの結合点ha、及び第2の静電容量部32の外部端子14dと第3の静電容量部33の外部端子14eとの結合点deには、測定装置200の交流電圧発生回路202から交流電圧が印加される。

【0054】

また、測定装置200の差動増幅回路203は、第1の静電容量部31の外部端子14bと第2の静電容量部32の外部端子14cとの結合点bcから供給される交流信号と、第3の静電容量部33の外部端子14fと第4の静電容量部34の外部端子14gとの結合点fgから供給される交流信号との差分成分を増幅する。

【0055】

このような構成により、結合点bcにおける交流信号と結合点fgにおける交流信号との差分信号が差動増幅回路203から出力されない場合には、ブリッジ回路2が平衡状態であることがわかる。

【0056】

なお、4つの静電容量部30における各静電容量に誤差を有しており、正常な実装状態であっても、差動増幅回路203から差分信号が出力される場合も考えられるために、差動増幅回路203から出力される差分信号に対して、正常な実装状態であると判断するための許容範囲を設定することが好ましい。

【0057】

すなわち、測定装置200の電圧コンパレータ回路204は、差動増幅回路203から出力される差分信号の電圧が、可変抵抗器205などによって設定される基準電圧よりも高い場合に、Hレベルの検出信号を出力する。

【0058】

また、電圧コンパレータ回路204は、差動増幅回路203から出力される差分信号の電圧が、可変抵抗器205などによって設定される基準電圧よりも低い場合に、Lレベルの検出信号を出力する。

【0059】

これにより、Hレベルの検出信号が出力された場合には、実装評価用基板10に対する実装評価用チップ20の実装状態が異常(傾斜した状態)であると判定でき、Lレベルの検出信号が出力された場合には、実装評価用基板10に対する実装評価用チップ20の実装状態が正常(正対した状態)であると判定できる。

【0060】

なお、ブリッジ回路2は、図4に示すように、測定装置200に接続することで、結合点ha及び結合点deに交流電圧が印加され、結合点bcにおける交流信号と結合点fgにおける交流信号との差分信号の有無を検出する回路構成としているが、結合点bc及び結合点fgに交流電圧が印加され、結合点haにおける交流信号と結合点deにおける交流信号との差分信号の有無を検出する回路構成としてもよい。これにより、ブリッジ回路2を用いた測定方法として、二通りの取り方が考えられる。

【0061】

なお、本実施形態に係る実装評価装置100においては、全ての第1の電極パターン30a及び第2の電極パターン30bを同一の平面形状及び平面寸法とする構成(各静電容量部30における第1の電極パターン30a及び第2の電極パターン30bの重畳する面積が一致する構成)にしているが、複数の静電容量部30の各第1の電極パターン30a及び各第2の電極パターン30bを互いに異なる平面形状及び平面寸法とする構成(各静電容量部30における第1の電極パターン30a及び第2の電極パターン30bの重畳する面積が異なる構成)であってもよい。

【0062】

この場合には、実装評価用基板10に対する実装評価用チップ20の実装状態が正常な状態における、複数の静電容量部30における各静電容量(第1の電極パターン30a及び第2の電極パターン30bの重畳する面積)を予め算出又は実測しておく。そして、予め算出又は実測した値に基づき、複数の静電容量部30における各静電容量の差分を零に補正する演算機能を測定装置に備えておくことで、前述した構成と同様に、実装状態を評価することができる。

【0063】

しかしながら、実装評価装置100は、静電容量部30の対向電極を統一性のある単純な形状にすることができるうえに、複数の静電容量部30における各静電容量の差分を零に補正する演算機能を測定装置に備える必要がないために、前述した、全ての第1の電極パターン30a及び第2の電極パターン30bを同一の平面形状及び平面寸法とする構成にすることが好ましい。

【0064】

なお、本実施形態に係る実装評価装置100においては、RSであるガラス基板に第1の電極パターン30a(第1の接続配線部12)を形成し、TEGであるガラスチップに第2の電極パターン30b(第2の接続配線部22)を形成することで、複数の静電容量部30における静電容量を測定できる構成にしているが、実製品である配線基板及び半導体チップに対して、対向する電極パターン等をそれぞれ形成し、複数の静電容量部30における静電容量を測定できる構成にしてもよい。

【0065】

この場合には、例えば、第1の電極パターン30a及び第2の電極パターン30bを、半導体チップに内蔵される演算部にそれぞれ接続し、当該演算部により複数の静電容量部30における各静電容量の差分を演算することで、実装評価用基板10に対する実装評価用チップ20の実装状態を評価する構成も考えられる。

【0066】

以上のように、複数の静電容量部30における各静電容量の差分を検出することで、実装評価用基板10に対する実装評価用チップ20の傾斜の有無を判断することができ、フリップチップボンダのボンディング精度を評価することができる。

【0067】

なお、本実施形態に係る実装評価装置100においては、静電容量部30の対をなす第1の電極パターン30a及び第2の電極パターン30b間の静電容量を少なくとも測定できる構成であればよいが、他の評価試験を併用できる構成としてもよい。

【0068】

例えば、実装評価用基板10の実装面10aの重畳領域Sにおけるコーナー近傍又は実装評価用チップ20の下面20aにおけるコーナー近傍に、バーニヤである応力評価用パターン3を配設させる構成としてもよい。この応力評価用パターン3は、例えば、図5に示すように、材質をCrとし、パターン長が60μmであり、パターン幅が4.8μmである矩形状のパターンを、幅方向に沿って9.75μmピッチで並設させ、4本間隔でパターンのパターン長を70μmとして突出させることで、目盛り形状としている。

【0069】

なお、本実施形態に係る実装評価用チップ20は透明なガラスチップを使用しているために、実装評価用チップ20の下面20aに、応力評価用パターン3を配設させる場合であっても、実装評価用基板10上に実装評価用チップ20を実装する前と実装した後の応力評価用パターン3をそれぞれ撮像することができ、画像処理して差分を比較することで、実装評価用チップ20に加わった応力の程度(歪み)を検出することができる。

【0070】

これに対し、不透明な実装評価用チップ20を使用した場合であっても、実装評価用チップ20の厚みが50μm以下となると、実装評価用チップ20に赤外線を透過させることができるため、同様に、実装評価用チップ20に加わった応力の程度(歪み)を検出することができる。

【0071】

特に、実装評価用基板10及び実装評価用チップ20の間隙に図示しないアンダーフィルが形成されることで、実装評価用チップ20の伸縮が生じることがあり、アンダーフィルによる実装評価用チップ20に加わる応力の程度を検出することができる。

【0072】

なお、アンダーフィルは、基板上に液体状の樹脂を塗布又はフィルム状の樹脂を敷設した後にチップを実装する先入れタイプと、基板上にチップを実装した後に液体状の樹脂を毛細管現象により注入する後入れタイプとがある。そこで、実装評価用基板10及び/又は実装評価用チップ20が透明であることは、実装評価用基板10及び実装評価用チップ20の間隙に挿入されるアンダーフィルの状態を視認できるという作用効果もある。

また、本実施形態に係る実装評価装置100の他の評価試験を併用できる構成として、以下の構成も考えられる。

【0073】

例えば、実装評価用基板10における隣り合う第1のパッド11間を交互にオープン又はショートとなるように非接続又は接続とし、実装評価用チップ20における隣り合う第2のパッド21間が実装評価用基板10における隣り合う第1のパッド11間の非接続又は接続に対して反転させて接続又は非接続とすることで、始端と終端とを有するチェーンをなす単線路を備えた構成としてもよい。

【0074】

この構成により、実装評価用基板10上に実装評価用チップ20を実装した場合に、単線路の始端から信号を入力し、終端における信号の有無を確認することで、この両端間における全ての第1のパッド11及び第2のパッド21間のボールバンプ1による導通状態を一度に評価することができる。ただし、単線路が断線していると判断できた場合であっても、断線している場所を特定することができない。特に、実装評価用チップ20の周縁部近傍における第1のパッド11及び第2のパッド21のボールバンプ1による接続箇所は数百箇所も存在するために、非導通となった第1のパッド11及び第2のパッド21を特定することは困難である。

【0075】

このため、第1のパッド11及び第2のパッド21間を固着するハンダにクラックが生じることによる接触不良や非導通の場所の特定にあたっては、時間領域反射(time domein reflectmetry:以下、TDRと称す)法を用いた検出方法が考えられる。このTDR法とは、線路インピーダンス、線路長、伝送速度を知ることができる測定法であり、立ち上がり時間が20〜50ps程度の高速スイッチング動作するステップ信号を伝送路に送り込み、その反射波形を高帯域な特性をもつオシロスコープで観測する。

【0076】

すなわち、実装評価装置100における第1のパッド11及び第2のパッド21を経由する単線路に、第1のパッド11及び第2のパッド21のボールバンプ1による接触不良や非導通が生じた場合には、単線路のインピーダンスが変動することとなり、TDR法により接触不良又は非導通の場所を特定することができる。特に、第1のパッド11及び第2のパッド21が非導通により単線路が断線している場合には、始端からの伝送路が最短長となる非導通箇所が終端となり、始端から入射した入射波が、この非導通箇所で反射して、始端で反射波を検出することとなる。

【0077】

なお、隣り合うボールバンプ1(第1のパッド11、第2のパッド21)間のピッチが狭すぎる場合(例えば、120μm)には、TDR法を用いて線路長を検出できない場合がある。このため、TDR法を用いて線路長を検出できる間隔で、第1のパッド11(第2のパッド21)間を接続することが好ましい。例えば、隣り合う第1のパッド11(第2のパッド21)間の間隔をdとし、TDR法を用いて線路長を検出できる間隔が2dであった場合に、接続する第1のパッド11(第2のパッド21)間の間隔が2dとなるように、隣り合う第1のパッド11(第2のパッド21)を接続せず1つ置きに、第1のパッド11(第2のパッド21)間を接続することで、接続する第1のパッド11(第2のパッド21)間の線路長を稼ぐことができる。そして、TDR法を用いて第1のパッド11及び第2のパッド21間の接触不良又は非導通の場所に目安を付け、目安を付けた場所近傍の断面形状を観察するなどの解析を行なうことで、第1のパッド11及び第2のパッド21間の接触不良又は非導通の場所を特定することができる。

【図面の簡単な説明】

【0078】

【図1】第1の実施形態に係る実装評価用基板の概略構成を示す平面図である。

【図2】第1の実施形態に係る実装評価用チップの概略構成を示す平面図である。

【図3】図1に示す実装評価用基板及び図2に示す実装評価用チップのボンディング状態の矢視A−A線の断面図である。

【図4】ブリッジ回路を構成することによる測定方法を説明するための説明図である。

【図5】応力評価用パターンの一例を示す平面図である。

【符号の説明】

【0079】

1 ボールバンプ

2 ブリッジ回路

3 応力評価用パターン

10 実装評価用基板

10a 実装面

11 第1のパッド

12 第1の接続配線部

13 引出配線部

14,14a,14b,14c,14d,14e,14f,14g,14h 外部端子

20 実装評価用チップ

20a 下面

21 第2のパッド

22 第2の接続配線部

30 静電容量部

30a 第1の電極パターン

30b 第2の電極パターン

31 第1の静電容量部

32 第2の静電容量部

33 第3の静電容量部

34 第4の静電容量部

100 実装評価装置

200 測定装置

201 プローブ

202 交流電圧発生回路

203 差動増幅回路

204 電圧コンパレータ回路

205 可変抵抗器

P 周辺領域

S 重畳領域

bc,de,fg,ha 結合点

【技術分野】

【0001】

この発明は、フリップチップボンディング法によって、チップが基板に実装される状態を評価するための実装評価構造及び実装評価方法に関し、特に、フリップチップボンディングの実装機(以下、フリップチップボンダと称す)のボンディング精度を評価するための実装評価構造及び実装評価方法に関する。

【背景技術】

【0002】

従来のフリップチップ実装評価方法は、バンプ付きLSIチップを配線基板にフリップチップ実装する工程を評価する際、透明ガラスからなり且つ寸法形状が製品のLSIチップと同じダミーチップの片面に製品のバンプと同じバンプが製品のバンプ付きLSIチップと同じ配列で且つ同じバンプ下地金属膜を介して形成されたバンプ付きダミーチップを使用してフリップチップ実装のトライアルを行い、トライアル品のボンディング部分とその周辺をダミーチップを透して目視により観察することで、ボンディング位置精度、バンプ接続形状等をチェックする(例えば、特許文献1参照)。

【0003】

また、フリップチップボンダに関する技術分野に属するものではないが、静電容量に基づいてアライメント誤差を測定する素子も知られている。例えば、特許文献2では、下地絶縁層上にY方向に延びる下層導電膜が形成され、さらにその上に絶縁層が形成されている。絶縁層上に、下層導電膜に隣接し、かつY方向に延びる帯状の上層導電膜が形成されている。また、特許文献3に記載された従来のマスクとウェハ間の間隙測定装置は、マスクのウェハに対向する面側と、ウェハのマスクに対向する面側とのいずれか一方に、電極パターンを作成し、該電極パターンを含む静電容量形位置センサを備えている。

【特許文献1】特開2001−68514号公報

【特許文献2】特開2003−172601号公報

【特許文献3】特開昭63−107022号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、従来のフリップ実装評価方法は、目視によりフリップ実装工程の評価を行なうものであり、必ずしも精確ではなく、ボンディング部分の欠陥を見過ごしてしまう恐れがあるという課題があった。

【0005】

特に、従来のフリップ実装評価方法は、透明なダミーチップを透かしてのボンディング部分の目視確認により、ボンディング位置精度をチェックするものであり、x−y平面上の位置ずれ(二次元的な変位)はチェックできるのであるが、z方向の位置ずれ(三次元的な変位)はチェックすることができないという課題があった。

【0006】

なお、従来の半導体装置におけるアライメント誤差の測定素子は、ボンディング精度を評価するものではなく、フォトリソグラフィ技術を用いて加工したエッチングマスクの合わせずれ量(アライメント誤差)を測定するものである。すなわち、従来の測定素子によるアライメント誤差の測定は、層間絶縁膜で形成されるキャパシタ自体の容量値の変化で検出するため、z方向のずれ量を測定することができないという課題があった。

【0007】

ここで、複数のボールバンプをチップ上に形成した場合に、バンプ高さには、ばらつきが生じるものである。このため、チップが基板に実装され、チップと基板との平行度が保たれていたとしても、バンプ高さが最小値となるボールバンプの部分においては、当該ボールバンプを介してチップと基板とが接触(導通)していない場合があり得る。

【0008】

これに対し、従来のマスクとウェハ間の間隙測定装置は、対向する電極による静電容量に基づき、マスクとウェハ間の間隙を測定できるのであるが、この間隙測定装置の特徴を、フリップチップボンダに単に適用したのみでは、チップと基板との導通状態を評価するという思想に容易に想到できないものと考えられる。

【0009】

この発明は、上述のような課題を解決するためになされたもので、目視に頼ることなく、基板に対するチップの実装状態を三次元的に評価することができる実装評価構造及び実装評価方法を提供するものである。

【課題を解決するための手段】

【0010】

この発明に係る実装評価構造においては、基板に配設される複数の第1の電極パターンと、当該各第1の電極パターンにそれぞれ対向してチップに配設される複数の第2の電極パターンと、からなる複数の静電容量部を形成し、当該複数の静電容量部における静電容量を比較し、当該比較結果に基づき、前記基板に対する前記チップの実装状態を評価するものである。

【発明の効果】

【0011】

この発明に係る実装評価構造においては、基板に配設される複数の第1の電極パターンと、当該各第1の電極パターンにそれぞれ対向してチップに配設される複数の第2の電極パターンと、からなる複数の静電容量部を形成し、当該複数の静電容量部における静電容量を比較し、当該比較結果に基づき、前記基板に対する前記チップの実装状態を評価することにより、従来のフリップ実装評価方法のような光学的な測定ではなく、電気的な測定により、精確かつ短時間に、基板に対するチップの実装状態を評価することができる。

【発明を実施するための最良の形態】

【0012】

(本発明の第1の実施形態)

図1は第1の実施形態に係る実装評価用基板の概略構成を示す平面図、図2は第1の実施形態に係る実装評価用チップの概略構成を示す平面図、図3は図1に示す実装評価用基板及び図2に示す実装評価用チップのボンディング状態の矢視A−A線の断面図、図4はブリッジ回路を構成することによる測定方法を説明するための説明図、図5は応力評価用パターンの一例を示す平面図である。

【0013】

RS(reference substrate)である実装評価用基板10は、図1に示すように、後述する実装評価用チップ20のボールバンプ1に対応する複数のパッド(以下、第1のパッド11と称す)が実装面10aに配設され、実装評価用チップ20がフリップチップボンディング法によって実装される。

【0014】

なお、以下の説明においては、実装評価用基板10の実装面10aに実装評価用チップ20を実装した場合に、実装面10aにおける実装評価用チップ20の重畳する領域を重畳領域Sと称し、実装面10aにおける重畳領域S以外の領域を周辺領域Pと称して説明する。また、実装評価用基板10及び実装評価用チップ20を総称して、実装評価装置100と称す。

【0015】

また、本実施形態に係る実装評価用基板10は、基材として、平面形状を正方形とし、平面寸法を15.0mm×15.0mmとし、材質を石英ガラスとしたガラス基板を使用しているが、この仕様に限られるものではない。

【0016】

また、本実施形態に係る第1のパッド11は、平面形状を正方形とし、平面寸法を40μm×40μmとし、材質をAl−Si系合金とし、隣り合うパッド間の間隔を50μmとして、実装面10aの重畳領域Sの各辺に136個(合計544個)並設させているが、この仕様に限られるものではない。

【0017】

第1の電極パターン30aは、実装評価用基板10の実装面10aの重畳領域Sに配設され、重畳領域Sに配設される接続配線部(以下、第1の接続配線部12と称す)及び周辺領域Pに配設される引出配線部13を介して、実装面10aの周縁部に配設される外部端子14に接続されている。

【0018】

また、第1の電極パターン30aは、後述する第2の電極パターン30bに対向させて静電容量部30を形成するために、実装評価用基板10の実装面10aにおける所定の位置に配設される。特に、後述する本発明に係る作用効果を奏するためには、複数の静電容量部30が必要であるために、第1の電極パターン30aは、実装評価用基板10の実装面10aの重畳領域Sに複数配設させる。

【0019】

なお、本実施形態に係る第1の電極パターン30aは、平面形状を正方形とし、平面寸法を2.0mm×2.0mmとし、材質をAl−Si系合金として、実装面10aの重畳領域Sの各コーナー近傍に1つ(合計4つ)配設させているが、静電容量部30における所望の静電容量(例えば、測定装置の分解能である2pF)を得ることができるのであれば、この仕様に限られるものではない。

【0020】

外部端子14は、静電容量部30における静電容量を検出するための信号処理回路を備えた図示しない測定装置のプローブを当接させるために、実装評価用基板10の実装面10aにおいて露出させている。

【0021】

なお、本実施形態に係る外部端子14は、平面形状を長方形とし、平面寸法を1.5mm×0.7mmとし、材質をAl−Si系合金として、実装評価用基板10の実装面10aの各辺に10個(合計40個)並設させているが、この仕様に限られるものではない。

【0022】

また、本実施形態に係る複数の外部端子14は、隣り合う外部端子14の少なくとも片側の外部端子14が、グラウンド端子となるように配設することが好ましい。これにより、外部端子14である信号端子及びグラウンド端子に特性インピーダンスが整合された高周波プローブを接続することができ、第1の電極パターン30a及び第2の電極パターン30b間における正確な高周波インピーダンス測定を行なうことができる。

【0023】

なお、高周波プローブには、同軸構造とコプレーナ構造とがあり、特性インピーダンスは一般的に50Ωである。また、使用する測定装置と高周波プローブとによって測定可能な周波数帯域は異なるのであるが、例えば、高周波プローブとして、信号用電極とグラウンド用電極との間隔が0.5mm以下であるコプレーナ構造の高周波プローブを使用し、測定装置として、高周波ベクトルネットワークアナライザを使用すれば、20GHz程度までの高周波インピーダンス測定が可能となる。

【0024】

ちなみに、外部端子14である信号端子の近傍に、グラウンド端子を配設しない場合には、インピーダンス整合された高周波プローブを接続することができないために、高周波信号の反射損失及び挿入損失が大きく、正確な高周波インピーダンス測定が行なえない。この場合の測定可能な周波数の上限は、数10MHzが限界である。

【0025】

特に、2つの信号端子を挟んで両側にグラウンド端子をそれぞれ配設させることで、同時に4つの端子に接触できる、グランド−信号1−信号2−グランドの電極配置を持つ既存のコプレーナ高周波プローブを使用することが可能となる。これにより、1個のプローブに2本の信号線があるプローブが使用できるために、プローブを使用する本数は半減し、プローブの費用を削減できる。また、信号−グラウンドのみの電極配置を持つ既存のコプレーナ高周波プローブ(以下、単一線プローブと称す)を使用した場合と比較して、実装評価装置100に対するプローブ時間を半分に短縮することができる。また、2つの信号端子を同一のプローブで接触できるために、プローブと信号端子との機械的な接触位置が常に一定となり、単一線プローブで問題となる機械的な接触位置における不安定性に依存する測定の不安定状態を取り除くことができる。

【0026】

なお、本実施形態に係る実装評価用基板10は、図3に示すように、基材であるガラス基板上にAl−Si係合金の薄膜を成膜させ、所望の形状にパターニングすることで、第1の電極パターン30a、第1のパッド11、第1の接続配線部12、引出配線部13及び外部端子14を単層にて形成したものである。

【0027】

TEG(test element group)である実装評価用チップ20は、図2に示すように、下面20aの周縁部に沿って配設される複数のパッド(以下、第2のパッド21と称す)上に、複数のボールバンプ1がそれぞれ配設される。

【0028】

また、実装評価用チップ20は、ボールバンプ1が下面20aの中央領域には配置されず、周縁部近傍のみに配置される構成であり、周縁部における実装評価用基板10とのボンディング状態を評価するためのチップを利用している。

【0029】

なお、本実施形態に係る実装評価用チップ20は、基材として、平面形状を正方形とし、平面寸法を7.4mm×7.4mmとし、材質を石英ガラスとしたガラスチップを使用しているが、この仕様に限られるものではない。

【0030】

また、本実施形態に係る第2のパッド21は、平面形状を正方形とし、平面寸法を40μm×40μmとし、材質をAl−Si系合金とし、隣り合うパッド間の間隔を50μmとして、実装評価用チップ20の下面20aの各辺に136個(合計544個)並設させているが、この仕様に限られるものではない。

【0031】

第2の電極パターン30bは、実装評価用チップ20の下面20aに配設され、接続配線部(以下、第2の接続配線部22と称す)を介して第2のパッド21に接続されている。

また、第2の電極パターン30bは、実装評価用チップ20がフリップチップボンディング法によって実装評価用基板10に実装されることで、第2のパッド21上のボールバンプ1と実装評価用基板10上の第1のパッド11とが導通し、この第1のパッド11に接続する引出配線部13を介して外部端子14に接続される。

【0032】

また、第2の電極パターン30bは、第1の電極パターン30aに対向させて静電容量部30を形成するために、実装評価用チップ20の下面20aにおける所定の位置に配設される。特に、後述する本発明に係る作用効果を奏するためには、複数の静電容量部30が必要であるために、第2の電極パターン30bは、実装評価用チップ20の下面20aに複数配設させる。

【0033】

なお、本実施形態に係る第2の電極パターン30bは、平面形状を正方形とし、平面寸法を2.0mm×2.0mmとし、材質をAl−Si系合金として、実装評価用チップ20の下面20aの各コーナー近傍に1つ(合計4つ)配設させているが、静電容量部30における所望の静電容量(例えば、測定装置の分解能である2pF)を得ることができるのであれば、この仕様に限られるものではない。

【0034】

また、本実施形態に係る実装評価用チップ20は、図3に示すように、基材であるガラスチップ上にAl−Si係合金の薄膜を成膜させ、所望の形状にパターニングすることで、第2の電極パターン30b、第2のパッド21及び第2の接続配線部22を単層にて形成したものである。

【0035】

静電容量部30は、対向する第1の電極パターン30a及び第2の電極パターン30bを互いに同一の平面形状及び平面寸法とし、複数の静電容量部30(ここでは、4つの静電容量部30)の各第1の電極パターン30a及び各第2の電極パターン30bについても互いに同一の平面形状及び平面寸法としている。すなわち、全ての第1の電極パターン30a及び第2の電極パターン30bが同一の平面形状及び平面寸法としている。

【0036】

また、静電容量部30は、実装評価用基板10上に実装評価用チップ20が正常(実装評価用基板10と実装評価用チップ20とが略平行となる、正対した状態)にフリップチップボンディングされた場合に、実装評価用基板10に垂直な方向において、対向する第1の電極パターン30a及び第2の電極パターン30bが完全に重畳する構成である。

【0037】

すなわち、実装評価用基板10上に実装評価用チップ20が正常にフリップチップボンディングされた場合には、対向する第1の電極パターン30a及び第2の電極パターン30b間の距離が全ての静電容量部30において等しく、対向する第1の電極パターン30a及び第2の電極パターン30bの重畳する面積が全ての静電容量部30において等しいために、4つの静電容量部30における各静電容量は、全て等しい値となる。

【0038】

したがって、本実施形態に係る実装評価構造においては、複数の静電容量部30における各静電容量を測定し、全て等しい測定値であれば、実装評価用基板10上に実装評価用チップ20が正常にフリップチップボンディングされた実装状態であると判定できる。また、複数の静電容量部30における各静電容量が、全て等しい測定値でないならば、実装評価用基板10上に実装評価用チップ20が異常(傾斜した状態)にフリップチップボンディングされた実装状態であると判定できる。

【0039】

特に、本実施形態に係る実装評価構造においては、対向する第1の電極パターン30a及び第2の電極パターン30bの重畳する面積S、対向する第1の電極パターン30a及び第2の電極パターン30b間の誘電率ε、並びに、静電容量部30における静電容量Cの測定値に基づき、第1の電極パターン30a及び第2の電極パターン30b間の間隙dの値を算出する。そして、第1の電極パターン30a及び第2の電極パターン30b間の間隙dが、ボールバンプ1の形成における高さばらつきによるバンプ高さの最小値よりも小さい場合に、実装評価用チップ20と実装評価用基板10とが全てのボールバンプ1において接触状態(導通状態)であると判定できる。

【0040】

なお、本実施形態に係る実装評価装置100は、複数の静電容量部30を備えているのであれば、複数の静電容量部30における各静電容量の差分を算出することができるために、4つの静電容量部30を備える構成に限られるものではない。

【0041】

しかしながら、本実施形態に係る実装評価装置100が静電容量部30を2つだけ備えている場合には、この2つの静電容量部30を結んだ直線を回転軸として実装評価用チップ20が傾斜してフリップチップ実装された場合に、2つの静電容量部30における静電容量が等しい値となってしまうために、実装状態の異常を検出することができないことになる。

【0042】

したがって、本実施形態に係る実装評価装置100は、全ての静電容量部30が同一直線上に並設されない3つ以上の静電容量部30を備えていることが好ましい。

また、本実施形態に係る実装評価装置100は、4つの静電容量部30を備えることで、実装状態の評価にあたり、4つの静電容量部30を接続してブリッジ回路を構成させることが考えられる。

【0043】

この構成により、ブリッジ回路の一次側(一の対角)に電圧を与え、二次側(他の対角)の電圧を測定し、二次側の電圧が零(許容範囲を含む)である場合に、4つの静電容量部30における静電容量が平衡状態であるために、実装評価用基板10上に実装評価用チップ20が正常にフリップチップボンディングされた実装状態であると判定できる。

【0044】

なお、本実施形態に係る実装評価装置100は、ブリッジ回路を構成させるために、隣り合う静電容量部30を接続する配線パターン、ブリッジ回路の一次側(一の対角)に電圧を入力するための端子及び配線パターン、並びに、ブリッジ回路の二次側(他の対角)の電圧を測定するための端子及び配線パターンを、予め、実装評価用基板10の実装面10aに形成してもよい。

【0045】

なお、本実施形態に係る実装評価装置100は、静電容量部30の配置を特に限定するものではないが、実装評価用基板10の重畳領域S(実装評価用チップ20の下面20a)の各コーナー近傍に静電容量部30を配設することで、実装評価用チップ20が傾斜して実装された場合に、重畳領域Sの中央部分に静電容量部30を配設する場合と比較して、複数の静電容量部30における静電容量の差分が大きく検出でき、異常な実装状態を漏れなく検出できるために好ましい。

【0046】

つぎに、実装評価構造を用いた、実装評価用基板10に対する実装評価用チップ20の実装状態の評価方法について説明する。

まず、実装評価用チップ20及び実装評価用基板10は、ボンディング精度の検証の対象装置である図示しないフリップチップボンダに投入される。

【0047】

そして、実装評価用チップ20及び実装評価用基板10は、図示しないアライメントマークなどに基づき位置決めされ、実装評価用チップ20の第2のパッド21(ボールバンプ1)と実装評価用基板10の第1のパッド11とを対向して密着させ、熱及び圧力を加えて接合される。

【0048】

接合された実装評価用チップ20及び実装評価用基板10は、実装評価用基板10の外部端子14に図示しない測定装置のプローブが当接され、静電容量部30の対をなす第1の電極パターン30a及び第2の電極パターン30b間の静電容量を、4つの静電容量部30に対してそれぞれ測定される。なお、測定装置としては、Qメータ、LCRメーター又はインピーダンスアナライザなどの既存の測定装置を用いる。

【0049】

そして、4つの静電容量部30における静電容量の測定値に基づき、4つの静電容量部30の静電容量が全て等しい測定値であれば、実装評価用基板10に対して実装評価用チップ20が正常(正対した状態)に実装されていると判定する。

【0050】

これに対し、4つの静電容量部30における静電容量の測定値に基づき、4つの静電容量部30の静電容量が全て等しい測定値でないならば、実装評価用基板10に対して実装評価用チップ20が異常(傾斜した状態)に実装されていると判定する。

【0051】

なお、前述したように、4つの静電容量部30を接続してブリッジ回路を構成し、ブリッジ回路の一次側(一の対角)に電圧を与え、二次側(他の対角)の電圧を測定することによっても、実装評価用基板10に対する実装評価用チップ20の実装状態を評価することができる。

この場合には、例えば、図4に示すような回路構成にて、実装状態を評価することが考えられる。

【0052】

測定装置200は、プローブ201(201a〜201h)を外部端子14(14a〜14h)に当接させることで、4つの静電容量部30のうち、第1の静電容量部31の一の外部端子14a及び第4の静電容量部34の他の外部端子14h、第1の静電容量部31の他の外部端子14b及び第2の静電容量部32の一の外部端子14c、第2の静電容量部32の他の外部端子14d及び第3の静電容量部33の一の外部端子14e、第3の静電容量部33の他の外部端子14f及び第4の静電容量部34の一の外部端子14gをそれぞれ接続させ、ブリッジ回路2を構成する。

【0053】

また、第1の静電容量部31の外部端子14aと第4の静電容量部34の外部端子14hとの結合点ha、及び第2の静電容量部32の外部端子14dと第3の静電容量部33の外部端子14eとの結合点deには、測定装置200の交流電圧発生回路202から交流電圧が印加される。

【0054】

また、測定装置200の差動増幅回路203は、第1の静電容量部31の外部端子14bと第2の静電容量部32の外部端子14cとの結合点bcから供給される交流信号と、第3の静電容量部33の外部端子14fと第4の静電容量部34の外部端子14gとの結合点fgから供給される交流信号との差分成分を増幅する。

【0055】

このような構成により、結合点bcにおける交流信号と結合点fgにおける交流信号との差分信号が差動増幅回路203から出力されない場合には、ブリッジ回路2が平衡状態であることがわかる。

【0056】

なお、4つの静電容量部30における各静電容量に誤差を有しており、正常な実装状態であっても、差動増幅回路203から差分信号が出力される場合も考えられるために、差動増幅回路203から出力される差分信号に対して、正常な実装状態であると判断するための許容範囲を設定することが好ましい。

【0057】

すなわち、測定装置200の電圧コンパレータ回路204は、差動増幅回路203から出力される差分信号の電圧が、可変抵抗器205などによって設定される基準電圧よりも高い場合に、Hレベルの検出信号を出力する。

【0058】

また、電圧コンパレータ回路204は、差動増幅回路203から出力される差分信号の電圧が、可変抵抗器205などによって設定される基準電圧よりも低い場合に、Lレベルの検出信号を出力する。

【0059】

これにより、Hレベルの検出信号が出力された場合には、実装評価用基板10に対する実装評価用チップ20の実装状態が異常(傾斜した状態)であると判定でき、Lレベルの検出信号が出力された場合には、実装評価用基板10に対する実装評価用チップ20の実装状態が正常(正対した状態)であると判定できる。

【0060】

なお、ブリッジ回路2は、図4に示すように、測定装置200に接続することで、結合点ha及び結合点deに交流電圧が印加され、結合点bcにおける交流信号と結合点fgにおける交流信号との差分信号の有無を検出する回路構成としているが、結合点bc及び結合点fgに交流電圧が印加され、結合点haにおける交流信号と結合点deにおける交流信号との差分信号の有無を検出する回路構成としてもよい。これにより、ブリッジ回路2を用いた測定方法として、二通りの取り方が考えられる。

【0061】

なお、本実施形態に係る実装評価装置100においては、全ての第1の電極パターン30a及び第2の電極パターン30bを同一の平面形状及び平面寸法とする構成(各静電容量部30における第1の電極パターン30a及び第2の電極パターン30bの重畳する面積が一致する構成)にしているが、複数の静電容量部30の各第1の電極パターン30a及び各第2の電極パターン30bを互いに異なる平面形状及び平面寸法とする構成(各静電容量部30における第1の電極パターン30a及び第2の電極パターン30bの重畳する面積が異なる構成)であってもよい。

【0062】

この場合には、実装評価用基板10に対する実装評価用チップ20の実装状態が正常な状態における、複数の静電容量部30における各静電容量(第1の電極パターン30a及び第2の電極パターン30bの重畳する面積)を予め算出又は実測しておく。そして、予め算出又は実測した値に基づき、複数の静電容量部30における各静電容量の差分を零に補正する演算機能を測定装置に備えておくことで、前述した構成と同様に、実装状態を評価することができる。

【0063】

しかしながら、実装評価装置100は、静電容量部30の対向電極を統一性のある単純な形状にすることができるうえに、複数の静電容量部30における各静電容量の差分を零に補正する演算機能を測定装置に備える必要がないために、前述した、全ての第1の電極パターン30a及び第2の電極パターン30bを同一の平面形状及び平面寸法とする構成にすることが好ましい。

【0064】

なお、本実施形態に係る実装評価装置100においては、RSであるガラス基板に第1の電極パターン30a(第1の接続配線部12)を形成し、TEGであるガラスチップに第2の電極パターン30b(第2の接続配線部22)を形成することで、複数の静電容量部30における静電容量を測定できる構成にしているが、実製品である配線基板及び半導体チップに対して、対向する電極パターン等をそれぞれ形成し、複数の静電容量部30における静電容量を測定できる構成にしてもよい。

【0065】

この場合には、例えば、第1の電極パターン30a及び第2の電極パターン30bを、半導体チップに内蔵される演算部にそれぞれ接続し、当該演算部により複数の静電容量部30における各静電容量の差分を演算することで、実装評価用基板10に対する実装評価用チップ20の実装状態を評価する構成も考えられる。

【0066】

以上のように、複数の静電容量部30における各静電容量の差分を検出することで、実装評価用基板10に対する実装評価用チップ20の傾斜の有無を判断することができ、フリップチップボンダのボンディング精度を評価することができる。

【0067】

なお、本実施形態に係る実装評価装置100においては、静電容量部30の対をなす第1の電極パターン30a及び第2の電極パターン30b間の静電容量を少なくとも測定できる構成であればよいが、他の評価試験を併用できる構成としてもよい。

【0068】

例えば、実装評価用基板10の実装面10aの重畳領域Sにおけるコーナー近傍又は実装評価用チップ20の下面20aにおけるコーナー近傍に、バーニヤである応力評価用パターン3を配設させる構成としてもよい。この応力評価用パターン3は、例えば、図5に示すように、材質をCrとし、パターン長が60μmであり、パターン幅が4.8μmである矩形状のパターンを、幅方向に沿って9.75μmピッチで並設させ、4本間隔でパターンのパターン長を70μmとして突出させることで、目盛り形状としている。

【0069】

なお、本実施形態に係る実装評価用チップ20は透明なガラスチップを使用しているために、実装評価用チップ20の下面20aに、応力評価用パターン3を配設させる場合であっても、実装評価用基板10上に実装評価用チップ20を実装する前と実装した後の応力評価用パターン3をそれぞれ撮像することができ、画像処理して差分を比較することで、実装評価用チップ20に加わった応力の程度(歪み)を検出することができる。

【0070】

これに対し、不透明な実装評価用チップ20を使用した場合であっても、実装評価用チップ20の厚みが50μm以下となると、実装評価用チップ20に赤外線を透過させることができるため、同様に、実装評価用チップ20に加わった応力の程度(歪み)を検出することができる。

【0071】

特に、実装評価用基板10及び実装評価用チップ20の間隙に図示しないアンダーフィルが形成されることで、実装評価用チップ20の伸縮が生じることがあり、アンダーフィルによる実装評価用チップ20に加わる応力の程度を検出することができる。

【0072】

なお、アンダーフィルは、基板上に液体状の樹脂を塗布又はフィルム状の樹脂を敷設した後にチップを実装する先入れタイプと、基板上にチップを実装した後に液体状の樹脂を毛細管現象により注入する後入れタイプとがある。そこで、実装評価用基板10及び/又は実装評価用チップ20が透明であることは、実装評価用基板10及び実装評価用チップ20の間隙に挿入されるアンダーフィルの状態を視認できるという作用効果もある。

また、本実施形態に係る実装評価装置100の他の評価試験を併用できる構成として、以下の構成も考えられる。

【0073】

例えば、実装評価用基板10における隣り合う第1のパッド11間を交互にオープン又はショートとなるように非接続又は接続とし、実装評価用チップ20における隣り合う第2のパッド21間が実装評価用基板10における隣り合う第1のパッド11間の非接続又は接続に対して反転させて接続又は非接続とすることで、始端と終端とを有するチェーンをなす単線路を備えた構成としてもよい。

【0074】

この構成により、実装評価用基板10上に実装評価用チップ20を実装した場合に、単線路の始端から信号を入力し、終端における信号の有無を確認することで、この両端間における全ての第1のパッド11及び第2のパッド21間のボールバンプ1による導通状態を一度に評価することができる。ただし、単線路が断線していると判断できた場合であっても、断線している場所を特定することができない。特に、実装評価用チップ20の周縁部近傍における第1のパッド11及び第2のパッド21のボールバンプ1による接続箇所は数百箇所も存在するために、非導通となった第1のパッド11及び第2のパッド21を特定することは困難である。

【0075】

このため、第1のパッド11及び第2のパッド21間を固着するハンダにクラックが生じることによる接触不良や非導通の場所の特定にあたっては、時間領域反射(time domein reflectmetry:以下、TDRと称す)法を用いた検出方法が考えられる。このTDR法とは、線路インピーダンス、線路長、伝送速度を知ることができる測定法であり、立ち上がり時間が20〜50ps程度の高速スイッチング動作するステップ信号を伝送路に送り込み、その反射波形を高帯域な特性をもつオシロスコープで観測する。

【0076】

すなわち、実装評価装置100における第1のパッド11及び第2のパッド21を経由する単線路に、第1のパッド11及び第2のパッド21のボールバンプ1による接触不良や非導通が生じた場合には、単線路のインピーダンスが変動することとなり、TDR法により接触不良又は非導通の場所を特定することができる。特に、第1のパッド11及び第2のパッド21が非導通により単線路が断線している場合には、始端からの伝送路が最短長となる非導通箇所が終端となり、始端から入射した入射波が、この非導通箇所で反射して、始端で反射波を検出することとなる。

【0077】

なお、隣り合うボールバンプ1(第1のパッド11、第2のパッド21)間のピッチが狭すぎる場合(例えば、120μm)には、TDR法を用いて線路長を検出できない場合がある。このため、TDR法を用いて線路長を検出できる間隔で、第1のパッド11(第2のパッド21)間を接続することが好ましい。例えば、隣り合う第1のパッド11(第2のパッド21)間の間隔をdとし、TDR法を用いて線路長を検出できる間隔が2dであった場合に、接続する第1のパッド11(第2のパッド21)間の間隔が2dとなるように、隣り合う第1のパッド11(第2のパッド21)を接続せず1つ置きに、第1のパッド11(第2のパッド21)間を接続することで、接続する第1のパッド11(第2のパッド21)間の線路長を稼ぐことができる。そして、TDR法を用いて第1のパッド11及び第2のパッド21間の接触不良又は非導通の場所に目安を付け、目安を付けた場所近傍の断面形状を観察するなどの解析を行なうことで、第1のパッド11及び第2のパッド21間の接触不良又は非導通の場所を特定することができる。

【図面の簡単な説明】

【0078】

【図1】第1の実施形態に係る実装評価用基板の概略構成を示す平面図である。

【図2】第1の実施形態に係る実装評価用チップの概略構成を示す平面図である。

【図3】図1に示す実装評価用基板及び図2に示す実装評価用チップのボンディング状態の矢視A−A線の断面図である。

【図4】ブリッジ回路を構成することによる測定方法を説明するための説明図である。

【図5】応力評価用パターンの一例を示す平面図である。

【符号の説明】

【0079】

1 ボールバンプ

2 ブリッジ回路

3 応力評価用パターン

10 実装評価用基板

10a 実装面

11 第1のパッド

12 第1の接続配線部

13 引出配線部

14,14a,14b,14c,14d,14e,14f,14g,14h 外部端子

20 実装評価用チップ

20a 下面

21 第2のパッド

22 第2の接続配線部

30 静電容量部

30a 第1の電極パターン

30b 第2の電極パターン

31 第1の静電容量部

32 第2の静電容量部

33 第3の静電容量部

34 第4の静電容量部

100 実装評価装置

200 測定装置

201 プローブ

202 交流電圧発生回路

203 差動増幅回路

204 電圧コンパレータ回路

205 可変抵抗器

P 周辺領域

S 重畳領域

bc,de,fg,ha 結合点

【特許請求の範囲】

【請求項1】

下面の縁部に沿って複数のボールバンプが配設されるチップを、前記複数のボールバンプに対応する複数のパッドが実装面に配設される基板に、フリップチップボンディング法によって実装される状態を評価する実装評価構造において、

前記基板に配設される複数の第1の電極パターンと、当該各第1の電極パターンにそれぞれ対向して前記チップに配設される複数の第2の電極パターンと、からなる複数の静電容量部を形成し、当該複数の静電容量部における各静電容量を比較し、当該比較結果に基づき、前記基板に対する前記チップの実装状態を評価することを特徴とする実装評価構造。

【請求項2】

前記請求項1に記載の実装評価構造において、

前記静電容量部における静電容量に基づき、前記第1の電極パターンと前記第2の電極パターンとの間隙の値を算出し、当該間隙が前記ボールバンプの形成における高さばらつきによるバンプ高さの最小値よりも小さい場合に、前記実装状態が正常であるとして判定することを特徴とする実装評価構造。

【請求項3】

前記請求項1又は2に記載の実装評価構造を用いた実装評価方法において、

フリップチップボンディング法によって、前記基板に対して前記チップを実装する第1のステップと、

前記複数の静電容量部における各静電容量をそれぞれ測定する第2のステップと、

前記第2のステップで得られた各静電容量の測定値に基づき、前記複数の静電容量部における全ての静電容量が同等である場合に、前記基板に対する前記チップの実装状態が正常であるとして判定する第3のステップと、

を備えていることを特徴とする実装評価方法。

【請求項4】

前記請求項2に記載の実装評価構造において、

フリップチップボンディング法によって、前記基板に対して前記チップを実装する第1のステップと、

ブリッジ回路を構成するように前記4つの静電容量部を接続し、当該ブリッジ回路の一次側に電圧を与え、二次側の電圧を測定する第2のステップと、

前記第2のステップで得られた二次側の電圧が零である場合に、前記基板に対する前記チップの実装状態が正常であるとして判定する第3のステップと、

を備えていることを特徴とする実装評価方法。

【請求項1】

下面の縁部に沿って複数のボールバンプが配設されるチップを、前記複数のボールバンプに対応する複数のパッドが実装面に配設される基板に、フリップチップボンディング法によって実装される状態を評価する実装評価構造において、

前記基板に配設される複数の第1の電極パターンと、当該各第1の電極パターンにそれぞれ対向して前記チップに配設される複数の第2の電極パターンと、からなる複数の静電容量部を形成し、当該複数の静電容量部における各静電容量を比較し、当該比較結果に基づき、前記基板に対する前記チップの実装状態を評価することを特徴とする実装評価構造。

【請求項2】

前記請求項1に記載の実装評価構造において、

前記静電容量部における静電容量に基づき、前記第1の電極パターンと前記第2の電極パターンとの間隙の値を算出し、当該間隙が前記ボールバンプの形成における高さばらつきによるバンプ高さの最小値よりも小さい場合に、前記実装状態が正常であるとして判定することを特徴とする実装評価構造。

【請求項3】

前記請求項1又は2に記載の実装評価構造を用いた実装評価方法において、

フリップチップボンディング法によって、前記基板に対して前記チップを実装する第1のステップと、

前記複数の静電容量部における各静電容量をそれぞれ測定する第2のステップと、

前記第2のステップで得られた各静電容量の測定値に基づき、前記複数の静電容量部における全ての静電容量が同等である場合に、前記基板に対する前記チップの実装状態が正常であるとして判定する第3のステップと、

を備えていることを特徴とする実装評価方法。

【請求項4】

前記請求項2に記載の実装評価構造において、

フリップチップボンディング法によって、前記基板に対して前記チップを実装する第1のステップと、

ブリッジ回路を構成するように前記4つの静電容量部を接続し、当該ブリッジ回路の一次側に電圧を与え、二次側の電圧を測定する第2のステップと、

前記第2のステップで得られた二次側の電圧が零である場合に、前記基板に対する前記チップの実装状態が正常であるとして判定する第3のステップと、

を備えていることを特徴とする実装評価方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2010−56429(P2010−56429A)

【公開日】平成22年3月11日(2010.3.11)

【国際特許分類】

【出願番号】特願2008−221949(P2008−221949)

【出願日】平成20年8月29日(2008.8.29)

【出願人】(391043332)財団法人福岡県産業・科学技術振興財団 (53)

【出願人】(598015084)学校法人福岡大学 (114)

【出願人】(508262836)株式会社ウォルツ (4)

【Fターム(参考)】

【公開日】平成22年3月11日(2010.3.11)

【国際特許分類】

【出願日】平成20年8月29日(2008.8.29)

【出願人】(391043332)財団法人福岡県産業・科学技術振興財団 (53)

【出願人】(598015084)学校法人福岡大学 (114)

【出願人】(508262836)株式会社ウォルツ (4)

【Fターム(参考)】

[ Back to top ]