容量性負荷駆動回路

【課題】複数の電荷蓄積素子を用いて、容量性負荷を効率よく駆動する。

【解決手段】電源と複数の電荷蓄積素子とを並列に接続することで電荷蓄積素子に充電し

た後(第1の接続状態)、複数の電荷蓄積素子の中から選択された1つの素子を容量性負

荷に対して並列に接続するか、あるいは複数選択した素子を直列に接続した状態で負荷に

並列に接続することで、容量性負荷に電圧を印加する(第2の接続状態)。また、第2の

接続状態の時に、選択する電荷蓄積素子の数を切り換えれば、容量性負荷に印加する電圧

を切り換えることができる。更に、1つの電荷蓄積素子が容量性負荷に並列に接続された

状態で、その電荷蓄積素子に対して他の電荷蓄積素子を並列に接続する(第3の接続状態

)。こうすれば、電荷蓄積素子間で電荷が再分配されるので、容量性負荷を効率よく駆動

することが可能となる。

【解決手段】電源と複数の電荷蓄積素子とを並列に接続することで電荷蓄積素子に充電し

た後(第1の接続状態)、複数の電荷蓄積素子の中から選択された1つの素子を容量性負

荷に対して並列に接続するか、あるいは複数選択した素子を直列に接続した状態で負荷に

並列に接続することで、容量性負荷に電圧を印加する(第2の接続状態)。また、第2の

接続状態の時に、選択する電荷蓄積素子の数を切り換えれば、容量性負荷に印加する電圧

を切り換えることができる。更に、1つの電荷蓄積素子が容量性負荷に並列に接続された

状態で、その電荷蓄積素子に対して他の電荷蓄積素子を並列に接続する(第3の接続状態

)。こうすれば、電荷蓄積素子間で電荷が再分配されるので、容量性負荷を効率よく駆動

することが可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、容量性の電気負荷を駆動する技術に関する。

【背景技術】

【0002】

電荷を蓄えた複数のコンデンサーを利用して、容量性負荷を効率よく駆動する技術が提

案されている(特許文献1)。この提案の技術では、各コンデンサーに異なる電圧で電荷

を蓄えておき、容量性負荷に接続するコンデンサーを次々と切り換えることによって負荷

を駆動する。

【0003】

例えば、負荷に印加する電圧値を上昇させる場合には、負荷に接続するコンデンサーを

、高い電圧で電荷が蓄えられた(端子間電圧の高い)コンデンサーに次々と切り換えてい

く。こうすればコンデンサーに蓄えられた電荷が容量性負荷に供給され、そして容量性負

荷に蓄えられた電荷が増加するに従って負荷の印加電圧が上昇していく。逆に、負荷の印

加電圧を低下させる場合には、負荷に接続するコンデンサーを端子間電圧の低いコンデン

サーに次々と切り換えていく。こうすれば、容量性負荷に蓄えられた電荷がコンデンサー

に回収されて、負荷に蓄えられた電荷が減少するに従って印加電圧が低下していく。

【0004】

このように、提案されている技術では、端子電圧の異なる複数のコンデンサーと、容量

性負荷との間で電荷の充放電を行うことにより、容量性負荷を効率よく駆動することが可

能となっている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−285441号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、提案されている技術では、個々のコンデンサーについてみれば、容量性負荷に

供給する電荷と容量性負荷から回収する電荷とが必ずしも釣り合うとは限らず、各コンデ

ンサーでの充放電バランスの崩れに起因した電力損失が発生してしまうという問題がある

。

【0007】

例えば、容量性負荷に供給する電荷よりも負荷から回収する電荷の方が多いコンデンサ

ーでは、蓄積した電荷が増加していき、これに伴ってコンデンサーの端子間電圧が増加す

る。端子間電圧が想定した電圧値と異なってしまっては、負荷に正確な電圧を印加するこ

とができなくなるので、過剰に蓄積した分の電荷を放出しなければならなくなり、その分

の電力損失が発生する。また逆に、容量性負荷に供給する電荷の方が負荷から回収する電

荷よりも多いコンデンサーでは、蓄積している電荷が減少していき、これに伴ってコンデ

ンサーの端子間電圧が減少してしまう。その結果、電源から電荷を補充しなければならな

くなって、その分の電力も損失となる。

【0008】

この発明は、従来の技術が有する上述した課題を解決するためになされたものであり、

コンデンサーなどの複数の電荷蓄積素子を用いて、容量性負荷を効率よく駆動することが

可能な技術の提供を目的とする。

【課題を解決するための手段】

【0009】

上述した課題の少なくとも一部を解決するために、本発明の容量性負荷駆動回路は次の

構成を採用した。すなわち、

容量性負荷を駆動する容量性負荷駆動回路であって、

電荷を蓄積する複数の電荷蓄積素子と、

前記電荷蓄積素子に電荷を供給する電源と、

前記複数の電荷蓄積素子と、前記電源と、前記容量性負荷との接続状態を切り換える接

続状態切換手段と

を備え、

前記接続状態切換手段は、

前記容量性負荷が前記電源および前記複数の電荷蓄積素子から切断された状態で、前

記電源と前記複数の電荷蓄積素子とが並列に接続される第1の接続状態と、

前記容量性負荷が前記電源および前記複数の電荷蓄積素子から切断された状態で、前

記複数の電荷蓄積素子のうちの1つの前記電荷蓄積素子、または直列に接続された少なく

とも2つの前記電荷蓄積素子が、前記容量性負荷に対して並列に接続される第2の接続状

態と、

前記電源が前記複数の電荷蓄積素子および前記容量性負荷から切断され、前記複数の

電荷蓄積素子のうちの1つの前記電荷蓄積素子が前記容量性負荷に対して並列に接続され

た状態で、該容量性負荷に接続された1つの該電荷蓄積素子に対して、他の前記電荷蓄積

素子が並列に接続される第3の接続状態と

に切り換え可能な手段であることを要旨とする。

【0010】

このような本発明の容量性負荷駆動回路においては、複数の電荷蓄積素子と電源とが並

列に接続された第1の接続状態とすることで、電荷蓄積素子に電荷を蓄えることができる

。続いて、複数の電荷蓄積素子の中から少なくとも1つの電荷蓄積素子を選択して、選択

した電荷蓄積素子が容量性負荷に対して並列に接続される第2の接続とすることで、容量

性負荷に対して電圧を印加することができる。このとき、選択した電荷蓄積素子が1つで

あれば、電荷蓄積素子1つ分の電圧が容量性負荷に印加されることになる。また、複数の

電荷蓄積素子を選択した場合には、それら電荷蓄積素子を直列に接続した状態で、容量性

負荷に並列に接続する。こうすれば複数の電荷蓄積素子を直列に接続して得られる電圧が

、容量性負荷に印加されることになる。従って、電荷蓄積素子と容量性負荷とを第2の接

続状態で接続する際に、複数の電荷蓄積素子の中から選択して負荷に接続する電荷蓄積素

子の個数によって、容量性負荷に印加する電圧を切り換えることができる。そして、選択

する電荷蓄積素子の個数を増やしていけば、容量性負荷に印加される電圧が上昇し、この

とき電荷蓄積素子から容量性負荷に向かって電荷が供給される。逆に、選択する電荷蓄積

素子の個数を減らしていけば、容量性負荷に印加される電圧が低下して、このとき容量性

負荷から放出される電荷が電荷蓄積素子によって回収される。このため、回収した電荷を

用いて再び負荷の印加電圧を上昇させることができるので、容量性負荷を効率よく駆動す

ることが可能である。更に、本発明の容量性負荷駆動回路においては、1つの電荷蓄積素

子を容量性負荷に接続した状態で、その電荷蓄積素子に他の電荷蓄積素子が並列に接続さ

れた第3の接続状態とすることができる。容量性負荷に対して電荷を供給する電荷蓄積素

子と、容量性負荷から電荷を回収する電荷蓄積素子とは、必ずしも一致するとは限らない

。このため複数の電荷蓄積素子の間で電荷の偏りが発生して、この電荷の偏りに起因した

電力損失を引き起こす可能性がある。そこで本発明では、第3の接続状態とすることによ

って、互いに並列に接続された電荷蓄積素子間で電荷の偏りが是正されるように、電荷を

再配分することができるので、電荷の偏りに起因した電力損失の発生を回避することが可

能となる。

【0011】

尚、第3の接続状態とする場合、電荷を再分配するという観点からは、容量性負荷に接

続された1つの電荷蓄積素子に対して、他の全ての電荷蓄積素子を並列に接続することが

多くの場合は望ましい。しかし、必ずしも、他の全ての電荷蓄積素子を並列に接続しなけ

ればならないわけではない。たとえば、印加する電圧波形の関係で、極端に電荷が不足す

る電荷蓄積素子が存在する場合などには、その電荷蓄積素子については電源から電荷を補

充することとして、他の電荷蓄積素子間で電荷の再分配を行うようにしても構わない。

【0012】

また、上述した本発明の容量性負荷駆動回路においては、複数の電荷蓄積素子が並列に

接続されており、尚且つ、電源および容量性負荷から切断された第4の接続状態に切り換

え可能としてもよい。

【0013】

複数の電荷蓄積素子を、このような第4の接続状態とすることができれば、容量性負荷

に電圧を印加していない状態で、複数の電荷蓄積素子の間で電荷を再分配することが可能

となるので好ましい。

【0014】

また、上述した本発明の容量性負荷駆動回路においては、次のようにしても良い。先ず

、電源、複数の電荷蓄積素子、および容量性負荷が並列に接続される第5の接続状態に切

り換え可能とする。そして、電源、複数の電荷蓄積素子、および容量性負荷の接続状態を

第3の接続状態に切り換えた後に、第5の接続状態に切り換えることとしてもよい。

【0015】

前述したように第3の接続状態では電荷蓄積素子の間で電荷の再分配が行われるから、

多くの電荷が蓄積されている電荷蓄積素子から、電荷の少ない電荷蓄積素子に向かって電

荷が供給される。その状態で、複数の電荷蓄積素子に対して電源を接続することで、第5

の接続状態に切り換えてやれば、電源から各電荷蓄積素子に補充する電荷を最小限にする

ことができるので、容量性負荷をより一層効率よく駆動することが可能となる。

【図面の簡単な説明】

【0016】

【図1】本実施例の容量性負荷駆動回路を搭載したインクジェットプリンターを例示した説明図である。

【図2】プリンター制御回路の制御の下で、噴射ヘッド駆動回路が噴射ヘッドを駆動する様子を示した説明図である。

【図3】第1実施例の噴射ヘッド駆動回路の詳細な構成を示した説明図である。

【図4】各スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続状態を切り換えてコンデンサーC1 〜C3 を充電する様子を示した説明図である。

【図5】各スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続状態を切り換えることでピエゾ素子に印加される電圧が切り換わる様子を示した説明図である。

【図6】ピエゾ素子に印加する電圧を切り換えた時に、コンデンサーC1 〜C3 とピエゾ素子との間で電荷の授受が行われる様子を示した説明図である。

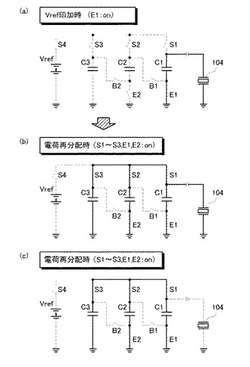

【図7】第1実施例の駆動波形生成回路で各コンデンサーC1 〜C3 の電荷を再分配する様子を示した説明図である。

【図8】第1実施例の駆動波形生成回路がピエゾ素子に電圧を印加しながら、コンデンサーC1 〜C3 間での電荷の再分配を行う様子を示した説明図である。

【図9】第1実施例の変形例の駆動波形生成回路においてコンデンサーC1 〜C3 で電荷の再分配を行った後に、電荷を補充する様子を示した説明図である。

【図10】第1実施例の変形例の駆動波形生成回路がピエゾ素子に電圧を印加する様子を示した説明図である。

【図11】第2実施例の駆動波形生成回路の一例を示した回路図である。

【図12】第2実施例の駆動波形生成回路がピエゾ素子の印加電圧を切り換える様子を示した説明図である。

【図13】第2実施例の駆動波形生成回路でコンデンサーC1 〜C3 間の電荷を再分配する様子を示す説明図である。

【図14】印加電圧が電圧Vref 以外のときに電荷の再分配を行う様子を例示した説明図である。

【発明を実施するための形態】

【0017】

以下では、上述した本願発明の内容を明確にするために、次のような順序に従って実施

例を説明する。

A.装置構成:

B.第1実施例:

B−1.回路構成:

B−2.容量性負荷の駆動原理:

B−3.変形例:

C.第2実施例:

C−1.回路構成:

C−2.容量性負荷の駆動原理:

【0018】

A.装置構成 :

図1は、本実施例の容量性負荷駆動回路としての噴射ヘッド駆動回路を搭載したインク

ジェットプリンター10を例示した説明図である。図示したインクジェットプリンター1

0は、主走査方向に往復動しながら印刷媒体2上にインクドットを形成するキャリッジ2

0と、キャリッジ20を往復動させる駆動機構30と、印刷媒体2の紙送りを行うための

プラテンローラー40などから構成されている。キャリッジ20には、インクを収容した

インクカートリッジ26や、インクカートリッジ26が装着されるキャリッジケース22

、キャリッジケース22の底面側(印刷媒体2に向いた側)に搭載されてインクを噴射す

る噴射ヘッド24などが設けられており、インクカートリッジ26内のインクを噴射ヘッ

ド24に導いて、噴射ヘッド24から印刷媒体2に向かって正確な分量のインクを噴射す

ることが可能となっている。

【0019】

キャリッジ20を往復動させる駆動機構30は、プーリーによって張設されたタイミン

グベルト32や、プーリーを介してタイミングベルト32を駆動するステップモータ34

などから構成されている。タイミングベルト32の一箇所はキャリッジケース22に固定

されており、タイミングベルト32を駆動することでキャリッジケース22を往復動させ

ることができる。また、プラテンローラー40は、図示しない駆動モータやギア機構とと

もに、印刷媒体2の紙送りを行う紙送り機構を構成しており、印刷媒体2を副走査方向に

所定量ずつ紙送りすることが可能となっている。

【0020】

また、インクジェットプリンター10には、全体の動作を制御するプリンター制御回路

50や、噴射ヘッド24を駆動するための噴射ヘッド駆動回路200も搭載されている。

噴射ヘッド駆動回路200や、駆動機構30、紙送り機構などは、プリンター制御回路5

0の制御の下で、印刷媒体2を紙送りしながら噴射ヘッド24を駆動してインクを噴射す

ることによって、印刷媒体2上に画像を印刷していく。

【0021】

図2は、プリンター制御回路50の制御の下で、噴射ヘッド駆動回路200が噴射ヘッ

ド24を駆動する様子を示した説明図である。先ず始めに、噴射ヘッド24の内部構造に

ついて簡単に説明する。図示されている様に、噴射ヘッド24の底面(印刷媒体2に向い

ている面)には、インク滴を噴射する複数の噴射口100が設けられている。各噴射口1

00はそれぞれインク室102に接続されており、インク室102には、インクカートリ

ッジ26から供給されたインクが満たされている。各インク室102の上にはピエゾ素子

104が設けられており、ピエゾ素子104に電圧を印加すると、ピエゾ素子が変形して

インク室102を加圧することによって、噴射口100からインク滴を噴射することが可

能となっている。また、ピエゾ素子104は、印加する電圧値に応じて変形量が変わるの

で、ピエゾ素子104に適切な電圧波形を印加して、インク室102の変形量やタイミン

グを制御してやれば、適切な大きさのインク滴を、適切なタイミングで噴射することが可

能となる。

【0022】

ピエゾ素子104に印加する電圧波形(駆動波形)は、プリンター制御回路50の制御

の下で噴射ヘッド駆動回路200によって生成される。また、生成された駆動波形は、ゲ

ートユニット300を介してピエゾ素子104に供給される。ゲートユニット300は、

複数のゲート素子302が並列に接続された回路ユニットであり、各ゲート素子302は

、プリンター制御回路50からの制御の下で、個別に導通状態または切断状態とすること

が可能である。従って、噴射ヘッド駆動回路200から駆動波形を出力すると、プリンタ

ー制御回路50によって予め導通状態に設定されたゲート素子302だけを通過して、対

応するピエゾ素子104に印加され、その噴射口からインク滴が噴射されるようになって

いる。また、図2に示されるように、本実施例の噴射ヘッド駆動回路200は、制御回路

202や、駆動波形生成回路204などから構成されている。そして、プリンター制御回

路50が噴射ヘッド駆動回路200に対して駆動波形の出力を命令すると、その命令に応

じて制御回路202が駆動波形生成回路204の動作を制御することにより、噴射ヘッド

駆動回路200から適切な駆動波形が出力されるようになっている。

【0023】

ここで、周知のようにピエゾ素子はいわゆる容量性の負荷であり、電圧を印加すると、

印加した電圧に応じた電荷が、ピエゾ素子の内部に蓄えられる。そして、蓄えられる電荷

量は印加する電圧が高くなるほど増えていき、逆に、印加する電圧が低くなると、内部に

蓄えられていた電荷が放出される。そこで、印加電圧が低くなる際にピエゾ素子から放出

される電荷を複数のコンデンサー(電荷蓄積素子)などに蓄えておき、次に印加電圧が高

くなる際には、コンデンサーに蓄えておいた電荷をピエゾ素子に供給するようにしてやれ

ば、ピエゾ素子を少ない電力で効率よく駆動することが可能である。もっとも、詳細には

後述するが、ピエゾ素子から放出される電荷をコンデンサーで蓄える際に、各コンデンサ

ーに蓄える電荷量に偏りが生じると、そのことが原因となって電力効率の低下を引き起こ

す。そこで、本実施例の駆動波形生成回路204では、ピエゾ素子から放出される電荷を

次のような方法で回収しながら、駆動波形を生成することにより、電力効率の低下を引き

起こすことなくピエゾ素子を駆動することが可能となっている。

【0024】

B.第1実施例 :

B−1.回路構成 :

図3は、第1実施例の噴射ヘッド駆動回路200の詳細な構成を示した説明図である。

図示されているように、噴射ヘッド駆動回路200は、制御回路202と、駆動波形生成

回路204とから構成されており、更に、駆動波形生成回路204は、複数のコンデンサ

ーと、電源Vref と、複数のスイッチなどから構成されている。そして、複数のスイッチ

の接続状態は、制御回路202によって制御されている。尚、図3に示した例では、図が

煩雑となることを回避するために、コンデンサーC1 〜C3 の3つのコンデンサーを用い

て構成されているものとしているが、より多くのコンデンサーを用いて構成しても良い。

また、ここではインクジェットプリンター10の噴射ヘッド24を駆動するものとしてい

るから、駆動する負荷はピエゾ素子104であるものとしているが、実際には、容量成分

を有する電気負荷(容量性負荷)でありさえすれば、ピエゾ素子104に限らずどのよう

な電気負荷(例えば液晶などの各種表示装置など)であっても構わない。

【0025】

これら3つのコンデンサーC1 〜C3 の一方の端子は、それぞれグランドに接地されて

いる。このうちのコンデンサーC1 については、端子とグランドとの間にスイッチE1 が

設けられ、コンデンサーC2 については、端子とグランドとの間にスイッチE2 が設けら

れている。このため、スイッチE1 ,E2 をOFF(切断状態)とすることにより、コン

デンサーC1 ,C2 をグランドから浮かせることが可能となっている。これに対して、コ

ンデンサーC3 については、一方の端子が直接グランドに接地されている。

【0026】

また、コンデンサーC1 〜C3 の他方の端子は、それぞれスイッチS1 〜S3 を介して

電源Vref に接続されている。尚、電源Vref と各スイッチS1 〜S3 との間にもスイッ

チS4 が設けられており、このためスイッチS4 をOFFとすることで、スイッチS1 〜

S3 の設定状態に拘わらず、電源Vref と各コンデンサーC1 〜C3 とを切り離すことが

可能となっている。

【0027】

更に、コンデンサーC1 の接地側の端子と、コンデンサーC2 の電源側の端子とは、ス

イッチB1 を介して接続されている。このため、コンデンサーC1 の接地側に設けられた

スイッチE1 をOFFにしてコンデンサーC1 をグランドから切り離し、代わりにスイッ

チB1 をON(接続状態)にすることで、コンデンサーC2 の上にコンデンサーC1 を積

み上げるようにして、2つのコンデンサーを直列に接続することが可能となる。また、コ

ンデンサーC2 とコンデンサーC3 との間にも、同様なスイッチB2 が設けられている。

従って、コンデンサーC2 の接地側に設けられたスイッチE2 をOFFにして、代わりに

スイッチB2 をONにすることで、コンデンサーC3 の上にコンデンサーC2 を積み上げ

るようにして、2つのコンデンサーを直列に接続することが可能となる。

【0028】

このように、第1実施例の駆動波形生成回路204は、電源Vref と、複数のコンデン

サーCn と、各コンデンサーの一方の端子をグランドに接地するためのスイッチEn と、

各コンデンサーの他方の端子を電源Vref に接続するためのスイッチSn と、コンデンサ

ーCn の接地側の端子をコンデンサーCn+1 の電源側の端子に接続するためのスイッチB

n などから構成されている。そして、これらのスイッチEn ,Sn ,Bn の接続状態を切

り換えることで、ピエゾ素子104などの容量性負荷を、極めて少ない電力で効率よく駆

動することが可能となっている。

【0029】

B−2.容量性負荷の駆動原理 :

第1実施例の駆動波形生成回路204を用いて負荷を駆動するためには、コンデンサー

C1 〜C3 を予め充電しておく必要がある。そこで、各スイッチE1 ,E2 ,S1 〜S4

,B1 ,B2 の接続状態を切り換えて、コンデンサーC1 〜C3 と電源Vref とが並列に

接続された状態とすることで、コンデンサーC1 〜C3 を充電する。

【0030】

図4は、各スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続状態を切り換えて、コ

ンデンサーC1 〜C3 を充電する様子を示した説明図である。コンデンサーC1 〜C3 を

充電するためには、図示されているように、コンデンサーC1 の接地側の端子とコンデン

サーC2 の電源側の端子とを接続するためのスイッチB1 、およびコンデンサーC2 の接

地側の端子とコンデンサーC3 の電源側の端子とを接続するためのスイッチB2 を除いて

、他の全てのスイッチE1 ,E2 ,S1 〜S4 をON(接続状態)とする。こうすると、

コンデンサーC1 〜C3 の一方の端子はグランドに接地され、他方の端子は電源Vref に

接続される。その結果、各コンデンサーC1 〜C3 が電源Vref に対して並列に接続され

た状態となり、各コンデンサーC1 〜C3 の端子間の電圧が電源Vref の電圧Vref にな

るまで電荷が蓄えられる。尚、理解の便宜を図るため、図4では、スイッチがONにされ

て電流が流れる状態となっている配線を太い実線で表し、スイッチがOFFにされて電流

が流れない状態となっている配線を細い破線で表している。

【0031】

こうして各コンデンサーC1 〜C3 の端子間電圧が電源Vref の出力電圧Vref になる

まで充電したら、各スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続状態を切り換え

てピエゾ素子104を駆動することが可能となる。

【0032】

図5は、各スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続状態を切り換えること

で、ピエゾ素子104に印加される電圧が切り換わる様子を示した説明図である。例えば

、図5(a)に示すように、コンデンサーC1 の接地側のスイッチE1 のみをONにして

、他のスイッチを全てOFFにすると、コンデンサーC1 のみがピエゾ素子104に接続

される。上述したようにコンデンサーC1 の端子間電圧は電圧Vref になっているから、

ピエゾ素子104には電圧Vref が印加されることになる。尚、図5においても、スイッ

チがONにされて電流が流れる状態となっている配線を太い実線で表し、スイッチがOF

Fにされて電流が流れない状態となっている配線を細い破線で表している。

【0033】

次に、図5(b)に示すように、コンデンサーC1 の接地側のスイッチE1 をOFFに

して、代わりにコンデンサーC2 の接地側のスイッチE2 をONにするとともに、コンデ

ンサーC1 の接地側の端子とコンデンサーC2 の電源側の端子とを接続するスイッチB1

をONにする。すると、コンデンサーC1 とコンデンサーC2 とが直列に接続され、そし

てその状態で、これら2つのコンデンサーC1 ,C2 が、ピエゾ素子104に対して並列

に接続される。その結果、ピエゾ素子104には、2つのコンデンサーC1 ,C2 が直列

に接続された電圧に相当する2Vref の電圧値が印加されることになる。

【0034】

更に、図5(c)に示すように、コンデンサーC2 の接地側のスイッチE2 をOFFに

するとともに、コンデンサーC2 の接地側の端子とコンデンサーC3 の電源側の端子とを

接続するスイッチB2 をONにする。すると、既に直列に接続されている2つのコンデン

サーC1 ,C2 に加えて、新たにコンデンサーC3 が直列に接続されて、それら3つのコ

ンデンサーC1 ,C2 ,C3 が、ピエゾ素子104に対して並列に接続される。その結果

、ピエゾ素子104には、3つのコンデンサーC1 ,C2 ,C3 が直列に接続された電圧

に相当する3Vref の電圧値が印加される。

【0035】

以上の説明から明らかなように、スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続

状態を、図5(a)に示した状態から、図5(b)に示した状態、図5(c)に示した状

態へと切り換えていけば、ピエゾ素子104に印加する電圧を、Vref 、2Vref 、3V

ref へと増加させることができる。また逆に、図5(c)に示した状態から、図5(b)

に示した状態、図5(a)に示した状態へと切り換えていけば、印加する電圧を、3Vre

f 、2Vref 、Vref へと減少させることも可能となる。また、ピエゾ素子104のよう

な容量性負荷では、印加する電圧を増加させるに従って、負荷の内部に蓄えられる電荷が

多くなり、印加する電圧を減少させるに従って、内部に蓄えられていた電荷が放出される

。図5を用いて前述したように、第1実施例の駆動波形生成回路204では、コンデンサ

ーC1 ,C2 ,C3 を用いてピエゾ素子104に電圧を印加しているから、印加する電圧

の減少時に放出される電荷を回収して蓄えておき、印加する電圧の増加時には蓄えておい

た電荷をピエゾ素子104に供給することで、電力消費を抑えてピエゾ素子104を駆動

することが可能となる。

【0036】

もっとも、上述したように駆動波形生成回路204では、ピエゾ素子104に接続され

るコンデンサーC1 〜C3 を切り換えているから、印加する電圧を増加させるためにピエ

ゾ素子104に対して電荷を供給するコンデンサーと、電圧を減少させるためにピエゾ素

子104から電荷を回収するコンデンサーとが一致するとは限らない。その結果、個々の

コンデンサーに着目すると、ピエゾ素子104に供給する電荷の方が、ピエゾ素子104

から回収する電荷よりも多く、電荷が次第に減少していくコンデンサーや、逆に、ピエゾ

素子104に供給する電荷より回収する電荷の方が多く、電荷が次第に増加していくコン

デンサーなどが生じ得る。実際に、駆動波形生成回路204を用いてピエゾ素子104を

駆動していると、コンデンサーC1 〜C3 間で電荷の偏りが発生することがある。

【0037】

図6は、ピエゾ素子104を駆動する際に、コンデンサーC1 〜C3 で電荷の偏りが発

生し得る理由を模式化して示した説明図である。図6(a)には、ピエゾ素子104に印

加される電圧(印加電圧)が切り換わる様子が示されており、図6(b)には、その時の

各コンデンサーC1 〜C3 の接続状態が示されている。先ず始めは、ピエゾ素子104に

電圧Vref が印加されているものとする。この時の各コンデンサーC1 〜C3 の接続状態

は、図5(a)に示したように、コンデンサーC1 のみがピエゾ素子104に接続されて

おり、コンデンサーC2 ,C3 はピエゾ素子104から切断された状態となっている。図

6(b)で「OFF」と表示されているのは、コンデンサーがピエゾ素子104から切断

された状態であることを意味している。例えば図6(b)の左端については、コンデンサ

ーC1 のみがピエゾ素子104に接続され、コンデンサーC2 ,C3 は切断された状態で

あることを示している。その結果、図6(a)に示したように、ピエゾ素子104にはコ

ンデンサーC1 の端子電圧(電圧Vref )が印加されることになる。

【0038】

次に、図6(a)に示すようにピエゾ素子104の印加電圧を、電圧Vref から電圧2

Vref に切り換える。各スイッチE1 ,E2 ,S1 〜S4 、B1 ,B2 の接続状態に関し

て言えば、図5(a)に示した接続状態から、図5(b)に示した接続状態に切り換えれ

ばよい。すると、前述したように2つのコンデンサーC1 ,C2 が直列に接続されて、合

計した電圧(すなわち電圧2Vref )がピエゾ素子104に印加される。ピエゾ素子10

4の端子間電圧は電圧Vref であり、ここに2つのコンデンサーC1 ,C2 の合計電圧2

Vref が印加されるから、コンデンサーC1 ,C2 からピエゾ素子104へと電荷が供給

され、ピエゾ素子104内に電荷が溜まるに従ってピエゾ素子104の端子間電圧が増加

していき、最終的には、2つのコンデンサーC1 ,C2 の合計電圧と等しくなる。

【0039】

図6(a)には、ピエゾ素子104の印加電圧を電圧Vref から電圧2Vref に増加さ

せる際に、以上のようにしてコンデンサーからピエゾ素子104に電荷が供給され、その

結果として電圧2Vref が印加される旨が、白抜きの矢印によって表されている。また、

図6(b)には、ピエゾ素子104の印加電圧を電圧Vref から電圧2Vref に増加させ

るに伴って、コンデンサーC1のみが接続された状態から、2つのコンデンサーC1 ,C

2 が接続された状態に切り換わる様子が示されている。そして、印加電圧を電圧Vref か

ら電圧2Vref に増加させる途中は2つのコンデンサーC1 ,C2 が接続されているから

、ピエゾ素子104に供給される電荷は2つのコンデンサーC1 ,C2 から供給される。

図6(b)中に示した白抜きの矢印は、コンデンサーからピエゾ素子104に電荷が供給

されることを表している。

【0040】

ピエゾ素子104の印加電圧を、電圧2Vref から電圧3Vref に切り換える場合も同

様に、コンデンサーからピエゾ素子104に電荷を供給することによって、ピエゾ素子1

04の端子間電圧を電圧3Vref まで増加させる。すなわち、スイッチE1 ,E2 ,S1

〜S4 、B1 ,B2 の接続状態を、図5(b)に示した状態から図5(c)に示した状態

に切り換えることで、2つのコンデンサーC1 ,C2 が直列に接続された状態から、3つ

のコンデンサーC1 〜C3 が直列に接続された状態に切り換える。すると、3つのコンデ

ンサーC1 〜C3 の合計電圧は電圧3Vref となって、ピエゾ素子104の端子間電圧2

Vref よりも高くなるので、3つコンデンサーC1 〜C3 からピエゾ素子104へと電荷

が供給されていく。図6(b)には、ピエゾ素子104の印加電圧を電圧2Vref から電

圧3Vref に増加させるに伴って、2つのコンデンサーC1 ,C2 が接続された状態から

、3つのコンデンサーC1 〜C3 が接続された状態に切り換わり、この時、コンデンサー

C1 〜C3 から電荷がピエゾ素子104に供給される様子が示されている。

【0041】

次に、ピエゾ素子104の印加電圧を電圧3Vref から電圧2Vref に減少させる場合

は、スイッチE1 ,E2 ,S1 〜S4 、B1 ,B2 の接続状態を、図5(c)に示した状

態から図5(b)に示した状態に切り換える。すると、3つのコンデンサーC1 〜C3 が

直列に接続された状態から、2つのコンデンサーC1 ,C2 が直列に接続された状態に切

り換わり、2つのコンデンサーC1 ,C2 の合計電圧2Vref よりも、ピエゾ素子104

の端子間電圧3Vref の方が高くなる。このためピエゾ素子104から2つのコンデンサ

ーC1 ,C2 に向かって電荷が放出され、ピエゾ素子104内の電荷が少なくなるに従っ

てピエゾ素子104の端子間電圧が減少していき、最終的には、2つのコンデンサーC1

,C2 の合計電圧と等しくなる。図6(a)には、ピエゾ素子104からコンデンサーに

電荷が放出されて、ピエゾ素子104の印加電圧が減少する様子が、斜線を付した矢印に

よって表されている。

【0042】

また、図6(b)には、ピエゾ素子104の印加電圧を電圧3Vref から電圧2Vref

に減少させるに伴って、3つのコンデンサーC1 〜C3 が接続された状態から、2つのコ

ンデンサーC1 ,C2 が接続された状態に切り換わる様子が示されている。そして、印加

電圧を電圧3Vref から電圧2Vref に減少させる途中は2つのコンデンサーC1 ,C2

が接続されているから、ピエゾ素子104から放出される電荷は2つのコンデンサーC1

,C2 に蓄えられることになる。図6(b)中に斜線を付して示した矢印は、コンデンサ

ーがピエゾ素子104から電荷を回収することを表している。

【0043】

ピエゾ素子104の印加電圧を、電圧2Vref から電圧Vref に減少させる場合も同様

である。すなわち、スイッチE1 ,E2 ,S1 〜S4 、B1 ,B2 の接続状態を、図5(

b)に示した状態から図5(a)に示した状態に切り換えると、2つのコンデンサーC1

,C2 が直列に接続されてピエゾ素子104に接続されている状態から、コンデンサーC

1 のみがピエゾ素子104に接続された状態に切り換わる。その結果、ピエゾ素子104

からコンデンサーC1 へと電荷が放出され、それに伴ってピエゾ素子104の端子間電圧

が減少していき、最終的には、ピエゾ素子104に印加電圧Vref が印加された状態とな

る。また、この時、ピエゾ素子104に接続されているコンデンサーはコンデンサーC1

のみであるから、ピエゾ素子104が放出する電荷はコンデンサーC1 に蓄えられること

になる。

【0044】

以上に説明したように、3つのコンデンサーC1 〜C3 を充電した後、各スイッチE1

,E2 ,S1 〜S4 、B1 ,B2 の接続状態を切り換えることで、ピエゾ素子104の印

加電圧を切り換えていくことが可能である。また、ここでは図示が煩雑となることを避け

るために、コンデンサーの個数は3つとしているが、実際にはコンデンサーを多くすると

ともに、電源Vref の電圧値を小さくすれば、印加電圧をより細かい電圧で切り換えるこ

とができる。その結果、任意の波形の電圧を生成してピエゾ素子104に印加することも

可能である。

【0045】

しかし、印加電圧を切り換えるために、各コンデンサーとピエゾ素子104との間でや

り取りする過程で、コンデンサー間に電荷の偏りが生じ得る。この点について、図6(b

)を用いて説明する。例えば、コンデンサーC2 については、印加電圧が電圧Vref から

電圧2Vref に増加する際と、電圧2Vref から電圧3Vref に増加する際とで電荷を放

出し、そして、印加電圧が電圧3Vref から電圧2Vref に減少する際にだけ電荷を受け

取っている。従って、コンデンサーC2 については、ピエゾ素子104に供給する電荷が

、ピエゾ素子104から回収する電荷を上回り、電荷が次第に減少するものと考えられる

。また、コンデンサーC3 については、ピエゾ素子104に電荷を供給するだけなので電

荷が減少することになる。

【0046】

各コンデンサー間で、このような電荷量の偏りが発生する理由は、次のように考えれば

直感的に了解できる。先ず、図5を用いて前述したように、印加電圧Vref はコンデンサ

ーC1 のみによって生成され、印加電圧2Vref は2つのコンデンサーC1 ,C2 を直列

接続することによって生成され、印加電圧3Vref は3つのコンデンサーC1 〜C3 を直

列接続することによって生成される。図6(c)には、これら3種類の印加電圧(Vref

、2Vref 、3Vref )と、それら印加電圧を生成するために用いられるコンデンサーと

が示されている。

【0047】

また、ピエゾ素子104の印加電圧を電圧Vref から電圧2Vref に増加させるために

は、2つのコンデンサーC1 ,C2 を直列接続して、コンデンサーC1 ,C2 からピエゾ

素子104に電荷を供給する。図6(c)には、直列接続された2つのコンデンサーC1

,C2 から電荷が供給されることで、ピエゾ素子104の印加電圧が徐々に増加する様子

が概念的に示されている。更に、ピエゾ素子104の印加電圧を電圧2Vref から電圧3

Vref に増加させる際には、3つのコンデンサーC1 〜C3 を直列接続してコンデンサー

C1 〜C3 からピエゾ素子104に電荷を供給する。図6(c)には、直列接続された3

つのコンデンサーC1 〜C3 から電荷が供給されることで、ピエゾ素子104の印加電圧

が2Vref から3Vref に徐々に増加する様子が概念的に示されている。

【0048】

このようにピエゾ素子104の印加電圧を増加させる際には、コンデンサーからピエゾ

素子104に電荷が供給され、その電荷は、その印加電圧を生成するために直列接続され

た各コンデンサーによって負担される。これに対してピエゾ素子104の印加電圧を減少

させる際には、ピエゾ素子104からコンデンサーに電荷が放出される。そして、放出さ

れた電荷は、その時に接続されているコンデンサーに蓄えられる。

【0049】

例えば、ピエゾ素子104の印加電圧を電圧3Vref から電圧2Vref に減少させる際

には、ピエゾ素子104から電荷量Qの電荷が放出され、この電荷は、電圧2Vref を生

成するための直列接続されている2つのコンデンサーC1 、C2 に蓄えられる。すなわち

、印加電圧を電圧2Vref から電圧3Vref に増加させる際には、3つのコンデンサーC

1 〜C3 から電荷を供給したにも拘わらず、印加電圧が電圧3Vref から電圧2Vref に

減少する際には、2つのコンデンサーC1 ,C2 によって電荷を回収することになる。図

6(c)には、ピエゾ素子104から電荷が放出されることで、印加電圧が電圧3Vref

から電圧2Vref に徐々に減少する様子が概念的に示されている。このように、印加電圧

を増加するために用いられるコンデンサー(ピエゾ素子104に電荷を供給するコンデン

サー)と、印加電圧を減少させるために用いられるコンデンサー(ピエゾ素子104から

電荷を回収するコンデンサー)との間に不一致が発生すると、その結果として、各コンデ

ンサーの間で電荷量の偏りが生ずることがある。同様にして、印加電圧を電圧Vref から

電圧2Vref に増加させる際には、2つのコンデンサーC1 ,C2 から電荷を供給するに

も拘わらず、印加電圧が電圧2Vref から電圧Vref に減少する際には、コンデンサーC

1 のみによって電荷を回収する。このため、印加電圧を電圧Vref から電圧2Vref に増

加させ、再び電圧Vref に減少させる際に、コンデンサーの間で電荷量の偏りが発生する

ことが起こり得る。また、図6に示した例では、コンデンサーC2 ,C3 の電荷が減少し

得るだけであるが、印加しようとする電圧波形が異なれば、他のコンデンサーで電荷が減

少したり、あるいは電荷が増加するコンデンサーが発生したりすることも起こり得る。

【0050】

もちろん、ピエゾ素子104を駆動するために用いられるコンデンサーC1 〜C3 の静

電容量は、ピエゾ素子104の静電容量に較べて十分に大きいので、ピエゾ素子104を

少しの間、駆動する程度では、コンデンサーC1 〜C3 の端子電圧が大きく変化すること

はない。しかし、長い間に亘ってピエゾ素子104を駆動していると、大きな電荷の偏り

が発生して、コンデンサーの端子間電圧が変化してしまう場合が生じ得る。そして、コン

デンサーの端子間電圧が大きく変化すると、適切な電圧波形を印加することができなくな

ってしまう。こうしたことを回避するためには、端子間電圧が増加したコンデンサーにつ

いては、過剰に蓄えられた電荷をグランドに放出して、コンデンサーの端子間電圧を初期

の電圧Vref まで下げなければならない。逆に、端子間電圧が減少したコンデンサーにつ

いては、不足した電荷を電源Vref から補充して、端子間電圧を初期の電圧Vref まで上

げなければならない。そして、グランドに放出した分の電荷は電力の損失となり、また、

電源Vref から補充した分の電荷は、新たな電力の供給となるため、結果として、ピエゾ

素子104を駆動する電力効率の低下を引き起こす。

【0051】

そこで第1実施例の駆動波形生成回路204では、コンデンサー間での電荷の偏り(端

子間電圧の偏り)に起因して生じるこのような電力損失の発生を回避するために、各コン

デンサーC1 〜C3 の間で、電荷の再分配を行う。

【0052】

図7は、第1実施例の駆動波形生成回路204で、各コンデンサーC1 〜C3 の電荷を

再分配する様子を示した説明図である。ピエゾ素子104を印加電圧Vref で駆動してい

る時は、前述したようにコンデンサーC1 のみをピエゾ素子104に接続しておくだけで

も、電圧Vref を印加することができる。図7(a)には、コンデンサーC1 のみがピエ

ゾ素子104に接続されている様子が示されている。図7(a)に示されているように、

コンデンサーC1 のみをピエゾ素子104に接続した状態では、他のコンデンサーC2 ,

C3 はいわば遊んだ状態となっている。そこで第1実施例の駆動波形生成回路204では

、これらのコンデンサーC2 ,C3 を、ピエゾ素子104に接続されたコンデンサーC1

に並列に接続する。すなわち、図7(b)に示したように、スイッチB1 ,B2 およびス

イッチS4 はOFFにしたまま、スイッチS1 〜S3 およびスイッチE2 をONにする。

【0053】

前述したように、コンデンサーC1 〜C3 は何れも電源Vref によって端子間電圧Vre

f に充電されている。従って、ピエゾ素子104にコンデンサーC1 を接続して電圧Vre

f を印加している処に、更にコンデンサーC1 に対してコンデンサーC2 ,C3 を並列に

接続しても、ピエゾ素子104に印加している電圧Vref にはほとんど影響が現れること

はない。そして、コンデンサーC1 〜C3 は互いに並列に接続されているから、端子間電

圧の高いコンデンサーから端子間電圧の低いコンデンサーに向かって電荷が供給されて、

コンデンサーC1 〜C3 の間で電荷の再分配が行われる。その結果、コンデンサー間での

電荷の偏り(端子間電圧の偏り)に起因した電力損失の発生を回避することが可能となる

。

【0054】

尚、以上では、ピエゾ素子104にコンデンサーC1 を接続して電圧Vref を印加した

まま、更にコンデンサーC2 ,C3 を接続するものとして説明した。コンデンサーC1 〜

C3 の端子間電圧は何れも電圧Vref であるから、コンデンサーC1 を用いて電圧Vref

を印加中でも、印加電圧にはほとんど影響を与えることなく、コンデンサーC2 ,C3 を

接続して電荷を再分配することが可能である。しかし、ピエゾ素子104に電圧を印加し

ない状態が発生するのであれば、その間に、図7(c)に示すように、コンデンサーC1

〜C3 を互いに並列に接続することで、電荷を再分配しても構わない。

【0055】

図8は、第1実施例の駆動波形生成回路204がピエゾ素子104に電圧を印加しなが

ら、コンデンサーC1 〜C3 間での電荷の再分配を行う様子を示した説明図である。図8

では、一例として、山型の電圧波形を生成した後に、コンデンサーC1 では電荷が増加し

、コンデンサーC2 ,C3 では電荷が減少するものとする。図8(a)には、各スイッチ

B1 ,B2 ,E1 ,E2 ,S1 〜S4 の接続状態が時間とともに切り換わる様子が示され

ており、図8(b)には、その結果として生成される電圧波形が示されており、そして図

8(c)には、電圧波形を生成した後に、各コンデンサーC1 〜C3 の電荷量が増減する

様子が示されている。

【0056】

第1実施例の駆動波形生成回路204が、ピエゾ素子104の印加電圧を電圧Vref か

ら電圧3Vref に増加させた後、電圧Vref まで減少させる動作については、図6を用い

て前述した動作と全く同じである。また、ここでは、ピエゾ素子104の印加電圧を変化

させることにより、コンデンサーC1 では電荷が増加し、コンデンサーC2 ,C3 では電

荷が減少するものとする。

【0057】

そこで、第1実施例の駆動波形生成回路204では、ピエゾ素子104の印加電圧を電

圧Vref まで減少させた後、図8(b)に示したように、電圧Vref を印加したままで、

コンデンサーC1 〜C3 を並列に接続する。図8では、ピエゾ素子104に電圧Vref を

印加したまま、コンデンサーC1 〜C3 を並列に接続している期間を、斜線を付して表し

ている。こうすれば、図8(c)中に太い破線の矢印で示したように、コンデンサーC1

に過剰に溜まった電荷が、電荷の減少したコンデンサーC2 ,C3 に供給されて、コンデ

ンサーC1 〜C3 間で電荷の再分配が行われる。その結果、図8(b)に示したように、

ピエゾ素子104の印加電圧も、正しい電圧Vref に収束していく。

【0058】

以上に説明したように、第1実施例の駆動波形生成回路204では、複数のコンデンサ

ーC1 〜C3 を予め同じ電圧に充電しておき、それらコンデンサーC1 〜C3 の接続状態

を切り換えることで、ピエゾ素子104を駆動する。そして、ピエゾ素子104に印加す

る電圧が、コンデンサー1つ分の電圧になると、複数のコンデンサーC1 〜C3 を互いに

並列に接続することで、コンデンサーC1 〜C3 間での電荷の再分配を行う。こうするこ

とで、電荷の偏りに起因して端子間電圧が変化することを回避することができるので、正

確な電圧の駆動波形を生成することが可能となる。

【0059】

B−3.変形例 :

上述した第1実施例では、ピエゾ素子104にコンデンサーC1 のみを接続して、印加

電圧を電圧Vref 近くまで減少させた後、コンデンサーC1 およびピエゾ素子104に対

して、コンデンサーC2 ,C3 を並列に接続することで、コンデンサーC1 〜C3 間で電

荷の再分配を行うものとして説明した。これに対して、ピエゾ素子104の印加電圧を電

圧Vref に切り換える際には、初めからピエゾ素子104に対して、3つのコンデンサー

C1 〜C3 を並列に接続することとしても良い。こうすれば、上述した第1実施例と比較

して、コンデンサーC1 〜C3 間で電荷を再分配するための時間を十分に確保することが

可能となる。

【0060】

更に加えて、こうした変形例の駆動波形生成回路204では、コンデンサーC1 〜C3

間で電荷を再分配するための時間を十分に確保することができるので、電荷の再分配がほ

とんど終了した後に、電源Vref から各コンデンサーC1 〜C3 に対して電荷を補充する

こととしても良い。

【0061】

図9は、第1実施例の変形例の駆動波形生成回路204において、コンデンサーC1 〜

C3 で電荷の再分配を行った後に、各コンデンサーC1 〜C3 に対して電荷を補充する様

子を示した説明図である。図9(a)は、コンデンサーC1 〜C3 で電荷の再分配を行っ

ている状態を表している。尚、ここでも、図8に示した場合と同様に、コンデンサーC1

では電荷が増加し、コンデンサーC2 ,C3 では電荷が減少するものとする。また、特に

言及しない点については、前述した第1実施例と同様である。第1実施例の変形例の駆動

波形生成回路204では、ピエゾ素子104に印加すべき電圧が電圧Vref になると、図

9(a)に示したように、各コンデンサーC1 〜C3 の電源側のスイッチS1 〜S3 、お

よび接地側のスイッチE1 、E2 を初めから接続状態(ON)に切り換えて、ピエゾ素子

104に電圧Vref を印加すると同時に、コンデンサーC1 〜C3 間での電荷の再分配を

行う。図9(a)には、電荷が過剰に蓄えられたコンデンサーC1 から、電荷の不足する

コンデンサーC2 ,C3 に向かって電荷が供給されることで、電荷の再分配が行われる様

子が、破線の矢印によって表されている。

【0062】

そして、電荷の再分配が、ある程度まで進んだら(たとえば、再分配の開始後、ある程

度の時間が経過したら)、図9(b)に示したように、その状態から更に、電源Vref を

接続するためのスイッチS4 をONにすることで、各コンデンサーC1 〜C3 に対して電

源Vref も並列に接続する。図9(b)には、電源Vref から各コンデンサーC1 〜C3

に対して電荷が補充される様子が、破線の矢印によって表されている。

【0063】

図10は、第1実施例の変形例の駆動波形生成回路204がピエゾ素子104に電圧を

印加する様子を示した説明図である。図示した第1実施例の変形例は、図8を用いて前述

した第1実施例に対して、印加電圧が電圧Vref になると、直ちに各コンデンサーC1 〜

C3 間で電荷の再分配を行う点と、電荷の再分配を行って暫く時間が経過した後は、電荷

の補充を行う点とが異なっている。その他の点については、同様である。図10では、電

荷の再分配を行っている時間には粗い斜線を付し、電荷を補充している時間には細かい斜

線を付して表示している。

【0064】

こうすれば、図10(c)に示されているように、印加電圧が電圧2Vref から電圧V

ref に減少する際に、ピエゾ素子104から放出される電荷が、コンデンサーC1 だけで

なく、コンデンサーC2 ,C3 にも分配されるので、コンデンサーC1 〜C3 間での電荷

の再分配を速やかに完了させることが可能となる。その結果、図10(b)に示されるよ

うに、ピエゾ素子104の印加電圧が、より速やかに電圧Vref に切り換わるので、より

正確な電圧波形でピエゾ素子104を駆動することが可能となる。

【0065】

また、回路での損失などによって電力損失が発生した場合には、電荷の再分配後にコン

デンサーC1 〜C3 の電荷量が不足する事態も生じ得る。しかし、第1実施例の変形例で

は、コンデンサーC1 〜C3 間で電荷の再分配を速やかに行うことができるので、図10

中に細かい斜線を付して示したように、その後は、電源Vref から電荷を補充することが

できる。その結果、各コンデンサーC1 〜C3 の端子間電圧を常に初期の電圧Vref に維

持しておくことができるので、ピエゾ素子104に正確な電圧を印加することが可能とな

る。また、コンデンサーC1 〜C3 間で電荷を再分配した後に、電源Vref から電荷を補

充しているため、電力損失で失われた最小限の電荷だけを補充することが可能となる。

【0066】

C.第2実施例 :

上述した第1実施例では、比較的単純な例として、駆動波形生成回路204が、各コン

デンサーC1 〜C3 と電源Vref とを接続するためのスイッチS1 〜S4 と、コンデンサ

ーC1 ,C2 の接地側の端子をグランドに接続するためのスイッチE1 ,E2 と、各コン

デンサーC1 〜C3 を直列に接続するためのスイッチB1 ,B2 とによって構成されてい

るものとして説明した。しかし実際には、各コンデンサーC1 〜C3 が同じ電圧で充電さ

れ、且つ、各コンデンサーC1 〜C3 が互いに並列に接続することが可能でありさえすれ

ば、どのような駆動波形生成回路に対しても、第1実施例と同様にして各コンデンサーC

1 〜C3 間での電荷を再分配することが可能である。以下では、このような第2実施例の

駆動波形生成回路304について説明する。尚、第2実施例において、第1実施例と同様

の構成部分については第1実施例と同様の符号を付すとともに、その詳細な説明を省略す

る。

【0067】

C−1.回路構成 :

図11は、第2実施例の駆動波形生成回路304の一例を示した回路図である。図11

に示した第2実施例の駆動波形生成回路304は、図3を用いて前述した第1実施例の駆

動波形生成回路204に対して、新たに補助電源Vbootが追加されており、この補助電源

VbootがコンデンサーC1 〜C3 の接地側の端子に接続され、そして、補助電源Vbootと

各コンデンサーC1 〜C3 との間には、スイッチSb1〜Sb3が設けられた回路構成となっ

ている。また、第1実施例の駆動波形生成回路204では、コンデンサーC3 の接地側の

端子はグランドに直接接続されていたが、第2実施例の駆動波形生成回路304では、コ

ンデンサーC3 の接地側(正確には低電位側)の端子に、スイッチSb3を介して補助電源

Vbootを接続可能となっていることに伴って、コンデンサーC3 の低電位側の端子とグラ

ンドとの間にも、スイッチE3 が新たに追加されている。

【0068】

このような第2実施例の駆動波形生成回路304では、補助電源Vbootを用いなければ

、前述した第1実施例の駆動波形生成回路204と同様に作動して、ピエゾ素子104の

印加電圧を、電圧Vref 〜電圧3Vref の範囲で変化させることができる。更に、補助電

源Vbootを用いれば、ピエゾ素子104に印加する電圧範囲を、電圧Vref 〜電圧3Vre

f +Vbootの範囲に拡大することが可能である。そして、このような第2実施例の駆動波

形生成回路304においても、印加電圧を変化させることに伴って、コンデンサーC1 〜

C3 間で電荷の偏りが発生する可能性があり、それに起因した電力損失が生じ得る。そこ

で、第2実施例の駆動波形生成回路304においても、コンデンサーC1 〜C3 間で電荷

の再分配を行うことにより、電荷の偏りに起因した電力損失が発生することを回避してい

る。以下では、この点について説明する。

【0069】

C−2.容量性負荷の駆動原理 :

図12は、第2実施例の駆動波形生成回路304がピエゾ素子104の印加電圧を切り

換える様子を示した説明図である。図12(a)には、ピエゾ素子104に印加しようと

する目標の電圧波形が示されており、図12(b)には、補助電源Vbootと各コンデンサ

ーC1 〜C3 とを接続するスイッチSb1〜Sb3の接続状態が示されている。たとえば、図

12(b)に「OFF」と表示されているのは、スイッチSb1〜Sb3が何れも切断状態(

OFF)になっていることを表しており、「Sb1」と表示されているのは、スイッチSb1

が接続状態(ON)になっていることを表している。また、図12(c)には、ピエゾ素

子104の印加電圧を切り換えるために、各コンデンサーC1 〜C3 とピエゾ素子104

との間で電荷のやり取りが行われる様子が示されており、そして、図12(d)には、実

際にピエゾ素子104に印加される電圧波形が示されている。

【0070】

先ず、印加電圧を電圧Vref 〜電圧3Vref まで増加させる際には、前述した第1実施

例と同様にして、各コンデンサーC1 〜C3 の接続状態を切り換えることにより、ピエゾ

素子104の印加電圧を変化させる。すなわち、図12(b)に示すように、補助電源V

bootを接続するためのスイッチSb1〜Sb3は何れもOFFにした状態で、コンデンサーC

1 の低電位側の端子をグランドに接続するスイッチE1 をONにすることで、コンデンサ

ーC1 のみを用いて電圧Vref をピエゾ素子104に印加する。次に、スイッチE1 をO

FFにして、代わりにコンデンサーC2 の低電位側の端子をグランドに接続するスイッチ

E2 をONにするとともに、コンデンサーC1 とコンデンサーC2 とを接続するスイッチ

B1 をONにする。こうすると、2つのコンデンサーC1 ,C2 を直列に接続して得られ

る電圧2Vref が、ピエゾ素子104に印加される。更に、スイッチE2 をOFFにして

、代わりに、コンデンサーC3 の低電位側の端子をグランドに接続するスイッチE3 をO

Nにするとともに、スイッチB1 ,B2 をONにすることで、3つのコンデンサーC1 〜

C3 を直列に接続する。こうすると、ピエゾ素子104には、3つのコンデンサーC1 〜

C3 を直列に接続して得られる電圧3Vref が印加されることになる。以上の動作は、第

1実施例の駆動波形生成回路204がピエゾ素子104の印加電圧を切り換える動作と同

様である。

【0071】

ここで、第2実施例の駆動波形生成回路304には補助電源Vbootが設けられているの

で、この補助電源Vbootを用いることで、更に高い電圧をピエゾ素子104に印加するこ

とが可能となる。たとえば、補助電源Vbootが出力する電圧Vbootを、少なくとも電圧2

Vref よりも高い電圧としておけば、補助電源VbootとコンデンサーC1 とを直列に接続

することで、3つのコンデンサーC1 〜C3 を直列に接続した場合よりも高い電圧を発生

させることが可能である。そこで、図12(b)に示したように、スイッチSb1をONに

して、コンデンサーC1 の低電位側の端子を補助電源Vbootに接続する。尚、スイッチS

b1をONにすることに伴って、コンデンサーC1 の低電位側の端子をグランドに接続する

ためのスイッチE1 はOFFにしておく。こうすれば、補助電源VbootとコンデンサーC

1 とが直列に接続されて、それによって得られた電圧Vboot+Vref が、ピエゾ素子10

4に印加されることになる。

【0072】

続いて、図12(b)に示すように、スイッチSb1をOFFにして代わりにスイッチS

b2をONにするとともに、コンデンサーC1 とコンデンサーC2 とを接続するスイッチB

1 をONにする。すると、補助電源VbootとコンデンサーC2 とが直列に接続され、更に

コンデンサーC1 とコンデンサーC2 とが直列に接続されるので、結局、補助電源Vboot

と、2つのコンデンサーC1 ,C2 とが直列に接続されて、補助電源Vbootの発生電圧V

bootに、2つのコンデンサーC1 ,C2 の端子間電圧を加えた合計電圧Vboot+2Vref

を、ピエゾ素子104に印加することができる。

【0073】

更に続いて、図12(b)に示すように、スイッチSb2をOFFにして代わりにスイッ

チSb3をONにすることで、補助電源VbootとコンデンサーC3 とを直列に接続するとと

もに、スイッチB1 およびスイッチB2 をONにすることで、3つのコンデンサーC1 〜

C3 を直列に接続する。その結果、補助電源Vbootと、3つのコンデンサーC1 〜C3 と

が直列に接続されて、発生電圧Vbootに3つのコンデンサーC1 〜C3 の端子間電圧を加

えた合計電圧Vboot+3Vref をピエゾ素子104に印加することが可能となる。

【0074】

以上のようにして、スイッチE1 〜E3 、Sb1〜Sb3、B1 、B2 の接続状態を切り換

えていけば、ピエゾ素子104の印加電圧を、電圧Vref 〜電圧Vboot+3Vref まで増

加させることができる。そして、前述した第1実施例の駆動波形生成回路204と同様に

、ピエゾ素子104の印加電圧を増加させるに伴って、ピエゾ素子104に接続されてい

るコンデンサーからピエゾ素子104に向かって電荷が供給される。図12(c)には、

印加電圧が電圧Vref 〜電圧Vboot+3Vref まで増加する際に、ピエゾ素子104に接

続されるコンデンサーと、各コンデンサーから電荷が供給される様子とが示されている。

尚、図6(b)と同様に、図12(c)中の「OFF」という表示は、コンデンサーがピ

エゾ素子104から切断された状態であることを意味している。また、図12(c)中の

白抜きの矢印は、コンデンサーからピエゾ素子104に電荷が供給されることを示してい

る。

【0075】

ピエゾ素子104の印加電圧を減少させる場合は、印加電圧を増加させる場合と逆の動

作を行えばよい。以下、簡単に説明すると、先ず、3つのコンデンサーC1 〜C3 が直列

に接続されている状態(すなわち、スイッチB1 ,B2 がON)から、コンデンサーC2

とコンデンサーC3 との間のスイッチB2 をOFFにして、コンデンサーC3 を切り離す

。そして、補助電源VbootとコンデンサーC3 との間のスイッチSb3をOFFにして、代

わりに補助電源VbootとコンデンサーC2 との間のスイッチSb2をONにすることで、補

助電源VbootをコンデンサーC2 に接続する。コンデンサーC3 が切り離されて2つのコ

ンデンサーC1 ,C2 が直列に接続されているところに、補助電源Vbootが接続されるか

ら、補助電源Vbootの発生電圧Vbootに、2つのコンデンサーC1 ,C2 の端子間電圧を

加えた合計電圧Vboot+2Vref が、ピエゾ素子104に印加されることになる。

【0076】

その状態から、更にスイッチB1 をOFFにしてコンデンサーC2 をコンデンサーC1

から切り離すとともに、スイッチSb2をOFFにしてスイッチSb1をONにすることで、

コンデンサーC2 に接続されていた補助電源VbootをコンデンサーC1 に繋ぎ代える。す

ると、ピエゾ素子104に印加される電圧は、電圧Vboot+2Vref から電圧Vboot+V

ref に減少する。更に、補助電源VbootとコンデンサーC1 とを接続するスイッチSb1を

OFFにするとともに、スイッチB1 ,B2 をONにして(すなわち、3つのコンデンサ

ーC1 〜C3 を直列に接続して)、コンデンサーC3 の低電位側の端子をグランドに接続

するべくスイッチE3 をONにする。すると、ピエゾ素子104に印加される電圧は、電

圧Vboot+Vref から電圧3Vref に減少する。ピエゾ素子104に印加される電圧を、

電圧3Vref から電圧Vref に減少させる手順は、図5あるいは図6を用いて前述した第

1実施例の駆動波形生成回路204と同様であるため説明は省略する。

【0077】

以上のようにして、スイッチE1 〜E3 、Sb1〜Sb3、B1 、B2 の接続状態を切り換

えることで、ピエゾ素子104の印加電圧を、電圧Vboot+3Vref 〜電圧Vref に減少

させることができる。そして、こうしてピエゾ素子104の印加電圧を減少させるに伴っ

て、ピエゾ素子104から放出された電荷が、ピエゾ素子104に接続されているコンデ

ンサーによって回収されることになる。図12(c)には、印加電圧が電圧Vboot+3V

ref 〜電圧Vref に減少する際に、ピエゾ素子104に接続されるコンデンサーと、各コ

ンデンサーによって電荷が回収される様子とが示されている。尚、図12(c)中に示し

た斜線付きの矢印は、ピエゾ素子104が放出した電荷がコンデンサーによって回収され

ることを表している。

【0078】

以上のようにして、第2実施例の駆動波形生成回路304では、ピエゾ素子104に印

加する電圧を、電圧Vref 〜電圧Vboot+3Vref までの範囲で自由に変化させることが

できるが、その際に、各コンデンサーC1 〜C3 とピエゾ素子104との間で電荷のやり

取りが行われ、その結果として、第1実施例の駆動波形生成回路204と同様に、コンデ

ンサーC1 〜C3 の間で電荷の偏りが生じ得る。そして、このような電荷の偏りが蓄積さ

れると、各コンデンサーC1 〜C3 の端子間電圧が変化してしまい、正確な電圧を印加す

ることができなくなる。また、こうした事態を回避しようとすると、電荷が過剰に蓄積さ

れたコンデンサーについては電荷をグランドに放出し、電荷が不足したコンデンサーにつ

いては電源Vref から電荷を補充しなければならないので、その分の電力は損失となる。

【0079】

そこで、第2実施例の駆動波形生成回路304においても、前述した第1実施例の駆動

波形生成回路204と同様に、各コンデンサーC1 〜C3 の間で電荷の再分配を行う。す

なわち、ピエゾ素子104の印加電圧を電圧Vref まで減少させた後、電圧Vref を印加

したままで、コンデンサーC1 〜C3 を並列に接続する。

【0080】

図13は、第2実施例の駆動波形生成回路304でコンデンサーC1 〜C3 間の電荷を

再分配する様子を示す説明図である。尚、ここでも、コンデンサーC1 では電荷が過剰に

回収され(電荷が増加し)、コンデンサーC2 ,C3 では電荷を過剰に供給(電荷が減少

)するものとする。図13(a)には、電圧Vref を印加している状態が示されており、

この状態から図13(b)に示したように、スイッチS1 〜S3 およびスイッチE1 〜E

3 をONにして、3つのコンデンサーC1 〜C3 が並列に接続された状態に切り換える。

すると、コンデンサーC1 に過剰に蓄えられた電荷が、コンデンサーC2 ,C3 に供給さ

れて、電荷の再分配が行われる。図13(b)には、コンデンサーC1 〜C3 間の電荷の

流れが破線の矢印によって示されている。

【0081】

以上に説明したように、第2実施例の駆動波形生成回路304においても、ピエゾ素子

104に接続されるコンデンサーが1つになると(すなわち印加電圧が電圧Vref になる

と)、他のコンデンサーもそのコンデンサーに対して並列に接続することで、各コンデン

サーC1 〜C3 間で電荷の再分配を行う。こうすることで、電荷の偏りに起因して端子間

電圧が変化することを回避して、正確な電圧を印加することが可能となる。

【0082】

もちろん、コンデンサーC1 〜C3 間で電荷の再分配を行った後に、電源Vref とコン

デンサーC1 〜C3 とを接続するスイッチS4 をONにすることで、電源Vref からコン

デンサーC1 〜C3 に電荷を補充することとしても良い。あるいは、図9および図10を

用いて前述した第1実施例の変形例と同様に、印加電圧を電圧Vref に切り換える際には

、初めから各コンデンサーC1 〜C3 を並列に接続して、電荷の再分配を行うこととして

も良い。更に、電荷の再分配を開始した後、再分配がある程度まで進んだら、電源Vref

も各コンデンサーC1 〜C3 に対して並列に接続することで、電源Vref から各コンデン

サーC1 〜C3 に電荷を補充することとしても良い。

【0083】

また、以上の説明では、コンデンサーC1 〜C3 間の電荷の再分配は、ピエゾ素子10

4の印加電圧が電圧Vref の時に行うものとした。しかし、実際には、ピエゾ素子104

に対して1つのコンデンサー(たとえば、コンデンサーC1 )のみが接続されており、他

のコンデンサー(たとえば、コンデンサーC2 ,C3 )が切り離されている状態であれば

、それら3つのコンデンサーC1 〜C3 を並列に接続して電荷の再分配を行うことが可能

である。

【0084】

図14は、印加電圧が電圧Vref 以外のときに電荷の再分配を行う様子を例示した説明

図である。たとえば図14(a)に示すように、ピエゾ素子104に電圧Vboot+Vref

を印加している状態では、ピエゾ素子104に接続されているコンデンサーは、コンデン

サーC1 のみであり、他のコンデンサーC2 ,C3 はピエゾ素子104から切り離された

状態となっている。そこで、図14(b)に示すように、スイッチS1 〜S3 およびスイ

ッチSb1〜Sb3をONにすることで、コンデンサーC1 〜C3 を並列に接続する。こうす

れば、ピエゾ素子104に電圧Vboot+Vref を印加したまま、コンデンサーC1 からコ

ンデンサーC2 およびコンデンサーC3 に電荷が供給されて、電荷を再分配することが可

能となる。

【0085】

以上、各種実施例および変形例の駆動波形生成回路について説明したが、本発明は上記

に限られるものではなく、その要旨を逸脱しない範囲において種々の態様で実施すること

が可能である。例えば、駆動波形生成回路によって駆動される容量性負荷はピエゾ素子1

04であるものとして説明したが、容量成分を有する負荷であればピエゾ素子104に限

らず、どのような負荷であっても構わない。例えば、液晶パネルや有機ELなどの各種表

示装置を負荷として駆動する場合にも、本発明を好適に適用することが可能である。

【符号の説明】

【0086】

10…インクジェットプリンター、 20…キャリッジ、 24…噴射ヘッド、

26…インクカートリッジ、 30…駆動機構、 40…プラテンローラー、

50…プリンター制御回路、 100…噴射口、 102…インク室、

104…ピエゾ素子、 200…噴射ヘッド駆動回路、 202…制御回路、

204…駆動波形生成回路、 300…ゲートユニット、 302…ゲート素子、

304…駆動波形生成回路、 Vref…電源、 Vboot…補助電源、

C1 ,C2 ,C3 …コンデンサー、 B1 ,B2 …スイッチ、

E1 ,E2 ,E3 …スイッチ、 S1 ,S2 ,S3 ,S4 …スイッチ

【技術分野】

【0001】

本発明は、容量性の電気負荷を駆動する技術に関する。

【背景技術】

【0002】

電荷を蓄えた複数のコンデンサーを利用して、容量性負荷を効率よく駆動する技術が提

案されている(特許文献1)。この提案の技術では、各コンデンサーに異なる電圧で電荷

を蓄えておき、容量性負荷に接続するコンデンサーを次々と切り換えることによって負荷

を駆動する。

【0003】

例えば、負荷に印加する電圧値を上昇させる場合には、負荷に接続するコンデンサーを

、高い電圧で電荷が蓄えられた(端子間電圧の高い)コンデンサーに次々と切り換えてい

く。こうすればコンデンサーに蓄えられた電荷が容量性負荷に供給され、そして容量性負

荷に蓄えられた電荷が増加するに従って負荷の印加電圧が上昇していく。逆に、負荷の印

加電圧を低下させる場合には、負荷に接続するコンデンサーを端子間電圧の低いコンデン

サーに次々と切り換えていく。こうすれば、容量性負荷に蓄えられた電荷がコンデンサー

に回収されて、負荷に蓄えられた電荷が減少するに従って印加電圧が低下していく。

【0004】

このように、提案されている技術では、端子電圧の異なる複数のコンデンサーと、容量

性負荷との間で電荷の充放電を行うことにより、容量性負荷を効率よく駆動することが可

能となっている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−285441号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、提案されている技術では、個々のコンデンサーについてみれば、容量性負荷に

供給する電荷と容量性負荷から回収する電荷とが必ずしも釣り合うとは限らず、各コンデ

ンサーでの充放電バランスの崩れに起因した電力損失が発生してしまうという問題がある

。

【0007】

例えば、容量性負荷に供給する電荷よりも負荷から回収する電荷の方が多いコンデンサ

ーでは、蓄積した電荷が増加していき、これに伴ってコンデンサーの端子間電圧が増加す

る。端子間電圧が想定した電圧値と異なってしまっては、負荷に正確な電圧を印加するこ

とができなくなるので、過剰に蓄積した分の電荷を放出しなければならなくなり、その分

の電力損失が発生する。また逆に、容量性負荷に供給する電荷の方が負荷から回収する電

荷よりも多いコンデンサーでは、蓄積している電荷が減少していき、これに伴ってコンデ

ンサーの端子間電圧が減少してしまう。その結果、電源から電荷を補充しなければならな

くなって、その分の電力も損失となる。

【0008】

この発明は、従来の技術が有する上述した課題を解決するためになされたものであり、

コンデンサーなどの複数の電荷蓄積素子を用いて、容量性負荷を効率よく駆動することが

可能な技術の提供を目的とする。

【課題を解決するための手段】

【0009】

上述した課題の少なくとも一部を解決するために、本発明の容量性負荷駆動回路は次の

構成を採用した。すなわち、

容量性負荷を駆動する容量性負荷駆動回路であって、

電荷を蓄積する複数の電荷蓄積素子と、

前記電荷蓄積素子に電荷を供給する電源と、

前記複数の電荷蓄積素子と、前記電源と、前記容量性負荷との接続状態を切り換える接

続状態切換手段と

を備え、

前記接続状態切換手段は、

前記容量性負荷が前記電源および前記複数の電荷蓄積素子から切断された状態で、前

記電源と前記複数の電荷蓄積素子とが並列に接続される第1の接続状態と、

前記容量性負荷が前記電源および前記複数の電荷蓄積素子から切断された状態で、前

記複数の電荷蓄積素子のうちの1つの前記電荷蓄積素子、または直列に接続された少なく

とも2つの前記電荷蓄積素子が、前記容量性負荷に対して並列に接続される第2の接続状

態と、

前記電源が前記複数の電荷蓄積素子および前記容量性負荷から切断され、前記複数の

電荷蓄積素子のうちの1つの前記電荷蓄積素子が前記容量性負荷に対して並列に接続され

た状態で、該容量性負荷に接続された1つの該電荷蓄積素子に対して、他の前記電荷蓄積

素子が並列に接続される第3の接続状態と

に切り換え可能な手段であることを要旨とする。

【0010】

このような本発明の容量性負荷駆動回路においては、複数の電荷蓄積素子と電源とが並

列に接続された第1の接続状態とすることで、電荷蓄積素子に電荷を蓄えることができる

。続いて、複数の電荷蓄積素子の中から少なくとも1つの電荷蓄積素子を選択して、選択

した電荷蓄積素子が容量性負荷に対して並列に接続される第2の接続とすることで、容量

性負荷に対して電圧を印加することができる。このとき、選択した電荷蓄積素子が1つで

あれば、電荷蓄積素子1つ分の電圧が容量性負荷に印加されることになる。また、複数の

電荷蓄積素子を選択した場合には、それら電荷蓄積素子を直列に接続した状態で、容量性

負荷に並列に接続する。こうすれば複数の電荷蓄積素子を直列に接続して得られる電圧が

、容量性負荷に印加されることになる。従って、電荷蓄積素子と容量性負荷とを第2の接

続状態で接続する際に、複数の電荷蓄積素子の中から選択して負荷に接続する電荷蓄積素

子の個数によって、容量性負荷に印加する電圧を切り換えることができる。そして、選択

する電荷蓄積素子の個数を増やしていけば、容量性負荷に印加される電圧が上昇し、この

とき電荷蓄積素子から容量性負荷に向かって電荷が供給される。逆に、選択する電荷蓄積

素子の個数を減らしていけば、容量性負荷に印加される電圧が低下して、このとき容量性

負荷から放出される電荷が電荷蓄積素子によって回収される。このため、回収した電荷を

用いて再び負荷の印加電圧を上昇させることができるので、容量性負荷を効率よく駆動す

ることが可能である。更に、本発明の容量性負荷駆動回路においては、1つの電荷蓄積素

子を容量性負荷に接続した状態で、その電荷蓄積素子に他の電荷蓄積素子が並列に接続さ

れた第3の接続状態とすることができる。容量性負荷に対して電荷を供給する電荷蓄積素

子と、容量性負荷から電荷を回収する電荷蓄積素子とは、必ずしも一致するとは限らない

。このため複数の電荷蓄積素子の間で電荷の偏りが発生して、この電荷の偏りに起因した

電力損失を引き起こす可能性がある。そこで本発明では、第3の接続状態とすることによ

って、互いに並列に接続された電荷蓄積素子間で電荷の偏りが是正されるように、電荷を

再配分することができるので、電荷の偏りに起因した電力損失の発生を回避することが可

能となる。

【0011】

尚、第3の接続状態とする場合、電荷を再分配するという観点からは、容量性負荷に接

続された1つの電荷蓄積素子に対して、他の全ての電荷蓄積素子を並列に接続することが

多くの場合は望ましい。しかし、必ずしも、他の全ての電荷蓄積素子を並列に接続しなけ

ればならないわけではない。たとえば、印加する電圧波形の関係で、極端に電荷が不足す

る電荷蓄積素子が存在する場合などには、その電荷蓄積素子については電源から電荷を補

充することとして、他の電荷蓄積素子間で電荷の再分配を行うようにしても構わない。

【0012】

また、上述した本発明の容量性負荷駆動回路においては、複数の電荷蓄積素子が並列に

接続されており、尚且つ、電源および容量性負荷から切断された第4の接続状態に切り換

え可能としてもよい。

【0013】

複数の電荷蓄積素子を、このような第4の接続状態とすることができれば、容量性負荷

に電圧を印加していない状態で、複数の電荷蓄積素子の間で電荷を再分配することが可能

となるので好ましい。

【0014】

また、上述した本発明の容量性負荷駆動回路においては、次のようにしても良い。先ず

、電源、複数の電荷蓄積素子、および容量性負荷が並列に接続される第5の接続状態に切

り換え可能とする。そして、電源、複数の電荷蓄積素子、および容量性負荷の接続状態を

第3の接続状態に切り換えた後に、第5の接続状態に切り換えることとしてもよい。

【0015】

前述したように第3の接続状態では電荷蓄積素子の間で電荷の再分配が行われるから、

多くの電荷が蓄積されている電荷蓄積素子から、電荷の少ない電荷蓄積素子に向かって電

荷が供給される。その状態で、複数の電荷蓄積素子に対して電源を接続することで、第5

の接続状態に切り換えてやれば、電源から各電荷蓄積素子に補充する電荷を最小限にする

ことができるので、容量性負荷をより一層効率よく駆動することが可能となる。

【図面の簡単な説明】

【0016】

【図1】本実施例の容量性負荷駆動回路を搭載したインクジェットプリンターを例示した説明図である。

【図2】プリンター制御回路の制御の下で、噴射ヘッド駆動回路が噴射ヘッドを駆動する様子を示した説明図である。

【図3】第1実施例の噴射ヘッド駆動回路の詳細な構成を示した説明図である。

【図4】各スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続状態を切り換えてコンデンサーC1 〜C3 を充電する様子を示した説明図である。

【図5】各スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続状態を切り換えることでピエゾ素子に印加される電圧が切り換わる様子を示した説明図である。

【図6】ピエゾ素子に印加する電圧を切り換えた時に、コンデンサーC1 〜C3 とピエゾ素子との間で電荷の授受が行われる様子を示した説明図である。

【図7】第1実施例の駆動波形生成回路で各コンデンサーC1 〜C3 の電荷を再分配する様子を示した説明図である。

【図8】第1実施例の駆動波形生成回路がピエゾ素子に電圧を印加しながら、コンデンサーC1 〜C3 間での電荷の再分配を行う様子を示した説明図である。

【図9】第1実施例の変形例の駆動波形生成回路においてコンデンサーC1 〜C3 で電荷の再分配を行った後に、電荷を補充する様子を示した説明図である。

【図10】第1実施例の変形例の駆動波形生成回路がピエゾ素子に電圧を印加する様子を示した説明図である。

【図11】第2実施例の駆動波形生成回路の一例を示した回路図である。

【図12】第2実施例の駆動波形生成回路がピエゾ素子の印加電圧を切り換える様子を示した説明図である。

【図13】第2実施例の駆動波形生成回路でコンデンサーC1 〜C3 間の電荷を再分配する様子を示す説明図である。

【図14】印加電圧が電圧Vref 以外のときに電荷の再分配を行う様子を例示した説明図である。

【発明を実施するための形態】

【0017】

以下では、上述した本願発明の内容を明確にするために、次のような順序に従って実施

例を説明する。

A.装置構成:

B.第1実施例:

B−1.回路構成:

B−2.容量性負荷の駆動原理:

B−3.変形例:

C.第2実施例:

C−1.回路構成:

C−2.容量性負荷の駆動原理:

【0018】

A.装置構成 :

図1は、本実施例の容量性負荷駆動回路としての噴射ヘッド駆動回路を搭載したインク

ジェットプリンター10を例示した説明図である。図示したインクジェットプリンター1

0は、主走査方向に往復動しながら印刷媒体2上にインクドットを形成するキャリッジ2

0と、キャリッジ20を往復動させる駆動機構30と、印刷媒体2の紙送りを行うための

プラテンローラー40などから構成されている。キャリッジ20には、インクを収容した

インクカートリッジ26や、インクカートリッジ26が装着されるキャリッジケース22

、キャリッジケース22の底面側(印刷媒体2に向いた側)に搭載されてインクを噴射す

る噴射ヘッド24などが設けられており、インクカートリッジ26内のインクを噴射ヘッ

ド24に導いて、噴射ヘッド24から印刷媒体2に向かって正確な分量のインクを噴射す

ることが可能となっている。

【0019】

キャリッジ20を往復動させる駆動機構30は、プーリーによって張設されたタイミン

グベルト32や、プーリーを介してタイミングベルト32を駆動するステップモータ34

などから構成されている。タイミングベルト32の一箇所はキャリッジケース22に固定

されており、タイミングベルト32を駆動することでキャリッジケース22を往復動させ

ることができる。また、プラテンローラー40は、図示しない駆動モータやギア機構とと

もに、印刷媒体2の紙送りを行う紙送り機構を構成しており、印刷媒体2を副走査方向に

所定量ずつ紙送りすることが可能となっている。

【0020】

また、インクジェットプリンター10には、全体の動作を制御するプリンター制御回路

50や、噴射ヘッド24を駆動するための噴射ヘッド駆動回路200も搭載されている。

噴射ヘッド駆動回路200や、駆動機構30、紙送り機構などは、プリンター制御回路5

0の制御の下で、印刷媒体2を紙送りしながら噴射ヘッド24を駆動してインクを噴射す

ることによって、印刷媒体2上に画像を印刷していく。

【0021】

図2は、プリンター制御回路50の制御の下で、噴射ヘッド駆動回路200が噴射ヘッ

ド24を駆動する様子を示した説明図である。先ず始めに、噴射ヘッド24の内部構造に

ついて簡単に説明する。図示されている様に、噴射ヘッド24の底面(印刷媒体2に向い

ている面)には、インク滴を噴射する複数の噴射口100が設けられている。各噴射口1

00はそれぞれインク室102に接続されており、インク室102には、インクカートリ

ッジ26から供給されたインクが満たされている。各インク室102の上にはピエゾ素子

104が設けられており、ピエゾ素子104に電圧を印加すると、ピエゾ素子が変形して

インク室102を加圧することによって、噴射口100からインク滴を噴射することが可

能となっている。また、ピエゾ素子104は、印加する電圧値に応じて変形量が変わるの

で、ピエゾ素子104に適切な電圧波形を印加して、インク室102の変形量やタイミン

グを制御してやれば、適切な大きさのインク滴を、適切なタイミングで噴射することが可

能となる。

【0022】

ピエゾ素子104に印加する電圧波形(駆動波形)は、プリンター制御回路50の制御

の下で噴射ヘッド駆動回路200によって生成される。また、生成された駆動波形は、ゲ

ートユニット300を介してピエゾ素子104に供給される。ゲートユニット300は、

複数のゲート素子302が並列に接続された回路ユニットであり、各ゲート素子302は

、プリンター制御回路50からの制御の下で、個別に導通状態または切断状態とすること

が可能である。従って、噴射ヘッド駆動回路200から駆動波形を出力すると、プリンタ

ー制御回路50によって予め導通状態に設定されたゲート素子302だけを通過して、対

応するピエゾ素子104に印加され、その噴射口からインク滴が噴射されるようになって

いる。また、図2に示されるように、本実施例の噴射ヘッド駆動回路200は、制御回路

202や、駆動波形生成回路204などから構成されている。そして、プリンター制御回

路50が噴射ヘッド駆動回路200に対して駆動波形の出力を命令すると、その命令に応

じて制御回路202が駆動波形生成回路204の動作を制御することにより、噴射ヘッド

駆動回路200から適切な駆動波形が出力されるようになっている。

【0023】

ここで、周知のようにピエゾ素子はいわゆる容量性の負荷であり、電圧を印加すると、

印加した電圧に応じた電荷が、ピエゾ素子の内部に蓄えられる。そして、蓄えられる電荷

量は印加する電圧が高くなるほど増えていき、逆に、印加する電圧が低くなると、内部に

蓄えられていた電荷が放出される。そこで、印加電圧が低くなる際にピエゾ素子から放出

される電荷を複数のコンデンサー(電荷蓄積素子)などに蓄えておき、次に印加電圧が高

くなる際には、コンデンサーに蓄えておいた電荷をピエゾ素子に供給するようにしてやれ

ば、ピエゾ素子を少ない電力で効率よく駆動することが可能である。もっとも、詳細には

後述するが、ピエゾ素子から放出される電荷をコンデンサーで蓄える際に、各コンデンサ

ーに蓄える電荷量に偏りが生じると、そのことが原因となって電力効率の低下を引き起こ

す。そこで、本実施例の駆動波形生成回路204では、ピエゾ素子から放出される電荷を

次のような方法で回収しながら、駆動波形を生成することにより、電力効率の低下を引き

起こすことなくピエゾ素子を駆動することが可能となっている。

【0024】

B.第1実施例 :

B−1.回路構成 :

図3は、第1実施例の噴射ヘッド駆動回路200の詳細な構成を示した説明図である。

図示されているように、噴射ヘッド駆動回路200は、制御回路202と、駆動波形生成

回路204とから構成されており、更に、駆動波形生成回路204は、複数のコンデンサ

ーと、電源Vref と、複数のスイッチなどから構成されている。そして、複数のスイッチ

の接続状態は、制御回路202によって制御されている。尚、図3に示した例では、図が

煩雑となることを回避するために、コンデンサーC1 〜C3 の3つのコンデンサーを用い

て構成されているものとしているが、より多くのコンデンサーを用いて構成しても良い。

また、ここではインクジェットプリンター10の噴射ヘッド24を駆動するものとしてい

るから、駆動する負荷はピエゾ素子104であるものとしているが、実際には、容量成分

を有する電気負荷(容量性負荷)でありさえすれば、ピエゾ素子104に限らずどのよう

な電気負荷(例えば液晶などの各種表示装置など)であっても構わない。

【0025】

これら3つのコンデンサーC1 〜C3 の一方の端子は、それぞれグランドに接地されて

いる。このうちのコンデンサーC1 については、端子とグランドとの間にスイッチE1 が

設けられ、コンデンサーC2 については、端子とグランドとの間にスイッチE2 が設けら

れている。このため、スイッチE1 ,E2 をOFF(切断状態)とすることにより、コン

デンサーC1 ,C2 をグランドから浮かせることが可能となっている。これに対して、コ

ンデンサーC3 については、一方の端子が直接グランドに接地されている。

【0026】

また、コンデンサーC1 〜C3 の他方の端子は、それぞれスイッチS1 〜S3 を介して

電源Vref に接続されている。尚、電源Vref と各スイッチS1 〜S3 との間にもスイッ

チS4 が設けられており、このためスイッチS4 をOFFとすることで、スイッチS1 〜

S3 の設定状態に拘わらず、電源Vref と各コンデンサーC1 〜C3 とを切り離すことが

可能となっている。

【0027】

更に、コンデンサーC1 の接地側の端子と、コンデンサーC2 の電源側の端子とは、ス

イッチB1 を介して接続されている。このため、コンデンサーC1 の接地側に設けられた

スイッチE1 をOFFにしてコンデンサーC1 をグランドから切り離し、代わりにスイッ

チB1 をON(接続状態)にすることで、コンデンサーC2 の上にコンデンサーC1 を積

み上げるようにして、2つのコンデンサーを直列に接続することが可能となる。また、コ

ンデンサーC2 とコンデンサーC3 との間にも、同様なスイッチB2 が設けられている。

従って、コンデンサーC2 の接地側に設けられたスイッチE2 をOFFにして、代わりに

スイッチB2 をONにすることで、コンデンサーC3 の上にコンデンサーC2 を積み上げ

るようにして、2つのコンデンサーを直列に接続することが可能となる。

【0028】

このように、第1実施例の駆動波形生成回路204は、電源Vref と、複数のコンデン

サーCn と、各コンデンサーの一方の端子をグランドに接地するためのスイッチEn と、

各コンデンサーの他方の端子を電源Vref に接続するためのスイッチSn と、コンデンサ

ーCn の接地側の端子をコンデンサーCn+1 の電源側の端子に接続するためのスイッチB

n などから構成されている。そして、これらのスイッチEn ,Sn ,Bn の接続状態を切

り換えることで、ピエゾ素子104などの容量性負荷を、極めて少ない電力で効率よく駆

動することが可能となっている。

【0029】

B−2.容量性負荷の駆動原理 :

第1実施例の駆動波形生成回路204を用いて負荷を駆動するためには、コンデンサー

C1 〜C3 を予め充電しておく必要がある。そこで、各スイッチE1 ,E2 ,S1 〜S4

,B1 ,B2 の接続状態を切り換えて、コンデンサーC1 〜C3 と電源Vref とが並列に

接続された状態とすることで、コンデンサーC1 〜C3 を充電する。

【0030】

図4は、各スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続状態を切り換えて、コ

ンデンサーC1 〜C3 を充電する様子を示した説明図である。コンデンサーC1 〜C3 を

充電するためには、図示されているように、コンデンサーC1 の接地側の端子とコンデン

サーC2 の電源側の端子とを接続するためのスイッチB1 、およびコンデンサーC2 の接

地側の端子とコンデンサーC3 の電源側の端子とを接続するためのスイッチB2 を除いて

、他の全てのスイッチE1 ,E2 ,S1 〜S4 をON(接続状態)とする。こうすると、

コンデンサーC1 〜C3 の一方の端子はグランドに接地され、他方の端子は電源Vref に

接続される。その結果、各コンデンサーC1 〜C3 が電源Vref に対して並列に接続され

た状態となり、各コンデンサーC1 〜C3 の端子間の電圧が電源Vref の電圧Vref にな

るまで電荷が蓄えられる。尚、理解の便宜を図るため、図4では、スイッチがONにされ

て電流が流れる状態となっている配線を太い実線で表し、スイッチがOFFにされて電流

が流れない状態となっている配線を細い破線で表している。

【0031】

こうして各コンデンサーC1 〜C3 の端子間電圧が電源Vref の出力電圧Vref になる

まで充電したら、各スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続状態を切り換え

てピエゾ素子104を駆動することが可能となる。

【0032】

図5は、各スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続状態を切り換えること

で、ピエゾ素子104に印加される電圧が切り換わる様子を示した説明図である。例えば

、図5(a)に示すように、コンデンサーC1 の接地側のスイッチE1 のみをONにして

、他のスイッチを全てOFFにすると、コンデンサーC1 のみがピエゾ素子104に接続

される。上述したようにコンデンサーC1 の端子間電圧は電圧Vref になっているから、

ピエゾ素子104には電圧Vref が印加されることになる。尚、図5においても、スイッ

チがONにされて電流が流れる状態となっている配線を太い実線で表し、スイッチがOF

Fにされて電流が流れない状態となっている配線を細い破線で表している。

【0033】

次に、図5(b)に示すように、コンデンサーC1 の接地側のスイッチE1 をOFFに

して、代わりにコンデンサーC2 の接地側のスイッチE2 をONにするとともに、コンデ

ンサーC1 の接地側の端子とコンデンサーC2 の電源側の端子とを接続するスイッチB1

をONにする。すると、コンデンサーC1 とコンデンサーC2 とが直列に接続され、そし

てその状態で、これら2つのコンデンサーC1 ,C2 が、ピエゾ素子104に対して並列

に接続される。その結果、ピエゾ素子104には、2つのコンデンサーC1 ,C2 が直列

に接続された電圧に相当する2Vref の電圧値が印加されることになる。

【0034】

更に、図5(c)に示すように、コンデンサーC2 の接地側のスイッチE2 をOFFに

するとともに、コンデンサーC2 の接地側の端子とコンデンサーC3 の電源側の端子とを

接続するスイッチB2 をONにする。すると、既に直列に接続されている2つのコンデン

サーC1 ,C2 に加えて、新たにコンデンサーC3 が直列に接続されて、それら3つのコ

ンデンサーC1 ,C2 ,C3 が、ピエゾ素子104に対して並列に接続される。その結果

、ピエゾ素子104には、3つのコンデンサーC1 ,C2 ,C3 が直列に接続された電圧

に相当する3Vref の電圧値が印加される。

【0035】

以上の説明から明らかなように、スイッチE1 ,E2 ,S1 〜S4 ,B1 ,B2 の接続

状態を、図5(a)に示した状態から、図5(b)に示した状態、図5(c)に示した状

態へと切り換えていけば、ピエゾ素子104に印加する電圧を、Vref 、2Vref 、3V

ref へと増加させることができる。また逆に、図5(c)に示した状態から、図5(b)

に示した状態、図5(a)に示した状態へと切り換えていけば、印加する電圧を、3Vre

f 、2Vref 、Vref へと減少させることも可能となる。また、ピエゾ素子104のよう

な容量性負荷では、印加する電圧を増加させるに従って、負荷の内部に蓄えられる電荷が

多くなり、印加する電圧を減少させるに従って、内部に蓄えられていた電荷が放出される

。図5を用いて前述したように、第1実施例の駆動波形生成回路204では、コンデンサ

ーC1 ,C2 ,C3 を用いてピエゾ素子104に電圧を印加しているから、印加する電圧

の減少時に放出される電荷を回収して蓄えておき、印加する電圧の増加時には蓄えておい

た電荷をピエゾ素子104に供給することで、電力消費を抑えてピエゾ素子104を駆動

することが可能となる。

【0036】

もっとも、上述したように駆動波形生成回路204では、ピエゾ素子104に接続され

るコンデンサーC1 〜C3 を切り換えているから、印加する電圧を増加させるためにピエ

ゾ素子104に対して電荷を供給するコンデンサーと、電圧を減少させるためにピエゾ素

子104から電荷を回収するコンデンサーとが一致するとは限らない。その結果、個々の

コンデンサーに着目すると、ピエゾ素子104に供給する電荷の方が、ピエゾ素子104

から回収する電荷よりも多く、電荷が次第に減少していくコンデンサーや、逆に、ピエゾ

素子104に供給する電荷より回収する電荷の方が多く、電荷が次第に増加していくコン

デンサーなどが生じ得る。実際に、駆動波形生成回路204を用いてピエゾ素子104を

駆動していると、コンデンサーC1 〜C3 間で電荷の偏りが発生することがある。

【0037】

図6は、ピエゾ素子104を駆動する際に、コンデンサーC1 〜C3 で電荷の偏りが発

生し得る理由を模式化して示した説明図である。図6(a)には、ピエゾ素子104に印

加される電圧(印加電圧)が切り換わる様子が示されており、図6(b)には、その時の

各コンデンサーC1 〜C3 の接続状態が示されている。先ず始めは、ピエゾ素子104に

電圧Vref が印加されているものとする。この時の各コンデンサーC1 〜C3 の接続状態

は、図5(a)に示したように、コンデンサーC1 のみがピエゾ素子104に接続されて

おり、コンデンサーC2 ,C3 はピエゾ素子104から切断された状態となっている。図

6(b)で「OFF」と表示されているのは、コンデンサーがピエゾ素子104から切断

された状態であることを意味している。例えば図6(b)の左端については、コンデンサ

ーC1 のみがピエゾ素子104に接続され、コンデンサーC2 ,C3 は切断された状態で

あることを示している。その結果、図6(a)に示したように、ピエゾ素子104にはコ

ンデンサーC1 の端子電圧(電圧Vref )が印加されることになる。

【0038】

次に、図6(a)に示すようにピエゾ素子104の印加電圧を、電圧Vref から電圧2

Vref に切り換える。各スイッチE1 ,E2 ,S1 〜S4 、B1 ,B2 の接続状態に関し

て言えば、図5(a)に示した接続状態から、図5(b)に示した接続状態に切り換えれ

ばよい。すると、前述したように2つのコンデンサーC1 ,C2 が直列に接続されて、合

計した電圧(すなわち電圧2Vref )がピエゾ素子104に印加される。ピエゾ素子10

4の端子間電圧は電圧Vref であり、ここに2つのコンデンサーC1 ,C2 の合計電圧2

Vref が印加されるから、コンデンサーC1 ,C2 からピエゾ素子104へと電荷が供給

され、ピエゾ素子104内に電荷が溜まるに従ってピエゾ素子104の端子間電圧が増加

していき、最終的には、2つのコンデンサーC1 ,C2 の合計電圧と等しくなる。

【0039】

図6(a)には、ピエゾ素子104の印加電圧を電圧Vref から電圧2Vref に増加さ

せる際に、以上のようにしてコンデンサーからピエゾ素子104に電荷が供給され、その

結果として電圧2Vref が印加される旨が、白抜きの矢印によって表されている。また、

図6(b)には、ピエゾ素子104の印加電圧を電圧Vref から電圧2Vref に増加させ

るに伴って、コンデンサーC1のみが接続された状態から、2つのコンデンサーC1 ,C

2 が接続された状態に切り換わる様子が示されている。そして、印加電圧を電圧Vref か

ら電圧2Vref に増加させる途中は2つのコンデンサーC1 ,C2 が接続されているから

、ピエゾ素子104に供給される電荷は2つのコンデンサーC1 ,C2 から供給される。

図6(b)中に示した白抜きの矢印は、コンデンサーからピエゾ素子104に電荷が供給

されることを表している。

【0040】

ピエゾ素子104の印加電圧を、電圧2Vref から電圧3Vref に切り換える場合も同

様に、コンデンサーからピエゾ素子104に電荷を供給することによって、ピエゾ素子1

04の端子間電圧を電圧3Vref まで増加させる。すなわち、スイッチE1 ,E2 ,S1

〜S4 、B1 ,B2 の接続状態を、図5(b)に示した状態から図5(c)に示した状態

に切り換えることで、2つのコンデンサーC1 ,C2 が直列に接続された状態から、3つ

のコンデンサーC1 〜C3 が直列に接続された状態に切り換える。すると、3つのコンデ

ンサーC1 〜C3 の合計電圧は電圧3Vref となって、ピエゾ素子104の端子間電圧2

Vref よりも高くなるので、3つコンデンサーC1 〜C3 からピエゾ素子104へと電荷

が供給されていく。図6(b)には、ピエゾ素子104の印加電圧を電圧2Vref から電

圧3Vref に増加させるに伴って、2つのコンデンサーC1 ,C2 が接続された状態から

、3つのコンデンサーC1 〜C3 が接続された状態に切り換わり、この時、コンデンサー

C1 〜C3 から電荷がピエゾ素子104に供給される様子が示されている。

【0041】

次に、ピエゾ素子104の印加電圧を電圧3Vref から電圧2Vref に減少させる場合

は、スイッチE1 ,E2 ,S1 〜S4 、B1 ,B2 の接続状態を、図5(c)に示した状

態から図5(b)に示した状態に切り換える。すると、3つのコンデンサーC1 〜C3 が

直列に接続された状態から、2つのコンデンサーC1 ,C2 が直列に接続された状態に切

り換わり、2つのコンデンサーC1 ,C2 の合計電圧2Vref よりも、ピエゾ素子104

の端子間電圧3Vref の方が高くなる。このためピエゾ素子104から2つのコンデンサ

ーC1 ,C2 に向かって電荷が放出され、ピエゾ素子104内の電荷が少なくなるに従っ

てピエゾ素子104の端子間電圧が減少していき、最終的には、2つのコンデンサーC1

,C2 の合計電圧と等しくなる。図6(a)には、ピエゾ素子104からコンデンサーに

電荷が放出されて、ピエゾ素子104の印加電圧が減少する様子が、斜線を付した矢印に

よって表されている。

【0042】

また、図6(b)には、ピエゾ素子104の印加電圧を電圧3Vref から電圧2Vref

に減少させるに伴って、3つのコンデンサーC1 〜C3 が接続された状態から、2つのコ

ンデンサーC1 ,C2 が接続された状態に切り換わる様子が示されている。そして、印加

電圧を電圧3Vref から電圧2Vref に減少させる途中は2つのコンデンサーC1 ,C2

が接続されているから、ピエゾ素子104から放出される電荷は2つのコンデンサーC1

,C2 に蓄えられることになる。図6(b)中に斜線を付して示した矢印は、コンデンサ

ーがピエゾ素子104から電荷を回収することを表している。

【0043】

ピエゾ素子104の印加電圧を、電圧2Vref から電圧Vref に減少させる場合も同様

である。すなわち、スイッチE1 ,E2 ,S1 〜S4 、B1 ,B2 の接続状態を、図5(

b)に示した状態から図5(a)に示した状態に切り換えると、2つのコンデンサーC1

,C2 が直列に接続されてピエゾ素子104に接続されている状態から、コンデンサーC

1 のみがピエゾ素子104に接続された状態に切り換わる。その結果、ピエゾ素子104

からコンデンサーC1 へと電荷が放出され、それに伴ってピエゾ素子104の端子間電圧

が減少していき、最終的には、ピエゾ素子104に印加電圧Vref が印加された状態とな

る。また、この時、ピエゾ素子104に接続されているコンデンサーはコンデンサーC1

のみであるから、ピエゾ素子104が放出する電荷はコンデンサーC1 に蓄えられること

になる。

【0044】

以上に説明したように、3つのコンデンサーC1 〜C3 を充電した後、各スイッチE1

,E2 ,S1 〜S4 、B1 ,B2 の接続状態を切り換えることで、ピエゾ素子104の印

加電圧を切り換えていくことが可能である。また、ここでは図示が煩雑となることを避け

るために、コンデンサーの個数は3つとしているが、実際にはコンデンサーを多くすると

ともに、電源Vref の電圧値を小さくすれば、印加電圧をより細かい電圧で切り換えるこ

とができる。その結果、任意の波形の電圧を生成してピエゾ素子104に印加することも

可能である。

【0045】

しかし、印加電圧を切り換えるために、各コンデンサーとピエゾ素子104との間でや

り取りする過程で、コンデンサー間に電荷の偏りが生じ得る。この点について、図6(b

)を用いて説明する。例えば、コンデンサーC2 については、印加電圧が電圧Vref から

電圧2Vref に増加する際と、電圧2Vref から電圧3Vref に増加する際とで電荷を放

出し、そして、印加電圧が電圧3Vref から電圧2Vref に減少する際にだけ電荷を受け

取っている。従って、コンデンサーC2 については、ピエゾ素子104に供給する電荷が

、ピエゾ素子104から回収する電荷を上回り、電荷が次第に減少するものと考えられる

。また、コンデンサーC3 については、ピエゾ素子104に電荷を供給するだけなので電

荷が減少することになる。

【0046】

各コンデンサー間で、このような電荷量の偏りが発生する理由は、次のように考えれば

直感的に了解できる。先ず、図5を用いて前述したように、印加電圧Vref はコンデンサ

ーC1 のみによって生成され、印加電圧2Vref は2つのコンデンサーC1 ,C2 を直列

接続することによって生成され、印加電圧3Vref は3つのコンデンサーC1 〜C3 を直

列接続することによって生成される。図6(c)には、これら3種類の印加電圧(Vref

、2Vref 、3Vref )と、それら印加電圧を生成するために用いられるコンデンサーと

が示されている。

【0047】

また、ピエゾ素子104の印加電圧を電圧Vref から電圧2Vref に増加させるために

は、2つのコンデンサーC1 ,C2 を直列接続して、コンデンサーC1 ,C2 からピエゾ

素子104に電荷を供給する。図6(c)には、直列接続された2つのコンデンサーC1

,C2 から電荷が供給されることで、ピエゾ素子104の印加電圧が徐々に増加する様子

が概念的に示されている。更に、ピエゾ素子104の印加電圧を電圧2Vref から電圧3

Vref に増加させる際には、3つのコンデンサーC1 〜C3 を直列接続してコンデンサー

C1 〜C3 からピエゾ素子104に電荷を供給する。図6(c)には、直列接続された3

つのコンデンサーC1 〜C3 から電荷が供給されることで、ピエゾ素子104の印加電圧

が2Vref から3Vref に徐々に増加する様子が概念的に示されている。

【0048】

このようにピエゾ素子104の印加電圧を増加させる際には、コンデンサーからピエゾ

素子104に電荷が供給され、その電荷は、その印加電圧を生成するために直列接続され

た各コンデンサーによって負担される。これに対してピエゾ素子104の印加電圧を減少

させる際には、ピエゾ素子104からコンデンサーに電荷が放出される。そして、放出さ

れた電荷は、その時に接続されているコンデンサーに蓄えられる。

【0049】

例えば、ピエゾ素子104の印加電圧を電圧3Vref から電圧2Vref に減少させる際

には、ピエゾ素子104から電荷量Qの電荷が放出され、この電荷は、電圧2Vref を生

成するための直列接続されている2つのコンデンサーC1 、C2 に蓄えられる。すなわち

、印加電圧を電圧2Vref から電圧3Vref に増加させる際には、3つのコンデンサーC

1 〜C3 から電荷を供給したにも拘わらず、印加電圧が電圧3Vref から電圧2Vref に

減少する際には、2つのコンデンサーC1 ,C2 によって電荷を回収することになる。図

6(c)には、ピエゾ素子104から電荷が放出されることで、印加電圧が電圧3Vref

から電圧2Vref に徐々に減少する様子が概念的に示されている。このように、印加電圧

を増加するために用いられるコンデンサー(ピエゾ素子104に電荷を供給するコンデン

サー)と、印加電圧を減少させるために用いられるコンデンサー(ピエゾ素子104から

電荷を回収するコンデンサー)との間に不一致が発生すると、その結果として、各コンデ

ンサーの間で電荷量の偏りが生ずることがある。同様にして、印加電圧を電圧Vref から

電圧2Vref に増加させる際には、2つのコンデンサーC1 ,C2 から電荷を供給するに

も拘わらず、印加電圧が電圧2Vref から電圧Vref に減少する際には、コンデンサーC

1 のみによって電荷を回収する。このため、印加電圧を電圧Vref から電圧2Vref に増

加させ、再び電圧Vref に減少させる際に、コンデンサーの間で電荷量の偏りが発生する

ことが起こり得る。また、図6に示した例では、コンデンサーC2 ,C3 の電荷が減少し

得るだけであるが、印加しようとする電圧波形が異なれば、他のコンデンサーで電荷が減

少したり、あるいは電荷が増加するコンデンサーが発生したりすることも起こり得る。

【0050】

もちろん、ピエゾ素子104を駆動するために用いられるコンデンサーC1 〜C3 の静

電容量は、ピエゾ素子104の静電容量に較べて十分に大きいので、ピエゾ素子104を

少しの間、駆動する程度では、コンデンサーC1 〜C3 の端子電圧が大きく変化すること

はない。しかし、長い間に亘ってピエゾ素子104を駆動していると、大きな電荷の偏り

が発生して、コンデンサーの端子間電圧が変化してしまう場合が生じ得る。そして、コン

デンサーの端子間電圧が大きく変化すると、適切な電圧波形を印加することができなくな

ってしまう。こうしたことを回避するためには、端子間電圧が増加したコンデンサーにつ

いては、過剰に蓄えられた電荷をグランドに放出して、コンデンサーの端子間電圧を初期

の電圧Vref まで下げなければならない。逆に、端子間電圧が減少したコンデンサーにつ

いては、不足した電荷を電源Vref から補充して、端子間電圧を初期の電圧Vref まで上

げなければならない。そして、グランドに放出した分の電荷は電力の損失となり、また、

電源Vref から補充した分の電荷は、新たな電力の供給となるため、結果として、ピエゾ

素子104を駆動する電力効率の低下を引き起こす。

【0051】

そこで第1実施例の駆動波形生成回路204では、コンデンサー間での電荷の偏り(端

子間電圧の偏り)に起因して生じるこのような電力損失の発生を回避するために、各コン

デンサーC1 〜C3 の間で、電荷の再分配を行う。

【0052】

図7は、第1実施例の駆動波形生成回路204で、各コンデンサーC1 〜C3 の電荷を

再分配する様子を示した説明図である。ピエゾ素子104を印加電圧Vref で駆動してい

る時は、前述したようにコンデンサーC1 のみをピエゾ素子104に接続しておくだけで

も、電圧Vref を印加することができる。図7(a)には、コンデンサーC1 のみがピエ

ゾ素子104に接続されている様子が示されている。図7(a)に示されているように、

コンデンサーC1 のみをピエゾ素子104に接続した状態では、他のコンデンサーC2 ,

C3 はいわば遊んだ状態となっている。そこで第1実施例の駆動波形生成回路204では

、これらのコンデンサーC2 ,C3 を、ピエゾ素子104に接続されたコンデンサーC1

に並列に接続する。すなわち、図7(b)に示したように、スイッチB1 ,B2 およびス

イッチS4 はOFFにしたまま、スイッチS1 〜S3 およびスイッチE2 をONにする。

【0053】

前述したように、コンデンサーC1 〜C3 は何れも電源Vref によって端子間電圧Vre

f に充電されている。従って、ピエゾ素子104にコンデンサーC1 を接続して電圧Vre

f を印加している処に、更にコンデンサーC1 に対してコンデンサーC2 ,C3 を並列に

接続しても、ピエゾ素子104に印加している電圧Vref にはほとんど影響が現れること

はない。そして、コンデンサーC1 〜C3 は互いに並列に接続されているから、端子間電

圧の高いコンデンサーから端子間電圧の低いコンデンサーに向かって電荷が供給されて、

コンデンサーC1 〜C3 の間で電荷の再分配が行われる。その結果、コンデンサー間での

電荷の偏り(端子間電圧の偏り)に起因した電力損失の発生を回避することが可能となる

。

【0054】

尚、以上では、ピエゾ素子104にコンデンサーC1 を接続して電圧Vref を印加した

まま、更にコンデンサーC2 ,C3 を接続するものとして説明した。コンデンサーC1 〜

C3 の端子間電圧は何れも電圧Vref であるから、コンデンサーC1 を用いて電圧Vref

を印加中でも、印加電圧にはほとんど影響を与えることなく、コンデンサーC2 ,C3 を

接続して電荷を再分配することが可能である。しかし、ピエゾ素子104に電圧を印加し

ない状態が発生するのであれば、その間に、図7(c)に示すように、コンデンサーC1

〜C3 を互いに並列に接続することで、電荷を再分配しても構わない。

【0055】

図8は、第1実施例の駆動波形生成回路204がピエゾ素子104に電圧を印加しなが

ら、コンデンサーC1 〜C3 間での電荷の再分配を行う様子を示した説明図である。図8

では、一例として、山型の電圧波形を生成した後に、コンデンサーC1 では電荷が増加し

、コンデンサーC2 ,C3 では電荷が減少するものとする。図8(a)には、各スイッチ

B1 ,B2 ,E1 ,E2 ,S1 〜S4 の接続状態が時間とともに切り換わる様子が示され

ており、図8(b)には、その結果として生成される電圧波形が示されており、そして図

8(c)には、電圧波形を生成した後に、各コンデンサーC1 〜C3 の電荷量が増減する

様子が示されている。

【0056】

第1実施例の駆動波形生成回路204が、ピエゾ素子104の印加電圧を電圧Vref か

ら電圧3Vref に増加させた後、電圧Vref まで減少させる動作については、図6を用い

て前述した動作と全く同じである。また、ここでは、ピエゾ素子104の印加電圧を変化

させることにより、コンデンサーC1 では電荷が増加し、コンデンサーC2 ,C3 では電

荷が減少するものとする。

【0057】

そこで、第1実施例の駆動波形生成回路204では、ピエゾ素子104の印加電圧を電

圧Vref まで減少させた後、図8(b)に示したように、電圧Vref を印加したままで、

コンデンサーC1 〜C3 を並列に接続する。図8では、ピエゾ素子104に電圧Vref を

印加したまま、コンデンサーC1 〜C3 を並列に接続している期間を、斜線を付して表し

ている。こうすれば、図8(c)中に太い破線の矢印で示したように、コンデンサーC1

に過剰に溜まった電荷が、電荷の減少したコンデンサーC2 ,C3 に供給されて、コンデ

ンサーC1 〜C3 間で電荷の再分配が行われる。その結果、図8(b)に示したように、

ピエゾ素子104の印加電圧も、正しい電圧Vref に収束していく。

【0058】

以上に説明したように、第1実施例の駆動波形生成回路204では、複数のコンデンサ

ーC1 〜C3 を予め同じ電圧に充電しておき、それらコンデンサーC1 〜C3 の接続状態

を切り換えることで、ピエゾ素子104を駆動する。そして、ピエゾ素子104に印加す

る電圧が、コンデンサー1つ分の電圧になると、複数のコンデンサーC1 〜C3 を互いに

並列に接続することで、コンデンサーC1 〜C3 間での電荷の再分配を行う。こうするこ

とで、電荷の偏りに起因して端子間電圧が変化することを回避することができるので、正

確な電圧の駆動波形を生成することが可能となる。

【0059】

B−3.変形例 :

上述した第1実施例では、ピエゾ素子104にコンデンサーC1 のみを接続して、印加

電圧を電圧Vref 近くまで減少させた後、コンデンサーC1 およびピエゾ素子104に対

して、コンデンサーC2 ,C3 を並列に接続することで、コンデンサーC1 〜C3 間で電

荷の再分配を行うものとして説明した。これに対して、ピエゾ素子104の印加電圧を電

圧Vref に切り換える際には、初めからピエゾ素子104に対して、3つのコンデンサー

C1 〜C3 を並列に接続することとしても良い。こうすれば、上述した第1実施例と比較

して、コンデンサーC1 〜C3 間で電荷を再分配するための時間を十分に確保することが

可能となる。

【0060】

更に加えて、こうした変形例の駆動波形生成回路204では、コンデンサーC1 〜C3

間で電荷を再分配するための時間を十分に確保することができるので、電荷の再分配がほ

とんど終了した後に、電源Vref から各コンデンサーC1 〜C3 に対して電荷を補充する

こととしても良い。

【0061】

図9は、第1実施例の変形例の駆動波形生成回路204において、コンデンサーC1 〜

C3 で電荷の再分配を行った後に、各コンデンサーC1 〜C3 に対して電荷を補充する様

子を示した説明図である。図9(a)は、コンデンサーC1 〜C3 で電荷の再分配を行っ

ている状態を表している。尚、ここでも、図8に示した場合と同様に、コンデンサーC1

では電荷が増加し、コンデンサーC2 ,C3 では電荷が減少するものとする。また、特に

言及しない点については、前述した第1実施例と同様である。第1実施例の変形例の駆動

波形生成回路204では、ピエゾ素子104に印加すべき電圧が電圧Vref になると、図

9(a)に示したように、各コンデンサーC1 〜C3 の電源側のスイッチS1 〜S3 、お

よび接地側のスイッチE1 、E2 を初めから接続状態(ON)に切り換えて、ピエゾ素子

104に電圧Vref を印加すると同時に、コンデンサーC1 〜C3 間での電荷の再分配を

行う。図9(a)には、電荷が過剰に蓄えられたコンデンサーC1 から、電荷の不足する

コンデンサーC2 ,C3 に向かって電荷が供給されることで、電荷の再分配が行われる様

子が、破線の矢印によって表されている。

【0062】

そして、電荷の再分配が、ある程度まで進んだら(たとえば、再分配の開始後、ある程

度の時間が経過したら)、図9(b)に示したように、その状態から更に、電源Vref を

接続するためのスイッチS4 をONにすることで、各コンデンサーC1 〜C3 に対して電

源Vref も並列に接続する。図9(b)には、電源Vref から各コンデンサーC1 〜C3

に対して電荷が補充される様子が、破線の矢印によって表されている。

【0063】

図10は、第1実施例の変形例の駆動波形生成回路204がピエゾ素子104に電圧を

印加する様子を示した説明図である。図示した第1実施例の変形例は、図8を用いて前述

した第1実施例に対して、印加電圧が電圧Vref になると、直ちに各コンデンサーC1 〜

C3 間で電荷の再分配を行う点と、電荷の再分配を行って暫く時間が経過した後は、電荷

の補充を行う点とが異なっている。その他の点については、同様である。図10では、電

荷の再分配を行っている時間には粗い斜線を付し、電荷を補充している時間には細かい斜

線を付して表示している。

【0064】

こうすれば、図10(c)に示されているように、印加電圧が電圧2Vref から電圧V

ref に減少する際に、ピエゾ素子104から放出される電荷が、コンデンサーC1 だけで

なく、コンデンサーC2 ,C3 にも分配されるので、コンデンサーC1 〜C3 間での電荷

の再分配を速やかに完了させることが可能となる。その結果、図10(b)に示されるよ

うに、ピエゾ素子104の印加電圧が、より速やかに電圧Vref に切り換わるので、より

正確な電圧波形でピエゾ素子104を駆動することが可能となる。

【0065】

また、回路での損失などによって電力損失が発生した場合には、電荷の再分配後にコン

デンサーC1 〜C3 の電荷量が不足する事態も生じ得る。しかし、第1実施例の変形例で

は、コンデンサーC1 〜C3 間で電荷の再分配を速やかに行うことができるので、図10

中に細かい斜線を付して示したように、その後は、電源Vref から電荷を補充することが

できる。その結果、各コンデンサーC1 〜C3 の端子間電圧を常に初期の電圧Vref に維

持しておくことができるので、ピエゾ素子104に正確な電圧を印加することが可能とな

る。また、コンデンサーC1 〜C3 間で電荷を再分配した後に、電源Vref から電荷を補

充しているため、電力損失で失われた最小限の電荷だけを補充することが可能となる。

【0066】

C.第2実施例 :

上述した第1実施例では、比較的単純な例として、駆動波形生成回路204が、各コン

デンサーC1 〜C3 と電源Vref とを接続するためのスイッチS1 〜S4 と、コンデンサ

ーC1 ,C2 の接地側の端子をグランドに接続するためのスイッチE1 ,E2 と、各コン

デンサーC1 〜C3 を直列に接続するためのスイッチB1 ,B2 とによって構成されてい

るものとして説明した。しかし実際には、各コンデンサーC1 〜C3 が同じ電圧で充電さ

れ、且つ、各コンデンサーC1 〜C3 が互いに並列に接続することが可能でありさえすれ

ば、どのような駆動波形生成回路に対しても、第1実施例と同様にして各コンデンサーC

1 〜C3 間での電荷を再分配することが可能である。以下では、このような第2実施例の

駆動波形生成回路304について説明する。尚、第2実施例において、第1実施例と同様

の構成部分については第1実施例と同様の符号を付すとともに、その詳細な説明を省略す

る。

【0067】

C−1.回路構成 :

図11は、第2実施例の駆動波形生成回路304の一例を示した回路図である。図11

に示した第2実施例の駆動波形生成回路304は、図3を用いて前述した第1実施例の駆

動波形生成回路204に対して、新たに補助電源Vbootが追加されており、この補助電源

VbootがコンデンサーC1 〜C3 の接地側の端子に接続され、そして、補助電源Vbootと

各コンデンサーC1 〜C3 との間には、スイッチSb1〜Sb3が設けられた回路構成となっ

ている。また、第1実施例の駆動波形生成回路204では、コンデンサーC3 の接地側の

端子はグランドに直接接続されていたが、第2実施例の駆動波形生成回路304では、コ

ンデンサーC3 の接地側(正確には低電位側)の端子に、スイッチSb3を介して補助電源

Vbootを接続可能となっていることに伴って、コンデンサーC3 の低電位側の端子とグラ

ンドとの間にも、スイッチE3 が新たに追加されている。

【0068】

このような第2実施例の駆動波形生成回路304では、補助電源Vbootを用いなければ

、前述した第1実施例の駆動波形生成回路204と同様に作動して、ピエゾ素子104の

印加電圧を、電圧Vref 〜電圧3Vref の範囲で変化させることができる。更に、補助電

源Vbootを用いれば、ピエゾ素子104に印加する電圧範囲を、電圧Vref 〜電圧3Vre

f +Vbootの範囲に拡大することが可能である。そして、このような第2実施例の駆動波

形生成回路304においても、印加電圧を変化させることに伴って、コンデンサーC1 〜

C3 間で電荷の偏りが発生する可能性があり、それに起因した電力損失が生じ得る。そこ

で、第2実施例の駆動波形生成回路304においても、コンデンサーC1 〜C3 間で電荷

の再分配を行うことにより、電荷の偏りに起因した電力損失が発生することを回避してい

る。以下では、この点について説明する。

【0069】

C−2.容量性負荷の駆動原理 :

図12は、第2実施例の駆動波形生成回路304がピエゾ素子104の印加電圧を切り

換える様子を示した説明図である。図12(a)には、ピエゾ素子104に印加しようと

する目標の電圧波形が示されており、図12(b)には、補助電源Vbootと各コンデンサ

ーC1 〜C3 とを接続するスイッチSb1〜Sb3の接続状態が示されている。たとえば、図

12(b)に「OFF」と表示されているのは、スイッチSb1〜Sb3が何れも切断状態(

OFF)になっていることを表しており、「Sb1」と表示されているのは、スイッチSb1

が接続状態(ON)になっていることを表している。また、図12(c)には、ピエゾ素

子104の印加電圧を切り換えるために、各コンデンサーC1 〜C3 とピエゾ素子104

との間で電荷のやり取りが行われる様子が示されており、そして、図12(d)には、実

際にピエゾ素子104に印加される電圧波形が示されている。

【0070】

先ず、印加電圧を電圧Vref 〜電圧3Vref まで増加させる際には、前述した第1実施

例と同様にして、各コンデンサーC1 〜C3 の接続状態を切り換えることにより、ピエゾ

素子104の印加電圧を変化させる。すなわち、図12(b)に示すように、補助電源V

bootを接続するためのスイッチSb1〜Sb3は何れもOFFにした状態で、コンデンサーC

1 の低電位側の端子をグランドに接続するスイッチE1 をONにすることで、コンデンサ

ーC1 のみを用いて電圧Vref をピエゾ素子104に印加する。次に、スイッチE1 をO

FFにして、代わりにコンデンサーC2 の低電位側の端子をグランドに接続するスイッチ

E2 をONにするとともに、コンデンサーC1 とコンデンサーC2 とを接続するスイッチ

B1 をONにする。こうすると、2つのコンデンサーC1 ,C2 を直列に接続して得られ

る電圧2Vref が、ピエゾ素子104に印加される。更に、スイッチE2 をOFFにして

、代わりに、コンデンサーC3 の低電位側の端子をグランドに接続するスイッチE3 をO

Nにするとともに、スイッチB1 ,B2 をONにすることで、3つのコンデンサーC1 〜

C3 を直列に接続する。こうすると、ピエゾ素子104には、3つのコンデンサーC1 〜

C3 を直列に接続して得られる電圧3Vref が印加されることになる。以上の動作は、第

1実施例の駆動波形生成回路204がピエゾ素子104の印加電圧を切り換える動作と同

様である。

【0071】

ここで、第2実施例の駆動波形生成回路304には補助電源Vbootが設けられているの

で、この補助電源Vbootを用いることで、更に高い電圧をピエゾ素子104に印加するこ

とが可能となる。たとえば、補助電源Vbootが出力する電圧Vbootを、少なくとも電圧2

Vref よりも高い電圧としておけば、補助電源VbootとコンデンサーC1 とを直列に接続

することで、3つのコンデンサーC1 〜C3 を直列に接続した場合よりも高い電圧を発生

させることが可能である。そこで、図12(b)に示したように、スイッチSb1をONに

して、コンデンサーC1 の低電位側の端子を補助電源Vbootに接続する。尚、スイッチS

b1をONにすることに伴って、コンデンサーC1 の低電位側の端子をグランドに接続する

ためのスイッチE1 はOFFにしておく。こうすれば、補助電源VbootとコンデンサーC

1 とが直列に接続されて、それによって得られた電圧Vboot+Vref が、ピエゾ素子10

4に印加されることになる。

【0072】

続いて、図12(b)に示すように、スイッチSb1をOFFにして代わりにスイッチS

b2をONにするとともに、コンデンサーC1 とコンデンサーC2 とを接続するスイッチB

1 をONにする。すると、補助電源VbootとコンデンサーC2 とが直列に接続され、更に

コンデンサーC1 とコンデンサーC2 とが直列に接続されるので、結局、補助電源Vboot

と、2つのコンデンサーC1 ,C2 とが直列に接続されて、補助電源Vbootの発生電圧V

bootに、2つのコンデンサーC1 ,C2 の端子間電圧を加えた合計電圧Vboot+2Vref

を、ピエゾ素子104に印加することができる。

【0073】

更に続いて、図12(b)に示すように、スイッチSb2をOFFにして代わりにスイッ

チSb3をONにすることで、補助電源VbootとコンデンサーC3 とを直列に接続するとと

もに、スイッチB1 およびスイッチB2 をONにすることで、3つのコンデンサーC1 〜

C3 を直列に接続する。その結果、補助電源Vbootと、3つのコンデンサーC1 〜C3 と

が直列に接続されて、発生電圧Vbootに3つのコンデンサーC1 〜C3 の端子間電圧を加

えた合計電圧Vboot+3Vref をピエゾ素子104に印加することが可能となる。

【0074】

以上のようにして、スイッチE1 〜E3 、Sb1〜Sb3、B1 、B2 の接続状態を切り換

えていけば、ピエゾ素子104の印加電圧を、電圧Vref 〜電圧Vboot+3Vref まで増

加させることができる。そして、前述した第1実施例の駆動波形生成回路204と同様に

、ピエゾ素子104の印加電圧を増加させるに伴って、ピエゾ素子104に接続されてい

るコンデンサーからピエゾ素子104に向かって電荷が供給される。図12(c)には、

印加電圧が電圧Vref 〜電圧Vboot+3Vref まで増加する際に、ピエゾ素子104に接

続されるコンデンサーと、各コンデンサーから電荷が供給される様子とが示されている。

尚、図6(b)と同様に、図12(c)中の「OFF」という表示は、コンデンサーがピ

エゾ素子104から切断された状態であることを意味している。また、図12(c)中の

白抜きの矢印は、コンデンサーからピエゾ素子104に電荷が供給されることを示してい

る。

【0075】

ピエゾ素子104の印加電圧を減少させる場合は、印加電圧を増加させる場合と逆の動

作を行えばよい。以下、簡単に説明すると、先ず、3つのコンデンサーC1 〜C3 が直列

に接続されている状態(すなわち、スイッチB1 ,B2 がON)から、コンデンサーC2

とコンデンサーC3 との間のスイッチB2 をOFFにして、コンデンサーC3 を切り離す

。そして、補助電源VbootとコンデンサーC3 との間のスイッチSb3をOFFにして、代

わりに補助電源VbootとコンデンサーC2 との間のスイッチSb2をONにすることで、補

助電源VbootをコンデンサーC2 に接続する。コンデンサーC3 が切り離されて2つのコ

ンデンサーC1 ,C2 が直列に接続されているところに、補助電源Vbootが接続されるか

ら、補助電源Vbootの発生電圧Vbootに、2つのコンデンサーC1 ,C2 の端子間電圧を

加えた合計電圧Vboot+2Vref が、ピエゾ素子104に印加されることになる。

【0076】

その状態から、更にスイッチB1 をOFFにしてコンデンサーC2 をコンデンサーC1

から切り離すとともに、スイッチSb2をOFFにしてスイッチSb1をONにすることで、

コンデンサーC2 に接続されていた補助電源VbootをコンデンサーC1 に繋ぎ代える。す

ると、ピエゾ素子104に印加される電圧は、電圧Vboot+2Vref から電圧Vboot+V

ref に減少する。更に、補助電源VbootとコンデンサーC1 とを接続するスイッチSb1を

OFFにするとともに、スイッチB1 ,B2 をONにして(すなわち、3つのコンデンサ

ーC1 〜C3 を直列に接続して)、コンデンサーC3 の低電位側の端子をグランドに接続

するべくスイッチE3 をONにする。すると、ピエゾ素子104に印加される電圧は、電

圧Vboot+Vref から電圧3Vref に減少する。ピエゾ素子104に印加される電圧を、

電圧3Vref から電圧Vref に減少させる手順は、図5あるいは図6を用いて前述した第

1実施例の駆動波形生成回路204と同様であるため説明は省略する。

【0077】

以上のようにして、スイッチE1 〜E3 、Sb1〜Sb3、B1 、B2 の接続状態を切り換

えることで、ピエゾ素子104の印加電圧を、電圧Vboot+3Vref 〜電圧Vref に減少

させることができる。そして、こうしてピエゾ素子104の印加電圧を減少させるに伴っ

て、ピエゾ素子104から放出された電荷が、ピエゾ素子104に接続されているコンデ

ンサーによって回収されることになる。図12(c)には、印加電圧が電圧Vboot+3V

ref 〜電圧Vref に減少する際に、ピエゾ素子104に接続されるコンデンサーと、各コ

ンデンサーによって電荷が回収される様子とが示されている。尚、図12(c)中に示し

た斜線付きの矢印は、ピエゾ素子104が放出した電荷がコンデンサーによって回収され

ることを表している。

【0078】

以上のようにして、第2実施例の駆動波形生成回路304では、ピエゾ素子104に印

加する電圧を、電圧Vref 〜電圧Vboot+3Vref までの範囲で自由に変化させることが

できるが、その際に、各コンデンサーC1 〜C3 とピエゾ素子104との間で電荷のやり

取りが行われ、その結果として、第1実施例の駆動波形生成回路204と同様に、コンデ

ンサーC1 〜C3 の間で電荷の偏りが生じ得る。そして、このような電荷の偏りが蓄積さ

れると、各コンデンサーC1 〜C3 の端子間電圧が変化してしまい、正確な電圧を印加す

ることができなくなる。また、こうした事態を回避しようとすると、電荷が過剰に蓄積さ

れたコンデンサーについては電荷をグランドに放出し、電荷が不足したコンデンサーにつ

いては電源Vref から電荷を補充しなければならないので、その分の電力は損失となる。

【0079】

そこで、第2実施例の駆動波形生成回路304においても、前述した第1実施例の駆動

波形生成回路204と同様に、各コンデンサーC1 〜C3 の間で電荷の再分配を行う。す

なわち、ピエゾ素子104の印加電圧を電圧Vref まで減少させた後、電圧Vref を印加

したままで、コンデンサーC1 〜C3 を並列に接続する。

【0080】

図13は、第2実施例の駆動波形生成回路304でコンデンサーC1 〜C3 間の電荷を

再分配する様子を示す説明図である。尚、ここでも、コンデンサーC1 では電荷が過剰に

回収され(電荷が増加し)、コンデンサーC2 ,C3 では電荷を過剰に供給(電荷が減少

)するものとする。図13(a)には、電圧Vref を印加している状態が示されており、

この状態から図13(b)に示したように、スイッチS1 〜S3 およびスイッチE1 〜E

3 をONにして、3つのコンデンサーC1 〜C3 が並列に接続された状態に切り換える。

すると、コンデンサーC1 に過剰に蓄えられた電荷が、コンデンサーC2 ,C3 に供給さ

れて、電荷の再分配が行われる。図13(b)には、コンデンサーC1 〜C3 間の電荷の

流れが破線の矢印によって示されている。

【0081】

以上に説明したように、第2実施例の駆動波形生成回路304においても、ピエゾ素子

104に接続されるコンデンサーが1つになると(すなわち印加電圧が電圧Vref になる

と)、他のコンデンサーもそのコンデンサーに対して並列に接続することで、各コンデン

サーC1 〜C3 間で電荷の再分配を行う。こうすることで、電荷の偏りに起因して端子間

電圧が変化することを回避して、正確な電圧を印加することが可能となる。

【0082】

もちろん、コンデンサーC1 〜C3 間で電荷の再分配を行った後に、電源Vref とコン

デンサーC1 〜C3 とを接続するスイッチS4 をONにすることで、電源Vref からコン

デンサーC1 〜C3 に電荷を補充することとしても良い。あるいは、図9および図10を

用いて前述した第1実施例の変形例と同様に、印加電圧を電圧Vref に切り換える際には

、初めから各コンデンサーC1 〜C3 を並列に接続して、電荷の再分配を行うこととして

も良い。更に、電荷の再分配を開始した後、再分配がある程度まで進んだら、電源Vref

も各コンデンサーC1 〜C3 に対して並列に接続することで、電源Vref から各コンデン

サーC1 〜C3 に電荷を補充することとしても良い。

【0083】

また、以上の説明では、コンデンサーC1 〜C3 間の電荷の再分配は、ピエゾ素子10

4の印加電圧が電圧Vref の時に行うものとした。しかし、実際には、ピエゾ素子104

に対して1つのコンデンサー(たとえば、コンデンサーC1 )のみが接続されており、他

のコンデンサー(たとえば、コンデンサーC2 ,C3 )が切り離されている状態であれば

、それら3つのコンデンサーC1 〜C3 を並列に接続して電荷の再分配を行うことが可能

である。

【0084】

図14は、印加電圧が電圧Vref 以外のときに電荷の再分配を行う様子を例示した説明

図である。たとえば図14(a)に示すように、ピエゾ素子104に電圧Vboot+Vref

を印加している状態では、ピエゾ素子104に接続されているコンデンサーは、コンデン

サーC1 のみであり、他のコンデンサーC2 ,C3 はピエゾ素子104から切り離された

状態となっている。そこで、図14(b)に示すように、スイッチS1 〜S3 およびスイ

ッチSb1〜Sb3をONにすることで、コンデンサーC1 〜C3 を並列に接続する。こうす

れば、ピエゾ素子104に電圧Vboot+Vref を印加したまま、コンデンサーC1 からコ

ンデンサーC2 およびコンデンサーC3 に電荷が供給されて、電荷を再分配することが可

能となる。

【0085】

以上、各種実施例および変形例の駆動波形生成回路について説明したが、本発明は上記

に限られるものではなく、その要旨を逸脱しない範囲において種々の態様で実施すること

が可能である。例えば、駆動波形生成回路によって駆動される容量性負荷はピエゾ素子1

04であるものとして説明したが、容量成分を有する負荷であればピエゾ素子104に限

らず、どのような負荷であっても構わない。例えば、液晶パネルや有機ELなどの各種表

示装置を負荷として駆動する場合にも、本発明を好適に適用することが可能である。

【符号の説明】

【0086】

10…インクジェットプリンター、 20…キャリッジ、 24…噴射ヘッド、

26…インクカートリッジ、 30…駆動機構、 40…プラテンローラー、

50…プリンター制御回路、 100…噴射口、 102…インク室、

104…ピエゾ素子、 200…噴射ヘッド駆動回路、 202…制御回路、

204…駆動波形生成回路、 300…ゲートユニット、 302…ゲート素子、

304…駆動波形生成回路、 Vref…電源、 Vboot…補助電源、

C1 ,C2 ,C3 …コンデンサー、 B1 ,B2 …スイッチ、

E1 ,E2 ,E3 …スイッチ、 S1 ,S2 ,S3 ,S4 …スイッチ

【特許請求の範囲】

【請求項1】

容量性負荷を駆動する容量性負荷駆動回路であって、

電荷を蓄積する複数の電荷蓄積素子と、

前記電荷蓄積素子に電荷を供給する電源と、

前記複数の電荷蓄積素子と、前記電源と、前記容量性負荷との接続状態を切り換える接

続状態切換手段と

を備え、

前記接続状態切換手段は、

前記容量性負荷が前記電源および前記複数の電荷蓄積素子から切断された状態で、前

記電源と前記複数の電荷蓄積素子とが並列に接続される第1の接続状態と、

前記容量性負荷が前記電源および前記複数の電荷蓄積素子から切断された状態で、前

記複数の電荷蓄積素子のうちの1つの前記電荷蓄積素子、または直列に接続された少なく

とも2つの前記電荷蓄積素子が、前記容量性負荷に対して並列に接続される第2の接続状

態と、

前記電源が前記複数の電荷蓄積素子および前記容量性負荷から切断され、前記複数の

電荷蓄積素子のうちの1つの前記電荷蓄積素子が前記容量性負荷に対して並列に接続され

た状態で、該容量性負荷に接続された1つの該電荷蓄積素子に対して、他の前記電荷蓄積

素子が並列に接続される第3の接続状態と

に切り換え可能な手段である容量性負荷駆動回路。

【請求項2】

請求項1に記載の容量性負荷駆動回路であって、

前記接続状態切換手段は、更に、前記複数の電荷蓄積素子が、前記電源および前記容量

性負荷から切断された状態で、該複数の電荷蓄積素子が並列に接続される第4の接続状態

に切り換え可能な手段である容量性負荷駆動回路。

【請求項3】

請求項1または請求項2に記載の容量性負荷駆動回路であって、

前記接続状態切換手段は、

前記電源、前記複数の電荷蓄積素子、および前記容量性負荷が並列に接続される第5

の接続状態に切り換え可能であり、

前記第3の接続状態に切り換えた後に、前記第5の接続状態に切り換える手段である

容量性負荷駆動回路。

【請求項4】

容量性負荷を駆動する容量性負荷駆動回路であって、

電荷を蓄積する第1の電荷蓄積素子および第2の電荷蓄積素子と、

前記第1および第2の電荷蓄積素子の少なくとも何れかにに電荷を供給する電源と、

前記第1および第2の電荷蓄積素子と、前記電源と、前記容量性負荷との接続状態を切

り換える接続状態切換手段と

を備え、

前記接続状態切換手段は、

前記容量性負荷が前記電源と、前記第1および第2の電荷蓄積素子とから切断された

状態で、前記電源と前記第1および第2の電荷蓄積素子とが並列に接続される第1の接続

状態と、

前記電源が前記第1および第2の電荷蓄積素子、並びに前記容量性負荷から切断され

た状態で、前記第1の電荷蓄積素子、または直列に接続された前記第1および第2の電荷

蓄積素子が、前記容量性負荷に対して並列に接続される第2の接続状態と、

前記電源が前記第1および第2の電荷蓄積素子並びに前記容量性負荷から切断され、

前記第1の電荷蓄積素子が前記容量性負荷に対して並列に接続された状態で、前記第1の

電荷蓄積素子に対して前記第2の電荷蓄積素子が並列に接続される第3の接続状態と

に切り換え可能な手段である容量性負荷駆動回路。

【請求項5】

請求項4に記載の容量性負荷駆動回路であって、

前記接続状態切換手段は、更に、前記第1および第2の電荷蓄積素子が、前記電源およ

び前記容量性負荷から切断された状態で、前記第1および第2の電荷蓄積素子が並列に接

続される第4の接続状態に切り換え可能な手段である容量性負荷駆動回路。

【請求項6】

請求項4または請求項5に記載の容量性負荷駆動回路であって、

前記接続状態切換手段は、

前記電源、前記第1および第2の電荷蓄積素子、並びに前記容量性負荷が並列に接続

される第5の接続状態に切り換え可能であり、

前記第3の接続状態に切り換えた後に、前記第5の接続状態に切り換える手段である

容量性負荷駆動回路。

【請求項1】

容量性負荷を駆動する容量性負荷駆動回路であって、

電荷を蓄積する複数の電荷蓄積素子と、

前記電荷蓄積素子に電荷を供給する電源と、

前記複数の電荷蓄積素子と、前記電源と、前記容量性負荷との接続状態を切り換える接

続状態切換手段と

を備え、

前記接続状態切換手段は、

前記容量性負荷が前記電源および前記複数の電荷蓄積素子から切断された状態で、前

記電源と前記複数の電荷蓄積素子とが並列に接続される第1の接続状態と、

前記容量性負荷が前記電源および前記複数の電荷蓄積素子から切断された状態で、前

記複数の電荷蓄積素子のうちの1つの前記電荷蓄積素子、または直列に接続された少なく

とも2つの前記電荷蓄積素子が、前記容量性負荷に対して並列に接続される第2の接続状

態と、

前記電源が前記複数の電荷蓄積素子および前記容量性負荷から切断され、前記複数の

電荷蓄積素子のうちの1つの前記電荷蓄積素子が前記容量性負荷に対して並列に接続され

た状態で、該容量性負荷に接続された1つの該電荷蓄積素子に対して、他の前記電荷蓄積

素子が並列に接続される第3の接続状態と

に切り換え可能な手段である容量性負荷駆動回路。

【請求項2】

請求項1に記載の容量性負荷駆動回路であって、

前記接続状態切換手段は、更に、前記複数の電荷蓄積素子が、前記電源および前記容量

性負荷から切断された状態で、該複数の電荷蓄積素子が並列に接続される第4の接続状態

に切り換え可能な手段である容量性負荷駆動回路。

【請求項3】

請求項1または請求項2に記載の容量性負荷駆動回路であって、

前記接続状態切換手段は、

前記電源、前記複数の電荷蓄積素子、および前記容量性負荷が並列に接続される第5

の接続状態に切り換え可能であり、

前記第3の接続状態に切り換えた後に、前記第5の接続状態に切り換える手段である

容量性負荷駆動回路。

【請求項4】

容量性負荷を駆動する容量性負荷駆動回路であって、

電荷を蓄積する第1の電荷蓄積素子および第2の電荷蓄積素子と、

前記第1および第2の電荷蓄積素子の少なくとも何れかにに電荷を供給する電源と、

前記第1および第2の電荷蓄積素子と、前記電源と、前記容量性負荷との接続状態を切

り換える接続状態切換手段と

を備え、

前記接続状態切換手段は、

前記容量性負荷が前記電源と、前記第1および第2の電荷蓄積素子とから切断された

状態で、前記電源と前記第1および第2の電荷蓄積素子とが並列に接続される第1の接続

状態と、

前記電源が前記第1および第2の電荷蓄積素子、並びに前記容量性負荷から切断され

た状態で、前記第1の電荷蓄積素子、または直列に接続された前記第1および第2の電荷

蓄積素子が、前記容量性負荷に対して並列に接続される第2の接続状態と、

前記電源が前記第1および第2の電荷蓄積素子並びに前記容量性負荷から切断され、

前記第1の電荷蓄積素子が前記容量性負荷に対して並列に接続された状態で、前記第1の

電荷蓄積素子に対して前記第2の電荷蓄積素子が並列に接続される第3の接続状態と

に切り換え可能な手段である容量性負荷駆動回路。

【請求項5】

請求項4に記載の容量性負荷駆動回路であって、

前記接続状態切換手段は、更に、前記第1および第2の電荷蓄積素子が、前記電源およ

び前記容量性負荷から切断された状態で、前記第1および第2の電荷蓄積素子が並列に接

続される第4の接続状態に切り換え可能な手段である容量性負荷駆動回路。

【請求項6】

請求項4または請求項5に記載の容量性負荷駆動回路であって、

前記接続状態切換手段は、

前記電源、前記第1および第2の電荷蓄積素子、並びに前記容量性負荷が並列に接続

される第5の接続状態に切り換え可能であり、

前記第3の接続状態に切り換えた後に、前記第5の接続状態に切り換える手段である

容量性負荷駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2011−45225(P2011−45225A)

【公開日】平成23年3月3日(2011.3.3)

【国際特許分類】

【出願番号】特願2009−193939(P2009−193939)

【出願日】平成21年8月25日(2009.8.25)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成23年3月3日(2011.3.3)

【国際特許分類】

【出願日】平成21年8月25日(2009.8.25)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]