導電性ペーストおよびセラミック電子部品の製造方法

【課題】 セラミック電子部品の外部電極の形成に使用した場合に、リフトオフ(セラミックからの剥離)の発生する可能性が低い導電性ペーストを提供する。

【解決手段】 導電性金属粉末の焼結開始温度(℃)と、ガラスフリットのガラス転移点Tg(℃)とを、

(ガラスフリットのTg)−(導電性金属粉末の焼結開始温度)<100

の関係を満たすようにする。

【解決手段】 導電性金属粉末の焼結開始温度(℃)と、ガラスフリットのガラス転移点Tg(℃)とを、

(ガラスフリットのTg)−(導電性金属粉末の焼結開始温度)<100

の関係を満たすようにする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、セラミック電子部品の外部電極などの形成に用いられる導電性ペーストに関し、さらに詳しくは、セラミック電子部品の外部電極の形成に使用した場合に、リフトオフ(セラミックからの剥離)の発生する可能性が低い導電性ペーストに関する。

【0002】

また、本発明は、上記導電性ペーストを使用した、セラミック電子部品の製造方法に関する。

【背景技術】

【0003】

従来から、セラミック電子部品の外部電極の形成方法として、特許文献1(特開2000‐40635号公報)に開示されるように、セラミック素子の表面に、導電性ペーストを塗布し、焼成する方法が一般的に用いられている。

【0004】

図2に、そのような方法で外部電極が形成されたセラミック電子部品の一例として、積層セラミックコンデンサ200を示す。

【0005】

積層セラミックコンデンサ200は、セラミック素子101を備える。

【0006】

セラミック素子101の内部には、セラミック素子101の一方の端部に引出された複数の内部電極102と、セラミック素子101の他方の端部に引出された複数の内部電極103とが、交互に、セラミック層104を介して形成されている。

【0007】

そして、セラミック素子101の一方の端部には、内部電極102と接続された外部電極105が形成され、セラミック素子101の他方の端部には、内部電極103と接続された外部電極106が形成されている。外部電極105、106は、それぞれ、セラミック素子101の端面から、その端面に続く4つの側面に跨って、キャップ状に形成されている。なお、図示しないが、外部電極105、106の表面には、さらに、はんだ付け性の向上などを目的として、めっき層が形成されることが多い。めっき層としては、たとえば、第1層としてNiめっき層、第2層としてSnめっき層が形成される。

【0008】

このような構造からなる積層セラミックコンデンサ200は、たとえば、次の方法で製造される。

【0009】

まず、誘電体セラミックで形成された、マザーグリーンシートを準備し、このマザーグリーンシートの表面に、導電性ペーストで複数個分の内部電極のパターンを形成する。そして、内部電極のパターンが形成されたマザーグリーンシートと、内部電極のパターンが形成されていないマザーグリーンシートとを、所定の枚数、所定の順番に積層し、圧着したうえで、素子単位ごとに切断し、未焼成のチップを得る。

【0010】

次に、未焼成のチップを、所定のプロファイルで焼成して、セラミック素子101を得る。

【0011】

次に、導電性金属粉末と、ガラスフリットと、ビヒクルとを含有した、外部電極用の導電性ペーストを準備し、ディッピングにより、セラミック素子101の両端に塗布し、所定のプロファイルで焼成して、外部電極105、106を形成する。導電性金属粉末としては、たとえば、Cu粉、Ni粉,Ag粉などが用いられる。なお、ガラスフリットは、外部電極のセラミック素子への密着性の向上や、外部に対するシール性の向上などのために含有されている。

【0012】

最後に、外部電極105、106の表面に、電解めっきにより、めっき層を形成して、積層セラミックコンデンサ200は完成する。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2000‐40635号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

近時、電子機器が、高温下、高湿度下など、さまざまな環境下で使用されるようになってきており、電子機器に使用されるセラミック電子部品においても、耐候性の確保が不可欠である。

【0015】

そして、セラミック電子部品の耐候性を確保するためには、外部電極を緻密な金属膜にすることが必要である。たとえば、粒度分布が比較的ブロードで、炭素などの焼結を阻害する不純物を含みにくく、焼結開始温度が低く、焼結後の金属充填密度が高いアトマイズ法で作製された導電性金属粉末を含有した導電性ペーストを使用して外部電極を形成することが有効である。

【0016】

しかしながら、焼結開始温度が低い導電性金属粉末を含有した導電性ペーストを使用してセラミック電子部品の外部電極を形成した場合、セラミック素子が小さい場合は良いが、セラミック素子が大きくなると、導電性ペーストの焼成時に、セラミック素子の側面部分において、外部電極がセラミック素子から剥離する、リフトオフと呼ばれる現象が発生することがある。

【0017】

図3は、上述した積層セラミックコンデンサ200において、外部電極106にリフトオフが発生した状態を示す。セラミック素子101の側面において、外部電極106の先端部がセラミック素子101から剥離し、隙間107が形成されている。

【0018】

特に、リフトオフは、比較的大きいセラミック素子に、外部電極を形成した場合に発生しやすい傾向がある。すなわち、セラミック素子が大きくなると、セラミック素子の端面が大きくなり、ディッピングにより導電性ペーストを塗布した場合、端面に多量の導電性ペーストが付着し、端面における導電性ペーストの膜厚が大きくなり、これに連なるセラミック素子の側面における導電性ペーストの膜厚も大きくなる。そして、セラミック素子の側面における導電性ペーストの膜厚が大きくなることにより、導電性ペーストの焼成時に、リフトオフを発生させる応力が大きくなる。

【0019】

図4に、セラミック素子101の端部に塗布された導電性ペーストを焼成して外部電極106を形成する場合に、塗布された導電性ペーストに生じる応力を矢印Fで示す。塗布された導電性ペーストには、セラミック素子101の側面における先端部と、セラミック素子101の稜線部において、引張応力が加わる。そして、上述のとおり、セラミック素子101のサイズが大きくなると、セラミック素子101の側面に塗布される導電性ペーストの膜厚が大きくなるため、この引張応力が大きくなり、リフトオフが発生してしまう。

【0020】

外部電極にリフトオフが発生すると、外部電極の表面にめっき層を形成する際に、めっき液が隙間からセラミック素子の内部に侵入して、特性が劣化するそれがある。また、隙間から、大気中の水蒸気などが侵入するおそれがあり、却って、セラミック電子部品の耐候性が低下してしまう。すなわち、外部電極のリフトオフは、セラミック電子部品を不良品とするものであり、極めて大きな問題である。

【0021】

本発明者は、鋭意検討を重ねた結果、リフトオフが発生する原因が、導電性金属粉末の焼結開始温度が、ガラスフリットのガラス転移点Tgに対して低すぎるため、ガラスフリットが軟化流動し、ガラス成分が導電性ペーストとセラミック素子とを固着してリフトオフの発生を阻止する作用を発現する前に、導電性金属粉末が焼結を開始してしまい、リフトオフにつながる応力が発生する点にあることを見出した。

【0022】

導電性ペーストには、セラミック素子との密着性を向上させるために、ガラスフリットが含有されている。しかしながら、焼結開始温度の低い導電性金属粉末を含有した導電性ペーストを使用した場合には、ガラスフリットは、有効にリフトオフの発生を阻止することができない。すなわち、比較的大きいセラミック素子に、比較的焼結開始温度が低い導電性金属粉末を含有する導電性ペーストを使用して外部電極を形成した場合に、リフトオフが発生するものと考えられる。たとえば、アトマイズ法で作製された導電性金属粉末を含有する導電性ペーストを使用してセラミック素子の端部に外部電極を形成した場合、縦1.6mm、横0.8mm、高さ0.8mmからなるサイズのセラミック電子部品においては、リフトオフは問題にならなかったが、縦2.0mm、横1.2mm、高さ1.2mmからなるサイズ以上のセラミック電子部品において、リフトオフが発生する場合があった。

【0023】

なお、比較的大きいセラミック素子に、焼結開始温度が低い導電性金属粉末を含有する導電性ペーストを使用して外部電極を形成する場合においても、リフトオフを発生させない方法として、電極ペーストの粘度を低くして、セラミック素子の側面に付着される導電性ペーストの厚みを小さくする方法が考えられる。しかしながら、導電性ペーストの粘度を小さくすると、セラミック素子の稜線部に付着する導電性ペーストの厚みが小さくなってしまい、その部分で外部電極が薄くなって耐候性が低下してしまうため、採用することができなかった。

【課題を解決するための手段】

【0024】

本発明は、上述した、従来の問題点を解消するためになされたものであり、セラミック電子部品の外部電極を形成するのに使用した場合に、リフトオフの発生がない導電性ペーストを提供することを目的とする。

【0025】

本発明の導電性ペーストは、導電性金属粉末と、ガラスフリットと、ビヒクルとを含み、前記導電性金属粉末の焼結開始温度(℃)と、前記ガラスフリットのガラス転移点Tg(℃)とが、

(ガラスフリットのTg)−(導電性金属粉末の焼結開始温度)<100

の関係を満たす。

【0026】

また、前記導電性金属粉末は、Cu、Ni、Agから選ばれる少なくとも1種とすることが好ましい。

【0027】

また、前記導電性金属粉末の内包炭素量は、0.1wt%以下であることが好ましい。この場合には、炭素による焼結の阻害を、許容範囲内に抑えることができる。

【0028】

また、前記導電性金属粉末は、アトマイズ法で作製されたものであることが好ましい。この場合には、焼結性が高いため、耐候性に優れた緻密な金属膜を形成することができる。

【0029】

また、前記導電性金属粉末のD10、D50、およびD90が、

0.5≦(D90−D10)/D50≦1.7

を満たすことが好ましい。この場合には、87%以上の高い焼結密度を実現することができる。

【0030】

また、本発明のセラミック電子部品の製造方法は、内部に内部電極を有し、該内部電極が導出された互いに対向する2つの端面と、それらの前記端面を結ぶ側面とを有するセラミック素子を形成する工程と、前記セラミック素子の両端面に、それぞれ、上記導電性ペーストをディッピングにより塗布する工程と、前記セラミック素子の両端面に塗布された導電性ペーストを、焼成し、外部電極を形成する工程とを備える。

【0031】

また、前記セラミック素子は、前記端面の面積が1.44mm2以上であることが好ましい。

【発明の効果】

【0032】

本発明の導電性ペーストは、上述の構成としたため、金属膜の緻密性を向上させるために、焼結開始温度の低い導電性金属粉末を含有させ、大きなセラミック素子、たとえば、2012サイズ以上のセラミック素子の外部電極の形成に使用しても、リフトオフが発生する可能性が低い。

【0033】

すなわち、導電性金属粉末の焼結開始温度と、ガラスフリットのガラス転移点Tgとの差を規定し、導電性金属粉末の焼結とガラスフリットの軟化流動とのタイミングを合わせているため、焼成時に、すでに液相となったガラス成分により、セラミック素子から導電性ペーストが剥離するのを抑制することができ、リフトオフの発生を有効に阻止することができる。

【図面の簡単な説明】

【0034】

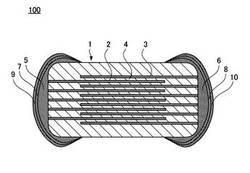

【図1】本発明にかかる導電性ペーストを使用して外部電極を形成した、セラミック電子部品(積層セラミックコンデンサ)100を示す断面図である。

【図2】従来の導電性ペーストを使用して外部電極を形成した、セラミック電子部品(積層セラミックコンデンサ)200を示す断面図である。

【図3】上記従来のセラミック電子部品(積層セラミックコンデンサ)200において、外部電極にリフトオフが発生した状態を示す部分断面図である。

【図4】上記従来のセラミック電子部品(積層セラミックコンデンサ)200において、塗布された導電性ペーストを焼成して外部電極を形成する場合に、導電性ペーストに生じる応力を示した部分断面図である。

【発明を実施するための形態】

【0035】

以下、本発明を実施するための形態について説明する。

[導電性ペーストの構成]

本実施形態にかかる導電性ペーストは、導電性金属粉末、ガラスフリット、ビヒクルを含有する。

【0036】

導電性金属粉末の焼結開始温度(℃)と、ガラスフリットのガラス転移点Tg(℃)とは、

(ガラスフリットのTg)−(導電性金属粉末の焼結開始温度)<100

の関係を満たす。

[導電性ペーストの製造]

本実施形態にかかる導電性ペーストは、たとえば、次の方法により製造される。

【0037】

まず、導電性金属粉末として、溶融したCuの中に、所定量のPを投入して、水アトマイズ法によりCu粉を作製する。

【0038】

Cu粉の焼結開始温度は、Cu粉中の微量成分であるP量を変化させることにより調整することができる。なお、Cu粉の焼結開始温度は、圧粉体を、TMAで測定して求める(測定条件:10℃/分、窒素雰囲気中、室温〜1000℃)。

【0039】

アトマイズ法によれば、真球状のCu粉を得ることができるため、これを使用した導電性ペーストは、ペースト乾燥膜の金属充填率が高くなる。したがって、セラミック電子部品の外部電極の形成に使用した場合、緻密性の高い電極膜を得ることができる。また、アトマイズ法によって作製されたCu粉は、合成過程において、炭素を含有することがないため、金属膜に、Cu粉中の炭素に起因してブリスタが発生することがない。

【0040】

ガラスフリットは、軟化点が500℃〜700℃の、Si‐B‐Zn系ガラスにより作製する。ガラスの綱目構成元素は、Si、Bとし、軟化点を調整するために、アルカリ金属(Li、Naなど)を添加する。また、耐酸性を上げるために(外部電極中のガラスの耐めっき溶解性を上げるために)Tiを添加する。

【0041】

ガラスフリットのガラス転移点(Tg)は、SiとBの割合を変化させることにより調整することができる。一般的に、Bの割合が増えると、ガラス転移点は低下する。

【0042】

まず、ガラスフリットの原料として、各元素の酸化物を用意する。次に、各酸化物を所定量混合し、1500℃で、20分間、ガラス溶融炉で熱処理しながら、混合、撹拌し、その後、冷却して、ガラスを作製する。そして、作製されたガラスを乾式で粉砕し、ガラスフリットを得る。なお、得られたガラスのガラス転移点は、TG‐DTAを測定して確認する。

【0043】

ビヒクルは、アクリル樹脂を、ターピネオールを主成分とする有機溶剤に溶解させて作製する。

【0044】

以上からなる、Cu粉、ガラスフリット、ビヒクルを、それぞれ、所定量秤量し、3本ロールで分散、混合して、本実施形態にかかる導電性ペーストを得る。

【0045】

導電性ペースト中のガラス量は、固形分(Cu粉およびガラスフリット)に対して、20体積%とする。ガラス量が22体積%以上では、外部電極を形成した場合に、電極膜の表面にガラスが偏析し、めっき不良が発生する。ガラス量が18体積%以下になると、外部電極の緻密性が低下し、耐湿負荷試験において、絶縁抵抗が低下する不良がみられる。したがって、導電性ペースト中のガラス量は、固形分に対して、18体積%より多く、22体積%未満が適当である。

【0046】

導電性ペーストの粘度は、E型粘度計において、25℃、1rpmの値で、20Pa・sに調整する。粘度が10Pa・s未満では、セラミック素子の側面における導電性ペーストの厚みが小さくなり、リフトオフは抑制されるが、セラミック素子の稜線部における導電性ペーストの厚みも小さくなってしまい、その部分で外部電極の耐候性が低下してしまうため、耐湿負荷試験で、絶縁抵抗の劣化がみられる。粘度が30Pa・sより大きくなると、塗布後形状がツノ形状になり、欠き取り時にクワレも発生するため、塗布形状の安定性を確保することができず、外部電極に局所的なガラスの偏析、厚みの小さい部分、緻密性不足などが発生して、耐候性が低下する。したがって、導電性ペーストの粘度は、10Pa・s以上、30Pa・s以下が適当である。

[積層セラミックコンデンサの構造]

本実施形態においては、セラミック電子部品として、積層セラミックコンデンサ100を製造した。

【0047】

図1に、積層セラミックコンデンサ100を示す。

【0048】

積層セラミックコンデンサ100は、Ba、Tiを主成分とするセラミックからなる、直方体形状のセラミック素子1を備える。

【0049】

セラミック素子1の内部には、セラミック素子1の一方の端部に引出された複数の内部電極2と、セラミック素子1の他方の端部に引出された複数の内部電極3とが、交互に、セラミック層4を介して形成されている。内部電極2、3は、Niを主成分としている。

【0050】

セラミック素子1の一方の端部には、内部電極2と接続された外部電極5が形成されている。セラミック素子1の他方の端部には、内部電極3と接続された外部電極6が形成されている。外部電極5、6は、それぞれ、セラミック素子1の端面から、その端面に続く4つの側面に跨って、キャップ状に形成されている。この外部電極5、6は、上述した、本発明にかかる導電性ペーストを使用して形成されている。

【0051】

外部電極5、6上には、それぞれ、2層からなるめっき層が形成されている。まず、第1層として、Niめっき層7、8が形成されている。Niめっき層7、8は、実装時のはんだクワレを抑制するために形成されたものである。そして、Niめっき層7、8上には、第2層として、それぞれ、Snめっき層9、10が形成されている。Snめっき層9、10は、はんだ付け性を向上させるために形成されたものである。

[積層セラミックコンデンサの製造]

積層セラミックコンデンサ100は、たとえば、次の方法で製造される。

【0052】

まず、Ba、Tiを主成分とする誘電体セラミックで形成された、複数の素子用の大きなマザーグリーンシートを複数枚準備する。

【0053】

次に、複数枚のマザーグリーンシートのうち所定枚数のマザーグリーンシートの表面に、Niを主成分とする内部電極用の導電性ペーストで、内部電極のパターンを形成する。

【0054】

次に、内部電極のパターンが形成されたマザーグリーンシートと、内部電極のパターンが形成されていないマザーグリーンシートとを、所定の枚数、所定の順番に積層し、圧着したうえで、切断し、個々の未焼成のチップを得る。

【0055】

次に、未焼成のチップを、バッチ炉を使用して、還元性雰囲気中において、所定のプロファイルで焼成して、セラミック素子1を得る。

【0056】

次に、上述した、本発明にかかる導電性ペーストを、ディッピングにより、セラミック素子1の両端面に塗布する。セラミック素子1が、縦2.0mm、横1.2mm、高さ1.2mmのサイズ(端面の面積=1.44mm2)場合には、塗布された導電性ペーストの膜厚は、セラミック素子1の端面において最大80μm程度、側面において最大40μm程度になる。

【0057】

次に、導電性ペーストを塗布したセラミック素子1を、ベルト炉を使用して、中性から還元性雰囲気中において、最高温度800℃〜900℃を10分間保持し、外部電極5、6を形成する。

【0058】

最後に、外部電極5、6上に、電解めっきにより、Niめっき層7、8を形成し、さらにNiめっき層7、8上に、同じく電解めっきにより、Snめっき層9、10を形成し、積層セラミックコンデンサ100を完成させる。

【0059】

以上、本発明の実施形態にかかる導電性ペースト、電子部品(積層セラミックコンデンサ)の製造方法について説明した。しかしながら、本発明が上述の内容に限定されることはなく、本発明の主旨に沿って、種々の変形をなすことができる。

【0060】

たとえば、導電ペーストの導電性金属粉末にCu粉を用いたが、これに代えて、たとえば、Ni粉、Ag粉、Au粉などを用いても良い。

【0061】

また、ガラスフリットの主材料、添加物、ビヒクル、溶剤なども任意であり、上述のものには限定されない。

【0062】

また、製造されるセラミック電子部品も、コンデンサに代えて、たとえば、コイル、抵抗、サーミスタなどであっても良い。さらに、外部電極の表面にめっき層を形成するか否か、形成する場合の種類や層数なども任意であり、上述した内容には限定されない。

【実験例】

【0063】

(実験例1)

本発明の効果を確認するため、次の実験をおこなった。

【0064】

導電性金属粉末としてCu粉を用い、このCu粉の焼結開始温度と、ガラスフリットのガラス転移点(Tg)とを変化させ、他の条件は上述した実施形態と同じにして、40種類の導電性ペーストを作製した。

【0065】

Cu粉の焼結開始温度は、500℃、550℃、600℃、650℃に変化させた。なお、焼結開始温度の変化は、上述のとおり、Pの添加量を変化させることによりおこなった。

【0066】

ガラスフリットのガラス転移点は、500℃、550℃、595℃、600℃、645℃、650℃、695℃、700℃、745℃、750℃に変化させた。なお、ガラス転移点の変化は、上述のとおり、ガラスの綱目構成元素である、Si、Bの割合を変化させることによりおこなった。

【0067】

これらの40種類の導電性ペーストを外部電極の形成に使用して、上述した実施形態と同じ方法で、縦2.0mm、横1.2mm、高さ1.2mmのサイズの積層セラミックコンデンサを製造した。そして、各積層セラミックコンデンサについて、外部電極におけるリフトオフ発生率と、耐湿性負荷試験での絶縁抵抗劣化率とを調べた。

【0068】

リフトオフ発生率は、セラミック素子の側面における外部電極の先端を観察し、一部にでもセラミック素子からの剥離のあるものをリフトオフ発生として、リフトオフ発生率を算出した(n=1000)。

【0069】

耐湿性負荷試験での絶縁抵抗劣化率は、70℃、相対湿度95%、6.3Vの条件で、1000時間放置し、絶縁抵抗をモニタリングし、絶縁抵抗が106Ωを下回ったものを絶縁抵抗劣化として、絶縁抵抗劣化率を算出した(n=70)。

【0070】

表1に、各積層セラミックコンデンサの、リフトオフ発生率と、耐湿性負荷試験での絶縁抵抗劣化率とを示す。なお、表1において、※の付されていないものが本発明にかかる実施例、※の付されたものが本発明の範囲外の比較例である。

【0071】

【表1】

【0072】

実施例はいずれも、リフトオフ発生率0%、耐湿性負荷試験における絶縁抵抗劣化率0%であり、導電性ペーストを、本発明の規定する金属粉の焼結開始温度とガラスフリットのガラス転移点との関係にすれば、比較的大きな素子からなるセラミック電子部品の外部電極の形成に使用しても、耐候性に優れた、信頼性の高い外部電極を形成できることがわかった。

【0073】

一方、比較例は、リフトオフの発生、および耐湿性負荷試験における絶縁抵抗劣化が生じており、実用上問題があることがわかった。

(実験例2)

使用する導電性金属粉末をAg粉にした以外は実験例1と同様にして、積層セラミックコンデンサを作製し、その外部電極におけるリフトオフ発生率と、耐湿性負荷試験での絶縁抵抗劣化率とを調べた。その結果を表2に示す。

【0074】

【表2】

【0075】

表2に示すように、実施例はいずれも、リフトオフ発生率0%、耐湿性負荷試験における絶縁抵抗劣化率0%であり、導電性ペーストを、本発明の規定する金属粉の焼結開始温度とガラスフリットのガラス転移点との関係にすれば、比較的大きな素子からなるセラミック電子部品の外部電極の形成に使用しても、耐候性に優れた、信頼性の高い外部電極を形成できることがわかった。

【0076】

一方、比較例は、リフトオフの発生、および耐湿性負荷試験における絶縁抵抗劣化が生じており、実用上問題があることがわかった。

(実験例3)

使用する導電性金属粉末をNi粉にした以外は実験例1と同様にして、積層セラミックコンデンサを作製し、その外部電極におけるリフトオフ発生率と、耐湿性負荷試験での絶縁抵抗劣化率とを調べた。その結果を表3に示す。

【0077】

【表3】

【0078】

表3に示すように、実施例はいずれも、リフトオフ発生率0%、耐湿性負荷試験における絶縁抵抗劣化率0%であり、導電性ペーストを、本発明の規定する金属粉の焼結開始温度とガラスフリットのガラス転移点との関係にすれば、比較的大きな素子からなるセラミック電子部品の外部電極の形成に使用しても、耐候性に優れた、信頼性の高い外部電極を形成できることがわかった。

【0079】

一方、比較例は、リフトオフの発生、および耐湿性負荷試験における絶縁抵抗劣化が生じており、実用上問題があることがわかった。

(実験例4)

導電性金属粉末として使用するCu粉の粒度分布を示す指標である(D90−D10)/D50を変えて、実験例1の試料番号14の条件で積層セラミックコンデンサを作製し、その外部電極の焼結密度を測定した。その結果を表4に示す。

【0080】

【表4】

【0081】

表4に示すように、(D90−D10)/D50が0.5〜1.7の範囲にあるものは、焼結密度が87%以上と十分に高い値となることがわかる。

【符号の説明】

【0082】

1:セラミック素子

2、3:内部電極

4:セラミック層

5、6:外部電極

7、8:めっき層(第1層)

9、10:めっき層(第2層)

【技術分野】

【0001】

本発明は、セラミック電子部品の外部電極などの形成に用いられる導電性ペーストに関し、さらに詳しくは、セラミック電子部品の外部電極の形成に使用した場合に、リフトオフ(セラミックからの剥離)の発生する可能性が低い導電性ペーストに関する。

【0002】

また、本発明は、上記導電性ペーストを使用した、セラミック電子部品の製造方法に関する。

【背景技術】

【0003】

従来から、セラミック電子部品の外部電極の形成方法として、特許文献1(特開2000‐40635号公報)に開示されるように、セラミック素子の表面に、導電性ペーストを塗布し、焼成する方法が一般的に用いられている。

【0004】

図2に、そのような方法で外部電極が形成されたセラミック電子部品の一例として、積層セラミックコンデンサ200を示す。

【0005】

積層セラミックコンデンサ200は、セラミック素子101を備える。

【0006】

セラミック素子101の内部には、セラミック素子101の一方の端部に引出された複数の内部電極102と、セラミック素子101の他方の端部に引出された複数の内部電極103とが、交互に、セラミック層104を介して形成されている。

【0007】

そして、セラミック素子101の一方の端部には、内部電極102と接続された外部電極105が形成され、セラミック素子101の他方の端部には、内部電極103と接続された外部電極106が形成されている。外部電極105、106は、それぞれ、セラミック素子101の端面から、その端面に続く4つの側面に跨って、キャップ状に形成されている。なお、図示しないが、外部電極105、106の表面には、さらに、はんだ付け性の向上などを目的として、めっき層が形成されることが多い。めっき層としては、たとえば、第1層としてNiめっき層、第2層としてSnめっき層が形成される。

【0008】

このような構造からなる積層セラミックコンデンサ200は、たとえば、次の方法で製造される。

【0009】

まず、誘電体セラミックで形成された、マザーグリーンシートを準備し、このマザーグリーンシートの表面に、導電性ペーストで複数個分の内部電極のパターンを形成する。そして、内部電極のパターンが形成されたマザーグリーンシートと、内部電極のパターンが形成されていないマザーグリーンシートとを、所定の枚数、所定の順番に積層し、圧着したうえで、素子単位ごとに切断し、未焼成のチップを得る。

【0010】

次に、未焼成のチップを、所定のプロファイルで焼成して、セラミック素子101を得る。

【0011】

次に、導電性金属粉末と、ガラスフリットと、ビヒクルとを含有した、外部電極用の導電性ペーストを準備し、ディッピングにより、セラミック素子101の両端に塗布し、所定のプロファイルで焼成して、外部電極105、106を形成する。導電性金属粉末としては、たとえば、Cu粉、Ni粉,Ag粉などが用いられる。なお、ガラスフリットは、外部電極のセラミック素子への密着性の向上や、外部に対するシール性の向上などのために含有されている。

【0012】

最後に、外部電極105、106の表面に、電解めっきにより、めっき層を形成して、積層セラミックコンデンサ200は完成する。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2000‐40635号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

近時、電子機器が、高温下、高湿度下など、さまざまな環境下で使用されるようになってきており、電子機器に使用されるセラミック電子部品においても、耐候性の確保が不可欠である。

【0015】

そして、セラミック電子部品の耐候性を確保するためには、外部電極を緻密な金属膜にすることが必要である。たとえば、粒度分布が比較的ブロードで、炭素などの焼結を阻害する不純物を含みにくく、焼結開始温度が低く、焼結後の金属充填密度が高いアトマイズ法で作製された導電性金属粉末を含有した導電性ペーストを使用して外部電極を形成することが有効である。

【0016】

しかしながら、焼結開始温度が低い導電性金属粉末を含有した導電性ペーストを使用してセラミック電子部品の外部電極を形成した場合、セラミック素子が小さい場合は良いが、セラミック素子が大きくなると、導電性ペーストの焼成時に、セラミック素子の側面部分において、外部電極がセラミック素子から剥離する、リフトオフと呼ばれる現象が発生することがある。

【0017】

図3は、上述した積層セラミックコンデンサ200において、外部電極106にリフトオフが発生した状態を示す。セラミック素子101の側面において、外部電極106の先端部がセラミック素子101から剥離し、隙間107が形成されている。

【0018】

特に、リフトオフは、比較的大きいセラミック素子に、外部電極を形成した場合に発生しやすい傾向がある。すなわち、セラミック素子が大きくなると、セラミック素子の端面が大きくなり、ディッピングにより導電性ペーストを塗布した場合、端面に多量の導電性ペーストが付着し、端面における導電性ペーストの膜厚が大きくなり、これに連なるセラミック素子の側面における導電性ペーストの膜厚も大きくなる。そして、セラミック素子の側面における導電性ペーストの膜厚が大きくなることにより、導電性ペーストの焼成時に、リフトオフを発生させる応力が大きくなる。

【0019】

図4に、セラミック素子101の端部に塗布された導電性ペーストを焼成して外部電極106を形成する場合に、塗布された導電性ペーストに生じる応力を矢印Fで示す。塗布された導電性ペーストには、セラミック素子101の側面における先端部と、セラミック素子101の稜線部において、引張応力が加わる。そして、上述のとおり、セラミック素子101のサイズが大きくなると、セラミック素子101の側面に塗布される導電性ペーストの膜厚が大きくなるため、この引張応力が大きくなり、リフトオフが発生してしまう。

【0020】

外部電極にリフトオフが発生すると、外部電極の表面にめっき層を形成する際に、めっき液が隙間からセラミック素子の内部に侵入して、特性が劣化するそれがある。また、隙間から、大気中の水蒸気などが侵入するおそれがあり、却って、セラミック電子部品の耐候性が低下してしまう。すなわち、外部電極のリフトオフは、セラミック電子部品を不良品とするものであり、極めて大きな問題である。

【0021】

本発明者は、鋭意検討を重ねた結果、リフトオフが発生する原因が、導電性金属粉末の焼結開始温度が、ガラスフリットのガラス転移点Tgに対して低すぎるため、ガラスフリットが軟化流動し、ガラス成分が導電性ペーストとセラミック素子とを固着してリフトオフの発生を阻止する作用を発現する前に、導電性金属粉末が焼結を開始してしまい、リフトオフにつながる応力が発生する点にあることを見出した。

【0022】

導電性ペーストには、セラミック素子との密着性を向上させるために、ガラスフリットが含有されている。しかしながら、焼結開始温度の低い導電性金属粉末を含有した導電性ペーストを使用した場合には、ガラスフリットは、有効にリフトオフの発生を阻止することができない。すなわち、比較的大きいセラミック素子に、比較的焼結開始温度が低い導電性金属粉末を含有する導電性ペーストを使用して外部電極を形成した場合に、リフトオフが発生するものと考えられる。たとえば、アトマイズ法で作製された導電性金属粉末を含有する導電性ペーストを使用してセラミック素子の端部に外部電極を形成した場合、縦1.6mm、横0.8mm、高さ0.8mmからなるサイズのセラミック電子部品においては、リフトオフは問題にならなかったが、縦2.0mm、横1.2mm、高さ1.2mmからなるサイズ以上のセラミック電子部品において、リフトオフが発生する場合があった。

【0023】

なお、比較的大きいセラミック素子に、焼結開始温度が低い導電性金属粉末を含有する導電性ペーストを使用して外部電極を形成する場合においても、リフトオフを発生させない方法として、電極ペーストの粘度を低くして、セラミック素子の側面に付着される導電性ペーストの厚みを小さくする方法が考えられる。しかしながら、導電性ペーストの粘度を小さくすると、セラミック素子の稜線部に付着する導電性ペーストの厚みが小さくなってしまい、その部分で外部電極が薄くなって耐候性が低下してしまうため、採用することができなかった。

【課題を解決するための手段】

【0024】

本発明は、上述した、従来の問題点を解消するためになされたものであり、セラミック電子部品の外部電極を形成するのに使用した場合に、リフトオフの発生がない導電性ペーストを提供することを目的とする。

【0025】

本発明の導電性ペーストは、導電性金属粉末と、ガラスフリットと、ビヒクルとを含み、前記導電性金属粉末の焼結開始温度(℃)と、前記ガラスフリットのガラス転移点Tg(℃)とが、

(ガラスフリットのTg)−(導電性金属粉末の焼結開始温度)<100

の関係を満たす。

【0026】

また、前記導電性金属粉末は、Cu、Ni、Agから選ばれる少なくとも1種とすることが好ましい。

【0027】

また、前記導電性金属粉末の内包炭素量は、0.1wt%以下であることが好ましい。この場合には、炭素による焼結の阻害を、許容範囲内に抑えることができる。

【0028】

また、前記導電性金属粉末は、アトマイズ法で作製されたものであることが好ましい。この場合には、焼結性が高いため、耐候性に優れた緻密な金属膜を形成することができる。

【0029】

また、前記導電性金属粉末のD10、D50、およびD90が、

0.5≦(D90−D10)/D50≦1.7

を満たすことが好ましい。この場合には、87%以上の高い焼結密度を実現することができる。

【0030】

また、本発明のセラミック電子部品の製造方法は、内部に内部電極を有し、該内部電極が導出された互いに対向する2つの端面と、それらの前記端面を結ぶ側面とを有するセラミック素子を形成する工程と、前記セラミック素子の両端面に、それぞれ、上記導電性ペーストをディッピングにより塗布する工程と、前記セラミック素子の両端面に塗布された導電性ペーストを、焼成し、外部電極を形成する工程とを備える。

【0031】

また、前記セラミック素子は、前記端面の面積が1.44mm2以上であることが好ましい。

【発明の効果】

【0032】

本発明の導電性ペーストは、上述の構成としたため、金属膜の緻密性を向上させるために、焼結開始温度の低い導電性金属粉末を含有させ、大きなセラミック素子、たとえば、2012サイズ以上のセラミック素子の外部電極の形成に使用しても、リフトオフが発生する可能性が低い。

【0033】

すなわち、導電性金属粉末の焼結開始温度と、ガラスフリットのガラス転移点Tgとの差を規定し、導電性金属粉末の焼結とガラスフリットの軟化流動とのタイミングを合わせているため、焼成時に、すでに液相となったガラス成分により、セラミック素子から導電性ペーストが剥離するのを抑制することができ、リフトオフの発生を有効に阻止することができる。

【図面の簡単な説明】

【0034】

【図1】本発明にかかる導電性ペーストを使用して外部電極を形成した、セラミック電子部品(積層セラミックコンデンサ)100を示す断面図である。

【図2】従来の導電性ペーストを使用して外部電極を形成した、セラミック電子部品(積層セラミックコンデンサ)200を示す断面図である。

【図3】上記従来のセラミック電子部品(積層セラミックコンデンサ)200において、外部電極にリフトオフが発生した状態を示す部分断面図である。

【図4】上記従来のセラミック電子部品(積層セラミックコンデンサ)200において、塗布された導電性ペーストを焼成して外部電極を形成する場合に、導電性ペーストに生じる応力を示した部分断面図である。

【発明を実施するための形態】

【0035】

以下、本発明を実施するための形態について説明する。

[導電性ペーストの構成]

本実施形態にかかる導電性ペーストは、導電性金属粉末、ガラスフリット、ビヒクルを含有する。

【0036】

導電性金属粉末の焼結開始温度(℃)と、ガラスフリットのガラス転移点Tg(℃)とは、

(ガラスフリットのTg)−(導電性金属粉末の焼結開始温度)<100

の関係を満たす。

[導電性ペーストの製造]

本実施形態にかかる導電性ペーストは、たとえば、次の方法により製造される。

【0037】

まず、導電性金属粉末として、溶融したCuの中に、所定量のPを投入して、水アトマイズ法によりCu粉を作製する。

【0038】

Cu粉の焼結開始温度は、Cu粉中の微量成分であるP量を変化させることにより調整することができる。なお、Cu粉の焼結開始温度は、圧粉体を、TMAで測定して求める(測定条件:10℃/分、窒素雰囲気中、室温〜1000℃)。

【0039】

アトマイズ法によれば、真球状のCu粉を得ることができるため、これを使用した導電性ペーストは、ペースト乾燥膜の金属充填率が高くなる。したがって、セラミック電子部品の外部電極の形成に使用した場合、緻密性の高い電極膜を得ることができる。また、アトマイズ法によって作製されたCu粉は、合成過程において、炭素を含有することがないため、金属膜に、Cu粉中の炭素に起因してブリスタが発生することがない。

【0040】

ガラスフリットは、軟化点が500℃〜700℃の、Si‐B‐Zn系ガラスにより作製する。ガラスの綱目構成元素は、Si、Bとし、軟化点を調整するために、アルカリ金属(Li、Naなど)を添加する。また、耐酸性を上げるために(外部電極中のガラスの耐めっき溶解性を上げるために)Tiを添加する。

【0041】

ガラスフリットのガラス転移点(Tg)は、SiとBの割合を変化させることにより調整することができる。一般的に、Bの割合が増えると、ガラス転移点は低下する。

【0042】

まず、ガラスフリットの原料として、各元素の酸化物を用意する。次に、各酸化物を所定量混合し、1500℃で、20分間、ガラス溶融炉で熱処理しながら、混合、撹拌し、その後、冷却して、ガラスを作製する。そして、作製されたガラスを乾式で粉砕し、ガラスフリットを得る。なお、得られたガラスのガラス転移点は、TG‐DTAを測定して確認する。

【0043】

ビヒクルは、アクリル樹脂を、ターピネオールを主成分とする有機溶剤に溶解させて作製する。

【0044】

以上からなる、Cu粉、ガラスフリット、ビヒクルを、それぞれ、所定量秤量し、3本ロールで分散、混合して、本実施形態にかかる導電性ペーストを得る。

【0045】

導電性ペースト中のガラス量は、固形分(Cu粉およびガラスフリット)に対して、20体積%とする。ガラス量が22体積%以上では、外部電極を形成した場合に、電極膜の表面にガラスが偏析し、めっき不良が発生する。ガラス量が18体積%以下になると、外部電極の緻密性が低下し、耐湿負荷試験において、絶縁抵抗が低下する不良がみられる。したがって、導電性ペースト中のガラス量は、固形分に対して、18体積%より多く、22体積%未満が適当である。

【0046】

導電性ペーストの粘度は、E型粘度計において、25℃、1rpmの値で、20Pa・sに調整する。粘度が10Pa・s未満では、セラミック素子の側面における導電性ペーストの厚みが小さくなり、リフトオフは抑制されるが、セラミック素子の稜線部における導電性ペーストの厚みも小さくなってしまい、その部分で外部電極の耐候性が低下してしまうため、耐湿負荷試験で、絶縁抵抗の劣化がみられる。粘度が30Pa・sより大きくなると、塗布後形状がツノ形状になり、欠き取り時にクワレも発生するため、塗布形状の安定性を確保することができず、外部電極に局所的なガラスの偏析、厚みの小さい部分、緻密性不足などが発生して、耐候性が低下する。したがって、導電性ペーストの粘度は、10Pa・s以上、30Pa・s以下が適当である。

[積層セラミックコンデンサの構造]

本実施形態においては、セラミック電子部品として、積層セラミックコンデンサ100を製造した。

【0047】

図1に、積層セラミックコンデンサ100を示す。

【0048】

積層セラミックコンデンサ100は、Ba、Tiを主成分とするセラミックからなる、直方体形状のセラミック素子1を備える。

【0049】

セラミック素子1の内部には、セラミック素子1の一方の端部に引出された複数の内部電極2と、セラミック素子1の他方の端部に引出された複数の内部電極3とが、交互に、セラミック層4を介して形成されている。内部電極2、3は、Niを主成分としている。

【0050】

セラミック素子1の一方の端部には、内部電極2と接続された外部電極5が形成されている。セラミック素子1の他方の端部には、内部電極3と接続された外部電極6が形成されている。外部電極5、6は、それぞれ、セラミック素子1の端面から、その端面に続く4つの側面に跨って、キャップ状に形成されている。この外部電極5、6は、上述した、本発明にかかる導電性ペーストを使用して形成されている。

【0051】

外部電極5、6上には、それぞれ、2層からなるめっき層が形成されている。まず、第1層として、Niめっき層7、8が形成されている。Niめっき層7、8は、実装時のはんだクワレを抑制するために形成されたものである。そして、Niめっき層7、8上には、第2層として、それぞれ、Snめっき層9、10が形成されている。Snめっき層9、10は、はんだ付け性を向上させるために形成されたものである。

[積層セラミックコンデンサの製造]

積層セラミックコンデンサ100は、たとえば、次の方法で製造される。

【0052】

まず、Ba、Tiを主成分とする誘電体セラミックで形成された、複数の素子用の大きなマザーグリーンシートを複数枚準備する。

【0053】

次に、複数枚のマザーグリーンシートのうち所定枚数のマザーグリーンシートの表面に、Niを主成分とする内部電極用の導電性ペーストで、内部電極のパターンを形成する。

【0054】

次に、内部電極のパターンが形成されたマザーグリーンシートと、内部電極のパターンが形成されていないマザーグリーンシートとを、所定の枚数、所定の順番に積層し、圧着したうえで、切断し、個々の未焼成のチップを得る。

【0055】

次に、未焼成のチップを、バッチ炉を使用して、還元性雰囲気中において、所定のプロファイルで焼成して、セラミック素子1を得る。

【0056】

次に、上述した、本発明にかかる導電性ペーストを、ディッピングにより、セラミック素子1の両端面に塗布する。セラミック素子1が、縦2.0mm、横1.2mm、高さ1.2mmのサイズ(端面の面積=1.44mm2)場合には、塗布された導電性ペーストの膜厚は、セラミック素子1の端面において最大80μm程度、側面において最大40μm程度になる。

【0057】

次に、導電性ペーストを塗布したセラミック素子1を、ベルト炉を使用して、中性から還元性雰囲気中において、最高温度800℃〜900℃を10分間保持し、外部電極5、6を形成する。

【0058】

最後に、外部電極5、6上に、電解めっきにより、Niめっき層7、8を形成し、さらにNiめっき層7、8上に、同じく電解めっきにより、Snめっき層9、10を形成し、積層セラミックコンデンサ100を完成させる。

【0059】

以上、本発明の実施形態にかかる導電性ペースト、電子部品(積層セラミックコンデンサ)の製造方法について説明した。しかしながら、本発明が上述の内容に限定されることはなく、本発明の主旨に沿って、種々の変形をなすことができる。

【0060】

たとえば、導電ペーストの導電性金属粉末にCu粉を用いたが、これに代えて、たとえば、Ni粉、Ag粉、Au粉などを用いても良い。

【0061】

また、ガラスフリットの主材料、添加物、ビヒクル、溶剤なども任意であり、上述のものには限定されない。

【0062】

また、製造されるセラミック電子部品も、コンデンサに代えて、たとえば、コイル、抵抗、サーミスタなどであっても良い。さらに、外部電極の表面にめっき層を形成するか否か、形成する場合の種類や層数なども任意であり、上述した内容には限定されない。

【実験例】

【0063】

(実験例1)

本発明の効果を確認するため、次の実験をおこなった。

【0064】

導電性金属粉末としてCu粉を用い、このCu粉の焼結開始温度と、ガラスフリットのガラス転移点(Tg)とを変化させ、他の条件は上述した実施形態と同じにして、40種類の導電性ペーストを作製した。

【0065】

Cu粉の焼結開始温度は、500℃、550℃、600℃、650℃に変化させた。なお、焼結開始温度の変化は、上述のとおり、Pの添加量を変化させることによりおこなった。

【0066】

ガラスフリットのガラス転移点は、500℃、550℃、595℃、600℃、645℃、650℃、695℃、700℃、745℃、750℃に変化させた。なお、ガラス転移点の変化は、上述のとおり、ガラスの綱目構成元素である、Si、Bの割合を変化させることによりおこなった。

【0067】

これらの40種類の導電性ペーストを外部電極の形成に使用して、上述した実施形態と同じ方法で、縦2.0mm、横1.2mm、高さ1.2mmのサイズの積層セラミックコンデンサを製造した。そして、各積層セラミックコンデンサについて、外部電極におけるリフトオフ発生率と、耐湿性負荷試験での絶縁抵抗劣化率とを調べた。

【0068】

リフトオフ発生率は、セラミック素子の側面における外部電極の先端を観察し、一部にでもセラミック素子からの剥離のあるものをリフトオフ発生として、リフトオフ発生率を算出した(n=1000)。

【0069】

耐湿性負荷試験での絶縁抵抗劣化率は、70℃、相対湿度95%、6.3Vの条件で、1000時間放置し、絶縁抵抗をモニタリングし、絶縁抵抗が106Ωを下回ったものを絶縁抵抗劣化として、絶縁抵抗劣化率を算出した(n=70)。

【0070】

表1に、各積層セラミックコンデンサの、リフトオフ発生率と、耐湿性負荷試験での絶縁抵抗劣化率とを示す。なお、表1において、※の付されていないものが本発明にかかる実施例、※の付されたものが本発明の範囲外の比較例である。

【0071】

【表1】

【0072】

実施例はいずれも、リフトオフ発生率0%、耐湿性負荷試験における絶縁抵抗劣化率0%であり、導電性ペーストを、本発明の規定する金属粉の焼結開始温度とガラスフリットのガラス転移点との関係にすれば、比較的大きな素子からなるセラミック電子部品の外部電極の形成に使用しても、耐候性に優れた、信頼性の高い外部電極を形成できることがわかった。

【0073】

一方、比較例は、リフトオフの発生、および耐湿性負荷試験における絶縁抵抗劣化が生じており、実用上問題があることがわかった。

(実験例2)

使用する導電性金属粉末をAg粉にした以外は実験例1と同様にして、積層セラミックコンデンサを作製し、その外部電極におけるリフトオフ発生率と、耐湿性負荷試験での絶縁抵抗劣化率とを調べた。その結果を表2に示す。

【0074】

【表2】

【0075】

表2に示すように、実施例はいずれも、リフトオフ発生率0%、耐湿性負荷試験における絶縁抵抗劣化率0%であり、導電性ペーストを、本発明の規定する金属粉の焼結開始温度とガラスフリットのガラス転移点との関係にすれば、比較的大きな素子からなるセラミック電子部品の外部電極の形成に使用しても、耐候性に優れた、信頼性の高い外部電極を形成できることがわかった。

【0076】

一方、比較例は、リフトオフの発生、および耐湿性負荷試験における絶縁抵抗劣化が生じており、実用上問題があることがわかった。

(実験例3)

使用する導電性金属粉末をNi粉にした以外は実験例1と同様にして、積層セラミックコンデンサを作製し、その外部電極におけるリフトオフ発生率と、耐湿性負荷試験での絶縁抵抗劣化率とを調べた。その結果を表3に示す。

【0077】

【表3】

【0078】

表3に示すように、実施例はいずれも、リフトオフ発生率0%、耐湿性負荷試験における絶縁抵抗劣化率0%であり、導電性ペーストを、本発明の規定する金属粉の焼結開始温度とガラスフリットのガラス転移点との関係にすれば、比較的大きな素子からなるセラミック電子部品の外部電極の形成に使用しても、耐候性に優れた、信頼性の高い外部電極を形成できることがわかった。

【0079】

一方、比較例は、リフトオフの発生、および耐湿性負荷試験における絶縁抵抗劣化が生じており、実用上問題があることがわかった。

(実験例4)

導電性金属粉末として使用するCu粉の粒度分布を示す指標である(D90−D10)/D50を変えて、実験例1の試料番号14の条件で積層セラミックコンデンサを作製し、その外部電極の焼結密度を測定した。その結果を表4に示す。

【0080】

【表4】

【0081】

表4に示すように、(D90−D10)/D50が0.5〜1.7の範囲にあるものは、焼結密度が87%以上と十分に高い値となることがわかる。

【符号の説明】

【0082】

1:セラミック素子

2、3:内部電極

4:セラミック層

5、6:外部電極

7、8:めっき層(第1層)

9、10:めっき層(第2層)

【特許請求の範囲】

【請求項1】

導電性金属粉末と、

ガラスフリットと、

ビヒクルと、を含んでなる導電性ペーストであって、

前記導電性金属粉末の焼結開始温度(℃)と、前記ガラスフリットのガラス転移点Tg(℃)とが、

(ガラスフリットのTg)−(導電性金属粉末の焼結開始温度)<100

の関係を満たす導電性ペースト。

【請求項2】

前記導電性金属粉末が、Cu、Ni、Agから選ばれる少なくとも1種である、請求項1に記載された導電性ペースト。

【請求項3】

前記導電性金属粉末の内包炭素量が、0.1wt%以下である、請求項1または2に記載された導電性ペースト。

【請求項4】

前記導電性金属粉末が、アトマイズ法で作製されたものである、請求項1ないし3のいずれか1項に記載された導電性ペースト。

【請求項5】

前記導電性金属粉末のD10、D50、およびD90が、

0.5≦(D90−D10)/D50≦1.7

を満たす、請求項1ないし4のいずれか1項に記載された導電性ペースト。

【請求項6】

内部に内部電極を有し、該内部電極が導出された互いに対向する2つの端面と、前記端面を結ぶ側面とを有するセラミック素子を形成する工程と、

前記セラミック素子の両端面に、それぞれ、請求項1ないし5のいずれか1項に記載された導電性ペーストをディッピングにより塗布する工程と、

前記セラミック素子の両端面に塗布された前記導電性ペーストを、焼成し、外部電極を形成する工程とを備えた、セラミック電子部品の製造方法。

【請求項7】

前記セラミック素子は、前記端面の面積が1.44mm2以上である、請求項6に記載のセラミック電子部品の製造方法。

【請求項1】

導電性金属粉末と、

ガラスフリットと、

ビヒクルと、を含んでなる導電性ペーストであって、

前記導電性金属粉末の焼結開始温度(℃)と、前記ガラスフリットのガラス転移点Tg(℃)とが、

(ガラスフリットのTg)−(導電性金属粉末の焼結開始温度)<100

の関係を満たす導電性ペースト。

【請求項2】

前記導電性金属粉末が、Cu、Ni、Agから選ばれる少なくとも1種である、請求項1に記載された導電性ペースト。

【請求項3】

前記導電性金属粉末の内包炭素量が、0.1wt%以下である、請求項1または2に記載された導電性ペースト。

【請求項4】

前記導電性金属粉末が、アトマイズ法で作製されたものである、請求項1ないし3のいずれか1項に記載された導電性ペースト。

【請求項5】

前記導電性金属粉末のD10、D50、およびD90が、

0.5≦(D90−D10)/D50≦1.7

を満たす、請求項1ないし4のいずれか1項に記載された導電性ペースト。

【請求項6】

内部に内部電極を有し、該内部電極が導出された互いに対向する2つの端面と、前記端面を結ぶ側面とを有するセラミック素子を形成する工程と、

前記セラミック素子の両端面に、それぞれ、請求項1ないし5のいずれか1項に記載された導電性ペーストをディッピングにより塗布する工程と、

前記セラミック素子の両端面に塗布された前記導電性ペーストを、焼成し、外部電極を形成する工程とを備えた、セラミック電子部品の製造方法。

【請求項7】

前記セラミック素子は、前記端面の面積が1.44mm2以上である、請求項6に記載のセラミック電子部品の製造方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2011−192608(P2011−192608A)

【公開日】平成23年9月29日(2011.9.29)

【国際特許分類】

【出願番号】特願2010−59721(P2010−59721)

【出願日】平成22年3月16日(2010.3.16)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成23年9月29日(2011.9.29)

【国際特許分類】

【出願日】平成22年3月16日(2010.3.16)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]