導電性ペーストおよびセラミック電子部品

【課題】未焼結のセラミック素体と同時焼成されるものであって、導体の焼結開始を遅らせる効果を有しつつ、導体の比抵抗を低くすることができる、導電性ペーストを提供する。

【解決手段】Al量が0.05〜0.15重量%であるCu−Al合金粉末を含有する、導電性ペースト。この導電性ペーストは、好ましくは、未焼結のセラミック素体と同時焼成される用途に向けられ、たとえば、多層セラミック基板1の端子電極5,7、内部導体膜8およびビアホール導体9といった導体を形成するために有利に用いられる。

【解決手段】Al量が0.05〜0.15重量%であるCu−Al合金粉末を含有する、導電性ペースト。この導電性ペーストは、好ましくは、未焼結のセラミック素体と同時焼成される用途に向けられ、たとえば、多層セラミック基板1の端子電極5,7、内部導体膜8およびビアホール導体9といった導体を形成するために有利に用いられる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、導電性ペーストおよびセラミック電子部品に関するもので、特に、Cu−Al合金粉末を含有する導電性ペースト、およびこの導電性ペーストの焼結体を導体として備えるセラミック電子部品に関するものである。

【背景技術】

【0002】

導電性ペーストは、セラミック電子部品に備える導体を形成するために用いられている。たとえば、セラミック電子部品の表面に設けられる端子電極やライン電極のような外部導体を形成するため、また、多層セラミック基板のような積層型セラミック電子部品の場合には、さらに内部に設けられる内部導体膜やビアホール導体のような内部導体を形成するため、導電性ペーストが用いられている。

【0003】

セラミック電子部品を製造するにあたり、上述した内部導体は、当然、セラミック電子部品のセラミック素体と同時焼成される。また、外部導体にあっても、セラミック素体と同時焼成されることが多い。しかし、同時焼成の場合には、導体がセラミック素体より先に焼結し、よって、先に収縮してしまうため、デラミネーションやクラックが生じるといった問題を招くことがある。

【0004】

この問題を解決するために、従来から、導体の焼結開始を遅らせることによって、導体の焼結タイミングをセラミック素体の焼結タイミングに近づける技術が提案されている。

【0005】

具体的には、たとえば特開2000−173346号公報(特許文献1)および特開2005−116337号公報(特許文献2)に記載されるように、導電性ペーストにアルミナ等のセラミック粉末を添加する技術が提案されたり、あるいは、たとえば特開2004−362822号公報(特許文献3)に記載されるように、導電性ペーストに含まれる金属粉末の表面をセラミック層でコーティングする技術が提案されたりしている。

【0006】

しかし、特許文献1〜3の記載の技術は、いずれを採用しても、焼結開始を遅らせる効果を十分に得るためには、導電性ペーストにおいて、セラミック成分の量を比較的多くしなければならないため、金属成分の比率が少なくなり、焼成後の導体の比抵抗が高くなってしまうという問題、言い換えると、焼成後の導体の比抵抗を低くすることができないという問題に遭遇する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000−173346号公報

【特許文献2】特開2005−116337号公報

【特許文献3】特開2004−362822号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

そこで、この発明の目的は、導体の焼結開始を遅らせる効果を有しつつ、導体の比抵抗を低くすることができる、導電性ペーストを提供しようとすることである。

【0009】

この発明の他の目的は、上述した導電性ペーストを用いて構成されるセラミック電子部品を提供しようとすることである。

【課題を解決するための手段】

【0010】

この発明に係る導電性ペーストは、上述した技術的課題を解決するため、Al量が0.05〜0.15重量%であるCu−Al合金粉末を含有することを特徴とするものである。

【0011】

この発明に係る導電性ペーストは、未焼結のセラミック素体と同時焼成される用途に向けられることが好ましい。

【0012】

また、この発明に係る導電性ペーストは、Cuが酸化されず、Alが酸化される酸素濃度を有する雰囲気下で焼成されることが好ましい。

【0013】

この発明に係るセラミック電子部品は、セラミック素体と、セラミック素体の表面および/または内部に設けられた導体とを備え、導体が、上記導電性ペーストの焼結体からなることを特徴としている。

【発明の効果】

【0014】

この発明に係る導電性ペーストによれば、焼成工程中において、Alが酸化することによって、Al2O3となり、このAl2O3がCu−Al合金粉末の各粒子の表面に出てきて、焼結開始温度を上げるように作用するものと推測される。すなわち、焼成前の原料の段階からCu粉末の各粒子の表面をAl2O3でコートした場合と同じ効果が得られる。その結果、導電性ペーストに由来する導体の焼結開始を遅らせることができる。

【0015】

したがって、導体の焼結タイミングをセラミック素体の焼結タイミングに近づけることができるため、この導電性ペーストとセラミック素体とが同時焼成されて得られるセラミック電子部品において、デラミネーションやクラックのような構造欠陥を生じにくくすることができる。

【0016】

また、この発明に係る導電性ペーストによれば、Cu−Al合金粉末中のAl添加量が0.15重量%以下と少ないため、導電性ペーストの焼結体からなる導体の比抵抗を低くすることができる。

【0017】

したがって、この導電性ペーストの焼結体からなる導体を備えるセラミック電子部品において、優れた高周波特性を得ることができる。

【図面の簡単な説明】

【0018】

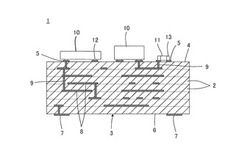

【図1】この発明に係る導電性ペーストの焼結体からなる導体を備えるセラミック電子部品の一例としての多層セラミック基板を図解的に示す断面図である。

【図2】実験例において作製された試料に形成されたライン電極パターンを示す平面図である。

【発明を実施するための形態】

【0019】

図1を参照して、この発明に係る導電性ペーストの焼結体からなる導体を備えるセラミック電子部品の一例としての多層セラミック基板1について説明する。

【0020】

多層セラミック基板1は、積層された複数のセラミック層2をもって構成されるセラミック素体3を備えている。このセラミック素体3の表面には外部導体が設けられ、セラミック素体3の内部には内部導体が設けられている。

【0021】

外部導体としては、セラミック素体3の上方主面4に設けられるいくつかの端子電極5と、セラミック素体3の下方主面6に設けられるいくつかの端子電極7とが図示されている。

【0022】

また、内部導体としては、セラミック層2の間の特定の界面に沿って設けられるいくつかの内部導体膜8と、セラミック層2の特定のものを貫通するように設けられるいくつかのビアホール導体9とが図示されている。

【0023】

セラミック素体3の上方主面4に設けられた端子電極5は、セラミック素体3上に搭載されるべき電子部品10および11への接続のために用いられる。図1では、たとえば半導体デバイスのように、バンプ電極12を備える電子部品10、およびたとえばチップコンデンサのように面状の端子電極13を備える電子部品11が図示されている。また、セラミック素体3の下方主面6に設けられた端子電極7は、この多層セラミック基板1を実装するマザーボード(図示せず)への接続のために用いられる。

【0024】

このような多層セラミック基板1は、複数のセラミック層2となるべき積層された複数のセラミックグリーン層と、導電性ペーストによって形成された端子電極5および7のような外部導体ならびに内部導体膜8およびビアホール導体9のような内部導体とを備えた、積層構造の生のセラミック素体3を同時焼成することによって得られるものである。上述した複数のセラミックグリーン層の積層構造は、典型的には、セラミックスラリーを成形して得られた複数枚のセラミックグリーンシートを積層することによって与えられる。

【0025】

この多層セラミック基板1において、端子電極5および7のような外部導体ならびに内部導体膜8およびビアホール導体9のような内部導体が、この発明に係る導電性ペーストの焼結体から構成される。導電性ペーストは、Al量が0.05〜0.15重量%であるCu−Al合金粉末を含有するものである。

【0026】

この導電性ペーストによる効果は、後述する実験例において確認することができるが、この導電性ペーストによれば、当該導電性ペーストによって形成された外部導体および内部導体の焼結開始を遅らせることができ、これら外部導体および内部導体の焼結タイミングを、これらと同時焼成されるセラミック素体3の焼結タイミングに近づけることができる。したがって、得られた多層セラミック基板1において、デラミネーションやクラックのような構造欠陥を生じにくくすることができる。

【0027】

また、この発明に係る導電性ペーストによれば、Cu−Al合金粉末中のAl添加量が0.15重量%以下と少ないため、端子電極5および7のような外部導体ならびに内部導体膜8およびビアホール導体9のような内部導体の比抵抗を低くすることができる。したがって、多層セラミック基板1において、優れた高周波特性を得ることができる。

【0028】

以上、この発明の実施形態を多層セラミック基板に関連して説明したが、この発明は、多層セラミック基板に限らず、他のセラミック電子部品に対しても適用することができる。特に、この発明に係る導電性ペーストは、どのようなセラミック電子部品においても、未焼結のセラミック素体と同時焼成される用途であれば、いずれの用途であっても、有利に適用することができる。

【0029】

次に、この発明による効果を確認するために実施した実験例について説明する。

【0030】

[実験例]

(1)セラミックグリーンシートの作製

SiO2、BaCO3、Al2O3、ZrO2、TiO2、MnCO3、およびMg(OH)2の各粉末を出発原料粉末とし、これら粉末を湿式混合粉砕し、乾燥した。次に、得られた混合物を1000℃の温度で3時間仮焼して仮焼粉を得た。

【0031】

次に、仮焼粉に、ブチラール樹脂およびDOP(フタル酸ジオクチル)を加えて、セラミックスラリーを作製し、混合粉砕した。

【0032】

次に、セラミックスラリーをドクターブレード法によってシート状に成形し、次いで乾燥することによって、セラミックグリーンシートを得た。

【0033】

(2)導電性ペーストの作製

平均粒径0.5μmの金属粉末58.6重量%と、溶剤36.7重量%と、エトセル樹脂4.7重量%とを混合して、導電性ペーストを作製した。

【0034】

ここで、上記金属粉末として、表1に示すように、Cuに対するAl添加量を0〜0.2重量%の範囲で変え、アトマイズ法によって作製したCu系粉末を用いた。

【0035】

【表1】

【0036】

表1において、ペースト記号に*を付したものは、この発明の範囲外の導電性ペーストである。

【0037】

(3)導電性ペーストの印刷

表1に示した導電性ペーストを用いて、スクリーン印刷により、前述のセラミックグリーンシート上に、図2に示すようなライン電極21を形成した。ライン電極21の幅は、図2に示すように、75μmであり、また、ライン電極21の長さは575mmであった。

【0038】

(4)セラミックグリーンシートの積層・圧着

次に、上記ライン電極を形成したセラミックグリーンシートが表層部に位置するよう、複数のセラミックグリーンシートを積層し、熱圧着を施し、生の積層体を得た。

【0039】

(5)積層体の焼成

次に、生の積層体を、N2−H2−H2Oからなる非酸化性雰囲気下で焼成し、評価すべき試料を得た。

【0040】

焼成にあたっては、Cuが酸化せず、Alが酸化する酸素濃度で焼成することが好ましい。

【0041】

なお、上記各金属が温度T(K)において酸化する酸素分圧は、以下の式により算出した。

・ln(CuPO2)>{-338904+(-33TlogT)+247T}/(8.314T)

・ln(AlPO2)>{-1117993+(-11TlogT)+244T}/(8.314T)

(6)評価

上記試料について、以下のようにして、断線率および比抵抗値を評価した。

【0042】

(6)−1.断線率評価

得られた試料のライン電極の断線率を測定した。すなわち、ライン電極の端部2箇所をテスターで押さえ、導通が取れなかったものを断線と判定し、ライン電極125本中の断線率を求めた。その結果が、表2の「断線率」の欄に示されている。

【0043】

また、断線率が15%未満のものを断線率が低いと評価し、表2の「断線率評価」の欄に「○」と表示し、他方、断線率が15%以上のものを断線率が高いと評価し、表2の「断線率評価」の欄に「×」と表示した。

【0044】

(6)−2.比抵抗値評価

得られた試料の抵抗値を測定した。すなわち、ライン電極の端部2箇所をテスターで押さえ、抵抗値を測定した。また、ライン電極の断面を研磨によって露出させ、その断面積を測定した。これら測定された抵抗値および断面積ならびにライン電極の長さから、以下の式に基づき、比抵抗値を算出した。

【0045】

Rdc=ρ・L/S

ただし、Rdc:抵抗値、ρ:比抵抗値、L:長さ、S:断面積。

【0046】

比抵抗値の結果が、表2の「比抵抗値」の欄に示されている。

【0047】

また、比抵抗値が2.5μΩ・cm未満のものを比抵抗値が低いと評価し、表2の「比抵抗値評価」の欄に「○」と表示し、他方、比抵抗値が2.5μΩ・cm以上のものを比抵抗値が高いと評価し、表2の「比抵抗値評価」の欄に「×」と表示した。

【0048】

(6)−3.総合評価

表2の「総合評価」の欄において、上記「断線率評価」および「比抵抗値評価」の双方が「○」となった試料については「○」と表示され、「断線率評価」および「比抵抗値評価」のいずれかが「×」となった試料については「×」と表示されている。

【0049】

【表2】

【0050】

表2において、試料番号に*を付したものは、この発明の範囲外の試料である。表2から、以下のことがわかった。

【0051】

この発明の範囲外の試料1および2では、「断線率」が15%以上と高く、「断線率評価」が「×」となり、応じて「総合評価」が「×」となった。これは、試料1および2では、それぞれ、表1に示したペーストP−1およびP−2を用いており、Alを含有しないか、Al添加量が0.05重量%未満と少ないため、焼成中にAlが酸化してAl2O3となってCu系粉末の粒子表面に出てくる量が少なく、Cu系粉末に対する焼結遅延作用が不十分であったことが原因であると推測される。

【0052】

また、この発明の範囲外の試料7では、「比抵抗値」が2.5μΩ・cm以上と高く、「比抵抗値評価」が「×」となり、応じて「総合評価」が「×」となった。これは、試料7では、表1に示したペーストP−7を用いており、Al含有量が0.15重量%を超えるため、焼成中にAlが酸化してAl2O3となってCu系粉末の粒子表面に出てくる量が多くなりすぎ、ライン電極が疎になったことが原因であると推測される。

【0053】

これらに対して、この発明の範囲内の試料3〜6では、「断線率」が15%未満と低く、「断線率評価」が「○」となるとともに、「比抵抗値」が2.5μΩ・cm未満と低く、「比抵抗値評価」が「○」となり、応じて「総合評価」が「○」となった。

【0054】

試料3〜6では、それぞれ、表1に示したペーストP−3〜P−6を用いており、Al添加量が0.05〜0.15重量%の範囲にある。ここで、まず、Al添加量が0.05重量%以上であるため、焼成中にAlが酸化してAl2O3となってCu系粉末の粒子表面に十分出てくることができ、したがって、Cu系粉末に対する焼結遅延作用が十分に働いて、「断線率評価」が「○」となったものと推測される。他方、Al添加量が0.15重量%以下であるため、比抵抗値がそれほど高くはならず、「比抵抗値評価」が「○」となったものと推測される。

【符号の説明】

【0055】

1 多層セラミック基板

2 セラミック層

3 セラミック素体

5,7 端子電極

8 内部導体膜

9 ビアホール導体

21 ライン電極

【技術分野】

【0001】

この発明は、導電性ペーストおよびセラミック電子部品に関するもので、特に、Cu−Al合金粉末を含有する導電性ペースト、およびこの導電性ペーストの焼結体を導体として備えるセラミック電子部品に関するものである。

【背景技術】

【0002】

導電性ペーストは、セラミック電子部品に備える導体を形成するために用いられている。たとえば、セラミック電子部品の表面に設けられる端子電極やライン電極のような外部導体を形成するため、また、多層セラミック基板のような積層型セラミック電子部品の場合には、さらに内部に設けられる内部導体膜やビアホール導体のような内部導体を形成するため、導電性ペーストが用いられている。

【0003】

セラミック電子部品を製造するにあたり、上述した内部導体は、当然、セラミック電子部品のセラミック素体と同時焼成される。また、外部導体にあっても、セラミック素体と同時焼成されることが多い。しかし、同時焼成の場合には、導体がセラミック素体より先に焼結し、よって、先に収縮してしまうため、デラミネーションやクラックが生じるといった問題を招くことがある。

【0004】

この問題を解決するために、従来から、導体の焼結開始を遅らせることによって、導体の焼結タイミングをセラミック素体の焼結タイミングに近づける技術が提案されている。

【0005】

具体的には、たとえば特開2000−173346号公報(特許文献1)および特開2005−116337号公報(特許文献2)に記載されるように、導電性ペーストにアルミナ等のセラミック粉末を添加する技術が提案されたり、あるいは、たとえば特開2004−362822号公報(特許文献3)に記載されるように、導電性ペーストに含まれる金属粉末の表面をセラミック層でコーティングする技術が提案されたりしている。

【0006】

しかし、特許文献1〜3の記載の技術は、いずれを採用しても、焼結開始を遅らせる効果を十分に得るためには、導電性ペーストにおいて、セラミック成分の量を比較的多くしなければならないため、金属成分の比率が少なくなり、焼成後の導体の比抵抗が高くなってしまうという問題、言い換えると、焼成後の導体の比抵抗を低くすることができないという問題に遭遇する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000−173346号公報

【特許文献2】特開2005−116337号公報

【特許文献3】特開2004−362822号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

そこで、この発明の目的は、導体の焼結開始を遅らせる効果を有しつつ、導体の比抵抗を低くすることができる、導電性ペーストを提供しようとすることである。

【0009】

この発明の他の目的は、上述した導電性ペーストを用いて構成されるセラミック電子部品を提供しようとすることである。

【課題を解決するための手段】

【0010】

この発明に係る導電性ペーストは、上述した技術的課題を解決するため、Al量が0.05〜0.15重量%であるCu−Al合金粉末を含有することを特徴とするものである。

【0011】

この発明に係る導電性ペーストは、未焼結のセラミック素体と同時焼成される用途に向けられることが好ましい。

【0012】

また、この発明に係る導電性ペーストは、Cuが酸化されず、Alが酸化される酸素濃度を有する雰囲気下で焼成されることが好ましい。

【0013】

この発明に係るセラミック電子部品は、セラミック素体と、セラミック素体の表面および/または内部に設けられた導体とを備え、導体が、上記導電性ペーストの焼結体からなることを特徴としている。

【発明の効果】

【0014】

この発明に係る導電性ペーストによれば、焼成工程中において、Alが酸化することによって、Al2O3となり、このAl2O3がCu−Al合金粉末の各粒子の表面に出てきて、焼結開始温度を上げるように作用するものと推測される。すなわち、焼成前の原料の段階からCu粉末の各粒子の表面をAl2O3でコートした場合と同じ効果が得られる。その結果、導電性ペーストに由来する導体の焼結開始を遅らせることができる。

【0015】

したがって、導体の焼結タイミングをセラミック素体の焼結タイミングに近づけることができるため、この導電性ペーストとセラミック素体とが同時焼成されて得られるセラミック電子部品において、デラミネーションやクラックのような構造欠陥を生じにくくすることができる。

【0016】

また、この発明に係る導電性ペーストによれば、Cu−Al合金粉末中のAl添加量が0.15重量%以下と少ないため、導電性ペーストの焼結体からなる導体の比抵抗を低くすることができる。

【0017】

したがって、この導電性ペーストの焼結体からなる導体を備えるセラミック電子部品において、優れた高周波特性を得ることができる。

【図面の簡単な説明】

【0018】

【図1】この発明に係る導電性ペーストの焼結体からなる導体を備えるセラミック電子部品の一例としての多層セラミック基板を図解的に示す断面図である。

【図2】実験例において作製された試料に形成されたライン電極パターンを示す平面図である。

【発明を実施するための形態】

【0019】

図1を参照して、この発明に係る導電性ペーストの焼結体からなる導体を備えるセラミック電子部品の一例としての多層セラミック基板1について説明する。

【0020】

多層セラミック基板1は、積層された複数のセラミック層2をもって構成されるセラミック素体3を備えている。このセラミック素体3の表面には外部導体が設けられ、セラミック素体3の内部には内部導体が設けられている。

【0021】

外部導体としては、セラミック素体3の上方主面4に設けられるいくつかの端子電極5と、セラミック素体3の下方主面6に設けられるいくつかの端子電極7とが図示されている。

【0022】

また、内部導体としては、セラミック層2の間の特定の界面に沿って設けられるいくつかの内部導体膜8と、セラミック層2の特定のものを貫通するように設けられるいくつかのビアホール導体9とが図示されている。

【0023】

セラミック素体3の上方主面4に設けられた端子電極5は、セラミック素体3上に搭載されるべき電子部品10および11への接続のために用いられる。図1では、たとえば半導体デバイスのように、バンプ電極12を備える電子部品10、およびたとえばチップコンデンサのように面状の端子電極13を備える電子部品11が図示されている。また、セラミック素体3の下方主面6に設けられた端子電極7は、この多層セラミック基板1を実装するマザーボード(図示せず)への接続のために用いられる。

【0024】

このような多層セラミック基板1は、複数のセラミック層2となるべき積層された複数のセラミックグリーン層と、導電性ペーストによって形成された端子電極5および7のような外部導体ならびに内部導体膜8およびビアホール導体9のような内部導体とを備えた、積層構造の生のセラミック素体3を同時焼成することによって得られるものである。上述した複数のセラミックグリーン層の積層構造は、典型的には、セラミックスラリーを成形して得られた複数枚のセラミックグリーンシートを積層することによって与えられる。

【0025】

この多層セラミック基板1において、端子電極5および7のような外部導体ならびに内部導体膜8およびビアホール導体9のような内部導体が、この発明に係る導電性ペーストの焼結体から構成される。導電性ペーストは、Al量が0.05〜0.15重量%であるCu−Al合金粉末を含有するものである。

【0026】

この導電性ペーストによる効果は、後述する実験例において確認することができるが、この導電性ペーストによれば、当該導電性ペーストによって形成された外部導体および内部導体の焼結開始を遅らせることができ、これら外部導体および内部導体の焼結タイミングを、これらと同時焼成されるセラミック素体3の焼結タイミングに近づけることができる。したがって、得られた多層セラミック基板1において、デラミネーションやクラックのような構造欠陥を生じにくくすることができる。

【0027】

また、この発明に係る導電性ペーストによれば、Cu−Al合金粉末中のAl添加量が0.15重量%以下と少ないため、端子電極5および7のような外部導体ならびに内部導体膜8およびビアホール導体9のような内部導体の比抵抗を低くすることができる。したがって、多層セラミック基板1において、優れた高周波特性を得ることができる。

【0028】

以上、この発明の実施形態を多層セラミック基板に関連して説明したが、この発明は、多層セラミック基板に限らず、他のセラミック電子部品に対しても適用することができる。特に、この発明に係る導電性ペーストは、どのようなセラミック電子部品においても、未焼結のセラミック素体と同時焼成される用途であれば、いずれの用途であっても、有利に適用することができる。

【0029】

次に、この発明による効果を確認するために実施した実験例について説明する。

【0030】

[実験例]

(1)セラミックグリーンシートの作製

SiO2、BaCO3、Al2O3、ZrO2、TiO2、MnCO3、およびMg(OH)2の各粉末を出発原料粉末とし、これら粉末を湿式混合粉砕し、乾燥した。次に、得られた混合物を1000℃の温度で3時間仮焼して仮焼粉を得た。

【0031】

次に、仮焼粉に、ブチラール樹脂およびDOP(フタル酸ジオクチル)を加えて、セラミックスラリーを作製し、混合粉砕した。

【0032】

次に、セラミックスラリーをドクターブレード法によってシート状に成形し、次いで乾燥することによって、セラミックグリーンシートを得た。

【0033】

(2)導電性ペーストの作製

平均粒径0.5μmの金属粉末58.6重量%と、溶剤36.7重量%と、エトセル樹脂4.7重量%とを混合して、導電性ペーストを作製した。

【0034】

ここで、上記金属粉末として、表1に示すように、Cuに対するAl添加量を0〜0.2重量%の範囲で変え、アトマイズ法によって作製したCu系粉末を用いた。

【0035】

【表1】

【0036】

表1において、ペースト記号に*を付したものは、この発明の範囲外の導電性ペーストである。

【0037】

(3)導電性ペーストの印刷

表1に示した導電性ペーストを用いて、スクリーン印刷により、前述のセラミックグリーンシート上に、図2に示すようなライン電極21を形成した。ライン電極21の幅は、図2に示すように、75μmであり、また、ライン電極21の長さは575mmであった。

【0038】

(4)セラミックグリーンシートの積層・圧着

次に、上記ライン電極を形成したセラミックグリーンシートが表層部に位置するよう、複数のセラミックグリーンシートを積層し、熱圧着を施し、生の積層体を得た。

【0039】

(5)積層体の焼成

次に、生の積層体を、N2−H2−H2Oからなる非酸化性雰囲気下で焼成し、評価すべき試料を得た。

【0040】

焼成にあたっては、Cuが酸化せず、Alが酸化する酸素濃度で焼成することが好ましい。

【0041】

なお、上記各金属が温度T(K)において酸化する酸素分圧は、以下の式により算出した。

・ln(CuPO2)>{-338904+(-33TlogT)+247T}/(8.314T)

・ln(AlPO2)>{-1117993+(-11TlogT)+244T}/(8.314T)

(6)評価

上記試料について、以下のようにして、断線率および比抵抗値を評価した。

【0042】

(6)−1.断線率評価

得られた試料のライン電極の断線率を測定した。すなわち、ライン電極の端部2箇所をテスターで押さえ、導通が取れなかったものを断線と判定し、ライン電極125本中の断線率を求めた。その結果が、表2の「断線率」の欄に示されている。

【0043】

また、断線率が15%未満のものを断線率が低いと評価し、表2の「断線率評価」の欄に「○」と表示し、他方、断線率が15%以上のものを断線率が高いと評価し、表2の「断線率評価」の欄に「×」と表示した。

【0044】

(6)−2.比抵抗値評価

得られた試料の抵抗値を測定した。すなわち、ライン電極の端部2箇所をテスターで押さえ、抵抗値を測定した。また、ライン電極の断面を研磨によって露出させ、その断面積を測定した。これら測定された抵抗値および断面積ならびにライン電極の長さから、以下の式に基づき、比抵抗値を算出した。

【0045】

Rdc=ρ・L/S

ただし、Rdc:抵抗値、ρ:比抵抗値、L:長さ、S:断面積。

【0046】

比抵抗値の結果が、表2の「比抵抗値」の欄に示されている。

【0047】

また、比抵抗値が2.5μΩ・cm未満のものを比抵抗値が低いと評価し、表2の「比抵抗値評価」の欄に「○」と表示し、他方、比抵抗値が2.5μΩ・cm以上のものを比抵抗値が高いと評価し、表2の「比抵抗値評価」の欄に「×」と表示した。

【0048】

(6)−3.総合評価

表2の「総合評価」の欄において、上記「断線率評価」および「比抵抗値評価」の双方が「○」となった試料については「○」と表示され、「断線率評価」および「比抵抗値評価」のいずれかが「×」となった試料については「×」と表示されている。

【0049】

【表2】

【0050】

表2において、試料番号に*を付したものは、この発明の範囲外の試料である。表2から、以下のことがわかった。

【0051】

この発明の範囲外の試料1および2では、「断線率」が15%以上と高く、「断線率評価」が「×」となり、応じて「総合評価」が「×」となった。これは、試料1および2では、それぞれ、表1に示したペーストP−1およびP−2を用いており、Alを含有しないか、Al添加量が0.05重量%未満と少ないため、焼成中にAlが酸化してAl2O3となってCu系粉末の粒子表面に出てくる量が少なく、Cu系粉末に対する焼結遅延作用が不十分であったことが原因であると推測される。

【0052】

また、この発明の範囲外の試料7では、「比抵抗値」が2.5μΩ・cm以上と高く、「比抵抗値評価」が「×」となり、応じて「総合評価」が「×」となった。これは、試料7では、表1に示したペーストP−7を用いており、Al含有量が0.15重量%を超えるため、焼成中にAlが酸化してAl2O3となってCu系粉末の粒子表面に出てくる量が多くなりすぎ、ライン電極が疎になったことが原因であると推測される。

【0053】

これらに対して、この発明の範囲内の試料3〜6では、「断線率」が15%未満と低く、「断線率評価」が「○」となるとともに、「比抵抗値」が2.5μΩ・cm未満と低く、「比抵抗値評価」が「○」となり、応じて「総合評価」が「○」となった。

【0054】

試料3〜6では、それぞれ、表1に示したペーストP−3〜P−6を用いており、Al添加量が0.05〜0.15重量%の範囲にある。ここで、まず、Al添加量が0.05重量%以上であるため、焼成中にAlが酸化してAl2O3となってCu系粉末の粒子表面に十分出てくることができ、したがって、Cu系粉末に対する焼結遅延作用が十分に働いて、「断線率評価」が「○」となったものと推測される。他方、Al添加量が0.15重量%以下であるため、比抵抗値がそれほど高くはならず、「比抵抗値評価」が「○」となったものと推測される。

【符号の説明】

【0055】

1 多層セラミック基板

2 セラミック層

3 セラミック素体

5,7 端子電極

8 内部導体膜

9 ビアホール導体

21 ライン電極

【特許請求の範囲】

【請求項1】

Al量が0.05〜0.15重量%であるCu−Al合金粉末を含有する、導電性ペースト。

【請求項2】

未焼結のセラミック素体と同時焼成される用途に向けられる、請求項1に記載の導電性ペースト。

【請求項3】

Cuが酸化されず、Alが酸化される酸素濃度を有する雰囲気下で未焼結のセラミック素体と同時焼成される用途に向けられる、請求項2に記載の導電性ペースト。

【請求項4】

セラミック素体と、前記セラミック素体の表面および/または内部に設けられた導体とを備え、前記導体は、請求項1に記載の導電性ペーストの焼結体からなる、セラミック電子部品。

【請求項1】

Al量が0.05〜0.15重量%であるCu−Al合金粉末を含有する、導電性ペースト。

【請求項2】

未焼結のセラミック素体と同時焼成される用途に向けられる、請求項1に記載の導電性ペースト。

【請求項3】

Cuが酸化されず、Alが酸化される酸素濃度を有する雰囲気下で未焼結のセラミック素体と同時焼成される用途に向けられる、請求項2に記載の導電性ペースト。

【請求項4】

セラミック素体と、前記セラミック素体の表面および/または内部に設けられた導体とを備え、前記導体は、請求項1に記載の導電性ペーストの焼結体からなる、セラミック電子部品。

【図1】

【図2】

【図2】

【公開番号】特開2013−26196(P2013−26196A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2011−163293(P2011−163293)

【出願日】平成23年7月26日(2011.7.26)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願日】平成23年7月26日(2011.7.26)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]