導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

【課題】公知のプロセスよりも高速であり、充てんされたビアにボイド、凹み又はキーホールを残さず、製造の費用効果が高い、改善された方法を提供する。

【解決手段】第1の表面214及び対向する第2の表面216を有する基板212を設け、基板の第1の表面に部分的にのみ前記基板の中に広がる少なくとも1つのブラインドビア218を形成する。酸化材料によって前記少なくとも1つのブラインドビアの表面をパッシベーションし、少なくとも一つのブラインドビアの酸化材料の表面に銅を含むシード材料228を、シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、基板の前記第1の表面を露出させるように形成する。シード材料の上に導電性材料230を前記少なくとも一つのブラインドビアを充填するように無電解めっきし、少なくとも一つのブラインドビアの導電性材料を露出させるために基板の前記第2の表面に研磨平坦化を実施する。

【解決手段】第1の表面214及び対向する第2の表面216を有する基板212を設け、基板の第1の表面に部分的にのみ前記基板の中に広がる少なくとも1つのブラインドビア218を形成する。酸化材料によって前記少なくとも1つのブラインドビアの表面をパッシベーションし、少なくとも一つのブラインドビアの酸化材料の表面に銅を含むシード材料228を、シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、基板の前記第1の表面を露出させるように形成する。シード材料の上に導電性材料230を前記少なくとも一つのブラインドビアを充填するように無電解めっきし、少なくとも一つのブラインドビアの導電性材料を露出させるために基板の前記第2の表面に研磨平坦化を実施する。

【発明の詳細な説明】

【技術分野】

【0001】

発明の分野:本発明は一般に半導体製造に関する。詳細には、本発明は、半導体構成部品の基板の一方の表面からその半導体構成部品のその基板の反対側の表面への電気相互接続を製造するため方法に関し、より詳細には、ウェーハ、インターポーザ又は他の基板に貫通ビアを製造するための方法に関する。

【背景技術】

【0002】

到達水準:半導体チップは、チップの両面に集積回路を有するように製作することができ、或いは、他の電子構成部品や他の半導体チップと接続し又は相互作用するように設計することができる。インターポーザは、半導体デバイスやプリント回路板などの2つの電気構成部品をインタフェースするのに利用することができ、コンタクタ・ボードは、半導体ウェーハ上のダイを試験するためにその半導体ウェーハとプローブ・カードをインタフェースするのに使用することができる。半導体チップは、半導体ウェーハ又は他のバルク基板材料から形成することができ、インターポーザ及びコンタクタ・ボードは、シリコン、セラミック又はポリマー基板から形成することができる。

【0003】

導電的にライニングされ又は充てんされた穴(以下「ビア」という)は、チップの一方の面の集積回路を、そのチップのもう一方の面の集積回路、大地又は他のバイアス電圧、他の電子構成部品、或いは他のチップの集積回路に接続するために使用される。ビアはさらに、インターポーザ又はコンタクタ・ボードの反対側の面に配置された構造間の電気通信を提供するために使用され、これらの構造は、コンタクト・パッド又は電気構成部品の他の構造と整列し、様々な構成部品間の電気接続を確立することができる。

【0004】

集積回路の連続的な小型化の結果、ビアのアスペクト比(この用語はビアの高さ又は長さと幅又は直径の比を指す)はますます大きくなるばかりである。この大きくなるばかりのアスペクト比に寄与する1つの要因は、ビアの幅が狭くなり続けていることである。積み重ねられたチップ、インターポーザ及びコンタクタ・ボードにおいて、典型的には幅が約50ミクロンである高アスペクト比ビアを充てんするために使用される公知のプロセスは、ビアにボイド又はキーホールを形成することなくビアを充てんすることが困難である。従来から、ビアは、化学蒸着(CVD)又は物理蒸着(PVD)を使用して銅などの金属のシード層でライニングすることができ、その後このシード層は電気めっきによってコーティングされる。ビアのアスペクト比が大きくなるにつれて、ビアの導電率に不利な影響を及ぼす空洞、ボイド又はキーホールを生じることなく、めっき材料でビアをライニングし又は充てんすることは一層困難になる。

【0005】

図1を参照すると、全体が10で示された基板の断面が示されている。この基板は、当技術分野で公知の電気めっきプロセスを使用して充てんされたビア12を含む。ビア12の内部は、電気めっきプロセスを使用して付着された金属層14でコーティングされている。電気めっきは、イオンの形態の金属を含む槽の中に浸した基板に、溶解したこのイオンの形態の金属を付着させる電気化学的なプロセスである。基板の金属シード層によって提供される陰極に金属イオンが付着するように、陽極から電気めっき溶液中に電流が流される。図示のとおり、金属層14の表面はでこぼこであり、ビア12が完全に充てんされると、このでこぼこの表面の結果、ビアを埋めるコンタクト塊の中に1つ又は複数のボイドが形成され得る。他の公知のプロセスでは、無電解めっきプロセスによってビアが充てんされる。無電解めっきでは、例えばプラズマ化学蒸着(PECVD)を使用することによってシード層が形成される。水溶液中の金属イオン及び化学還元剤を含む槽の中に基板を浸して、金属イオンが化学還元過程によってシード層に付着するようにすることにより、シード層は金属層によってコーティングされる。

【0006】

図2は、全体が20で示された他の基板の断面を示している。基板20は、当技術分野で公知の電気めっきを使用して金属層24で充てんされたビア22を含む。金属層24は、基板20の上面及び下面の近くでより効率的に付着しており、その結果、基板の上面及び下面の近くでビア22が実質的に閉じられており、ビア22の中間部分は充てんされずに残されている。ビア22の充てんされていない部分26はキーホールと呼ばれ、キーホールの存在はビア22の導電率を低下させる。

【0007】

ビアの中のボイド及びキーホールの形成を防ぐ試みの中で、ビアを充てんする他の方法が開発された。図3は、全体が30で示された基板の断面図である。基板30は、当該技術分野で公知の無電解めっきを使用して充てんされているビア32を含む。基板30は、浸漬めっきとも呼ばれる無電解めっきプロセス用の槽の中に置かれている。図示のように、金属の連続付着によって、ビア32が金属で実質的に充てんされるまで、ビア32の側壁のシード層(図示せず)の上に金属層34が形成される。しかし、図3の無電解付着プロセスの結果、ビア32の中にボイド又は凹みが生じる可能性がある。さらに、無電解めっきは比較的にゆっくりと進むため、すなわち、ニッケルなどの金属が約20ミクロン/時の最大速度で付着するため、付着プロセスが完了するまでに要する長い時間が望ましくない場合がある。例えばビアの幅が70μmの場合、この付着プロセスでは、金属層34がビアの中心に向かって内側へ成長してビア32を完全に充てんするときにビア32の内部に約35μm(70μm/2)の金属が付着するのに約1時間45分かかる。

【0008】

ビアにボイド及びキーホールが形成されるのを防ぐ他の試みでは、当該技術分野で公知の無電解ボトムフィル・プロセスを使用することができる。図4は、全体が40で示された基板の断面図を示す。基板40は、ビア42と、ビア42の底46に付着しビア42の頂部48に向かって成長する金属層44とを含む。ビア42の底46は、銅(Cu)、ニッケル(Ni)、タングステン(W)など適宜の金属を含むことができる。このボトムフィル・プロセスのアプローチは、金属層44を、(図3に示すような)ビア42の側面からではなく一方向に即ち上方へ付着させることによって、互いに向かって成長している金属層間にボイド及びキーホールが形成されないというものである。このボトムフィル・プロセスは、銅を用い、銅の移動によってビアにキーホールが形成されるのを防ぐ試みにおいて実行することができる。しかし、例えば700ミクロンなどビアが深い場合があり、無電解めっきは、前述の比較的に緩慢な速度で金属を付着させるため、ビアを完全に充てんするプロセスは容認できないほどに時間がかかる。ビアの底からの電気めっきも知られており、ここでは、陰極の役目を果たす導体が基板の底に置かれてビアの底を覆う。しかし、このようなアプローチは、ビアが充てんされるウェーハ処理ステージを厳しく限定し、基板上に形成された他の構造又は基板の上に形成される他の構造に設計上の制限を課す場合がある。

【0009】

したがって、ビアを充てんする改良された方法であって、公知のプロセスよりも高速であり、充てんされたビアにボイド、凹み又はキーホールを残さず、製造の費用効果が高い、改善された方法に対する必要性が存在する。

【0010】

[発明の開示]

本発明は、幾つかの実施の形態においては、上記の困難を、半導体構成部品に導電性ビアを形成するための方法、及び該方法から得られる半導体構成部品を提供することによって克服する。導電性ビアが電気めっき又は無電解めっきされた金属で完全には充てんされないため、導電性ビアを形成する本発明の方法は、公知のプロセスよりも高速である。さらに、本発明の導電性ビアは、空洞、ボイド及びキーホールを実質的に含まず、そのため、ビアの導電率が損なわれない導電材料の環状層を含む。

【0011】

半導体構成部品に導電性ビアを形成するための方法の例示的な一つの実施の形態は、第1の表面及び反対側の第2の表面を有する基板を設けるステップを含む。基板を貫通して、基板の第1の表面から第2の表面まで延びる少なくとも1つの穴が形成される。第1の表面、第2の表面、及び基板に形成された少なくとも1つの穴を規定する側壁にシード層が付着される。基板の第1の表面及び反対側の第2の表面の上にあるシード層が除去され、この少なくとも1つの穴の側壁にシード層が残される。側壁のシード層は導電層でコーティングされ、この少なくとも1つの穴の残りの空間に、導電性又は非導電性の充てん材料が導入される。

【0012】

別の例示的な実施の形態では、基板を貫通した導電性ビアを製造するための第2の方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板を設けるステップを含む。基板の第1の表面に少なくとも1つの空胴が形成される。基板の第1の表面及びこの少なくとも1つの空胴を規定している基板の露出領域の上に、導電層が付着される。この少なくとも1つの空胴の残りの空間に充てん材料が導入される。基板の反対側の第2の表面上に、導電層及びこの少なくとも1つの空胴に導入された充てん材料が露出される。

【0013】

例示的なさらに別の実施の形態は、少なくとも1つの導電性ビア前駆構造を含む中間半導体構成部品を含む。この中間半導体構成部品は、第1の表面及び反対側の第2の表面を有する基板を含む。この少なくとも1つの導電性ビア前駆構造は、基板の第1の表面中へ延び、反対側の第2の表面に達する前に基板の中で止まる。この少なくとも1つのビア前駆構造は、第1の表面から延び、導電性又は非導電性の充てん材料を囲む環状の導電層を含む。

【0014】

本発明の他の例示的な実施の形態は、第1の表面及び反対側の第2の表面を有する基板と、これらの表面の間に延びる少なくとも1つの導電性ビアとを含む半導体構成部品を含む。この少なくとも1つの導電性ビアは、基板の第1の表面から基板の第2の表面まで延びる環状の導電層を含む。この環状導電層によって導電性又は非導電性の充てん材料を囲み、導電性又は非導電性の充てん材料は、基板の第1の表面から基板の反対側の第2の表面まで延びる。

【0015】

他の実施形態において、本発明はさらに、マイクロプロセッサと、このマイクロプロセッサと通信する少なくとも1つのメモリ・デバイスとを含むシステムを包含する。この少なくとも1つのメモリ・デバイスは、第1の表面及び反対側の第2の表面を有する基板と、これらの表面の間に延びる少なくとも1つの導電性ビアとを含む。この少なくとも1つの導電性ビアは、基板の第1の表面から基板の反対側の第2の表面まで延びる導電材料の環状層を含む。この導電材料の環状層によって導電性又は非導電性の充てん材料を囲み、導電性又は非導電性の充てん材料は、基板の第1の表面から基板の反対側の第2の表面まで延びる。このメモリ・デバイスはさらに、この少なくとも1つの導電性ビアの上に重なる少なくとも1つのボンド・パッドを含む。

【0016】

添付図面は、現時点において本発明を実施するための最良の形態と考えられるものを示す。

【図面の簡単な説明】

【0017】

【図1】当該技術分野で公知の電気めっきプロセスを使用して充てんされた基板におけるビアの断面図である。

【図2】当該技術分野で公知の電気めっきプロセスを使用して実質的に充てんされたビアを有する基板の断面図である。

【図3】当該技術分野で公知の無電解めっきプロセスを使用して充てんされたビアを有する基板の断面図である。

【図4】当該技術分野で公知のボトムフィル・プロセスを使用して充てんされたビアを有する基板の断面図である。

【図5A】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5B】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5C】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5D】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5E】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5F】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5G】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図6A】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6B】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6C】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

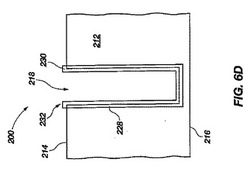

【図6D】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6E】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6F】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6G】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6H】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す 図である。

【図7A】ビアを充てんする本発明の方法の他の実施の形態の一段階を示す図である。

【図7B】ビアを充てんする本発明の方法の他の実施の形態の一段階を示す図である。

【図8】本発明を使用して形成された電気相互接続を有する半導体構成部品を示す図である。

【図9】本発明の方法を使用して製造された電気相互接続を含む電子システムの概略図である。

【発明を実施するための形態】

【0018】

一般に、本発明は、半導体構成部品の基板の一方の表面からその基板の反対側の表面への電気相互接続、すなわちビアを製造するための方法を含む。ビアは、半導体構成部品の様々な電気構造を電気的に接続することができ、又は他の構成部品と電気的に接続するために使用することができる。当業者には明白なように、ビアを製造するための本発明の方法は、電気相互接続が要求されるインターポーザやコンタクタ・ボードなど他の基板を製造する際にも有用である。本明細書で使用されるとき、用語「半導体構成部品」は、半導体ウェーハ、他のバルク半導体基板、及び本発明に基づく貫通ビアの形成が可能な他の基板材料から製造された電子構成部品を意味し、このような電子構成部品を含む。

【0019】

添付図面を参照すると、ウェーハ又は他の基板の厚さを貫通して形成されるビアを製造するための方法の様々な実施の形態が示されており、これらの図面では、同種の特徴及び要素は同じ参照符号又は同種の参照符号によって識別される。本明細書で説明されるプロセスはビアを製造するための方法を例示するが、当業者には明白なように、本明細書で説明される諸段階は半導体構成部品の製造プロセス全体の一部を構成し、これらを、他の製造プロセスと組み合わせることができる。本明細書で使用されるとき、用語「基板」は、ビアを形成することができる任意の支持構造を指し、これには、半導体ウェーハ、インターポーザ基板、コンタクタ・ボード又は基板ベースの他の構造が含まれるが、これらに限定されるものではない。

【0020】

本発明は、ウェーハ又は他の基板の厚さを貫通するビアを製造するための方法を含み、これらのビアは、導電性ライナ材料と充てん材料とを含む。充てん材料は導電材料又は非導電材料とすることができる。次に図5Aを参照すると、全体が100で示された半導体構成部品の断面が示されている。半導体構成部品100は、第1の表面114及び反対側の第2の表面116を有する基板112を含む。基板112は未処理の半導体ウェーハ又は他の基板を含むことができ、この基板は、1つ又は複数の半導体層又は他の構造を含む、自体の表面に形成された様々なプロセス層を有することができる。基板112はさらに、エッチング、付着又は他の公知の技法によって製造され且つ自体の表面に位置する活性部分又は他の動作可能部分を含むことができる。基板112はさらに、試験装置と試験される半導体デバイス(コンタクタ・ボード)との間で用いられる、又は、他の基板の中でのルーティングを提供するためのパッケージにおけるメモリ・デバイスとシステムとの間で使用されるインターポーザ基板を含むことができる。この例示的な実施の形態では、基板112は単結晶シリコンなどの半導体材料を含む。他の実施の形態では、基板112は、多結晶シリコン、ゲルマニウム、シリコン・オン・ガラス、シリコン・オン・サファイア、セラミック、ポリマー又はガラス充てん材入りエポキシ樹脂材料を含むことができる。基板112はさらに、公知の他の任意の基板材料を含むことができる。

【0021】

半導体構成部品100は、基板112の第1の表面114から第2の表面116まで延びるビア118を有する。この例示的な実施の形態では、ビア118は実質的に円筒形の形状を有し、内部表面ないし側壁120によって規定される。他の実施の形態では、ビア118は砂時計形などの他の形状を有し、又はビア形成用の公知の他の任意の形状を有することができる。ビア118の最上端122及び最下端124を限定する基板112の部分は破線で示されている。図を見やすくするため、後続の図面では、ビア118の最上端122及び最下端124が省かれる。

【0022】

この図示の実施の形態では、基板112の中にレーザ・アブレーションによってビア118が形成され、ビア118は約10μmから2ミルの代表的な直径を有することができる。積み重ねられたチップ、インターポーザ、コンタクタ・ボード又は他の公知の電子構成部品向けに半導体構成部品100が使用されるとき、ビア118は一般に約50μmの直径を有する。ビアの高さと幅の比は、集積回路の連続的な小型化に伴って絶えず低下しているため、直径約30μmのビア118が形成されることが予想される。当業者には明白なように、基板のタイプに応じて基板を1分当たり最高5μm除去することができる反応性イオン・エッチング(RIE)などのドライエッチング、光化学エッチング又は公知の他の任意のビア形成プロセス(ただし、これらに限定はされるわけではない)を含む、半導体構成部品100の形成に使用される種類の基板112に対して適切な公知の任意のビア形成方法を使用してビア118を形成することができる。ビア118の直径及び基板112の厚さは、半導体構成部品100の所望の使用に応じた所望の任意の寸法とすることができることも当業者には明白である。

【0023】

基板112の中にビア118が形成された後、レーザ・アブレーション・プロセスによって生成される熱の影響を受けた基板材料を除去するために、内部表面120を洗浄することができる。所望ならば、TMAH(テトラメチルアンモニウムヒドロキシド)溶液を使用して形成後のビア118を洗浄することができ、これによってビアの断面を四角にすることができる。

【0024】

基板112の材料の種類に適した誘電材料又は絶縁材料の絶縁層126で基板112の内部表面120をコーティングすることによって、洗浄された内面120を被膜保護することができる。絶縁層126は、スピン・オン・ガラス、熱酸化物、パリレン(Palylene、登録商標)ポリマー、二酸化シリコン、窒化シリコン、酸窒化シリコン、ガラスすなわちホウ燐珪酸ガラス、燐珪酸ガラス又はホウ珪酸ガラス、又は低い誘電率を有する当技術分野で公知の任意の誘電体を含むことができる。このパッシベーションを達成するため、物理蒸着(PVD)、CVD、低圧化学蒸着(LPCVD)、急速熱窒化(RTN)、スピン・オン・ガラス(SOG)プロセス、フロー・コーティング又は公知の他のプロセスを含む公知の任意のプロセスを使用して、絶縁層126を所望の任意の厚さに付着させることができる。他の実施の形態では、絶縁層126は注入又はキャピラリプロセス或いは真空ドロー(vacuum draw)を使用して付着させた、BT樹脂、ポリイミド、ベンゾシクロブテン又はポリベンゾキサゾールなどの絶縁ポリマーを含む。絶縁層126の厚さは例えば約1から5μmとすることができる。基板112がセラミックなどの電気絶縁材料を含む場合、絶縁層126は省くことができる。

【0025】

図5Bに示すとおり、基板112の第1の表面114及び第2の表面116ならびにビア118の内部表面120に、導電材料のシード層(seed layer)128が付着され、シード層128は絶縁層126(図5Aに示されている)を覆う。図を見やすくするため、図5B及び後続の他の図面では、図5Aの絶縁層126が省かれる。この図示の実施の形態では、シード層128は窒化チタン(TiN)を含み、シード層128はCVDによって付着される。シード層128として使用できる材料には、この他に、チタン(Ti)、窒化シリコン(Si3N4)、ポリシリコン、窒化タンタル(TaN)及び銅が含まれるが、これらに限定されるわけではない。シード層128を付着させるために使用することができる付着プロセスにはこの他、PVD、原子層付着(ALD)、PECVD、真空蒸着及びスパッタリングが含まれる。明らかなように、シード層128を付着させるために利用される材料の種類及び付着プロセスの選択は、ビア118を貫く電気相互接続を形成するために使用される材料の種類に応じて変化する。

【0026】

図5Cに示すように、基板112の第1の表面114及び第2の表面116を露出させるために、基板112の第1の表面114及び第2の表面116を覆っている部分のシード層128が除去される。この図示の実施の形態では、化学的機械的平坦化(CMP)などの研磨平坦化プロセスによってシード層128が除去される。しかし、シード層128の選択的除去は、ビア118の内部のシード層128の部分をマスクした後に、シード層128を構成する材料の種類に適したエッチング剤を使用したウェットエッチング、ドライエッチングなどの公知の他の任意のプロセスを使用して実施することもできる。

【0027】

シード層128をレジスト層129で覆うことができる。CMPプロセスによって生み出される粒子がビア118の中に付着することをレジスト129が防ぐように、レジスト129はCMPの前にシード層128に塗布される。CMPプロセスが終了した後、レジスト129は公知の技法を使用して除去され、導電材料の選択的付着のためのシード層128の清潔な表面を生み出す。

【0028】

基板112の表面を覆うために使用される導電材料の種類及び使用される基板112の種類によっては起こる可能性がある剥離を防ぐために、例示的な他の実施の形態では、基板112の第1の表面114及び第2の表面116を窒化層で覆って、基板112の第1の表面114及び第2の表面116にシード層128が付着することを防ぐことができる。ビア118の中に窒化層が付着することを防ぐためにビア118をマスクし、又は基板112にビア118が形成される前の基板112の第1の表面114及び第2の表面116に窒化層を塗布することができる。当業者には明白であるように、窒化層を使用する以外に、基板112の第1の表面114及び第2の表面116にシード層128が付着することを防ぐ他の任意の材料を使用することができる。

【0029】

図5Dに示すように、シード層128は無電解付着プロセスを使用して金属導電層130でコーティングされる。導電層130はシード層128には付着されるが、基板112の露出した第1及び第2の表面114及び116には付着されない。これは、シード層128はこれらの表面から除去されており(又はこれらの表面に元から存在せず)、無電解付着プロセスは、導電層130の付着のためにシード層128を必要とするからである。基板112の第1の表面114及び第2の表面116のシード層128を除去し、ビア118の中のシード層128を残すこの選択的除去、すなわちビアの中にだけ導電層130を付着させる選択的付着は、過剰な材料を除去する後続のCMPステップを不要にする。この導電層130の選択的付着は、導電層として使用される金属の量を減らし、したがって製造コストを低下させる。また、ビア118の中にだけ導電層130を付着させる選択的付着は、厚い導電層130をめっきするときに起こる可能性がある接着の問題を防ぐのに役立つ。基板112の露出した第1の表面114及び露出した第2の表面116の導電層130上での剥離を引き起こす応力は、ビア118の内部の剥離応力よりも大きい。導電層130は、ニッケル、コバルト、銅、銀、チタン、イリジウム、金、タングステン、タンタル、モリブデン、白金、パラジウム、ニッケル−リン(NiP)、パラジウム−リン(Pd−P)、コバルト−リン(Co−P)、Co−W−P合金、上記金属の他の合金及びこれらの混合物を含む任意のタイプの金属を含むことができるが、これらに限定されるわけではない。導電層130に使用される金属の種類及び厚さは、半導体構成部品100の所望の導電率及び使用に応じて変化し、これらは、少なくとも部分的に、当技術分野で公知の式R=ρL/Aによって表される金属又は導電層の抵抗(R)によって決定される。

【0030】

適宜の金属の導電層130でシード層128をコーティングすることによって、ビア118を貫く環状の導電経路が生み出される。無電解めっきプロセスは、ボイド又はキーホールを実質的に含まない実質的に絶縁保護コーティングをビア118の中に形成する。無電解めっきプロセスによって形成された導電層130は、一般に均一な厚さと低い多孔率を有し、防食を提供し、比較的硬い。無電解めっきプロセスは、付着させる金属のイオン形態の水溶液を含む浴の中に基板112を浸すことによって実施される。電気エネルギーを使用せずに金属を付着させることができるように、水溶液はさらに化学還元剤を含む。無電解めっきプロセスにおける金属イオンの還元及び後続の付着の推進力は化学還元剤によって推進される。水溶液が(例えば超音波によって)十分に攪拌されて、均一な濃度の金属イオン及び還元剤が水溶液中に分配されることが保証される限り、還元反応はシード層128上のあらゆる点で本質的に一定である。

【0031】

例示的な他の実施の形態では、浸漬めっきプロセスなどの浸漬プロセスを使用して、導電層130が銀又は金でライニングされる。導電層130がニッケル又はコバルトを含む場合、銀及び金はニッケル及びコバルトよりも貴であるから、銀又は金のライニングをニッケル又はコバルトに代えて使用し得る。銀又は金のライニングは導電率を増大させ、半田を濡らして、半田のボイドなし充てん及び半田とビア118の側壁との連続接触を保証するのに役立つ。

【0032】

シード層128は、基板112の第1の表面114及び第2の表面116と同じ高さの平面まで延びているため、導電層130の付着の結果、導電層130の小部分132が、基板112の第1の表面114又は第2の表面116の平面を越えて延びる可能性がある。所望ならば、小部分132をCMP又は他の公知の除去プロセスを使用して除去して、図5Eに示すように、導電層130が基板112の第1の表面114及び第2の表面116の平面と実質的に同じ高さになるようにすることができる。

【0033】

図5Eに示すように、ビア118は、第1の表面114から第2の表面116まで延びる開口134を有し、開口134は導電層130によって囲まれる。導電層130を形成するために使用される無電解めっきプロセスは、小さい凹み又はボイドを付随的に導電層130の中に残し得るが、所望の導電率を得るために必要な導電層130の厚さは、ボイド又は凹みが導電率に影響を及ぼさないような寸法でなければならない。ビア118の開口134は、図5Fに示すように充てん材料136で充てんされる。所望の厚さの導電層130を形成し、ビア118の残りの開口134を充てん材料136で充てんすることによって、基板に対する物理的な支持がビアの中に提供され、同時に導電層130によって提供された導電経路が維持される。

【0034】

充てん後のビア118の所望の導電率及び意図される半導体構成部品100の使用に応じて、充てん材料136は導電材料又は非導電材料とすることができる。例えば、充てん後のビア118の導電率は、少なくとも最低限、導電層130の材料と厚さによって決定されるため、導電層130が十分な導電経路を提供する場合には、非導電材料を使用してビア118の開口134を充てんすることができる。充てん材料136として使用することができる物質の代表的な非限定的な例にはシリコン含有充てん材が含まれ、これには例えば、スピンコーティング・プロセスを使用して塗布された、非導電性充てん材料136としてのスピン・オン・ガラス(SOG)、拡散プロセスを使用して付着されドープされた導電性充てん材料136としてのポリシリコンなどがある。スキージを用いて塗布され、それに続いてリフローされた半田ペーストを導電性充てん材料136として使用することもできる。半田ペーストは、共晶半田、Cu−Sn−Ag、Sn−Ag、公知の他の半田材料、又はこれらの組合せを含むことができる。使用することができる他の充てん材料136には、開口134の中にスクリーン印刷された半田合金、導電性及び非導電性のポリマー、金属充てん材入りシリコン、炭素充てん材入りインク、等方性又は異方性の導電性接着剤、及び、銀充てん材入りエポキシペーストなどの導体充てん材入りエポキシが含まれるが、これらに限定されるわけではない。

【0035】

ビア118の開口134が充てんされた後に、基板112の第1の表面114又は第2の表面116の平面を越えて充てん材料136が広がった場合には、当該技術分野で知られており図5Gに示すように、ビア118の一端又は両端にボンド・パッド138を形成することができるように、はみ出した充てん材料136をCMP又は他の公知の平滑化プロセスを使用して除去することができる。充てん材料136は、ビア118の上にあるボンド・パッド138に物理的支持を提供する。この例示的な実施の形態では、半導体構成部品100が1つのビア118を有するように示されているが、当業者には明らかにように、開示されたプロセスを使用して半導体構成部品100に任意の数のビア118を同時に形成し、ライニングし、充てんすることができる。

【0036】

例示的な他の実施の形態では、ブラインド・ビアを使用して本発明の導電性ビアを形成する。図6Aには、全体が200で示された半導体構成部品の断面が示されている。半導体構成部品200は、第1の表面214及び反対側の第2の表面216を有する基板212を含む。基板212は、未処理の半導体ウェーハ、又は、図5Aの基板112に関して以前に説明された製造プロセスで使用された他の基板材料を含むことができる。

【0037】

半導体構成部品200は、基板212に途中まで侵入して第1の表面214から基板212の中へ実質的に延びるブラインド・ビア218を含み、ブラインド・ビア218の底213は基板212の第2の表面216に達しない。ブラインド・ビア218は、レーザ・アブレーション・プロセスを使用して、又は、基板112の中にビア118が形成されたときに図5Aに関して本明細書で説明した他の任意の方法で基板212に形成することができる。ブラインド・ビア218は、基板212の内面ないし側壁220によって規定される。ブラインド・ビア218の最上端222を規定する基板212の部分は破線で示されており、この線は図を見やすくするために後続の図面では省かれる。

【0038】

図6Aの例示的な実施の形態では、ブラインド・ビア218はまた、細い線224で示すカバー層225で密閉可能にカバー又はキャップされた、基板212を貫通して延びる(図5Aのビア118と実質的に同様の)開口を基板212に含むことができる。カバー層225はブラインド・ビア218を実質的に密閉するので、カバーされたビアは本質的にブラインド・ビア218と実質的に同じように充てんされる。したがって、ブラインド・ビア218の底213を形成するカバー層225にもシード層を付着させることができ

る。例示的な他の実施の形態では、カバー層225は、基板212にブラインド・ビア218が形成される前に基板212に付着させた金属層を含むことができる。次いでレーザ・アブレーションを使用してブラインド・ビア218を途中まで形成し、次いでこれを、カバー層225の金属の表面で止まるドライエッチングを使用して完成させることができる。必要ならばブラインド・ビア218をパッシベーション層(図示せず)で絶縁することができる。

【0039】

図6Aの実施の形態を使用してブラインド・ビア218を形成することによって、汚染物質及び他のプロセス材料がウェーハ・チャック217又は他の支持構造に付着し又はこれらを汚染することを防ぐことができる。ウェーハ・チャック217は、製造プロセス期間に半導体構成部品200を支持するために使用することができ、後続の図面ではウェーハ・チャック217の図示が省かれる。

【0040】

ブラインド・ビア218の内面220を洗浄して、破片、残留した材料、又はブラインド・ビア218の形成によって不利な影響を受けた基板材料を除去することができる。洗浄後の内面220は、基板212の種類に適した誘電材料又は絶縁材料の層で基板212の内部表面220をコーティングすることによって、被膜保護することができる。図を見やすくするため図6Aにはパッシベーション層が示されていないが、当業者には明らなように、ブラインド・ビア218のパッシベーション層は、図5Aに関して説明された絶縁層126と実質的に同じ層とすることができる。さらに、基板212の材料によってはパッシベーション層を省くことができる。

【0041】

図6Bを参照すると、基板212の第1の表面214及びブラインド・ビア218の内面220に導電性金属のシード層228が形成された半導体構成部品200が示されている。この図示の実施の形態ではシード層228はTiNであり、シード層228はCVDによって付着される。しかし、シード層228は、図5Bのシード層128に関して本明細書で説明された他の任意の材料を含むことができる。

【0042】

基板212の第1の表面214を覆うシード層228の部分は、図6Cに示すように、基板212の第1の表面214を露出させるためにCMPによって除去される。シード層228は、本明細書で以前に説明した公知の任意のプロセスを使用して除去することができることは明白である。図6Dに示すように、本明細書で以前に説明した無電解付着プロセスを使用して、シード層228の上に導電層230が付着される。基板212の第1の表面214にはシード層228が存在しないため、基板212の第1の表面214には導電層230が付着しない。導電層230は、図5Dの導電層130に関して本明細書で説明した任意の導電性金属を含むことができ、導電層230に利用される金属の種類と厚さは、半導体構成部品200の所望の導電率及び最終的な使用に応じて変化する。

【0043】

例示的な他の実施の形態では、CMPの前にシード層228の上にレジスト層229が置かれる。レジスト229の存在は、CMPプロセスによって生み出される粒子がブラインド・ビア218を汚染することを防ぐ。CMPの後、レジスト229は公知の技法を使用して除去され、その結果、続く導電層230の付着のための清潔な表面が得られる。

【0044】

シード層228に導電層230が付着されたときに、導電層230の一部232が、基板212の第1の表面214の平面を越えて延びる可能性がある。これが起きた場合には、図5Eに関して本明細書で以前に説明したように、第1の表面214の平面を越えて延びた導電層230の部分232を除去することができ、これによって図6Eの半導体構成部品200が得られる。他の例示的な実施の形態では、基板212の第1の表面214の平面よりも上に延びている導電層230の部分232をそのまま残し、これを少なくとも部分的に使用して、基板212の第1の表面214に続いて構築されるボンド・パッド(図6Hに図示されている)の少なくとも一部を形成することができる。

【0045】

他の例示的な実施の形態では、浸漬めっきプロセスを使用して導電層230を銀又は金でライニングすることができる。導電層130がニッケル又はコバルトを含む場合、銀及び金はこれらよりも貴であるので、ニッケル又はコバルトは銀又は金に置き換えられる。導電層130に銀又は金のライニングを含めることは、導電率を高め、半田を濡らすのを助ける。

【0046】

図6Eに示すように、ブラインド・ビア218は、基板212の第1の表面214から実質的に基板212を貫通してブラインド・ビア218の底213まで延びる開口であって、ブラインド・ビア218の底213を覆う導電層230によって実質的に取り囲まれた開口234を含む。ブラインド・ビア218の開口234は、図6Fのクロスハッチング線で示すように、充てん材料236で充てんされる。図5Fに関して本明細書で以前に説明したとおり、充てん材料236は、充てんされたブラインド・ビア218の所望の導電率に応じて導電材料又は非導電材料を含むことができる。

【0047】

基板212の第2の表面216は、CMPなどの研磨平坦化プロセス又は公知の他の適当な除去プロセスを使用して半導体構成部品200から除去される。図6Gに示すように、基板212の第2の表面216にブラインド・ビア218が露出するように、基板212の材料は、図6Fの破線240によって示す深さまで除去される。当該技術分野で知られており且つ図6Hに示すように、ブラインド・ビア218の反対側の端にボンド・パッド238が形成される。この例示的な実施の形態の変形例では、ブラインド・ビア218が基板212の中をカバー層225まで延びる場合には、図6Aに関して説明したように、カバー層225を除去して、導電層230でライニングされ且つ充てん材料236で充てんされたブラインド・ビア218を露出させることができる。

【0048】

本発明の方法における活動の他の例示的な実施の形態が図7A及び7Bに示されている。半導体構成部品は全体として200′で示される。半導体構成部品200′は、第1の表面214及び反対側の第2の表面216を有する基板212を含む。基板212の第1の表面214にはバリア層203が形成される。バリア層203は、自体にシード層228が付着することを防ぐ材料を含む。バリア層203は、二酸化シリコン、窒化シリコンなどの酸化物含有材料又は窒化物含有材料を含むことができる。バリア層203を貫通して基板212にブラインド・ビア218が形成される。本明細書で以前に論じたとおり、ブラインド・ビア218の中にシード層228及び導電層230が形成され、その後、ブラインド・ビア218の残りの開口234が充てん材料で充てんされる。次いで、以前に説明したとおりに導電性のブラインド・ビア218の製造を完了させることができる。

【0049】

次に図8を参照すると、本発明の方法を使用して製造された半導体構成部品300の部分断面図が示されている。半導体構成部品300は、導電性ビア318を有する基板312を含む。導電性ビア318は、充てん材料336と、半導体構成部品300の反対側の表面に位置するボンド・パッド338間の電気接続を形成する環状の導電性ライナ330とを含む。

【0050】

半導体構成部品300は、コンタクト・パッド342又は他の導電性構造にビア318を電気的に接続する回路トレース340又は他の相互接続及びコンタクト構造を含むことができる。また、回路トレース340又は他の導電性構造は、半導体構成部品300の回路を、基板312の反対側に形成された集積回路などの他の回路に、半導体構成部品300の上又は下に配置された1つのスタックにおける他の半導体構成部品の回路に、インターポーザに、コンタクタ・ボードに、或いはマイクロプロセッサなどの他の半導体構成部品を担持するマザーボード、モジュールボードなどのキャリア基板に接続するのに使用することができる。さらに、ボンド・パッド338が形成されるブランケット材料層をパターン形成して、ビア318からコンタクト・パッド342に達する回路トレース340を規定することもできる。このように、導電性ビア318を使用して、基板312の第1の表面314のコンタクト・パッド342を、基板312の第2の表面316のコンタクト・パッド342に電気的に接続することができる。

【0051】

先に述べたとおり、半導体構成部品300の基板312は、様々な半導体構成部品を接続するためのインターポーザとして、半導体試験基板(コンタクタ・ボード)として、又は半導体チップを接続することができるよりレベルのパッケージを形成するキャリア基板として設計し、製造することができる。能動回路を有する半導体デバイスとして構成される場合には、半導体構成部品300のボンド・パッド338又はコンタクト・パッド342を、試験基板又はキャリア基板上の端子パッドのパターンに対応するパターンに配置することができる。インターポーザ又はコンタクタ・ボードとして使用される場合には、ボンド・パッド338又はコンタクト・パッド342を、基板312の一方の面で試験基板又はキャリア基板の端子パッドに対応し、もう一方の面で、接触される半導体デバイス上のボンド・パッド又は他のI/O位置に対応するパターンに配置することができる。

【0052】

次に図9を参照すると、本発明の導電性ビアを含むシステム400の一つの実施の形態が示されている。システム400は、スタティック・ランダムアクセス・メモリ(SRAM)、ダイナミック・ランダムアクセス・メモリ(DRAM)又は公知の他のメモリ・デバイスなどの少なくとも1つのメモリ・デバイス402を含み、この少なくとも1つのメモリ・デバイス402は、本発明の方法を使用して製造された少なくとも1つの導電性ビアを含む。メモリ・デバイス402は、当該技術分野で公知の特定の機能を実行するようにプログラムすることができるマイクロプロセッサ404に動作可能に結合される。

【0053】

上で示した本発明の実施の形態は、低コストの材料を使用して製造することができ、単純な方法を要し、実質的にボイド及びキーホールを含まない頑強な電気相互接続を与える貫通ビアの形態の電気相互接続を開示する。本発明は様々な例示的な実施の形態に関して図示して説明してきたが、本発明の範囲又は必須の特性から、様々な追加、削除及び変更が企図される。さらに、本発明は半導体デバイス又はインターポーザの文脈で説明されたが、本発明は、半導体構成部品を用いて製造された任意のデバイス又は構成部品に電気相互接続を形成するのに有用である。したがって、本発明の範囲は、以上の説明ではなく、添付の請求項によって示される。添付の請求項の等価物の意味及び範囲に含まれる全ての変更は、添付の請求項の範囲に包含される。

【技術分野】

【0001】

発明の分野:本発明は一般に半導体製造に関する。詳細には、本発明は、半導体構成部品の基板の一方の表面からその半導体構成部品のその基板の反対側の表面への電気相互接続を製造するため方法に関し、より詳細には、ウェーハ、インターポーザ又は他の基板に貫通ビアを製造するための方法に関する。

【背景技術】

【0002】

到達水準:半導体チップは、チップの両面に集積回路を有するように製作することができ、或いは、他の電子構成部品や他の半導体チップと接続し又は相互作用するように設計することができる。インターポーザは、半導体デバイスやプリント回路板などの2つの電気構成部品をインタフェースするのに利用することができ、コンタクタ・ボードは、半導体ウェーハ上のダイを試験するためにその半導体ウェーハとプローブ・カードをインタフェースするのに使用することができる。半導体チップは、半導体ウェーハ又は他のバルク基板材料から形成することができ、インターポーザ及びコンタクタ・ボードは、シリコン、セラミック又はポリマー基板から形成することができる。

【0003】

導電的にライニングされ又は充てんされた穴(以下「ビア」という)は、チップの一方の面の集積回路を、そのチップのもう一方の面の集積回路、大地又は他のバイアス電圧、他の電子構成部品、或いは他のチップの集積回路に接続するために使用される。ビアはさらに、インターポーザ又はコンタクタ・ボードの反対側の面に配置された構造間の電気通信を提供するために使用され、これらの構造は、コンタクト・パッド又は電気構成部品の他の構造と整列し、様々な構成部品間の電気接続を確立することができる。

【0004】

集積回路の連続的な小型化の結果、ビアのアスペクト比(この用語はビアの高さ又は長さと幅又は直径の比を指す)はますます大きくなるばかりである。この大きくなるばかりのアスペクト比に寄与する1つの要因は、ビアの幅が狭くなり続けていることである。積み重ねられたチップ、インターポーザ及びコンタクタ・ボードにおいて、典型的には幅が約50ミクロンである高アスペクト比ビアを充てんするために使用される公知のプロセスは、ビアにボイド又はキーホールを形成することなくビアを充てんすることが困難である。従来から、ビアは、化学蒸着(CVD)又は物理蒸着(PVD)を使用して銅などの金属のシード層でライニングすることができ、その後このシード層は電気めっきによってコーティングされる。ビアのアスペクト比が大きくなるにつれて、ビアの導電率に不利な影響を及ぼす空洞、ボイド又はキーホールを生じることなく、めっき材料でビアをライニングし又は充てんすることは一層困難になる。

【0005】

図1を参照すると、全体が10で示された基板の断面が示されている。この基板は、当技術分野で公知の電気めっきプロセスを使用して充てんされたビア12を含む。ビア12の内部は、電気めっきプロセスを使用して付着された金属層14でコーティングされている。電気めっきは、イオンの形態の金属を含む槽の中に浸した基板に、溶解したこのイオンの形態の金属を付着させる電気化学的なプロセスである。基板の金属シード層によって提供される陰極に金属イオンが付着するように、陽極から電気めっき溶液中に電流が流される。図示のとおり、金属層14の表面はでこぼこであり、ビア12が完全に充てんされると、このでこぼこの表面の結果、ビアを埋めるコンタクト塊の中に1つ又は複数のボイドが形成され得る。他の公知のプロセスでは、無電解めっきプロセスによってビアが充てんされる。無電解めっきでは、例えばプラズマ化学蒸着(PECVD)を使用することによってシード層が形成される。水溶液中の金属イオン及び化学還元剤を含む槽の中に基板を浸して、金属イオンが化学還元過程によってシード層に付着するようにすることにより、シード層は金属層によってコーティングされる。

【0006】

図2は、全体が20で示された他の基板の断面を示している。基板20は、当技術分野で公知の電気めっきを使用して金属層24で充てんされたビア22を含む。金属層24は、基板20の上面及び下面の近くでより効率的に付着しており、その結果、基板の上面及び下面の近くでビア22が実質的に閉じられており、ビア22の中間部分は充てんされずに残されている。ビア22の充てんされていない部分26はキーホールと呼ばれ、キーホールの存在はビア22の導電率を低下させる。

【0007】

ビアの中のボイド及びキーホールの形成を防ぐ試みの中で、ビアを充てんする他の方法が開発された。図3は、全体が30で示された基板の断面図である。基板30は、当該技術分野で公知の無電解めっきを使用して充てんされているビア32を含む。基板30は、浸漬めっきとも呼ばれる無電解めっきプロセス用の槽の中に置かれている。図示のように、金属の連続付着によって、ビア32が金属で実質的に充てんされるまで、ビア32の側壁のシード層(図示せず)の上に金属層34が形成される。しかし、図3の無電解付着プロセスの結果、ビア32の中にボイド又は凹みが生じる可能性がある。さらに、無電解めっきは比較的にゆっくりと進むため、すなわち、ニッケルなどの金属が約20ミクロン/時の最大速度で付着するため、付着プロセスが完了するまでに要する長い時間が望ましくない場合がある。例えばビアの幅が70μmの場合、この付着プロセスでは、金属層34がビアの中心に向かって内側へ成長してビア32を完全に充てんするときにビア32の内部に約35μm(70μm/2)の金属が付着するのに約1時間45分かかる。

【0008】

ビアにボイド及びキーホールが形成されるのを防ぐ他の試みでは、当該技術分野で公知の無電解ボトムフィル・プロセスを使用することができる。図4は、全体が40で示された基板の断面図を示す。基板40は、ビア42と、ビア42の底46に付着しビア42の頂部48に向かって成長する金属層44とを含む。ビア42の底46は、銅(Cu)、ニッケル(Ni)、タングステン(W)など適宜の金属を含むことができる。このボトムフィル・プロセスのアプローチは、金属層44を、(図3に示すような)ビア42の側面からではなく一方向に即ち上方へ付着させることによって、互いに向かって成長している金属層間にボイド及びキーホールが形成されないというものである。このボトムフィル・プロセスは、銅を用い、銅の移動によってビアにキーホールが形成されるのを防ぐ試みにおいて実行することができる。しかし、例えば700ミクロンなどビアが深い場合があり、無電解めっきは、前述の比較的に緩慢な速度で金属を付着させるため、ビアを完全に充てんするプロセスは容認できないほどに時間がかかる。ビアの底からの電気めっきも知られており、ここでは、陰極の役目を果たす導体が基板の底に置かれてビアの底を覆う。しかし、このようなアプローチは、ビアが充てんされるウェーハ処理ステージを厳しく限定し、基板上に形成された他の構造又は基板の上に形成される他の構造に設計上の制限を課す場合がある。

【0009】

したがって、ビアを充てんする改良された方法であって、公知のプロセスよりも高速であり、充てんされたビアにボイド、凹み又はキーホールを残さず、製造の費用効果が高い、改善された方法に対する必要性が存在する。

【0010】

[発明の開示]

本発明は、幾つかの実施の形態においては、上記の困難を、半導体構成部品に導電性ビアを形成するための方法、及び該方法から得られる半導体構成部品を提供することによって克服する。導電性ビアが電気めっき又は無電解めっきされた金属で完全には充てんされないため、導電性ビアを形成する本発明の方法は、公知のプロセスよりも高速である。さらに、本発明の導電性ビアは、空洞、ボイド及びキーホールを実質的に含まず、そのため、ビアの導電率が損なわれない導電材料の環状層を含む。

【0011】

半導体構成部品に導電性ビアを形成するための方法の例示的な一つの実施の形態は、第1の表面及び反対側の第2の表面を有する基板を設けるステップを含む。基板を貫通して、基板の第1の表面から第2の表面まで延びる少なくとも1つの穴が形成される。第1の表面、第2の表面、及び基板に形成された少なくとも1つの穴を規定する側壁にシード層が付着される。基板の第1の表面及び反対側の第2の表面の上にあるシード層が除去され、この少なくとも1つの穴の側壁にシード層が残される。側壁のシード層は導電層でコーティングされ、この少なくとも1つの穴の残りの空間に、導電性又は非導電性の充てん材料が導入される。

【0012】

別の例示的な実施の形態では、基板を貫通した導電性ビアを製造するための第2の方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板を設けるステップを含む。基板の第1の表面に少なくとも1つの空胴が形成される。基板の第1の表面及びこの少なくとも1つの空胴を規定している基板の露出領域の上に、導電層が付着される。この少なくとも1つの空胴の残りの空間に充てん材料が導入される。基板の反対側の第2の表面上に、導電層及びこの少なくとも1つの空胴に導入された充てん材料が露出される。

【0013】

例示的なさらに別の実施の形態は、少なくとも1つの導電性ビア前駆構造を含む中間半導体構成部品を含む。この中間半導体構成部品は、第1の表面及び反対側の第2の表面を有する基板を含む。この少なくとも1つの導電性ビア前駆構造は、基板の第1の表面中へ延び、反対側の第2の表面に達する前に基板の中で止まる。この少なくとも1つのビア前駆構造は、第1の表面から延び、導電性又は非導電性の充てん材料を囲む環状の導電層を含む。

【0014】

本発明の他の例示的な実施の形態は、第1の表面及び反対側の第2の表面を有する基板と、これらの表面の間に延びる少なくとも1つの導電性ビアとを含む半導体構成部品を含む。この少なくとも1つの導電性ビアは、基板の第1の表面から基板の第2の表面まで延びる環状の導電層を含む。この環状導電層によって導電性又は非導電性の充てん材料を囲み、導電性又は非導電性の充てん材料は、基板の第1の表面から基板の反対側の第2の表面まで延びる。

【0015】

他の実施形態において、本発明はさらに、マイクロプロセッサと、このマイクロプロセッサと通信する少なくとも1つのメモリ・デバイスとを含むシステムを包含する。この少なくとも1つのメモリ・デバイスは、第1の表面及び反対側の第2の表面を有する基板と、これらの表面の間に延びる少なくとも1つの導電性ビアとを含む。この少なくとも1つの導電性ビアは、基板の第1の表面から基板の反対側の第2の表面まで延びる導電材料の環状層を含む。この導電材料の環状層によって導電性又は非導電性の充てん材料を囲み、導電性又は非導電性の充てん材料は、基板の第1の表面から基板の反対側の第2の表面まで延びる。このメモリ・デバイスはさらに、この少なくとも1つの導電性ビアの上に重なる少なくとも1つのボンド・パッドを含む。

【0016】

添付図面は、現時点において本発明を実施するための最良の形態と考えられるものを示す。

【図面の簡単な説明】

【0017】

【図1】当該技術分野で公知の電気めっきプロセスを使用して充てんされた基板におけるビアの断面図である。

【図2】当該技術分野で公知の電気めっきプロセスを使用して実質的に充てんされたビアを有する基板の断面図である。

【図3】当該技術分野で公知の無電解めっきプロセスを使用して充てんされたビアを有する基板の断面図である。

【図4】当該技術分野で公知のボトムフィル・プロセスを使用して充てんされたビアを有する基板の断面図である。

【図5A】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5B】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5C】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5D】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5E】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5F】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図5G】ビアを充てんする本発明の方法の例示的な一つの実施の形態の一段階を示す図である。

【図6A】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6B】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6C】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6D】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6E】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6F】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6G】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す図である。

【図6H】ビアを充てんする本発明の方法の例示的な他の実施の形態の一段階を示す 図である。

【図7A】ビアを充てんする本発明の方法の他の実施の形態の一段階を示す図である。

【図7B】ビアを充てんする本発明の方法の他の実施の形態の一段階を示す図である。

【図8】本発明を使用して形成された電気相互接続を有する半導体構成部品を示す図である。

【図9】本発明の方法を使用して製造された電気相互接続を含む電子システムの概略図である。

【発明を実施するための形態】

【0018】

一般に、本発明は、半導体構成部品の基板の一方の表面からその基板の反対側の表面への電気相互接続、すなわちビアを製造するための方法を含む。ビアは、半導体構成部品の様々な電気構造を電気的に接続することができ、又は他の構成部品と電気的に接続するために使用することができる。当業者には明白なように、ビアを製造するための本発明の方法は、電気相互接続が要求されるインターポーザやコンタクタ・ボードなど他の基板を製造する際にも有用である。本明細書で使用されるとき、用語「半導体構成部品」は、半導体ウェーハ、他のバルク半導体基板、及び本発明に基づく貫通ビアの形成が可能な他の基板材料から製造された電子構成部品を意味し、このような電子構成部品を含む。

【0019】

添付図面を参照すると、ウェーハ又は他の基板の厚さを貫通して形成されるビアを製造するための方法の様々な実施の形態が示されており、これらの図面では、同種の特徴及び要素は同じ参照符号又は同種の参照符号によって識別される。本明細書で説明されるプロセスはビアを製造するための方法を例示するが、当業者には明白なように、本明細書で説明される諸段階は半導体構成部品の製造プロセス全体の一部を構成し、これらを、他の製造プロセスと組み合わせることができる。本明細書で使用されるとき、用語「基板」は、ビアを形成することができる任意の支持構造を指し、これには、半導体ウェーハ、インターポーザ基板、コンタクタ・ボード又は基板ベースの他の構造が含まれるが、これらに限定されるものではない。

【0020】

本発明は、ウェーハ又は他の基板の厚さを貫通するビアを製造するための方法を含み、これらのビアは、導電性ライナ材料と充てん材料とを含む。充てん材料は導電材料又は非導電材料とすることができる。次に図5Aを参照すると、全体が100で示された半導体構成部品の断面が示されている。半導体構成部品100は、第1の表面114及び反対側の第2の表面116を有する基板112を含む。基板112は未処理の半導体ウェーハ又は他の基板を含むことができ、この基板は、1つ又は複数の半導体層又は他の構造を含む、自体の表面に形成された様々なプロセス層を有することができる。基板112はさらに、エッチング、付着又は他の公知の技法によって製造され且つ自体の表面に位置する活性部分又は他の動作可能部分を含むことができる。基板112はさらに、試験装置と試験される半導体デバイス(コンタクタ・ボード)との間で用いられる、又は、他の基板の中でのルーティングを提供するためのパッケージにおけるメモリ・デバイスとシステムとの間で使用されるインターポーザ基板を含むことができる。この例示的な実施の形態では、基板112は単結晶シリコンなどの半導体材料を含む。他の実施の形態では、基板112は、多結晶シリコン、ゲルマニウム、シリコン・オン・ガラス、シリコン・オン・サファイア、セラミック、ポリマー又はガラス充てん材入りエポキシ樹脂材料を含むことができる。基板112はさらに、公知の他の任意の基板材料を含むことができる。

【0021】

半導体構成部品100は、基板112の第1の表面114から第2の表面116まで延びるビア118を有する。この例示的な実施の形態では、ビア118は実質的に円筒形の形状を有し、内部表面ないし側壁120によって規定される。他の実施の形態では、ビア118は砂時計形などの他の形状を有し、又はビア形成用の公知の他の任意の形状を有することができる。ビア118の最上端122及び最下端124を限定する基板112の部分は破線で示されている。図を見やすくするため、後続の図面では、ビア118の最上端122及び最下端124が省かれる。

【0022】

この図示の実施の形態では、基板112の中にレーザ・アブレーションによってビア118が形成され、ビア118は約10μmから2ミルの代表的な直径を有することができる。積み重ねられたチップ、インターポーザ、コンタクタ・ボード又は他の公知の電子構成部品向けに半導体構成部品100が使用されるとき、ビア118は一般に約50μmの直径を有する。ビアの高さと幅の比は、集積回路の連続的な小型化に伴って絶えず低下しているため、直径約30μmのビア118が形成されることが予想される。当業者には明白なように、基板のタイプに応じて基板を1分当たり最高5μm除去することができる反応性イオン・エッチング(RIE)などのドライエッチング、光化学エッチング又は公知の他の任意のビア形成プロセス(ただし、これらに限定はされるわけではない)を含む、半導体構成部品100の形成に使用される種類の基板112に対して適切な公知の任意のビア形成方法を使用してビア118を形成することができる。ビア118の直径及び基板112の厚さは、半導体構成部品100の所望の使用に応じた所望の任意の寸法とすることができることも当業者には明白である。

【0023】

基板112の中にビア118が形成された後、レーザ・アブレーション・プロセスによって生成される熱の影響を受けた基板材料を除去するために、内部表面120を洗浄することができる。所望ならば、TMAH(テトラメチルアンモニウムヒドロキシド)溶液を使用して形成後のビア118を洗浄することができ、これによってビアの断面を四角にすることができる。

【0024】

基板112の材料の種類に適した誘電材料又は絶縁材料の絶縁層126で基板112の内部表面120をコーティングすることによって、洗浄された内面120を被膜保護することができる。絶縁層126は、スピン・オン・ガラス、熱酸化物、パリレン(Palylene、登録商標)ポリマー、二酸化シリコン、窒化シリコン、酸窒化シリコン、ガラスすなわちホウ燐珪酸ガラス、燐珪酸ガラス又はホウ珪酸ガラス、又は低い誘電率を有する当技術分野で公知の任意の誘電体を含むことができる。このパッシベーションを達成するため、物理蒸着(PVD)、CVD、低圧化学蒸着(LPCVD)、急速熱窒化(RTN)、スピン・オン・ガラス(SOG)プロセス、フロー・コーティング又は公知の他のプロセスを含む公知の任意のプロセスを使用して、絶縁層126を所望の任意の厚さに付着させることができる。他の実施の形態では、絶縁層126は注入又はキャピラリプロセス或いは真空ドロー(vacuum draw)を使用して付着させた、BT樹脂、ポリイミド、ベンゾシクロブテン又はポリベンゾキサゾールなどの絶縁ポリマーを含む。絶縁層126の厚さは例えば約1から5μmとすることができる。基板112がセラミックなどの電気絶縁材料を含む場合、絶縁層126は省くことができる。

【0025】

図5Bに示すとおり、基板112の第1の表面114及び第2の表面116ならびにビア118の内部表面120に、導電材料のシード層(seed layer)128が付着され、シード層128は絶縁層126(図5Aに示されている)を覆う。図を見やすくするため、図5B及び後続の他の図面では、図5Aの絶縁層126が省かれる。この図示の実施の形態では、シード層128は窒化チタン(TiN)を含み、シード層128はCVDによって付着される。シード層128として使用できる材料には、この他に、チタン(Ti)、窒化シリコン(Si3N4)、ポリシリコン、窒化タンタル(TaN)及び銅が含まれるが、これらに限定されるわけではない。シード層128を付着させるために使用することができる付着プロセスにはこの他、PVD、原子層付着(ALD)、PECVD、真空蒸着及びスパッタリングが含まれる。明らかなように、シード層128を付着させるために利用される材料の種類及び付着プロセスの選択は、ビア118を貫く電気相互接続を形成するために使用される材料の種類に応じて変化する。

【0026】

図5Cに示すように、基板112の第1の表面114及び第2の表面116を露出させるために、基板112の第1の表面114及び第2の表面116を覆っている部分のシード層128が除去される。この図示の実施の形態では、化学的機械的平坦化(CMP)などの研磨平坦化プロセスによってシード層128が除去される。しかし、シード層128の選択的除去は、ビア118の内部のシード層128の部分をマスクした後に、シード層128を構成する材料の種類に適したエッチング剤を使用したウェットエッチング、ドライエッチングなどの公知の他の任意のプロセスを使用して実施することもできる。

【0027】

シード層128をレジスト層129で覆うことができる。CMPプロセスによって生み出される粒子がビア118の中に付着することをレジスト129が防ぐように、レジスト129はCMPの前にシード層128に塗布される。CMPプロセスが終了した後、レジスト129は公知の技法を使用して除去され、導電材料の選択的付着のためのシード層128の清潔な表面を生み出す。

【0028】

基板112の表面を覆うために使用される導電材料の種類及び使用される基板112の種類によっては起こる可能性がある剥離を防ぐために、例示的な他の実施の形態では、基板112の第1の表面114及び第2の表面116を窒化層で覆って、基板112の第1の表面114及び第2の表面116にシード層128が付着することを防ぐことができる。ビア118の中に窒化層が付着することを防ぐためにビア118をマスクし、又は基板112にビア118が形成される前の基板112の第1の表面114及び第2の表面116に窒化層を塗布することができる。当業者には明白であるように、窒化層を使用する以外に、基板112の第1の表面114及び第2の表面116にシード層128が付着することを防ぐ他の任意の材料を使用することができる。

【0029】

図5Dに示すように、シード層128は無電解付着プロセスを使用して金属導電層130でコーティングされる。導電層130はシード層128には付着されるが、基板112の露出した第1及び第2の表面114及び116には付着されない。これは、シード層128はこれらの表面から除去されており(又はこれらの表面に元から存在せず)、無電解付着プロセスは、導電層130の付着のためにシード層128を必要とするからである。基板112の第1の表面114及び第2の表面116のシード層128を除去し、ビア118の中のシード層128を残すこの選択的除去、すなわちビアの中にだけ導電層130を付着させる選択的付着は、過剰な材料を除去する後続のCMPステップを不要にする。この導電層130の選択的付着は、導電層として使用される金属の量を減らし、したがって製造コストを低下させる。また、ビア118の中にだけ導電層130を付着させる選択的付着は、厚い導電層130をめっきするときに起こる可能性がある接着の問題を防ぐのに役立つ。基板112の露出した第1の表面114及び露出した第2の表面116の導電層130上での剥離を引き起こす応力は、ビア118の内部の剥離応力よりも大きい。導電層130は、ニッケル、コバルト、銅、銀、チタン、イリジウム、金、タングステン、タンタル、モリブデン、白金、パラジウム、ニッケル−リン(NiP)、パラジウム−リン(Pd−P)、コバルト−リン(Co−P)、Co−W−P合金、上記金属の他の合金及びこれらの混合物を含む任意のタイプの金属を含むことができるが、これらに限定されるわけではない。導電層130に使用される金属の種類及び厚さは、半導体構成部品100の所望の導電率及び使用に応じて変化し、これらは、少なくとも部分的に、当技術分野で公知の式R=ρL/Aによって表される金属又は導電層の抵抗(R)によって決定される。

【0030】

適宜の金属の導電層130でシード層128をコーティングすることによって、ビア118を貫く環状の導電経路が生み出される。無電解めっきプロセスは、ボイド又はキーホールを実質的に含まない実質的に絶縁保護コーティングをビア118の中に形成する。無電解めっきプロセスによって形成された導電層130は、一般に均一な厚さと低い多孔率を有し、防食を提供し、比較的硬い。無電解めっきプロセスは、付着させる金属のイオン形態の水溶液を含む浴の中に基板112を浸すことによって実施される。電気エネルギーを使用せずに金属を付着させることができるように、水溶液はさらに化学還元剤を含む。無電解めっきプロセスにおける金属イオンの還元及び後続の付着の推進力は化学還元剤によって推進される。水溶液が(例えば超音波によって)十分に攪拌されて、均一な濃度の金属イオン及び還元剤が水溶液中に分配されることが保証される限り、還元反応はシード層128上のあらゆる点で本質的に一定である。

【0031】

例示的な他の実施の形態では、浸漬めっきプロセスなどの浸漬プロセスを使用して、導電層130が銀又は金でライニングされる。導電層130がニッケル又はコバルトを含む場合、銀及び金はニッケル及びコバルトよりも貴であるから、銀又は金のライニングをニッケル又はコバルトに代えて使用し得る。銀又は金のライニングは導電率を増大させ、半田を濡らして、半田のボイドなし充てん及び半田とビア118の側壁との連続接触を保証するのに役立つ。

【0032】

シード層128は、基板112の第1の表面114及び第2の表面116と同じ高さの平面まで延びているため、導電層130の付着の結果、導電層130の小部分132が、基板112の第1の表面114又は第2の表面116の平面を越えて延びる可能性がある。所望ならば、小部分132をCMP又は他の公知の除去プロセスを使用して除去して、図5Eに示すように、導電層130が基板112の第1の表面114及び第2の表面116の平面と実質的に同じ高さになるようにすることができる。

【0033】

図5Eに示すように、ビア118は、第1の表面114から第2の表面116まで延びる開口134を有し、開口134は導電層130によって囲まれる。導電層130を形成するために使用される無電解めっきプロセスは、小さい凹み又はボイドを付随的に導電層130の中に残し得るが、所望の導電率を得るために必要な導電層130の厚さは、ボイド又は凹みが導電率に影響を及ぼさないような寸法でなければならない。ビア118の開口134は、図5Fに示すように充てん材料136で充てんされる。所望の厚さの導電層130を形成し、ビア118の残りの開口134を充てん材料136で充てんすることによって、基板に対する物理的な支持がビアの中に提供され、同時に導電層130によって提供された導電経路が維持される。

【0034】

充てん後のビア118の所望の導電率及び意図される半導体構成部品100の使用に応じて、充てん材料136は導電材料又は非導電材料とすることができる。例えば、充てん後のビア118の導電率は、少なくとも最低限、導電層130の材料と厚さによって決定されるため、導電層130が十分な導電経路を提供する場合には、非導電材料を使用してビア118の開口134を充てんすることができる。充てん材料136として使用することができる物質の代表的な非限定的な例にはシリコン含有充てん材が含まれ、これには例えば、スピンコーティング・プロセスを使用して塗布された、非導電性充てん材料136としてのスピン・オン・ガラス(SOG)、拡散プロセスを使用して付着されドープされた導電性充てん材料136としてのポリシリコンなどがある。スキージを用いて塗布され、それに続いてリフローされた半田ペーストを導電性充てん材料136として使用することもできる。半田ペーストは、共晶半田、Cu−Sn−Ag、Sn−Ag、公知の他の半田材料、又はこれらの組合せを含むことができる。使用することができる他の充てん材料136には、開口134の中にスクリーン印刷された半田合金、導電性及び非導電性のポリマー、金属充てん材入りシリコン、炭素充てん材入りインク、等方性又は異方性の導電性接着剤、及び、銀充てん材入りエポキシペーストなどの導体充てん材入りエポキシが含まれるが、これらに限定されるわけではない。

【0035】

ビア118の開口134が充てんされた後に、基板112の第1の表面114又は第2の表面116の平面を越えて充てん材料136が広がった場合には、当該技術分野で知られており図5Gに示すように、ビア118の一端又は両端にボンド・パッド138を形成することができるように、はみ出した充てん材料136をCMP又は他の公知の平滑化プロセスを使用して除去することができる。充てん材料136は、ビア118の上にあるボンド・パッド138に物理的支持を提供する。この例示的な実施の形態では、半導体構成部品100が1つのビア118を有するように示されているが、当業者には明らかにように、開示されたプロセスを使用して半導体構成部品100に任意の数のビア118を同時に形成し、ライニングし、充てんすることができる。

【0036】

例示的な他の実施の形態では、ブラインド・ビアを使用して本発明の導電性ビアを形成する。図6Aには、全体が200で示された半導体構成部品の断面が示されている。半導体構成部品200は、第1の表面214及び反対側の第2の表面216を有する基板212を含む。基板212は、未処理の半導体ウェーハ、又は、図5Aの基板112に関して以前に説明された製造プロセスで使用された他の基板材料を含むことができる。

【0037】

半導体構成部品200は、基板212に途中まで侵入して第1の表面214から基板212の中へ実質的に延びるブラインド・ビア218を含み、ブラインド・ビア218の底213は基板212の第2の表面216に達しない。ブラインド・ビア218は、レーザ・アブレーション・プロセスを使用して、又は、基板112の中にビア118が形成されたときに図5Aに関して本明細書で説明した他の任意の方法で基板212に形成することができる。ブラインド・ビア218は、基板212の内面ないし側壁220によって規定される。ブラインド・ビア218の最上端222を規定する基板212の部分は破線で示されており、この線は図を見やすくするために後続の図面では省かれる。

【0038】

図6Aの例示的な実施の形態では、ブラインド・ビア218はまた、細い線224で示すカバー層225で密閉可能にカバー又はキャップされた、基板212を貫通して延びる(図5Aのビア118と実質的に同様の)開口を基板212に含むことができる。カバー層225はブラインド・ビア218を実質的に密閉するので、カバーされたビアは本質的にブラインド・ビア218と実質的に同じように充てんされる。したがって、ブラインド・ビア218の底213を形成するカバー層225にもシード層を付着させることができ

る。例示的な他の実施の形態では、カバー層225は、基板212にブラインド・ビア218が形成される前に基板212に付着させた金属層を含むことができる。次いでレーザ・アブレーションを使用してブラインド・ビア218を途中まで形成し、次いでこれを、カバー層225の金属の表面で止まるドライエッチングを使用して完成させることができる。必要ならばブラインド・ビア218をパッシベーション層(図示せず)で絶縁することができる。

【0039】

図6Aの実施の形態を使用してブラインド・ビア218を形成することによって、汚染物質及び他のプロセス材料がウェーハ・チャック217又は他の支持構造に付着し又はこれらを汚染することを防ぐことができる。ウェーハ・チャック217は、製造プロセス期間に半導体構成部品200を支持するために使用することができ、後続の図面ではウェーハ・チャック217の図示が省かれる。

【0040】

ブラインド・ビア218の内面220を洗浄して、破片、残留した材料、又はブラインド・ビア218の形成によって不利な影響を受けた基板材料を除去することができる。洗浄後の内面220は、基板212の種類に適した誘電材料又は絶縁材料の層で基板212の内部表面220をコーティングすることによって、被膜保護することができる。図を見やすくするため図6Aにはパッシベーション層が示されていないが、当業者には明らなように、ブラインド・ビア218のパッシベーション層は、図5Aに関して説明された絶縁層126と実質的に同じ層とすることができる。さらに、基板212の材料によってはパッシベーション層を省くことができる。

【0041】

図6Bを参照すると、基板212の第1の表面214及びブラインド・ビア218の内面220に導電性金属のシード層228が形成された半導体構成部品200が示されている。この図示の実施の形態ではシード層228はTiNであり、シード層228はCVDによって付着される。しかし、シード層228は、図5Bのシード層128に関して本明細書で説明された他の任意の材料を含むことができる。

【0042】

基板212の第1の表面214を覆うシード層228の部分は、図6Cに示すように、基板212の第1の表面214を露出させるためにCMPによって除去される。シード層228は、本明細書で以前に説明した公知の任意のプロセスを使用して除去することができることは明白である。図6Dに示すように、本明細書で以前に説明した無電解付着プロセスを使用して、シード層228の上に導電層230が付着される。基板212の第1の表面214にはシード層228が存在しないため、基板212の第1の表面214には導電層230が付着しない。導電層230は、図5Dの導電層130に関して本明細書で説明した任意の導電性金属を含むことができ、導電層230に利用される金属の種類と厚さは、半導体構成部品200の所望の導電率及び最終的な使用に応じて変化する。

【0043】

例示的な他の実施の形態では、CMPの前にシード層228の上にレジスト層229が置かれる。レジスト229の存在は、CMPプロセスによって生み出される粒子がブラインド・ビア218を汚染することを防ぐ。CMPの後、レジスト229は公知の技法を使用して除去され、その結果、続く導電層230の付着のための清潔な表面が得られる。

【0044】

シード層228に導電層230が付着されたときに、導電層230の一部232が、基板212の第1の表面214の平面を越えて延びる可能性がある。これが起きた場合には、図5Eに関して本明細書で以前に説明したように、第1の表面214の平面を越えて延びた導電層230の部分232を除去することができ、これによって図6Eの半導体構成部品200が得られる。他の例示的な実施の形態では、基板212の第1の表面214の平面よりも上に延びている導電層230の部分232をそのまま残し、これを少なくとも部分的に使用して、基板212の第1の表面214に続いて構築されるボンド・パッド(図6Hに図示されている)の少なくとも一部を形成することができる。

【0045】

他の例示的な実施の形態では、浸漬めっきプロセスを使用して導電層230を銀又は金でライニングすることができる。導電層130がニッケル又はコバルトを含む場合、銀及び金はこれらよりも貴であるので、ニッケル又はコバルトは銀又は金に置き換えられる。導電層130に銀又は金のライニングを含めることは、導電率を高め、半田を濡らすのを助ける。

【0046】

図6Eに示すように、ブラインド・ビア218は、基板212の第1の表面214から実質的に基板212を貫通してブラインド・ビア218の底213まで延びる開口であって、ブラインド・ビア218の底213を覆う導電層230によって実質的に取り囲まれた開口234を含む。ブラインド・ビア218の開口234は、図6Fのクロスハッチング線で示すように、充てん材料236で充てんされる。図5Fに関して本明細書で以前に説明したとおり、充てん材料236は、充てんされたブラインド・ビア218の所望の導電率に応じて導電材料又は非導電材料を含むことができる。

【0047】

基板212の第2の表面216は、CMPなどの研磨平坦化プロセス又は公知の他の適当な除去プロセスを使用して半導体構成部品200から除去される。図6Gに示すように、基板212の第2の表面216にブラインド・ビア218が露出するように、基板212の材料は、図6Fの破線240によって示す深さまで除去される。当該技術分野で知られており且つ図6Hに示すように、ブラインド・ビア218の反対側の端にボンド・パッド238が形成される。この例示的な実施の形態の変形例では、ブラインド・ビア218が基板212の中をカバー層225まで延びる場合には、図6Aに関して説明したように、カバー層225を除去して、導電層230でライニングされ且つ充てん材料236で充てんされたブラインド・ビア218を露出させることができる。

【0048】

本発明の方法における活動の他の例示的な実施の形態が図7A及び7Bに示されている。半導体構成部品は全体として200′で示される。半導体構成部品200′は、第1の表面214及び反対側の第2の表面216を有する基板212を含む。基板212の第1の表面214にはバリア層203が形成される。バリア層203は、自体にシード層228が付着することを防ぐ材料を含む。バリア層203は、二酸化シリコン、窒化シリコンなどの酸化物含有材料又は窒化物含有材料を含むことができる。バリア層203を貫通して基板212にブラインド・ビア218が形成される。本明細書で以前に論じたとおり、ブラインド・ビア218の中にシード層228及び導電層230が形成され、その後、ブラインド・ビア218の残りの開口234が充てん材料で充てんされる。次いで、以前に説明したとおりに導電性のブラインド・ビア218の製造を完了させることができる。

【0049】

次に図8を参照すると、本発明の方法を使用して製造された半導体構成部品300の部分断面図が示されている。半導体構成部品300は、導電性ビア318を有する基板312を含む。導電性ビア318は、充てん材料336と、半導体構成部品300の反対側の表面に位置するボンド・パッド338間の電気接続を形成する環状の導電性ライナ330とを含む。

【0050】

半導体構成部品300は、コンタクト・パッド342又は他の導電性構造にビア318を電気的に接続する回路トレース340又は他の相互接続及びコンタクト構造を含むことができる。また、回路トレース340又は他の導電性構造は、半導体構成部品300の回路を、基板312の反対側に形成された集積回路などの他の回路に、半導体構成部品300の上又は下に配置された1つのスタックにおける他の半導体構成部品の回路に、インターポーザに、コンタクタ・ボードに、或いはマイクロプロセッサなどの他の半導体構成部品を担持するマザーボード、モジュールボードなどのキャリア基板に接続するのに使用することができる。さらに、ボンド・パッド338が形成されるブランケット材料層をパターン形成して、ビア318からコンタクト・パッド342に達する回路トレース340を規定することもできる。このように、導電性ビア318を使用して、基板312の第1の表面314のコンタクト・パッド342を、基板312の第2の表面316のコンタクト・パッド342に電気的に接続することができる。

【0051】

先に述べたとおり、半導体構成部品300の基板312は、様々な半導体構成部品を接続するためのインターポーザとして、半導体試験基板(コンタクタ・ボード)として、又は半導体チップを接続することができるよりレベルのパッケージを形成するキャリア基板として設計し、製造することができる。能動回路を有する半導体デバイスとして構成される場合には、半導体構成部品300のボンド・パッド338又はコンタクト・パッド342を、試験基板又はキャリア基板上の端子パッドのパターンに対応するパターンに配置することができる。インターポーザ又はコンタクタ・ボードとして使用される場合には、ボンド・パッド338又はコンタクト・パッド342を、基板312の一方の面で試験基板又はキャリア基板の端子パッドに対応し、もう一方の面で、接触される半導体デバイス上のボンド・パッド又は他のI/O位置に対応するパターンに配置することができる。

【0052】

次に図9を参照すると、本発明の導電性ビアを含むシステム400の一つの実施の形態が示されている。システム400は、スタティック・ランダムアクセス・メモリ(SRAM)、ダイナミック・ランダムアクセス・メモリ(DRAM)又は公知の他のメモリ・デバイスなどの少なくとも1つのメモリ・デバイス402を含み、この少なくとも1つのメモリ・デバイス402は、本発明の方法を使用して製造された少なくとも1つの導電性ビアを含む。メモリ・デバイス402は、当該技術分野で公知の特定の機能を実行するようにプログラムすることができるマイクロプロセッサ404に動作可能に結合される。

【0053】

上で示した本発明の実施の形態は、低コストの材料を使用して製造することができ、単純な方法を要し、実質的にボイド及びキーホールを含まない頑強な電気相互接続を与える貫通ビアの形態の電気相互接続を開示する。本発明は様々な例示的な実施の形態に関して図示して説明してきたが、本発明の範囲又は必須の特性から、様々な追加、削除及び変更が企図される。さらに、本発明は半導体デバイス又はインターポーザの文脈で説明されたが、本発明は、半導体構成部品を用いて製造された任意のデバイス又は構成部品に電気相互接続を形成するのに有用である。したがって、本発明の範囲は、以上の説明ではなく、添付の請求項によって示される。添付の請求項の等価物の意味及び範囲に含まれる全ての変更は、添付の請求項の範囲に包含される。

【特許請求の範囲】

【請求項1】

基板に導電性ビアを形成するための方法であって、

第1の表面及び対向する第2の表面を有する基板を設けるステップと、

前記基板の前記第1の表面に部分的にのみ前記基板の中に広がる少なくとも1つのブラインドビアを形成するステップと、

酸化材料によって前記少なくとも1つのブラインドビアの表面をパッシベーションするステップと、

前記少なくとも一つのブラインドビアの前記酸化材料の表面に銅を含むシード材料を、前記シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、前記基板の前記第1の表面を露出させるように形成するステップと、

前記シード材料の上に導電性材料を前記少なくとも一つのブラインドビアを充填するように無電解めっきするステップと、

前記少なくとも一つのブラインドビアの前記導電性材料を露出させるために前記基板の前記第2の表面に研磨平坦化を実施するステップと、

を含むことを特徴とする方法。

【請求項2】

前記第1の表面に前記少なくとも1つのブラインドビアを形成するステップが、レーザ・アブレーション、ドライエッチング及びウェットエッチングのうちの少なくとも1つを

含むことを特徴とする請求項1に記載の方法。

【請求項3】

前記酸化材料により前記少なくとも一つのブラインドビアの表面をパッシベーションするステップの前に、前記少なくとも1つのブラインドビアの表面を洗浄するステップをさらに含むことを特徴とする請求項1に記載の方法。

【請求項4】

前記少なくとも一つのブラインドビアの前記導電性材料の少なくとも一部分の上に重なる少なくとも1つのボンド・パッドを、前記基板の前記第1の表面と前記対向する第2の表面とのうちの少なくとも一方の表面に形成するステップをさらに含むことを特徴とする請求項1に記載の方法。

【請求項5】

前記少なくとも一つのブラインドビアの前記酸化材料の表面に前記シード材料を、前記シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、前記基板の前記第1の表面を露出させるように形成させるステップであって、

前記基板の前記第1の表面及び前記少なくとも1つのブラインドビアの前記酸化材料の表面にシード材料を付着させるステップと、

前記少なくとも一つのブラインドビアの内部のシード材料を保持する一方で、前記基板の前記第1の表面を露出させるために、少なくとも前記基板の前記第1の表面の上にある前記シード材料を全面的に除去するステップと、

を含むステップを更に含むことを特徴とする請求項1に記載の方法。

【請求項6】

前記少なくとも一つのブラインドビアの前記酸化材料の表面に前記シード材料を付着させるステップが、スパッタリングを使用して前記酸化材料の表面に銅を付着させるステップを含むことを特徴とする請求項1に記載の方法。

【請求項7】

前記基板の前記第1の表面の上にある前記シード材料を全面的に除去するステップが、前記基板の前記第1の表面上にある前記シード材料を全面的に除去するための研磨平坦化プロセスを含むことを特徴とする請求項6に記載の方法。

【請求項8】

前記シード材料を前記導電材料で無電解めっきするステップが、前記シード材料を金属材料で無電解めっきするステップを含むことを特徴とする請求項1に記載の方法。

【請求項9】

前記銅を含むシード材料を前記導電材料で無電解めっきするステップが、前記シード材料に銅を無電解めっきするステップを含むことを特徴とする請求項1に記載の方法。

【請求項10】

前記少なくとも1つのブラインドビアを形成するステップの前に前記基板の前記第1の表面をバリア材料で覆うステップをさらに含むことを特徴とする請求項1に記載の方法。

【請求項1】

基板に導電性ビアを形成するための方法であって、

第1の表面及び対向する第2の表面を有する基板を設けるステップと、

前記基板の前記第1の表面に部分的にのみ前記基板の中に広がる少なくとも1つのブラインドビアを形成するステップと、

酸化材料によって前記少なくとも1つのブラインドビアの表面をパッシベーションするステップと、

前記少なくとも一つのブラインドビアの前記酸化材料の表面に銅を含むシード材料を、前記シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、前記基板の前記第1の表面を露出させるように形成するステップと、

前記シード材料の上に導電性材料を前記少なくとも一つのブラインドビアを充填するように無電解めっきするステップと、

前記少なくとも一つのブラインドビアの前記導電性材料を露出させるために前記基板の前記第2の表面に研磨平坦化を実施するステップと、

を含むことを特徴とする方法。

【請求項2】

前記第1の表面に前記少なくとも1つのブラインドビアを形成するステップが、レーザ・アブレーション、ドライエッチング及びウェットエッチングのうちの少なくとも1つを

含むことを特徴とする請求項1に記載の方法。

【請求項3】

前記酸化材料により前記少なくとも一つのブラインドビアの表面をパッシベーションするステップの前に、前記少なくとも1つのブラインドビアの表面を洗浄するステップをさらに含むことを特徴とする請求項1に記載の方法。

【請求項4】

前記少なくとも一つのブラインドビアの前記導電性材料の少なくとも一部分の上に重なる少なくとも1つのボンド・パッドを、前記基板の前記第1の表面と前記対向する第2の表面とのうちの少なくとも一方の表面に形成するステップをさらに含むことを特徴とする請求項1に記載の方法。

【請求項5】

前記少なくとも一つのブラインドビアの前記酸化材料の表面に前記シード材料を、前記シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、前記基板の前記第1の表面を露出させるように形成させるステップであって、

前記基板の前記第1の表面及び前記少なくとも1つのブラインドビアの前記酸化材料の表面にシード材料を付着させるステップと、

前記少なくとも一つのブラインドビアの内部のシード材料を保持する一方で、前記基板の前記第1の表面を露出させるために、少なくとも前記基板の前記第1の表面の上にある前記シード材料を全面的に除去するステップと、

を含むステップを更に含むことを特徴とする請求項1に記載の方法。

【請求項6】

前記少なくとも一つのブラインドビアの前記酸化材料の表面に前記シード材料を付着させるステップが、スパッタリングを使用して前記酸化材料の表面に銅を付着させるステップを含むことを特徴とする請求項1に記載の方法。

【請求項7】

前記基板の前記第1の表面の上にある前記シード材料を全面的に除去するステップが、前記基板の前記第1の表面上にある前記シード材料を全面的に除去するための研磨平坦化プロセスを含むことを特徴とする請求項6に記載の方法。

【請求項8】

前記シード材料を前記導電材料で無電解めっきするステップが、前記シード材料を金属材料で無電解めっきするステップを含むことを特徴とする請求項1に記載の方法。

【請求項9】

前記銅を含むシード材料を前記導電材料で無電解めっきするステップが、前記シード材料に銅を無電解めっきするステップを含むことを特徴とする請求項1に記載の方法。

【請求項10】

前記少なくとも1つのブラインドビアを形成するステップの前に前記基板の前記第1の表面をバリア材料で覆うステップをさらに含むことを特徴とする請求項1に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図5F】

【図5G】

【図6A】

【図6B】

【図6C】

【図6D】

【図6E】

【図6F】

【図6G】

【図6H】

【図7A】

【図7B】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図5F】

【図5G】

【図6A】

【図6B】

【図6C】

【図6D】

【図6E】

【図6F】

【図6G】

【図6H】

【図7A】

【図7B】

【図8】

【図9】

【公開番号】特開2012−235134(P2012−235134A)

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願番号】特願2012−141907(P2012−141907)

【出願日】平成24年6月25日(2012.6.25)

【分割の表示】特願2006−528112(P2006−528112)の分割

【原出願日】平成16年9月21日(2004.9.21)

【出願人】(595168543)マイクロン テクノロジー, インク. (444)

【Fターム(参考)】

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願日】平成24年6月25日(2012.6.25)

【分割の表示】特願2006−528112(P2006−528112)の分割

【原出願日】平成16年9月21日(2004.9.21)

【出願人】(595168543)マイクロン テクノロジー, インク. (444)

【Fターム(参考)】

[ Back to top ]