小数部の入出力位相に基づいたデジタル位相同期ループ動作

【課題】デジタルPLL(DPLL)は、入出力位相の小数部に基づいて動作を提供する。

【解決手段】DPLLは、入力位相を得るために少なくとも1つの入力信号を蓄積し、例えばタイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいて出力位相の小数部を決定する。DPLLは、入力位相の小数部および出力位相の小数部に基づいて位相エラーを決定する。その後、DPLLは、位相エラーに基づいて発振器のための制御信号を生成する。別の態様では、合成されたアキュムレータを含むDPLLは、参照信号に基づいて、発振信号サイクルの数のトラッキングを保持することにより粗い出力位相を決定する。

【解決手段】DPLLは、入力位相を得るために少なくとも1つの入力信号を蓄積し、例えばタイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいて出力位相の小数部を決定する。DPLLは、入力位相の小数部および出力位相の小数部に基づいて位相エラーを決定する。その後、DPLLは、位相エラーに基づいて発振器のための制御信号を生成する。別の態様では、合成されたアキュムレータを含むDPLLは、参照信号に基づいて、発振信号サイクルの数のトラッキングを保持することにより粗い出力位相を決定する。

【発明の詳細な説明】

【分野】

【0001】

現在の開示は、エレクトロニクス、さらに、特にデジタル位相同期ループに一般に関係がある。

【背景】

【0002】

位相同期ループ(PLL)は、多くのエレクトロニクス回路の不可欠な部分であり、通信回路において特に重要である。例えば、デジタル回路は、同期回路(synchronous circuit)をトリガするためにクロック信号を使用する、例えば、フリップフロップである。送信機と受信機は、局部発振器(LO)の信号を周波数アップコンバーション(upconversion)およびダウンコンバーション(downconversion)にそれぞれ使用する。無線通信システムのための無線デバイス(例えば、携帯電話)は、一般的に、送信機および受信機のためのデジタル回路およびLO信号にクロック信号を使用する。クロックおよびLO信号は発振器で生成される。そして、それらの周波数はPLLでしばしばコントロールされる。

【0003】

PLLは、一般的に、発振器からの発振信号の周波数および/または位相を調節するために使われた様々な回路ブロックを含む。これらの回路ブロックは、比較的大量の電力を消費するかもしれない。それは携帯電話のような携帯機器には不適当かもしれない。したがって、パフォーマンスを犠牲にせずに、PLLの消費電力を低減するためのテクニックに関する技術が必要である。

【概要】

【0004】

よいパフォーマンスおよび低い消費電力を有しているデジタルPLL(DPLL)は、ここに記述される。DPLLは、アナログ回路でよりむしろデジタルでインプリメントされた回路ブロックを備えたPLLである。デジタルインプリメーションは、低コスト、少ない回路面積のような特定の利点を備えてもよい。

【0005】

1つの態様では、DPLLは入出力位相の小数部(fractional portion)に基づいて動作してもよい。DPLLは、入力位相を得るために、少なくとも1つの入力信号(それは変調信号を含んでもよい)を蓄積してもよい。DPLLは、例えば、タイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいた出力位相の小数部を決定してもよい。その後、DPLLは、入力位相の小数部および出力位相の小数部に基づいた位相エラーを決定してもよい。小数部は、発振信号の1つのサイクルの範囲を有してもよい。1つのデザインでは、DPLLは、出力位相の小数部と入力位相の小数部との間の位相差を決定してもよい。その後、結果の位相エラーが所定範囲内(例えば、マイナス2分の1発振サイクルからプラス2分の1発振サイクルまで)であるように、DPLLは、必要に応じて、位相差から所定値(例えば、1発振サイクル)を加えてもよい、または、所定値を引いてもよい。DPLLは、位相エラーに基づいた発振器に関する制御信号を生成してもよい。

【0006】

別の態様では、DPLLは合成されたアキュムレータおよびTDCを含んでいてもよい。合成されたアキュムレータは、発振信号のサイクル数のトラッキングを保持することにより、粗い(coarse)出力位相を決定してもよい。合成されたアキュムレータは、発振信号の周波数より低い周波数を持っている参照信号に基づいて更新されてもよい。TDCは、発振信号と参照信号との間の位相差に基づいて細かい(fine)出力位相を決定してもよい。DPLLは、粗い出力位相、細かい出力位相および入力位相に基づいて、発振器のための制御信号を生成してもよい。

【0007】

開示の種々の態様および特徴は、さらに詳細に下に記述される。

【図面の簡単な説明】

【0008】

【図1】図1は、DPLLのブロック図を示す。

【図2】図2は、TDCに関する入力に対する出力のプロットを示す。

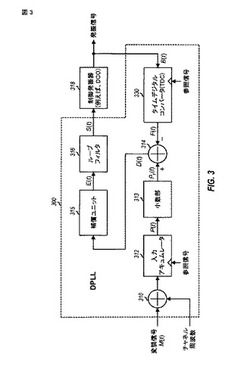

【図3】図3は、小数入出力位相に基づいて動作するDPLLのブロック図を示す。

【図4】図4は、合成されたアキュムレータの動作を示す。

【図5】図5は、合成されたアキュムレータを備えたDPLLのブロック図を示す。

【図6】図6は、合成されたアキュムレータを備えた位相検出器のブロック図を示す。

【図7】図7は、TDCの概略図を示す。

【図8】図8は、合成されたアキュムレータを備えた別のDPLLのブロック図を示す。

【図9】図9は、通信デバイスのブロック図を示す。

【図10】図10は、発振器をコントロールするプロセスを示す。

【図11】図11は、発振器をコントロールする別のプロセスを示す。

【詳細な説明】

【0009】

図1は、DPLL100のデザインのブロック図を示す。DPLL100内では、アナログ加算器110は、通信のために使用された周波数チャネルの中心周波数に対する静的な値で変調信号M(t)を受け取りそして合計する。入力アキュムレータ112は、アナログ加算器110の出力を蓄積し、入力位相P(t)を提供する。蓄積は、基本的に周波数を位相に変換する。入力アキュムレータ112は、参照信号によって引き起こされる。それは、frefの固定周波数を持っていてもよい。DPLL100内の様々な回路ブロックおよび信号も参照信号で更新される。また、tは参照信号のためのインデックスである。

【0010】

無線周波数(RF)アキュムレータ122は、各発振サイクルの1つ(それは制御発振器118からの発振信号の1つのサイクルである)によってインクリメントする。ラッチ124は、参照信号が引き金となって起きた時、RFアキュムレータ122の出力をラッチし、そして、粗い/整数部の出力位相A(t)を提供する。TDC130は、発振信号と参照信号を受け取り、参照信号が引き金となって起きた時、発振信号の位相を決定し、発振信号と参照信号との間の細かい/小数部の位相差を示すTDC出力F(t)を提供する。TDC130は、DPLL100のための小数位相センサをインプリメントする。アナログ加算器126は、粗い出力位相A(t)およびTDC出力F(t)を受け取りそして合計し、そして、出力位相B(t)の予測であるフィードバック位相Z(t)を提供する。

【0011】

アナログ加算器114は、入力位相P(t)からフィードバック位相Z(t)を受け取りそして引き、位相エラーE(t)を提供する。ループフィルタ116は、位相エラーをフィルタし、発振器118に制御信号S(t)を供給する。ループフィルタ116は、DPLL100のループ・ダイナミクスをセットする。制御信号は、発振信号の位相が変調の位相に続くように、発振器118の周波数を調節する。制御信号は、例えば、8、12、16、20、24、またはそれ以上のビットの分解能である、分解能の任意の適切なビット数を有してもよい。

【0012】

発振器118は、デジタル制御発振器(DCO)、電圧制御発振器(VCO)、電流制御発振器(ICO)、または周波数を制御信号によって調節することができるいくつかの他のタイプの発振器であってもよい。発振器118は、DPLL100が使用されるアプリケーションによって決定されてもよいfoscの公称周波数(nominal frequency)で動作してもよい。例えば、DPLL100は無線通信デバイスに使用されてもよい。また、foscは何百ものメガヘルツ(MHz)またはわずかのギガヘルツ(GHz)かもしれない。参照信号は、水晶発振器(XO)、電圧制御水晶発振器(VCXO)、温度補償水晶発振器(TCXO)または正確な周波数を持っているいくつかの他のタイプの発振器に基づいて生成されてもよい。参照信号の周波数は、発振信号の周波数よりはるかに低くあってもよい。例えば、frefは10MHzであってもよく、foscは数GHzであってもよい。

【0013】

入力位相P(t)、出力位相B(t)およびフィードバック位相Z(t)は、発振サイクルのユニットで与えられてもよい。図1で示されたデザインにおいて、DPLL100のフィードバック経路は、(i)発振サイクルの整数で与えられる粗い出力位相を測定するためのRFアキュムレータ122、および(ii)1つの発振サイクルの小数によって与えられる細かい出力位相を測定するためのTDC130、を含んでいる。RFアキュムレータ122およびTDC130のコンビネーションは、RFアキュムレータ122からの粗い/整数部およびTDC130からの細かい/小数部を含んでいるトータルの出力位相B(t)を測定する。ここにある記述において、「細かい(fine)」と「小数(fractional)」の用語は交換可能に使用される、そして「粗い(coarse)」と「整数(integer)」も交換可能に使用される。出力位相の予測であるフィードバック位相Z(t)は、ループフィルタ116のための位相エラーを得るために、入力位相から引かれる。

【0014】

DPLL100の中のブロックはすべて、RFアキュムレータ122を除いて、参照信号に基づいて動作されてもよい。RFアキュムレータ122は、発振信号に基づいて動作する。それは、参照信号より周波数において何倍も高いかもしれない。従って、RFアキュムレータ122は、DPLL100のトータル消費電力の大きな小数(例えば、およそ50%)に関与するかもしれない。したがって、バッテリー電源を節約するために、RFアキュムレータ122を備えたDPLL100をターンオフする動作は望ましいかもしれない。

【0015】

参照信号の1サイクルである1つの基準サイクルにおいて、トータル出力位相θtotalは次のように与えられてもよい。

【数1】

【0016】

トータル出力位相は、発振サイクルのユニットで与えられ、整数部θintおよび小数部θfracに分割されてもよい。整数部θintは、発振サイクルの整数または2πラジアンの整数倍で与えられてもよい。小数部θfracは、1発振サイクルの小数によってまたは0から2πラジアンの範囲内で与えられてもよい。整数部θintおよび小数部θfracは、以下のように与えられてもよい。

【数2】

【数3】

【0017】

RFアキュムレータ122は、基準サイクル内の発振サイクルの数の決定により、出力位相の整数部を決定してもよい。TDC130は、参照信号の位相に対する発振信号の位相の比較により、出力位相の小数部を決定してもよい。

【0018】

図2は、TDC130の入力に対する出力のプロットを示す。水平軸は出力位相B(t)を示す。それはTDC130への入力である。垂直軸は、TDC出力F(t)を示す。水平および垂直軸の両方については、1発振サイクルは2πに等しい。図2に示されるように、TDC130は、入力に対する不連続な出力を有する。TDC出力F(t)は、0から2πまでの出力位相B(t)と等しい。その後、B(t)=2πの時、0にラップアラウンドする。その後、2πから4πまでのB(t)で直線的に増加する。その後、B(t)=4πの時、0にラップアラウンドする、など。

【0019】

TDC出力での不連続は、DPLLが適切に動作するために取り組まれるべきである。これらの不連続に取り組む方法の1つは、出力位相B(t)が2πを超える回数の跡を追うために、RFアキュムレータ122を使用することである。そのとき、RFアキュムレータ122の出力は、不連続を避ける0から2πまでの動作範囲を制限するために、2πの整数倍で、TDC出力に加えられてもよい。しかしながら、RFアキュムレータ122は、その高い動作周波数のために多くの電流を消費してもよい。

【0020】

図2に示されるように、TDC出力はすべての2πをジャンプするが、連続的な位相跳躍間、2πの範囲を超えて連続する。出力位相の変化率が制限された場合、それらが生じるとともに、TDC出力での位相跳躍は確認されて説明されてもよい。例えば、M(t)=0のため、DPLL100は調節されていないかもしれない。P(t)はすべてのtのための小数部がない。初期条件は、E(0)=0のため、F(0)=0、A(0)=P(0)でもよい。DPLLがロックされるので、制御信号S(t)は一定値を有してもよい。出力位相がわずかに(例えば、0.1ラジアンによって)増加する場合、そのとき、TDC130はこの位相を測定し、補償信号(例えば、E(t)=−0.1ラジアン)を提供するだろう。しかしながら、出力位相B(t)がわずかに(例えば、−0.1ラジアンによって)減少する場合、そのとき、TDC130は大きな値(例えば、2π−0.1ラジアン)を出力するだろう。そのとき、位相エラーは、1発振サイクル毎に間違われるだろう。それは、逆に、DPLLのパフォーマンスに影響を与えるかもしれない。

【0021】

しかしながら、出力位相の変化率が制限された場合、基準サイクル内のTDC出力のどんな大規模な変更も、位相跳躍に起因してもよい。そのとき、1発振サイクルは、正確な位相値を得るために、TDC出力に追加され、または、TDC出力から引かれてもよい。上記の例で、TDC出力のための2π−0.1ラジアンの大きな値は、位相跳躍に起因されてもよい。2πは、この値から引かれてもよい。−0.1ラジアンは、正確なTDC出力値として提供されてもよい。

【0022】

一態様では、DPLLは、RFアキュムレータを使用せずに、TDCからの出力位相の小数および入力位相の小数部に基づいて操作される。各基準サイクルでは、TDC出力は、入力位相の小数部から以下のように引かれてもよい。

【数4】

【0023】

ここで、Pf(t)は、入力位相の小数部で、0から2πまでの範囲である。D(t)は、入力位相の小数部と出力位相の小数部であるTDC出力との間の差である。

【0024】

入力位相の変化率および出力位相の変化率は、制限されていると仮定されてもよい。また、位相エラーは、各基準サイクルの−πからπの範囲内にあると仮定されてもよい。位相エラーは、以下のように決定されてもよい。

【数5】

【0025】

方程式(5)は、D(t)が+πおよび−πのしきい値と比較されたデザインを示す。D(t)は、他のしきい値と比較されてもよい。

【0026】

方程式(5)に示されるように、位相差がπより大きいまたはπより小さい場合、位相跳躍は生じたと仮定される。この場合、2πは、合成の位相エラーがゼロ近くであるように、位相差から追加されるかまたは引かれてもよい。

図3は、もっぱら入力位相および出力位相の小数部に基づいて動作するDPLL300のデザインのブロック図を示す。DPLL300内では、図1でアナログ加算器110および入力アキュムレータ112に関して上述されるように、アナログ加算器310および入力アキュムレータ312は、動作し、そして、入力位相P(t)を提供する。ユニット313は、入力位相を受け取り、小数部Pf(t)を提供する。TDC330は、制御発振器318からの発振信号および参照信号を受け取り、発振信号と参照信号との間の細かい/小数位相差を示すTDC出力F(t)を提供する。アナログ加算器314は、小数入力位相Pf(t)からTDC出力F(t)を引き、そして、位相差D(t)を提供する。ユニット315は、位相差を受け取り、例えば、方程式(5)に示されるように、位相エラーE(t)を決定する。ループフィルタ316は、位相エラーをフィルタし、発振器318に制御信号S(t)を供給する。

【0027】

1つのデザインでは、RFアキュムレータは、変調信号のために発振器318をロックするために最初に使用されてもよい。(図3中で示されない)ロック検出器は、例えば、位相エラーの大きさの観察によって、DPLL300がロックしたかどうか判断してもよい。DPLL300がロックした後、RFアキュムレータはディセーブルになってもよい。また、入力位相および出力位相の小数部だけが、DPLLを操作するために使用されてもよい。

【0028】

別の態様では、合成されたアキュムレータは、粗い/整数出力位相を決定するために使用されてもよい。合成されたアキュムレータは、発振信号の代わりに参照信号に基づいて動作し、したがって、RFアキュムレータより非常に少ない電力を消費してもよい。

【0029】

図4は、合成されたアキュムレータでDPLLの動作を例証する。図4中で示される例で、発振信号の周波数は、参照信号の周波数の3.25倍である。また、3.25の周波数制御ワード(FCW)は、図1中のチャネル周波数として提供されてもよい。簡単にするために、DPLLは、発振信号と参照信号の立ち上がりエッジに基づいて、ロックされ引き起こされると仮定される。

【0030】

発振信号は、図4の一番上の第1のラインで示される。また、参照信号は、第2のラインで示される。RFアキュムレータの出力は、第3のラインで示される。RFアキュムレータは、発振信号の各立ち上がりエッジの一つによって増加し、それらが生じるとき、発振サイクルのトラックをキープする。RFアキュムレータの出力は、参照信号の各立ち上がりエッジでラッチされる。また、ラッチされた値のそれぞれは、第3のラインで円内に示される。ラッチされた値のそれぞれは、最も近い整数値へ発振サイクルの数を切り捨てることにより得られる。例えば、図4中に参照信号の第1および第2の立ち上がりエッジの間に3.25の発振サイクルがある。そして、RFアキュムレータの出力は、端数が切り捨てられた3.25に等しい、3である。図4中で示される例で、基準サイクル毎に3.25の発振サイクルがある。また、ラッチされた値は、0、3、6、9、13などである。

【0031】

理想的なTDCの出力は、第4のラインで示される。TDCは、端数を切り捨てる機能によって見落とされた出力位相の小数部を測定する。小数部は、参照信号の立ち上がりエッジと発振信号の最も近い前の立ち上がりエッジとの間の差に等しい。TDCは、参照信号の各立ち上がりエッジのために0と1.0の間の小数値を供給する。図4に示されるように、TDCの出力は周期的である。フィードバック位相は、TDCからの細かい/小数部およびRFアキュムレータからの粗い/整数部を加えることにより得られてもよい。

整数インクリメントN(t)と呼ばれる、1つの基準サイクル当たりの発振サイクルの端数を切り捨てた数は、第5のラインで示される。参照信号の各立ち上がりエッジについては、N(t)は、現在のラッチされた値と先のラッチされた値の間の差に等しい。図4中で示される例で、N(t)は、3、3、3、4、3、3、3、4、3などのシーケンスである。N(t)は、3.25の平均値を持っており、TDC出力と同じ方法で周期的である。更に、N(t)は、たった2つの可能な整数値しか持っていない。それは、DPLLがロックした後、図4中で示される例において3と4である。DPLLがナローバンド周波数変調で適用される場合さえ、2つの整数値間のこのトグリングは真実である。3つの整数値間でトグルするために、周波数変調は基準周波数frefより大きい必要があるだろう。その結果、付加的な十分な発振サイクルは、基準サイクル内に適合することができる。一般的には、ピーク変調周波数は、基準周波数のほんの少しである。例えば、ピーク変調周波数は、ほとんどMHzではないかもしれない。一方、基準周波数は、10MHzかもしれない。この場合、N(t)は、2つの可能な整数値しかない。

【0032】

N(t)が2つの可能な整数値しか取得できない場合、発振器周波数foscで動作するRFアキュムレータの使用なしでN(t)を決定することは可能かもしれない。これは、DPLLが変調される場合さえ、1つの基準サイクル当たりの少量だけによって位相エラーが変わるという事実の開発により達成されてもよい。例えば、4GHzの発振器を備えたローバンドEDGEおよびDPLL出力の4倍のディビジョンのために、ピーク周波数変調はおよそ3MHzかもしれない。基準周波数は、およそ57MHzかもしれない。また、1つの基準サイクル当たりの入力位相の最大の変更は、基準サイクルのおよそ0.3ラジアンまたは約5%かもしれない。したがって、変調は、2π位相跳躍を不明瞭にしない。DPLLの操作は、本質的に不変である。

【0033】

N(t)は、以下のようにRFアキュムレータを使用せずに決定されてもよい。各基準サイクルまたは最新間隔tについては、N(t)の正確な値は、N(t)のための2つの仮説の評価により決定されてもよい。第1の仮説aは、N(t)が2つの値の中でより小さい場合のためである。それは、NLとして表示され、図4で示される例のために3に等しい。第2の仮説bは、N(t)が2つの値の中でより大きい場合のためである。それは、NHとして表示され、図4で示される例のために4に等しい。より小さな位相エラー大きさを提供する仮説は、選択されてもよい。また、正確な仮説のためのNLまたはNHは、発振サイクルの数のランニングカウントを格納するレジスタを更新するために使用されてもよい。このレジスタは、粗い出力位相C(t)を提供する。それは、発振サイクルの整数の中で与えられる。

【0034】

2つの仮説aおよびbは、以下のように評価されてもよい。レジスタは、例えば、DPLLがロックした後、入力位相P(t)の整数部に基づいて、初期化されてもよい。図4で示される例で、レジスタはゼロにするために初期化される。参照信号の第2の立ち上がりエッジで、仮説aは、Za(1)=3+0+0.25=3.25の仮定された出力位相を有する。ここで、3は仮説aのためのNL値であり、0はレジスタからの粗い出力位相C(1)であり、0.25はTDC出力値である。仮説bは、Zb(1)=4+0+0.25=4.25の仮定された出力位相を有する。ここで、4は仮説bのためのNH値である。2つの仮説用の仮定された出力位相Za(1)およびZb(1)は、入力位相P(1)=3.25と比較される。Za(1)はZb(1)よりP(1)に接近しているので、仮説aは正確な仮説である。その後、レジスタは3ずつ更新される。それは、正確な仮説aのためのNL値で、3の粗い出力位相を格納する。

【0035】

参照信号の第3の立ち上がりエッジにおいて、仮説aは、Za(2)=3+3+0.5=6.5の仮定された出力位相を有する。ここで、1つ目の3は仮説aのためのNL値であり、2つ目の3はレジスタからの粗い出力位相C(2)であり、0.5はTDC出力値である。仮説bは、Zb(2)=4+3+0.5=7.5の仮定された出力位相を有する。ここで、4は仮説bのためのNH値である。2つの仮説用の仮定された出力位相Za(2)およびZb(2)は、入力位相P(2)=6.5と比較される。Za(2)はZb(2)よりP(2)に接近しているので、仮説aは正確な仮説である。その後、レジスタは3ずつ更新される。それは、正確な仮説aのためのNL値であり、6の粗い出力位相を格納する。同じ処理は、個々の後の基準サイクルのために繰り返されてもよい。

【0036】

一般に、N(t)のための2つの可能な整数値は以下のように決定されてもよい。

【数6】

【0037】

ここで、NLは、N(t)のための2つの可能な整数値の中でより小さい。NHは、N(t)のための2つの可能な整数値の中でより大きい。

仮説aおよびbのための仮定された出力相は、以下のように決定されてもよい。

【数7】

【数8】

【0038】

ここで、C(t)は、基準サイクルtの中の粗い出力位相である。Za(t)は、基準サイクルtの中の仮説aのための仮定された出力位相である。Zb(t)は、基準サイクルtの中の仮説bのための仮定された出力位相である。

【0039】

仮説aおよびbのための仮定された位相エラーは、以下のように決定されてもよい。

【数9】

【数10】

【0040】

ここで、Ea(t)は、基準サイクルtの中の仮説aのための仮定された位相エラーである。Eb(t)は、基準サイクルtの中の仮説bのための仮定された位相エラーである。

粗い出力位相、以下のように更新されてもよい。

【数11】

【0041】

基準サイクルtの中の位相エラーE(t)は、以下のように決定されてもよい。

【数12】

【0042】

方程式(12)からの位相エラーは、DPLLの中のループフィルタに提供されてもよい。

【0043】

方程式(6)から(12)で示されるように、与えられた基準サイクルの中でN(t)の2つの可能な整数値間で選ぶために、2つの仮説aおよびbは評価されてもよい。入力位相に近い仮定された出力位相を有する、または、小さな位相エラーの大きさと等しい仮説が選択されてもよい。

【0044】

図5は、合成されたアキュムレータを備えたDPLL500のデザインのブロック図を示す。DPLL500の内では、図1中のアナログ加算器110および入力アキュムレータ112に関して上述されるように、アナログ加算器510および入力アキュムレータ512は動作し、入力位相P(t)を提供する。

【0045】

TDC530は、制御発振器518からの発振信号および参照信号を受け取り、発振信号と参照信号との間の位相差を示すTDC出力F(t)を提供する。位相検出器520は、発振信号、TDC出力および入力位相を受け取り、第1の位相エラーE1(t)を生成する。位相検出器520は、図1中のRFアキュムレータ122、ラッチ124およびアナログ加算器114と126に関して上述されるように動作する、RFアキュムレータ522、ラッチ524およびアナログ加算器526を含んでいる。位相検出器520は、モード信号によってイネーブル(enable)になってもよいしディセーブル(disable)になってもよい。位相検出器540は、チャネル周波数、参照信号、TDC出力および入力位相を受け取り、第2の位相エラーE2(t)を生成する。位相検出器540は、合成されたアキュムレータを含んでおり、下記に述べられるようにインプリメントされてもよい。位相検出器540は、モード信号によってイネーブルになってもよいしディセーブルになってもよい。位相検出器520または540の一方は、任意の所定のモーメントでイネーブルになってもよい。また、他方の位相検出器は、バッテリー電源を保存するためにディセーブルになってもよい。

【0046】

マルチプレクサ(Mux)514は、位相検出器520および540のそれぞれから2つの位相エラーE1(t)およびE2(t)、モード信号を受け取り、位相エラーE(t)を提供する。マルチプレクサ514は、位相検出器520がイネーブルになる場合に、位相エラーE(t)として第1の位相エラーE1(t)を提供し、位相検出器540がイネーブルになる場合に、位相エラーE(t)として第2の位相エラーE2(t)を提供する。ループフィルタ516は、位相エラーE(t)をフィルタし、発振器518に制御信号S(t)を供給する。

【0047】

1つのデザインでは、位相検出器520は、最初にイネーブルになり、変調信号への発振器518をロックするために使用されてもよい。DPLL500がロックした後、位相検出器520はディセーブルになってもよく、位相検出器540はイネーブルになってもよい。ロック検出器550は、位相検出器520から第1の位相エラーE1(t)を受け取り、DPLL500がロックしたかどうか判断する。これは、第1の位相エラーE1(t)の大きさの観察により達成されてもよい。それは、DPLL500がロックされない場合、最初に大きいかもしれないし、DPLL500がロックされる場合、小さいかもしれない。ロック検出器550は、DPLLがロックされる場合にある論理値(例えば「1」)またはDPLLがロックされない場合に他の論理値(例えば「0」)にセットされてもよいロックインジケータを提供する。モードセレクタ552は、ロックインジケータおよび図5中で示されない可能な他の入力を受け取り、モード信号を提供する。例えば、モードセレクタ552は、位相検出器540をイネーブルにし、DPLLがロックされたらすぐにまたは後で位相検出器520をディセーブルにしてもよい。位相検出器520および540の両方は、RFアキュムレータ522のスイッチを切る前に、期間のために同時にイネーブルになってもよい。ロックの損失が検知される場合(例えば、DPLL500へ致命的な妨害のために)は常にまたは他の理由の場合、モードセレクタ552は再度位相検出器520もイネーブルにしてもよい。DPLLがロックされない場合に、(図3中で示されない)RFアキュムレータの出力を備えた位相エラーを生成するために、ロック検出器550およびモードセレクタ552も、図3中でDPLL300のために使用されてもよい。

図6は、図5中の位相検出器540のデザインのブロック図を示す。このデザインでは、位相検出器540は、合成されたアキュムレータ610、仮説評価ユニット(hypotheses evaluation unit)620およびラウンディングユニット(rounding unit)630を含んでいる。ラウンディングユニット630は、チャネル周波数を受け取り、N(t)のための2つの可能な整数値を決定してもよい。それは、NLおよびNHである。または、ユニット630は、図5中のラッチ524から粗い出力位相A(t)を受け取ってもよい。DPLL500がロックされ、位相検出器520がイネーブルになる場合、粗い出力位相A(t)は、NLおよびNHの間でトグルすべきである。したがって、ユニット630は、DPLL500がロックした後、粗い出力位相A(t)の値に基づいて、NLおよびNHを決定してもよい。

【0048】

合成されたアキュムレータ610は、発振サイクルの数のトラッキングを保持するが、発振信号の代わりに参照信号に基づいて動作する。これは、DPLL500のための消費電力を非常に低減してもよい。合成されたアキュムレータ610は、レジスタ612、アナログ加算器614およびマルチプレクサ616を含んでいる。レジスタ612は、発振サイクルの整数中の現在の粗い出力位相C(t)を格納する。マルチプレクサ616は、NLおよびNH、仮説が正確な/勝利の仮説かを示すセレクト信号を受け取る。各基準サイクルでは、マルチプレクサ616は、仮説aが正確な仮説である場合にNLを提供し、仮説bが正確な仮説である場合にNHを提供する。アナログ加算器614は、レジスタ612からの現在の粗い出力位相C(t)およびマルチプレクサ616の出力を合計し、最新の粗い出力位相C(t+1)を提供する。それは、レジスタ612に格納される。レジスタ612、アナログ加算器614およびマルチプレクサ616は、方程式(11)でインプリメントする。

【0049】

ユニット620は、各基準サイクル中の2つの仮説aおよびbを評価し、正確な仮説を示すセレクト信号と同様に位相エラーE2(t)を提供する。方程式(7)で示されるように、ユニット620内では、アナログ加算器622aは、レジスタ612からの粗い出力位相C(t)、TDC出力F(t)およびNLを受け取り、合計し、仮説aのために仮定された出力位相Za(t)を供給する。方程式(9)で示されるように、アナログ加算器624aは、入力位相P(t)から仮定された出力位相Za(t)を引き、仮説aのために仮定された位相エラーEa(t)を供給する。同様に、方程式(8)で示されるように、アナログ加算器622bは、粗い出力位相C(t)、TDC出力F(t)およびNHを受け取り、合計し、仮説bに仮定された出力位相Zb(t)を供給する。方程式(10)で示されるように、アナログ加算器624bは、入力位相P(t)から仮定された出力位相Zb(t)を引き、仮説bに仮定された位相エラーEb(t)を供給する。

【0050】

セレクタ626は、2つの仮説のために仮定された位相エラーEa(t)およびEb(t)を受け取り、2つの仮定された位相エラーの小さな大きさを決定する。方程式(12)で示されるように、セレクタ626は、位相検出器540からの位相エラーE2(t)として小さな大きさで仮定された位相エラーに供給する。セレクタ626は、セレクト信号も提供する。それは、小さな仮定された位相エラー大きさを生産する正確な仮説を示す。

【0051】

図4および6は、RFアキュムレータ出力を、例えば、3.25から3まで下がる、6.5から6まで下がるなど切り捨てたデザインを示す。この場合、TDC出力F(t)は、各仮説のために粗い出力位相C(t)に加えられる。別のデザインでは、RFアキュムレータ出力は、例えば、3.25から4まで上がる、6.5〜7まで上がるなど、切り上げられる。この場合、TDC出力F(t)は、(図中で示されない)各仮説のために粗い出力位相C(t)から引かれる。一般に、仮説は、合成されたアキュムレータがどのように更新されるかと一致するやり方で評価されてもよい。

【0052】

図6は、2つの整数値NLおよびNHがDPLL500の通常動作の間に可能な場合用の合成されたアキュムレータ610および仮説評価ユニット620のデザイン例を示す。N(t)は、例えば、広帯域の変調またはDPLL500が初めにパワーアップするために、2つを超える可能な整数値を有してもよい。広帯域の変調による大規模な周波数差は、合成されたアキュムレータからの粗い出力位相に補正率(correction factor)を適用することにより補正されてもよい。一般に、1つの仮説は、N(t)の個々の可能な整数値のために評価されてもよい。最も小さな位相エラーを備えた仮説は、選択されてもよい。合成されたアキュムレータは、選択された仮説のためにN(t)値に基づいて更新されてもよい。

1つのデザインでは、例えば、図5に示されるように、DPLLは、発振周波数で動作するRFアキュムレータと、基準周波数で動作する合成されたアキュムレータとの両方を含んでいる。図5に関して上述されるように、RFアキュムレータは、動作の最初に使用されてもよい。DPLLがロックした後、合成されたアキュムレータは、通常動作の間に使用されてもよい。

【0053】

別のデザインでは、DPLLは、基準周波数で動作する合成されたアキュムレータだけを含んでいる。オペレーションの最初で、さらに(例えば、3、4または恐らくより多くの)仮説は、N(t)のより多くの可能な値のために評価されてもよい。DPLLがロックした後、少数(例えば2つ)の仮説がより少数の可能なN(t)値のために評価されてもよい。選択的に、同じ数の仮説(例えば2つの仮説)は、オペレーションの最初におよび通常動作の間に評価されてもよい。ループ帯域幅は、可能なN(t)値の制限された数を備えたDPLLのために、希望の獲得パフォーマンスを達成するために選択されてもよい。

【0054】

図5中のDPLL500は、図3中のDPLL300と等価なやり方で動作してもよい。DPLL500がロックされる場合、仮定された位相の整数部(それは合成されたアキュムレータ610からの粗い出力位相C(t)である)は、入力位相の整数部と一致するべきである。これらの2つの整数部は、図6中のアナログ加算器624aおよび624bによってキャンセルされるだろう。小数部間の違いだけは、位相エラーE2(t)の中で提供されるだろう。

【0055】

図7は、図5中のTDC530のデザインの概略図を示す。TDC530は、参照信号の位相に対する発振信号の位相を比較し、分解能の多数の(B)ビットで検出された位相差を提供する。

【0056】

TDC530は、2Bの遅延素子710aから710z、2BのDフリップフロップ712aから712z、およびサーモメータバイナリコンバータ714を含んでいる。遅延素子710aから710zは、発振信号を受け取る遅延要素710aと連続して結合される。各遅延要素710は、希望の遅延分解能を得るためにインバーターおよび/または他のタイプの論理素子でインプリメントされてもよい。遅延素子710aから710zは、およそ1発振サイクルの合計遅延を提供する。例えば、発振周波数foscが4GHzである場合、1発振サイクルは250ピコセカンド(ps)である。各遅延要素710は、約250/2Bpsの遅れを提供する。

【0057】

Dフリップフロップ712aから712zは、遅延素子710aから710zの出力にそれぞれつながれたそれらのD入力と、参照信号を受け取るそれらのクロック入力を有する。各Dフリップフロップ712は、関連する遅延要素710からの出力信号をサンプリングし、コンバータ714にサンプリングされた出力を供給する。ロジックロウのDフリップフロップの数に対してロジックハイのDフリップフロップの数は、発振信号と参照信号との間の位相差を示す。この位相差は、1/2B発振サイクルの分解能を有する。コンバータ714は、Dフリップフロップ712aから712zからの2Bの出力を受け取り、これらの2Bの出力をBビット2進値に変換し、細かい/小数出力位相としてBビット2進値を提供する。

【0058】

一般に、TDC530は、分解能のビットの任意数でデザインされてもよい。例えば、Bは、希望の遅延分解能、集積回路(IC)プロセスなどにおいて利用可能な最小の遅延に応じて、8以上かもしれない。希望の遅延分解能は、DPLL500が使用されるアプリケーションに依存してもよい。

【0059】

DPLLは、様々なアプリケーションに使用されてもよい。例えば、DPLLは、周波数合成器が希望の周波数で発振信号を生成するために使用されてもよい。この場合、変調信号M(t)は、省略されるか、またはゼロにセットされてもよい。DPLLは、ポーラモジュレータ、クアドラチュアモジュレータ、位相変調器、周波数変調器、復調器などに使用されてもよい。モジュレータについては、変調信号の帯域幅は、DPLLの閉じたループ帯域幅より大きくてもよい。DPLLは、変調信号の広い帯域幅に対応するデザインでもよい。

【0060】

図8は、広帯域変調を支援するDPLL302のデザインのブロック図を示す。DPLL302は、図3中のDPLL300のブロックをすべて含んでいる。DPLL302は、スケーリングユニット320およびアナログ加算器317をさらに含んでいる。

【0061】

DPLL302は、高帯域変調を達成するために2ポイントまたはデュアルポートの変調をインプリメントする。変調信号M(t)は、ローパス変調パスおよびハイパス変調パスの両方に提供されてもよい。ローパス変調パスでは、アナログ加算器310および入力アキュムレータ312は、変調信号M(t)上で動作し、入力位相P(t)を提供する。入力アキュムレータ312による蓄積は、本質的に周波数を位相に変換する。ハイパス変調パスでは、スケーリングユニット320は、利得g(t)で変調信号M(t)を受け取り、スケールし、第2の変調信号X(t)を提供する。アナログ加算器317は、ループフィルタ316の出力と発振器318の入力との間で連結される。アナログ加算器317は、ループフィルタ316からのフィルタされた位相エラー信号およびスケーリングユニット320からの第2の変調信号X(t)を合計し、発振器318のために制御信号S(t)を供給する。

【0062】

変調信号の帯域幅は、DPLL302が使用されるアプリケーションによって決定されてもよく、DPLLの閉じたループ帯域幅より広くてもよい。DPLL302の中のローパス変調パスの帯域幅は、ループフィルタ316によって決定され、希望のノイズ・フィルタリングおよびループ・ダイナミクスを達成するために、比較的狭い(例えば、100kHz未満)かもしれない。個別のハイパスおよびローパス変調パスによって変調信号M(t)を適用することによって、DPLL302は、DPLLの閉じたループ帯域幅より広い信号の帯域幅を備えた発振器318を変調することができる。

【0063】

簡単にするために、図3、5および8は、DPLL300、500および502の機能的ブロックをそれぞれ示す。特定の詳細は、明瞭さのために省略される。例えば、遅延は、これらのDPLL内の様々な信号を適切な時間で調整するために、DPLL300、302および500の内の適切な場所に挿入されてもよい。

【0064】

図3、5および8は、変調するDPLLのいくつかのデザイン例を示す。変調するDPLLは、他のデザインでインプリメントされてもよい。それらのうちのいくらかは、2005年6月21日に提出された「PHASE LOCKED LOOP HAVING A FORWARD GAIN ADAPTATION MODULE」とタイトルをつけられた米国特許6,909,331号に記述される。米国特許6,909,331号に記述されるように、ハイパス変調パス用の利得g(t)が決定されてもよい。

【0065】

図3、5および8の中のDPLL300、500および302のそれぞれのために、出力位相中の連続性は、発振器への妨害によってアップセットされるかもしれない。そのような妨害は、電源の故障、他のループなどからの誤った結合などから起こるかもしれない。一般に、基準サイクル当たりのピーク出力位相シフトの大きさが基準サイクルの2分の1未満である場合(通常はその場合であろう)、妨害は面倒ではない。したがって、これらのDPLLは、強健なパフォーマンスを提供することができてもよい。

【0066】

図9は、ここに記述されたDPLLを使用する通信デバイス900のデザインのブロック図を示す。デバイス900は、無線通信デバイス、携帯電話、携帯情報端末(PDA)、ハンドヘルドデバイス、無線モデム、コードレス電話機、無線ステーション、ブルートゥースデバイスなどで使用されてもよい。デバイス900は、符号分割多元接続(CDMA)システム、時分割多元接続(TDMA)システム、周波数分割多元接続(FDMA)システム、直交FDMA(OFDMA)システム、無線ローカルエリアネットワーク(WLAN)などのような様々な無線通信方式に使用されてもよい。デバイス900は、cdma2000、広帯域CDMA(W−CDMA)などのようなCDMA無線技術をサポートしてもよい。デバイス900は、さらにグローバル移動体通信システム(GSM(登録商標))のようなTDMA無線技術をサポートしてもよい。これらの様々なシステムと無線の技術は、技術で知られている。

【0067】

デバイス900内では、データプロセッサ910は、シンボルを得るためにデータを処理(例えば、符号化および変調)してもよい。プロセッサ910は、合成された貴重なサンプルを得るために通信用に使われた無線技術に従って、シンボル上で他の処理(例えば、スプリーディング、スクランブルなど)を実行してもよい。プロセッサ910は、各合成された貴重なサンプルの実数部分を含む同相(inphase)データ信号I(t)と、各合成された貴重なサンプルの虚数部分を含む直交(quadrature)データ信号Q(t)と、を提供してもよい。クアドラチュアポーラコンバータ920は、I(t)およびQ(t)データ信号を受け取ってもよく、各合成された貴重なサンプルをデカルト座標から極座標に変換し、エンベロープ信号Y(t)および位相信号θ(t)を提供する。

【0068】

エンベロープパスでは、マルチプライヤ922は、所望の出力電力レベルを得るために、エンベロープ信号に利得Gを掛けてもよい。遅延ユニット924は、エンベロープ信号と位相信号を調整する時間にプログラム可能な遅延量を供給してもよい。フィルタ926は、適切なフィルタ応答を備えた遅延エンベロープ信号をフィルタしてもよい。デジタル−アナログ変換器(DAC)928は、フィルタされたエンベロープ信号をアナログに変換し、出力エンベロープ信号を提供してもよい。電力増幅器(PA)954の利得は、振幅変調を達成するために出力エンベロープ信号によって変えられてもよい。

【0069】

位相パスでは、微分器930は、位相信号(t)を微分し、変調信号M(t)を提供してもよい。それは、I(t)およびQ(t)データ信号の周波数成分を含んでいてもよい。DPLL940は、変調信号M(t)を受け取り、DCO950のために制御信号S(t)を生成してもよい。DPLL940は、図3中のDPLL300、図5の中のDPLL500、または図8中のDPLL302でインプリメントされてもよい。DCO950は、変調信号によって変調される位相変調信号を生成してもよい。増幅器(Amp)952は、位相変調信号を増幅してもよい。PA954は、出力エンベロープ信号に基づいて増幅器952の出力をさらに増幅してもよく、変調された位相と振幅の両方があるRF出力信号を提供する。

【0070】

コントローラ/プロセッサ960は、データプロセッサ910およびデバイス900内の他のブロックのオペレーションをコントロールしてもよい。メモリ962は、コントローラ/プロセッサ960および/または他のブロックのために、データとプログラムコードを格納してもよい。

【0071】

デバイス900中の様々なブロックは、デジタルでインプリメントされてもよい。例えば、プロセッサ910からフィルタ926、微分器930、DPLL940およびコントローラ/プロセッサ960は、デジタルシグナルプロセッサ(DSP)、縮小命令セットコンピュータ(RISC)プロセッサ、中央処理装置(CPU)などの1つ以上で、インプリメントされてもよい。デジタルブロックは、特定用途向け集積回路(ASIC)および/または他の集積回路(IC)の1つ以上で、インプリメントされてもよい。デバイス900中の残りのブロックは、アナログ回路でインプリメントされてもよい。DCO950、増幅器952および/またはPA954の一部は、RF IC(RFIC)、アナログIC、混合信号ICなどの1つ以上で、インプリメントされてもよい。

【0072】

図10は、発振器、例えば、DCO、VCOなどをコントロールするためのプロセス1000のデザインを示す。入力位相を得るために、変調信号を含んでもよい少なくとも1つの入力信号は、蓄積されてもよい(ブロック1012)。発振信号と参照信号との間の位相差は、発振信号のための出力位相の小数部を得るために、(例えばTDC)で決定されてもよい(ブロック1014)。

【0073】

位相エラーは、入力位相の小数部および出力位相の小数部にのみ基づいて決定されてもよい(ブロック1016)。小数部は、発振信号の1サイクルの範囲を有してもよい。ブロック1016については、出力位相の小数部と入力位相の小数との間の位相差は、決定されてもよい。それが第1の値(例えば、マイナス2分の1発振サイクル)未満である場合、所定値(例えば、1発振サイクル)は位相差に加えられてもよい。それが第2の値(例えば、プラス2分の1発振サイクル)より大きい場合、所定値は位相差から引かれてもよい。所定値を加えるまたは引いた後の位相差がもしあれば、位相エラーとして提供されてもよい。発振器のための制御信号は、位相エラーに基づいて生成されてもよい(ブロック1018)。

【0074】

出力位相の整数部は、(例えば、RFアキュムレータで)発振信号のサイクル数のトラッキングを保持することにより決定されてもよい。位相エラーは、ロックされなかった場合、入力位相の整数および小数部、および出力位相の整数および小数部に基づいて決定されてもよい。位相エラーは、ロックされた場合、入力位相の小数部および出力位相の小数部にのみ基づいて決定されてもよい。

【0075】

図11は、発振器、例えば、DCO、VCOなどをコントロールするためのプロセス1100のデザインを示す。粗い出力位相C(t)は、発振信号の周波数より低い周波数を持っている参照信号に基づいて、発振器から発振信号のサイクル数のトラッキングを追うことによって、(例えば、合成されたアキュムレータで)決定されてもよい(ブロック1112)。細かい出力位相F(t)は、発振信号と参照信号との間の位相差に基づいて、例えばTDCで、決定されてもよい(ブロック1114)。位相エラーE(t)は、粗い出力位相、細かい出力位相および入力位相P(t)に基づいて、決定されてもよい(ブロック1116)。発振器のための制御信号S(t)は、位相エラーに基づいて生成されてもよい(ブロック1118)。

【0076】

ブロック1112については、粗い出力位相は、各最新間隔、例えば、各基準サイクルの第1の整数値NLまたは第2の整数値NHのいずれかによって更新されてもよい。第1および第2の整数値は、例えば、方程式(6)に示されるように、発振信号の周波数および参照信号の周波数に基づいて決定された連続する整数値でもよい。2つの仮説は、第1および第2の整数値、粗い出力位相、細かい出力位相および入力位相に基づいて、各最新間隔の第1および第2の整数値のために評価されてもよい。粗い出力位相は、2つの仮説の評価の結果に基づいて、第1または第2の整数値によって更新されてもよい。例えば、第1の仮定された出力位相Za(t)は、第1の整数値、粗い出力位相および細かい出力位相に基づいて決定されてもよい。第2の仮定された出力位相Zb(t)は、第2の整数値、粗い出力位相および細かい出力位相に基づいて決定されてもよい。粗い出力位相は、(i)第1の仮定された出力位相が第2の仮定された出力位相より入力位相に接近している場合は、第1の整数値によって、または、(ii)他の方法の場合は、第2の整数値によって、更新されてもよい。

【0077】

粗い出力位相A(t)は、例えば、オペレーションの最初で、第1の持続時間の発振信号に基づいて、発振信号のサイクル数のトラッキングを保持することにより決定されてもよい。粗い出力位相C(t)は、例えば、ロックが達成された後、第2の持続時間の参照信号に基づいて、発振信号のサイクル数のトラッキングを保持することにより決定されてもよい。

【0078】

ここに記述されたDPLLは、様々な手段によってインプリメントされてもよい。例えば、DPLLは、ハードウェア、ファームウェア、ソフトウェアまたはそれらのコンビネーションでインプリメントされてもよい。ハードウェアインプリメンテーションについては、DPLL内のブロックは、DSP、デジタル信号処理装置(DSPD)、プログラマブルロジックデバイス(PLD)、フィールドプログラマブルゲートアレイ(FPGA)、プロセッサ、コントローラ、マイクロコントローラ、マイクロプロセッサ、電子デバイス、他の電子ユニットまたはここに記述した機能を実行するためにデザインされたデジタル回路、コンピュータ、またはそれらのコンビネーションの1つ以上で、インプリメントされてもよい。

【0079】

DPLLは、IC、アナログIC、デジタルIC、RFIC、混合信号(mixed-signal)IC、ASIC、プリント回路基板(PCB)、電子デバイスなどで、インプリメントされてもよい。DPLLは、相補型金属酸化膜半導体(CMOS)、NチャネルMOS(N−MOS)、PチャネルMOS(P−MOS)、バイポーラ接合トランジスタ(BJT)、バイポーラCMOS(BiCMOS)、シリコンゲルマニウム(SiGe)、砒化ガリウムなど(GaAs)のような様々なICプロセス技術で作り上げられてもよい。

【0080】

ファームウェアおよび/またはソフトウェアインプリメンテーションについては、DPLL内のブロックは、ここに記述された機能を実行するコード(例えば、手順、機能、モジュール、インストラクションなど)でインプリメントされてもよい。一般に、ファームウェアおよび/またはソフトウェアコードを明確に具体化するどんなコンピュータ/プロセッサ判読可能な媒体は、ここに記述された技術をインプリメントするのに使用されてもよい。例えば、ファームウェアおよび/またはソフトウェアコードは、メモリ(例えば、図9中のメモリ962)に格納されてもよく、プロセッサ(例えば、プロセッサ960)によって実行されてもよい。メモリは、プロセッサ内またはプロセッサの外部でインプリメントされてもよい。ファームウェアおよび/またはソフトウェアコードは、ランダムアクセスメモリ(RAM)、読み取り専用メモリ(ROM)、不揮発性ランダムアクセスメモリ(NVRAM)、プログラム可能な読み取り専用メモリ(PROM)、電気的消去可能なPROM(EEPROM)、フラッシュメモリ、フロッピー(登録商標)ディスク、コンパクトディスク(CD)、デジタルバーサタイルディスク(DVD)、磁気または光データ記憶デバイスなどのようなコンピュータ/プロセッサ判読可能な媒体に格納されてもよい。コードは、1つ以上のコンピュータ/プロセッサによって実行可能にされてもよく、コンピュータ/プロセッサ(s)にここに記述された機能の特定の態様を実行させてもよい。

【0081】

ここに記述されたDPLLをインプリメントする装置は、スタンドアロンデバイスかもしれないし、または大型デバイスの一部かもしれない。デバイスは、(i)スタンドアロンIC、(ii)データおよび/またはインストラクションを格納するためのメモリICを含んでもよい1つ以上のICのセット、(iii)RF受信機(RFR)またはRF送信機/受信機(RTR)のようなRFIC、(iv)移動局モデム(MSM)のようなASIC、(v)他のデバイス内に埋め込まれてもよいモジュール、(vi)受信機、携帯電話、無線デバイス、ハンドセット、または移動体ユニット、(vii)その他、であってもよい。

【0082】

開示の前の記述は、どんな当業者でも開示を実施または使用することを可能にするために提供される。開示への様々な変更は、当業者に容易に明白であろう。ここに定義された一般的な本質は、開示の範囲から外れずに、他の変化に適用されてもよい。したがって、その開示は、ここで記述した例およびデザインに制限されることは意図されず、ここに開示された本質および新しい特徴と一致する最も広い範囲を与えられる。

【分野】

【0001】

現在の開示は、エレクトロニクス、さらに、特にデジタル位相同期ループに一般に関係がある。

【背景】

【0002】

位相同期ループ(PLL)は、多くのエレクトロニクス回路の不可欠な部分であり、通信回路において特に重要である。例えば、デジタル回路は、同期回路(synchronous circuit)をトリガするためにクロック信号を使用する、例えば、フリップフロップである。送信機と受信機は、局部発振器(LO)の信号を周波数アップコンバーション(upconversion)およびダウンコンバーション(downconversion)にそれぞれ使用する。無線通信システムのための無線デバイス(例えば、携帯電話)は、一般的に、送信機および受信機のためのデジタル回路およびLO信号にクロック信号を使用する。クロックおよびLO信号は発振器で生成される。そして、それらの周波数はPLLでしばしばコントロールされる。

【0003】

PLLは、一般的に、発振器からの発振信号の周波数および/または位相を調節するために使われた様々な回路ブロックを含む。これらの回路ブロックは、比較的大量の電力を消費するかもしれない。それは携帯電話のような携帯機器には不適当かもしれない。したがって、パフォーマンスを犠牲にせずに、PLLの消費電力を低減するためのテクニックに関する技術が必要である。

【概要】

【0004】

よいパフォーマンスおよび低い消費電力を有しているデジタルPLL(DPLL)は、ここに記述される。DPLLは、アナログ回路でよりむしろデジタルでインプリメントされた回路ブロックを備えたPLLである。デジタルインプリメーションは、低コスト、少ない回路面積のような特定の利点を備えてもよい。

【0005】

1つの態様では、DPLLは入出力位相の小数部(fractional portion)に基づいて動作してもよい。DPLLは、入力位相を得るために、少なくとも1つの入力信号(それは変調信号を含んでもよい)を蓄積してもよい。DPLLは、例えば、タイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいた出力位相の小数部を決定してもよい。その後、DPLLは、入力位相の小数部および出力位相の小数部に基づいた位相エラーを決定してもよい。小数部は、発振信号の1つのサイクルの範囲を有してもよい。1つのデザインでは、DPLLは、出力位相の小数部と入力位相の小数部との間の位相差を決定してもよい。その後、結果の位相エラーが所定範囲内(例えば、マイナス2分の1発振サイクルからプラス2分の1発振サイクルまで)であるように、DPLLは、必要に応じて、位相差から所定値(例えば、1発振サイクル)を加えてもよい、または、所定値を引いてもよい。DPLLは、位相エラーに基づいた発振器に関する制御信号を生成してもよい。

【0006】

別の態様では、DPLLは合成されたアキュムレータおよびTDCを含んでいてもよい。合成されたアキュムレータは、発振信号のサイクル数のトラッキングを保持することにより、粗い(coarse)出力位相を決定してもよい。合成されたアキュムレータは、発振信号の周波数より低い周波数を持っている参照信号に基づいて更新されてもよい。TDCは、発振信号と参照信号との間の位相差に基づいて細かい(fine)出力位相を決定してもよい。DPLLは、粗い出力位相、細かい出力位相および入力位相に基づいて、発振器のための制御信号を生成してもよい。

【0007】

開示の種々の態様および特徴は、さらに詳細に下に記述される。

【図面の簡単な説明】

【0008】

【図1】図1は、DPLLのブロック図を示す。

【図2】図2は、TDCに関する入力に対する出力のプロットを示す。

【図3】図3は、小数入出力位相に基づいて動作するDPLLのブロック図を示す。

【図4】図4は、合成されたアキュムレータの動作を示す。

【図5】図5は、合成されたアキュムレータを備えたDPLLのブロック図を示す。

【図6】図6は、合成されたアキュムレータを備えた位相検出器のブロック図を示す。

【図7】図7は、TDCの概略図を示す。

【図8】図8は、合成されたアキュムレータを備えた別のDPLLのブロック図を示す。

【図9】図9は、通信デバイスのブロック図を示す。

【図10】図10は、発振器をコントロールするプロセスを示す。

【図11】図11は、発振器をコントロールする別のプロセスを示す。

【詳細な説明】

【0009】

図1は、DPLL100のデザインのブロック図を示す。DPLL100内では、アナログ加算器110は、通信のために使用された周波数チャネルの中心周波数に対する静的な値で変調信号M(t)を受け取りそして合計する。入力アキュムレータ112は、アナログ加算器110の出力を蓄積し、入力位相P(t)を提供する。蓄積は、基本的に周波数を位相に変換する。入力アキュムレータ112は、参照信号によって引き起こされる。それは、frefの固定周波数を持っていてもよい。DPLL100内の様々な回路ブロックおよび信号も参照信号で更新される。また、tは参照信号のためのインデックスである。

【0010】

無線周波数(RF)アキュムレータ122は、各発振サイクルの1つ(それは制御発振器118からの発振信号の1つのサイクルである)によってインクリメントする。ラッチ124は、参照信号が引き金となって起きた時、RFアキュムレータ122の出力をラッチし、そして、粗い/整数部の出力位相A(t)を提供する。TDC130は、発振信号と参照信号を受け取り、参照信号が引き金となって起きた時、発振信号の位相を決定し、発振信号と参照信号との間の細かい/小数部の位相差を示すTDC出力F(t)を提供する。TDC130は、DPLL100のための小数位相センサをインプリメントする。アナログ加算器126は、粗い出力位相A(t)およびTDC出力F(t)を受け取りそして合計し、そして、出力位相B(t)の予測であるフィードバック位相Z(t)を提供する。

【0011】

アナログ加算器114は、入力位相P(t)からフィードバック位相Z(t)を受け取りそして引き、位相エラーE(t)を提供する。ループフィルタ116は、位相エラーをフィルタし、発振器118に制御信号S(t)を供給する。ループフィルタ116は、DPLL100のループ・ダイナミクスをセットする。制御信号は、発振信号の位相が変調の位相に続くように、発振器118の周波数を調節する。制御信号は、例えば、8、12、16、20、24、またはそれ以上のビットの分解能である、分解能の任意の適切なビット数を有してもよい。

【0012】

発振器118は、デジタル制御発振器(DCO)、電圧制御発振器(VCO)、電流制御発振器(ICO)、または周波数を制御信号によって調節することができるいくつかの他のタイプの発振器であってもよい。発振器118は、DPLL100が使用されるアプリケーションによって決定されてもよいfoscの公称周波数(nominal frequency)で動作してもよい。例えば、DPLL100は無線通信デバイスに使用されてもよい。また、foscは何百ものメガヘルツ(MHz)またはわずかのギガヘルツ(GHz)かもしれない。参照信号は、水晶発振器(XO)、電圧制御水晶発振器(VCXO)、温度補償水晶発振器(TCXO)または正確な周波数を持っているいくつかの他のタイプの発振器に基づいて生成されてもよい。参照信号の周波数は、発振信号の周波数よりはるかに低くあってもよい。例えば、frefは10MHzであってもよく、foscは数GHzであってもよい。

【0013】

入力位相P(t)、出力位相B(t)およびフィードバック位相Z(t)は、発振サイクルのユニットで与えられてもよい。図1で示されたデザインにおいて、DPLL100のフィードバック経路は、(i)発振サイクルの整数で与えられる粗い出力位相を測定するためのRFアキュムレータ122、および(ii)1つの発振サイクルの小数によって与えられる細かい出力位相を測定するためのTDC130、を含んでいる。RFアキュムレータ122およびTDC130のコンビネーションは、RFアキュムレータ122からの粗い/整数部およびTDC130からの細かい/小数部を含んでいるトータルの出力位相B(t)を測定する。ここにある記述において、「細かい(fine)」と「小数(fractional)」の用語は交換可能に使用される、そして「粗い(coarse)」と「整数(integer)」も交換可能に使用される。出力位相の予測であるフィードバック位相Z(t)は、ループフィルタ116のための位相エラーを得るために、入力位相から引かれる。

【0014】

DPLL100の中のブロックはすべて、RFアキュムレータ122を除いて、参照信号に基づいて動作されてもよい。RFアキュムレータ122は、発振信号に基づいて動作する。それは、参照信号より周波数において何倍も高いかもしれない。従って、RFアキュムレータ122は、DPLL100のトータル消費電力の大きな小数(例えば、およそ50%)に関与するかもしれない。したがって、バッテリー電源を節約するために、RFアキュムレータ122を備えたDPLL100をターンオフする動作は望ましいかもしれない。

【0015】

参照信号の1サイクルである1つの基準サイクルにおいて、トータル出力位相θtotalは次のように与えられてもよい。

【数1】

【0016】

トータル出力位相は、発振サイクルのユニットで与えられ、整数部θintおよび小数部θfracに分割されてもよい。整数部θintは、発振サイクルの整数または2πラジアンの整数倍で与えられてもよい。小数部θfracは、1発振サイクルの小数によってまたは0から2πラジアンの範囲内で与えられてもよい。整数部θintおよび小数部θfracは、以下のように与えられてもよい。

【数2】

【数3】

【0017】

RFアキュムレータ122は、基準サイクル内の発振サイクルの数の決定により、出力位相の整数部を決定してもよい。TDC130は、参照信号の位相に対する発振信号の位相の比較により、出力位相の小数部を決定してもよい。

【0018】

図2は、TDC130の入力に対する出力のプロットを示す。水平軸は出力位相B(t)を示す。それはTDC130への入力である。垂直軸は、TDC出力F(t)を示す。水平および垂直軸の両方については、1発振サイクルは2πに等しい。図2に示されるように、TDC130は、入力に対する不連続な出力を有する。TDC出力F(t)は、0から2πまでの出力位相B(t)と等しい。その後、B(t)=2πの時、0にラップアラウンドする。その後、2πから4πまでのB(t)で直線的に増加する。その後、B(t)=4πの時、0にラップアラウンドする、など。

【0019】

TDC出力での不連続は、DPLLが適切に動作するために取り組まれるべきである。これらの不連続に取り組む方法の1つは、出力位相B(t)が2πを超える回数の跡を追うために、RFアキュムレータ122を使用することである。そのとき、RFアキュムレータ122の出力は、不連続を避ける0から2πまでの動作範囲を制限するために、2πの整数倍で、TDC出力に加えられてもよい。しかしながら、RFアキュムレータ122は、その高い動作周波数のために多くの電流を消費してもよい。

【0020】

図2に示されるように、TDC出力はすべての2πをジャンプするが、連続的な位相跳躍間、2πの範囲を超えて連続する。出力位相の変化率が制限された場合、それらが生じるとともに、TDC出力での位相跳躍は確認されて説明されてもよい。例えば、M(t)=0のため、DPLL100は調節されていないかもしれない。P(t)はすべてのtのための小数部がない。初期条件は、E(0)=0のため、F(0)=0、A(0)=P(0)でもよい。DPLLがロックされるので、制御信号S(t)は一定値を有してもよい。出力位相がわずかに(例えば、0.1ラジアンによって)増加する場合、そのとき、TDC130はこの位相を測定し、補償信号(例えば、E(t)=−0.1ラジアン)を提供するだろう。しかしながら、出力位相B(t)がわずかに(例えば、−0.1ラジアンによって)減少する場合、そのとき、TDC130は大きな値(例えば、2π−0.1ラジアン)を出力するだろう。そのとき、位相エラーは、1発振サイクル毎に間違われるだろう。それは、逆に、DPLLのパフォーマンスに影響を与えるかもしれない。

【0021】

しかしながら、出力位相の変化率が制限された場合、基準サイクル内のTDC出力のどんな大規模な変更も、位相跳躍に起因してもよい。そのとき、1発振サイクルは、正確な位相値を得るために、TDC出力に追加され、または、TDC出力から引かれてもよい。上記の例で、TDC出力のための2π−0.1ラジアンの大きな値は、位相跳躍に起因されてもよい。2πは、この値から引かれてもよい。−0.1ラジアンは、正確なTDC出力値として提供されてもよい。

【0022】

一態様では、DPLLは、RFアキュムレータを使用せずに、TDCからの出力位相の小数および入力位相の小数部に基づいて操作される。各基準サイクルでは、TDC出力は、入力位相の小数部から以下のように引かれてもよい。

【数4】

【0023】

ここで、Pf(t)は、入力位相の小数部で、0から2πまでの範囲である。D(t)は、入力位相の小数部と出力位相の小数部であるTDC出力との間の差である。

【0024】

入力位相の変化率および出力位相の変化率は、制限されていると仮定されてもよい。また、位相エラーは、各基準サイクルの−πからπの範囲内にあると仮定されてもよい。位相エラーは、以下のように決定されてもよい。

【数5】

【0025】

方程式(5)は、D(t)が+πおよび−πのしきい値と比較されたデザインを示す。D(t)は、他のしきい値と比較されてもよい。

【0026】

方程式(5)に示されるように、位相差がπより大きいまたはπより小さい場合、位相跳躍は生じたと仮定される。この場合、2πは、合成の位相エラーがゼロ近くであるように、位相差から追加されるかまたは引かれてもよい。

図3は、もっぱら入力位相および出力位相の小数部に基づいて動作するDPLL300のデザインのブロック図を示す。DPLL300内では、図1でアナログ加算器110および入力アキュムレータ112に関して上述されるように、アナログ加算器310および入力アキュムレータ312は、動作し、そして、入力位相P(t)を提供する。ユニット313は、入力位相を受け取り、小数部Pf(t)を提供する。TDC330は、制御発振器318からの発振信号および参照信号を受け取り、発振信号と参照信号との間の細かい/小数位相差を示すTDC出力F(t)を提供する。アナログ加算器314は、小数入力位相Pf(t)からTDC出力F(t)を引き、そして、位相差D(t)を提供する。ユニット315は、位相差を受け取り、例えば、方程式(5)に示されるように、位相エラーE(t)を決定する。ループフィルタ316は、位相エラーをフィルタし、発振器318に制御信号S(t)を供給する。

【0027】

1つのデザインでは、RFアキュムレータは、変調信号のために発振器318をロックするために最初に使用されてもよい。(図3中で示されない)ロック検出器は、例えば、位相エラーの大きさの観察によって、DPLL300がロックしたかどうか判断してもよい。DPLL300がロックした後、RFアキュムレータはディセーブルになってもよい。また、入力位相および出力位相の小数部だけが、DPLLを操作するために使用されてもよい。

【0028】

別の態様では、合成されたアキュムレータは、粗い/整数出力位相を決定するために使用されてもよい。合成されたアキュムレータは、発振信号の代わりに参照信号に基づいて動作し、したがって、RFアキュムレータより非常に少ない電力を消費してもよい。

【0029】

図4は、合成されたアキュムレータでDPLLの動作を例証する。図4中で示される例で、発振信号の周波数は、参照信号の周波数の3.25倍である。また、3.25の周波数制御ワード(FCW)は、図1中のチャネル周波数として提供されてもよい。簡単にするために、DPLLは、発振信号と参照信号の立ち上がりエッジに基づいて、ロックされ引き起こされると仮定される。

【0030】

発振信号は、図4の一番上の第1のラインで示される。また、参照信号は、第2のラインで示される。RFアキュムレータの出力は、第3のラインで示される。RFアキュムレータは、発振信号の各立ち上がりエッジの一つによって増加し、それらが生じるとき、発振サイクルのトラックをキープする。RFアキュムレータの出力は、参照信号の各立ち上がりエッジでラッチされる。また、ラッチされた値のそれぞれは、第3のラインで円内に示される。ラッチされた値のそれぞれは、最も近い整数値へ発振サイクルの数を切り捨てることにより得られる。例えば、図4中に参照信号の第1および第2の立ち上がりエッジの間に3.25の発振サイクルがある。そして、RFアキュムレータの出力は、端数が切り捨てられた3.25に等しい、3である。図4中で示される例で、基準サイクル毎に3.25の発振サイクルがある。また、ラッチされた値は、0、3、6、9、13などである。

【0031】

理想的なTDCの出力は、第4のラインで示される。TDCは、端数を切り捨てる機能によって見落とされた出力位相の小数部を測定する。小数部は、参照信号の立ち上がりエッジと発振信号の最も近い前の立ち上がりエッジとの間の差に等しい。TDCは、参照信号の各立ち上がりエッジのために0と1.0の間の小数値を供給する。図4に示されるように、TDCの出力は周期的である。フィードバック位相は、TDCからの細かい/小数部およびRFアキュムレータからの粗い/整数部を加えることにより得られてもよい。

整数インクリメントN(t)と呼ばれる、1つの基準サイクル当たりの発振サイクルの端数を切り捨てた数は、第5のラインで示される。参照信号の各立ち上がりエッジについては、N(t)は、現在のラッチされた値と先のラッチされた値の間の差に等しい。図4中で示される例で、N(t)は、3、3、3、4、3、3、3、4、3などのシーケンスである。N(t)は、3.25の平均値を持っており、TDC出力と同じ方法で周期的である。更に、N(t)は、たった2つの可能な整数値しか持っていない。それは、DPLLがロックした後、図4中で示される例において3と4である。DPLLがナローバンド周波数変調で適用される場合さえ、2つの整数値間のこのトグリングは真実である。3つの整数値間でトグルするために、周波数変調は基準周波数frefより大きい必要があるだろう。その結果、付加的な十分な発振サイクルは、基準サイクル内に適合することができる。一般的には、ピーク変調周波数は、基準周波数のほんの少しである。例えば、ピーク変調周波数は、ほとんどMHzではないかもしれない。一方、基準周波数は、10MHzかもしれない。この場合、N(t)は、2つの可能な整数値しかない。

【0032】

N(t)が2つの可能な整数値しか取得できない場合、発振器周波数foscで動作するRFアキュムレータの使用なしでN(t)を決定することは可能かもしれない。これは、DPLLが変調される場合さえ、1つの基準サイクル当たりの少量だけによって位相エラーが変わるという事実の開発により達成されてもよい。例えば、4GHzの発振器を備えたローバンドEDGEおよびDPLL出力の4倍のディビジョンのために、ピーク周波数変調はおよそ3MHzかもしれない。基準周波数は、およそ57MHzかもしれない。また、1つの基準サイクル当たりの入力位相の最大の変更は、基準サイクルのおよそ0.3ラジアンまたは約5%かもしれない。したがって、変調は、2π位相跳躍を不明瞭にしない。DPLLの操作は、本質的に不変である。

【0033】

N(t)は、以下のようにRFアキュムレータを使用せずに決定されてもよい。各基準サイクルまたは最新間隔tについては、N(t)の正確な値は、N(t)のための2つの仮説の評価により決定されてもよい。第1の仮説aは、N(t)が2つの値の中でより小さい場合のためである。それは、NLとして表示され、図4で示される例のために3に等しい。第2の仮説bは、N(t)が2つの値の中でより大きい場合のためである。それは、NHとして表示され、図4で示される例のために4に等しい。より小さな位相エラー大きさを提供する仮説は、選択されてもよい。また、正確な仮説のためのNLまたはNHは、発振サイクルの数のランニングカウントを格納するレジスタを更新するために使用されてもよい。このレジスタは、粗い出力位相C(t)を提供する。それは、発振サイクルの整数の中で与えられる。

【0034】

2つの仮説aおよびbは、以下のように評価されてもよい。レジスタは、例えば、DPLLがロックした後、入力位相P(t)の整数部に基づいて、初期化されてもよい。図4で示される例で、レジスタはゼロにするために初期化される。参照信号の第2の立ち上がりエッジで、仮説aは、Za(1)=3+0+0.25=3.25の仮定された出力位相を有する。ここで、3は仮説aのためのNL値であり、0はレジスタからの粗い出力位相C(1)であり、0.25はTDC出力値である。仮説bは、Zb(1)=4+0+0.25=4.25の仮定された出力位相を有する。ここで、4は仮説bのためのNH値である。2つの仮説用の仮定された出力位相Za(1)およびZb(1)は、入力位相P(1)=3.25と比較される。Za(1)はZb(1)よりP(1)に接近しているので、仮説aは正確な仮説である。その後、レジスタは3ずつ更新される。それは、正確な仮説aのためのNL値で、3の粗い出力位相を格納する。

【0035】

参照信号の第3の立ち上がりエッジにおいて、仮説aは、Za(2)=3+3+0.5=6.5の仮定された出力位相を有する。ここで、1つ目の3は仮説aのためのNL値であり、2つ目の3はレジスタからの粗い出力位相C(2)であり、0.5はTDC出力値である。仮説bは、Zb(2)=4+3+0.5=7.5の仮定された出力位相を有する。ここで、4は仮説bのためのNH値である。2つの仮説用の仮定された出力位相Za(2)およびZb(2)は、入力位相P(2)=6.5と比較される。Za(2)はZb(2)よりP(2)に接近しているので、仮説aは正確な仮説である。その後、レジスタは3ずつ更新される。それは、正確な仮説aのためのNL値であり、6の粗い出力位相を格納する。同じ処理は、個々の後の基準サイクルのために繰り返されてもよい。

【0036】

一般に、N(t)のための2つの可能な整数値は以下のように決定されてもよい。

【数6】

【0037】

ここで、NLは、N(t)のための2つの可能な整数値の中でより小さい。NHは、N(t)のための2つの可能な整数値の中でより大きい。

仮説aおよびbのための仮定された出力相は、以下のように決定されてもよい。

【数7】

【数8】

【0038】

ここで、C(t)は、基準サイクルtの中の粗い出力位相である。Za(t)は、基準サイクルtの中の仮説aのための仮定された出力位相である。Zb(t)は、基準サイクルtの中の仮説bのための仮定された出力位相である。

【0039】

仮説aおよびbのための仮定された位相エラーは、以下のように決定されてもよい。

【数9】

【数10】

【0040】

ここで、Ea(t)は、基準サイクルtの中の仮説aのための仮定された位相エラーである。Eb(t)は、基準サイクルtの中の仮説bのための仮定された位相エラーである。

粗い出力位相、以下のように更新されてもよい。

【数11】

【0041】

基準サイクルtの中の位相エラーE(t)は、以下のように決定されてもよい。

【数12】

【0042】

方程式(12)からの位相エラーは、DPLLの中のループフィルタに提供されてもよい。

【0043】

方程式(6)から(12)で示されるように、与えられた基準サイクルの中でN(t)の2つの可能な整数値間で選ぶために、2つの仮説aおよびbは評価されてもよい。入力位相に近い仮定された出力位相を有する、または、小さな位相エラーの大きさと等しい仮説が選択されてもよい。

【0044】

図5は、合成されたアキュムレータを備えたDPLL500のデザインのブロック図を示す。DPLL500の内では、図1中のアナログ加算器110および入力アキュムレータ112に関して上述されるように、アナログ加算器510および入力アキュムレータ512は動作し、入力位相P(t)を提供する。

【0045】

TDC530は、制御発振器518からの発振信号および参照信号を受け取り、発振信号と参照信号との間の位相差を示すTDC出力F(t)を提供する。位相検出器520は、発振信号、TDC出力および入力位相を受け取り、第1の位相エラーE1(t)を生成する。位相検出器520は、図1中のRFアキュムレータ122、ラッチ124およびアナログ加算器114と126に関して上述されるように動作する、RFアキュムレータ522、ラッチ524およびアナログ加算器526を含んでいる。位相検出器520は、モード信号によってイネーブル(enable)になってもよいしディセーブル(disable)になってもよい。位相検出器540は、チャネル周波数、参照信号、TDC出力および入力位相を受け取り、第2の位相エラーE2(t)を生成する。位相検出器540は、合成されたアキュムレータを含んでおり、下記に述べられるようにインプリメントされてもよい。位相検出器540は、モード信号によってイネーブルになってもよいしディセーブルになってもよい。位相検出器520または540の一方は、任意の所定のモーメントでイネーブルになってもよい。また、他方の位相検出器は、バッテリー電源を保存するためにディセーブルになってもよい。

【0046】

マルチプレクサ(Mux)514は、位相検出器520および540のそれぞれから2つの位相エラーE1(t)およびE2(t)、モード信号を受け取り、位相エラーE(t)を提供する。マルチプレクサ514は、位相検出器520がイネーブルになる場合に、位相エラーE(t)として第1の位相エラーE1(t)を提供し、位相検出器540がイネーブルになる場合に、位相エラーE(t)として第2の位相エラーE2(t)を提供する。ループフィルタ516は、位相エラーE(t)をフィルタし、発振器518に制御信号S(t)を供給する。

【0047】

1つのデザインでは、位相検出器520は、最初にイネーブルになり、変調信号への発振器518をロックするために使用されてもよい。DPLL500がロックした後、位相検出器520はディセーブルになってもよく、位相検出器540はイネーブルになってもよい。ロック検出器550は、位相検出器520から第1の位相エラーE1(t)を受け取り、DPLL500がロックしたかどうか判断する。これは、第1の位相エラーE1(t)の大きさの観察により達成されてもよい。それは、DPLL500がロックされない場合、最初に大きいかもしれないし、DPLL500がロックされる場合、小さいかもしれない。ロック検出器550は、DPLLがロックされる場合にある論理値(例えば「1」)またはDPLLがロックされない場合に他の論理値(例えば「0」)にセットされてもよいロックインジケータを提供する。モードセレクタ552は、ロックインジケータおよび図5中で示されない可能な他の入力を受け取り、モード信号を提供する。例えば、モードセレクタ552は、位相検出器540をイネーブルにし、DPLLがロックされたらすぐにまたは後で位相検出器520をディセーブルにしてもよい。位相検出器520および540の両方は、RFアキュムレータ522のスイッチを切る前に、期間のために同時にイネーブルになってもよい。ロックの損失が検知される場合(例えば、DPLL500へ致命的な妨害のために)は常にまたは他の理由の場合、モードセレクタ552は再度位相検出器520もイネーブルにしてもよい。DPLLがロックされない場合に、(図3中で示されない)RFアキュムレータの出力を備えた位相エラーを生成するために、ロック検出器550およびモードセレクタ552も、図3中でDPLL300のために使用されてもよい。

図6は、図5中の位相検出器540のデザインのブロック図を示す。このデザインでは、位相検出器540は、合成されたアキュムレータ610、仮説評価ユニット(hypotheses evaluation unit)620およびラウンディングユニット(rounding unit)630を含んでいる。ラウンディングユニット630は、チャネル周波数を受け取り、N(t)のための2つの可能な整数値を決定してもよい。それは、NLおよびNHである。または、ユニット630は、図5中のラッチ524から粗い出力位相A(t)を受け取ってもよい。DPLL500がロックされ、位相検出器520がイネーブルになる場合、粗い出力位相A(t)は、NLおよびNHの間でトグルすべきである。したがって、ユニット630は、DPLL500がロックした後、粗い出力位相A(t)の値に基づいて、NLおよびNHを決定してもよい。

【0048】

合成されたアキュムレータ610は、発振サイクルの数のトラッキングを保持するが、発振信号の代わりに参照信号に基づいて動作する。これは、DPLL500のための消費電力を非常に低減してもよい。合成されたアキュムレータ610は、レジスタ612、アナログ加算器614およびマルチプレクサ616を含んでいる。レジスタ612は、発振サイクルの整数中の現在の粗い出力位相C(t)を格納する。マルチプレクサ616は、NLおよびNH、仮説が正確な/勝利の仮説かを示すセレクト信号を受け取る。各基準サイクルでは、マルチプレクサ616は、仮説aが正確な仮説である場合にNLを提供し、仮説bが正確な仮説である場合にNHを提供する。アナログ加算器614は、レジスタ612からの現在の粗い出力位相C(t)およびマルチプレクサ616の出力を合計し、最新の粗い出力位相C(t+1)を提供する。それは、レジスタ612に格納される。レジスタ612、アナログ加算器614およびマルチプレクサ616は、方程式(11)でインプリメントする。

【0049】

ユニット620は、各基準サイクル中の2つの仮説aおよびbを評価し、正確な仮説を示すセレクト信号と同様に位相エラーE2(t)を提供する。方程式(7)で示されるように、ユニット620内では、アナログ加算器622aは、レジスタ612からの粗い出力位相C(t)、TDC出力F(t)およびNLを受け取り、合計し、仮説aのために仮定された出力位相Za(t)を供給する。方程式(9)で示されるように、アナログ加算器624aは、入力位相P(t)から仮定された出力位相Za(t)を引き、仮説aのために仮定された位相エラーEa(t)を供給する。同様に、方程式(8)で示されるように、アナログ加算器622bは、粗い出力位相C(t)、TDC出力F(t)およびNHを受け取り、合計し、仮説bに仮定された出力位相Zb(t)を供給する。方程式(10)で示されるように、アナログ加算器624bは、入力位相P(t)から仮定された出力位相Zb(t)を引き、仮説bに仮定された位相エラーEb(t)を供給する。

【0050】

セレクタ626は、2つの仮説のために仮定された位相エラーEa(t)およびEb(t)を受け取り、2つの仮定された位相エラーの小さな大きさを決定する。方程式(12)で示されるように、セレクタ626は、位相検出器540からの位相エラーE2(t)として小さな大きさで仮定された位相エラーに供給する。セレクタ626は、セレクト信号も提供する。それは、小さな仮定された位相エラー大きさを生産する正確な仮説を示す。

【0051】

図4および6は、RFアキュムレータ出力を、例えば、3.25から3まで下がる、6.5から6まで下がるなど切り捨てたデザインを示す。この場合、TDC出力F(t)は、各仮説のために粗い出力位相C(t)に加えられる。別のデザインでは、RFアキュムレータ出力は、例えば、3.25から4まで上がる、6.5〜7まで上がるなど、切り上げられる。この場合、TDC出力F(t)は、(図中で示されない)各仮説のために粗い出力位相C(t)から引かれる。一般に、仮説は、合成されたアキュムレータがどのように更新されるかと一致するやり方で評価されてもよい。

【0052】

図6は、2つの整数値NLおよびNHがDPLL500の通常動作の間に可能な場合用の合成されたアキュムレータ610および仮説評価ユニット620のデザイン例を示す。N(t)は、例えば、広帯域の変調またはDPLL500が初めにパワーアップするために、2つを超える可能な整数値を有してもよい。広帯域の変調による大規模な周波数差は、合成されたアキュムレータからの粗い出力位相に補正率(correction factor)を適用することにより補正されてもよい。一般に、1つの仮説は、N(t)の個々の可能な整数値のために評価されてもよい。最も小さな位相エラーを備えた仮説は、選択されてもよい。合成されたアキュムレータは、選択された仮説のためにN(t)値に基づいて更新されてもよい。

1つのデザインでは、例えば、図5に示されるように、DPLLは、発振周波数で動作するRFアキュムレータと、基準周波数で動作する合成されたアキュムレータとの両方を含んでいる。図5に関して上述されるように、RFアキュムレータは、動作の最初に使用されてもよい。DPLLがロックした後、合成されたアキュムレータは、通常動作の間に使用されてもよい。

【0053】

別のデザインでは、DPLLは、基準周波数で動作する合成されたアキュムレータだけを含んでいる。オペレーションの最初で、さらに(例えば、3、4または恐らくより多くの)仮説は、N(t)のより多くの可能な値のために評価されてもよい。DPLLがロックした後、少数(例えば2つ)の仮説がより少数の可能なN(t)値のために評価されてもよい。選択的に、同じ数の仮説(例えば2つの仮説)は、オペレーションの最初におよび通常動作の間に評価されてもよい。ループ帯域幅は、可能なN(t)値の制限された数を備えたDPLLのために、希望の獲得パフォーマンスを達成するために選択されてもよい。

【0054】

図5中のDPLL500は、図3中のDPLL300と等価なやり方で動作してもよい。DPLL500がロックされる場合、仮定された位相の整数部(それは合成されたアキュムレータ610からの粗い出力位相C(t)である)は、入力位相の整数部と一致するべきである。これらの2つの整数部は、図6中のアナログ加算器624aおよび624bによってキャンセルされるだろう。小数部間の違いだけは、位相エラーE2(t)の中で提供されるだろう。

【0055】

図7は、図5中のTDC530のデザインの概略図を示す。TDC530は、参照信号の位相に対する発振信号の位相を比較し、分解能の多数の(B)ビットで検出された位相差を提供する。

【0056】

TDC530は、2Bの遅延素子710aから710z、2BのDフリップフロップ712aから712z、およびサーモメータバイナリコンバータ714を含んでいる。遅延素子710aから710zは、発振信号を受け取る遅延要素710aと連続して結合される。各遅延要素710は、希望の遅延分解能を得るためにインバーターおよび/または他のタイプの論理素子でインプリメントされてもよい。遅延素子710aから710zは、およそ1発振サイクルの合計遅延を提供する。例えば、発振周波数foscが4GHzである場合、1発振サイクルは250ピコセカンド(ps)である。各遅延要素710は、約250/2Bpsの遅れを提供する。

【0057】

Dフリップフロップ712aから712zは、遅延素子710aから710zの出力にそれぞれつながれたそれらのD入力と、参照信号を受け取るそれらのクロック入力を有する。各Dフリップフロップ712は、関連する遅延要素710からの出力信号をサンプリングし、コンバータ714にサンプリングされた出力を供給する。ロジックロウのDフリップフロップの数に対してロジックハイのDフリップフロップの数は、発振信号と参照信号との間の位相差を示す。この位相差は、1/2B発振サイクルの分解能を有する。コンバータ714は、Dフリップフロップ712aから712zからの2Bの出力を受け取り、これらの2Bの出力をBビット2進値に変換し、細かい/小数出力位相としてBビット2進値を提供する。

【0058】

一般に、TDC530は、分解能のビットの任意数でデザインされてもよい。例えば、Bは、希望の遅延分解能、集積回路(IC)プロセスなどにおいて利用可能な最小の遅延に応じて、8以上かもしれない。希望の遅延分解能は、DPLL500が使用されるアプリケーションに依存してもよい。

【0059】

DPLLは、様々なアプリケーションに使用されてもよい。例えば、DPLLは、周波数合成器が希望の周波数で発振信号を生成するために使用されてもよい。この場合、変調信号M(t)は、省略されるか、またはゼロにセットされてもよい。DPLLは、ポーラモジュレータ、クアドラチュアモジュレータ、位相変調器、周波数変調器、復調器などに使用されてもよい。モジュレータについては、変調信号の帯域幅は、DPLLの閉じたループ帯域幅より大きくてもよい。DPLLは、変調信号の広い帯域幅に対応するデザインでもよい。

【0060】

図8は、広帯域変調を支援するDPLL302のデザインのブロック図を示す。DPLL302は、図3中のDPLL300のブロックをすべて含んでいる。DPLL302は、スケーリングユニット320およびアナログ加算器317をさらに含んでいる。

【0061】

DPLL302は、高帯域変調を達成するために2ポイントまたはデュアルポートの変調をインプリメントする。変調信号M(t)は、ローパス変調パスおよびハイパス変調パスの両方に提供されてもよい。ローパス変調パスでは、アナログ加算器310および入力アキュムレータ312は、変調信号M(t)上で動作し、入力位相P(t)を提供する。入力アキュムレータ312による蓄積は、本質的に周波数を位相に変換する。ハイパス変調パスでは、スケーリングユニット320は、利得g(t)で変調信号M(t)を受け取り、スケールし、第2の変調信号X(t)を提供する。アナログ加算器317は、ループフィルタ316の出力と発振器318の入力との間で連結される。アナログ加算器317は、ループフィルタ316からのフィルタされた位相エラー信号およびスケーリングユニット320からの第2の変調信号X(t)を合計し、発振器318のために制御信号S(t)を供給する。

【0062】

変調信号の帯域幅は、DPLL302が使用されるアプリケーションによって決定されてもよく、DPLLの閉じたループ帯域幅より広くてもよい。DPLL302の中のローパス変調パスの帯域幅は、ループフィルタ316によって決定され、希望のノイズ・フィルタリングおよびループ・ダイナミクスを達成するために、比較的狭い(例えば、100kHz未満)かもしれない。個別のハイパスおよびローパス変調パスによって変調信号M(t)を適用することによって、DPLL302は、DPLLの閉じたループ帯域幅より広い信号の帯域幅を備えた発振器318を変調することができる。

【0063】

簡単にするために、図3、5および8は、DPLL300、500および502の機能的ブロックをそれぞれ示す。特定の詳細は、明瞭さのために省略される。例えば、遅延は、これらのDPLL内の様々な信号を適切な時間で調整するために、DPLL300、302および500の内の適切な場所に挿入されてもよい。

【0064】

図3、5および8は、変調するDPLLのいくつかのデザイン例を示す。変調するDPLLは、他のデザインでインプリメントされてもよい。それらのうちのいくらかは、2005年6月21日に提出された「PHASE LOCKED LOOP HAVING A FORWARD GAIN ADAPTATION MODULE」とタイトルをつけられた米国特許6,909,331号に記述される。米国特許6,909,331号に記述されるように、ハイパス変調パス用の利得g(t)が決定されてもよい。

【0065】

図3、5および8の中のDPLL300、500および302のそれぞれのために、出力位相中の連続性は、発振器への妨害によってアップセットされるかもしれない。そのような妨害は、電源の故障、他のループなどからの誤った結合などから起こるかもしれない。一般に、基準サイクル当たりのピーク出力位相シフトの大きさが基準サイクルの2分の1未満である場合(通常はその場合であろう)、妨害は面倒ではない。したがって、これらのDPLLは、強健なパフォーマンスを提供することができてもよい。

【0066】

図9は、ここに記述されたDPLLを使用する通信デバイス900のデザインのブロック図を示す。デバイス900は、無線通信デバイス、携帯電話、携帯情報端末(PDA)、ハンドヘルドデバイス、無線モデム、コードレス電話機、無線ステーション、ブルートゥースデバイスなどで使用されてもよい。デバイス900は、符号分割多元接続(CDMA)システム、時分割多元接続(TDMA)システム、周波数分割多元接続(FDMA)システム、直交FDMA(OFDMA)システム、無線ローカルエリアネットワーク(WLAN)などのような様々な無線通信方式に使用されてもよい。デバイス900は、cdma2000、広帯域CDMA(W−CDMA)などのようなCDMA無線技術をサポートしてもよい。デバイス900は、さらにグローバル移動体通信システム(GSM(登録商標))のようなTDMA無線技術をサポートしてもよい。これらの様々なシステムと無線の技術は、技術で知られている。

【0067】

デバイス900内では、データプロセッサ910は、シンボルを得るためにデータを処理(例えば、符号化および変調)してもよい。プロセッサ910は、合成された貴重なサンプルを得るために通信用に使われた無線技術に従って、シンボル上で他の処理(例えば、スプリーディング、スクランブルなど)を実行してもよい。プロセッサ910は、各合成された貴重なサンプルの実数部分を含む同相(inphase)データ信号I(t)と、各合成された貴重なサンプルの虚数部分を含む直交(quadrature)データ信号Q(t)と、を提供してもよい。クアドラチュアポーラコンバータ920は、I(t)およびQ(t)データ信号を受け取ってもよく、各合成された貴重なサンプルをデカルト座標から極座標に変換し、エンベロープ信号Y(t)および位相信号θ(t)を提供する。

【0068】

エンベロープパスでは、マルチプライヤ922は、所望の出力電力レベルを得るために、エンベロープ信号に利得Gを掛けてもよい。遅延ユニット924は、エンベロープ信号と位相信号を調整する時間にプログラム可能な遅延量を供給してもよい。フィルタ926は、適切なフィルタ応答を備えた遅延エンベロープ信号をフィルタしてもよい。デジタル−アナログ変換器(DAC)928は、フィルタされたエンベロープ信号をアナログに変換し、出力エンベロープ信号を提供してもよい。電力増幅器(PA)954の利得は、振幅変調を達成するために出力エンベロープ信号によって変えられてもよい。

【0069】

位相パスでは、微分器930は、位相信号(t)を微分し、変調信号M(t)を提供してもよい。それは、I(t)およびQ(t)データ信号の周波数成分を含んでいてもよい。DPLL940は、変調信号M(t)を受け取り、DCO950のために制御信号S(t)を生成してもよい。DPLL940は、図3中のDPLL300、図5の中のDPLL500、または図8中のDPLL302でインプリメントされてもよい。DCO950は、変調信号によって変調される位相変調信号を生成してもよい。増幅器(Amp)952は、位相変調信号を増幅してもよい。PA954は、出力エンベロープ信号に基づいて増幅器952の出力をさらに増幅してもよく、変調された位相と振幅の両方があるRF出力信号を提供する。

【0070】

コントローラ/プロセッサ960は、データプロセッサ910およびデバイス900内の他のブロックのオペレーションをコントロールしてもよい。メモリ962は、コントローラ/プロセッサ960および/または他のブロックのために、データとプログラムコードを格納してもよい。

【0071】

デバイス900中の様々なブロックは、デジタルでインプリメントされてもよい。例えば、プロセッサ910からフィルタ926、微分器930、DPLL940およびコントローラ/プロセッサ960は、デジタルシグナルプロセッサ(DSP)、縮小命令セットコンピュータ(RISC)プロセッサ、中央処理装置(CPU)などの1つ以上で、インプリメントされてもよい。デジタルブロックは、特定用途向け集積回路(ASIC)および/または他の集積回路(IC)の1つ以上で、インプリメントされてもよい。デバイス900中の残りのブロックは、アナログ回路でインプリメントされてもよい。DCO950、増幅器952および/またはPA954の一部は、RF IC(RFIC)、アナログIC、混合信号ICなどの1つ以上で、インプリメントされてもよい。

【0072】

図10は、発振器、例えば、DCO、VCOなどをコントロールするためのプロセス1000のデザインを示す。入力位相を得るために、変調信号を含んでもよい少なくとも1つの入力信号は、蓄積されてもよい(ブロック1012)。発振信号と参照信号との間の位相差は、発振信号のための出力位相の小数部を得るために、(例えばTDC)で決定されてもよい(ブロック1014)。

【0073】

位相エラーは、入力位相の小数部および出力位相の小数部にのみ基づいて決定されてもよい(ブロック1016)。小数部は、発振信号の1サイクルの範囲を有してもよい。ブロック1016については、出力位相の小数部と入力位相の小数との間の位相差は、決定されてもよい。それが第1の値(例えば、マイナス2分の1発振サイクル)未満である場合、所定値(例えば、1発振サイクル)は位相差に加えられてもよい。それが第2の値(例えば、プラス2分の1発振サイクル)より大きい場合、所定値は位相差から引かれてもよい。所定値を加えるまたは引いた後の位相差がもしあれば、位相エラーとして提供されてもよい。発振器のための制御信号は、位相エラーに基づいて生成されてもよい(ブロック1018)。

【0074】

出力位相の整数部は、(例えば、RFアキュムレータで)発振信号のサイクル数のトラッキングを保持することにより決定されてもよい。位相エラーは、ロックされなかった場合、入力位相の整数および小数部、および出力位相の整数および小数部に基づいて決定されてもよい。位相エラーは、ロックされた場合、入力位相の小数部および出力位相の小数部にのみ基づいて決定されてもよい。

【0075】

図11は、発振器、例えば、DCO、VCOなどをコントロールするためのプロセス1100のデザインを示す。粗い出力位相C(t)は、発振信号の周波数より低い周波数を持っている参照信号に基づいて、発振器から発振信号のサイクル数のトラッキングを追うことによって、(例えば、合成されたアキュムレータで)決定されてもよい(ブロック1112)。細かい出力位相F(t)は、発振信号と参照信号との間の位相差に基づいて、例えばTDCで、決定されてもよい(ブロック1114)。位相エラーE(t)は、粗い出力位相、細かい出力位相および入力位相P(t)に基づいて、決定されてもよい(ブロック1116)。発振器のための制御信号S(t)は、位相エラーに基づいて生成されてもよい(ブロック1118)。

【0076】

ブロック1112については、粗い出力位相は、各最新間隔、例えば、各基準サイクルの第1の整数値NLまたは第2の整数値NHのいずれかによって更新されてもよい。第1および第2の整数値は、例えば、方程式(6)に示されるように、発振信号の周波数および参照信号の周波数に基づいて決定された連続する整数値でもよい。2つの仮説は、第1および第2の整数値、粗い出力位相、細かい出力位相および入力位相に基づいて、各最新間隔の第1および第2の整数値のために評価されてもよい。粗い出力位相は、2つの仮説の評価の結果に基づいて、第1または第2の整数値によって更新されてもよい。例えば、第1の仮定された出力位相Za(t)は、第1の整数値、粗い出力位相および細かい出力位相に基づいて決定されてもよい。第2の仮定された出力位相Zb(t)は、第2の整数値、粗い出力位相および細かい出力位相に基づいて決定されてもよい。粗い出力位相は、(i)第1の仮定された出力位相が第2の仮定された出力位相より入力位相に接近している場合は、第1の整数値によって、または、(ii)他の方法の場合は、第2の整数値によって、更新されてもよい。

【0077】

粗い出力位相A(t)は、例えば、オペレーションの最初で、第1の持続時間の発振信号に基づいて、発振信号のサイクル数のトラッキングを保持することにより決定されてもよい。粗い出力位相C(t)は、例えば、ロックが達成された後、第2の持続時間の参照信号に基づいて、発振信号のサイクル数のトラッキングを保持することにより決定されてもよい。

【0078】

ここに記述されたDPLLは、様々な手段によってインプリメントされてもよい。例えば、DPLLは、ハードウェア、ファームウェア、ソフトウェアまたはそれらのコンビネーションでインプリメントされてもよい。ハードウェアインプリメンテーションについては、DPLL内のブロックは、DSP、デジタル信号処理装置(DSPD)、プログラマブルロジックデバイス(PLD)、フィールドプログラマブルゲートアレイ(FPGA)、プロセッサ、コントローラ、マイクロコントローラ、マイクロプロセッサ、電子デバイス、他の電子ユニットまたはここに記述した機能を実行するためにデザインされたデジタル回路、コンピュータ、またはそれらのコンビネーションの1つ以上で、インプリメントされてもよい。

【0079】

DPLLは、IC、アナログIC、デジタルIC、RFIC、混合信号(mixed-signal)IC、ASIC、プリント回路基板(PCB)、電子デバイスなどで、インプリメントされてもよい。DPLLは、相補型金属酸化膜半導体(CMOS)、NチャネルMOS(N−MOS)、PチャネルMOS(P−MOS)、バイポーラ接合トランジスタ(BJT)、バイポーラCMOS(BiCMOS)、シリコンゲルマニウム(SiGe)、砒化ガリウムなど(GaAs)のような様々なICプロセス技術で作り上げられてもよい。

【0080】

ファームウェアおよび/またはソフトウェアインプリメンテーションについては、DPLL内のブロックは、ここに記述された機能を実行するコード(例えば、手順、機能、モジュール、インストラクションなど)でインプリメントされてもよい。一般に、ファームウェアおよび/またはソフトウェアコードを明確に具体化するどんなコンピュータ/プロセッサ判読可能な媒体は、ここに記述された技術をインプリメントするのに使用されてもよい。例えば、ファームウェアおよび/またはソフトウェアコードは、メモリ(例えば、図9中のメモリ962)に格納されてもよく、プロセッサ(例えば、プロセッサ960)によって実行されてもよい。メモリは、プロセッサ内またはプロセッサの外部でインプリメントされてもよい。ファームウェアおよび/またはソフトウェアコードは、ランダムアクセスメモリ(RAM)、読み取り専用メモリ(ROM)、不揮発性ランダムアクセスメモリ(NVRAM)、プログラム可能な読み取り専用メモリ(PROM)、電気的消去可能なPROM(EEPROM)、フラッシュメモリ、フロッピー(登録商標)ディスク、コンパクトディスク(CD)、デジタルバーサタイルディスク(DVD)、磁気または光データ記憶デバイスなどのようなコンピュータ/プロセッサ判読可能な媒体に格納されてもよい。コードは、1つ以上のコンピュータ/プロセッサによって実行可能にされてもよく、コンピュータ/プロセッサ(s)にここに記述された機能の特定の態様を実行させてもよい。

【0081】

ここに記述されたDPLLをインプリメントする装置は、スタンドアロンデバイスかもしれないし、または大型デバイスの一部かもしれない。デバイスは、(i)スタンドアロンIC、(ii)データおよび/またはインストラクションを格納するためのメモリICを含んでもよい1つ以上のICのセット、(iii)RF受信機(RFR)またはRF送信機/受信機(RTR)のようなRFIC、(iv)移動局モデム(MSM)のようなASIC、(v)他のデバイス内に埋め込まれてもよいモジュール、(vi)受信機、携帯電話、無線デバイス、ハンドセット、または移動体ユニット、(vii)その他、であってもよい。

【0082】

開示の前の記述は、どんな当業者でも開示を実施または使用することを可能にするために提供される。開示への様々な変更は、当業者に容易に明白であろう。ここに定義された一般的な本質は、開示の範囲から外れずに、他の変化に適用されてもよい。したがって、その開示は、ここで記述した例およびデザインに制限されることは意図されず、ここに開示された本質および新しい特徴と一致する最も広い範囲を与えられる。

【特許請求の範囲】

【請求項1】

発振器からの発振信号を受け取り、入力位相の小数部および出力位相の小数部のみに基づいて位相エラーを決定し、前記位相エラーに基づいて前記発振器のための制御信号を生成するように構成されたデジタル位相同期ループ(DPLL)と、

を具備する装置。

【請求項2】

請求項1の装置であって、前記入力位相の前記小数部および前記出力位相の前記小数部は、前記発振信号の1サイクルの範囲をそれぞれ有する。

【請求項3】

請求項1の装置であって、前記DPLLは、前記発振信号と参照信号との間の位相差を決定し、前記出力位相の前記小数部として前記位相差を提供するように構成されたタイムデジタルコンバータ(TDC)を具備する。

【請求項4】

請求項1の装置であって、前記DPLLは、

前記入力位相を得るための少なくとも1つの入力信号を蓄積するように構成されたアキュムレータと、

前記入力位相を受け取り、前記入力位相の前記小数部を提供するように構成されたユニットと、

を具備する。

【請求項5】

請求項4の装置であって、前記少なくとも1つの入力信号は、変調信号を具備する。

【請求項6】

請求項1の装置であって、前記DPLLは、前記出力位相の前記小数部と前記入力位相の前記小数部との間の位相差を決定し、前記位相差が第1の値未満である場合は前記位相差に所定値を加え、前記位相差が第2の値より大きい場合は前記位相差から前記所定値を引き、前記位相エラーがある場合は前記所定値を加えるまたは引いた後に前記位相差を提供するように構成される。

【請求項7】

請求項6の装置であって、前記所定値は前記発振信号の1サイクルに相当し、前記第1の値は前記発振信号のマイナス2分の1サイクルに相当し、前記第2の値は前記発振信号のプラス2分の1サイクルに相当する。

【請求項8】

請求項1の装置であって、前記DPLLは、

前記発振信号のサイクル数のトラッキングを保持することによって前記出力位相の整数部を決定するように構成された無線周波数(RF)アキュムレータを具備し、

前記DPLLは、前記DPLLがロックされない場合は、前記入力位相の前記整数部および小数部、前記出力位相の前記整数部および前記小数部に基づいて前記位相エラーを決定し、前記DPLLがロックされる場合は、前記入力位相の前記小数部および前記出力位相の前記小数部にのみ基づいて前記位相エラーを決定するように構成される。

【請求項9】

発振器からの発振信号のために入力位相の小数部および出力位相の小数部にのみ基づいて位相エラーを決定することと、

前記位相エラーに基づいて前記発振器のために制御信号を生成することと、前記入力位相の前記小数部および前記出力位相の前記小数部は前記発振信号の1サイクルの範囲をそれぞれ有する、

を具備する方法。

【請求項10】

請求項9の方法であって、

前記発振信号と参照信号との間の位相差に基づいて前記出力位相の前記小数部を決定することと、

をさらに具備する。

【請求項11】

請求項9の方法であって、前記位相エラーを決定することは、

前記出力位相の前記小数部と前記入力位相の前記小数部との間の位相差を決定することと、

前記位相差が第1の値未満である場合は、前記位相差に所定値を加えることと、

前記位相差が第2の値より大きい場合は、前記位相差から所定値を引くことと、

前記位相エラーがある場合は前記所定値を加えるまたは引いた後に前記位相差を提供することと、

を具備する。

【請求項12】

請求項9の方法であって、

前記発振信号のサイクル数のトラッキングを保持することによって前記出力位相の整数部を決定することと、

ロックされない場合は、前記入力位相の前記整数部および小数部、前記出力位相の前記整数部および前記小数部に基づいて前記位相エラーを決定することと、

ロックされる場合は、前記入力位相の前記小数部および前記出力位相の前記小数部にのみ基づいて前記位相エラーを決定することと、

をさらに具備する。

【請求項13】

発振器からの発振信号のために入力位相の小数部および出力位相の小数部にのみ基づいて位相エラーを決定する手段と、

前記位相エラーに基づいて前記発振器のために制御信号を生成する手段と、前記入力位相の前記小数部および前記出力位相の前記小数部は前記発振信号の1サイクルの範囲をそれぞれ有する、

を具備する装置。

【請求項14】

請求項13の装置であって、

前記発振信号と参照信号との間の位相差に基づいて前記出力位相の前記小数部を決定する手段と、

をさらに具備する。

【請求項15】

請求項13の装置であって、前記位相エラーを決定する手段は、

前記出力位相の前記小数部と前記入力位相の前記小数部との間の位相差を決定する手段と、

前記位相差が第1の値未満である場合は、前記位相差に所定値を加える手段と、

前記位相差が第2の値より大きい場合は、前記位相差から所定値を引く手段と、

前記位相エラーがある場合は前記所定値を加えるまたは引いた後に前記位相差を提供する手段と、

を具備する。

【請求項16】

請求項13の装置であって、

前記発振信号のサイクル数のトラッキングを保持することによって前記出力位相の整数部を決定する手段と、

ロックされない場合は、前記入力位相の前記整数部および小数部、前記出力位相の前記整数部および前記小数部に基づいて前記位相エラーを決定する手段と、

ロックされる場合は、前記入力位相の前記小数部および前記出力位相の前記小数部にのみ基づいて前記位相エラーを決定する手段と、

をさらに具備する。

【請求項17】

コンピュータ可読媒体を具備するコンピュータプログラムプロダクトであって、

前記コンピュータ可読媒体は、

少なくとも1つのコンピュータに、発振器からの発振信号のために入力位相の小数部および出力位相の小数部にのみ基づいて位相エラーを決定させるためのコードと、

前記少なくとも1つのコンピュータに、前記位相エラーに基づいて前記発振器のために制御信号を生成させるためのコードと、前記入力位相の前記小数部および前記出力位相の前記小数部は前記発振信号の1サイクルの範囲をそれぞれ有する、

を具備する。

【請求項18】

発振器からの発振信号および参照信号を受け取り、前記発振器のための制御信号を生成するように構成されたデジタル位相同期ループ(DPLL)と、

を具備する装置であって、

前記DPLLは、前記発振信号のサイクル数のトラッキングを保持することによって粗い出力位相を決定するように構成された合成されたアキュムレータを具備し、

前記合成されたアキュムレータは、前記発振信号の周波数より低い周波数を有する前記参照信号に基づいて更新される。

【請求項19】

請求項18の装置であって、前記合成されたアキュムレータは、各最新間隔で第1の整数値または第2の整数値によって更新され、前記第1のまたは前記第2の整数値は、前記発振信号の前記周波数および前記参照信号の前記周波数によって決定された連続する整数値である。

【請求項20】

請求項19の装置であって、前記DPLLは、各最新間隔で第1および第2の整数値のための2つの仮説を評価し、前記2つの仮説の評価の結果に基づいて各最新間隔で第1または第2の整数値によって前記合成されたアキュムレータを更新するために指示を提供するように構成された評価ユニットをさらに具備する。

【請求項21】

請求項20の装置であって、前記DPLLは、前記発振信号と前記参照信号との間の位相差に基づいて細かい出力位相を決定するように構成されたタイムデジタルコンバータ(TDC)をさらに具備し、

前記評価ユニットは、第1および第2の整数値、前記粗い出力位相、前記細かい出力位相および前記入力位相に基づいて前記2つの仮説を評価するように構成される。

【請求項22】

請求項21の装置であって、前記評価ユニットは、前記第1の整数値、前記粗い出力位相および前記細かい出力位相に基づいて第1の仮定された出力位相を決定し、前記第2の整数値、前記粗い出力位相および前記細かい出力位相に基づいて第2の仮定された出力位相を決定し、前記第1の仮定された出力位相が前記第2の仮定された出力位相より前記入力位相に接近している場合に前記第1の整数値によってまたは別の前記第2の整数値によって前記合成されたアキュムレータを更新するために指示を提供するように構成される。

【請求項23】

請求項21の装置であって、前記評価ユニットは、前記第1の整数値、前記粗い出力位相、前記細かい出力位相および前記入力位相に基づいて第1の仮定された位相エラーを決定し、前記第2の整数値、前記粗い出力位相、前記細かい出力位相および前記入力位相に基づいて第2の仮定された位相エラーを決定し、前記第1の仮定された位相エラーの大きさが前記第2の仮定された位相の大きさより小さい場合に前記第1の整数値によってまたは別の前記第2の整数値によって前記合成されたアキュムレータを更新するために指示を提供するように構成される。

【請求項24】

請求項18の装置であって、前記DPLLは、

前記発振信号のサイクル数のトラッキングを保持することによって前記粗い出力位相を決定するように構成された無線周波数(RF)アキュムレータと、前記RFアキュムレータは前記発振信号に基づいて操作される、

をさらに具備する。

【請求項25】

請求項24の装置であって、前記RFアキュムレータは、第1の持続時間の間イネーブルにされ、第2の持続時間の間ディセーブルにされ、前記合成されたアキュムレータは、前記第2の持続時間の間イネーブルにされる。

【請求項26】

請求項24の装置であって、前記DPLLは、前記DPLLがロックされるかどうかを決定するように構成されたロック検出器をさらに具備し、

前記RFアキュムレータは、前記DPLLがロックされない場合にイネーブルにされ、

前記合成されたアキュムレータは、前記DPLLがロックした後にイネーブルにされる。

【請求項27】

発振信号の周波数より低い周波数を有する参照信号に基づいて、発振器からの前記発振信号のサイクル数のトラッキングを保持することにより、粗い出力位相を決定することと、

前記粗い出力位相および入力位相に基づいて位相エラーを決定することと、

前記位相エラーに基づいて前記発振器のために制御信号の生成することと、

を具備する方法。

【請求項1】

発振器からの発振信号を受け取り、入力位相の小数部および出力位相の小数部のみに基づいて位相エラーを決定し、前記位相エラーに基づいて前記発振器のための制御信号を生成するように構成されたデジタル位相同期ループ(DPLL)と、

を具備する装置。

【請求項2】

請求項1の装置であって、前記入力位相の前記小数部および前記出力位相の前記小数部は、前記発振信号の1サイクルの範囲をそれぞれ有する。

【請求項3】

請求項1の装置であって、前記DPLLは、前記発振信号と参照信号との間の位相差を決定し、前記出力位相の前記小数部として前記位相差を提供するように構成されたタイムデジタルコンバータ(TDC)を具備する。

【請求項4】

請求項1の装置であって、前記DPLLは、

前記入力位相を得るための少なくとも1つの入力信号を蓄積するように構成されたアキュムレータと、

前記入力位相を受け取り、前記入力位相の前記小数部を提供するように構成されたユニットと、

を具備する。

【請求項5】

請求項4の装置であって、前記少なくとも1つの入力信号は、変調信号を具備する。

【請求項6】

請求項1の装置であって、前記DPLLは、前記出力位相の前記小数部と前記入力位相の前記小数部との間の位相差を決定し、前記位相差が第1の値未満である場合は前記位相差に所定値を加え、前記位相差が第2の値より大きい場合は前記位相差から前記所定値を引き、前記位相エラーがある場合は前記所定値を加えるまたは引いた後に前記位相差を提供するように構成される。

【請求項7】

請求項6の装置であって、前記所定値は前記発振信号の1サイクルに相当し、前記第1の値は前記発振信号のマイナス2分の1サイクルに相当し、前記第2の値は前記発振信号のプラス2分の1サイクルに相当する。

【請求項8】

請求項1の装置であって、前記DPLLは、

前記発振信号のサイクル数のトラッキングを保持することによって前記出力位相の整数部を決定するように構成された無線周波数(RF)アキュムレータを具備し、

前記DPLLは、前記DPLLがロックされない場合は、前記入力位相の前記整数部および小数部、前記出力位相の前記整数部および前記小数部に基づいて前記位相エラーを決定し、前記DPLLがロックされる場合は、前記入力位相の前記小数部および前記出力位相の前記小数部にのみ基づいて前記位相エラーを決定するように構成される。

【請求項9】

発振器からの発振信号のために入力位相の小数部および出力位相の小数部にのみ基づいて位相エラーを決定することと、

前記位相エラーに基づいて前記発振器のために制御信号を生成することと、前記入力位相の前記小数部および前記出力位相の前記小数部は前記発振信号の1サイクルの範囲をそれぞれ有する、

を具備する方法。

【請求項10】

請求項9の方法であって、

前記発振信号と参照信号との間の位相差に基づいて前記出力位相の前記小数部を決定することと、

をさらに具備する。

【請求項11】

請求項9の方法であって、前記位相エラーを決定することは、

前記出力位相の前記小数部と前記入力位相の前記小数部との間の位相差を決定することと、

前記位相差が第1の値未満である場合は、前記位相差に所定値を加えることと、

前記位相差が第2の値より大きい場合は、前記位相差から所定値を引くことと、

前記位相エラーがある場合は前記所定値を加えるまたは引いた後に前記位相差を提供することと、

を具備する。

【請求項12】

請求項9の方法であって、

前記発振信号のサイクル数のトラッキングを保持することによって前記出力位相の整数部を決定することと、

ロックされない場合は、前記入力位相の前記整数部および小数部、前記出力位相の前記整数部および前記小数部に基づいて前記位相エラーを決定することと、

ロックされる場合は、前記入力位相の前記小数部および前記出力位相の前記小数部にのみ基づいて前記位相エラーを決定することと、

をさらに具備する。

【請求項13】

発振器からの発振信号のために入力位相の小数部および出力位相の小数部にのみ基づいて位相エラーを決定する手段と、

前記位相エラーに基づいて前記発振器のために制御信号を生成する手段と、前記入力位相の前記小数部および前記出力位相の前記小数部は前記発振信号の1サイクルの範囲をそれぞれ有する、

を具備する装置。

【請求項14】

請求項13の装置であって、

前記発振信号と参照信号との間の位相差に基づいて前記出力位相の前記小数部を決定する手段と、

をさらに具備する。

【請求項15】

請求項13の装置であって、前記位相エラーを決定する手段は、

前記出力位相の前記小数部と前記入力位相の前記小数部との間の位相差を決定する手段と、

前記位相差が第1の値未満である場合は、前記位相差に所定値を加える手段と、

前記位相差が第2の値より大きい場合は、前記位相差から所定値を引く手段と、

前記位相エラーがある場合は前記所定値を加えるまたは引いた後に前記位相差を提供する手段と、

を具備する。

【請求項16】

請求項13の装置であって、

前記発振信号のサイクル数のトラッキングを保持することによって前記出力位相の整数部を決定する手段と、

ロックされない場合は、前記入力位相の前記整数部および小数部、前記出力位相の前記整数部および前記小数部に基づいて前記位相エラーを決定する手段と、

ロックされる場合は、前記入力位相の前記小数部および前記出力位相の前記小数部にのみ基づいて前記位相エラーを決定する手段と、

をさらに具備する。

【請求項17】

コンピュータ可読媒体を具備するコンピュータプログラムプロダクトであって、

前記コンピュータ可読媒体は、

少なくとも1つのコンピュータに、発振器からの発振信号のために入力位相の小数部および出力位相の小数部にのみ基づいて位相エラーを決定させるためのコードと、

前記少なくとも1つのコンピュータに、前記位相エラーに基づいて前記発振器のために制御信号を生成させるためのコードと、前記入力位相の前記小数部および前記出力位相の前記小数部は前記発振信号の1サイクルの範囲をそれぞれ有する、

を具備する。

【請求項18】

発振器からの発振信号および参照信号を受け取り、前記発振器のための制御信号を生成するように構成されたデジタル位相同期ループ(DPLL)と、

を具備する装置であって、

前記DPLLは、前記発振信号のサイクル数のトラッキングを保持することによって粗い出力位相を決定するように構成された合成されたアキュムレータを具備し、

前記合成されたアキュムレータは、前記発振信号の周波数より低い周波数を有する前記参照信号に基づいて更新される。

【請求項19】

請求項18の装置であって、前記合成されたアキュムレータは、各最新間隔で第1の整数値または第2の整数値によって更新され、前記第1のまたは前記第2の整数値は、前記発振信号の前記周波数および前記参照信号の前記周波数によって決定された連続する整数値である。

【請求項20】

請求項19の装置であって、前記DPLLは、各最新間隔で第1および第2の整数値のための2つの仮説を評価し、前記2つの仮説の評価の結果に基づいて各最新間隔で第1または第2の整数値によって前記合成されたアキュムレータを更新するために指示を提供するように構成された評価ユニットをさらに具備する。

【請求項21】

請求項20の装置であって、前記DPLLは、前記発振信号と前記参照信号との間の位相差に基づいて細かい出力位相を決定するように構成されたタイムデジタルコンバータ(TDC)をさらに具備し、

前記評価ユニットは、第1および第2の整数値、前記粗い出力位相、前記細かい出力位相および前記入力位相に基づいて前記2つの仮説を評価するように構成される。

【請求項22】

請求項21の装置であって、前記評価ユニットは、前記第1の整数値、前記粗い出力位相および前記細かい出力位相に基づいて第1の仮定された出力位相を決定し、前記第2の整数値、前記粗い出力位相および前記細かい出力位相に基づいて第2の仮定された出力位相を決定し、前記第1の仮定された出力位相が前記第2の仮定された出力位相より前記入力位相に接近している場合に前記第1の整数値によってまたは別の前記第2の整数値によって前記合成されたアキュムレータを更新するために指示を提供するように構成される。

【請求項23】

請求項21の装置であって、前記評価ユニットは、前記第1の整数値、前記粗い出力位相、前記細かい出力位相および前記入力位相に基づいて第1の仮定された位相エラーを決定し、前記第2の整数値、前記粗い出力位相、前記細かい出力位相および前記入力位相に基づいて第2の仮定された位相エラーを決定し、前記第1の仮定された位相エラーの大きさが前記第2の仮定された位相の大きさより小さい場合に前記第1の整数値によってまたは別の前記第2の整数値によって前記合成されたアキュムレータを更新するために指示を提供するように構成される。

【請求項24】

請求項18の装置であって、前記DPLLは、

前記発振信号のサイクル数のトラッキングを保持することによって前記粗い出力位相を決定するように構成された無線周波数(RF)アキュムレータと、前記RFアキュムレータは前記発振信号に基づいて操作される、

をさらに具備する。

【請求項25】

請求項24の装置であって、前記RFアキュムレータは、第1の持続時間の間イネーブルにされ、第2の持続時間の間ディセーブルにされ、前記合成されたアキュムレータは、前記第2の持続時間の間イネーブルにされる。

【請求項26】

請求項24の装置であって、前記DPLLは、前記DPLLがロックされるかどうかを決定するように構成されたロック検出器をさらに具備し、

前記RFアキュムレータは、前記DPLLがロックされない場合にイネーブルにされ、

前記合成されたアキュムレータは、前記DPLLがロックした後にイネーブルにされる。

【請求項27】

発振信号の周波数より低い周波数を有する参照信号に基づいて、発振器からの前記発振信号のサイクル数のトラッキングを保持することにより、粗い出力位相を決定することと、

前記粗い出力位相および入力位相に基づいて位相エラーを決定することと、

前記位相エラーに基づいて前記発振器のために制御信号の生成することと、

を具備する方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2012−257269(P2012−257269A)

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−158980(P2012−158980)

【出願日】平成24年7月17日(2012.7.17)

【分割の表示】特願2010−536210(P2010−536210)の分割

【原出願日】平成20年11月29日(2008.11.29)

【出願人】(595020643)クゥアルコム・インコーポレイテッド (7,166)

【氏名又は名称原語表記】QUALCOMM INCORPORATED

【Fターム(参考)】

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【出願番号】特願2012−158980(P2012−158980)

【出願日】平成24年7月17日(2012.7.17)

【分割の表示】特願2010−536210(P2010−536210)の分割

【原出願日】平成20年11月29日(2008.11.29)

【出願人】(595020643)クゥアルコム・インコーポレイテッド (7,166)

【氏名又は名称原語表記】QUALCOMM INCORPORATED

【Fターム(参考)】

[ Back to top ]