少なくとも1つの複数の厚さを有する活性部を備える構造を形成するための方法

【課題】少なくとも1つが単結晶半導体からなる数層によって形成される活性部を備える構造を形成する、SOI基板を用いるよりも低コストであり、より速い方法を提供すること。

【解決手段】第1の単結晶シリコン基板から少なくとも2つの層を備える活性部を備える構造を製造する方法であって、a)第1の基板に少なくとも1つの多孔質シリコン領域を形成する段階、b)第1の基板の表面全体及び多孔質シリコン領域の表面に単結晶シリコン層をエピタキシャル成長成膜させる段階、c)多孔質シリコン領域にエピタキシャル成長された単結晶層を加工して第1の懸架領域を形成する段階、d)多孔質シリコンを除去または酸化する段階、g)シリコンに対して選択的な犠牲層を成膜する段階、f)第1の基板を加工する段階、及びg)犠牲層を除去することによって懸架領域をリリースする段階を備える方法である。

【解決手段】第1の単結晶シリコン基板から少なくとも2つの層を備える活性部を備える構造を製造する方法であって、a)第1の基板に少なくとも1つの多孔質シリコン領域を形成する段階、b)第1の基板の表面全体及び多孔質シリコン領域の表面に単結晶シリコン層をエピタキシャル成長成膜させる段階、c)多孔質シリコン領域にエピタキシャル成長された単結晶層を加工して第1の懸架領域を形成する段階、d)多孔質シリコンを除去または酸化する段階、g)シリコンに対して選択的な犠牲層を成膜する段階、f)第1の基板を加工する段階、及びg)犠牲層を除去することによって懸架領域をリリースする段階を備える方法である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えばセンサまたはアクチュエータを形成するための微小電気機械システム(MEMS)及び/またはナノ電気機械システム(NEMS)の形成に用いることができる少なくとも1つの複数の厚さを有する活性部を備える構造を形成する方法に関する。

【背景技術】

【0002】

MEMS及びNEMSセンサは、固定部及び固定部に対して懸架された少なくとも1つの部分を備え、「活性部」と呼ばれる1つまたは複数の懸架された部分は、機械的、電気的、磁気的動作のような外部の動作の効果の下、変位及び/または変形することが可能である。

【0003】

固定部に対する可動部の変位及び/または変形は、例えば、加速度計の場合には加速度、ジャイロメータの場合にはコリオリ力を判別可能にする。可動部の変位は、例えばひずみゲージによって測定される。

【0004】

非特許文献1には、平面内加速度計を形成するMEMS及びNEMS構造が記載されている。この構造は、2つの異なる活性部の厚さで形成された活性部を備える。ひずみゲージを形成するNEMS部はこれらの活性部の厚さのうち1つを備え、振動錘を形成するMEMS部は、2つの活性部の厚さを備える。

【0005】

そのような活性部を形成する方法は、コスト費の高いSOI(Silicon on Insulator)型基板から形成される。さらには、厚いエピタキシャル成長段階が実施され、そのような段階は一般的に長く高価である。ひずみゲージは、SOI基板から形成され、振動錘はSOI基板及び厚いエピタキシャル形成された層から形成される。

【0006】

一方、活性部を画定する段階は、酸化物層を用い、その上にエピタキシャル成長を部分的に行う。

【0007】

しかしながら、酸化物層上にエピタキシャル形成された層は、酸化物層で保護された両者の厚さの間の界面領域において単結晶層ではない。これらの「多結晶」領域は、構造内に欠陥を発生させる可能性がある。

【0008】

さらには、エピタキシャル成長の速度は、成長が単結晶シリコン上で行われる領域と、成長が、例えば両者の厚さの界面を形成する酸化物層上で行われる領域との間で異なる。この成長速度の違いによって、最終的な構造において厚さの不均一性が大きくなる可能性がある。

【0009】

単結晶層内の多結晶領域の存在及び厚さの不均一性の存在によるこの構造の不均一性の問題は、3つ以上の異なる層または2つの高領域層間にある界面領域を利用することが望ましい場合に、全て、さらに問題となる。

【先行技術文献】

【非特許文献】

【0010】

【非特許文献1】Ph.Robert,V.Nguyen,S.Hentz,L.Duraffourg,G.Jourdan,J.Arcamone,S.Harrison,M&NEMS:A new approach for ultra−low cost 3D inertial sensor,IEEE SENSORS 2009 Conference 25−28 October 2009 Christchurch New Zealand, (2009)

【発明の概要】

【発明が解決しようとする課題】

【0011】

従って、本発明の目的は、少なくとも1つが単結晶半導体材料らなる数層によって形成される活性部を備える構造を形成する、SOI基板を用いる方法よりも低コストであり、より速い方法を提供することである。

【課題を解決するための手段】

【0012】

本発明の目的は、複数層の活性部を有する構造を形成する方法によって達成され、その方法は、基板上に単結晶半導体材料をエピタキシャル成長させる段階を備え、エピタキシーが行われる少なくともその表面が、単結晶半導体材料からなり、基板が、半導体材料が不連続である少なくとも1つの領域を備える。

【0013】

本出願において、「半導体材料が不連続である領域」は、多孔質材料または半導体材料からなり互いに短い間隔で配される複数の細い柱のいずれかによって形成される領域を意味する。

【0014】

エピタキシーの段階は、SOI基板から形成されるのと類似した第1の活性層を形成するために用いられる。この第1の層は、一般的に薄い厚さである。第2の活性層は、一般的に第1の活性層よりも厚く、次いで、有利には第2の基板を接合した後に第1の基板の「バルク」部の全てまたは一部によって形成される。一方SOI基板を用いる従来の方法では、この第2の活性層は、エピタキシャル形成される。そのため、厚いエピタキシーに関する欠点が回避される。

【0015】

本発明によれば、エピタキシャル成長した層は、単結晶層であり、成長層によるエピタキシャルに対して選択的に離隔させることができる多孔質層上に成長させるため、結果的に多孔質層は犠牲層として働く。

【0016】

さらには、不連続な半導体材料上へのエピタキシー成長のために、界面における多結晶領域の発生が起こらず、成長速度は不連続な半導体材料と基板の単結晶半導体材料との間でほぼ均一である。

【0017】

本発明に従う製造方法は、SOI基板を用いる必要がなく、厚いエピタキシーを実施しないため、このことにより製造コスト及び時間を得ることができる。それに加えて、厚さの不均一性が減少されるために、厚さの違いを補うために重要な化学的機械的研磨の段階を有する必要がない。

【0018】

非常に有利なことに、多孔質領域の実施形態において、この実施形態は表面上に非常に小さい穴を備えるため、このことが、この多孔質領域上にエピタキシャル成長するシリコンの品質を向上させ、深い部分がより大きい穴では、選択性エッチングまたはより高速な酸化を行うことができる。

【0019】

従って、本発明の対象は、単結晶半導体材料からなる、前面と呼ばれる第1の平面及び第1の平面と対向する背面と呼ばれる第2の平面を備える第1の基板から少なくとも2つの層を備える活性部を備える構造を製造する方法を提供することであり、この方法は、次の段階を備える。

【0020】

a)単結晶半導体材料からなる前面から、第1の基板内に不連続な半導体材料の少なくとも1つの領域を形成する段階。

【0021】

b)第1の基板の前面上の半導体材料から、層のエピタキシャル成長成膜を行う段階であって、層が不連続な半導体材料の領域の表面上の少なくとも単結晶層である、段階。

【0022】

c)エピタキシャル成長した単結晶層を、少なくとも不連続な半導体材料の領域において加工し、第1の懸架領域を形成する段階。

【0023】

d)不連続な半導体材料を除去または酸化する段階。

【0024】

e)前面の半導体材料及びエピタキシャル成長した半導体層の材料に対して選択的にエッチングすることができる犠牲層を形成する段階。

【0025】

f)犠牲層からいくつかの領域をクリアにするまで第1の基板の背面を加工し、第2の懸架領域を形成し、第1の懸架領域に到達できるようにする段階。

【0026】

g)犠牲層の少なくとも一部を除去することにより第1及び第2の懸架領域をリリースする段階。

【0027】

段階e)において、犠牲層の形成は、少なくとも前面上で行い、その結果、第1の懸架領域を完全にまたは部分的に覆う。

【0028】

エピタキシャル成長の段階は、第1の基板の前面の半導体材料と同じ材料または面の材料に近い格子定数を好適には有する他の半導体材料から形成することができる。

【0029】

犠牲層の形成は、例えば酸化物の成膜によって及び/または熱酸化によって行われる。

【0030】

この方法は、有利には、段階e)の後であって段階f)の前に、第1の基板の前面上に第2の基板を接合または成膜する段階e’)を備えることができる。

【0031】

第1の実施形態において、段階a)の間に、多孔質半導体材料の領域が形成される。多孔質半導体材料の領域は、電気化学エッチングによって達成される。

【0032】

有利な例において、多孔質半導体材料の領域は、表面においてより小さく、深い部分でより大きい穴を備える。

【0033】

段階d)において、多孔質半導体材料の除去は、エッチング、例えばウェットエッチングまたは、多孔質半導体材料の熱酸化及び酸化された多孔質半導体材料のエッチング、例えば、ウェットエッチング及び/または蒸気エッチングによるエッチングによって行うことができる。

【0034】

他の一実施形態において、段階a)の間、半導体材料の領域は、複数の小さな断面積の柱を備え、互いに短い間隔で配されるように形成される。段階a)は、次の段階を備えることができる。

【0035】

柱を画定するマスクを形成する段階。

【0036】

柱の間の領域をエッチングする段階。

【0037】

マスクを除去する段階。

【0038】

この実施形態において、段階d)の間に、柱を形成する半導体材料を除去する段階は、材料の融点に近い温度でアニールすることにより行われる。

【0039】

選択的に、この方法は、段階e’)に先立って、第2の基板を構造形成する段階を備える。例えば、構造形成の段階において、第2の基板の表面がエッチングされて第2の懸架部のための機械的停止部を形成し、第2の基板の接合段階における接合層を形成するために層の構造形成された表面に成膜が行われる。

【0040】

追加的な特徴に従えば、この方法は、段階e)に引き続いて、犠牲層を構造形成する段階及び/または犠牲層上に1つまたは複数の中間層を成膜する段階を備えることができ、中間層は構造形成されることができる。犠牲層及び1つまたは複数の中間層の構造形成は、例えば、リソグラフィ及びそれぞれ基板上で停止する犠牲層のエッチング及び犠牲層上で停止する1つまたは複数の中間層のエッチングによって行うことができる。

【0041】

この方法は、構造形成された犠牲層及び/または1つまたは複数の中間層上にSiO2層を成膜し、平坦化する段階を備えることができ、SiO2層は接合において用いられる。

【0042】

第1及び第2の基板の接合は、直接接合または共晶接合によって行われる。

【0043】

一例に従えば、第1の基板は、段階a)の前に構造形成される。

【0044】

段階e’)の後に、第1の基板及び/または第2の基板は、背面の裏面研削及びそれに次いで化学的機械的研磨によって薄化されることができる。

【0045】

この方法は、段階a)に先立って、基板の前面上に多孔質半導体層を形成し、多孔質半導体層上に単結晶半導体層をエピタキシャル成長させる段階を備えることができ、単結晶半導体層は、不連続多孔質領域が形成される前面を形成する。接合に引き続いて、多孔質半導体層は、例えばエッチングされて第1の基板を薄化する。

【0046】

第1の実施形態において、多孔質半導体材料のいくつかの領域を形成することができ、これは異なる深さを有する。

【0047】

第2の懸架領域を形成するための加工及び第1の懸架領域を利用可能にするための加工を行う段階f)は、領域において第1の基板を同時に加工することによって、またはこれらの領域のそれぞれにおいて逐次的に加工することによって行うことができる。

【0048】

3つ以上の層を有する活性部を形成するために、段階a)からe)が繰り返される。

【0049】

第1の基板の前面の半導体材料、第2の基板及びエピタキシーによって形成された層は、好適にはシリコンからなる。

【0050】

この方法は、有利には、センサ及び/またはアクチュエータを形成するための微小電気機械構造及び/またはナノ電気機械構造を形成することができる。

【0051】

本発明は、以下の説明および添付された図面を用いてより理解されるであろう。

【図面の簡単な説明】

【0052】

【図1A】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1B】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1C】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1D】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1E】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1F】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1G】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

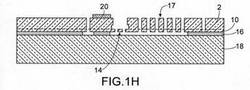

【図1H】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図2A】第1の実施形態の代替的な形成方法のそれぞれの段階を示す概略図である。

【図2B】第1の実施形態の代替的な形成方法のそれぞれの段階を示す概略図である。

【図2C】第1の実施形態の代替的な形成方法のそれぞれの段階を示す概略図である。

【図3A】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図3B】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図3C】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図3D】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図3E】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図4A】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図4B】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図4C】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図4D】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図4E】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図5A】第2の実施形態に従う製造方法の第1の各段階を示す概略図である。

【図5B】第2の実施形態に従う製造方法の第1の各段階を示す概略図である。

【図5C】第2の実施形態に従う製造方法の第1の各段階を示す概略図である。

【図5D】第2の実施形態に従う製造方法の第1の各段階を示す概略図である。

【図6A】第2の実施形態に従う代替的な製造方法の第1の各段階を示す概略図である。

【図6B】第2の実施形態に従う代替的な製造方法の第1の各段階を示す概略図である。

【図6C】第2の実施形態に従う代替的な製造方法の第1の各段階を示す概略図である。

【図6D】第2の実施形態に従う代替的な製造方法の第1の各段階を示す概略図である。

【図6E】第2の実施形態に従う代替的な製造方法の第1の各段階を示す概略図である。

【発明を実施するための形態】

【0053】

図1Aから1Hには、少なくとも1つが単結晶半導体材料からなるいくつかの層によって形成された活性部を備える構造を形成するための本発明に従う方法の第1の実施形態の各段階が示されている。

【0054】

本出願において、MEMS及び/またはNEMS構造の「活性部」は、外部の(機械的、電気的、磁気的など)の動作の影響のもとに変位及び/または変形するような懸架部を意味する。

【0055】

以下の説明において、簡単化のために、半導体材料としてシリコンの例が用いられる。他のどのような半導体材料の利用も、本発明の範囲から逸脱するものではないことに注意すべきである。

【0056】

第1の実施形態に従う方法は、バルク型シリコン基板から、以下の主要な段階を備える。

【0057】

a)この基板の全てまたは一部に1つまたは複数の多孔質シリコン領域を形成する段階。

【0058】

b)基板の表面全体上及び多孔質シリコンの表面上にシリコンまたは単結晶SiGeエピタキシーを行う段階。

【0059】

c)エピタキシャル成長されたシリコンまたはSiGe層を加工して、単結晶シリコンの第1の厚さに、第1の懸架領域の形状を画定し、多孔質シリコンの一部を局所的に開口する段階。

【0060】

d)完全にまたは部分的に多孔質シリコンを除去もしくは多孔質シリコンを熱酸化する段階。

【0061】

e)シリコンに対して選択的な犠牲層を成膜及び/または熱酸化する段階。

【0062】

f)犠牲層及び/または多孔質シリコン領域の全てまたは一部からいくつかの領域をクリアにするまで第1の基板を加工し、第2の懸架領域を形成し、第1の懸架領域の全てまたは一部をクリアにする段階。

【0063】

g)犠牲層を除去することによって懸架領域をリリースする段階。

【0064】

有利には、段階e)とf)との間に、第1の基板の背面上に支持部を移設または成膜し構造化する段階e’)が設けられる。

【0065】

この方法の段階a)からg)をこれから詳細に説明する。

【0066】

本発明に従う方法は、有利には単結晶シリコンの第1の基板2を用いる。

【0067】

第1の段階a)において、マスク4が、約100nmの厚さの層を成膜することによって基板2の表面上に形成される。この層4は、例えば窒化シリコンからなる。

【0068】

次いで、リソグラフィの段階を層4に行ってエッチングされるべき層2の領域を画定し、層4のエッチングの段階を行って、基板2の領域6を露出させる。

【0069】

次の段階において、領域6は所定の厚さで、例えば電気化学エッチングを用いる多孔質化によって、多孔質化される。このエッチングは、時間によるエッチングである。多孔質を形成されるシリコンの厚さは0.1μmから10μmの間であり、有利には、約1μmに等しい。

【0070】

図1Aに概略的に示された要素が得られ、多孔質シリコンの部分は符号8によって示される。

【0071】

1つまたは複数の多孔質部を形成することは、本発明の範囲内であり、形成される構造による。

【0072】

特に有利には、多孔質部6は、表面で非常に小さい大きさを有する穴6.1及び深い部分でより大きい穴6.2を備え、穴6.1により、この多孔質部の上にエピタキシャル成長されるシリコンの質が向上し、穴6.2により多孔質シリコンの選択的エッチングまたはより高速な酸化が可能となる。異なる穴の大きさを有するこの多孔質部は、多孔質化の段階において電気化学エッチングの条件を変化させることにより、例えば電流密度を変化させることにより、得ることができる。例えば、望まれる穴の大きさは2から50nmの間であり、このとき得られる材料はメソポーラス型からなる。

【0073】

次の段階において、マスク4が、例えば窒化シリコンの化学的エッチングによって除去される。

【0074】

次いで、シリコンまたはSiGe層10のエピタキシャル成長の段階b)が行われ、この層は、多孔質部6上の単結晶層であり、基板表面の残り全体の上では単結晶層または多結晶であってもよい。シリコンまたは多結晶SiGeは、例えばエピタキシー前の基板の表面に酸化物層または窒化物層を成膜することによって得られる。層10の厚さは数10nmから数10μmの間であり、有利には約0.25μmに等しい。

【0075】

層10は、第1の基板と同一の半導体材料または第1の基板の材料と近い格子定数を好適には有する他の半導体材料からなるものであってもよい。例えば、上述のように、第1のSi基板の場合には、SiまたはSiGeエピタキシーが例えば実施される。

【0076】

明瞭化のために、それぞれの段階の概略図において、層10及び基板2は点線によって分離されている。

【0077】

このようにして得られた要素が、図1Bに示されている。多孔質領域6の上に形成されたシリコン部12は、第1の懸架領域14を形成するためにエッチングされる。

【0078】

次の段階c)において、第1の懸架領域14が画定する。このために、リソグラフィを行って層10の表面上にマスクを形成し、次いで多孔質シリコン6の部分の上または中で停止する部分12のエッチングが実施される。

【0079】

エッチングは例えば深掘り反応性イオンエッチング(DRIE)である。

【0080】

第1の懸架領域14は、いわゆるM及びNEMS構造の場合にはNEMS部を形成する。

【0081】

このようにして得られた要素が、図1Cに示されている。

【0082】

次の段階d)において、多孔質部6の除去が行われ、そうでない場合には多孔質部6が単に酸化される。

【0083】

この除去は、多孔質シリコンのウェットエッチングによって実施することができる。このエッチングは、「非多孔質」シリコンよりも速く多孔質シリコンをエッチングするという特性を有し、そのためエッチング時間を制御することによって、懸架領域14は全くまたはほとんどエッチングされないのに対して、多孔質シリコンは除去される。エッチングの継続時間は、用いられるエッチング溶液の濃度及び温度の関数として、数秒から数分の間とすることが可能であり、このエッチング溶液は、KOH、TMAH(テトラメチルアンモニウムヒドロキサイド)などとすることが可能である。典型的には、エッチングは、KOH溶液で室温においては数分間続ける。

【0084】

代替的に、多孔質シリコンの除去は、まず熱酸化を行い、次いで蒸気及び/またはウェットフッ酸エッチングによって、形成された酸化物をエッチングすることによって、2つの段階で達成される。多孔質シリコンは、「非多孔質」シリコンよりもずっと高速で酸化され、そのため酸化段階の継続時間を制御することにより、ほとんど多孔質シリコンだけを酸化することが可能である。例えば、数10nmの厚さのシリコンを酸化することを試みる。酸化の条件は当業者に周知であり、詳細に説明しない。この代替例に従えば、このエッチングは以下で説明される犠牲層のエッチングの間に行うことが可能である。そのため、この方法の時間は、有利に減少させることができる。

【0085】

このようにして得られた要素が、図1Dに示される。

【0086】

次の段階e)において、成膜16が第1の基板の前面において行われ、完全にまたは部分的に第1の懸架領域14を覆い、第1の基板の前面を覆う。成膜16の材料はシリコンに対して選択的であり、例えばSiO2からなる。次いで層16は犠牲層を形成する。この層16はまた、多孔質Siのエッチングのキャビティを(完全にまたは部分的に)ふさぐことができる。有利には、この層16を成膜する前に例えば数10nmの深さのシリコンのわずかな熱酸化を行うことができる。懸架領域14の周囲及びキャビティ内の熱酸化は、停止層を形成し、段階f)の加工における保護の確実性を向上させることができる。多孔質シリコンが単に酸化されている場合には、被覆は部分的または第1の懸架領域14のみを覆う。

【0087】

層16を成膜した後に得られる表面の表面形状又は粗さが極めて高い場合には、酸化物層16の平坦化の段階を行うことができる。この平坦化は例えば、化学的機械的研磨によって行われる。

【0088】

このようにして得られた要素が、図1Eに示される。

【0089】

有利には、このとき支持部が第1の基板の背面上に接合または成膜される(段階e’)。示された例においては、支持部は、前面において第1の基板に接合された単結晶シリコンの第2の基板18によって形成される。次いで犠牲層16が第1の基板2と第2の基板18との間に設けられる。

【0090】

この組み立ては、例えば当業者に周知の技術であるシリコン直接接合(silicon direct bonding,SDB)によって行われる。支持部または第2の基板の成膜の場合、これはローリングによって実施することが可能である。

【0091】

支持部は、第1の基板と異なる材料からなるものとしてもよく、例えばパイレックス(登録商標)のガラス支持部の使用であっても考えることが可能である。

【0092】

このようにして得られた要素が、図1Fに示される。

【0093】

第1の基板の薄化は、例えば「裏面研削」及び化学的機械的研磨によって実施することが可能である。

【0094】

この薄化は、いわゆるMEMS及びNEMS構造の場合において、MEMS部の厚さを画定することが可能である。

【0095】

次の段階において、電気的コンタクト20を、第1の基板2の背面において形成するために、金属層の成膜が実施され、この背面は第1及び第2の基板の接合によって得られる要素の前面を形成する。

【0096】

コンタクト20を形成するために、リソグラフィ段階、次いでエッチング段階が実施される。

【0097】

段階f)において、リソグラフィ及び例えば第1の基板2の深掘り反応性イオンエッチング(DRIE)型のエッチングを行い、第1の懸架領域14をクリアにし、第2の懸架領域17、例えばいわゆるMEMS及びNEMS構造の場合におけるMEMS部を形成する。エッチングは、犠牲層16及びこれまでに除去されていない場合には多孔質シリコンに到達する。第1の基板の構造形成の段階は、MEMS及びNEMS技術において知られた段階である。

【0098】

このようにして得られた要素が、図1Gに示される。

【0099】

最後に、段階g)において、懸架領域14及び17は、例えば犠牲層16及びもしあれば酸化された多孔質シリコンの、フッ酸を用いたウェットエッチングまたは蒸気相エッチングによってリリースされる。これは、時間によるエッチングである(図1H)。

【0100】

図2Aから2Cには、図1Aから1Hの製造方法の代替的な実施形態が示され、第2の基板118が、第1の基板に接合される前に構造形成される。

【0101】

このような事前の構造形成は、例えば電気的配線や1つまたは複数のキャビティを形成する1つまたは複数の活性部を励起する電極が設けられた基板を形成するために、CMOS回路を製造するために実施することが可能である。

【0102】

第2の基板118の構造形成は、以下のようにして行うことが可能である。

【0103】

第1の段階において、フォトリソグラフィの段階が、エッチングされるべき基板の表面の領域を画定するために実施され、例えば0.5μmの深さだけ基板の表面をエッチングする。このエッチングは、時間で停止するエッチングである。このようにして機械的停止部122が形成される。

【0104】

次いで、SiO2層124が構造形成された表面に成膜され、この層は接合層を形成する。

【0105】

最後に、層26の平坦化の段階が実施される。

【0106】

このようにして得られた要素が、図2Aに示される。

【0107】

次いで、第2の構造形成された基板118と第1の基板2との接合が行われる。層24は、例えば前述したように直接接合を通じて犠牲層16と接触した状態にされる。

【0108】

次いで、例えば「裏面研削」によって第1の基板の薄化の段階が実施され、このことによりMEMS及びNEMSシステムの場合において例えばMEMS部の厚さを画定することができる。

【0109】

このようにして得られた要素が、図2Bに示される。

【0110】

次いで、電気的コンタクトが、図1Aから1Hの方法と類似した方法で形成される。

【0111】

次いで、第1の基板2が、段階f)と類似した方法で構造形成され、懸架構造がフッ酸によってリリースされる。リリース段階において、フッ酸は、犠牲層16及び層26をエッチングする。

【0112】

このようにして得られた要素が、図2Cに示される。示された例において、第2の基板118は、第1の基板との接合に先立って形成された図2Cに示される、垂直な方向に沿って下方に機械的停止部22を備える。

【0113】

図3Aから3Eには、本発明に従う製造方法の他の一代替例が示され、第1の基板上に成膜された犠牲層が、接合前に構造形成され、接合前に、構造形成された犠牲層上に中間層が成膜される。

【0114】

第1の段階において、犠牲層16上のリソグラフィの段階が行われて、エッチングされるべき第1の層16の領域27が画定され、シリコン上、つまりエピタキシャル成長されたシリコン層上で停止する層16のエッチングの段階が行われる。

【0115】

このようにして得られた要素が、図3Aに示される。

【0116】

次の段階において、多結晶シリコン層の成膜が実施されて、例えば下部電極28.1及び電気的配線28.2を形成する。

【0117】

次いで、層28上でリソグラフィの段階が行われ、層28のエッチングの段階が、犠牲層16上で停止するように行われる。

【0118】

次の段階において、例えば、リリース段階においてSiO2に対して選択的であるSiNからなる停止層30の成膜が実施される。

【0119】

次いで、例えばSiO2からなる接合層32が層30上に成膜される。

【0120】

最後に、例えば、化学的機械的研磨によって、層30の平坦化の段階が行われる。

【0121】

このようにして得られた第1の基板202が、図3Bに示される。

【0122】

次の段階において、第1の基板202と第2の基板18または118との接合が行われる。このようにして得られた要素が、図3Cに示される。

【0123】

次いで、例えば「裏面研削」、次いで化学的機械的研磨によって、第1の基板の薄化の段階が任意に実施される。

【0124】

次いで、電気的コンタクト20が、図1Aから1Hの方法と類似した方法で形成される。

【0125】

このようにして得られた要素が、図3Dに示される。

【0126】

次いで、第1の基板2が、段階g)と類似した方法で構造形成され、懸架構造がフッ酸による犠牲層16のエッチングによってリリースされる。

【0127】

このようにして得られた要素が、図3Eに示される。

【0128】

犠牲層16の構造形成及び中間層の成膜のために、例えば多結晶シリコンの部分28.1によって形成された下部電極及び多結晶シリコンの部分28.2によって形成された電気的配線を形成することが可能である。

【0129】

代替的に、犠牲層の構造形成のみまたは構造形成されていない犠牲層上に中間層を成膜することを考えることが可能である。

【0130】

代替的に、1つまたは複数の多孔質シリコン部6を形成する前に、第1の基板2を加工して、例えば電極、1つまたは複数の電気的配線、1つまたは複数のキャビティなどを設けた基板を形成することを考えることが可能である。

【0131】

第2の基板と接合したのちに第1の基板を薄化することが可能であることはすでに説明した。代替的に、第1及び第2の基板は接合後に薄化されることも可能であり、または第2の基板だけが薄化されることが可能である。

【0132】

異なる深さを有するいくつかの多孔質シリコン部、より一般的には多孔質半導体材料を形成することを考えることもでき、これらの異なる深さは、逐次的な多孔質化段階によって得られる。

【0133】

さらには、本発明に従う方法は、段階a)からe)を繰り返すことにより、3つ以上の厚さを形成することも可能であり、中間犠牲層、つまり接合において界面層として用いられない層は、このときエピタキシーの前に、所定のパターンに従って加工される。

【0134】

そのような方法の例がここで説明され、その各段階が、図4Aから4Eに概略的に示される。

【0135】

第1の段階において、例えばシリコンからなる単結晶半導体の基板402の表面上に、基板の表面全体に延在する多孔質シリコン層403が形成される。多孔質層403は、例えば電気化学エッチングによる多孔質化によって得られる。このエッチングは時間によるエッチングである。多孔質に形成されるシリコンの厚さは、0.5μmから数10μmの間であり、有利には、約5μmに等しい。

【0136】

次いで、単結晶シリコン層405が、多孔質層403の全体の上にエピタキシャル成長によって形成される。この層は、例えば1μmから数10μmの間の厚さを有する。この層の厚さは、MEMS及びNEMS構造のMEMS部の厚さを画定する。

【0137】

このようにして得られた要素が、図4Aに示される。

【0138】

以下の段階において、多孔質シリコン領域406が、例えばSiN型マスクによるリソグラフィ及び多孔質化によって、図1Aから1Hに示された方法の段階a)に類似した方法で形成される。

【0139】

次いで、半導体のシリコン層410がエピタキシーによって形成され、これは少なくとも多孔質領域406上の単結晶層である。層410は、約数100nmから数10μmの間の厚さを有する。

【0140】

この層の厚さは、例えばMEMS及びNEMS構造のNEMS部の厚さを画定する。

【0141】

このようにして得られた要素が、図4Bに示される。

【0142】

次の段階において、リソグラフィを実施して多孔質領域406上に第1の懸架構造414を画定し、次いで例えばDRIE型のエッチングを実施して多孔質領域406まで開口する。このようにして得られた要素が、図4Cに示される。

【0143】

次いで、領域406の多孔質シリコンの除去が、例えばエッチングによって図1Aから1Hに関連して説明された方法と類似した方法で実施される。

【0144】

次の段階において、第1の基板の前面上に成膜416が行われて、完全にまたは部分的に第1の懸架領域114を覆い、第1の基板の前面を覆う。成膜16の材料は、シリコンに対して選択的であり、例えばSiO2からなる。次いで、層16が犠牲層を形成する。

【0145】

層16の成膜後に得られる表面の表面形状又は粗さが極めて重要な場合には、酸化物層16の平坦化の段階を行うことが可能である。この平坦化は、例えば化学的機械的研磨によって実施される。

【0146】

次の段階において、支持部が第1の基板の背面に接合されまたは成膜される。

【0147】

示された例において、支持部は、前面において第1の基板上に接合された単結晶シリコンの第2の基板118によって形成される。組み立ては、例えば当業者に周知の技術であるシリコン直接接合(SDB)によって行われる。支持部または第2の基板の成膜の場合、これはローリングによって行うことが可能である。

【0148】

このようにして得られた要素が、図4Dに示される。

【0149】

次いで、多孔質シリコン層105のエッチングが、例えばウェットエッチングによって行われ、次いで、多孔質要素105に関して第1の懸架要素と反対側に位置する基板の部分が、除去されることが可能である。第1の基板の薄化がそれによって得られる。

【0150】

次の段階は図示されていない。しかしながら、これらは図1G及び1Hに示された段階と類似している。

【0151】

この方法は、エピタキシーによるMEMSの厚さの良好な制御を提供するという利点を有する。

【0152】

本発明に従う方法の代替例は、互いに排除し合うものではなく、組み合わせることも可能である。

【0153】

図5Aから5Dには、本発明に従う方法の第2の実施形態の第1の各段階が示され、これは半導体が多孔質である領域によって形成されるのではなく複数の細い、互いに短い距離を隔てて設けられた柱によって形成された領域によって形成されるという点で、第1の実施形態とは異なる。

【0154】

柱は、例えば約0.5μmから2μmの間の幅を有し、互いに約0.3μmから1μmの間の間隔で設けられる。

【0155】

活性部が形成される単結晶シリコンの第1の基板302が用いられる。

【0156】

第1の段階において、マスクがフォトリソグラフィによって基板302の表面上に形成される。柱によって形成される領域が形成されるべき場所において、マスクは例えば図6上から示されたようなハニカムネットワークを画定する。

【0157】

このマスクは、エッチングされるべき柱の間の領域を画定する。柱の間の領域の幅dは、例えば0.3μmから1μmの間であり、柱の2つの平行な面の間の距離Dは、例えば0.5μmから2μmの間である。幅d及び距離Dは、図5A’に示される。

【0158】

次いで、基板302のエッチングの段階を、例えば時間による停止を有するDRIE型によって、典型的には0.5μmから2μmの間の深さで行う。

【0159】

次いで、図5Aに概略的に示された要素が得られ、柱によって形成されるシリコン部は、符号306として示される(詳細図)。

【0160】

次の段階において、マスクが除去される。

【0161】

次いで、基板302の表面全体の上および部分306の柱の頂部上に、単結晶シリコン層310をエピタキシャル成長する段階が行われる。このようにして形成された層は、典型的には1μmから数10μmの間の厚さを有する。エピタキシャル成長した層310は、領域306をふさぐ。

【0162】

例えば、エピタキシャル成長は、脱酸素環境において、例えば高濃度水素を有する雰囲気下で、好適にはトリクロロシランSiHCl3を用いて実施される。エピタキシャル成長される層310は、柱の表面上に成長し、柱が配置されるキャビティをふさぐ。

【0163】

次いで、図5Bに概略的に示された要素が得られる。

【0164】

エピタキシー後、SiNの柱の場合には、その材料の融点に近い温度で高温アニールが実施され、その温度は約1200℃であり、これによって柱が破壊される。次いで、懸架メンブレン307が領域306上に形成される。化学的機械的研磨による平坦化がなされて、表面の状態を改善し、このメンブレンの厚さを薄くすることが可能である。

【0165】

このようにして得られた要素が、図5Cに示される。

【0166】

次の段階において、第1の懸架領域314が画定される。このために、リソグラフィが行われて層310の表面上にマスクを形成し、次いで部分312をエッチングし、キャビティ内で停止させる。

【0167】

エッチングは例えば深掘り反応性イオンエッチング(DRIE)である。

【0168】

第1の懸架領域は、いわゆるM及びNEMS構造の場合にはMEMS部を形成する(図5D)。

【0169】

代替的には、図6Aから6Eに示されるように、これらの柱の熱酸化を行うことによる柱の部分的な抑制が考えられる。図6A’は、図6Aの要素の上面図を示している。

【0170】

図6A及び6Bに示された段階は、図5A及び5Bに示されたものと類似しており、説明しない。

【0171】

エピタキシー成長の後、リソグラフィ及び例えばDRIEによる柱上にエピタキシャル成長された層510のエッチングが実施され、第1の懸架構造、例えばMEMS及びNEMS技術におけるNEMS部を画定し、柱をふさぐキャビティ内まで開口させる。このようにして形成された要素が、図6Cに示される。

【0172】

次の段階において、高温アニール段階が実施され、これは、完全に柱を酸化させるのに十分である。酸化物層513もまた、要素の表面全体の上に形成される。

【0173】

この段階において、NEMS部もまた酸化され、酸化物除去段階においてその断面を減少させることになることは注意されるべきである。この断面の減少は、NEMSエッチングマスクの大きさ及びエピタキシャル成長された層の厚さの適切な選択によって未然に防ぐことが可能である。このようにして形成された要素が、図6Dに示される。

【0174】

次の段階において、酸化物は例えばフッ酸によるウェットエッチングまたは蒸気エッチングによって除去される。次いで柱が抑制される。このようにして形成された要素が、図6Eに示される。

【0175】

次の段階は、第1の実施形態において説明されたものと類似しており、ここでは説明しない。

【0176】

この代替例は、柱が十分細く、例えば0.6μmの幅を有し、0.3μmの間隔で位置しているような場合には、特に興味深い。

【0177】

第1の実施形態に従う方法に関連して上述した代替例は、第2の実施形態の方法に対しても全面的に適用可能である。

【0178】

本発明に従う方法によれば、SOI基板の使用に頼らず、もはや厚いエピタキシーを行わないことが可能である。そのため、コスト及び時間を得ることができる。単結晶と多結晶領域との間の厚さの違いを補うために重要なエピタキシー後の化学的機械的研磨の段階を実施する必要がもはやなくなるため、本方法の時間もまた減少する。

【0179】

1つまたは複数の下部電極、MEMS層に接続されたグランド面、1つまたは複数の接合防止停止部などを形成することについて前述したとおり、犠牲層を機能化することも可能である。

【0180】

本発明に従う方法によれば、多孔質半導体の形成及び半導体のエピタキシャル成長のいくつかの段階を交互に行い、場合によりリソグラフィ及びエッチングの中間段階と組み合わせることにより、異なる厚さを有するいくつかの層を形成することもまた可能である。

【0181】

3次元でCMOSと互いに統合することも実施可能である。この場合、第2の基板は、CMOS基板と置き換えられる。

【0182】

コンタクトの回復は、ビアまたはTSV(貫通シリコンビア)によって、又は接合においてこの場合例えばAlGe型の共晶によって行うことが可能であり、これらは当業者によく知られた技術である。

【0183】

本発明に従う方法は、微小電気機械センサ及びアクチュエータ及び/またはナノ電気機械システムの形成に特に適合している。

【符号の説明】

【0184】

2、202、302、402 第1の基板

4 マスク

6、406 多孔質部

6.1、6.2 穴

8 多孔質シリコン

10 SiGe層

12 シリコン部

14、314、414 第1の懸架領域

16 犠牲層

17 第2の懸架領域

18、118 第2の基板

20 コンタクト

122 機械的停止部

124 SiO2層

26 層

27 領域

28 多結晶シリコン層

28.1 下部電極

28.2 電気的配線

30 停止層

32 接合層

105 多孔質シリコン層

306 柱によって形成されるシリコン部

307 懸架メンブレン

310 単結晶シリコン層

312 部分

403 多孔質シリコン層

405 単結晶シリコン層

410 シリコン層

416 成膜

510 エピタキシャル成長された層

513 酸化物層

【技術分野】

【0001】

本発明は、例えばセンサまたはアクチュエータを形成するための微小電気機械システム(MEMS)及び/またはナノ電気機械システム(NEMS)の形成に用いることができる少なくとも1つの複数の厚さを有する活性部を備える構造を形成する方法に関する。

【背景技術】

【0002】

MEMS及びNEMSセンサは、固定部及び固定部に対して懸架された少なくとも1つの部分を備え、「活性部」と呼ばれる1つまたは複数の懸架された部分は、機械的、電気的、磁気的動作のような外部の動作の効果の下、変位及び/または変形することが可能である。

【0003】

固定部に対する可動部の変位及び/または変形は、例えば、加速度計の場合には加速度、ジャイロメータの場合にはコリオリ力を判別可能にする。可動部の変位は、例えばひずみゲージによって測定される。

【0004】

非特許文献1には、平面内加速度計を形成するMEMS及びNEMS構造が記載されている。この構造は、2つの異なる活性部の厚さで形成された活性部を備える。ひずみゲージを形成するNEMS部はこれらの活性部の厚さのうち1つを備え、振動錘を形成するMEMS部は、2つの活性部の厚さを備える。

【0005】

そのような活性部を形成する方法は、コスト費の高いSOI(Silicon on Insulator)型基板から形成される。さらには、厚いエピタキシャル成長段階が実施され、そのような段階は一般的に長く高価である。ひずみゲージは、SOI基板から形成され、振動錘はSOI基板及び厚いエピタキシャル形成された層から形成される。

【0006】

一方、活性部を画定する段階は、酸化物層を用い、その上にエピタキシャル成長を部分的に行う。

【0007】

しかしながら、酸化物層上にエピタキシャル形成された層は、酸化物層で保護された両者の厚さの間の界面領域において単結晶層ではない。これらの「多結晶」領域は、構造内に欠陥を発生させる可能性がある。

【0008】

さらには、エピタキシャル成長の速度は、成長が単結晶シリコン上で行われる領域と、成長が、例えば両者の厚さの界面を形成する酸化物層上で行われる領域との間で異なる。この成長速度の違いによって、最終的な構造において厚さの不均一性が大きくなる可能性がある。

【0009】

単結晶層内の多結晶領域の存在及び厚さの不均一性の存在によるこの構造の不均一性の問題は、3つ以上の異なる層または2つの高領域層間にある界面領域を利用することが望ましい場合に、全て、さらに問題となる。

【先行技術文献】

【非特許文献】

【0010】

【非特許文献1】Ph.Robert,V.Nguyen,S.Hentz,L.Duraffourg,G.Jourdan,J.Arcamone,S.Harrison,M&NEMS:A new approach for ultra−low cost 3D inertial sensor,IEEE SENSORS 2009 Conference 25−28 October 2009 Christchurch New Zealand, (2009)

【発明の概要】

【発明が解決しようとする課題】

【0011】

従って、本発明の目的は、少なくとも1つが単結晶半導体材料らなる数層によって形成される活性部を備える構造を形成する、SOI基板を用いる方法よりも低コストであり、より速い方法を提供することである。

【課題を解決するための手段】

【0012】

本発明の目的は、複数層の活性部を有する構造を形成する方法によって達成され、その方法は、基板上に単結晶半導体材料をエピタキシャル成長させる段階を備え、エピタキシーが行われる少なくともその表面が、単結晶半導体材料からなり、基板が、半導体材料が不連続である少なくとも1つの領域を備える。

【0013】

本出願において、「半導体材料が不連続である領域」は、多孔質材料または半導体材料からなり互いに短い間隔で配される複数の細い柱のいずれかによって形成される領域を意味する。

【0014】

エピタキシーの段階は、SOI基板から形成されるのと類似した第1の活性層を形成するために用いられる。この第1の層は、一般的に薄い厚さである。第2の活性層は、一般的に第1の活性層よりも厚く、次いで、有利には第2の基板を接合した後に第1の基板の「バルク」部の全てまたは一部によって形成される。一方SOI基板を用いる従来の方法では、この第2の活性層は、エピタキシャル形成される。そのため、厚いエピタキシーに関する欠点が回避される。

【0015】

本発明によれば、エピタキシャル成長した層は、単結晶層であり、成長層によるエピタキシャルに対して選択的に離隔させることができる多孔質層上に成長させるため、結果的に多孔質層は犠牲層として働く。

【0016】

さらには、不連続な半導体材料上へのエピタキシー成長のために、界面における多結晶領域の発生が起こらず、成長速度は不連続な半導体材料と基板の単結晶半導体材料との間でほぼ均一である。

【0017】

本発明に従う製造方法は、SOI基板を用いる必要がなく、厚いエピタキシーを実施しないため、このことにより製造コスト及び時間を得ることができる。それに加えて、厚さの不均一性が減少されるために、厚さの違いを補うために重要な化学的機械的研磨の段階を有する必要がない。

【0018】

非常に有利なことに、多孔質領域の実施形態において、この実施形態は表面上に非常に小さい穴を備えるため、このことが、この多孔質領域上にエピタキシャル成長するシリコンの品質を向上させ、深い部分がより大きい穴では、選択性エッチングまたはより高速な酸化を行うことができる。

【0019】

従って、本発明の対象は、単結晶半導体材料からなる、前面と呼ばれる第1の平面及び第1の平面と対向する背面と呼ばれる第2の平面を備える第1の基板から少なくとも2つの層を備える活性部を備える構造を製造する方法を提供することであり、この方法は、次の段階を備える。

【0020】

a)単結晶半導体材料からなる前面から、第1の基板内に不連続な半導体材料の少なくとも1つの領域を形成する段階。

【0021】

b)第1の基板の前面上の半導体材料から、層のエピタキシャル成長成膜を行う段階であって、層が不連続な半導体材料の領域の表面上の少なくとも単結晶層である、段階。

【0022】

c)エピタキシャル成長した単結晶層を、少なくとも不連続な半導体材料の領域において加工し、第1の懸架領域を形成する段階。

【0023】

d)不連続な半導体材料を除去または酸化する段階。

【0024】

e)前面の半導体材料及びエピタキシャル成長した半導体層の材料に対して選択的にエッチングすることができる犠牲層を形成する段階。

【0025】

f)犠牲層からいくつかの領域をクリアにするまで第1の基板の背面を加工し、第2の懸架領域を形成し、第1の懸架領域に到達できるようにする段階。

【0026】

g)犠牲層の少なくとも一部を除去することにより第1及び第2の懸架領域をリリースする段階。

【0027】

段階e)において、犠牲層の形成は、少なくとも前面上で行い、その結果、第1の懸架領域を完全にまたは部分的に覆う。

【0028】

エピタキシャル成長の段階は、第1の基板の前面の半導体材料と同じ材料または面の材料に近い格子定数を好適には有する他の半導体材料から形成することができる。

【0029】

犠牲層の形成は、例えば酸化物の成膜によって及び/または熱酸化によって行われる。

【0030】

この方法は、有利には、段階e)の後であって段階f)の前に、第1の基板の前面上に第2の基板を接合または成膜する段階e’)を備えることができる。

【0031】

第1の実施形態において、段階a)の間に、多孔質半導体材料の領域が形成される。多孔質半導体材料の領域は、電気化学エッチングによって達成される。

【0032】

有利な例において、多孔質半導体材料の領域は、表面においてより小さく、深い部分でより大きい穴を備える。

【0033】

段階d)において、多孔質半導体材料の除去は、エッチング、例えばウェットエッチングまたは、多孔質半導体材料の熱酸化及び酸化された多孔質半導体材料のエッチング、例えば、ウェットエッチング及び/または蒸気エッチングによるエッチングによって行うことができる。

【0034】

他の一実施形態において、段階a)の間、半導体材料の領域は、複数の小さな断面積の柱を備え、互いに短い間隔で配されるように形成される。段階a)は、次の段階を備えることができる。

【0035】

柱を画定するマスクを形成する段階。

【0036】

柱の間の領域をエッチングする段階。

【0037】

マスクを除去する段階。

【0038】

この実施形態において、段階d)の間に、柱を形成する半導体材料を除去する段階は、材料の融点に近い温度でアニールすることにより行われる。

【0039】

選択的に、この方法は、段階e’)に先立って、第2の基板を構造形成する段階を備える。例えば、構造形成の段階において、第2の基板の表面がエッチングされて第2の懸架部のための機械的停止部を形成し、第2の基板の接合段階における接合層を形成するために層の構造形成された表面に成膜が行われる。

【0040】

追加的な特徴に従えば、この方法は、段階e)に引き続いて、犠牲層を構造形成する段階及び/または犠牲層上に1つまたは複数の中間層を成膜する段階を備えることができ、中間層は構造形成されることができる。犠牲層及び1つまたは複数の中間層の構造形成は、例えば、リソグラフィ及びそれぞれ基板上で停止する犠牲層のエッチング及び犠牲層上で停止する1つまたは複数の中間層のエッチングによって行うことができる。

【0041】

この方法は、構造形成された犠牲層及び/または1つまたは複数の中間層上にSiO2層を成膜し、平坦化する段階を備えることができ、SiO2層は接合において用いられる。

【0042】

第1及び第2の基板の接合は、直接接合または共晶接合によって行われる。

【0043】

一例に従えば、第1の基板は、段階a)の前に構造形成される。

【0044】

段階e’)の後に、第1の基板及び/または第2の基板は、背面の裏面研削及びそれに次いで化学的機械的研磨によって薄化されることができる。

【0045】

この方法は、段階a)に先立って、基板の前面上に多孔質半導体層を形成し、多孔質半導体層上に単結晶半導体層をエピタキシャル成長させる段階を備えることができ、単結晶半導体層は、不連続多孔質領域が形成される前面を形成する。接合に引き続いて、多孔質半導体層は、例えばエッチングされて第1の基板を薄化する。

【0046】

第1の実施形態において、多孔質半導体材料のいくつかの領域を形成することができ、これは異なる深さを有する。

【0047】

第2の懸架領域を形成するための加工及び第1の懸架領域を利用可能にするための加工を行う段階f)は、領域において第1の基板を同時に加工することによって、またはこれらの領域のそれぞれにおいて逐次的に加工することによって行うことができる。

【0048】

3つ以上の層を有する活性部を形成するために、段階a)からe)が繰り返される。

【0049】

第1の基板の前面の半導体材料、第2の基板及びエピタキシーによって形成された層は、好適にはシリコンからなる。

【0050】

この方法は、有利には、センサ及び/またはアクチュエータを形成するための微小電気機械構造及び/またはナノ電気機械構造を形成することができる。

【0051】

本発明は、以下の説明および添付された図面を用いてより理解されるであろう。

【図面の簡単な説明】

【0052】

【図1A】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1B】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1C】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1D】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1E】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1F】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1G】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図1H】第1の実施形態に従う活性部を有する構造を形成するための方法の各段階を示す概略図である。

【図2A】第1の実施形態の代替的な形成方法のそれぞれの段階を示す概略図である。

【図2B】第1の実施形態の代替的な形成方法のそれぞれの段階を示す概略図である。

【図2C】第1の実施形態の代替的な形成方法のそれぞれの段階を示す概略図である。

【図3A】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図3B】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図3C】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図3D】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図3E】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図4A】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図4B】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図4C】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図4D】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図4E】第1の実施形態の代替的な製造方法のそれぞれの段階を示す概略図である。

【図5A】第2の実施形態に従う製造方法の第1の各段階を示す概略図である。

【図5B】第2の実施形態に従う製造方法の第1の各段階を示す概略図である。

【図5C】第2の実施形態に従う製造方法の第1の各段階を示す概略図である。

【図5D】第2の実施形態に従う製造方法の第1の各段階を示す概略図である。

【図6A】第2の実施形態に従う代替的な製造方法の第1の各段階を示す概略図である。

【図6B】第2の実施形態に従う代替的な製造方法の第1の各段階を示す概略図である。

【図6C】第2の実施形態に従う代替的な製造方法の第1の各段階を示す概略図である。

【図6D】第2の実施形態に従う代替的な製造方法の第1の各段階を示す概略図である。

【図6E】第2の実施形態に従う代替的な製造方法の第1の各段階を示す概略図である。

【発明を実施するための形態】

【0053】

図1Aから1Hには、少なくとも1つが単結晶半導体材料からなるいくつかの層によって形成された活性部を備える構造を形成するための本発明に従う方法の第1の実施形態の各段階が示されている。

【0054】

本出願において、MEMS及び/またはNEMS構造の「活性部」は、外部の(機械的、電気的、磁気的など)の動作の影響のもとに変位及び/または変形するような懸架部を意味する。

【0055】

以下の説明において、簡単化のために、半導体材料としてシリコンの例が用いられる。他のどのような半導体材料の利用も、本発明の範囲から逸脱するものではないことに注意すべきである。

【0056】

第1の実施形態に従う方法は、バルク型シリコン基板から、以下の主要な段階を備える。

【0057】

a)この基板の全てまたは一部に1つまたは複数の多孔質シリコン領域を形成する段階。

【0058】

b)基板の表面全体上及び多孔質シリコンの表面上にシリコンまたは単結晶SiGeエピタキシーを行う段階。

【0059】

c)エピタキシャル成長されたシリコンまたはSiGe層を加工して、単結晶シリコンの第1の厚さに、第1の懸架領域の形状を画定し、多孔質シリコンの一部を局所的に開口する段階。

【0060】

d)完全にまたは部分的に多孔質シリコンを除去もしくは多孔質シリコンを熱酸化する段階。

【0061】

e)シリコンに対して選択的な犠牲層を成膜及び/または熱酸化する段階。

【0062】

f)犠牲層及び/または多孔質シリコン領域の全てまたは一部からいくつかの領域をクリアにするまで第1の基板を加工し、第2の懸架領域を形成し、第1の懸架領域の全てまたは一部をクリアにする段階。

【0063】

g)犠牲層を除去することによって懸架領域をリリースする段階。

【0064】

有利には、段階e)とf)との間に、第1の基板の背面上に支持部を移設または成膜し構造化する段階e’)が設けられる。

【0065】

この方法の段階a)からg)をこれから詳細に説明する。

【0066】

本発明に従う方法は、有利には単結晶シリコンの第1の基板2を用いる。

【0067】

第1の段階a)において、マスク4が、約100nmの厚さの層を成膜することによって基板2の表面上に形成される。この層4は、例えば窒化シリコンからなる。

【0068】

次いで、リソグラフィの段階を層4に行ってエッチングされるべき層2の領域を画定し、層4のエッチングの段階を行って、基板2の領域6を露出させる。

【0069】

次の段階において、領域6は所定の厚さで、例えば電気化学エッチングを用いる多孔質化によって、多孔質化される。このエッチングは、時間によるエッチングである。多孔質を形成されるシリコンの厚さは0.1μmから10μmの間であり、有利には、約1μmに等しい。

【0070】

図1Aに概略的に示された要素が得られ、多孔質シリコンの部分は符号8によって示される。

【0071】

1つまたは複数の多孔質部を形成することは、本発明の範囲内であり、形成される構造による。

【0072】

特に有利には、多孔質部6は、表面で非常に小さい大きさを有する穴6.1及び深い部分でより大きい穴6.2を備え、穴6.1により、この多孔質部の上にエピタキシャル成長されるシリコンの質が向上し、穴6.2により多孔質シリコンの選択的エッチングまたはより高速な酸化が可能となる。異なる穴の大きさを有するこの多孔質部は、多孔質化の段階において電気化学エッチングの条件を変化させることにより、例えば電流密度を変化させることにより、得ることができる。例えば、望まれる穴の大きさは2から50nmの間であり、このとき得られる材料はメソポーラス型からなる。

【0073】

次の段階において、マスク4が、例えば窒化シリコンの化学的エッチングによって除去される。

【0074】

次いで、シリコンまたはSiGe層10のエピタキシャル成長の段階b)が行われ、この層は、多孔質部6上の単結晶層であり、基板表面の残り全体の上では単結晶層または多結晶であってもよい。シリコンまたは多結晶SiGeは、例えばエピタキシー前の基板の表面に酸化物層または窒化物層を成膜することによって得られる。層10の厚さは数10nmから数10μmの間であり、有利には約0.25μmに等しい。

【0075】

層10は、第1の基板と同一の半導体材料または第1の基板の材料と近い格子定数を好適には有する他の半導体材料からなるものであってもよい。例えば、上述のように、第1のSi基板の場合には、SiまたはSiGeエピタキシーが例えば実施される。

【0076】

明瞭化のために、それぞれの段階の概略図において、層10及び基板2は点線によって分離されている。

【0077】

このようにして得られた要素が、図1Bに示されている。多孔質領域6の上に形成されたシリコン部12は、第1の懸架領域14を形成するためにエッチングされる。

【0078】

次の段階c)において、第1の懸架領域14が画定する。このために、リソグラフィを行って層10の表面上にマスクを形成し、次いで多孔質シリコン6の部分の上または中で停止する部分12のエッチングが実施される。

【0079】

エッチングは例えば深掘り反応性イオンエッチング(DRIE)である。

【0080】

第1の懸架領域14は、いわゆるM及びNEMS構造の場合にはNEMS部を形成する。

【0081】

このようにして得られた要素が、図1Cに示されている。

【0082】

次の段階d)において、多孔質部6の除去が行われ、そうでない場合には多孔質部6が単に酸化される。

【0083】

この除去は、多孔質シリコンのウェットエッチングによって実施することができる。このエッチングは、「非多孔質」シリコンよりも速く多孔質シリコンをエッチングするという特性を有し、そのためエッチング時間を制御することによって、懸架領域14は全くまたはほとんどエッチングされないのに対して、多孔質シリコンは除去される。エッチングの継続時間は、用いられるエッチング溶液の濃度及び温度の関数として、数秒から数分の間とすることが可能であり、このエッチング溶液は、KOH、TMAH(テトラメチルアンモニウムヒドロキサイド)などとすることが可能である。典型的には、エッチングは、KOH溶液で室温においては数分間続ける。

【0084】

代替的に、多孔質シリコンの除去は、まず熱酸化を行い、次いで蒸気及び/またはウェットフッ酸エッチングによって、形成された酸化物をエッチングすることによって、2つの段階で達成される。多孔質シリコンは、「非多孔質」シリコンよりもずっと高速で酸化され、そのため酸化段階の継続時間を制御することにより、ほとんど多孔質シリコンだけを酸化することが可能である。例えば、数10nmの厚さのシリコンを酸化することを試みる。酸化の条件は当業者に周知であり、詳細に説明しない。この代替例に従えば、このエッチングは以下で説明される犠牲層のエッチングの間に行うことが可能である。そのため、この方法の時間は、有利に減少させることができる。

【0085】

このようにして得られた要素が、図1Dに示される。

【0086】

次の段階e)において、成膜16が第1の基板の前面において行われ、完全にまたは部分的に第1の懸架領域14を覆い、第1の基板の前面を覆う。成膜16の材料はシリコンに対して選択的であり、例えばSiO2からなる。次いで層16は犠牲層を形成する。この層16はまた、多孔質Siのエッチングのキャビティを(完全にまたは部分的に)ふさぐことができる。有利には、この層16を成膜する前に例えば数10nmの深さのシリコンのわずかな熱酸化を行うことができる。懸架領域14の周囲及びキャビティ内の熱酸化は、停止層を形成し、段階f)の加工における保護の確実性を向上させることができる。多孔質シリコンが単に酸化されている場合には、被覆は部分的または第1の懸架領域14のみを覆う。

【0087】

層16を成膜した後に得られる表面の表面形状又は粗さが極めて高い場合には、酸化物層16の平坦化の段階を行うことができる。この平坦化は例えば、化学的機械的研磨によって行われる。

【0088】

このようにして得られた要素が、図1Eに示される。

【0089】

有利には、このとき支持部が第1の基板の背面上に接合または成膜される(段階e’)。示された例においては、支持部は、前面において第1の基板に接合された単結晶シリコンの第2の基板18によって形成される。次いで犠牲層16が第1の基板2と第2の基板18との間に設けられる。

【0090】

この組み立ては、例えば当業者に周知の技術であるシリコン直接接合(silicon direct bonding,SDB)によって行われる。支持部または第2の基板の成膜の場合、これはローリングによって実施することが可能である。

【0091】

支持部は、第1の基板と異なる材料からなるものとしてもよく、例えばパイレックス(登録商標)のガラス支持部の使用であっても考えることが可能である。

【0092】

このようにして得られた要素が、図1Fに示される。

【0093】

第1の基板の薄化は、例えば「裏面研削」及び化学的機械的研磨によって実施することが可能である。

【0094】

この薄化は、いわゆるMEMS及びNEMS構造の場合において、MEMS部の厚さを画定することが可能である。

【0095】

次の段階において、電気的コンタクト20を、第1の基板2の背面において形成するために、金属層の成膜が実施され、この背面は第1及び第2の基板の接合によって得られる要素の前面を形成する。

【0096】

コンタクト20を形成するために、リソグラフィ段階、次いでエッチング段階が実施される。

【0097】

段階f)において、リソグラフィ及び例えば第1の基板2の深掘り反応性イオンエッチング(DRIE)型のエッチングを行い、第1の懸架領域14をクリアにし、第2の懸架領域17、例えばいわゆるMEMS及びNEMS構造の場合におけるMEMS部を形成する。エッチングは、犠牲層16及びこれまでに除去されていない場合には多孔質シリコンに到達する。第1の基板の構造形成の段階は、MEMS及びNEMS技術において知られた段階である。

【0098】

このようにして得られた要素が、図1Gに示される。

【0099】

最後に、段階g)において、懸架領域14及び17は、例えば犠牲層16及びもしあれば酸化された多孔質シリコンの、フッ酸を用いたウェットエッチングまたは蒸気相エッチングによってリリースされる。これは、時間によるエッチングである(図1H)。

【0100】

図2Aから2Cには、図1Aから1Hの製造方法の代替的な実施形態が示され、第2の基板118が、第1の基板に接合される前に構造形成される。

【0101】

このような事前の構造形成は、例えば電気的配線や1つまたは複数のキャビティを形成する1つまたは複数の活性部を励起する電極が設けられた基板を形成するために、CMOS回路を製造するために実施することが可能である。

【0102】

第2の基板118の構造形成は、以下のようにして行うことが可能である。

【0103】

第1の段階において、フォトリソグラフィの段階が、エッチングされるべき基板の表面の領域を画定するために実施され、例えば0.5μmの深さだけ基板の表面をエッチングする。このエッチングは、時間で停止するエッチングである。このようにして機械的停止部122が形成される。

【0104】

次いで、SiO2層124が構造形成された表面に成膜され、この層は接合層を形成する。

【0105】

最後に、層26の平坦化の段階が実施される。

【0106】

このようにして得られた要素が、図2Aに示される。

【0107】

次いで、第2の構造形成された基板118と第1の基板2との接合が行われる。層24は、例えば前述したように直接接合を通じて犠牲層16と接触した状態にされる。

【0108】

次いで、例えば「裏面研削」によって第1の基板の薄化の段階が実施され、このことによりMEMS及びNEMSシステムの場合において例えばMEMS部の厚さを画定することができる。

【0109】

このようにして得られた要素が、図2Bに示される。

【0110】

次いで、電気的コンタクトが、図1Aから1Hの方法と類似した方法で形成される。

【0111】

次いで、第1の基板2が、段階f)と類似した方法で構造形成され、懸架構造がフッ酸によってリリースされる。リリース段階において、フッ酸は、犠牲層16及び層26をエッチングする。

【0112】

このようにして得られた要素が、図2Cに示される。示された例において、第2の基板118は、第1の基板との接合に先立って形成された図2Cに示される、垂直な方向に沿って下方に機械的停止部22を備える。

【0113】

図3Aから3Eには、本発明に従う製造方法の他の一代替例が示され、第1の基板上に成膜された犠牲層が、接合前に構造形成され、接合前に、構造形成された犠牲層上に中間層が成膜される。

【0114】

第1の段階において、犠牲層16上のリソグラフィの段階が行われて、エッチングされるべき第1の層16の領域27が画定され、シリコン上、つまりエピタキシャル成長されたシリコン層上で停止する層16のエッチングの段階が行われる。

【0115】

このようにして得られた要素が、図3Aに示される。

【0116】

次の段階において、多結晶シリコン層の成膜が実施されて、例えば下部電極28.1及び電気的配線28.2を形成する。

【0117】

次いで、層28上でリソグラフィの段階が行われ、層28のエッチングの段階が、犠牲層16上で停止するように行われる。

【0118】

次の段階において、例えば、リリース段階においてSiO2に対して選択的であるSiNからなる停止層30の成膜が実施される。

【0119】

次いで、例えばSiO2からなる接合層32が層30上に成膜される。

【0120】

最後に、例えば、化学的機械的研磨によって、層30の平坦化の段階が行われる。

【0121】

このようにして得られた第1の基板202が、図3Bに示される。

【0122】

次の段階において、第1の基板202と第2の基板18または118との接合が行われる。このようにして得られた要素が、図3Cに示される。

【0123】

次いで、例えば「裏面研削」、次いで化学的機械的研磨によって、第1の基板の薄化の段階が任意に実施される。

【0124】

次いで、電気的コンタクト20が、図1Aから1Hの方法と類似した方法で形成される。

【0125】

このようにして得られた要素が、図3Dに示される。

【0126】

次いで、第1の基板2が、段階g)と類似した方法で構造形成され、懸架構造がフッ酸による犠牲層16のエッチングによってリリースされる。

【0127】

このようにして得られた要素が、図3Eに示される。

【0128】

犠牲層16の構造形成及び中間層の成膜のために、例えば多結晶シリコンの部分28.1によって形成された下部電極及び多結晶シリコンの部分28.2によって形成された電気的配線を形成することが可能である。

【0129】

代替的に、犠牲層の構造形成のみまたは構造形成されていない犠牲層上に中間層を成膜することを考えることが可能である。

【0130】

代替的に、1つまたは複数の多孔質シリコン部6を形成する前に、第1の基板2を加工して、例えば電極、1つまたは複数の電気的配線、1つまたは複数のキャビティなどを設けた基板を形成することを考えることが可能である。

【0131】

第2の基板と接合したのちに第1の基板を薄化することが可能であることはすでに説明した。代替的に、第1及び第2の基板は接合後に薄化されることも可能であり、または第2の基板だけが薄化されることが可能である。

【0132】

異なる深さを有するいくつかの多孔質シリコン部、より一般的には多孔質半導体材料を形成することを考えることもでき、これらの異なる深さは、逐次的な多孔質化段階によって得られる。

【0133】

さらには、本発明に従う方法は、段階a)からe)を繰り返すことにより、3つ以上の厚さを形成することも可能であり、中間犠牲層、つまり接合において界面層として用いられない層は、このときエピタキシーの前に、所定のパターンに従って加工される。

【0134】

そのような方法の例がここで説明され、その各段階が、図4Aから4Eに概略的に示される。

【0135】

第1の段階において、例えばシリコンからなる単結晶半導体の基板402の表面上に、基板の表面全体に延在する多孔質シリコン層403が形成される。多孔質層403は、例えば電気化学エッチングによる多孔質化によって得られる。このエッチングは時間によるエッチングである。多孔質に形成されるシリコンの厚さは、0.5μmから数10μmの間であり、有利には、約5μmに等しい。

【0136】

次いで、単結晶シリコン層405が、多孔質層403の全体の上にエピタキシャル成長によって形成される。この層は、例えば1μmから数10μmの間の厚さを有する。この層の厚さは、MEMS及びNEMS構造のMEMS部の厚さを画定する。

【0137】

このようにして得られた要素が、図4Aに示される。

【0138】

以下の段階において、多孔質シリコン領域406が、例えばSiN型マスクによるリソグラフィ及び多孔質化によって、図1Aから1Hに示された方法の段階a)に類似した方法で形成される。

【0139】

次いで、半導体のシリコン層410がエピタキシーによって形成され、これは少なくとも多孔質領域406上の単結晶層である。層410は、約数100nmから数10μmの間の厚さを有する。

【0140】

この層の厚さは、例えばMEMS及びNEMS構造のNEMS部の厚さを画定する。

【0141】

このようにして得られた要素が、図4Bに示される。

【0142】

次の段階において、リソグラフィを実施して多孔質領域406上に第1の懸架構造414を画定し、次いで例えばDRIE型のエッチングを実施して多孔質領域406まで開口する。このようにして得られた要素が、図4Cに示される。

【0143】

次いで、領域406の多孔質シリコンの除去が、例えばエッチングによって図1Aから1Hに関連して説明された方法と類似した方法で実施される。

【0144】

次の段階において、第1の基板の前面上に成膜416が行われて、完全にまたは部分的に第1の懸架領域114を覆い、第1の基板の前面を覆う。成膜16の材料は、シリコンに対して選択的であり、例えばSiO2からなる。次いで、層16が犠牲層を形成する。

【0145】

層16の成膜後に得られる表面の表面形状又は粗さが極めて重要な場合には、酸化物層16の平坦化の段階を行うことが可能である。この平坦化は、例えば化学的機械的研磨によって実施される。

【0146】

次の段階において、支持部が第1の基板の背面に接合されまたは成膜される。

【0147】

示された例において、支持部は、前面において第1の基板上に接合された単結晶シリコンの第2の基板118によって形成される。組み立ては、例えば当業者に周知の技術であるシリコン直接接合(SDB)によって行われる。支持部または第2の基板の成膜の場合、これはローリングによって行うことが可能である。

【0148】

このようにして得られた要素が、図4Dに示される。

【0149】

次いで、多孔質シリコン層105のエッチングが、例えばウェットエッチングによって行われ、次いで、多孔質要素105に関して第1の懸架要素と反対側に位置する基板の部分が、除去されることが可能である。第1の基板の薄化がそれによって得られる。

【0150】

次の段階は図示されていない。しかしながら、これらは図1G及び1Hに示された段階と類似している。

【0151】

この方法は、エピタキシーによるMEMSの厚さの良好な制御を提供するという利点を有する。

【0152】

本発明に従う方法の代替例は、互いに排除し合うものではなく、組み合わせることも可能である。

【0153】

図5Aから5Dには、本発明に従う方法の第2の実施形態の第1の各段階が示され、これは半導体が多孔質である領域によって形成されるのではなく複数の細い、互いに短い距離を隔てて設けられた柱によって形成された領域によって形成されるという点で、第1の実施形態とは異なる。

【0154】

柱は、例えば約0.5μmから2μmの間の幅を有し、互いに約0.3μmから1μmの間の間隔で設けられる。

【0155】

活性部が形成される単結晶シリコンの第1の基板302が用いられる。

【0156】

第1の段階において、マスクがフォトリソグラフィによって基板302の表面上に形成される。柱によって形成される領域が形成されるべき場所において、マスクは例えば図6上から示されたようなハニカムネットワークを画定する。

【0157】

このマスクは、エッチングされるべき柱の間の領域を画定する。柱の間の領域の幅dは、例えば0.3μmから1μmの間であり、柱の2つの平行な面の間の距離Dは、例えば0.5μmから2μmの間である。幅d及び距離Dは、図5A’に示される。

【0158】

次いで、基板302のエッチングの段階を、例えば時間による停止を有するDRIE型によって、典型的には0.5μmから2μmの間の深さで行う。

【0159】

次いで、図5Aに概略的に示された要素が得られ、柱によって形成されるシリコン部は、符号306として示される(詳細図)。

【0160】

次の段階において、マスクが除去される。

【0161】

次いで、基板302の表面全体の上および部分306の柱の頂部上に、単結晶シリコン層310をエピタキシャル成長する段階が行われる。このようにして形成された層は、典型的には1μmから数10μmの間の厚さを有する。エピタキシャル成長した層310は、領域306をふさぐ。

【0162】

例えば、エピタキシャル成長は、脱酸素環境において、例えば高濃度水素を有する雰囲気下で、好適にはトリクロロシランSiHCl3を用いて実施される。エピタキシャル成長される層310は、柱の表面上に成長し、柱が配置されるキャビティをふさぐ。

【0163】

次いで、図5Bに概略的に示された要素が得られる。

【0164】

エピタキシー後、SiNの柱の場合には、その材料の融点に近い温度で高温アニールが実施され、その温度は約1200℃であり、これによって柱が破壊される。次いで、懸架メンブレン307が領域306上に形成される。化学的機械的研磨による平坦化がなされて、表面の状態を改善し、このメンブレンの厚さを薄くすることが可能である。

【0165】

このようにして得られた要素が、図5Cに示される。

【0166】

次の段階において、第1の懸架領域314が画定される。このために、リソグラフィが行われて層310の表面上にマスクを形成し、次いで部分312をエッチングし、キャビティ内で停止させる。

【0167】

エッチングは例えば深掘り反応性イオンエッチング(DRIE)である。

【0168】

第1の懸架領域は、いわゆるM及びNEMS構造の場合にはMEMS部を形成する(図5D)。

【0169】

代替的には、図6Aから6Eに示されるように、これらの柱の熱酸化を行うことによる柱の部分的な抑制が考えられる。図6A’は、図6Aの要素の上面図を示している。

【0170】

図6A及び6Bに示された段階は、図5A及び5Bに示されたものと類似しており、説明しない。

【0171】

エピタキシー成長の後、リソグラフィ及び例えばDRIEによる柱上にエピタキシャル成長された層510のエッチングが実施され、第1の懸架構造、例えばMEMS及びNEMS技術におけるNEMS部を画定し、柱をふさぐキャビティ内まで開口させる。このようにして形成された要素が、図6Cに示される。

【0172】

次の段階において、高温アニール段階が実施され、これは、完全に柱を酸化させるのに十分である。酸化物層513もまた、要素の表面全体の上に形成される。

【0173】

この段階において、NEMS部もまた酸化され、酸化物除去段階においてその断面を減少させることになることは注意されるべきである。この断面の減少は、NEMSエッチングマスクの大きさ及びエピタキシャル成長された層の厚さの適切な選択によって未然に防ぐことが可能である。このようにして形成された要素が、図6Dに示される。

【0174】

次の段階において、酸化物は例えばフッ酸によるウェットエッチングまたは蒸気エッチングによって除去される。次いで柱が抑制される。このようにして形成された要素が、図6Eに示される。

【0175】

次の段階は、第1の実施形態において説明されたものと類似しており、ここでは説明しない。

【0176】

この代替例は、柱が十分細く、例えば0.6μmの幅を有し、0.3μmの間隔で位置しているような場合には、特に興味深い。

【0177】

第1の実施形態に従う方法に関連して上述した代替例は、第2の実施形態の方法に対しても全面的に適用可能である。

【0178】

本発明に従う方法によれば、SOI基板の使用に頼らず、もはや厚いエピタキシーを行わないことが可能である。そのため、コスト及び時間を得ることができる。単結晶と多結晶領域との間の厚さの違いを補うために重要なエピタキシー後の化学的機械的研磨の段階を実施する必要がもはやなくなるため、本方法の時間もまた減少する。

【0179】

1つまたは複数の下部電極、MEMS層に接続されたグランド面、1つまたは複数の接合防止停止部などを形成することについて前述したとおり、犠牲層を機能化することも可能である。

【0180】

本発明に従う方法によれば、多孔質半導体の形成及び半導体のエピタキシャル成長のいくつかの段階を交互に行い、場合によりリソグラフィ及びエッチングの中間段階と組み合わせることにより、異なる厚さを有するいくつかの層を形成することもまた可能である。

【0181】

3次元でCMOSと互いに統合することも実施可能である。この場合、第2の基板は、CMOS基板と置き換えられる。

【0182】

コンタクトの回復は、ビアまたはTSV(貫通シリコンビア)によって、又は接合においてこの場合例えばAlGe型の共晶によって行うことが可能であり、これらは当業者によく知られた技術である。

【0183】

本発明に従う方法は、微小電気機械センサ及びアクチュエータ及び/またはナノ電気機械システムの形成に特に適合している。

【符号の説明】

【0184】

2、202、302、402 第1の基板

4 マスク

6、406 多孔質部

6.1、6.2 穴

8 多孔質シリコン

10 SiGe層

12 シリコン部

14、314、414 第1の懸架領域

16 犠牲層

17 第2の懸架領域

18、118 第2の基板

20 コンタクト

122 機械的停止部

124 SiO2層

26 層

27 領域

28 多結晶シリコン層

28.1 下部電極

28.2 電気的配線

30 停止層

32 接合層

105 多孔質シリコン層

306 柱によって形成されるシリコン部

307 懸架メンブレン

310 単結晶シリコン層

312 部分

403 多孔質シリコン層

405 単結晶シリコン層

410 シリコン層

416 成膜

510 エピタキシャル成長された層

513 酸化物層

【特許請求の範囲】

【請求項1】

前面と呼ばれる単結晶半導体材料の第1の表面及び前記第1の表面と対向する背面と呼ばれる第2の表面を備える第1の基板から、少なくとも2つの層を備える活性部を備える構造を製造する方法であって、

a)前記第1の基板において単結晶半導体材料からなる前記第1の表面から不連続な半導体材料の少なくとも1つの領域を形成する段階、

b)前記第1の基板の前記前面上へ半導体材料から層のエピタキシャル成長成膜を行う段階であって、前記層が、不連続な半導体材料の前記領域の表面上の少なくとも単結晶層である段階、

c)少なくとも不連続な半導体材料の前記領域に、第1の懸架領域を形成するためにエピタキシャル成長された単結晶層を加工する段階、

d)前記不連続な半導体材料を除去または酸化する段階、

e)前記前面の前記半導体材料及び前記エピタキシャル成長された半導体層の材料に対して選択的にエッチング可能である犠牲層を形成し、前記第1の懸架領域を完全にまたは部分的に覆う段階、

f)前記第1の基板の前記背面を、前記犠牲層からいくつかの領域をクリアにするまで加工して第2の懸架領域を画定し、前記第1の懸架領域まで到達できるようにする段階、

g)前記犠牲層の少なくとも一部を除去することによって前記第1及び第2の懸架領域をリリースする段階、

を備える方法。

【請求項2】

前記エピタキシャル成長させる段階が、前記第1の基板の前記前面の半導体材料と同一の材料または前記表面の材料と近い格子定数を好適には有する他の半導体材料から形成される、請求項1に記載の方法。

【請求項3】

前記犠牲層を形成する段階が、酸化物の成膜によって及び/または熱酸化によって実施される、請求項1または2に記載の方法。

【請求項4】

前記段階e)の後であって前記段階f)の前に、前記第1の基板の前記前面上に第2の基板を接合または成膜する段階e’)をさらに備えることを特徴とする、請求項1から3のいずれか一項に記載の方法。

【請求項5】

前記段階a)において、多孔質半導体材料の領域が形成される、請求項1から4のいずれか一項に記載の製造方法。

【請求項6】

多孔質半導体材料の前記領域が、電気化学エッチングによって達成される、請求項5に記載の製造方法。

【請求項7】

多孔質半導体材料の前記領域が、前記表面においてより小さい大きさの穴及び深い部分でより大きい大きさの穴を備える、請求項5または6に記載の製造方法。

【請求項8】

前記段階d)において、前記多孔質半導体材料の除去が、エッチング、例えばウェットエッチングによって行われる、請求項5から7のいずれか一項に記載の製造方法。

【請求項9】

前記段階d)において、前記多孔質半導体材料の除去が、前記多孔質半導体材料を熱酸化し、酸化された前記多孔質半導体材料を例えばウェットエッチング及び/または蒸気によってエッチングすることにより行われる、請求項5から7のいずれか一項に記載の製造方法。

【請求項10】

前記段階a)において、半導体材料の領域が、複数の小さな断面積の柱であって互いに短い間隔で配された柱を備えるように形成される、請求項1から4のいずれか一項に記載の製造方法。

【請求項11】

前記段階a)が、

柱を画定するマスクを形成する段階、

柱の間の領域をエッチングする段階及び

前記マスクを除去する段階を備える、請求項10に記載の製造方法。

【請求項12】

前記段階d)において、柱を形成する前記半導体材料の除去が、前記材料の融点に近い温度でアニールすることにより行われる、請求項10または11に記載の製造方法。

【請求項13】

前記段階e’)に先立って、前記第2の基板を構造形成する段階、及び前記段階e)の後であって前記段階f)の前において、前記第1の基板の前記前面上に第2の基板を接合または成膜する段階e’)を備える、請求項1から12のいずれか一項に記載の製造方法。

【請求項14】

前記構造形成する段階において、前記第2の基板の表面がエッチングされて前記第2の懸架部のための機械的停止部を形成し、層の前記構造形成された表面に、前記第2の基板の前記接合段階において接合層を形成するための成膜が行われる、請求項13に記載の製造方法。

【請求項15】

段階e)に続いて、前記犠牲層の構造形成及び/または前記犠牲層上への1つまたは複数の中間層の成膜の段階を備え、前記中間層を構造形成することができる、請求項1から14のいずれか一項に記載の製造方法。

【請求項16】

前記犠牲層及び1つまたは複数の前記中間層の前記構造形成が、リソグラフィ及びそれぞれ前記基板上で停止する前記犠牲層のエッチング及び前記犠牲層上で停止する1つまたは複数の前記中間層のエッチングによって行われる、請求項15に記載の製造方法。

【請求項17】

前記構造形成された犠牲層及び/または1つまたは複数の前記中間層上にSiO2層を成膜し、平坦化する段階を備え、前記SiO2層が、接合において用いられる、請求項15又は16に記載の製造方法。

【請求項18】

前記第1及び第2の基板の前記接合が、直接接合または共晶接合によって行われ、前記段階e)の後であって前記段階f)の前に、前記第1の基板の前記前面上に第2の基板を接合または成膜する段階e’)をさらに備える、請求項1から17のいずれか一項に記載の製造方法。

【請求項19】

前記第1の基板が、前記段階a)の前に構造形成される、請求項1から18のいずれか一項に記載の製造方法。

【請求項20】

前記段階e’)の後に、前記第1の基板及び/または前記第2の基板が、前記背面を裏面研削、次いで化学的機械的研磨することによって薄化され、前記段階e)の後であって前記段階f)の前に、前記第1の基板の前記前面上に第2の基板を接合または成膜する段階e’)をさらに備える、請求項1から19のいずれか一項に記載の製造方法。

【請求項21】

前記段階a)に先立って、前記基板の前記前面上に多孔質半導体層を形成し、前記多孔質半導体層上に単結晶半導体層をエピタキシャル成長させる段階を備え、前記単結晶半導体層が、前記不連続な多孔質領域が形成される前記前面を形成する、請求項1から19のいずれか一項に記載の製造方法。

【請求項22】

前記接合に続いて、前記多孔質半導体層がエッチングされて前記第1の基板を薄化し、前記段階e)の後であって前記段階f)の前に、前記第1の基板の前記前面上に第2の基板を接合または成膜する段階e’)をさらに備える、請求項21に記載の製造方法。

【請求項23】

多孔質半導体材料のいくつかの領域が形成され、これが異なる深さを有する、請求項5から9のいずれか一項に記載の製造方法。

【請求項24】

第2の懸架領域を形成するために加工し、前記第1の懸架領域を得るために加工する前記段階f)が、前記領域において前記第1の基板を同時に加工またはこれらの領域のそれぞれにおいて逐次的に加工することによって行われる、請求項1から23のいずれか一項に記載の製造方法。

【請求項25】

前記段階a)からe)が、3つ以上の層を有する活性部を形成するように繰り返される、請求項1から24のいずれか一項に記載の製造方法。

【請求項26】

前記第1の基板の前記前面、前記第2の基板及び前記エピタキシャル成長された層の前記半導体材料が、シリコンからなる、請求項1から25のいずれか一項に記載の製造方法。

【請求項27】

センサ及び/またはアクチュエータを形成するための微小電気機械構造及び/またはナノ電気機械構造を製造するための、請求項1から26のいずれか一項に記載の方法。

【請求項1】

前面と呼ばれる単結晶半導体材料の第1の表面及び前記第1の表面と対向する背面と呼ばれる第2の表面を備える第1の基板から、少なくとも2つの層を備える活性部を備える構造を製造する方法であって、

a)前記第1の基板において単結晶半導体材料からなる前記第1の表面から不連続な半導体材料の少なくとも1つの領域を形成する段階、

b)前記第1の基板の前記前面上へ半導体材料から層のエピタキシャル成長成膜を行う段階であって、前記層が、不連続な半導体材料の前記領域の表面上の少なくとも単結晶層である段階、

c)少なくとも不連続な半導体材料の前記領域に、第1の懸架領域を形成するためにエピタキシャル成長された単結晶層を加工する段階、

d)前記不連続な半導体材料を除去または酸化する段階、

e)前記前面の前記半導体材料及び前記エピタキシャル成長された半導体層の材料に対して選択的にエッチング可能である犠牲層を形成し、前記第1の懸架領域を完全にまたは部分的に覆う段階、

f)前記第1の基板の前記背面を、前記犠牲層からいくつかの領域をクリアにするまで加工して第2の懸架領域を画定し、前記第1の懸架領域まで到達できるようにする段階、

g)前記犠牲層の少なくとも一部を除去することによって前記第1及び第2の懸架領域をリリースする段階、

を備える方法。

【請求項2】

前記エピタキシャル成長させる段階が、前記第1の基板の前記前面の半導体材料と同一の材料または前記表面の材料と近い格子定数を好適には有する他の半導体材料から形成される、請求項1に記載の方法。

【請求項3】

前記犠牲層を形成する段階が、酸化物の成膜によって及び/または熱酸化によって実施される、請求項1または2に記載の方法。

【請求項4】

前記段階e)の後であって前記段階f)の前に、前記第1の基板の前記前面上に第2の基板を接合または成膜する段階e’)をさらに備えることを特徴とする、請求項1から3のいずれか一項に記載の方法。

【請求項5】

前記段階a)において、多孔質半導体材料の領域が形成される、請求項1から4のいずれか一項に記載の製造方法。

【請求項6】

多孔質半導体材料の前記領域が、電気化学エッチングによって達成される、請求項5に記載の製造方法。

【請求項7】

多孔質半導体材料の前記領域が、前記表面においてより小さい大きさの穴及び深い部分でより大きい大きさの穴を備える、請求項5または6に記載の製造方法。

【請求項8】

前記段階d)において、前記多孔質半導体材料の除去が、エッチング、例えばウェットエッチングによって行われる、請求項5から7のいずれか一項に記載の製造方法。

【請求項9】

前記段階d)において、前記多孔質半導体材料の除去が、前記多孔質半導体材料を熱酸化し、酸化された前記多孔質半導体材料を例えばウェットエッチング及び/または蒸気によってエッチングすることにより行われる、請求項5から7のいずれか一項に記載の製造方法。

【請求項10】

前記段階a)において、半導体材料の領域が、複数の小さな断面積の柱であって互いに短い間隔で配された柱を備えるように形成される、請求項1から4のいずれか一項に記載の製造方法。

【請求項11】

前記段階a)が、

柱を画定するマスクを形成する段階、

柱の間の領域をエッチングする段階及び

前記マスクを除去する段階を備える、請求項10に記載の製造方法。

【請求項12】

前記段階d)において、柱を形成する前記半導体材料の除去が、前記材料の融点に近い温度でアニールすることにより行われる、請求項10または11に記載の製造方法。

【請求項13】

前記段階e’)に先立って、前記第2の基板を構造形成する段階、及び前記段階e)の後であって前記段階f)の前において、前記第1の基板の前記前面上に第2の基板を接合または成膜する段階e’)を備える、請求項1から12のいずれか一項に記載の製造方法。

【請求項14】

前記構造形成する段階において、前記第2の基板の表面がエッチングされて前記第2の懸架部のための機械的停止部を形成し、層の前記構造形成された表面に、前記第2の基板の前記接合段階において接合層を形成するための成膜が行われる、請求項13に記載の製造方法。

【請求項15】

段階e)に続いて、前記犠牲層の構造形成及び/または前記犠牲層上への1つまたは複数の中間層の成膜の段階を備え、前記中間層を構造形成することができる、請求項1から14のいずれか一項に記載の製造方法。

【請求項16】

前記犠牲層及び1つまたは複数の前記中間層の前記構造形成が、リソグラフィ及びそれぞれ前記基板上で停止する前記犠牲層のエッチング及び前記犠牲層上で停止する1つまたは複数の前記中間層のエッチングによって行われる、請求項15に記載の製造方法。

【請求項17】

前記構造形成された犠牲層及び/または1つまたは複数の前記中間層上にSiO2層を成膜し、平坦化する段階を備え、前記SiO2層が、接合において用いられる、請求項15又は16に記載の製造方法。

【請求項18】

前記第1及び第2の基板の前記接合が、直接接合または共晶接合によって行われ、前記段階e)の後であって前記段階f)の前に、前記第1の基板の前記前面上に第2の基板を接合または成膜する段階e’)をさらに備える、請求項1から17のいずれか一項に記載の製造方法。

【請求項19】

前記第1の基板が、前記段階a)の前に構造形成される、請求項1から18のいずれか一項に記載の製造方法。

【請求項20】

前記段階e’)の後に、前記第1の基板及び/または前記第2の基板が、前記背面を裏面研削、次いで化学的機械的研磨することによって薄化され、前記段階e)の後であって前記段階f)の前に、前記第1の基板の前記前面上に第2の基板を接合または成膜する段階e’)をさらに備える、請求項1から19のいずれか一項に記載の製造方法。

【請求項21】

前記段階a)に先立って、前記基板の前記前面上に多孔質半導体層を形成し、前記多孔質半導体層上に単結晶半導体層をエピタキシャル成長させる段階を備え、前記単結晶半導体層が、前記不連続な多孔質領域が形成される前記前面を形成する、請求項1から19のいずれか一項に記載の製造方法。

【請求項22】

前記接合に続いて、前記多孔質半導体層がエッチングされて前記第1の基板を薄化し、前記段階e)の後であって前記段階f)の前に、前記第1の基板の前記前面上に第2の基板を接合または成膜する段階e’)をさらに備える、請求項21に記載の製造方法。

【請求項23】

多孔質半導体材料のいくつかの領域が形成され、これが異なる深さを有する、請求項5から9のいずれか一項に記載の製造方法。

【請求項24】

第2の懸架領域を形成するために加工し、前記第1の懸架領域を得るために加工する前記段階f)が、前記領域において前記第1の基板を同時に加工またはこれらの領域のそれぞれにおいて逐次的に加工することによって行われる、請求項1から23のいずれか一項に記載の製造方法。

【請求項25】

前記段階a)からe)が、3つ以上の層を有する活性部を形成するように繰り返される、請求項1から24のいずれか一項に記載の製造方法。

【請求項26】

前記第1の基板の前記前面、前記第2の基板及び前記エピタキシャル成長された層の前記半導体材料が、シリコンからなる、請求項1から25のいずれか一項に記載の製造方法。

【請求項27】

センサ及び/またはアクチュエータを形成するための微小電気機械構造及び/またはナノ電気機械構造を製造するための、請求項1から26のいずれか一項に記載の方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図2A】

【図2B】

【図2C】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図5A】

【図5B】

【図5C】

【図5D】

【図6A】

【図6B】

【図6C】

【図6D】

【図6E】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図2A】

【図2B】

【図2C】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図5A】

【図5B】

【図5C】

【図5D】

【図6A】

【図6B】

【図6C】

【図6D】

【図6E】

【公開番号】特開2013−111746(P2013−111746A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−260857(P2012−260857)

【出願日】平成24年11月29日(2012.11.29)

【出願人】(502124444)コミッサリア ア レネルジー アトミーク エ オ ゼネルジ ザルタナテイヴ (383)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2012−260857(P2012−260857)

【出願日】平成24年11月29日(2012.11.29)

【出願人】(502124444)コミッサリア ア レネルジー アトミーク エ オ ゼネルジ ザルタナテイヴ (383)

【Fターム(参考)】

[ Back to top ]