希土類元素がドープされたシリコン/二酸化ケイ素格子構造とその製造方法

【課題】電界発光(EL)素子および、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造の形成方法の提供。

【解決手段】基板を被うSi層のDCスパッタリングする工程1004と、該Si層へドープするための希土類元素のDCスパッタリングする工程1006と、希土類元素がドープされたSi層を被うSiO2層のDCスパッタリングする工程1010と、格子構造を形成する工程1012と、希土類元素がドープされたSi層においてナノ結晶を形成するためのアニール工程1014とを含む。一形態において、希土類元素およびSiは、同時DCスパッタされる。格子構造において、SiO2層と希土類元素がドープされたSi層が交互に複数積層されるように、SiのDCスパッタリング、希土類元素のDCスパッタリング、およびSiO2のDCスパッタリングする工程は5〜60回繰り返される。

【解決手段】基板を被うSi層のDCスパッタリングする工程1004と、該Si層へドープするための希土類元素のDCスパッタリングする工程1006と、希土類元素がドープされたSi層を被うSiO2層のDCスパッタリングする工程1010と、格子構造を形成する工程1012と、希土類元素がドープされたSi層においてナノ結晶を形成するためのアニール工程1014とを含む。一形態において、希土類元素およびSiは、同時DCスパッタされる。格子構造において、SiO2層と希土類元素がドープされたSi層が交互に複数積層されるように、SiのDCスパッタリング、希土類元素のDCスパッタリング、およびSiO2のDCスパッタリングする工程は5〜60回繰り返される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に集積回路(IC)の製造に関連し、より具体的には、希土類元素がドープされたシリコン/二酸化ケイ素格子構造と、電界発光素子に使用可能な関連製造工程とに関する。

【背景技術】

【0002】

多孔性のシリコン(Si)から発せられる、常温における可視発光の観察により、ナノサイズのSiを使用してSiを基にした光源を開発するための莫大な量の研究が行われることとなった。広く使用されているナノクラスターSi(nc−Si)の製造方法の一つに、しばしばシリコンリッチシリコン酸化物(SRSO)と呼ばれる、SiOx(x<2)からnc−Siを凝結させ、化学気相堆積(CVD)、高周波(RF)スパッタリング、およびSi注入を使用して膜を作る方法がある。Erがドープされたナノ結晶Si(Er−doped nanocrystal Si)を形成するEr注入もまた、Siを基にした光源に使用される。しかしながら、最先端の注入方法では、ドーパントを均一にすることはできず、発光効率が低減し、コストが高くなる。同時に、そのようなドーパントの使用を支持するに足りるインターフェース工学もいまだ存在しない。素子(デバイス;device)の効率がきわめて低く、かつ加工温度がきわめて高いため、装置の用途が限定されてしまう。素子の効率を上げるためには、ナノ結晶SiとSiO2との間に大きな界面領域を形成しなければならない。

【0003】

従来、シリコンは、そのエネルギーバンドギャップという間接性のため、光電子的用途には適さないと考えられてきた。バルクシリコンは実際、きわめて効率の悪い発光体である。この問題を解決するために発展した、異なるアプローチの中で、Siナノ構造の量子閉じ込め、および、結晶シリコンへの希土類のドーピングは、きわめて強い注目を浴びた。特に、SiO2に埋め込まれたSiナノクラスター(NC)は、Siを基にした可視光源を製造することが期待できる新しい物質として、近年科学界の関心を惹いている。あるいは、Erがドープされた結晶Siは、4f殻内Er放射遷移(radiative intra−4f shell Er transition)を活用するために広く研究されてきた。室温で作動し、約0.05%の効率を有する素子が実現されたが、上述したとおり、素子の効率がきわめて低く、かつ加工温度がきわめて高く、通常1100℃を超えてしまう。

【発明の開示】

【発明が解決しようとする課題】

【0004】

近年、パスクァレロ(Pasquarello)博士は、Si‐SiO2界面の光電子放出理論を提案した。上記理論に基づくと、Si(001)‐SiO2界面におけるSi 2P内殻レベルのシフトは、もっとも近傍にある酸素原子に直線的に依存する。二番目に近傍にある酸素原子の影響は取るに足りないほど小さいことがわかった。従って、光電子放出スペクトルは、酸化状態にあるすべてのSiが界面に存在することを要求する。つまり、Si‐SiO2界面の大きな領域を設けることは、EL素子応用にとって重要な課題なのである。

【0005】

希土類がドープされたSiEL素子を、効率的に、低い加工温度において製造することができれば、好都合であると考えられる。

【0006】

希土類元素を、より効率的にSi薄膜において均一化することができれば、ナノ結晶の形成が促進されるため、好都合であると考えられる。

【課題を解決するための手段】

【0007】

概括すると、本発明は、ELおよび発光ダイオード(LED)素子の工程ならびに製造に関する。また、本発明は、ELおよびLED素子応用を目的とした、SiO2とともに多層構造または超格子構造を形成する、希土類元素のドーパントを有するナノ結晶性Siの製造方法に関連する。このような工程は、熱アニール工程、または、プラズマ酸化および熱アニール処理の両方を含む工程とともに、DCスパッタリングを使用する。イオン注入工程を排除し、同時スパッタリングにより希土類のドーピングが行われる。上記同時スパッタリング工程は経費を低減し、薄膜構造におけるドーピング密度およびドーピングプロファイルに関して、よりよく制御することができる。このような工程を用いることによって、上記加工温度は、ガラス基板(温度感受性または感温性)上のELおよびLED素子の製造に対応できるくらい充分に低下させることができる。

【0008】

したがって、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を製造する方法を提供する。上記方法は、基板を設ける工程、該基板を被うアモルファスSi層をDCスパッタリングする工程、希土類元素をDCスパッタリングする工程、該DCスパッタリングに応じて希土類元素をSi層にドーピングする工程、該希土類元素がドープされたSiを被うSiO2層をDCスパッタリングする工程、格子構造を形成する工程、アニールする工程、および該アニールに応じて、該希土類元素がドープされたSi内に1〜5ナノメートル(nm)の粒径を有するナノ結晶を形成する工程を含む。一形態において、上記希土類元素およびSiは、同時DCスパッタされる。

【0009】

代表的な形態では、上記格子構造が、複数(5〜60)のSiO2層および希土類元素がドープされたSi層を交互に含むように、SiをDCスパッタリングする上記工程、希土類元素をDCスパッタリングする上記工程、およびSiO2をDCスパッタリングする上記工程は、5〜60回繰り返される。上記Siは、1〜5nmの厚さを有するSi層を堆積させるようDCスパッタされる。上記SiO2は、2〜3nmの厚さを有するSiO2層を堆積させるようDCスパッタしている。上記アニールは、酸素ないかつArまたはN2のようなガスを有する雰囲気において、850〜1250℃の温度で10〜60分間行われる。上記希土類元素は、エルビウム(Er)、イッテルビウム(Yb)、セリウム(Ce)、プラセオジウム(Pr)、またはテルビウム(Tb)であってもよい。

【0010】

他の形態においては、上記基板が底部電極として機能するか、または、該基板と上記格子構造との間に底部電極が形成されてもよい。そして、上記方法は、上記格子構造を被う上部電極を形成する工程をさらに含む。この方法により、EL素子は製造される。

【0011】

本発明の製造方法は、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を形成する方法であって、基板を被うアモルファスSi層をスパッタリングする工程と、アモルファスSi層に希土類元素をスパッタリングし、該アモルファスSi層に希土類元素をドーピングする工程と、を含んでいることを特徴としてもよい。

【0012】

これにより、上記アモルファスSi層において、ドーパントとしての希土類元素を均一に拡散することができ、発光効率を向上させることができる。

【0013】

本発明の製造方法は、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を形成する方法であって、基板を被うアモルファスSi層および希土類元素を同時スパッタリングする工程と、アモルファスSi層に希土類元素をスパッタリングし、該アモルファスSi層に希土類元素をドーピングする工程と、を含んでいることを特徴としてもよい。

【0014】

これにより、薄膜構造におけるドーピング密度およびドーピングプロファイルについて、制御が容易となる。さらに、加工温度の低下が可能となるため、ガラス、プラスチック、および石英基板(温度感受性または感温性)上のELおよびLED素子の製造にも対応が可能となる。

【0015】

本発明の製造方法は、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を形成する方法であって、SiをDCスパッタリングする工程、希土類元素をDCスパッタリングする工程、およびSiO2をDCスパッタリングする工程を複数(5〜60)サイクル繰り返す工程を含み、該希土類元素がドープされたSi層および該SiO2層が、1〜5ナノメートルの厚さを有することを特徴としてもよい。

【0016】

これにより、希土類元素をドープしたSi層およびSiO2層は交互に積層され、超格子構造(格子構造)を形成することができる。超格子構造を形成している層には単結晶とは異なる性質が付与される。例えば、電子の移動速度が大きくなる、共鳴トンネル効果によりトンネル電流が流れやすくなる、電子と正孔の結合による発光効率が高くなる、という効果が付与される。

【0017】

二つ以上の組成の異なる、厚さ5ナノメートル以下の薄膜を複数積層させた構造を、超格子構造(格子構造)と呼ぶ。

【0018】

上述した方法、対応する格子構造、およびEL素子について、さらに以下に詳細に述べる。

【発明を実施するための最良の形態】

【0019】

図1は、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造の部分断面図である。構造100は、基板102と、基板102を被う格子構造104とを含む。上記基板102は、Si、N型Si、P型Si、Siガラス、ガリウムヒ素(GaAs)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、またはAl2O3(サファイア)のような物質であってもよい。上記格子構造104は、希土類元素がドープされたSi層106およびSiO2層108を含む。なお、ドープされたSi層106は、上記基板102と上記SiO2層108との間に挟まれて示されているが、該SiO2層108が該基板102を直接被うよう、層の順番は逆であってもよい。

【0020】

図2は、図1の格子構造の第一の変形例を示す部分断面図である。図1は、交互になっている層を1組だけ有する格子構造を示しているが、上記格子構造104は多数の組200の交互になっている層からなるのが代表的であり、各組200は希土類元素がドープされたSi層106とSiO2層108とを含む。一形態において、組200の数は、5〜60の範囲である。

【0021】

図1に戻ると、上記希土類元素がドープされたSi層106は、1〜5ナノメートルの厚さ110を有する。上記希土類元素がドープされたSi層106は、1〜5ナノメートルの粒径114を有するナノ結晶112のようなSiナノ結晶を含む。上記SiO2層108は2〜3ナノメートルの厚さ116を有する。上記ドープされたSi層106のドーピングに使用される上記希土類元素は、エルビウム(Er)、イッテルビウム(Yb)、セリウム(Ce)、プラセオジウム(Pr)、またはテルビウム(Tb)であってもよい。しかしながら、本発明はまた、周期表に記されている上記元素の近傍にあり、類似した特性を有することが知られている他の元素を用いて実施されてもよい。

【0022】

図3は、電界発光(EL)素子を示し、図1の上記格子構造の変形例の部分断面図である。ここで、上記基板102は基板底部電極であり、構造100は、上記格子構造104を被う上部電極300をさらに含む。上記上部電極300は、何例か名前を挙げると、多結晶Si、インジウムスズ酸化物(ITO)、金(Au)、アルミニウム(Al)、酸化亜鉛(ZnO)、またはクロム(Cr)のような物質であってもよい。技術的にこの技術分野では、他の電極材もよく知られている。図のように、SiO2の初期層108が、基板底部電極102を直接被っている。つまり、SiO2の初期層108は、上記上部電極300および上記底部電極102の両方に直接隣接している。トンネル素子を形成する場合には、そのような構成が有効である。しかしながら、他の応用においては、SiO2層がどちらか一方、または両方の電極に直接隣接していることは必ずしも重要ではない。

【0023】

図4は、図3に示すEL素子の変形例の部分断面図である。上記基板102は、ガラス、プラスチック、または石英のような温度感受性物質である。そのような物質は、たとえばディスプレイの製造に使用されてもよい。上記構造100はさらに、上記基板102と上記格子構造104との間に挟まれた底部電極400を含む。上部電極300は上記格子構造104を被っている。トンネル素子を所望する場合には、図のように、SiO2の初期層108が上記底部電極400を直接被うように形成されるのであってもよい。あるいは、図示されていないが、上記SiO2の初期層108は必ずしもどちらか一方、または両方の上記電極に直接隣接している必要はない。

[機能的説明]

図5は、図3の上記構造と類似のEL素子構造を示す別の図である。本発明は、ELおよびLED素子に応用するために、希土類をドーパントとしたナノ結晶Si(Nc−Si)/SiO2多重層および超格子構造を利用する。本発明を説明するために、上記希土類元素Erを例として使用する。以下に述べるように、本発明の製造工程には同時DCスパッタリング工程、熱アニール工程、またはプラズマ酸化工程を使用する。1〜5nmの厚さを有するきわめて薄いアモルファスシリコン層を堆積させるために上記DCスパッタリング工程を用いる。それから厚さ1〜5nmの二酸化ケイ素層を堆積させるために、電力レベルおよびと酸素分圧を調節する。上記DCスパッタリング工程が繰り返され、Si‐SiO2の超格子構造を形成している。上記Si層の堆積中に、Erのような希土類元素を同時スパッタリングし、ErがドープされたSi層を形成するのであってもよい。Si、SiO2、およびErを材料とする上記DCスパッタリング工程を表1、表2、および表3に示す。

【0024】

【表1】

【0025】

【表2】

【0026】

【表3】

図6は、上記Si層の厚さと堆積時間との関係を示すグラフである。Si層を形成する堆積条件は以下の通りである:電力150W、堆積温度250℃、堆積圧力1000ミリパスカル(mPa)(7.5mTorr)、そして雰囲気Ar。約1分の堆積時間で、厚さ2〜3nmのSi層を得ることができる。

【0027】

Yを上記Si層の厚さ、xを堆積時間とすると、Y=15.313x+9.4205となる。

【0028】

図7は、上記SiO2層の厚さと堆積時間との関係を示すグラフである。SiO2層の堆積条件は以下の通りである:電力150W、堆積温度250℃、堆積圧力1000ミリパスカル(mPa)(7.5mTorr)、そして雰囲気15%O2/Ar(Arに対して15%の酸素)。約1分の堆積時間で、厚さ2〜3nmのSiO2層を形成することができる。

【0029】

Yを上記SiO2層の厚さ、xを堆積時間とすると、Y=30.905x+14.901となる。

【0030】

図8は、様々な熱アニール温度におけるSi‐SiO2超格子構造のX線パターンを示すグラフである。堆積されたシリコンは非結晶質であり、熱アニール工程の後、ナノ結晶ポリシリコンを形成する。X線演算(x−ray calculation)によると、熱酸化温度が850℃から1050℃に上がるのに応じて、ポリシリコンの粒径は2.3nmから5nmまで増加する。

【0031】

図9は、1050℃で1時間熱アニールされた20層のSi‐SiO2超格子構造のX線パターンを示すグラフである。X線データ演算(x−ray data calculation)によると、ナノ結晶Siの粒径は、およそ4〜5nmである。また、実験結果は、ナノ結晶Si層の粒径が熱アニーリング温度、アニール時間、ならびに各Si層の厚さによって制御されることを示している。所定のアニール条件では、ポリシリコン層が薄いほど、結果としてSiナノ結晶の大きさは小さくなる。所定のポリシリコンの厚さでは、温度が低く、アニール時間が短いほど、結果としてSiナノ結晶の大きさは小さくなる。

【0032】

Siナノ結晶を含むSiO2薄膜のフォトルミネセンス効率は、該SiO2層にリン(P)をドーピングすることによって改善できる。したがって、DCスパッタリングによって形成された、ナノ結晶Si/リンドープSiO2多重層および超格子構造は、結果としてより明るくかつ効果的なSiを基にしたELおよびLED素子になる。

【0033】

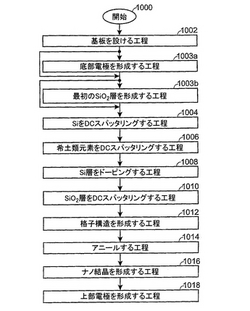

図10は、希土類元素がドープされたSi/SiO2格子構造を形成するための方法を図示したフローチャートである。上記方法は、わかりやすくするために番号を振った一連の工程として記されているが、明確に記述されている場合を除き、順序は上記番号付けに限定されるものではない。こうした工程のいくつかは省略するか、同時に行われてもよいし、または、この手順を厳密に守って行う必要はないと理解されたい。上記方法は工程1000から始まっている。

【0034】

工程1002では、基板を設ける。たとえば、上記基板となる物質は、Si、n型Si、p型Si、Siガラス、ガリウムヒ素(GaAs)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、またはAl2O3(サファイア)であってもよい。工程1004では、上記基板を被うアモルファスSi層をDCスパッタする。工程1006では、希土類元素をDCスパッタする。一形態においては、上記希土類元素およびSiは同時DCスパッタされる。つまり、工程1004および工程1006は同時に行われる。工程1008では、上記DCスパッタリングに応じて上記希土類元素を上記Si層にドープする。工程1010では、希土類元素がドープされたSi層を被うSiO2層をDCスパッタする。工程1012では、格子構造を形成する。工程1014ではアニールを行う。工程1016では、アニールに応じて1〜5nmの粒径を有するナノ結晶を、上記希土類元素がドープされたSi内に形成させる。なお、本発明のいくつかの形態において、工程1010は工程1004の前に行われる。

【0035】

典型的には、上記方法は、SiのDCスパッタリング(工程1004)、上記希土類元素のDCスパッタリング(工程1006)および上記SiO2のスパッタリングというこれらの工程を複数サイクル繰り返す。したがって、工程1012で、SiO2層、および、希土類元素がドープされたSi層を、交互に複数層有する格子構造を形成する。たとえば、工程1004、工程1006、および工程1010は5〜60回繰り返されてもよい。

【0036】

一形態において、工程1004における上記Si層のDCスパッタリングは、1〜5ナノメートルの厚さを有するSi層の堆積を含む。他の形態においては、工程1004は以下の条件である:

NおよびP型ドーパントを含む群から選択されたドーパントを含むSiターゲットを使用、

電力レベル100〜300ワット(W)、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル(mPa)(2〜10mTorr(mT))、

ArまたはN2のようなガスを含む雰囲気、および、

堆積時間0.1〜5分。

【0037】

同様に、工程1006における上記希土類元素のDCスパッタリングは、以下の条件:

希土類元素ターゲットを使用、

電力レベル50〜300W、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル(mPa)(2〜10mT)、

ArまたはN2のようなガスを含む雰囲気、および、

堆積時間0.1〜5分

におけるDCスパッタリングを含んでいてもよい。

【0038】

上記希土類元素は、エルビウム(Er)、イッテルビウム(Yb)、セリウム(Ce)、プラセオジウム(Pr)、またはテルビウム(Tb)であってもよい。

【0039】

工程1008における上記希土類元素のSi層へのドーピングには、該希土類元素のDCスパッタリング電力レベルに応じた濃度の希土類元素のSi層へのドーピングが含まれていてもよい。

【0040】

他の形態において、工程1010における上記希土類元素がドープされたSiを被う上記SiO2層のDCスパッタリングには、2〜3nmの厚さを有するSiO2層の堆積を含んでいてもよい。一形態において、工程1010は以下の条件:

NおよびP型ドーパントを含むSiターゲットを使用、

電力レベル100〜300ワットW、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル(mPa)(2〜10mT)、

ArまたはN2のようなガスに対して2〜30%の酸素を含む雰囲気、および、

堆積時間0.1〜5分

で行われる。

【0041】

他の形態において、工程1014におけるアニールには、酸素がなくArまたはN2のようなガスを含む雰囲気中で、850〜1250℃の温度を10〜60分間使用することが含まれる。

【0042】

他の形態において、工程1002における基板の設置には、基板底部電極の設置が含まれる。そのとき、上記方法はもう一つの工程を含む。すなわち、工程1018で、上記格子構造を被う上部電極を形成する。該上部電極は、多結晶Si、インジウムスズ酸化物(ITO)、金(Au)、アルミニウム(Al)、酸化亜鉛(ZnO)、またはクロム(Cr)のような物質であってもよい。

【0043】

一変形例として、工程1002における基板の設置には、ガラス、プラスチック、または石英のような温度感受性物質で製造された基板の設置が含まれる。付加的な工程、工程1003Aは、上記基板と上記格子構造との間に挟まれた底部電極を形成する。つまり、工程1003Aは、工程1004または工程1010どちらかの前に行われる。工程1018では、上記格子構造を被う該上部電極を形成する。

【0044】

トンネル素子の上記製造に有用な他の変形において、SiO2の初めの層は、上記底部電極基板を直接被うようにDCスパッタされる。

【0045】

図11は、電界発光(EL)素子を形成する方法を図示したフローチャートである。上記方法は工程1100から始まっている。工程1102では、底部電極を形成する。工程1104では、上記基板を被っているアモルファスSi層をDCスパッタする。工程1106では、上記希土類元素を上記Siと同時DCスパッタする。工程1108では、上記同時DCスパッタリングに応じて上記希土類元素を上記Si層にドープする。工程1110では、上記希土類元素がドープされたSi層を被うSiO2層をDCスパッタする。工程1112では、格子構造を形成する。工程1114ではアニールを行い、工程1116では、上記格子構造を被う上部電極を形成する。

【0046】

いくつかの形態においては、工程1101でガラス、プラスチック、または石英のような温度感受性物質で製造された基板を設ける。工程1102で上記基板を被う上記底部電極を形成させる。上記工程の詳細については図10の上記説明に記されているので、説明を簡略にするためここでは繰り返さない。

【0047】

SiO2層と接合した、希土類元素がドープされたSi層から作られた格子構造およびEL素子が提供され、また、製造についての詳細が提供されている。

【0048】

以上のように、本発明は、電界発光(EL)素子と、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を形成する対応法とを提供する。その方法は、基板を設ける工程と、基板を被うアモルファスSi層のDCスパッタリング工程と、希土類元素のDCスパッタリング工程と、それに応じて希土類元素をSi層にドーピングする工程と、希土類元素がドープされたSiの上に重なるSiO2層のDCスパッタリング工程と、格子構造を形成する工程と、アニール工程と、アニール工程に応じて希土類元素がドープされたSi内に1〜5ナノメートルの粒径を有するナノ結晶を形成する工程とを含む。一形態において、該希土類元素およびSiは、同時スパッタされる。一般に、格子構造がSiO2および希土類元素がドープされたSiの複数(5〜60)の交互層を含むように、SiのDCスパッタリング、希土類元素のDCスパッタリング、およびSiO2のDCスパッタリングという工程は5〜60回繰り返される。

【0049】

本発明を明確にするために特定の工程段階および物質の具体例があげられているが、本発明は単にこれらの例に限定されるものではない。当業者には、本発明の他の変形や実施形態が想像されるであろう。

【図面の簡単な説明】

【0050】

【図1】図1は、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造の部分断面図である。

【図2】図2は、図1の格子構造の第一の変形例を示す部分断面図である。

【図3】図3は、電界発光(EL)素子を示す、図1の格子構造の変形例の部分断面図である。

【図4】図4は、図3に示すEL素子の変形例の部分断面図である。

【図5】図5は、図3の構造と同じEL素子構造を示す別の図である。

【図6】図6は、Si層の厚さと堆積時間との関係を示すグラフである。

【図7】図7は、SiO2層の厚さと堆積時間との関係を示すグラフである。

【図8】図8は、様々な熱アニール温度におけるSi‐SiO2超格子構造のX線パターンを示すグラフである。

【図9】図9は、1050℃で1時間熱アニールされた20層のSi‐SiO2超格子構造のX線パターンを示すグラフである。

【図10】図10は、希土類元素がドープされたSi/SiO2格子構造を形成する方法を図示したフローチャートである。

【図11】図11は、電界発光(EL)素子を形成する方法を図示したフローチャートである。

【符号の説明】

【0051】

100 電界発光素子

102 基板

104 格子構造

106 ドープされたSi層

108 SiO2層

110 ドープされたSi層の厚さ

112 ナノ結晶

114 ナノ結晶の粒径

116 SiO2層の厚さ

200 一組のドープされたSi層、およびSiO2層

300 上部電極

400 底部電極

【技術分野】

【0001】

本発明は、一般に集積回路(IC)の製造に関連し、より具体的には、希土類元素がドープされたシリコン/二酸化ケイ素格子構造と、電界発光素子に使用可能な関連製造工程とに関する。

【背景技術】

【0002】

多孔性のシリコン(Si)から発せられる、常温における可視発光の観察により、ナノサイズのSiを使用してSiを基にした光源を開発するための莫大な量の研究が行われることとなった。広く使用されているナノクラスターSi(nc−Si)の製造方法の一つに、しばしばシリコンリッチシリコン酸化物(SRSO)と呼ばれる、SiOx(x<2)からnc−Siを凝結させ、化学気相堆積(CVD)、高周波(RF)スパッタリング、およびSi注入を使用して膜を作る方法がある。Erがドープされたナノ結晶Si(Er−doped nanocrystal Si)を形成するEr注入もまた、Siを基にした光源に使用される。しかしながら、最先端の注入方法では、ドーパントを均一にすることはできず、発光効率が低減し、コストが高くなる。同時に、そのようなドーパントの使用を支持するに足りるインターフェース工学もいまだ存在しない。素子(デバイス;device)の効率がきわめて低く、かつ加工温度がきわめて高いため、装置の用途が限定されてしまう。素子の効率を上げるためには、ナノ結晶SiとSiO2との間に大きな界面領域を形成しなければならない。

【0003】

従来、シリコンは、そのエネルギーバンドギャップという間接性のため、光電子的用途には適さないと考えられてきた。バルクシリコンは実際、きわめて効率の悪い発光体である。この問題を解決するために発展した、異なるアプローチの中で、Siナノ構造の量子閉じ込め、および、結晶シリコンへの希土類のドーピングは、きわめて強い注目を浴びた。特に、SiO2に埋め込まれたSiナノクラスター(NC)は、Siを基にした可視光源を製造することが期待できる新しい物質として、近年科学界の関心を惹いている。あるいは、Erがドープされた結晶Siは、4f殻内Er放射遷移(radiative intra−4f shell Er transition)を活用するために広く研究されてきた。室温で作動し、約0.05%の効率を有する素子が実現されたが、上述したとおり、素子の効率がきわめて低く、かつ加工温度がきわめて高く、通常1100℃を超えてしまう。

【発明の開示】

【発明が解決しようとする課題】

【0004】

近年、パスクァレロ(Pasquarello)博士は、Si‐SiO2界面の光電子放出理論を提案した。上記理論に基づくと、Si(001)‐SiO2界面におけるSi 2P内殻レベルのシフトは、もっとも近傍にある酸素原子に直線的に依存する。二番目に近傍にある酸素原子の影響は取るに足りないほど小さいことがわかった。従って、光電子放出スペクトルは、酸化状態にあるすべてのSiが界面に存在することを要求する。つまり、Si‐SiO2界面の大きな領域を設けることは、EL素子応用にとって重要な課題なのである。

【0005】

希土類がドープされたSiEL素子を、効率的に、低い加工温度において製造することができれば、好都合であると考えられる。

【0006】

希土類元素を、より効率的にSi薄膜において均一化することができれば、ナノ結晶の形成が促進されるため、好都合であると考えられる。

【課題を解決するための手段】

【0007】

概括すると、本発明は、ELおよび発光ダイオード(LED)素子の工程ならびに製造に関する。また、本発明は、ELおよびLED素子応用を目的とした、SiO2とともに多層構造または超格子構造を形成する、希土類元素のドーパントを有するナノ結晶性Siの製造方法に関連する。このような工程は、熱アニール工程、または、プラズマ酸化および熱アニール処理の両方を含む工程とともに、DCスパッタリングを使用する。イオン注入工程を排除し、同時スパッタリングにより希土類のドーピングが行われる。上記同時スパッタリング工程は経費を低減し、薄膜構造におけるドーピング密度およびドーピングプロファイルに関して、よりよく制御することができる。このような工程を用いることによって、上記加工温度は、ガラス基板(温度感受性または感温性)上のELおよびLED素子の製造に対応できるくらい充分に低下させることができる。

【0008】

したがって、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を製造する方法を提供する。上記方法は、基板を設ける工程、該基板を被うアモルファスSi層をDCスパッタリングする工程、希土類元素をDCスパッタリングする工程、該DCスパッタリングに応じて希土類元素をSi層にドーピングする工程、該希土類元素がドープされたSiを被うSiO2層をDCスパッタリングする工程、格子構造を形成する工程、アニールする工程、および該アニールに応じて、該希土類元素がドープされたSi内に1〜5ナノメートル(nm)の粒径を有するナノ結晶を形成する工程を含む。一形態において、上記希土類元素およびSiは、同時DCスパッタされる。

【0009】

代表的な形態では、上記格子構造が、複数(5〜60)のSiO2層および希土類元素がドープされたSi層を交互に含むように、SiをDCスパッタリングする上記工程、希土類元素をDCスパッタリングする上記工程、およびSiO2をDCスパッタリングする上記工程は、5〜60回繰り返される。上記Siは、1〜5nmの厚さを有するSi層を堆積させるようDCスパッタされる。上記SiO2は、2〜3nmの厚さを有するSiO2層を堆積させるようDCスパッタしている。上記アニールは、酸素ないかつArまたはN2のようなガスを有する雰囲気において、850〜1250℃の温度で10〜60分間行われる。上記希土類元素は、エルビウム(Er)、イッテルビウム(Yb)、セリウム(Ce)、プラセオジウム(Pr)、またはテルビウム(Tb)であってもよい。

【0010】

他の形態においては、上記基板が底部電極として機能するか、または、該基板と上記格子構造との間に底部電極が形成されてもよい。そして、上記方法は、上記格子構造を被う上部電極を形成する工程をさらに含む。この方法により、EL素子は製造される。

【0011】

本発明の製造方法は、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を形成する方法であって、基板を被うアモルファスSi層をスパッタリングする工程と、アモルファスSi層に希土類元素をスパッタリングし、該アモルファスSi層に希土類元素をドーピングする工程と、を含んでいることを特徴としてもよい。

【0012】

これにより、上記アモルファスSi層において、ドーパントとしての希土類元素を均一に拡散することができ、発光効率を向上させることができる。

【0013】

本発明の製造方法は、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を形成する方法であって、基板を被うアモルファスSi層および希土類元素を同時スパッタリングする工程と、アモルファスSi層に希土類元素をスパッタリングし、該アモルファスSi層に希土類元素をドーピングする工程と、を含んでいることを特徴としてもよい。

【0014】

これにより、薄膜構造におけるドーピング密度およびドーピングプロファイルについて、制御が容易となる。さらに、加工温度の低下が可能となるため、ガラス、プラスチック、および石英基板(温度感受性または感温性)上のELおよびLED素子の製造にも対応が可能となる。

【0015】

本発明の製造方法は、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を形成する方法であって、SiをDCスパッタリングする工程、希土類元素をDCスパッタリングする工程、およびSiO2をDCスパッタリングする工程を複数(5〜60)サイクル繰り返す工程を含み、該希土類元素がドープされたSi層および該SiO2層が、1〜5ナノメートルの厚さを有することを特徴としてもよい。

【0016】

これにより、希土類元素をドープしたSi層およびSiO2層は交互に積層され、超格子構造(格子構造)を形成することができる。超格子構造を形成している層には単結晶とは異なる性質が付与される。例えば、電子の移動速度が大きくなる、共鳴トンネル効果によりトンネル電流が流れやすくなる、電子と正孔の結合による発光効率が高くなる、という効果が付与される。

【0017】

二つ以上の組成の異なる、厚さ5ナノメートル以下の薄膜を複数積層させた構造を、超格子構造(格子構造)と呼ぶ。

【0018】

上述した方法、対応する格子構造、およびEL素子について、さらに以下に詳細に述べる。

【発明を実施するための最良の形態】

【0019】

図1は、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造の部分断面図である。構造100は、基板102と、基板102を被う格子構造104とを含む。上記基板102は、Si、N型Si、P型Si、Siガラス、ガリウムヒ素(GaAs)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、またはAl2O3(サファイア)のような物質であってもよい。上記格子構造104は、希土類元素がドープされたSi層106およびSiO2層108を含む。なお、ドープされたSi層106は、上記基板102と上記SiO2層108との間に挟まれて示されているが、該SiO2層108が該基板102を直接被うよう、層の順番は逆であってもよい。

【0020】

図2は、図1の格子構造の第一の変形例を示す部分断面図である。図1は、交互になっている層を1組だけ有する格子構造を示しているが、上記格子構造104は多数の組200の交互になっている層からなるのが代表的であり、各組200は希土類元素がドープされたSi層106とSiO2層108とを含む。一形態において、組200の数は、5〜60の範囲である。

【0021】

図1に戻ると、上記希土類元素がドープされたSi層106は、1〜5ナノメートルの厚さ110を有する。上記希土類元素がドープされたSi層106は、1〜5ナノメートルの粒径114を有するナノ結晶112のようなSiナノ結晶を含む。上記SiO2層108は2〜3ナノメートルの厚さ116を有する。上記ドープされたSi層106のドーピングに使用される上記希土類元素は、エルビウム(Er)、イッテルビウム(Yb)、セリウム(Ce)、プラセオジウム(Pr)、またはテルビウム(Tb)であってもよい。しかしながら、本発明はまた、周期表に記されている上記元素の近傍にあり、類似した特性を有することが知られている他の元素を用いて実施されてもよい。

【0022】

図3は、電界発光(EL)素子を示し、図1の上記格子構造の変形例の部分断面図である。ここで、上記基板102は基板底部電極であり、構造100は、上記格子構造104を被う上部電極300をさらに含む。上記上部電極300は、何例か名前を挙げると、多結晶Si、インジウムスズ酸化物(ITO)、金(Au)、アルミニウム(Al)、酸化亜鉛(ZnO)、またはクロム(Cr)のような物質であってもよい。技術的にこの技術分野では、他の電極材もよく知られている。図のように、SiO2の初期層108が、基板底部電極102を直接被っている。つまり、SiO2の初期層108は、上記上部電極300および上記底部電極102の両方に直接隣接している。トンネル素子を形成する場合には、そのような構成が有効である。しかしながら、他の応用においては、SiO2層がどちらか一方、または両方の電極に直接隣接していることは必ずしも重要ではない。

【0023】

図4は、図3に示すEL素子の変形例の部分断面図である。上記基板102は、ガラス、プラスチック、または石英のような温度感受性物質である。そのような物質は、たとえばディスプレイの製造に使用されてもよい。上記構造100はさらに、上記基板102と上記格子構造104との間に挟まれた底部電極400を含む。上部電極300は上記格子構造104を被っている。トンネル素子を所望する場合には、図のように、SiO2の初期層108が上記底部電極400を直接被うように形成されるのであってもよい。あるいは、図示されていないが、上記SiO2の初期層108は必ずしもどちらか一方、または両方の上記電極に直接隣接している必要はない。

[機能的説明]

図5は、図3の上記構造と類似のEL素子構造を示す別の図である。本発明は、ELおよびLED素子に応用するために、希土類をドーパントとしたナノ結晶Si(Nc−Si)/SiO2多重層および超格子構造を利用する。本発明を説明するために、上記希土類元素Erを例として使用する。以下に述べるように、本発明の製造工程には同時DCスパッタリング工程、熱アニール工程、またはプラズマ酸化工程を使用する。1〜5nmの厚さを有するきわめて薄いアモルファスシリコン層を堆積させるために上記DCスパッタリング工程を用いる。それから厚さ1〜5nmの二酸化ケイ素層を堆積させるために、電力レベルおよびと酸素分圧を調節する。上記DCスパッタリング工程が繰り返され、Si‐SiO2の超格子構造を形成している。上記Si層の堆積中に、Erのような希土類元素を同時スパッタリングし、ErがドープされたSi層を形成するのであってもよい。Si、SiO2、およびErを材料とする上記DCスパッタリング工程を表1、表2、および表3に示す。

【0024】

【表1】

【0025】

【表2】

【0026】

【表3】

図6は、上記Si層の厚さと堆積時間との関係を示すグラフである。Si層を形成する堆積条件は以下の通りである:電力150W、堆積温度250℃、堆積圧力1000ミリパスカル(mPa)(7.5mTorr)、そして雰囲気Ar。約1分の堆積時間で、厚さ2〜3nmのSi層を得ることができる。

【0027】

Yを上記Si層の厚さ、xを堆積時間とすると、Y=15.313x+9.4205となる。

【0028】

図7は、上記SiO2層の厚さと堆積時間との関係を示すグラフである。SiO2層の堆積条件は以下の通りである:電力150W、堆積温度250℃、堆積圧力1000ミリパスカル(mPa)(7.5mTorr)、そして雰囲気15%O2/Ar(Arに対して15%の酸素)。約1分の堆積時間で、厚さ2〜3nmのSiO2層を形成することができる。

【0029】

Yを上記SiO2層の厚さ、xを堆積時間とすると、Y=30.905x+14.901となる。

【0030】

図8は、様々な熱アニール温度におけるSi‐SiO2超格子構造のX線パターンを示すグラフである。堆積されたシリコンは非結晶質であり、熱アニール工程の後、ナノ結晶ポリシリコンを形成する。X線演算(x−ray calculation)によると、熱酸化温度が850℃から1050℃に上がるのに応じて、ポリシリコンの粒径は2.3nmから5nmまで増加する。

【0031】

図9は、1050℃で1時間熱アニールされた20層のSi‐SiO2超格子構造のX線パターンを示すグラフである。X線データ演算(x−ray data calculation)によると、ナノ結晶Siの粒径は、およそ4〜5nmである。また、実験結果は、ナノ結晶Si層の粒径が熱アニーリング温度、アニール時間、ならびに各Si層の厚さによって制御されることを示している。所定のアニール条件では、ポリシリコン層が薄いほど、結果としてSiナノ結晶の大きさは小さくなる。所定のポリシリコンの厚さでは、温度が低く、アニール時間が短いほど、結果としてSiナノ結晶の大きさは小さくなる。

【0032】

Siナノ結晶を含むSiO2薄膜のフォトルミネセンス効率は、該SiO2層にリン(P)をドーピングすることによって改善できる。したがって、DCスパッタリングによって形成された、ナノ結晶Si/リンドープSiO2多重層および超格子構造は、結果としてより明るくかつ効果的なSiを基にしたELおよびLED素子になる。

【0033】

図10は、希土類元素がドープされたSi/SiO2格子構造を形成するための方法を図示したフローチャートである。上記方法は、わかりやすくするために番号を振った一連の工程として記されているが、明確に記述されている場合を除き、順序は上記番号付けに限定されるものではない。こうした工程のいくつかは省略するか、同時に行われてもよいし、または、この手順を厳密に守って行う必要はないと理解されたい。上記方法は工程1000から始まっている。

【0034】

工程1002では、基板を設ける。たとえば、上記基板となる物質は、Si、n型Si、p型Si、Siガラス、ガリウムヒ素(GaAs)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、またはAl2O3(サファイア)であってもよい。工程1004では、上記基板を被うアモルファスSi層をDCスパッタする。工程1006では、希土類元素をDCスパッタする。一形態においては、上記希土類元素およびSiは同時DCスパッタされる。つまり、工程1004および工程1006は同時に行われる。工程1008では、上記DCスパッタリングに応じて上記希土類元素を上記Si層にドープする。工程1010では、希土類元素がドープされたSi層を被うSiO2層をDCスパッタする。工程1012では、格子構造を形成する。工程1014ではアニールを行う。工程1016では、アニールに応じて1〜5nmの粒径を有するナノ結晶を、上記希土類元素がドープされたSi内に形成させる。なお、本発明のいくつかの形態において、工程1010は工程1004の前に行われる。

【0035】

典型的には、上記方法は、SiのDCスパッタリング(工程1004)、上記希土類元素のDCスパッタリング(工程1006)および上記SiO2のスパッタリングというこれらの工程を複数サイクル繰り返す。したがって、工程1012で、SiO2層、および、希土類元素がドープされたSi層を、交互に複数層有する格子構造を形成する。たとえば、工程1004、工程1006、および工程1010は5〜60回繰り返されてもよい。

【0036】

一形態において、工程1004における上記Si層のDCスパッタリングは、1〜5ナノメートルの厚さを有するSi層の堆積を含む。他の形態においては、工程1004は以下の条件である:

NおよびP型ドーパントを含む群から選択されたドーパントを含むSiターゲットを使用、

電力レベル100〜300ワット(W)、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル(mPa)(2〜10mTorr(mT))、

ArまたはN2のようなガスを含む雰囲気、および、

堆積時間0.1〜5分。

【0037】

同様に、工程1006における上記希土類元素のDCスパッタリングは、以下の条件:

希土類元素ターゲットを使用、

電力レベル50〜300W、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル(mPa)(2〜10mT)、

ArまたはN2のようなガスを含む雰囲気、および、

堆積時間0.1〜5分

におけるDCスパッタリングを含んでいてもよい。

【0038】

上記希土類元素は、エルビウム(Er)、イッテルビウム(Yb)、セリウム(Ce)、プラセオジウム(Pr)、またはテルビウム(Tb)であってもよい。

【0039】

工程1008における上記希土類元素のSi層へのドーピングには、該希土類元素のDCスパッタリング電力レベルに応じた濃度の希土類元素のSi層へのドーピングが含まれていてもよい。

【0040】

他の形態において、工程1010における上記希土類元素がドープされたSiを被う上記SiO2層のDCスパッタリングには、2〜3nmの厚さを有するSiO2層の堆積を含んでいてもよい。一形態において、工程1010は以下の条件:

NおよびP型ドーパントを含むSiターゲットを使用、

電力レベル100〜300ワットW、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル(mPa)(2〜10mT)、

ArまたはN2のようなガスに対して2〜30%の酸素を含む雰囲気、および、

堆積時間0.1〜5分

で行われる。

【0041】

他の形態において、工程1014におけるアニールには、酸素がなくArまたはN2のようなガスを含む雰囲気中で、850〜1250℃の温度を10〜60分間使用することが含まれる。

【0042】

他の形態において、工程1002における基板の設置には、基板底部電極の設置が含まれる。そのとき、上記方法はもう一つの工程を含む。すなわち、工程1018で、上記格子構造を被う上部電極を形成する。該上部電極は、多結晶Si、インジウムスズ酸化物(ITO)、金(Au)、アルミニウム(Al)、酸化亜鉛(ZnO)、またはクロム(Cr)のような物質であってもよい。

【0043】

一変形例として、工程1002における基板の設置には、ガラス、プラスチック、または石英のような温度感受性物質で製造された基板の設置が含まれる。付加的な工程、工程1003Aは、上記基板と上記格子構造との間に挟まれた底部電極を形成する。つまり、工程1003Aは、工程1004または工程1010どちらかの前に行われる。工程1018では、上記格子構造を被う該上部電極を形成する。

【0044】

トンネル素子の上記製造に有用な他の変形において、SiO2の初めの層は、上記底部電極基板を直接被うようにDCスパッタされる。

【0045】

図11は、電界発光(EL)素子を形成する方法を図示したフローチャートである。上記方法は工程1100から始まっている。工程1102では、底部電極を形成する。工程1104では、上記基板を被っているアモルファスSi層をDCスパッタする。工程1106では、上記希土類元素を上記Siと同時DCスパッタする。工程1108では、上記同時DCスパッタリングに応じて上記希土類元素を上記Si層にドープする。工程1110では、上記希土類元素がドープされたSi層を被うSiO2層をDCスパッタする。工程1112では、格子構造を形成する。工程1114ではアニールを行い、工程1116では、上記格子構造を被う上部電極を形成する。

【0046】

いくつかの形態においては、工程1101でガラス、プラスチック、または石英のような温度感受性物質で製造された基板を設ける。工程1102で上記基板を被う上記底部電極を形成させる。上記工程の詳細については図10の上記説明に記されているので、説明を簡略にするためここでは繰り返さない。

【0047】

SiO2層と接合した、希土類元素がドープされたSi層から作られた格子構造およびEL素子が提供され、また、製造についての詳細が提供されている。

【0048】

以上のように、本発明は、電界発光(EL)素子と、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を形成する対応法とを提供する。その方法は、基板を設ける工程と、基板を被うアモルファスSi層のDCスパッタリング工程と、希土類元素のDCスパッタリング工程と、それに応じて希土類元素をSi層にドーピングする工程と、希土類元素がドープされたSiの上に重なるSiO2層のDCスパッタリング工程と、格子構造を形成する工程と、アニール工程と、アニール工程に応じて希土類元素がドープされたSi内に1〜5ナノメートルの粒径を有するナノ結晶を形成する工程とを含む。一形態において、該希土類元素およびSiは、同時スパッタされる。一般に、格子構造がSiO2および希土類元素がドープされたSiの複数(5〜60)の交互層を含むように、SiのDCスパッタリング、希土類元素のDCスパッタリング、およびSiO2のDCスパッタリングという工程は5〜60回繰り返される。

【0049】

本発明を明確にするために特定の工程段階および物質の具体例があげられているが、本発明は単にこれらの例に限定されるものではない。当業者には、本発明の他の変形や実施形態が想像されるであろう。

【図面の簡単な説明】

【0050】

【図1】図1は、希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造の部分断面図である。

【図2】図2は、図1の格子構造の第一の変形例を示す部分断面図である。

【図3】図3は、電界発光(EL)素子を示す、図1の格子構造の変形例の部分断面図である。

【図4】図4は、図3に示すEL素子の変形例の部分断面図である。

【図5】図5は、図3の構造と同じEL素子構造を示す別の図である。

【図6】図6は、Si層の厚さと堆積時間との関係を示すグラフである。

【図7】図7は、SiO2層の厚さと堆積時間との関係を示すグラフである。

【図8】図8は、様々な熱アニール温度におけるSi‐SiO2超格子構造のX線パターンを示すグラフである。

【図9】図9は、1050℃で1時間熱アニールされた20層のSi‐SiO2超格子構造のX線パターンを示すグラフである。

【図10】図10は、希土類元素がドープされたSi/SiO2格子構造を形成する方法を図示したフローチャートである。

【図11】図11は、電界発光(EL)素子を形成する方法を図示したフローチャートである。

【符号の説明】

【0051】

100 電界発光素子

102 基板

104 格子構造

106 ドープされたSi層

108 SiO2層

110 ドープされたSi層の厚さ

112 ナノ結晶

114 ナノ結晶の粒径

116 SiO2層の厚さ

200 一組のドープされたSi層、およびSiO2層

300 上部電極

400 底部電極

【特許請求の範囲】

【請求項1】

希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を形成する方法であって、該方法が、

基板を設ける工程と、

該基板の上に重なるアモルファスSi層をDCスパッタリングする工程と、

希土類元素をDCスパッタリングする工程と、

該DCスパッタリングに応じて該希土類元素を該Si層にドーピングする工程と、

該希土類元素がドープされたSiを被うSiO2層をDCスパッタリングする工程と、

格子構造を形成する工程と、

アニールする工程と

を含む方法。

【請求項2】

上記希土類元素およびSiが同時DCスパッタされる、請求項1に記載の方法。

【請求項3】

SiをDCスパッタリングする上記工程、希土類元素をDCスパッタリングする上記工程、およびSiO2をDCスパッタリングする上記工程を複数サイクル繰り返す工程をさらに含み、

上記格子構造を形成する工程は、SiO2層と希土類元素がドープされたSi層とが交互になっている層を複数有する格子構造を形成する工程を含む、

請求項1に記載の方法。

【請求項4】

上記Si層をDCスパッタリングする工程が、1〜5ナノメートル(nm)の厚さを有する該Si層を堆積する工程を含む、請求項1に記載の方法。

【請求項5】

上記Si層をDCスパッタリングする工程が、以下の条件:

N型およびP型ドーパントを含む群から選択されたドーパントを含むSiターゲットを使用、

電力レベル100〜300ワット(W)、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル(mPa)、

ArおよびN2を含む群から選択された気体を含む雰囲気、および、

堆積時間0.1〜5分

でDCスパッタリングする工程を含む、請求項2に記載の方法。

【請求項6】

上記アニールする工程に応じて、上記希土類元素がドープされたSi内に1〜5nmの粒径を有するナノ結晶を形成する工程をさらに含む、請求項1に記載の方法。

【請求項7】

SiをDCスパッタリングする上記工程、希土類元素をDCスパッタリングする上記工程、およびSiO2をDCスパッタリングする上記工程を複数サイクル繰り返す工程が、5〜60サイクルの範囲で実行される工程を含む、請求項3に記載の方法。

【請求項8】

アニールする工程が、酸素がなくかつArおよびN2の群から選択されたガスを含む雰囲気において、850〜1250℃の範囲の温度を10〜60分間使用する工程を含む、請求項1に記載の方法。

【請求項9】

上記希土類元素をDCスパッタリングする工程が、以下の条件:

希土類元素ターゲットを使用、

電力レベル50〜300W、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル、

ArおよびN2を含む群から選択されたガスを含む雰囲気、および、

堆積時間0.1〜5分

でDCスパッタリングする工程を含む、請求項2に記載の方法。

【請求項10】

上記希土類元素を上記Si層にドーピングする工程が、該希土類元素のDCスパッタリング電力レベルに応じた希土類元素濃度を該Si層にドーピングする工程を含む、請求項9に記載の方法。

【請求項11】

上記希土類元素がドープされたSiを被う上記SiO2層をDCスパッタリングする工程が、2〜3nmの厚さを有するSiO2層を堆積させる工程を含む、請求項1に記載の方法。

【請求項12】

上記希土類元素がドープされたSiを被う上記SiO2層をDCスパッタリングする工程が、以下の条件:

N型およびP型ドーパントを含む群から選択されたドーパントを含む、Siターゲットを使用、

電力レベル100〜300W、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル、

2〜30%割合の酸素と、ArおよびN2を含む群から選択されたガスとを含む雰囲気、および、

堆積時間0.1〜5分

でDCスパッタリングする工程を含む、請求項2に記載の方法。

【請求項13】

上記希土類元素をDCスパッタリングする工程は、エルビウム(Er)、イッテルビウム(Yb)、セリウム(Ce)、プラセオジウム(Pr)、およびテルビウム(Tb)を含む群から選択された希土類元素をDCスパッタリングする工程を含む、請求項1に記載の方法。

【請求項14】

基板を設ける工程が、基板底部電極を設ける工程を含み、

上記方法が、

上記格子構造を被う上部電極を形成する工程

をさらに含む、請求項1に記載の方法。

【請求項15】

上記基板底部電極を直接被うSiO2の初期層をDCスパッタリングする工程

をさらに含む、請求項14に記載の方法。

【請求項16】

上部電極を形成する工程が、多結晶Si、インジウムスズ酸化物(ITO)、金(Au)、アルミニウム(Al)、酸化亜鉛(ZnO)、およびクロム(Cr)を含む群から選択された物質から上部電極を形成する工程を含む、請求項14に記載の方法。

【請求項17】

基板を設ける工程が、Si、N型Si、P型Si、Siガラス、ガリウムヒ素(GaAs)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、およびAl2O3(サファイア)を含む群から選択された基板物質を設ける工程を含む、請求項1に記載の方法。

【請求項18】

基板を設ける工程が、ガラス、プラスチック、および石英を含む群から選択された温度感受性物質により製造された基板を設ける工程を含み、

上記方法は、

該基板と上記格子構造との間に挟まれた底部電極を形成する工程と、

該格子構造を被う上部電極を形成する工程と、

をさらに含む、請求項1に記載の方法。

【請求項19】

電界発光(EL)素子を形成する方法であって、該方法が、

底部電極を形成する工程と、

上記基板を被うアモルファスSi層をDCスパッタリングする工程と、

該Siと希土類元素とを同時DCスパッタリングする工程と、

該同時DCスパッタリングに応じて、該希土類元素を該Si層にドーピングする工程と、

該希土類元素がドープされたSiを被うSiO2層をDCスパッタリングする工程と、

格子構造を形成する工程と、

アニールする工程と、

該格子構造を被う上部電極を形成する工程と

を含む方法。

【請求項20】

ガラス、プラスチック、および石英を含む群から選択された温度感受性物質で製造された基板を設ける工程をさらに含み、

上記底部電極を設ける工程が、該基板を被う底部電極を形成する工程を含む、

請求項19に記載の方法。

【請求項21】

希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造であり、該構造は、

基板と、

該基板を被う格子構造であって、希土類元素がドープされたSi層と、SiO2層とを含む格子構造と

を含む構造。

【請求項22】

上記格子構造が、5〜60組の層数の交互層を含み、各組は希土類元素がドープされたSi層、およびSiO2層を含む、請求項21に記載の構造。

【請求項23】

上記希土類元素がドープされたSi層が1〜5nmの厚さを有している、請求項21に記載の構造。

【請求項24】

上記希土類元素がドープされたSi層が1〜5nmの粒径を有するSiナノ結晶を含む、請求項21に記載の構造。

【請求項25】

上記SiO2層が2〜3nmの厚さを有している、請求項21に記載の構造。

【請求項26】

上記希土類元素がドープされたSi層が、エルビウム(Er)、イッテルビウム(Yb)、セリウム(Ce)、プラセオジウム(Pr)、およびテルビウム(Tb)を含む群から選択された希土類元素を含む、請求項21に記載の構造。

【請求項27】

上記基板は基板底部電極であり、

上記構造が、

上記格子構造を被う上部電極

をさらに含む、請求項21に記載の構造。

【請求項28】

上記基板底部電極を直接被うSiO2の初期層をさらに含む、請求項27に記載の構造。

【請求項29】

上記上部電極が、多結晶Si、インジウムスズ酸化物(ITO)、金(Au)、アルミニウム(Al)、酸化亜鉛(ZnO)、およびクロム(Cr)を含む群から選択された物質である、請求項27に記載の構造。

【請求項30】

上記基板が、Si、N型Si、P型Si、Siガラス、ガリウムヒ素(GaAs)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、およびAl2O3(サファイア)を含む群から選択された物質である、請求項21に記載の構造。

【請求項31】

上記基板が、ガラス、プラスチック、および石英を含む群から選択された温度感受性物質であり、

上記構造が、

該基板と上記格子構造との間に挟まれた底部電極と、

該格子構造を被う上部電極と、

をさらに含む、請求項21に記載の構造。

【請求項32】

底部電極と、

該底部電極を被い、複数の交互層を有する格子構造であって、希土類元素がドープされたSi層と、SiO2層とを含む格子構造と、

該格子構造を被う上部電極と

を含む、電界発光素子。

【請求項33】

ガラス、プラスチック、および石英を含む群から選択された温度感受性物質で製造された基板をさらに含み、

上記底部電極が該基板と上記格子構造との間に挟まれている、

請求項32に記載の電界発光素子。

【請求項1】

希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造を形成する方法であって、該方法が、

基板を設ける工程と、

該基板の上に重なるアモルファスSi層をDCスパッタリングする工程と、

希土類元素をDCスパッタリングする工程と、

該DCスパッタリングに応じて該希土類元素を該Si層にドーピングする工程と、

該希土類元素がドープされたSiを被うSiO2層をDCスパッタリングする工程と、

格子構造を形成する工程と、

アニールする工程と

を含む方法。

【請求項2】

上記希土類元素およびSiが同時DCスパッタされる、請求項1に記載の方法。

【請求項3】

SiをDCスパッタリングする上記工程、希土類元素をDCスパッタリングする上記工程、およびSiO2をDCスパッタリングする上記工程を複数サイクル繰り返す工程をさらに含み、

上記格子構造を形成する工程は、SiO2層と希土類元素がドープされたSi層とが交互になっている層を複数有する格子構造を形成する工程を含む、

請求項1に記載の方法。

【請求項4】

上記Si層をDCスパッタリングする工程が、1〜5ナノメートル(nm)の厚さを有する該Si層を堆積する工程を含む、請求項1に記載の方法。

【請求項5】

上記Si層をDCスパッタリングする工程が、以下の条件:

N型およびP型ドーパントを含む群から選択されたドーパントを含むSiターゲットを使用、

電力レベル100〜300ワット(W)、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル(mPa)、

ArおよびN2を含む群から選択された気体を含む雰囲気、および、

堆積時間0.1〜5分

でDCスパッタリングする工程を含む、請求項2に記載の方法。

【請求項6】

上記アニールする工程に応じて、上記希土類元素がドープされたSi内に1〜5nmの粒径を有するナノ結晶を形成する工程をさらに含む、請求項1に記載の方法。

【請求項7】

SiをDCスパッタリングする上記工程、希土類元素をDCスパッタリングする上記工程、およびSiO2をDCスパッタリングする上記工程を複数サイクル繰り返す工程が、5〜60サイクルの範囲で実行される工程を含む、請求項3に記載の方法。

【請求項8】

アニールする工程が、酸素がなくかつArおよびN2の群から選択されたガスを含む雰囲気において、850〜1250℃の範囲の温度を10〜60分間使用する工程を含む、請求項1に記載の方法。

【請求項9】

上記希土類元素をDCスパッタリングする工程が、以下の条件:

希土類元素ターゲットを使用、

電力レベル50〜300W、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル、

ArおよびN2を含む群から選択されたガスを含む雰囲気、および、

堆積時間0.1〜5分

でDCスパッタリングする工程を含む、請求項2に記載の方法。

【請求項10】

上記希土類元素を上記Si層にドーピングする工程が、該希土類元素のDCスパッタリング電力レベルに応じた希土類元素濃度を該Si層にドーピングする工程を含む、請求項9に記載の方法。

【請求項11】

上記希土類元素がドープされたSiを被う上記SiO2層をDCスパッタリングする工程が、2〜3nmの厚さを有するSiO2層を堆積させる工程を含む、請求項1に記載の方法。

【請求項12】

上記希土類元素がドープされたSiを被う上記SiO2層をDCスパッタリングする工程が、以下の条件:

N型およびP型ドーパントを含む群から選択されたドーパントを含む、Siターゲットを使用、

電力レベル100〜300W、

堆積温度20〜300℃、

堆積圧力266.6〜1333ミリパスカル、

2〜30%割合の酸素と、ArおよびN2を含む群から選択されたガスとを含む雰囲気、および、

堆積時間0.1〜5分

でDCスパッタリングする工程を含む、請求項2に記載の方法。

【請求項13】

上記希土類元素をDCスパッタリングする工程は、エルビウム(Er)、イッテルビウム(Yb)、セリウム(Ce)、プラセオジウム(Pr)、およびテルビウム(Tb)を含む群から選択された希土類元素をDCスパッタリングする工程を含む、請求項1に記載の方法。

【請求項14】

基板を設ける工程が、基板底部電極を設ける工程を含み、

上記方法が、

上記格子構造を被う上部電極を形成する工程

をさらに含む、請求項1に記載の方法。

【請求項15】

上記基板底部電極を直接被うSiO2の初期層をDCスパッタリングする工程

をさらに含む、請求項14に記載の方法。

【請求項16】

上部電極を形成する工程が、多結晶Si、インジウムスズ酸化物(ITO)、金(Au)、アルミニウム(Al)、酸化亜鉛(ZnO)、およびクロム(Cr)を含む群から選択された物質から上部電極を形成する工程を含む、請求項14に記載の方法。

【請求項17】

基板を設ける工程が、Si、N型Si、P型Si、Siガラス、ガリウムヒ素(GaAs)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、およびAl2O3(サファイア)を含む群から選択された基板物質を設ける工程を含む、請求項1に記載の方法。

【請求項18】

基板を設ける工程が、ガラス、プラスチック、および石英を含む群から選択された温度感受性物質により製造された基板を設ける工程を含み、

上記方法は、

該基板と上記格子構造との間に挟まれた底部電極を形成する工程と、

該格子構造を被う上部電極を形成する工程と、

をさらに含む、請求項1に記載の方法。

【請求項19】

電界発光(EL)素子を形成する方法であって、該方法が、

底部電極を形成する工程と、

上記基板を被うアモルファスSi層をDCスパッタリングする工程と、

該Siと希土類元素とを同時DCスパッタリングする工程と、

該同時DCスパッタリングに応じて、該希土類元素を該Si層にドーピングする工程と、

該希土類元素がドープされたSiを被うSiO2層をDCスパッタリングする工程と、

格子構造を形成する工程と、

アニールする工程と、

該格子構造を被う上部電極を形成する工程と

を含む方法。

【請求項20】

ガラス、プラスチック、および石英を含む群から選択された温度感受性物質で製造された基板を設ける工程をさらに含み、

上記底部電極を設ける工程が、該基板を被う底部電極を形成する工程を含む、

請求項19に記載の方法。

【請求項21】

希土類元素がドープされたシリコン(Si)/二酸化ケイ素(SiO2)格子構造であり、該構造は、

基板と、

該基板を被う格子構造であって、希土類元素がドープされたSi層と、SiO2層とを含む格子構造と

を含む構造。

【請求項22】

上記格子構造が、5〜60組の層数の交互層を含み、各組は希土類元素がドープされたSi層、およびSiO2層を含む、請求項21に記載の構造。

【請求項23】

上記希土類元素がドープされたSi層が1〜5nmの厚さを有している、請求項21に記載の構造。

【請求項24】

上記希土類元素がドープされたSi層が1〜5nmの粒径を有するSiナノ結晶を含む、請求項21に記載の構造。

【請求項25】

上記SiO2層が2〜3nmの厚さを有している、請求項21に記載の構造。

【請求項26】

上記希土類元素がドープされたSi層が、エルビウム(Er)、イッテルビウム(Yb)、セリウム(Ce)、プラセオジウム(Pr)、およびテルビウム(Tb)を含む群から選択された希土類元素を含む、請求項21に記載の構造。

【請求項27】

上記基板は基板底部電極であり、

上記構造が、

上記格子構造を被う上部電極

をさらに含む、請求項21に記載の構造。

【請求項28】

上記基板底部電極を直接被うSiO2の初期層をさらに含む、請求項27に記載の構造。

【請求項29】

上記上部電極が、多結晶Si、インジウムスズ酸化物(ITO)、金(Au)、アルミニウム(Al)、酸化亜鉛(ZnO)、およびクロム(Cr)を含む群から選択された物質である、請求項27に記載の構造。

【請求項30】

上記基板が、Si、N型Si、P型Si、Siガラス、ガリウムヒ素(GaAs)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、およびAl2O3(サファイア)を含む群から選択された物質である、請求項21に記載の構造。

【請求項31】

上記基板が、ガラス、プラスチック、および石英を含む群から選択された温度感受性物質であり、

上記構造が、

該基板と上記格子構造との間に挟まれた底部電極と、

該格子構造を被う上部電極と、

をさらに含む、請求項21に記載の構造。

【請求項32】

底部電極と、

該底部電極を被い、複数の交互層を有する格子構造であって、希土類元素がドープされたSi層と、SiO2層とを含む格子構造と、

該格子構造を被う上部電極と

を含む、電界発光素子。

【請求項33】

ガラス、プラスチック、および石英を含む群から選択された温度感受性物質で製造された基板をさらに含み、

上記底部電極が該基板と上記格子構造との間に挟まれている、

請求項32に記載の電界発光素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2006−207027(P2006−207027A)

【公開日】平成18年8月10日(2006.8.10)

【国際特許分類】

【出願番号】特願2005−360973(P2005−360973)

【出願日】平成17年12月14日(2005.12.14)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成18年8月10日(2006.8.10)

【国際特許分類】

【出願日】平成17年12月14日(2005.12.14)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]