帯域阻止フィルタ

【課題】信号レベルの減衰の対象となる周波数帯域のみにおいて信号レベルを減衰させ、さらにその減衰量を大きくする。

【解決手段】帯域阻止フィルタには、2つの圧電基板5,6が気密封止されており、圧電基板5,6それぞれには、一主面に入出力電極対が形成され、他主面に入出力電極対に対応したアース電極が形成されている。これら入出力電極対は、入力振動電極と出力振動電極とがギャップを有して一主面に配されてなる。また、圧電基板5,6の入力振動電極及び出力振動電極が相互に接続されている。

【解決手段】帯域阻止フィルタには、2つの圧電基板5,6が気密封止されており、圧電基板5,6それぞれには、一主面に入出力電極対が形成され、他主面に入出力電極対に対応したアース電極が形成されている。これら入出力電極対は、入力振動電極と出力振動電極とがギャップを有して一主面に配されてなる。また、圧電基板5,6の入力振動電極及び出力振動電極が相互に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、特定の周波数帯の信号のみを遮断する帯域阻止フィルタに関する。

【背景技術】

【0002】

現在、無線機では、発生する不要な信号やノイズを取り除くために、特定の周波数帯における信号レベルを大きく減衰させ、特定の周波数帯の信号を遮断する帯域阻止フィルタが用いられ、特にLC回路のみからなる帯域阻止フィルタが用いられている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開昭58−42309号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

現在用いられているLC回路のみの帯域阻止フィルタによれば、特定の周波数帯の信号を遮断することはできるが、信号レベルの減衰の対象となる周波数帯域が広く、さらに減衰量が小さいため、不要な信号やノイズのみを取り除くことは難しく、通過させたい信号レベルも減衰させてしまう場合がある。

【0005】

例えば、信号を通過させる周波数帯域(以下、通過周波数帯域という)と、信号レベルを減衰させて信号を遮断する周波数帯域(以下、減衰周波数帯域という)とを隣接させた周波数設計を行った際、LC回路のみの帯域阻止フィルタによれば、通過周波数帯域の信号レベルが減衰する、もしくは、減衰周波数帯域の信号レベルが十分に減衰しないといった問題が起こる。

【0006】

そこで、上記課題を解決するために、本発明は、信号レベルの減衰の対象となる減衰周波数帯域のみにおいて信号レベルを減衰させ、さらにその減衰量が大きい帯域阻止フィルタを提供することを目的とする。

【課題を解決するための手段】

【0007】

上記の目的を達成するため、本発明にかかる帯域阻止フィルタは、複数の圧電基板が気密封止された帯域阻止フィルタにおいて、前記圧電基板には、一主面に入出力電極対が形成され、他主面に前記入出力電極対に対応したアース電極が形成され、前記入出力電極対は、入力振動電極と出力振動電極とがギャップを有して前記一主面に配されてなり、全ての前記圧電基板の入力振動電極及び出力振動電極が相互に接続されたことを特徴とする。

【0008】

本発明によれば、回路を複雑にせずに、信号レベルの減衰の対象となる減衰周波数帯域のみにおける信号レベルの減衰量を大きくすることが可能となる。特に、通過周波数帯域近傍の周波数帯域のみを急峻に減衰させるのに好適である。これは、圧電基板の特性に関係する効果であり、従前のLC回路のみを用いた帯域阻止フィルタでは、通過周波数帯域に影響を及ぼさずに通過周波数帯域近傍の周波数帯域のみを急峻に減衰させることができない。これに対して、本発明にかかる帯域阻止フィルタによれば、例えば、減衰周波数帯域に対して±1kHzの周波数帯域において、減衰量を20dB以上確保することが可能であり、このように、本発明によれば、通過周波数帯域近傍の周波数帯域であっても所望の周波数帯域のみを急峻に減衰させることが可能である。

【0009】

また、本発明によれば、複数の圧電基板を用いて複数の入出力電極対を用いており、1つの入出力電極対を用いた場合と比較して大きな減衰量を持たせることが可能である。なお、ここでいう減衰量は、入出力電極の数に比例して増加する。

【0010】

また、上記の目的を達成するため、本発明にかかる別の帯域阻止フィルタは、1つの圧電基板が気密封止された帯域阻止フィルタにおいて、前記圧電基板には、一主面に複数の入出力電極対が形成され、他主面に複数の前記入出力電極対にそれぞれ対応した複数のアース電極が形成され、前記入出力電極対は、入力振動電極と出力振動電極とがギャップを有して前記一主面に配されてなり、全ての前記入力振動電極及び前記出力振動電極が相互に接続されたことを特徴とする。

【0011】

本発明によれば、回路を複雑にせずに、信号レベルの減衰の対象となる減衰周波数帯域のみにおける信号レベルの減衰量を大きくすることが可能となる。特に、通過周波数帯域近傍の周波数帯域のみを急峻に減衰させることが可能となる。これは、圧電基板の特性に関係する効果であり、従前のLC回路のみを用いた帯域阻止フィルタでは、通過周波数帯域に影響を及ぼさずに通過周波数帯域近傍の周波数帯域のみを急峻に減衰させることができない。これに対して、本発明にかかる帯域阻止フィルタによれば、例えば、減衰周波数帯域に対して±1kHzの周波数帯域において、減衰量を20dB以上確保することが可能であり、このように、本発明によれば、通過周波数帯域近傍の周波数帯域であっても所望の周波数帯域のみを急峻に減衰させることが可能である。

【0012】

また、本発明によれば、1つの圧電基板に複数の入出力電極対を用いており、1つの入出力電極対を用いた場合と比較して大きな減衰量を持たせることが可能である。なお、ここでいう減衰量は、入出力電極の数に比例して増加する。

【0013】

前記構成において、前記圧電基板の入出力端子の少なくとも1つの端子にマッチング回路が接続されてもよい。

【0014】

この場合、前記圧電基板の入出力端子の少なくとも1つの端子に前記マッチング回路が接続されるので、このことにより、減衰周波数帯域の減衰量を増大させることが可能となり、挿入損失の改善を図ることが可能となる。このような減衰量の増大および挿入損失の改善により、対象となる不要な信号やノイズの除去能力を向上させることが可能となり、また所望の帯域阻止特性を得ることが可能となる。

【0015】

前記構成において、アース電極は、容量部を介して接地されてもよい。

【0016】

この場合、前記アース電極が前記容量部を介して接地されるので、前記容量部により当該帯域阻止フィルタの周波数調整を行うことが可能となり、また所望の減衰特性を得ることが可能となる。

【発明の効果】

【0017】

本発明にかかる帯域阻止フィルタは、信号レベルの減衰の対象となる減衰周波数帯域のみにおいて信号レベルを減衰させ、さらにその減衰量を大きくすることができる。

【図面の簡単な説明】

【0018】

【図1】図1は、本実施の形態にかかる帯域阻止フィルタの概略ブロック図である。

【図2】図2は、本実施の形態にかかる圧電デバイスの内部を公開した概略構成図である。

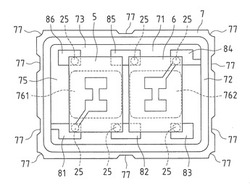

【図3】図3は、本実施の形態にかかる、圧電基板を搭載した状態のベースの概略平面図である。

【図4】図4は、本実施の形態にかかる圧電基板の概略平面図である。

【図5】図5は、本実施の形態にかかる圧電基板の概略裏面図である。

【図6】図6は、本実施の形態にかかる帯域阻止フィルタのフィルタ回路である。

【図7】図7は、図6に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図8】図8は、図6に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図9】図9は、図6に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図10】図10は、他の実施の形態にかかる圧電基板の概略平面図である。

【図11】図11は、他の実施の形態にかかる圧電基板の概略裏面図である。

【図12】図12は、他の実施の形態にかかる帯域阻止フィルタのフィルタ回路である。

【図13】図13は、図12に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図14】図14は、図12に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図15】図15は、図12に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図16】図16は、他の実施の形態にかかる帯域阻止フィルタのフィルタ回路である。

【図17】図17は、図16に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態について図面を参照して説明する。なお、以下に示す各実施例では、圧電基板として水晶基板に本発明を適用した場合を示す。また、電子デバイスとして無線機に本発明を適用した場合を示す。

【0020】

本実施の形態にかかる帯域阻止フィルタ1は、図1に示すように、少なくとも、圧電デバイス2と、2つのマッチング回路31,32と、2つの容量部41,42とから構成され、この帯域阻止フィルタ1は、無線機の回路基板(図示省略)に設けられている。

【0021】

圧電デバイス2では、図2,3に示すように、パッケージ21内に2つの圧電基板5,6が並設されている。なお、この圧電デバイス2は、周波数45GHzで動作する水晶デバイスである。

【0022】

この圧電デバイス2では、図2に示すように、ベース7と蓋22とからパッケージ21が構成され、ベース7と蓋22とが、接合材23により接合されて、気密封止された内部空間24が形成される。この内部空間24では、図2,3に示すように、2つの圧電基板5,6がベース7に導電性接合材25を用いて電気機械的に接合されている。なお、本実施の形態では、接合材23に、Agろう(AgCu合金)を用い、これをシーム溶接にて接合するが、これに限定されるものではなく、Niメッキの形成された金属リングを用いたシーム溶接でもよい。また、AuとSn等のSn合金ろう材、ガラスろう材等を用いてもよい。また、導電性接合材25に、シリコーン等の導電性樹脂接着剤やAu等の金属バンプやメッキバンプが用いられている。

【0023】

ベース7は、アルミナ等のセラミック材料の基材からなり、図2,3に示すように、2つの圧電基板5,6を搭載する底部71と、蓋22との接合部位である壁部72とから構成され、ベース7の筺体表面(一主面73)の主面外周に沿って底部71から上方に壁部72が突設されて箱状体に成形されている。本実施の形態にかかるベース7では、セラミック材料の一枚板(底部71に対応)上に、複数のセラミック材料の環状板(壁部72に対応)と、電極8(下記参照)の導電材料とが積層され、断面で見て凹状に一体焼成されている。

【0024】

ベース7の一主面73には、図2,3に示すように、底部71と壁部72とによって囲まれた平面視矩形のキャビティ75が成形され、キャビティ75の底面751に、2つのピット761,762が形成されている。これら2つのピット761,762上に圧電基板5,6がそれぞれ配され、導電性接合材25を介して電極8の接続部位(下記の電極パッド81〜86参照)に電気機械的に接合される。この接合により、2つのピット761,762は、圧電基板5,6によってそれぞれ略被覆された状態となる。なお、本実施の形態では、キャビティ75の底面751に2つのピット761,762が形成されているが、これに限定されるものではなく、キャビティ75の底面751にピットが形成されていなくてもよい。

【0025】

また、ベース7の筺体裏面(他主面74)の四隅及び各辺の任意の位置(本実施の形態では、長辺の全長を2等分する位置と、短辺の全長を3等分する位置)に、キャスタレーション77がそれぞれ形成されている。これらキャスタレーション77は、ベース7の筺体側面に高さ方向に沿って帯状に切り欠いた状態で形成されている。

【0026】

ベース7の電極8は、圧電基板5,6を電気機械的に接合する電極パッド81〜86と、無線機の回路基板に電気機械的に接合する外部端子(図示省略)と、電極パッド81〜86を外部端子に引き回す引き回しパターン(図示省略)とから構成され、電極パッド81〜86は引き回しパターンによって外部端子に接続されている。ベース7の電極8は、W,Mo等のメタライズ材料を印刷した後にベース7と一体的に焼成して形成される。このうち、電極8の端子部分(圧電基板5,6との接続部分である電極パッド81〜86と、無線機の回路基板との接続部分である外部端子)などの露出部分には、メタライズ上部にNiメッキが形成され、その上部にAuメッキが形成されて構成される。なお、ここでいうメッキ形成の工法として、電解メッキ法が挙げられる。

【0027】

蓋22は、金属材料から成形され、直方体の一枚板に成形されている。この蓋22の下面がベース7との接合部位となり、蓋22の下面がベース7の壁部72の天面にシーム溶接により接合材23により接合されて、蓋22とベース7とによる圧電デバイス2のパッケージ21が構成される。

【0028】

2つの圧電基板5,6は、ともにATカット水晶材料からなり、直方体の一枚板の基板51,61に成形され、3端子を有する同一構成のものである。なお、圧電基板5,6は、同一構成からなるので、圧電基板5,6の説明では、圧電基板5を示す図面を用いる。

【0029】

圧電基板5では、図4,5に示すように、一方の面(一主面52)に入力振動電極54と出力振動電極55とがギャップを有して並んで配された入出力電極対が形成されている。また、他方の面(他主面53)に入力振動電極54及び出力振動電極55に対応するアース電極56が形成されている。この圧電基板5では、3箇所のコーナー部分に入力端子57と出力端子58とアース端子59とが形成され、入力振動電極54は引き出し電極パターン510によって入力端子57に引き出され、出力振動電極55は引き出し電極パターン511によって出力端子58に引き出され、アース電極59は引き出し電極パターン512によってアース端子59に引き出されている。なお、入力端子57と出力端子58とは、基板51の対角線上に位置するコーナー部にそれぞれ形成され、アース端子59は残るコーナー部分の一角に形成されている。この圧電基板5は、入力端子57、出力端子58およびアース端子59が導電性接合材25によってベース7の電極パッド81,82,86に電気機械的に接合されることで、圧電基板5がベース7に設けられる。

【0030】

また、圧電基板6では、圧電基板5と同様の構成からなり、図4,5を参照して、一方の面(一主面62)に入力振動電極64と出力振動電極65とがギャップを有して並んで配された入出力電極対が形成されている。また、他方の面(他主面63)に入力振動電極64及び出力振動電極65に対応するアース電極66が形成されている。この圧電基板6では、3箇所のコーナー部分に入力端子67と出力端子68とアース端子69とが形成され、入力振動電極64は引き出し電極パターン610によって入力端子67に引き出され、出力振動電極65は引き出し電極パターン611によって出力端子68に引き出され、アース電極66は引き出し電極パターン612によってアース端子69に引き出されている。なお、入力端子57と出力端子68とは、基板61の対角線上に位置するコーナー部にそれぞれ形成され、アース端子69は残るコーナー部分の一角に形成されている。この圧電基板6は、入力端子67、出力端子68およびアース端子69が導電性接合材25によってベース7の電極パッド83,84,85に電気機械的に接合されることで、圧電基板6がベース7に設けられる。

【0031】

上記構成の圧電デバイス2では、圧電基板5,6をベース7に接合した後に、ベース7に蓋22を配し、窒素雰囲気下でシーム封止によりベース7と蓋22との接合を行う。このシーム封止により、ベース7と蓋22とが接合されて、圧電基板5,6が気密封止される。

【0032】

上記の圧電デバイス2を用いた帯域阻止フィルタ1のフィルタ回路11について図6を用いて説明する。

【0033】

本実施の形態にかかる圧電デバイス2では、1つのパッケージ21内に、3端子(入力端子57,67、出力端子58,68、アース端子59,69)を有する圧電基板5,6が並設されており、一方の圧電基板5の入力端子57と出力端子58と、他方の圧電基板6の入力端子67と出力端子68とが相互に直接接続され、一方の圧電基板5のアース端子59と他方の圧電基板6のアース端子69とが相互に接続されている。

【0034】

また、本実施の形態にかかる帯域阻止フィルタ1の一部構成であるマッチング回路31,32は、圧電デバイス2の入出力端子(符号57,67参照)にそれぞれ接続されるコンデンサ311,321およびインダクタ312,322からそれぞれ構成され、インダクタ312,322の一端が接地されている。このように、これらマッチング回路31,32は、LC回路で構成されている。このLC回路では、圧電デバイス2の入力端子(圧電基板5の入力端子57)にコンデンサ311が接続され、入力端子57とコンデンサ311間にインダクタ312の一端が接続され、インダクタ312の他端が接地されている。また、圧電デバイス2の出力端子(圧電基板6の入力端子67)にコンデンサ321が接続され、入力端子67とコンデンサ321間にインダクタ322の一端が接続され、インダクタ322の他端が接地されている。このようなLC回路の構成により、ハイパスフィルタが構成され、圧電デバイス2とLC回路のハイパスフィルタにより、周波数帯域の複数領域において信号を遮断することができる。

【0035】

また、本実施の形態にかかる帯域阻止フィルタ1の一部構成である容量部41,42は、圧電デバイス2のアース端子(符号59,69参照)にそれぞれ接続される容量部からなり、容量部41,42は接地されている。なお、本実施の形態では、容量部41に可変容量部のトリマーコンデンサを用い、容量部42にコンデンサ42を用いている。

【0036】

本実施の形態では、圧電デバイス2とマッチング回路31,32と容量部41,42とを、半田などの導電性接合材(図示省略)により無線機の回路基板に接合して図6に示す帯域阻止フィルタ1の回路を構成する。この帯域阻止フィルタ1による周波数の帯域阻止特性を図7〜9に示す。

【0037】

本実施の形態にかかる帯域阻止フィルタ1によれば、回路を複雑にせずに、図7〜9に示すように信号レベルの減衰の対象となる減衰周波数帯域における信号レベルの減衰量を大きくすることができる。なお、図7〜9は、横軸のスケールが異なるだけで、全て本実施の形態にかかる帯域阻止フィルタ1による信号レベルのデータから生成されたグラフである。

【0038】

また、上記の回路を構築した帯域阻止フィルタ1では、圧電基板5の入力端子57と出力端子58と、圧電基板6の入力端子67と出力端子68とを直接接続し、圧電基板5のアース端子59と圧電基板6のアース端子69とを接続しているので、不要な信号を取り除くことができ、図7〜9に示すように通過周波数帯域近傍の周波数帯域のみを急峻に減衰させることができる。これは、圧電基板5,6の特性に関係する効果であり、従前のLC回路のみを用いた帯域阻止フィルタでは、通過周波数帯域に影響を及ぼさずに通過周波数帯域近傍の周波数帯域のみを急峻に減衰させることができない。これに対して、本実施の形態にかかる帯域阻止フィルタ1によれば、例えば、減衰周波数帯域に対して±1kHzの周波数帯域において、減衰量を20dB以上確保することができ、このように、本実施の形態にかかる帯域阻止フィルタ1によれば、通過周波数帯域近傍の周波数帯域であっても所望の周波数帯域のみを急峻に減衰させることができる。

【0039】

また、圧電基板5の入力端子57と、圧電基板6の入力端子67と、にマッチング回路31,32が接続されるので、このことにより、減衰周波数帯域の減衰量を増大させることができ、挿入損失の改善を図ることができる。このような減衰量の増大および挿入損失の改善により、対象となる不要な信号やノイズの除去能力を向上させることができ、また所望の減衰特性を得ることができる。

【0040】

また、アース電極56,66が容量部41,42を介して接地されるので、容量部41,42により帯域阻止フィルタ1の周波数調整を行うことができ、また所望の減衰特性を得ることができる。

【0041】

また、本実施の形態にかかる帯域阻止フィルタ1では、2つの圧電基板5,6を用いて2つの入出力電極対を用いており、1つの入出力電極対を用いた場合と比較して約2倍(段数)の減衰量を持たせることができる。なお、入出力電極対の数に比例して減衰量を増加させることができるので、本実施の形態に限らず3つ以上の圧電基板を用いて3つ以上の入出力電極対を用いることが好ましいが、小型の帯域阻止フィルタ1を構成する場合、本実施の形態にかかる2つの入出力電極対が好適である。

【0042】

また、本実施の形態にかかる帯域阻止フィルタ1では、図7〜9に示すように、通過周波数帯域の低周波数側に隣接する信号レベルを減衰させたい時に特に有効である。

【0043】

なお、本実施の形態では、圧電基板5,6に水晶基板を用いているが、圧電材料であれば他の材料であってもよい。

【0044】

また、本実施の形態では、電子デバイスに無線機を適用しているが、無線機以外の電子デバイスであってもよく、例えば周波数の帯域阻止を必要とする電子デバイスであれば、本発明は適用可能である。

【0045】

また、本実施の形態にかかる帯域阻止フィルタ1では、2つの圧電基板5,6にそれぞれ3端子の電極構成を有しているが、これに限定されるものではなく、1つの圧電基板に複数の3端子の電極構成を設けてもよい。すなわち、圧電基板の一主面に複数の入出力電極対が形成され、他主面に複数の入出力電極対にそれぞれ対応した複数のアース電極が形成され、入出力電極対は、入力振動電極と出力振動電極とがギャップを有して配され、全ての入力振動電極及び出力振動電極が相互に接続されてもよい。具体的には、図10,11に示す圧電基板9を用いてもよい。図10,11に示す圧電基板9では、一主面91に2つの入出力電極対93,94が形成され、他主面92に2つの入出力電極対93,94にそれぞれ対応した2つのアース電極95,96が形成され、入出力電極対93,94は、それぞれ入力振動電極931,941と出力振動電極932,942とがギャップを有して配され、全ての入力振動電極931,941及び出力振動電極932,942が相互に接続されてもよい。この図10,11に示す圧電基板9を圧電デバイス2に設けることで、本実施の形態にかかる帯域阻止フィルタ1と同様の作用効果を有する。

【0046】

また、本実施の形態にかかる帯域阻止フィルタ1では、マッチング回路31,32を、コンデンサ311,321およびインダクタ312,322からそれぞれ構成しているが、これに限定されるものではなく、図12に示すような構成であってもよい。図12に示す帯域阻止フィルタ1では、マッチング回路31は、圧電デバイス2の入力端子に接続されたインダクタ313およびトリマーコンデンサ314から構成されており、トリマーコンデンサ314の一端は接地されている。また、マッチング回路32は、圧電デバイス2の出力端子に接続されたインダクタ323およびトリマーコンデンサ324から構成されており、トリマーコンデンサ324の一端は接地されている。また、この帯域阻止フィルタ1では、容量部42に可変容量部のトリマーコンデンサ42が用いられている。この図12に示すLC回路では、圧電デバイス2の入力端子(圧電基板5の入力端子57)にインダクタ313が接続され、入力端子57とインダクタ313間にトリマーコンデンサ314の一端が接続され、トリマーコンデンサ314の他端が接地されている。また、圧電デバイス2の出力端子(圧電基板6の入力端子67)にインダクタ323が接続され、入力端子57とインダクタ323間にトリマーコンデンサ324の一端が接続され、トリマーコンデンサ324の他端が接地されている。このようなLC回路の構成により、ローバスフィルタが構成され、圧電デバイス2とこのLC回路のローパスフィルタとにより、周波数帯域の複数領域において信号を遮断することができる。また、マッチング回路には減衰周波数域の減衰量の調整と、他の領域の減衰量調整の機能がある。

【0047】

この図12に示す帯域阻止フィルタ1では、図6に示す帯域阻止フィルタ1と異なり、図13〜15に示すように通過周波数帯域の高周波数側に隣接する信号レベルを減衰させるのに有効である。

【0048】

また、本実施の形態にかかる帯域阻止フィルタ1では、一方のアース端子59にトリマーコンデンサを接続し、他方のアース端子69にコンデンサを接続しているが、これに限定されるものではなく、図12に示すようにアース端子59,69に、一端が接地された容量部41,42であるトリマーコンデンサをそれぞれ接続してもよい。

【0049】

この図12に示す帯域阻止フィルタ1による減衰周波数帯域における信号レベルの減衰を示したグラフを図13〜15に示す。図13〜15に示すように、図12に示す帯域阻止フィルタ1によれば、回路を複雑にせずに、信号レベルの減衰の対象となる減衰周波数帯域における信号レベルの減衰量を大きくすることができる。なお、図13〜15は、横軸のスケールが異なるだけで、全て図12に示す帯域阻止フィルタ1による信号レベルのデータから生成されたグラフである。

【0050】

また、本実施の形態にかかる帯域阻止フィルタ1では、一方のアース端子59にトリマーコンデンサを接続し、他方のアース端子69にコンデンサを接続しているが、これに限定されるものではなく、他方のアース端子69にトリマーコンデンサを接続し、一方のアース端子59にコンデンサを接続してもよい。なお、本実施の形態に示すように、トリマーコンデンサの代わり固定コンデンサを用いてもよい。

【0051】

また、図6に示すフィルタ回路11では、圧電基板5の入力端子57と出力端子58と、圧電基板6の入力端子67と出力端子68とを直接接続しているが、これに限定されるものではなく、図16に示すように圧電基板5の入力端子57(圧電基板6の入力端子67)と圧電基板6の出力端子68(圧電基板5の出力端子58)とをインダクタ10を介して接続してもよい。この場合、2つの圧電基板5,6により、4つの圧電基板を用いた構成を構築することができ、その結果、信号レベルの減衰量を増加させるのにより好適である。

【0052】

この図16に示す帯域阻止フィルタ1による減衰周波数帯域における信号レベルの減衰を示したグラフを図17に示す。この図17に示すように、図16に示す帯域阻止フィルタ1によれば、回路を複雑にせずに、信号レベルの減衰の対象となる減衰周波数帯域における信号レベルの減衰量をさらに大きくすることができる。

【0053】

なお、上記の図8,14,17に示す帯域阻止フィルタ1による減衰周波数帯域における信号レベルの減衰を示したグラフでは、減衰周波数帯域の中央位置(図中の0点参照)からプラス側に位置する周波数帯域(約+200〜+700Hz)において、スプリアスが発生している。このスプリアスは、パッケージ7に圧電基板(5,6)が導電性接合材により収納保持(搭載)され、蓋22により気密封止された圧電デバイス2特有のスプリアスである。

【0054】

また、本実施の形態では、圧電デバイス2とマッチング回路31,32と容量部41,42とを別々に設けているが、これに限定されるものではなく、圧電デバイス2のパッケージ21内にマッチング回路31,32と容量部41,42との少なくとも一方を組み込んでもよい。しかしながら、圧電デバイス2のパッケージ21の小型化を考慮すると、本実施の形態が好ましい。

【0055】

また、本実施の形態では、無線機の回路基板に直接、圧電デバイス2とマッチング回路31,32と容量部41,42とを設けているが、これに限定されるものではなく、圧電デバイス2とマッチング回路31,32と容量部41,42とを設けた帯域阻止フィルタの回路基板を別途用い、この帯域阻止フィルタの回路基板を無線機の回路基板に接続してもよい。

【0056】

なお、本発明は、その精神や主旨または主要な特徴から逸脱することなく、他のいろいろな形で実施することができる。そのため、上述の実施例はあらゆる点で単なる例示にすぎず、限定的に解釈してはならない。本発明の範囲は特許請求の範囲によって示すものであって、明細書本文には、なんら拘束されない。さらに、特許請求の範囲の均等範囲に属する変形や変更は、全て本発明の範囲内のものである。

【産業上の利用可能性】

【0057】

本発明は、電子デバイスにおいて周波数の帯域阻止を行う帯域阻止フィルタに適用できる。

【符号の説明】

【0058】

1 帯域阻止フィルタ

11 フィルタ回路

2 圧電デバイス

21 パッケージ

22 蓋

23 接合材

24 内部空間

25 導電性接合材

31 マッチング回路

311 コンデンサ

312 インダクタ

313 インダクタ

314 トリマーコンデンサ

32 マッチング回路

321 コンデンサ

322 インダクタ

323 インダクタ

324 トリマーコンデンサ

41,42 容量部

5 圧電基板

51 基板

52 一主面

53 他主面

54 入力振動電極

55 出力振動電極

56 アース電極

57 入力端子

58 出力端子

59 アース端子

510 引き出し電極パターン

511 引き出し電極パターン

512 引き出し電極パターン

6 圧電基板

61 基板

62 一主面

63 他主面

64 入力振動電極

65 出力振動電極

66 アース電極

67 入力端子

68 出力端子

69 アース端子

610 引き出し電極パターン

611 引き出し電極パターン

612 引き出し電極パターン

7 ベース

71 底部

72 壁部

73 一主面

74 他主面

75 キャビティ

751 底面

761,762 ピット

77 キャスタレーション

8 電極

81,82,83,84,85,86 電極パッド

9 圧電基板

91 一主面

92 他主面

93 入出力電極対

931 入力振動電極

932 出力振動電極

95,96アース電極

94 入出力電極対

941 入力振動電極

942 出力振動電極

10 インダクタ

【技術分野】

【0001】

本発明は、特定の周波数帯の信号のみを遮断する帯域阻止フィルタに関する。

【背景技術】

【0002】

現在、無線機では、発生する不要な信号やノイズを取り除くために、特定の周波数帯における信号レベルを大きく減衰させ、特定の周波数帯の信号を遮断する帯域阻止フィルタが用いられ、特にLC回路のみからなる帯域阻止フィルタが用いられている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開昭58−42309号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

現在用いられているLC回路のみの帯域阻止フィルタによれば、特定の周波数帯の信号を遮断することはできるが、信号レベルの減衰の対象となる周波数帯域が広く、さらに減衰量が小さいため、不要な信号やノイズのみを取り除くことは難しく、通過させたい信号レベルも減衰させてしまう場合がある。

【0005】

例えば、信号を通過させる周波数帯域(以下、通過周波数帯域という)と、信号レベルを減衰させて信号を遮断する周波数帯域(以下、減衰周波数帯域という)とを隣接させた周波数設計を行った際、LC回路のみの帯域阻止フィルタによれば、通過周波数帯域の信号レベルが減衰する、もしくは、減衰周波数帯域の信号レベルが十分に減衰しないといった問題が起こる。

【0006】

そこで、上記課題を解決するために、本発明は、信号レベルの減衰の対象となる減衰周波数帯域のみにおいて信号レベルを減衰させ、さらにその減衰量が大きい帯域阻止フィルタを提供することを目的とする。

【課題を解決するための手段】

【0007】

上記の目的を達成するため、本発明にかかる帯域阻止フィルタは、複数の圧電基板が気密封止された帯域阻止フィルタにおいて、前記圧電基板には、一主面に入出力電極対が形成され、他主面に前記入出力電極対に対応したアース電極が形成され、前記入出力電極対は、入力振動電極と出力振動電極とがギャップを有して前記一主面に配されてなり、全ての前記圧電基板の入力振動電極及び出力振動電極が相互に接続されたことを特徴とする。

【0008】

本発明によれば、回路を複雑にせずに、信号レベルの減衰の対象となる減衰周波数帯域のみにおける信号レベルの減衰量を大きくすることが可能となる。特に、通過周波数帯域近傍の周波数帯域のみを急峻に減衰させるのに好適である。これは、圧電基板の特性に関係する効果であり、従前のLC回路のみを用いた帯域阻止フィルタでは、通過周波数帯域に影響を及ぼさずに通過周波数帯域近傍の周波数帯域のみを急峻に減衰させることができない。これに対して、本発明にかかる帯域阻止フィルタによれば、例えば、減衰周波数帯域に対して±1kHzの周波数帯域において、減衰量を20dB以上確保することが可能であり、このように、本発明によれば、通過周波数帯域近傍の周波数帯域であっても所望の周波数帯域のみを急峻に減衰させることが可能である。

【0009】

また、本発明によれば、複数の圧電基板を用いて複数の入出力電極対を用いており、1つの入出力電極対を用いた場合と比較して大きな減衰量を持たせることが可能である。なお、ここでいう減衰量は、入出力電極の数に比例して増加する。

【0010】

また、上記の目的を達成するため、本発明にかかる別の帯域阻止フィルタは、1つの圧電基板が気密封止された帯域阻止フィルタにおいて、前記圧電基板には、一主面に複数の入出力電極対が形成され、他主面に複数の前記入出力電極対にそれぞれ対応した複数のアース電極が形成され、前記入出力電極対は、入力振動電極と出力振動電極とがギャップを有して前記一主面に配されてなり、全ての前記入力振動電極及び前記出力振動電極が相互に接続されたことを特徴とする。

【0011】

本発明によれば、回路を複雑にせずに、信号レベルの減衰の対象となる減衰周波数帯域のみにおける信号レベルの減衰量を大きくすることが可能となる。特に、通過周波数帯域近傍の周波数帯域のみを急峻に減衰させることが可能となる。これは、圧電基板の特性に関係する効果であり、従前のLC回路のみを用いた帯域阻止フィルタでは、通過周波数帯域に影響を及ぼさずに通過周波数帯域近傍の周波数帯域のみを急峻に減衰させることができない。これに対して、本発明にかかる帯域阻止フィルタによれば、例えば、減衰周波数帯域に対して±1kHzの周波数帯域において、減衰量を20dB以上確保することが可能であり、このように、本発明によれば、通過周波数帯域近傍の周波数帯域であっても所望の周波数帯域のみを急峻に減衰させることが可能である。

【0012】

また、本発明によれば、1つの圧電基板に複数の入出力電極対を用いており、1つの入出力電極対を用いた場合と比較して大きな減衰量を持たせることが可能である。なお、ここでいう減衰量は、入出力電極の数に比例して増加する。

【0013】

前記構成において、前記圧電基板の入出力端子の少なくとも1つの端子にマッチング回路が接続されてもよい。

【0014】

この場合、前記圧電基板の入出力端子の少なくとも1つの端子に前記マッチング回路が接続されるので、このことにより、減衰周波数帯域の減衰量を増大させることが可能となり、挿入損失の改善を図ることが可能となる。このような減衰量の増大および挿入損失の改善により、対象となる不要な信号やノイズの除去能力を向上させることが可能となり、また所望の帯域阻止特性を得ることが可能となる。

【0015】

前記構成において、アース電極は、容量部を介して接地されてもよい。

【0016】

この場合、前記アース電極が前記容量部を介して接地されるので、前記容量部により当該帯域阻止フィルタの周波数調整を行うことが可能となり、また所望の減衰特性を得ることが可能となる。

【発明の効果】

【0017】

本発明にかかる帯域阻止フィルタは、信号レベルの減衰の対象となる減衰周波数帯域のみにおいて信号レベルを減衰させ、さらにその減衰量を大きくすることができる。

【図面の簡単な説明】

【0018】

【図1】図1は、本実施の形態にかかる帯域阻止フィルタの概略ブロック図である。

【図2】図2は、本実施の形態にかかる圧電デバイスの内部を公開した概略構成図である。

【図3】図3は、本実施の形態にかかる、圧電基板を搭載した状態のベースの概略平面図である。

【図4】図4は、本実施の形態にかかる圧電基板の概略平面図である。

【図5】図5は、本実施の形態にかかる圧電基板の概略裏面図である。

【図6】図6は、本実施の形態にかかる帯域阻止フィルタのフィルタ回路である。

【図7】図7は、図6に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図8】図8は、図6に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図9】図9は、図6に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図10】図10は、他の実施の形態にかかる圧電基板の概略平面図である。

【図11】図11は、他の実施の形態にかかる圧電基板の概略裏面図である。

【図12】図12は、他の実施の形態にかかる帯域阻止フィルタのフィルタ回路である。

【図13】図13は、図12に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図14】図14は、図12に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図15】図15は、図12に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【図16】図16は、他の実施の形態にかかる帯域阻止フィルタのフィルタ回路である。

【図17】図17は、図16に示す帯域阻止フィルタによる減衰周波数帯域における信号レベルの減衰を示したグラフである。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態について図面を参照して説明する。なお、以下に示す各実施例では、圧電基板として水晶基板に本発明を適用した場合を示す。また、電子デバイスとして無線機に本発明を適用した場合を示す。

【0020】

本実施の形態にかかる帯域阻止フィルタ1は、図1に示すように、少なくとも、圧電デバイス2と、2つのマッチング回路31,32と、2つの容量部41,42とから構成され、この帯域阻止フィルタ1は、無線機の回路基板(図示省略)に設けられている。

【0021】

圧電デバイス2では、図2,3に示すように、パッケージ21内に2つの圧電基板5,6が並設されている。なお、この圧電デバイス2は、周波数45GHzで動作する水晶デバイスである。

【0022】

この圧電デバイス2では、図2に示すように、ベース7と蓋22とからパッケージ21が構成され、ベース7と蓋22とが、接合材23により接合されて、気密封止された内部空間24が形成される。この内部空間24では、図2,3に示すように、2つの圧電基板5,6がベース7に導電性接合材25を用いて電気機械的に接合されている。なお、本実施の形態では、接合材23に、Agろう(AgCu合金)を用い、これをシーム溶接にて接合するが、これに限定されるものではなく、Niメッキの形成された金属リングを用いたシーム溶接でもよい。また、AuとSn等のSn合金ろう材、ガラスろう材等を用いてもよい。また、導電性接合材25に、シリコーン等の導電性樹脂接着剤やAu等の金属バンプやメッキバンプが用いられている。

【0023】

ベース7は、アルミナ等のセラミック材料の基材からなり、図2,3に示すように、2つの圧電基板5,6を搭載する底部71と、蓋22との接合部位である壁部72とから構成され、ベース7の筺体表面(一主面73)の主面外周に沿って底部71から上方に壁部72が突設されて箱状体に成形されている。本実施の形態にかかるベース7では、セラミック材料の一枚板(底部71に対応)上に、複数のセラミック材料の環状板(壁部72に対応)と、電極8(下記参照)の導電材料とが積層され、断面で見て凹状に一体焼成されている。

【0024】

ベース7の一主面73には、図2,3に示すように、底部71と壁部72とによって囲まれた平面視矩形のキャビティ75が成形され、キャビティ75の底面751に、2つのピット761,762が形成されている。これら2つのピット761,762上に圧電基板5,6がそれぞれ配され、導電性接合材25を介して電極8の接続部位(下記の電極パッド81〜86参照)に電気機械的に接合される。この接合により、2つのピット761,762は、圧電基板5,6によってそれぞれ略被覆された状態となる。なお、本実施の形態では、キャビティ75の底面751に2つのピット761,762が形成されているが、これに限定されるものではなく、キャビティ75の底面751にピットが形成されていなくてもよい。

【0025】

また、ベース7の筺体裏面(他主面74)の四隅及び各辺の任意の位置(本実施の形態では、長辺の全長を2等分する位置と、短辺の全長を3等分する位置)に、キャスタレーション77がそれぞれ形成されている。これらキャスタレーション77は、ベース7の筺体側面に高さ方向に沿って帯状に切り欠いた状態で形成されている。

【0026】

ベース7の電極8は、圧電基板5,6を電気機械的に接合する電極パッド81〜86と、無線機の回路基板に電気機械的に接合する外部端子(図示省略)と、電極パッド81〜86を外部端子に引き回す引き回しパターン(図示省略)とから構成され、電極パッド81〜86は引き回しパターンによって外部端子に接続されている。ベース7の電極8は、W,Mo等のメタライズ材料を印刷した後にベース7と一体的に焼成して形成される。このうち、電極8の端子部分(圧電基板5,6との接続部分である電極パッド81〜86と、無線機の回路基板との接続部分である外部端子)などの露出部分には、メタライズ上部にNiメッキが形成され、その上部にAuメッキが形成されて構成される。なお、ここでいうメッキ形成の工法として、電解メッキ法が挙げられる。

【0027】

蓋22は、金属材料から成形され、直方体の一枚板に成形されている。この蓋22の下面がベース7との接合部位となり、蓋22の下面がベース7の壁部72の天面にシーム溶接により接合材23により接合されて、蓋22とベース7とによる圧電デバイス2のパッケージ21が構成される。

【0028】

2つの圧電基板5,6は、ともにATカット水晶材料からなり、直方体の一枚板の基板51,61に成形され、3端子を有する同一構成のものである。なお、圧電基板5,6は、同一構成からなるので、圧電基板5,6の説明では、圧電基板5を示す図面を用いる。

【0029】

圧電基板5では、図4,5に示すように、一方の面(一主面52)に入力振動電極54と出力振動電極55とがギャップを有して並んで配された入出力電極対が形成されている。また、他方の面(他主面53)に入力振動電極54及び出力振動電極55に対応するアース電極56が形成されている。この圧電基板5では、3箇所のコーナー部分に入力端子57と出力端子58とアース端子59とが形成され、入力振動電極54は引き出し電極パターン510によって入力端子57に引き出され、出力振動電極55は引き出し電極パターン511によって出力端子58に引き出され、アース電極59は引き出し電極パターン512によってアース端子59に引き出されている。なお、入力端子57と出力端子58とは、基板51の対角線上に位置するコーナー部にそれぞれ形成され、アース端子59は残るコーナー部分の一角に形成されている。この圧電基板5は、入力端子57、出力端子58およびアース端子59が導電性接合材25によってベース7の電極パッド81,82,86に電気機械的に接合されることで、圧電基板5がベース7に設けられる。

【0030】

また、圧電基板6では、圧電基板5と同様の構成からなり、図4,5を参照して、一方の面(一主面62)に入力振動電極64と出力振動電極65とがギャップを有して並んで配された入出力電極対が形成されている。また、他方の面(他主面63)に入力振動電極64及び出力振動電極65に対応するアース電極66が形成されている。この圧電基板6では、3箇所のコーナー部分に入力端子67と出力端子68とアース端子69とが形成され、入力振動電極64は引き出し電極パターン610によって入力端子67に引き出され、出力振動電極65は引き出し電極パターン611によって出力端子68に引き出され、アース電極66は引き出し電極パターン612によってアース端子69に引き出されている。なお、入力端子57と出力端子68とは、基板61の対角線上に位置するコーナー部にそれぞれ形成され、アース端子69は残るコーナー部分の一角に形成されている。この圧電基板6は、入力端子67、出力端子68およびアース端子69が導電性接合材25によってベース7の電極パッド83,84,85に電気機械的に接合されることで、圧電基板6がベース7に設けられる。

【0031】

上記構成の圧電デバイス2では、圧電基板5,6をベース7に接合した後に、ベース7に蓋22を配し、窒素雰囲気下でシーム封止によりベース7と蓋22との接合を行う。このシーム封止により、ベース7と蓋22とが接合されて、圧電基板5,6が気密封止される。

【0032】

上記の圧電デバイス2を用いた帯域阻止フィルタ1のフィルタ回路11について図6を用いて説明する。

【0033】

本実施の形態にかかる圧電デバイス2では、1つのパッケージ21内に、3端子(入力端子57,67、出力端子58,68、アース端子59,69)を有する圧電基板5,6が並設されており、一方の圧電基板5の入力端子57と出力端子58と、他方の圧電基板6の入力端子67と出力端子68とが相互に直接接続され、一方の圧電基板5のアース端子59と他方の圧電基板6のアース端子69とが相互に接続されている。

【0034】

また、本実施の形態にかかる帯域阻止フィルタ1の一部構成であるマッチング回路31,32は、圧電デバイス2の入出力端子(符号57,67参照)にそれぞれ接続されるコンデンサ311,321およびインダクタ312,322からそれぞれ構成され、インダクタ312,322の一端が接地されている。このように、これらマッチング回路31,32は、LC回路で構成されている。このLC回路では、圧電デバイス2の入力端子(圧電基板5の入力端子57)にコンデンサ311が接続され、入力端子57とコンデンサ311間にインダクタ312の一端が接続され、インダクタ312の他端が接地されている。また、圧電デバイス2の出力端子(圧電基板6の入力端子67)にコンデンサ321が接続され、入力端子67とコンデンサ321間にインダクタ322の一端が接続され、インダクタ322の他端が接地されている。このようなLC回路の構成により、ハイパスフィルタが構成され、圧電デバイス2とLC回路のハイパスフィルタにより、周波数帯域の複数領域において信号を遮断することができる。

【0035】

また、本実施の形態にかかる帯域阻止フィルタ1の一部構成である容量部41,42は、圧電デバイス2のアース端子(符号59,69参照)にそれぞれ接続される容量部からなり、容量部41,42は接地されている。なお、本実施の形態では、容量部41に可変容量部のトリマーコンデンサを用い、容量部42にコンデンサ42を用いている。

【0036】

本実施の形態では、圧電デバイス2とマッチング回路31,32と容量部41,42とを、半田などの導電性接合材(図示省略)により無線機の回路基板に接合して図6に示す帯域阻止フィルタ1の回路を構成する。この帯域阻止フィルタ1による周波数の帯域阻止特性を図7〜9に示す。

【0037】

本実施の形態にかかる帯域阻止フィルタ1によれば、回路を複雑にせずに、図7〜9に示すように信号レベルの減衰の対象となる減衰周波数帯域における信号レベルの減衰量を大きくすることができる。なお、図7〜9は、横軸のスケールが異なるだけで、全て本実施の形態にかかる帯域阻止フィルタ1による信号レベルのデータから生成されたグラフである。

【0038】

また、上記の回路を構築した帯域阻止フィルタ1では、圧電基板5の入力端子57と出力端子58と、圧電基板6の入力端子67と出力端子68とを直接接続し、圧電基板5のアース端子59と圧電基板6のアース端子69とを接続しているので、不要な信号を取り除くことができ、図7〜9に示すように通過周波数帯域近傍の周波数帯域のみを急峻に減衰させることができる。これは、圧電基板5,6の特性に関係する効果であり、従前のLC回路のみを用いた帯域阻止フィルタでは、通過周波数帯域に影響を及ぼさずに通過周波数帯域近傍の周波数帯域のみを急峻に減衰させることができない。これに対して、本実施の形態にかかる帯域阻止フィルタ1によれば、例えば、減衰周波数帯域に対して±1kHzの周波数帯域において、減衰量を20dB以上確保することができ、このように、本実施の形態にかかる帯域阻止フィルタ1によれば、通過周波数帯域近傍の周波数帯域であっても所望の周波数帯域のみを急峻に減衰させることができる。

【0039】

また、圧電基板5の入力端子57と、圧電基板6の入力端子67と、にマッチング回路31,32が接続されるので、このことにより、減衰周波数帯域の減衰量を増大させることができ、挿入損失の改善を図ることができる。このような減衰量の増大および挿入損失の改善により、対象となる不要な信号やノイズの除去能力を向上させることができ、また所望の減衰特性を得ることができる。

【0040】

また、アース電極56,66が容量部41,42を介して接地されるので、容量部41,42により帯域阻止フィルタ1の周波数調整を行うことができ、また所望の減衰特性を得ることができる。

【0041】

また、本実施の形態にかかる帯域阻止フィルタ1では、2つの圧電基板5,6を用いて2つの入出力電極対を用いており、1つの入出力電極対を用いた場合と比較して約2倍(段数)の減衰量を持たせることができる。なお、入出力電極対の数に比例して減衰量を増加させることができるので、本実施の形態に限らず3つ以上の圧電基板を用いて3つ以上の入出力電極対を用いることが好ましいが、小型の帯域阻止フィルタ1を構成する場合、本実施の形態にかかる2つの入出力電極対が好適である。

【0042】

また、本実施の形態にかかる帯域阻止フィルタ1では、図7〜9に示すように、通過周波数帯域の低周波数側に隣接する信号レベルを減衰させたい時に特に有効である。

【0043】

なお、本実施の形態では、圧電基板5,6に水晶基板を用いているが、圧電材料であれば他の材料であってもよい。

【0044】

また、本実施の形態では、電子デバイスに無線機を適用しているが、無線機以外の電子デバイスであってもよく、例えば周波数の帯域阻止を必要とする電子デバイスであれば、本発明は適用可能である。

【0045】

また、本実施の形態にかかる帯域阻止フィルタ1では、2つの圧電基板5,6にそれぞれ3端子の電極構成を有しているが、これに限定されるものではなく、1つの圧電基板に複数の3端子の電極構成を設けてもよい。すなわち、圧電基板の一主面に複数の入出力電極対が形成され、他主面に複数の入出力電極対にそれぞれ対応した複数のアース電極が形成され、入出力電極対は、入力振動電極と出力振動電極とがギャップを有して配され、全ての入力振動電極及び出力振動電極が相互に接続されてもよい。具体的には、図10,11に示す圧電基板9を用いてもよい。図10,11に示す圧電基板9では、一主面91に2つの入出力電極対93,94が形成され、他主面92に2つの入出力電極対93,94にそれぞれ対応した2つのアース電極95,96が形成され、入出力電極対93,94は、それぞれ入力振動電極931,941と出力振動電極932,942とがギャップを有して配され、全ての入力振動電極931,941及び出力振動電極932,942が相互に接続されてもよい。この図10,11に示す圧電基板9を圧電デバイス2に設けることで、本実施の形態にかかる帯域阻止フィルタ1と同様の作用効果を有する。

【0046】

また、本実施の形態にかかる帯域阻止フィルタ1では、マッチング回路31,32を、コンデンサ311,321およびインダクタ312,322からそれぞれ構成しているが、これに限定されるものではなく、図12に示すような構成であってもよい。図12に示す帯域阻止フィルタ1では、マッチング回路31は、圧電デバイス2の入力端子に接続されたインダクタ313およびトリマーコンデンサ314から構成されており、トリマーコンデンサ314の一端は接地されている。また、マッチング回路32は、圧電デバイス2の出力端子に接続されたインダクタ323およびトリマーコンデンサ324から構成されており、トリマーコンデンサ324の一端は接地されている。また、この帯域阻止フィルタ1では、容量部42に可変容量部のトリマーコンデンサ42が用いられている。この図12に示すLC回路では、圧電デバイス2の入力端子(圧電基板5の入力端子57)にインダクタ313が接続され、入力端子57とインダクタ313間にトリマーコンデンサ314の一端が接続され、トリマーコンデンサ314の他端が接地されている。また、圧電デバイス2の出力端子(圧電基板6の入力端子67)にインダクタ323が接続され、入力端子57とインダクタ323間にトリマーコンデンサ324の一端が接続され、トリマーコンデンサ324の他端が接地されている。このようなLC回路の構成により、ローバスフィルタが構成され、圧電デバイス2とこのLC回路のローパスフィルタとにより、周波数帯域の複数領域において信号を遮断することができる。また、マッチング回路には減衰周波数域の減衰量の調整と、他の領域の減衰量調整の機能がある。

【0047】

この図12に示す帯域阻止フィルタ1では、図6に示す帯域阻止フィルタ1と異なり、図13〜15に示すように通過周波数帯域の高周波数側に隣接する信号レベルを減衰させるのに有効である。

【0048】

また、本実施の形態にかかる帯域阻止フィルタ1では、一方のアース端子59にトリマーコンデンサを接続し、他方のアース端子69にコンデンサを接続しているが、これに限定されるものではなく、図12に示すようにアース端子59,69に、一端が接地された容量部41,42であるトリマーコンデンサをそれぞれ接続してもよい。

【0049】

この図12に示す帯域阻止フィルタ1による減衰周波数帯域における信号レベルの減衰を示したグラフを図13〜15に示す。図13〜15に示すように、図12に示す帯域阻止フィルタ1によれば、回路を複雑にせずに、信号レベルの減衰の対象となる減衰周波数帯域における信号レベルの減衰量を大きくすることができる。なお、図13〜15は、横軸のスケールが異なるだけで、全て図12に示す帯域阻止フィルタ1による信号レベルのデータから生成されたグラフである。

【0050】

また、本実施の形態にかかる帯域阻止フィルタ1では、一方のアース端子59にトリマーコンデンサを接続し、他方のアース端子69にコンデンサを接続しているが、これに限定されるものではなく、他方のアース端子69にトリマーコンデンサを接続し、一方のアース端子59にコンデンサを接続してもよい。なお、本実施の形態に示すように、トリマーコンデンサの代わり固定コンデンサを用いてもよい。

【0051】

また、図6に示すフィルタ回路11では、圧電基板5の入力端子57と出力端子58と、圧電基板6の入力端子67と出力端子68とを直接接続しているが、これに限定されるものではなく、図16に示すように圧電基板5の入力端子57(圧電基板6の入力端子67)と圧電基板6の出力端子68(圧電基板5の出力端子58)とをインダクタ10を介して接続してもよい。この場合、2つの圧電基板5,6により、4つの圧電基板を用いた構成を構築することができ、その結果、信号レベルの減衰量を増加させるのにより好適である。

【0052】

この図16に示す帯域阻止フィルタ1による減衰周波数帯域における信号レベルの減衰を示したグラフを図17に示す。この図17に示すように、図16に示す帯域阻止フィルタ1によれば、回路を複雑にせずに、信号レベルの減衰の対象となる減衰周波数帯域における信号レベルの減衰量をさらに大きくすることができる。

【0053】

なお、上記の図8,14,17に示す帯域阻止フィルタ1による減衰周波数帯域における信号レベルの減衰を示したグラフでは、減衰周波数帯域の中央位置(図中の0点参照)からプラス側に位置する周波数帯域(約+200〜+700Hz)において、スプリアスが発生している。このスプリアスは、パッケージ7に圧電基板(5,6)が導電性接合材により収納保持(搭載)され、蓋22により気密封止された圧電デバイス2特有のスプリアスである。

【0054】

また、本実施の形態では、圧電デバイス2とマッチング回路31,32と容量部41,42とを別々に設けているが、これに限定されるものではなく、圧電デバイス2のパッケージ21内にマッチング回路31,32と容量部41,42との少なくとも一方を組み込んでもよい。しかしながら、圧電デバイス2のパッケージ21の小型化を考慮すると、本実施の形態が好ましい。

【0055】

また、本実施の形態では、無線機の回路基板に直接、圧電デバイス2とマッチング回路31,32と容量部41,42とを設けているが、これに限定されるものではなく、圧電デバイス2とマッチング回路31,32と容量部41,42とを設けた帯域阻止フィルタの回路基板を別途用い、この帯域阻止フィルタの回路基板を無線機の回路基板に接続してもよい。

【0056】

なお、本発明は、その精神や主旨または主要な特徴から逸脱することなく、他のいろいろな形で実施することができる。そのため、上述の実施例はあらゆる点で単なる例示にすぎず、限定的に解釈してはならない。本発明の範囲は特許請求の範囲によって示すものであって、明細書本文には、なんら拘束されない。さらに、特許請求の範囲の均等範囲に属する変形や変更は、全て本発明の範囲内のものである。

【産業上の利用可能性】

【0057】

本発明は、電子デバイスにおいて周波数の帯域阻止を行う帯域阻止フィルタに適用できる。

【符号の説明】

【0058】

1 帯域阻止フィルタ

11 フィルタ回路

2 圧電デバイス

21 パッケージ

22 蓋

23 接合材

24 内部空間

25 導電性接合材

31 マッチング回路

311 コンデンサ

312 インダクタ

313 インダクタ

314 トリマーコンデンサ

32 マッチング回路

321 コンデンサ

322 インダクタ

323 インダクタ

324 トリマーコンデンサ

41,42 容量部

5 圧電基板

51 基板

52 一主面

53 他主面

54 入力振動電極

55 出力振動電極

56 アース電極

57 入力端子

58 出力端子

59 アース端子

510 引き出し電極パターン

511 引き出し電極パターン

512 引き出し電極パターン

6 圧電基板

61 基板

62 一主面

63 他主面

64 入力振動電極

65 出力振動電極

66 アース電極

67 入力端子

68 出力端子

69 アース端子

610 引き出し電極パターン

611 引き出し電極パターン

612 引き出し電極パターン

7 ベース

71 底部

72 壁部

73 一主面

74 他主面

75 キャビティ

751 底面

761,762 ピット

77 キャスタレーション

8 電極

81,82,83,84,85,86 電極パッド

9 圧電基板

91 一主面

92 他主面

93 入出力電極対

931 入力振動電極

932 出力振動電極

95,96アース電極

94 入出力電極対

941 入力振動電極

942 出力振動電極

10 インダクタ

【特許請求の範囲】

【請求項1】

複数の圧電基板が気密封止された帯域阻止フィルタにおいて、

前記圧電基板には、一主面に入出力電極対が形成され、他主面に前記入出力電極対に対応したアース電極が形成され、

前記入出力電極対は、入力振動電極と出力振動電極とがギャップを有して前記一主面に配されてなり、

全ての前記圧電基板の入力振動電極及び出力振動電極が相互に接続されたことを特徴とする帯域阻止フィルタ。

【請求項2】

1つの圧電基板が気密封止された帯域阻止フィルタにおいて、

前記圧電基板には、一主面に複数の入出力電極対が形成され、他主面に複数の前記入出力電極対にそれぞれ対応した複数のアース電極が形成され、

前記入出力電極対は、入力振動電極と出力振動電極とがギャップを有して前記一主面に配されてなり、

全ての前記入力振動電極及び前記出力振動電極が相互に接続されたことを特徴とする帯域阻止フィルタ。

【請求項3】

請求項1または2に記載の帯域阻止フィルタにおいて、

前記圧電基板の入出力端子の少なくとも1つの端子にマッチング回路が接続されたことを特徴とする帯域阻止フィルタ。

【請求項4】

請求項1または2に記載の帯域阻止フィルタにおいて、

前記アース電極は、容量部を介して接地されたことを特徴とする帯域阻止フィルタ。

【請求項1】

複数の圧電基板が気密封止された帯域阻止フィルタにおいて、

前記圧電基板には、一主面に入出力電極対が形成され、他主面に前記入出力電極対に対応したアース電極が形成され、

前記入出力電極対は、入力振動電極と出力振動電極とがギャップを有して前記一主面に配されてなり、

全ての前記圧電基板の入力振動電極及び出力振動電極が相互に接続されたことを特徴とする帯域阻止フィルタ。

【請求項2】

1つの圧電基板が気密封止された帯域阻止フィルタにおいて、

前記圧電基板には、一主面に複数の入出力電極対が形成され、他主面に複数の前記入出力電極対にそれぞれ対応した複数のアース電極が形成され、

前記入出力電極対は、入力振動電極と出力振動電極とがギャップを有して前記一主面に配されてなり、

全ての前記入力振動電極及び前記出力振動電極が相互に接続されたことを特徴とする帯域阻止フィルタ。

【請求項3】

請求項1または2に記載の帯域阻止フィルタにおいて、

前記圧電基板の入出力端子の少なくとも1つの端子にマッチング回路が接続されたことを特徴とする帯域阻止フィルタ。

【請求項4】

請求項1または2に記載の帯域阻止フィルタにおいて、

前記アース電極は、容量部を介して接地されたことを特徴とする帯域阻止フィルタ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2012−142740(P2012−142740A)

【公開日】平成24年7月26日(2012.7.26)

【国際特許分類】

【出願番号】特願2010−293235(P2010−293235)

【出願日】平成22年12月28日(2010.12.28)

【出願人】(000149734)株式会社大真空 (312)

【Fターム(参考)】

【公開日】平成24年7月26日(2012.7.26)

【国際特許分類】

【出願日】平成22年12月28日(2010.12.28)

【出願人】(000149734)株式会社大真空 (312)

【Fターム(参考)】

[ Back to top ]