帰還型発振装置

【課題】発振開始時の立ち上がりを迅速に行うとともに、増幅素子に流れるバイアス電流を適正化すること。

【解決手段】準ミリ波帯域またはミリ波帯域を発振周波数帯域とする帰還型発振装置1において、入力端子から入力された信号を出力端子から出力する増幅素子(HEMT10)と、増幅素子の出力端子から入力端子に信号を帰還するための帰還回路(帰還回路40)と、増幅素子の出力端子と電源の間に挿入され、持続発振時に増幅素子に流れるバイアス電流を制限する抵抗素子(抵抗素子35)と、を有する。

【解決手段】準ミリ波帯域またはミリ波帯域を発振周波数帯域とする帰還型発振装置1において、入力端子から入力された信号を出力端子から出力する増幅素子(HEMT10)と、増幅素子の出力端子から入力端子に信号を帰還するための帰還回路(帰還回路40)と、増幅素子の出力端子と電源の間に挿入され、持続発振時に増幅素子に流れるバイアス電流を制限する抵抗素子(抵抗素子35)と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、帰還型発振装置に関するものである。

【背景技術】

【0002】

近年、高速かつ大容量の無線通信の需要が高まっており、このような需要を満たすことができる、準ミリ波およびミリ波を用いた無線通信への期待が高まっている。

【0003】

従来において、このようなミリ波帯域の発振を行うための発振装置としては、例えば、特許文献1に示すような技術が知られている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5−110338号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、これらの帯域で発振を行う帰還型の発振装置では、発振動作時には増幅素子の出力端子からの出力信号の一部が入力信号として入力端子に帰還される。発振開始時の立ち上がりを迅速にするとともに、環境変化に拘わらず安定して発振を行うためには、この帰還に係るループゲインをある程度高く設定することが望ましい。しかしながら、ループゲインを高く設定すると、持続発振時(定常動作時)において増幅素子に流れるバイアス電流の値が大きくなり、増幅素子の寿命を短縮したり、場合によっては増幅素子の故障を招来したりするという問題点がある。

【0006】

そこで、本発明は発振開始時の立ち上がりを迅速に行うとともに、増幅素子に流れるバイアス電流を適正化することが可能な帰還型発振装置を提供することを目的としている。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明は、準ミリ波帯域またはミリ波帯域を発振周波数帯域とする帰還型発振装置において、入力端子から入力された信号を出力端子から出力する増幅素子と、前記増幅素子の前記出力端子から前記入力端子に信号を帰還するための帰還回路と、前記増幅素子の前記出力端子と電源の間に挿入され、持続発振時に前記増幅素子に流れるバイアス電流を制限する抵抗素子と、を有することを特徴とする。

このような構成によれば、発振開始時の立ち上がりを迅速に行うとともに、増幅素子に流れるバイアス電流を適正化することが可能となる。

【0008】

また、他の発明は、上記発明に加えて、前記抵抗素子の抵抗値をRrとし、前記増幅素子の持続発振時における内部等価抵抗の抵抗値をRsとし、前記増幅素子の前記出力端子に印加される前記電源の電圧値をVとし、前記持続発振時において前記電源から前記増幅素子の出力端子に流れる電流をIsとし、前記増幅素子の初期状態における内部等価抵抗の抵抗値をRiとし、初期状態において前記電源から前記増幅素子の出力端子に流れる電流値をIiとし、前記増幅素子の出力端子へ流れる電流の安全動作電流上限値をIsmaxとする場合、これらの間に以下の関係が成立する、

V/(Rs+Rr)=Is

V=Ii×(Ri+Rr)

但し、Ri×0.5<Rs<Ri

Is<Ismax

ことを特徴とする。

このような構成によれば、過剰な電流が流れることによる増幅素子の劣化を抑え、持続発振時においてもバイアス電流を確実に適正な範囲に保つことが可能となり、周囲環境の変化などによりループゲインが減少した際でも発振条件を確保し、かつ、発振の立ち上がりを迅速に行うことが可能になる。

【0009】

また、他の発明は、上記発明に加えて、前記増幅素子は高電子移動度トランジスタによって構成されていることを特徴とする。

このような構成によれば、準ミリ波またはミリ波帯域において安定した発振を継続して行うことができる。

【発明の効果】

【0010】

本発明によれば、発振開始時の立ち上がりを迅速に行うとともに、増幅素子に流れるバイアス電流を適正化することが可能な帰還型発振装置を提供することが可能となる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施形態に係る帰還型発振装置の構成例を示すブロック図である。

【図2】本発明の実施形態に係る帰還型発振装置の構成例を示す回路図である。

【図3】図2の回路において抵抗素子を有しない場合の回路図である。

【図4】図3の回路におけるループゲインとドレイン電流の関係を示す図である。

【図5】図2の回路において抵抗素子および電源電圧を変更した場合のループゲインとドレイン電流の関係を示す図である。

【発明を実施するための形態】

【0012】

次に、本発明の実施形態について説明する。

【0013】

(A)実施形態の構成の説明

図1は、本発明の実施形態に係る帰還型発振装置の構成例を示すブロック図である。この図1に示すように、帰還型発振装置1は、HEMT(High Electron Mobility Transistor)10、バイアス回路20,30、および、帰還回路40を主要な構成要素としている。なお、帰還型発振装置1は、周波数が30〜300GHzで波長が10〜1mm程度であるミリ波帯域または10〜30GHz程度の準ミリ波帯域を発振周波数としている。

【0014】

ここで、HEMT10(請求の範囲における「増幅素子」に対応)は、高電子移動度トランジスタとも称される増幅素子であり、半導体のヘテロ接合の界面に発生する、高い移動度(変調ドープ構造)の電子を利用する電界効果トランジスタである。図1の例では、HEMT10の入力端子であるゲート(G)端子はバイアス回路20および帰還回路40の一方の端子に接続され、ソース(S)端子は接地され、出力端子であるドレイン(D)端子はバイアス回路30および帰還回路40の他方の端子に接続されている。

【0015】

バイアス回路20はゲート端子にバイアス電圧を供給する。バイアス回路30は、ドレイン端子にバイアス電流を供給する。帰還回路40(請求の範囲における「帰還回路」に対応)は、出力端子であるドレイン端子に現れる出力信号の一部を入力端子であるドレイン端子に帰還させる。

【0016】

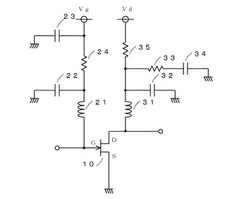

図2は、図1に示すブロック図の詳細な構成例を示す回路図である。この図2に示すように、本実施形態に係る帰還型発振装置1は、HEMT10、インダクタ素子21,31、キャパシタ素子22,23,32,34、および、抵抗素子24,33,35を有している。

【0017】

ここで、インダクタ素子21、キャパシタ素子22,23、および、抵抗素子24は、図1に示すバイアス回路20を構成する。インダクタ素子31、キャパシタ素子32,34、ならびに、抵抗素子33および抵抗素子35(請求の範囲における「抵抗素子」に対応)は、図1に示すバイアス回路30を構成する。図2に示す回路は、例えば、マイクロストリップラインおよびスルーホール等の平面回路を用いて、多層基板により構成される。なお、図2では図1に示すループ回路帰還回路40は説明を簡略化するために省略している。

【0018】

ここで、インダクタ素子21は、例えば、マイクロストリップラインまたはチップ部品によって構成され、一方の端子(以下、単に「一端」と称する)がHEMT10のゲート端子に接続され、他方の端子(以下、単に「他端」と称する)がキャパシタ素子22の一端および抵抗素子24の一端に接続されている。インダクタ素子21はHEMT10から流入する高周波信号を減衰させる。キャパシタ素子22は、一端がインダクタ素子21の他端、抵抗素子24の一端に接続され、他端が接地されている。キャパシタ素子23は、一端が抵抗素子24の他端に接続され、他端が接地されている。これらキャパシタ素子21,22は、バイパスキャパシタであり、高周波信号をグランドに対して逃がす機能を有している。抵抗素子24は、一端がインダクタ素子21の他端、キャパシタ素子22の一端に接続され、他端がキャパシタ素子23の一端、および、電源Vgに接続されている。

【0019】

インダクタ素子31は、前述の場合と同様にマイクロストリップラインまたはチップ部品によって構成され、一端がHEMT10のドレイン端子に接続され、他端がキャパシタ素子32の一端、抵抗素子33の一端、および、抵抗素子35の一端に接続されている。インダクタ素子31はHEMT10から流入する高周波信号を減衰させる。キャパシタ素子32は、一端がインダクタ素子31の他端、抵抗素子33の一端、および、抵抗素子35の一端に接続され、他端が接地されている。キャパシタ素子34は、一端が抵抗素子33の他端に接続され、他端が接地されている。これらキャパシタ素子32,34は、バイパスコンデンサであり、高周波信号をグランドに対して逃がす機能を有する。抵抗素子33は、一端がインダクタ素子21の他端、キャパシタ素子32の一端、および、抵抗素子35の一端に接続され、他端がキャパシタ素子34の一端に接続されている。抵抗素子35は、一端がインダクタ素子31の他端、キャパシタ素子32の一端、および、抵抗素子33の一端に接続され、他端が電源Vdに接続されている。なお、この抵抗素子35は、HEMT10のドレインに流れるバイアス電流を制限するための抵抗素子である。

【0020】

本実施形態では、抵抗素子35をドレイン端子の電源ラインに挿入したことを特徴としている。そこで、抵抗素子35を挿入していない図3の例との比較に基づいて、本実施形態に係る帰還型発振装置1の動作について説明する。まず、図3に示す回路の発振原理について簡単に説明する。図3に示す回路において、発振が開始されると、HEMT10で増幅された出力信号が帰還回路40を介して帰還され、HEMT10のゲート端子に再び入力される。そして、入力された信号は再び増幅されて出力され、再度、帰還されて繰り返し増幅される。しかしながら、信号は無限に増幅されるのではなく、HEMT10に入力される信号の電力が増大すると、HEMT10自体の利得が圧縮されること(振幅制限効果)により、ループゲインが0dBになるポイントで平衡状態となり、帰還型発振装置1は定常動作状態となる。なお、帰還回路40は所定の周波数の信号のみを選択的に帰還させることから、帰還回路40によって選択される周波数の信号が発振信号として出力されることになる。

【0021】

ところで、図3に示す回路において、発振停止状態から速やかに発振状態に移行するとともに、温度等の環境変化に拘わらず安定した発振状態を維持するためには、HEMT10および帰還回路40によって形成されるループのループゲイン(利得圧縮量)をある程度確保する必要がある(例えば、数dB程度確保する必要がある)。ループゲインを確保するためには、HEMT10のゲインを確保する必要がある。ここで、HEMT10のゲインは、相互コンダクタンスgmによって決定されるが、当該相互コンダクタンスgmは、ドレイン電流Idの増加に応じて増加する関係を有している。このため、HEMT10のゲインを確保するためにはドレイン電流Idをある程度流すことが必要になる。

【0022】

図3の回路のドレイン電流Idは、HEMT10のドレイン−ソース間の内部等価抵抗(ドレイン−ソース間に印加される電圧と流れる電流によって求められる等価的な抵抗)をRとし、ドレイン端子に印加する電源電圧をVdとすると、以下の式(1)によって求められる。なお、ゲート端子へ印加する電源電圧Vgは一定とする。

Id=Vd/R ・・・(1)

【0023】

したがって、ある程度のドレイン電流Idを流すためには、電源電圧Vd(請求の範囲における「電源の電圧値V」に対応)を調整して所望の電流が流れるようにする必要がある。ところで、帰還型発振装置1では、持続発振状態(発振が持続した状態)になると、ドレイン−ソース間の等価抵抗の値が減少する。すなわち、初期状態(発振していない状態)における等価抵抗をRiとし、持続発振時の等価抵抗をRsとすると、これらの関係は

Ri×0.5< Rs < Ri ・・・(2)

と表すことが出来る。このため、前述した式(1)は、初期状態におけるドレイン電流をIdiとし、持続発振時のドレイン電流をIdsとすると、Idi=Vd/Riであり、Ids=Vd/Rsとなることから持続発振時にはドレイン電流が増加する。ここで、HEMT10の消費電力Pは、以下の式(3)で表される。

P=Vd2/R ・・・(3)

【0024】

このため、初期状態の消費電力(バイアス電流による消費電力)はPi=Vd2/Riとなり、また、持続発振時の消費電力はPs=Vd2/Rsとなり、Pi<Psとなる。このため、持続発振時には、消費電力が増加することから、HEMT10に負担がかかって寿命が短くなったり、場合によっては、HEMT10が損傷したりする場合があった。

【0025】

そこで、本実施形態に係る帰還型発振装置1では、電源Vdとドレイン端子との間に電流制限用の抵抗素子35を直列に挿入している。ここで、この抵抗素子35の抵抗値をRrとすると、初期状態における式(1)は、式(4)のようになり、持続発振時は式(5)のようになる。

Idi=Vd/(Ri+Rr) ・・・(4)

Ids=Vd/(Rs+Rr) ・・・(5)

【0026】

持続発振時の消費電力Psは、以下の式(6)で表される。

Ps=Vd2/(Rs+Rr) ・・・(6)

【0027】

この消費電力PsがHEMT10の安全動作領域に属していれば、HEMT10は安全に動作する。したがって、消費電力Psが安全動作領域に属するとともに、発振前(初期状態)におけるループゲインが所望の値(例えば、数dB程度)になるように、VdおよびRrを決めればよい。

【0028】

なお、Rrの範囲は以下の式(9)で表される。

式(5)から

Ri=(Vd/Idi)−Rr ・・・(7)

と展開でき、これを式(2)へ代入すると

0.5×{(Vd/Idi)−Rr}< Rs <(Vd/Idi)−Rr・・・(8)

となる。

式(8)を展開して

(Vd/Idi)−2Rs< Rr < (Vd/Idi)−Rs ・・・(9)

となる。

【0029】

従って、本実施形態では、前述の条件を満たす抵抗素子Rrをドレイン端子と電源Vdの間に直列に挿入することにより、持続発振時においてもHEMT10は安全動作領域内において動作するので、例えば、素子の寿命が短縮したり、あるいは、素子が破損したりすることを防止できる。

【0030】

つぎに、より具体的な構成例について説明する。例えば、図3に示す回路において、HEMT10の安全動作領域(または推奨動作領域)がId<15mA(請求の範囲における「安全動作電流上限値Ismax」に対応)である場合に、ループゲインを3dB確保する場合を考える。図4は、図3の回路のループゲインとドレイン電流との関係を示すグラフである。この図に示すように、抵抗Rrを有しない場合、ループゲインを3dB確保するには、Id>15mAとなり、安全動作領域を超えてしまう。

【0031】

一方、図2に示す本実施形態の場合、抵抗Rrの値を変更することにより、ドレイン電流とループゲインの関係を調整することができる。図5は、抵抗Rrおよび電源電圧Vdを変更した場合におけるループゲインとドレイン電流の関係を示す図である。この例では、各曲線は、抵抗Rrの値を、0,10,20,50,100Ωに設定するとともに、電源電圧Vdを2.0,2.1,2.2,2.5,3.0Vに設定した場合におけるループゲインとドレイン電流の関係をそれぞれ示している。この図に示すように、抵抗Rr=50Ω、電圧Vd=2.5Vの場合、および、抵抗Rr=100Ω、電圧Vd=3.0Vの場合にループゲインが3dBにおいてドレイン電流が安全動作領域に属する15mA以下となっている。このため、この図から、抵抗Rrを50Ω程度よりも大きくするとともに、電圧Vdを2.5程度よりも大きくすることで、所望のループゲインを得るとともに、安全動作領域内でHEMT10を動作させることができる。

【0032】

これは、以下の式によって表すことができる。式(4)より

Vd=Idi×(Ri+Rr) ・・・(10)

ここで、Idi=10mA(請求の範囲における「電流値Ii」に対応)、Ri=200Ωとすると、式(10)は、以下の式(11)で表される。

Vd=0.01×(200+Rr) ・・・(11)

【0033】

式(11)を式(5)に代入すると、以下の式(12)を得る。

Ids=Vd/(Rs+Rr)

=0.01×(200+Rr)/(Rs+Rr)<0.015 ・・・(12)

【0034】

式(12)を展開すると、以下の式(13)を得る。

400−3×Rs<Rr ・・・(13)

【0035】

ここで、図4から、ループゲインが3dBのときのRsは、約122Ω(=2.0V/16.4mA)となるので、Rs=122Ωを式(13)に代入すると、33Ω<Rrとなる。

【0036】

したがって、以上の式から、Rr>33Ωとなるように設定すればよい。また、電圧Vdについては式(11)から、Vd>2.33Vとなるように設定すればよい。

【0037】

以上に説明したように、本実施形態では、準ミリ波帯域またはミリ波帯域の帰還型発振装置1のドレイン端子と電源Vdとの間に抵抗素子35を挿入するようにしたので、持続発振時における電流を制限することで、HEMT10への負担を軽減することができる。

【0038】

また、抵抗素子35を挿入するとともに、電源電圧Vdを調整することにより、HEMT10への負担を軽減しつつ、ループゲインを確保することができる。これにより、発振開始時の発振の立ち上がりを迅速に行うことができる。

【0039】

また、本実施形態では、抵抗素子35の素子値と電源電圧Vdの電圧を調整することで、ループゲインに対する消費電流量が調整可能になるので、様々な制約条件が多い高周波数帯域においても高いループゲインを得ることができる。また、これに伴い、採用部品や構成を含めた帰還回路の設計の自由度を高くすることができる。

【0040】

なお、バイアス回路に抵抗を直列に挿入することは、電力損失の増大による出力の低下を意味する。すなわち、バイアス回路での電圧降下によりバイアス条件が変化して利得や出力が低減する。このため、バイアス回路に直列に抵抗を挿入することは、当業者であれば回避していた。しかしながら、本実施形態では敢えて抵抗を直列に挿入し、電源電圧と抵抗値によってゲインと電流値を調整するようにすることで、電力損失は生じるものの、それ以上に、安定的な発振と増幅素子への負荷の軽減を図るという特段の効果が期待できる。

【0041】

(D)変形実施形態の説明

以上の実施形態は一例であって、本発明が上述したような場合のみに限定されるものでないことはいうまでもない。例えば、以上の実施形態では、HEMTを増幅素子として用いるようにしたが、HEMT以外の増幅素子(例えば、MMIC(Monolithic Microwave Integrated Circuit)等)を用いることも可能である。

【0042】

また、以上の実施形態では、ノイズ除去用またはバイパスコンデンサとしてのキャパシタ素子22,23,32,34、抵抗素子33、および、インダクタ素子21,31を用いるようにしたが、これらについては使用目的や使用環境によっては除外するようにしてもよい。

【0043】

また、以上の実施形態では、V/(Rs+Rr)<Is<Ismaxとなるように電源電圧を設定するようにしたが、V/(Rs+Rr)≒Ismaxとなるように設定した場合、または、0.8×Ismax<V/(Rs+Rr)<Ismaxとなるように設定した場合に、本願の効果が顕著となり、HEMT10への負担を軽減しつつループゲインを確保することができる。

【0044】

また、以上の実施形態では、抵抗素子35については、単一の抵抗素子を用いることを想定しているが、例えば、複数の抵抗素子を直列または並列接続するようにしてもよい。例えば、並列接続する場合、並列する抵抗素子の値を調整することで、HEMT10のバラツキに対応することができる。

【0045】

また、図4および図5に示すグラフは、一例であって、HEMT10の種類によってはこれらの図とは異なる特性を有するので、個々のHEMT10の種類に応じて適切なドレイン電流、ループゲイン、および、抵抗値等を設定する必要がある。

【0046】

また、以上の実施形態では、帰還型発振装置1は、継続的に発振する場合を想定して説明を行った。しかしながら、例えば、UWB(Ultra Wide Band)レーダの場合では、短期間のパルス発振を行うので、短期間の発振の場合にはそれに対応してループゲインやドレイン電流を設定するようにしてもよい。具体的には、短期間の発振を行う場合には、発振開始時の立ち上がりが重要になるので、例えば、前述の例では、ループゲインを3dBに設定するようにしたが、3dBを超えるゲインに設定するようにしてもよい。また、短期間発振する場合には継続的に発振する場合に比較して、発熱も断続的になるので、ドレイン電流についても継続的発振の場合に比較して多少高めに設定するようにしてもよい。

【符号の説明】

【0047】

1 帰還型発振装置

10 HEMT(増幅素子)

20 バイアス回路

21 インダクタ素子

22,23 キャパシタ素子

24 抵抗素子

30 バイアス回路

31 インダクタ素子

32,34 キャパシタ素子

33 抵抗素子

35 抵抗素子

40 帰還回路

【技術分野】

【0001】

本発明は、帰還型発振装置に関するものである。

【背景技術】

【0002】

近年、高速かつ大容量の無線通信の需要が高まっており、このような需要を満たすことができる、準ミリ波およびミリ波を用いた無線通信への期待が高まっている。

【0003】

従来において、このようなミリ波帯域の発振を行うための発振装置としては、例えば、特許文献1に示すような技術が知られている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5−110338号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、これらの帯域で発振を行う帰還型の発振装置では、発振動作時には増幅素子の出力端子からの出力信号の一部が入力信号として入力端子に帰還される。発振開始時の立ち上がりを迅速にするとともに、環境変化に拘わらず安定して発振を行うためには、この帰還に係るループゲインをある程度高く設定することが望ましい。しかしながら、ループゲインを高く設定すると、持続発振時(定常動作時)において増幅素子に流れるバイアス電流の値が大きくなり、増幅素子の寿命を短縮したり、場合によっては増幅素子の故障を招来したりするという問題点がある。

【0006】

そこで、本発明は発振開始時の立ち上がりを迅速に行うとともに、増幅素子に流れるバイアス電流を適正化することが可能な帰還型発振装置を提供することを目的としている。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明は、準ミリ波帯域またはミリ波帯域を発振周波数帯域とする帰還型発振装置において、入力端子から入力された信号を出力端子から出力する増幅素子と、前記増幅素子の前記出力端子から前記入力端子に信号を帰還するための帰還回路と、前記増幅素子の前記出力端子と電源の間に挿入され、持続発振時に前記増幅素子に流れるバイアス電流を制限する抵抗素子と、を有することを特徴とする。

このような構成によれば、発振開始時の立ち上がりを迅速に行うとともに、増幅素子に流れるバイアス電流を適正化することが可能となる。

【0008】

また、他の発明は、上記発明に加えて、前記抵抗素子の抵抗値をRrとし、前記増幅素子の持続発振時における内部等価抵抗の抵抗値をRsとし、前記増幅素子の前記出力端子に印加される前記電源の電圧値をVとし、前記持続発振時において前記電源から前記増幅素子の出力端子に流れる電流をIsとし、前記増幅素子の初期状態における内部等価抵抗の抵抗値をRiとし、初期状態において前記電源から前記増幅素子の出力端子に流れる電流値をIiとし、前記増幅素子の出力端子へ流れる電流の安全動作電流上限値をIsmaxとする場合、これらの間に以下の関係が成立する、

V/(Rs+Rr)=Is

V=Ii×(Ri+Rr)

但し、Ri×0.5<Rs<Ri

Is<Ismax

ことを特徴とする。

このような構成によれば、過剰な電流が流れることによる増幅素子の劣化を抑え、持続発振時においてもバイアス電流を確実に適正な範囲に保つことが可能となり、周囲環境の変化などによりループゲインが減少した際でも発振条件を確保し、かつ、発振の立ち上がりを迅速に行うことが可能になる。

【0009】

また、他の発明は、上記発明に加えて、前記増幅素子は高電子移動度トランジスタによって構成されていることを特徴とする。

このような構成によれば、準ミリ波またはミリ波帯域において安定した発振を継続して行うことができる。

【発明の効果】

【0010】

本発明によれば、発振開始時の立ち上がりを迅速に行うとともに、増幅素子に流れるバイアス電流を適正化することが可能な帰還型発振装置を提供することが可能となる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施形態に係る帰還型発振装置の構成例を示すブロック図である。

【図2】本発明の実施形態に係る帰還型発振装置の構成例を示す回路図である。

【図3】図2の回路において抵抗素子を有しない場合の回路図である。

【図4】図3の回路におけるループゲインとドレイン電流の関係を示す図である。

【図5】図2の回路において抵抗素子および電源電圧を変更した場合のループゲインとドレイン電流の関係を示す図である。

【発明を実施するための形態】

【0012】

次に、本発明の実施形態について説明する。

【0013】

(A)実施形態の構成の説明

図1は、本発明の実施形態に係る帰還型発振装置の構成例を示すブロック図である。この図1に示すように、帰還型発振装置1は、HEMT(High Electron Mobility Transistor)10、バイアス回路20,30、および、帰還回路40を主要な構成要素としている。なお、帰還型発振装置1は、周波数が30〜300GHzで波長が10〜1mm程度であるミリ波帯域または10〜30GHz程度の準ミリ波帯域を発振周波数としている。

【0014】

ここで、HEMT10(請求の範囲における「増幅素子」に対応)は、高電子移動度トランジスタとも称される増幅素子であり、半導体のヘテロ接合の界面に発生する、高い移動度(変調ドープ構造)の電子を利用する電界効果トランジスタである。図1の例では、HEMT10の入力端子であるゲート(G)端子はバイアス回路20および帰還回路40の一方の端子に接続され、ソース(S)端子は接地され、出力端子であるドレイン(D)端子はバイアス回路30および帰還回路40の他方の端子に接続されている。

【0015】

バイアス回路20はゲート端子にバイアス電圧を供給する。バイアス回路30は、ドレイン端子にバイアス電流を供給する。帰還回路40(請求の範囲における「帰還回路」に対応)は、出力端子であるドレイン端子に現れる出力信号の一部を入力端子であるドレイン端子に帰還させる。

【0016】

図2は、図1に示すブロック図の詳細な構成例を示す回路図である。この図2に示すように、本実施形態に係る帰還型発振装置1は、HEMT10、インダクタ素子21,31、キャパシタ素子22,23,32,34、および、抵抗素子24,33,35を有している。

【0017】

ここで、インダクタ素子21、キャパシタ素子22,23、および、抵抗素子24は、図1に示すバイアス回路20を構成する。インダクタ素子31、キャパシタ素子32,34、ならびに、抵抗素子33および抵抗素子35(請求の範囲における「抵抗素子」に対応)は、図1に示すバイアス回路30を構成する。図2に示す回路は、例えば、マイクロストリップラインおよびスルーホール等の平面回路を用いて、多層基板により構成される。なお、図2では図1に示すループ回路帰還回路40は説明を簡略化するために省略している。

【0018】

ここで、インダクタ素子21は、例えば、マイクロストリップラインまたはチップ部品によって構成され、一方の端子(以下、単に「一端」と称する)がHEMT10のゲート端子に接続され、他方の端子(以下、単に「他端」と称する)がキャパシタ素子22の一端および抵抗素子24の一端に接続されている。インダクタ素子21はHEMT10から流入する高周波信号を減衰させる。キャパシタ素子22は、一端がインダクタ素子21の他端、抵抗素子24の一端に接続され、他端が接地されている。キャパシタ素子23は、一端が抵抗素子24の他端に接続され、他端が接地されている。これらキャパシタ素子21,22は、バイパスキャパシタであり、高周波信号をグランドに対して逃がす機能を有している。抵抗素子24は、一端がインダクタ素子21の他端、キャパシタ素子22の一端に接続され、他端がキャパシタ素子23の一端、および、電源Vgに接続されている。

【0019】

インダクタ素子31は、前述の場合と同様にマイクロストリップラインまたはチップ部品によって構成され、一端がHEMT10のドレイン端子に接続され、他端がキャパシタ素子32の一端、抵抗素子33の一端、および、抵抗素子35の一端に接続されている。インダクタ素子31はHEMT10から流入する高周波信号を減衰させる。キャパシタ素子32は、一端がインダクタ素子31の他端、抵抗素子33の一端、および、抵抗素子35の一端に接続され、他端が接地されている。キャパシタ素子34は、一端が抵抗素子33の他端に接続され、他端が接地されている。これらキャパシタ素子32,34は、バイパスコンデンサであり、高周波信号をグランドに対して逃がす機能を有する。抵抗素子33は、一端がインダクタ素子21の他端、キャパシタ素子32の一端、および、抵抗素子35の一端に接続され、他端がキャパシタ素子34の一端に接続されている。抵抗素子35は、一端がインダクタ素子31の他端、キャパシタ素子32の一端、および、抵抗素子33の一端に接続され、他端が電源Vdに接続されている。なお、この抵抗素子35は、HEMT10のドレインに流れるバイアス電流を制限するための抵抗素子である。

【0020】

本実施形態では、抵抗素子35をドレイン端子の電源ラインに挿入したことを特徴としている。そこで、抵抗素子35を挿入していない図3の例との比較に基づいて、本実施形態に係る帰還型発振装置1の動作について説明する。まず、図3に示す回路の発振原理について簡単に説明する。図3に示す回路において、発振が開始されると、HEMT10で増幅された出力信号が帰還回路40を介して帰還され、HEMT10のゲート端子に再び入力される。そして、入力された信号は再び増幅されて出力され、再度、帰還されて繰り返し増幅される。しかしながら、信号は無限に増幅されるのではなく、HEMT10に入力される信号の電力が増大すると、HEMT10自体の利得が圧縮されること(振幅制限効果)により、ループゲインが0dBになるポイントで平衡状態となり、帰還型発振装置1は定常動作状態となる。なお、帰還回路40は所定の周波数の信号のみを選択的に帰還させることから、帰還回路40によって選択される周波数の信号が発振信号として出力されることになる。

【0021】

ところで、図3に示す回路において、発振停止状態から速やかに発振状態に移行するとともに、温度等の環境変化に拘わらず安定した発振状態を維持するためには、HEMT10および帰還回路40によって形成されるループのループゲイン(利得圧縮量)をある程度確保する必要がある(例えば、数dB程度確保する必要がある)。ループゲインを確保するためには、HEMT10のゲインを確保する必要がある。ここで、HEMT10のゲインは、相互コンダクタンスgmによって決定されるが、当該相互コンダクタンスgmは、ドレイン電流Idの増加に応じて増加する関係を有している。このため、HEMT10のゲインを確保するためにはドレイン電流Idをある程度流すことが必要になる。

【0022】

図3の回路のドレイン電流Idは、HEMT10のドレイン−ソース間の内部等価抵抗(ドレイン−ソース間に印加される電圧と流れる電流によって求められる等価的な抵抗)をRとし、ドレイン端子に印加する電源電圧をVdとすると、以下の式(1)によって求められる。なお、ゲート端子へ印加する電源電圧Vgは一定とする。

Id=Vd/R ・・・(1)

【0023】

したがって、ある程度のドレイン電流Idを流すためには、電源電圧Vd(請求の範囲における「電源の電圧値V」に対応)を調整して所望の電流が流れるようにする必要がある。ところで、帰還型発振装置1では、持続発振状態(発振が持続した状態)になると、ドレイン−ソース間の等価抵抗の値が減少する。すなわち、初期状態(発振していない状態)における等価抵抗をRiとし、持続発振時の等価抵抗をRsとすると、これらの関係は

Ri×0.5< Rs < Ri ・・・(2)

と表すことが出来る。このため、前述した式(1)は、初期状態におけるドレイン電流をIdiとし、持続発振時のドレイン電流をIdsとすると、Idi=Vd/Riであり、Ids=Vd/Rsとなることから持続発振時にはドレイン電流が増加する。ここで、HEMT10の消費電力Pは、以下の式(3)で表される。

P=Vd2/R ・・・(3)

【0024】

このため、初期状態の消費電力(バイアス電流による消費電力)はPi=Vd2/Riとなり、また、持続発振時の消費電力はPs=Vd2/Rsとなり、Pi<Psとなる。このため、持続発振時には、消費電力が増加することから、HEMT10に負担がかかって寿命が短くなったり、場合によっては、HEMT10が損傷したりする場合があった。

【0025】

そこで、本実施形態に係る帰還型発振装置1では、電源Vdとドレイン端子との間に電流制限用の抵抗素子35を直列に挿入している。ここで、この抵抗素子35の抵抗値をRrとすると、初期状態における式(1)は、式(4)のようになり、持続発振時は式(5)のようになる。

Idi=Vd/(Ri+Rr) ・・・(4)

Ids=Vd/(Rs+Rr) ・・・(5)

【0026】

持続発振時の消費電力Psは、以下の式(6)で表される。

Ps=Vd2/(Rs+Rr) ・・・(6)

【0027】

この消費電力PsがHEMT10の安全動作領域に属していれば、HEMT10は安全に動作する。したがって、消費電力Psが安全動作領域に属するとともに、発振前(初期状態)におけるループゲインが所望の値(例えば、数dB程度)になるように、VdおよびRrを決めればよい。

【0028】

なお、Rrの範囲は以下の式(9)で表される。

式(5)から

Ri=(Vd/Idi)−Rr ・・・(7)

と展開でき、これを式(2)へ代入すると

0.5×{(Vd/Idi)−Rr}< Rs <(Vd/Idi)−Rr・・・(8)

となる。

式(8)を展開して

(Vd/Idi)−2Rs< Rr < (Vd/Idi)−Rs ・・・(9)

となる。

【0029】

従って、本実施形態では、前述の条件を満たす抵抗素子Rrをドレイン端子と電源Vdの間に直列に挿入することにより、持続発振時においてもHEMT10は安全動作領域内において動作するので、例えば、素子の寿命が短縮したり、あるいは、素子が破損したりすることを防止できる。

【0030】

つぎに、より具体的な構成例について説明する。例えば、図3に示す回路において、HEMT10の安全動作領域(または推奨動作領域)がId<15mA(請求の範囲における「安全動作電流上限値Ismax」に対応)である場合に、ループゲインを3dB確保する場合を考える。図4は、図3の回路のループゲインとドレイン電流との関係を示すグラフである。この図に示すように、抵抗Rrを有しない場合、ループゲインを3dB確保するには、Id>15mAとなり、安全動作領域を超えてしまう。

【0031】

一方、図2に示す本実施形態の場合、抵抗Rrの値を変更することにより、ドレイン電流とループゲインの関係を調整することができる。図5は、抵抗Rrおよび電源電圧Vdを変更した場合におけるループゲインとドレイン電流の関係を示す図である。この例では、各曲線は、抵抗Rrの値を、0,10,20,50,100Ωに設定するとともに、電源電圧Vdを2.0,2.1,2.2,2.5,3.0Vに設定した場合におけるループゲインとドレイン電流の関係をそれぞれ示している。この図に示すように、抵抗Rr=50Ω、電圧Vd=2.5Vの場合、および、抵抗Rr=100Ω、電圧Vd=3.0Vの場合にループゲインが3dBにおいてドレイン電流が安全動作領域に属する15mA以下となっている。このため、この図から、抵抗Rrを50Ω程度よりも大きくするとともに、電圧Vdを2.5程度よりも大きくすることで、所望のループゲインを得るとともに、安全動作領域内でHEMT10を動作させることができる。

【0032】

これは、以下の式によって表すことができる。式(4)より

Vd=Idi×(Ri+Rr) ・・・(10)

ここで、Idi=10mA(請求の範囲における「電流値Ii」に対応)、Ri=200Ωとすると、式(10)は、以下の式(11)で表される。

Vd=0.01×(200+Rr) ・・・(11)

【0033】

式(11)を式(5)に代入すると、以下の式(12)を得る。

Ids=Vd/(Rs+Rr)

=0.01×(200+Rr)/(Rs+Rr)<0.015 ・・・(12)

【0034】

式(12)を展開すると、以下の式(13)を得る。

400−3×Rs<Rr ・・・(13)

【0035】

ここで、図4から、ループゲインが3dBのときのRsは、約122Ω(=2.0V/16.4mA)となるので、Rs=122Ωを式(13)に代入すると、33Ω<Rrとなる。

【0036】

したがって、以上の式から、Rr>33Ωとなるように設定すればよい。また、電圧Vdについては式(11)から、Vd>2.33Vとなるように設定すればよい。

【0037】

以上に説明したように、本実施形態では、準ミリ波帯域またはミリ波帯域の帰還型発振装置1のドレイン端子と電源Vdとの間に抵抗素子35を挿入するようにしたので、持続発振時における電流を制限することで、HEMT10への負担を軽減することができる。

【0038】

また、抵抗素子35を挿入するとともに、電源電圧Vdを調整することにより、HEMT10への負担を軽減しつつ、ループゲインを確保することができる。これにより、発振開始時の発振の立ち上がりを迅速に行うことができる。

【0039】

また、本実施形態では、抵抗素子35の素子値と電源電圧Vdの電圧を調整することで、ループゲインに対する消費電流量が調整可能になるので、様々な制約条件が多い高周波数帯域においても高いループゲインを得ることができる。また、これに伴い、採用部品や構成を含めた帰還回路の設計の自由度を高くすることができる。

【0040】

なお、バイアス回路に抵抗を直列に挿入することは、電力損失の増大による出力の低下を意味する。すなわち、バイアス回路での電圧降下によりバイアス条件が変化して利得や出力が低減する。このため、バイアス回路に直列に抵抗を挿入することは、当業者であれば回避していた。しかしながら、本実施形態では敢えて抵抗を直列に挿入し、電源電圧と抵抗値によってゲインと電流値を調整するようにすることで、電力損失は生じるものの、それ以上に、安定的な発振と増幅素子への負荷の軽減を図るという特段の効果が期待できる。

【0041】

(D)変形実施形態の説明

以上の実施形態は一例であって、本発明が上述したような場合のみに限定されるものでないことはいうまでもない。例えば、以上の実施形態では、HEMTを増幅素子として用いるようにしたが、HEMT以外の増幅素子(例えば、MMIC(Monolithic Microwave Integrated Circuit)等)を用いることも可能である。

【0042】

また、以上の実施形態では、ノイズ除去用またはバイパスコンデンサとしてのキャパシタ素子22,23,32,34、抵抗素子33、および、インダクタ素子21,31を用いるようにしたが、これらについては使用目的や使用環境によっては除外するようにしてもよい。

【0043】

また、以上の実施形態では、V/(Rs+Rr)<Is<Ismaxとなるように電源電圧を設定するようにしたが、V/(Rs+Rr)≒Ismaxとなるように設定した場合、または、0.8×Ismax<V/(Rs+Rr)<Ismaxとなるように設定した場合に、本願の効果が顕著となり、HEMT10への負担を軽減しつつループゲインを確保することができる。

【0044】

また、以上の実施形態では、抵抗素子35については、単一の抵抗素子を用いることを想定しているが、例えば、複数の抵抗素子を直列または並列接続するようにしてもよい。例えば、並列接続する場合、並列する抵抗素子の値を調整することで、HEMT10のバラツキに対応することができる。

【0045】

また、図4および図5に示すグラフは、一例であって、HEMT10の種類によってはこれらの図とは異なる特性を有するので、個々のHEMT10の種類に応じて適切なドレイン電流、ループゲイン、および、抵抗値等を設定する必要がある。

【0046】

また、以上の実施形態では、帰還型発振装置1は、継続的に発振する場合を想定して説明を行った。しかしながら、例えば、UWB(Ultra Wide Band)レーダの場合では、短期間のパルス発振を行うので、短期間の発振の場合にはそれに対応してループゲインやドレイン電流を設定するようにしてもよい。具体的には、短期間の発振を行う場合には、発振開始時の立ち上がりが重要になるので、例えば、前述の例では、ループゲインを3dBに設定するようにしたが、3dBを超えるゲインに設定するようにしてもよい。また、短期間発振する場合には継続的に発振する場合に比較して、発熱も断続的になるので、ドレイン電流についても継続的発振の場合に比較して多少高めに設定するようにしてもよい。

【符号の説明】

【0047】

1 帰還型発振装置

10 HEMT(増幅素子)

20 バイアス回路

21 インダクタ素子

22,23 キャパシタ素子

24 抵抗素子

30 バイアス回路

31 インダクタ素子

32,34 キャパシタ素子

33 抵抗素子

35 抵抗素子

40 帰還回路

【特許請求の範囲】

【請求項1】

準ミリ波帯域またはミリ波帯域を発振周波数帯域とする帰還型発振装置において、

入力端子から入力された信号を出力端子から出力する増幅素子と、

前記増幅素子の前記出力端子から前記入力端子に信号を帰還するための帰還回路と、

前記増幅素子の前記出力端子と電源の間に挿入され、持続発振時に前記増幅素子に流れるバイアス電流を制限する抵抗素子と、

を有することを特徴とする帰還型発振装置。

【請求項2】

前記抵抗素子の抵抗値をRrとし、前記増幅素子の持続発振時における内部等価抵抗の抵抗値をRsとし、前記増幅素子の前記出力端子に印加される前記電源の電圧値をVとし、前記持続発振時において前記電源から前記増幅素子の出力端子に流れる電流をIsとし、前記増幅素子の初期状態における内部等価抵抗の抵抗値をRiとし、初期状態において前記電源から前記増幅素子の出力端子に流れる電流値をIiとし、前記増幅器の出力端子に流れる安全動作電流上限値をIsmaxとする場合、これらの間に以下の関係が成立する、

V/(Rs+Rr)=Is

V=Ii×(Ri+Rr)

但し、Ri×0.5<Rs<Ri

Is<Ismax

ことを特徴とする請求項1に記載の帰還型発振回路。

【請求項3】

前記増幅素子は高電子移動度トランジスタによって構成されていることを特徴とする請求項1または2に記載の帰還型発振装置。

【請求項1】

準ミリ波帯域またはミリ波帯域を発振周波数帯域とする帰還型発振装置において、

入力端子から入力された信号を出力端子から出力する増幅素子と、

前記増幅素子の前記出力端子から前記入力端子に信号を帰還するための帰還回路と、

前記増幅素子の前記出力端子と電源の間に挿入され、持続発振時に前記増幅素子に流れるバイアス電流を制限する抵抗素子と、

を有することを特徴とする帰還型発振装置。

【請求項2】

前記抵抗素子の抵抗値をRrとし、前記増幅素子の持続発振時における内部等価抵抗の抵抗値をRsとし、前記増幅素子の前記出力端子に印加される前記電源の電圧値をVとし、前記持続発振時において前記電源から前記増幅素子の出力端子に流れる電流をIsとし、前記増幅素子の初期状態における内部等価抵抗の抵抗値をRiとし、初期状態において前記電源から前記増幅素子の出力端子に流れる電流値をIiとし、前記増幅器の出力端子に流れる安全動作電流上限値をIsmaxとする場合、これらの間に以下の関係が成立する、

V/(Rs+Rr)=Is

V=Ii×(Ri+Rr)

但し、Ri×0.5<Rs<Ri

Is<Ismax

ことを特徴とする請求項1に記載の帰還型発振回路。

【請求項3】

前記増幅素子は高電子移動度トランジスタによって構成されていることを特徴とする請求項1または2に記載の帰還型発振装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−209907(P2012−209907A)

【公開日】平成24年10月25日(2012.10.25)

【国際特許分類】

【出願番号】特願2011−76123(P2011−76123)

【出願日】平成23年3月30日(2011.3.30)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【出願人】(391045897)古河AS株式会社 (571)

【Fターム(参考)】

【公開日】平成24年10月25日(2012.10.25)

【国際特許分類】

【出願日】平成23年3月30日(2011.3.30)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【出願人】(391045897)古河AS株式会社 (571)

【Fターム(参考)】

[ Back to top ]