平面型X線センサ

【課題】内部駆動タイミングと外部基準クロックとを整合させる。

【解決手段】X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサの内部駆動信号を生成する内部駆動信号生成回路50に、PLL構成の基準クロック生成回路51を備える。基準クロック生成回路51は、電圧制御発振器62と分周回路63と位相比較回路61とを備える。電圧制御発振器62は、たとえば水晶発振器を用いて、内部基準クロックを生成する。分周回路63は、内部基準クロックをあらかじめ定められた分周比で分周して分周クロックを出力する。位相比較回路61は、外部基準クロックと前記分周クロックとの位相を比較してその位相差を電圧制御発振器62に入力する。

【解決手段】X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサの内部駆動信号を生成する内部駆動信号生成回路50に、PLL構成の基準クロック生成回路51を備える。基準クロック生成回路51は、電圧制御発振器62と分周回路63と位相比較回路61とを備える。電圧制御発振器62は、たとえば水晶発振器を用いて、内部基準クロックを生成する。分周回路63は、内部基準クロックをあらかじめ定められた分周比で分周して分周クロックを出力する。位相比較回路61は、外部基準クロックと前記分周クロックとの位相を比較してその位相差を電圧制御発振器62に入力する。

【発明の詳細な説明】

【技術分野】

【0001】

本実施形態は、平面型X線センサに関する。

【背景技術】

【0002】

入射されたX線を光に変換し、その光を平面にアレイ状に配置された光電変換素子を用いて、電気信号として取り出すことによりX線撮影像をリアルタイムのデジタル信号として出力させる平面状に光電変換素子を配列した光電変換素子アレイを用いた固体検出器が開発されている。平面状の固体検出器であることから、画質性能や安定性の面でも優れている。

【0003】

この固体検出器は、たとえばX線発生装置などからなる外部装置ともに用いられる。一般に、X線発生装置などからなる外部装置は、外部基準クロックに基づいてX線を発生させる信号を生成し、X線を照射する。光電変換素子アレイは、照射されたX線のうち被写体を経由して入射したX線量を、電荷に変換し電気信号として取り出す。外部装置は外部基準クロックを平面型X線センサにも伝達するが、光電変換素子アレイを用いた平面型X線センサは、通常、内部のクロック生成回路によって一定の周波数の内部基準クロックを生成し、そのクロックを分周することによって内部の動作のタイミングを決める駆動信号を生成する。

【0004】

外部装置は、測定する対象物や測定内容によって外部基準クロックを変化させて、同期周波数を変更する場合がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−152599号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

平面型X線センサにおいて画像はデジタル信号であり、一般に、平面型X線センサは内部で作成される特定の周波数で与えられるタイミング信号を基準として動作している。このため、その動作をX線発生装置などの外部装置から伝達される外部基準クロックに完全にあわせることはできず、内部のタイミングとずれが発生する。その結果、画像に乱れが発生する可能性がある。

【0007】

たとえば内部の読出動作と外部の同期信号が一致した際には、読み出しを一周期分禁止するなどの対応を行う。平面センサに配置された光電変換素子にはリーク電荷が存在するため、内部の読み出しを一周期分停めるとリーク電荷が画像信号に漏れることによって、輝度レベルが変動したり、画像むらが発生するなどの問題が発生してしまう。

【0008】

そこで各実施形態は、光電変換素子アレイの内部駆動タイミングと外部装置の動作の基準となる外部基準クロックとをできるだけ整合させることを目的とする。

【課題を解決するための手段】

【0009】

上述の課題を解決するため実施形態による平面型X線センサは、X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサにおいて、二次元配列された複数の光電変換素子と前記光電変換素子のそれぞれに対して設けられたスイッチング素子と前記光電変換素子のそれぞれの行に対して設けられて前記スイッチング素子に接続されたゲートラインと前記光電変換素子のそれぞれの列に対して設けられて前記スイッチング素子を介して前記光電変換素子に接続されたデータラインとを有する光電変換素子アレイと、内部基準クロックを生成する電圧制御発振器と、前記内部基準クロックをあらかじめ定められた分周比で分周して分周クロックを出力する分周回路と、前記外部基準クロックと前記分周クロックとの位相を比較してその位相差を前記電圧制御発振器に入力する位相比較回路と、を備えて前記内部基準クロックに基づいて内部駆動信号を生成する内部駆動信号生成回路と、前記内部駆動信号に基づいて前記ゲートラインにゲート駆動信号を与えるゲート駆動回路と、前記内部駆動信号に基づいて前記光電変換素子アレイから前記データラインを介して画素信号を読み出す読出回路と、を具備することを特徴とする。

【0010】

また、実施形態による平面型X線センサは、X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサにおいて、二次元配列された複数の光電変換素子と前記光電変換素子のそれぞれに対して設けられたスイッチング素子と前記光電変換素子のそれぞれの行に対して設けられて前記スイッチング素子に接続されたゲートラインと前記光電変換素子のそれぞれの列に対して設けられて前記スイッチング素子を介して前記光電変換素子に接続されたデータラインとを有する光電変換素子アレイと、所定の周波数の固定クロックを生成する基準発振器と、前記外部基準クロックの1周期での前記固定クロックのクロック数をカウントしてそのクロック数に基づいて分周比を算出する周波数判定回路と、前記固定クロックを前記分周比で分周して内部基準クロックを生成する分周回路と、を備えて前記内部基準クロックに基づいて内部駆動信号を生成する内部駆動信号生成回路と、前記内部駆動信号に基づいて前記ゲートラインにゲート駆動信号を与えるゲート駆動回路と、前記内部駆動信号に基づいて前記光電変換素子アレイから前記データラインを介して画素信号を読み出す読出回路と、を具備することを特徴とする。

【図面の簡単な説明】

【0011】

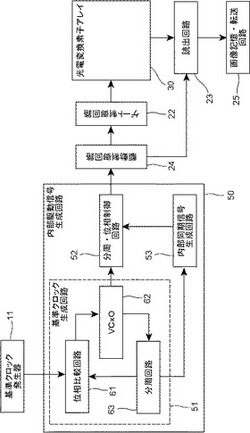

【図1】第1実施形態による平面型X線センサのブロック図である。

【図2】第1実施形態によるX線撮像システムのブロック図である。

【図3】第1実施形態による光電変換素子アレイの模式的斜視図である。

【図4】第1実施形態による光電変換素子アレイの等価回路図である。

【図5】第1実施形態におけるタイミングチャートである。

【図6】第1実施形態において内部分周クロックの位相が外部基準クロックに対して進んだ場合の変化を示すタイミングチャートである。

【図7】第1実施形態において内部分周クロックの位相が外部基準クロックに対して遅れた場合の変化を示すタイミングチャートである。

【図8】第2実施形態による平面型X線センサのブロック図である。

【図9】第2実施形態におけるタイミングチャートである。

【図10】第2実施形態において内部分周クロックの位相が外部基準クロックに対して遅れた場合の変化を示すタイミングチャートである。

【図11】第2実施形態において内部分周クロックの位相が外部基準クロックに対して進んだ場合の変化を示すタイミングチャートである。

【発明を実施するための形態】

【0012】

以下、いくつかの実施形態によるX線平面センサを、図面を参照して説明する。なお、同一または類似の構成には同一の符号を付し、重複する説明は省略する。

【0013】

[第1実施形態]

図2は、第1実施形態によるX線撮像システムのブロック図である。

【0014】

X線撮像システムは、X線発生装置10と平面型X線センサ20とを有している。X線発生装置10は、外部基準クロック発生器11とX線発生器12とを有している。外部基準クロック発生器11は、外部基準クロックを発生する。外部基準クロックは、X線発生器12がX線を発生するタイミングの基準となる。外部基準クロックは、パルス状の信号として伝達される。X線発生器12は、外部基準クロックに基づく所定の周期でX線13を発生する。たとえば、X線発生器12は、外部基準クロックの1周期毎にX線を発生する。

【0015】

平面型X線センサ20は、光電変換素子アレイ30、ゲート駆動回路22、読出回路23、駆動制御回路24、画像記憶・転送回路25および内部駆動信号生成回路50を有している。

【0016】

光電変換素子アレイ30には、患者などの撮像対象14を透過したX線13が入射する。光電変換素子アレイ30は、入射したX線13の線量を電荷に変換して電気信号として出力する。

【0017】

ゲート駆動回路22は、光電変換素子アレイ30にゲート駆動信号を与える。読出回路23は、入射したX線13の線量を電荷に変換した電気信号を光電変換素子アレイ30から読み出す。

【0018】

内部駆動信号生成回路50は、光電変換素子アレイ30に蓄えられた電気信号を取り出すために、X線発生装置10から与えられた外部基準クロックから内部の駆動タイミング信号を生成する。より具体的には、内部駆動信号生成回路50は、外部基準クロック発生器11から外部基準クロックの信号を受信して駆動タイミング信号を生成し、駆動制御回路24に与える。

【0019】

駆動制御回路24は、内部駆動信号生成回路50で生成された駆動タイミング信号に従って光電変換素子アレイ30を駆動する。より具体的には、駆動制御回路24は、駆動タイミング信号に従ってゲート駆動回路22および読出回路23を制御する。画像記憶・転送回路25は、読出回路23が読み出した電気信号を記憶し、外部に転送する。

【0020】

図3は、本実施形態による光電変換素子アレイの模式的斜視図である。図4は、本実施形態による光電変換素子アレイの等価回路図である。

【0021】

光電変換素子アレイ30は、アレイ基板31とシンチレータ膜32とを有している。アレイ基板31は、ガラス基板33を有している。ガラス基板33の表面には、複数の微細な画素34が正方格子状に配列されている。それぞれの画素34は、薄膜トランジスタ35とフォトダイオード36とを有している。また、ガラス基板33の表面には、画素34が配列された正方格子の行と同数のゲートライン37が各画素34の間を延びている。さらに、ガラス基板33の表面には、画素34が配列された正方格子の列の数と同数のデータライン38が各画素34の間を延びている。

【0022】

シンチレータ膜32は、アレイ基板31の画素34が配列された領域の表面に形成されている。シンチレータ膜32は、X線13が入射すると可視光領域の蛍光を発生する。発生した蛍光は、アレイ基板31の表面に到達する。

【0023】

アレイ基板31は、シンチレータ膜32で発生した蛍光を受光して電気信号を発生する。その結果、入射したX線によってシンチレータ膜32で発生した可視光像は、電気信号で表現された画像情報に変換される。

【0024】

それぞれのフォトダイオード36は、スイッチング素子である薄膜トランジスタ35を介してゲートライン37およびデータライン38に接続されている。また、それぞれのフォトダイオード36には、蓄積キャパシタ39が並列に接続されている。

【0025】

フォトダイオード36およびそれに並列に接続された蓄積キャパシタ39は、薄膜トランジスタ35のドレイン・ソース電極を介してデータライン38に接続されている。薄膜トランジスタ35のゲート電極は、ゲートライン37に接続されている。

【0026】

配列の同じ行に位置する画素34の薄膜トランジスタ35のゲート電極は、同一のゲートライン37に接続されている。配列の同じ列に位置する画素34のフォトダイオード36および蓄積キャパシタ39は、薄膜トランジスタ35を介して同一のデータライン38に接続されている。各薄膜トランジスタ35は、フォトダイオード36への蛍光の入射にて発生した電荷を蓄積および放出させるスイッチング機能を担う。

【0027】

光電変換素子アレイ30は、平面構造のため2次元的に走査する必要がある。ゲート駆動回路22は、2次元配列された画素34の横方向の1行を選択し、その1行に対応するゲートライン37に薄膜トランジスタ35をONの状態にするパルス状の信号を与える。ゲート駆動回路22が選択するラインを縦方向に順次切り替えて、すべての行選択を走査することにより、平面すべてが選択される。また、読出回路23は、ゲート駆動回路22によって選択された1行内で、横方向に信号を走査して読み出すための回路である。

【0028】

このように、ゲート駆動回路22による行選択と、読出回路23による1行内の信号読出を繰り返すことにより、平面すべての画素34の信号を読み出すことができる。画像記憶・転送回路25は、順次読み出された電気信号を一時的に記録し、画像処理、画像表示に適したデータに並び替え、転送する。これらの動作により、被写体を透過したX線信号を電気信号の強弱の2次元データとして取り込むことができる。

【0029】

なお、図3および図4において、画素は5行5列あるいは4行4列分しか記載していないが、実際にはもっと多く、解像度、撮像面積に応じて必要な画素が形成されている。

【0030】

図1は、本実施形態による平面型X線センサのブロック図である。

【0031】

内部駆動信号生成回路50は、基準クロック生成回路51、分周・位相制御回路52および内部同期信号生成回路53を有している。基準クロック生成回路51は、位相比較回路61と電圧制御発振器62と分周回路63とを有している。電圧制御発振器62は、高い精度で発振する水晶発振子を用いた電圧制御発振器(VCxO)であることが望ましい。

【0032】

基準クロック生成回路51は、いわゆる位相同期回路(PLL)であり、外部基準クロック発生器11が生成した外部基準クロックと位相のそろった内部基準クロックを生成する。内部基準クロックは、たとえば15MHzである。したがって、内部基準クロックの周期は67nsecである。

【0033】

外部基準クロックは、パルス状の信号として、位相比較回路61に入力される。位相比較回路61の出力は、電圧制御発振器62に入力される。電圧制御発振器62の出力信号は、分周・位相制御回路に伝達されるとともに、分周回路63に伝達される。分周回路63は、電圧制御発振器62の出力信号をあらかじめ定められた分周比で分周する。分周回路63から出力される分周クロックは、位相比較回路61に入力される。位相比較回路61は、外部基準クロックおよび分周クロックの位相を比較し、位相差を出力し、電圧制御発振器62に入力する。このようにして電圧制御発振器62は、内部基準クロックを生成する。

【0034】

内部同期信号生成回路53は、分周回路63から内部基準クロックを分周したクロック信号を受け取り、内部同期信号を生成する。分周・位相制御回路52は、内部同期信号生成回路53から内部同期信号を受信し、また、電圧制御発振器62から内部基準クロックを受信して、スタートパルスを生成する。分周・位相制御回路52が生成するスタートパルスは、駆動制御回路24に与えられる。駆動制御回路24は、スタートパルスを受け取ると処理を開始する。つまり、スタートパルスは、駆動制御回路24による処理の開始のタイミングを示す内部駆動信号である。

【0035】

図5は、本実施形態におけるタイミングチャートである。図6は、本実施形態において内部分周クロックの位相が外部基準クロックに対して進んだ場合の変化を示すタイミングチャートである。図7は、本実施形態において内部分周クロックの位相が外部基準クロックに対して遅れた場合の変化を示すタイミングチャートである。

【0036】

図5に示すように、本実施形態によれば、分周回路63が生成する内部分周クロックは、外部基準クロックと位相のそろったものとなる。この内部分周クロックが外部基準クロックと周波数がずれたりして、位相がずれてしまった場合には、位相比較回路Xがその位相差を検出し、位相差を電圧値に変換する。この位相差が変換された電圧によって電圧制御発振器Xが制御される。

【0037】

図6に示すように、内部分周クロックが外部基準クロックの位相に対して進んだ場合、すなわち、内部分周クロックの周波数が外部基準クロックの周波数に比べて高い場合には、電圧制御発振器Xの発振周波数を下げる方向に制御される。つまり、この場合には、内部分周クロックと外部基準クロックの位相を比較した後の内部基準クロックの周期t2は、位相比較前の内部分周クロックの周期t1よりも長くなるように制御される。

【0038】

逆に、内部分周クロックが外部基準クロックの位相に対して遅れた場合、すなわち、内部分周クロックの周波数が外部基準クロックの周波数に比べて低い場合には、電圧制御発振器Xの発振周波数を上げる方向に制御される。つまり、この場合には、内部分周クロックと外部基準クロックの位相を比較した後の内部基準クロックの周期t3は、位相比較前の内部分周クロックの周期t1よりも長くなるように制御される。

【0039】

これらの制御によって、外部基準クロックと内部分周クロックとは完全に周波数および位相が一致する。1秒間に60フレームの動画を撮影する場合には、撮像間隔は約17msecである。しかし、本実施形態のようにPLL回路によって周波数を追従させる場合、周波数の追従に要する時間はこの撮像間隔に比べて非常に小さいため、次の撮像までの間に周波数は追従する。さらに、一旦、外部基準クロックと内部分周クロックとが同期した後には、同期した状態からの変化にのみ追従すればよいため、より速く同期することになる。

【0040】

このように、本実施形態の平面型X線センサ20においては、外部基準クロックと内部分周クロックを一致させるために、内部駆動信号発生回路50内の基準基準クロックを生成する回路で生成するクロックの周波数を固定ではなく、可変としている。内部基準クロックを、外部基準クロックにあわせて可変とすることで外部基準クロックと内部動作の基準となる内部分周クロックの周波数および位相を一致させることができる。

【0041】

外部基準クロックとは無関係に特定の周波数のクロックを発振して内部基準クロックを生成し、内部同期信号もそのクロックを分周して生成すると、外部基準クロックと内部同期信号との位相を完全に一致させることはできない。つまり、外部基準クロックと内部の処理クロックは非同期の関係となる。この場合、以下のような問題が生じる。

【0042】

X線発生装置10と平面型X線センサ20とが非同期に動作する場合、外部基準クロックは、平面型X線センサ20の処理クロックとは非同期に入力されることになる。動画を撮像する場合は、通常、外部基準クロックは一定の周波数で入力され、平面型X線センサ20も外部基準クロックに合わせて動作する。

【0043】

平面型X線センサ20の動作期間(内部処理の期間)は、X線からの透過線による電荷を取り込む信号蓄積期間と、受け取った電荷を外部装置に転送するための信号処理・転送期間とに分けられる。信号蓄積期間は、内部基準クロックを分周することによって得られるX線の電荷蓄積を決める期間である。このため、信号蓄積期間の長さが変わると蓄積される電荷量も変わってしまう。また、信号処理・転送期間も、処理に所定の時間が必要である。したがって、信号蓄積期間および信号処理・転送期間を動画のフレーム毎に変えることはできない。つまり、内部処理の期間は、いずれのフレームでも実質的に一定である。

【0044】

そこで、外部基準クロックによって、これらの動作の開始タイミングを設定し、一定期間を確保することで、外部基準クロックに追従させる方法がある。この方法では、信号蓄積期間と信号処理・転送期間の和が外部基準クロックの周期より十分短い場合は、待機時間を設けることによって同期をとることができる。逆に、信号蓄期間と信号処理・転送期間の和が、外部基準クロックの周期より長い場合は、たとえば外部基準クロックの2周期毎に1回の信号蓄積および信号処理・転送をするなど、外部基準クロックを間引くことにより、外部基準クロックと同期をとって平面型X線センサを動作させることができる。

【0045】

しかし、外部基準クロックと内部分周クロックがほぼ同じ周期になり内部基準クロックの1周期内の差しかない場合や、外部基準クロックの周期が、信号蓄積時間と信号処理・転送時間の和の周期が整数倍になる場合には、内部処理が外部基準クロックの周期に間に合う場合と間に合わない場合が発生する。間に合う場合には、外部装置から伝達される次の同期信号で次の処理に移ることができるが、間に合わない場合には、次の外部基準クロック1周期分は処理をせず、その次の同期信号で動作が開始することになる。すなわち、同期信号に追従できない期間が発生し、特定のタイミングで1フレーム抜けることになる。

【0046】

つまり、外部基準クロックの周期と内部処理の周期がほぼ一致してしまう場合や外部同期信号が内部処理周期のほぼ整数倍になってしまう場合の問題点は、内部基準クロックの1クロックの期間内で同期ずれが発生するために、固定周期の内部基準クロックでは制御できないことにある。内部基準クロックを分周して作成される内部同期と外部同期では内部クロック1クロックの期間内のずれが発生するため、同期周波数がほぼ一致する場合には、1周期毎、外部基準クロックの周期が内部分周クロックの周期のN倍の場合には、N回の同期ごとに処理が間に合わない期間が発生してしまう。

【0047】

平面センサ内の光電変換素子には、電荷が蓄積される。この電荷は、読み出す必要があるため、TFT構造の素子に接続されている。しかし、TFT構造の半導体を通して電荷が少しずつリークしてしまい、隣接画素や信号線へ電荷が移動してしまう症状が発生する。リーク量は、画素から読み出しをしない場合に発生し、画素によって特性が異なるため、読み出しを行わない時間差が大きいほどリークによる影響が大きくなる。その結果、内部処理が外部基準クロックに追従できない期間が発生した場合、その間でのリーク電荷の影響により、周期内に読み出せる場合と読み出し電荷量が変化し画像輝度が一定にならないという問題が発生する。結果として、特定の周期で動画の画像輝度が揺れる症状となってしまう。

【0048】

しかし、本実施形態では、内部基準クロックを生成する基準クロック生成回路51は、PLL構成をとり、内部基準クロックは電圧制御発振器62により生成される。内部基準クロックは、分周回路63で分周され、外部基準クロックとほぼ同じ周波数の内部分周クロックが生成される。この際、分周回路63の分周比は、外部基準クロックの周期にあわせて電圧制御発振器62の発振範囲を超えないように制御される。

【0049】

その結果、外部基準クロックと内部分周クロックのタイミングが一致し、平面型X線センサ20における処理を開始するタイミング信号であるスタートパルスは、外部基準クロックに対応したタイミングとなる。このように本実施形態によれば、光電変換素子アレイの内部駆動タイミングと外部装置の動作の基準となる外部基準クロックとをできるだけ整合させることができる。

【0050】

したがって、外部基準クロックのある特定期間に平面型X線センサ20が処理できない状況が発生する可能性は極めて小さくなる。動画を撮影している場合には、特定のタイミングで1フレーム抜けてしまう可能性が極めて小さくなる。また、画素34からのリーク電荷の影響を抑制することができる。

【0051】

また、本実施形態によれば、X線発生装置10などの外部装置と平面型X線センサとで同一の基準クロックを用いなくても、フリッカやむらの無い画像を得ることができる。したがって、平面型X線センサとX線発生装置などの外部装置とを独立して設計できる。このため、既存のX線発生装置と本実施形態の平面型X線センサとを組み合わせても、フリッカやむらの無い画像を得ることができる。

【0052】

[第2実施形態]

図8は、第2実施形態による平面型X線センサのブロック図である。

【0053】

本実施形態の平面型X線センサは、第1実施形態の基準クロック生成回路51(図1参照)の代わりに、同期追従回路54を設けたものである。同期追従回路54は、基準発振器72と、周波数判定回路71と、分周回路73と、を有している。

【0054】

基準発振器72は、所定の周波数の固定クロックを生成する。基準発振器72は、たとえば水晶発振器であって、非常に精度の高い周波数の固定クロックを生成する。周波数判定回路71は、外部基準クロックの1周期での固定クロックのクロック数をカウントする。また、周波数判定回路71は、カウントしたクロック数に基づいて分周比を算出する。分周回路73は、基準発振器72が生成した固定クロックをこの分周比で分周して内部基準クロックを生成する。

【0055】

図9は、本実施形態におけるタイミングチャートである。図10は、本実施形態において内部分周クロックの位相が外部基準クロックに対して遅れた場合の変化を示すタイミングチャートである。図11は、本実施形態において内部分周クロックの位相が外部基準クロックに対して進んだ場合の変化を示すタイミングチャートである。

【0056】

周波数判定回路71は、次のようにして分周比を算出する。まず、外部基準クロックの1周期での固定クロックのクロック数をカウントする。次に、ここでカウントしたクロック数を、規定カウント数と比較する。ここで、この規定カウント数とは、内部処理に必要な時間を基準発振器72が発振する固定クロックのクロック数で表したものである。

【0057】

外部基準クロック1周期での固定クロックのカウント数が、規定カウント数で表した値よりも少ない場合を考える。この場合、外部基準クロックの1周期の間に内部処理が完了しないことになる。そこで、このような場合には、外部基準クロックを数パルス間引くことによって、内部処理が可能な最短周期よりも長くなるように外部基準クロックを調整する。たとえば外部基準クロックの2周期毎に、信号蓄積とその信号の読み取り・転送を行うこととする。

【0058】

このようにして、外部基準クロック1周期あるいは所定の周期の間に内部処理が完了するように、内部処理の時間を設定しておく。つまり、外部基準クロック1周期あるいは所定の周期での固定クロックのカウント数が、規定カウント数よりも小さくならないようにしておく。さらに、内部分周クロックの周期を間引かれた外部基準クロックの周期と同一になるように分周比を設定する。

【0059】

次に、外部基準クロック1周期での固定クロックのカウント数が、規定カウント数に比べて多い場合を考える。この場合、基準カウント数を分周比として、内部分周クロックを生成すると、その内部分周クロックの周波数は外部基準クロックの周波数よりも高くなる。したがって、外部基準クロックの1周期よりも短い時間で内部処理は完了する。そこで、内部処理の完了後、基準クロックのいくつかの周期分、次のスタートパルスを遅らせる。つまり分周比を大きくする。これにより、外部基準クロック1周期ごとに、適切に内部処理を完了することができる。

【0060】

外部基準クロックの周期と内部処理の周期とがほぼ一致する場合や、外部基準クロックの周期が内部処理周期のほぼ整数倍する場合以外、つまり、これらの周波数が異なる場合は、周波数の差に応じて、数周期間隔で処理が間に合わないタイミングが発生する。この場合、本実施形態では、内部の基準となるクロックの周波数の調整を行わずに、駆動制御回路24などを制御する。

【0061】

分周回路73は、外部基準クロックにあわせて、基準発振器72が生成した固定クロックを分周して、内部分周クロックを生成する。この内部分周クロックが外部基準クロックと比べて遅れてしまうと、次の外部基準クロック1周期分は処理をせず、その次の同期信号で動作が開始することになる。すなわち、同期信号に追従できない期間が発生し、特定のタイミングで1フレーム抜けることになる。

【0062】

この状態を避けるため、本実施形態では、分周回路73のクロック分周比を必ず外部基準クロックの周期と比べて内部分周クロックの周期が小さくなるように設定する。この分周比を決定するのが、周波数判定回路71である。

【0063】

外部基準クロックの周期が内部処理に要する時間よりも短い場合は、同期信号を数パルス間引くことにより、処理可能な最小周期となるように外部同期信号を調整する。また、内部分周クロックの周期を間引かれた外部同期信号と同一になるように、分周比を調整する。更に、クロック1個分の差によって内部分周クロックに遅れが発生する場合は、分周比を1クロック分少なくすることにより位相遅れが無い様に随時調整を行う。この動作を継続的に行うことによって、外部同期1周期のずれをなくし、1クロック分の時間差で吸収する事ができる。

【0064】

このように本実施形態によれば、光電変換素子アレイの内部駆動タイミングと外部装置の動作の基準となる外部基準クロックとをできるだけ整合させることができる。このときリーク電荷は、同期信号一周期分である数ミリ〜数十ミリ秒の単位から、数十ナノ秒〜数マイクロ秒に圧縮される為、無視できるレベルに低減される。

【0065】

また、本実施形態と第1実施形態を組み合わせてもよい。この場合は、外部基準クロックと内部分周クロックの位相差が固定クロックの1クロック範囲内の違いかどうかを周波数判別回路で判断する。位相差が1クロック範囲外であれば、本実施形態の処理を行い、1クロック内であれば第1実施形態と同様の処理を行う。このような組合せで処理を行うことにより、本実施形態では発生する1クロック分のリーク電荷の影響も避けることができる。

【0066】

[他の実施の形態]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0067】

10…X線発生装置、11…外部基準クロック発生器、12…X線発生器、13…X線、14…撮像対象、20…平面型X線センサ、22…ゲート駆動回路、23…読出回路、24…駆動制御回路、25…画像記憶・転送回路、30…光電変換素子アレイ、31…アレイ基板、32…シンチレータ膜、33…ガラス基板、34…画素、35…薄膜トランジスタ、36…フォトダイオード、37…ゲートライン、38…データライン、39…蓄積キャパシタ、50…内部駆動信号生成回路、51…基準クロック生成回路、52…分周・位相制御回路、53…内部同期信号生成回路、54…同期追従回路、61…位相比較回路、62…電圧制御発振器、63…分周回路、71…周波数判定回路、72…基準発振器、73…分周回路

【技術分野】

【0001】

本実施形態は、平面型X線センサに関する。

【背景技術】

【0002】

入射されたX線を光に変換し、その光を平面にアレイ状に配置された光電変換素子を用いて、電気信号として取り出すことによりX線撮影像をリアルタイムのデジタル信号として出力させる平面状に光電変換素子を配列した光電変換素子アレイを用いた固体検出器が開発されている。平面状の固体検出器であることから、画質性能や安定性の面でも優れている。

【0003】

この固体検出器は、たとえばX線発生装置などからなる外部装置ともに用いられる。一般に、X線発生装置などからなる外部装置は、外部基準クロックに基づいてX線を発生させる信号を生成し、X線を照射する。光電変換素子アレイは、照射されたX線のうち被写体を経由して入射したX線量を、電荷に変換し電気信号として取り出す。外部装置は外部基準クロックを平面型X線センサにも伝達するが、光電変換素子アレイを用いた平面型X線センサは、通常、内部のクロック生成回路によって一定の周波数の内部基準クロックを生成し、そのクロックを分周することによって内部の動作のタイミングを決める駆動信号を生成する。

【0004】

外部装置は、測定する対象物や測定内容によって外部基準クロックを変化させて、同期周波数を変更する場合がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−152599号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

平面型X線センサにおいて画像はデジタル信号であり、一般に、平面型X線センサは内部で作成される特定の周波数で与えられるタイミング信号を基準として動作している。このため、その動作をX線発生装置などの外部装置から伝達される外部基準クロックに完全にあわせることはできず、内部のタイミングとずれが発生する。その結果、画像に乱れが発生する可能性がある。

【0007】

たとえば内部の読出動作と外部の同期信号が一致した際には、読み出しを一周期分禁止するなどの対応を行う。平面センサに配置された光電変換素子にはリーク電荷が存在するため、内部の読み出しを一周期分停めるとリーク電荷が画像信号に漏れることによって、輝度レベルが変動したり、画像むらが発生するなどの問題が発生してしまう。

【0008】

そこで各実施形態は、光電変換素子アレイの内部駆動タイミングと外部装置の動作の基準となる外部基準クロックとをできるだけ整合させることを目的とする。

【課題を解決するための手段】

【0009】

上述の課題を解決するため実施形態による平面型X線センサは、X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサにおいて、二次元配列された複数の光電変換素子と前記光電変換素子のそれぞれに対して設けられたスイッチング素子と前記光電変換素子のそれぞれの行に対して設けられて前記スイッチング素子に接続されたゲートラインと前記光電変換素子のそれぞれの列に対して設けられて前記スイッチング素子を介して前記光電変換素子に接続されたデータラインとを有する光電変換素子アレイと、内部基準クロックを生成する電圧制御発振器と、前記内部基準クロックをあらかじめ定められた分周比で分周して分周クロックを出力する分周回路と、前記外部基準クロックと前記分周クロックとの位相を比較してその位相差を前記電圧制御発振器に入力する位相比較回路と、を備えて前記内部基準クロックに基づいて内部駆動信号を生成する内部駆動信号生成回路と、前記内部駆動信号に基づいて前記ゲートラインにゲート駆動信号を与えるゲート駆動回路と、前記内部駆動信号に基づいて前記光電変換素子アレイから前記データラインを介して画素信号を読み出す読出回路と、を具備することを特徴とする。

【0010】

また、実施形態による平面型X線センサは、X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサにおいて、二次元配列された複数の光電変換素子と前記光電変換素子のそれぞれに対して設けられたスイッチング素子と前記光電変換素子のそれぞれの行に対して設けられて前記スイッチング素子に接続されたゲートラインと前記光電変換素子のそれぞれの列に対して設けられて前記スイッチング素子を介して前記光電変換素子に接続されたデータラインとを有する光電変換素子アレイと、所定の周波数の固定クロックを生成する基準発振器と、前記外部基準クロックの1周期での前記固定クロックのクロック数をカウントしてそのクロック数に基づいて分周比を算出する周波数判定回路と、前記固定クロックを前記分周比で分周して内部基準クロックを生成する分周回路と、を備えて前記内部基準クロックに基づいて内部駆動信号を生成する内部駆動信号生成回路と、前記内部駆動信号に基づいて前記ゲートラインにゲート駆動信号を与えるゲート駆動回路と、前記内部駆動信号に基づいて前記光電変換素子アレイから前記データラインを介して画素信号を読み出す読出回路と、を具備することを特徴とする。

【図面の簡単な説明】

【0011】

【図1】第1実施形態による平面型X線センサのブロック図である。

【図2】第1実施形態によるX線撮像システムのブロック図である。

【図3】第1実施形態による光電変換素子アレイの模式的斜視図である。

【図4】第1実施形態による光電変換素子アレイの等価回路図である。

【図5】第1実施形態におけるタイミングチャートである。

【図6】第1実施形態において内部分周クロックの位相が外部基準クロックに対して進んだ場合の変化を示すタイミングチャートである。

【図7】第1実施形態において内部分周クロックの位相が外部基準クロックに対して遅れた場合の変化を示すタイミングチャートである。

【図8】第2実施形態による平面型X線センサのブロック図である。

【図9】第2実施形態におけるタイミングチャートである。

【図10】第2実施形態において内部分周クロックの位相が外部基準クロックに対して遅れた場合の変化を示すタイミングチャートである。

【図11】第2実施形態において内部分周クロックの位相が外部基準クロックに対して進んだ場合の変化を示すタイミングチャートである。

【発明を実施するための形態】

【0012】

以下、いくつかの実施形態によるX線平面センサを、図面を参照して説明する。なお、同一または類似の構成には同一の符号を付し、重複する説明は省略する。

【0013】

[第1実施形態]

図2は、第1実施形態によるX線撮像システムのブロック図である。

【0014】

X線撮像システムは、X線発生装置10と平面型X線センサ20とを有している。X線発生装置10は、外部基準クロック発生器11とX線発生器12とを有している。外部基準クロック発生器11は、外部基準クロックを発生する。外部基準クロックは、X線発生器12がX線を発生するタイミングの基準となる。外部基準クロックは、パルス状の信号として伝達される。X線発生器12は、外部基準クロックに基づく所定の周期でX線13を発生する。たとえば、X線発生器12は、外部基準クロックの1周期毎にX線を発生する。

【0015】

平面型X線センサ20は、光電変換素子アレイ30、ゲート駆動回路22、読出回路23、駆動制御回路24、画像記憶・転送回路25および内部駆動信号生成回路50を有している。

【0016】

光電変換素子アレイ30には、患者などの撮像対象14を透過したX線13が入射する。光電変換素子アレイ30は、入射したX線13の線量を電荷に変換して電気信号として出力する。

【0017】

ゲート駆動回路22は、光電変換素子アレイ30にゲート駆動信号を与える。読出回路23は、入射したX線13の線量を電荷に変換した電気信号を光電変換素子アレイ30から読み出す。

【0018】

内部駆動信号生成回路50は、光電変換素子アレイ30に蓄えられた電気信号を取り出すために、X線発生装置10から与えられた外部基準クロックから内部の駆動タイミング信号を生成する。より具体的には、内部駆動信号生成回路50は、外部基準クロック発生器11から外部基準クロックの信号を受信して駆動タイミング信号を生成し、駆動制御回路24に与える。

【0019】

駆動制御回路24は、内部駆動信号生成回路50で生成された駆動タイミング信号に従って光電変換素子アレイ30を駆動する。より具体的には、駆動制御回路24は、駆動タイミング信号に従ってゲート駆動回路22および読出回路23を制御する。画像記憶・転送回路25は、読出回路23が読み出した電気信号を記憶し、外部に転送する。

【0020】

図3は、本実施形態による光電変換素子アレイの模式的斜視図である。図4は、本実施形態による光電変換素子アレイの等価回路図である。

【0021】

光電変換素子アレイ30は、アレイ基板31とシンチレータ膜32とを有している。アレイ基板31は、ガラス基板33を有している。ガラス基板33の表面には、複数の微細な画素34が正方格子状に配列されている。それぞれの画素34は、薄膜トランジスタ35とフォトダイオード36とを有している。また、ガラス基板33の表面には、画素34が配列された正方格子の行と同数のゲートライン37が各画素34の間を延びている。さらに、ガラス基板33の表面には、画素34が配列された正方格子の列の数と同数のデータライン38が各画素34の間を延びている。

【0022】

シンチレータ膜32は、アレイ基板31の画素34が配列された領域の表面に形成されている。シンチレータ膜32は、X線13が入射すると可視光領域の蛍光を発生する。発生した蛍光は、アレイ基板31の表面に到達する。

【0023】

アレイ基板31は、シンチレータ膜32で発生した蛍光を受光して電気信号を発生する。その結果、入射したX線によってシンチレータ膜32で発生した可視光像は、電気信号で表現された画像情報に変換される。

【0024】

それぞれのフォトダイオード36は、スイッチング素子である薄膜トランジスタ35を介してゲートライン37およびデータライン38に接続されている。また、それぞれのフォトダイオード36には、蓄積キャパシタ39が並列に接続されている。

【0025】

フォトダイオード36およびそれに並列に接続された蓄積キャパシタ39は、薄膜トランジスタ35のドレイン・ソース電極を介してデータライン38に接続されている。薄膜トランジスタ35のゲート電極は、ゲートライン37に接続されている。

【0026】

配列の同じ行に位置する画素34の薄膜トランジスタ35のゲート電極は、同一のゲートライン37に接続されている。配列の同じ列に位置する画素34のフォトダイオード36および蓄積キャパシタ39は、薄膜トランジスタ35を介して同一のデータライン38に接続されている。各薄膜トランジスタ35は、フォトダイオード36への蛍光の入射にて発生した電荷を蓄積および放出させるスイッチング機能を担う。

【0027】

光電変換素子アレイ30は、平面構造のため2次元的に走査する必要がある。ゲート駆動回路22は、2次元配列された画素34の横方向の1行を選択し、その1行に対応するゲートライン37に薄膜トランジスタ35をONの状態にするパルス状の信号を与える。ゲート駆動回路22が選択するラインを縦方向に順次切り替えて、すべての行選択を走査することにより、平面すべてが選択される。また、読出回路23は、ゲート駆動回路22によって選択された1行内で、横方向に信号を走査して読み出すための回路である。

【0028】

このように、ゲート駆動回路22による行選択と、読出回路23による1行内の信号読出を繰り返すことにより、平面すべての画素34の信号を読み出すことができる。画像記憶・転送回路25は、順次読み出された電気信号を一時的に記録し、画像処理、画像表示に適したデータに並び替え、転送する。これらの動作により、被写体を透過したX線信号を電気信号の強弱の2次元データとして取り込むことができる。

【0029】

なお、図3および図4において、画素は5行5列あるいは4行4列分しか記載していないが、実際にはもっと多く、解像度、撮像面積に応じて必要な画素が形成されている。

【0030】

図1は、本実施形態による平面型X線センサのブロック図である。

【0031】

内部駆動信号生成回路50は、基準クロック生成回路51、分周・位相制御回路52および内部同期信号生成回路53を有している。基準クロック生成回路51は、位相比較回路61と電圧制御発振器62と分周回路63とを有している。電圧制御発振器62は、高い精度で発振する水晶発振子を用いた電圧制御発振器(VCxO)であることが望ましい。

【0032】

基準クロック生成回路51は、いわゆる位相同期回路(PLL)であり、外部基準クロック発生器11が生成した外部基準クロックと位相のそろった内部基準クロックを生成する。内部基準クロックは、たとえば15MHzである。したがって、内部基準クロックの周期は67nsecである。

【0033】

外部基準クロックは、パルス状の信号として、位相比較回路61に入力される。位相比較回路61の出力は、電圧制御発振器62に入力される。電圧制御発振器62の出力信号は、分周・位相制御回路に伝達されるとともに、分周回路63に伝達される。分周回路63は、電圧制御発振器62の出力信号をあらかじめ定められた分周比で分周する。分周回路63から出力される分周クロックは、位相比較回路61に入力される。位相比較回路61は、外部基準クロックおよび分周クロックの位相を比較し、位相差を出力し、電圧制御発振器62に入力する。このようにして電圧制御発振器62は、内部基準クロックを生成する。

【0034】

内部同期信号生成回路53は、分周回路63から内部基準クロックを分周したクロック信号を受け取り、内部同期信号を生成する。分周・位相制御回路52は、内部同期信号生成回路53から内部同期信号を受信し、また、電圧制御発振器62から内部基準クロックを受信して、スタートパルスを生成する。分周・位相制御回路52が生成するスタートパルスは、駆動制御回路24に与えられる。駆動制御回路24は、スタートパルスを受け取ると処理を開始する。つまり、スタートパルスは、駆動制御回路24による処理の開始のタイミングを示す内部駆動信号である。

【0035】

図5は、本実施形態におけるタイミングチャートである。図6は、本実施形態において内部分周クロックの位相が外部基準クロックに対して進んだ場合の変化を示すタイミングチャートである。図7は、本実施形態において内部分周クロックの位相が外部基準クロックに対して遅れた場合の変化を示すタイミングチャートである。

【0036】

図5に示すように、本実施形態によれば、分周回路63が生成する内部分周クロックは、外部基準クロックと位相のそろったものとなる。この内部分周クロックが外部基準クロックと周波数がずれたりして、位相がずれてしまった場合には、位相比較回路Xがその位相差を検出し、位相差を電圧値に変換する。この位相差が変換された電圧によって電圧制御発振器Xが制御される。

【0037】

図6に示すように、内部分周クロックが外部基準クロックの位相に対して進んだ場合、すなわち、内部分周クロックの周波数が外部基準クロックの周波数に比べて高い場合には、電圧制御発振器Xの発振周波数を下げる方向に制御される。つまり、この場合には、内部分周クロックと外部基準クロックの位相を比較した後の内部基準クロックの周期t2は、位相比較前の内部分周クロックの周期t1よりも長くなるように制御される。

【0038】

逆に、内部分周クロックが外部基準クロックの位相に対して遅れた場合、すなわち、内部分周クロックの周波数が外部基準クロックの周波数に比べて低い場合には、電圧制御発振器Xの発振周波数を上げる方向に制御される。つまり、この場合には、内部分周クロックと外部基準クロックの位相を比較した後の内部基準クロックの周期t3は、位相比較前の内部分周クロックの周期t1よりも長くなるように制御される。

【0039】

これらの制御によって、外部基準クロックと内部分周クロックとは完全に周波数および位相が一致する。1秒間に60フレームの動画を撮影する場合には、撮像間隔は約17msecである。しかし、本実施形態のようにPLL回路によって周波数を追従させる場合、周波数の追従に要する時間はこの撮像間隔に比べて非常に小さいため、次の撮像までの間に周波数は追従する。さらに、一旦、外部基準クロックと内部分周クロックとが同期した後には、同期した状態からの変化にのみ追従すればよいため、より速く同期することになる。

【0040】

このように、本実施形態の平面型X線センサ20においては、外部基準クロックと内部分周クロックを一致させるために、内部駆動信号発生回路50内の基準基準クロックを生成する回路で生成するクロックの周波数を固定ではなく、可変としている。内部基準クロックを、外部基準クロックにあわせて可変とすることで外部基準クロックと内部動作の基準となる内部分周クロックの周波数および位相を一致させることができる。

【0041】

外部基準クロックとは無関係に特定の周波数のクロックを発振して内部基準クロックを生成し、内部同期信号もそのクロックを分周して生成すると、外部基準クロックと内部同期信号との位相を完全に一致させることはできない。つまり、外部基準クロックと内部の処理クロックは非同期の関係となる。この場合、以下のような問題が生じる。

【0042】

X線発生装置10と平面型X線センサ20とが非同期に動作する場合、外部基準クロックは、平面型X線センサ20の処理クロックとは非同期に入力されることになる。動画を撮像する場合は、通常、外部基準クロックは一定の周波数で入力され、平面型X線センサ20も外部基準クロックに合わせて動作する。

【0043】

平面型X線センサ20の動作期間(内部処理の期間)は、X線からの透過線による電荷を取り込む信号蓄積期間と、受け取った電荷を外部装置に転送するための信号処理・転送期間とに分けられる。信号蓄積期間は、内部基準クロックを分周することによって得られるX線の電荷蓄積を決める期間である。このため、信号蓄積期間の長さが変わると蓄積される電荷量も変わってしまう。また、信号処理・転送期間も、処理に所定の時間が必要である。したがって、信号蓄積期間および信号処理・転送期間を動画のフレーム毎に変えることはできない。つまり、内部処理の期間は、いずれのフレームでも実質的に一定である。

【0044】

そこで、外部基準クロックによって、これらの動作の開始タイミングを設定し、一定期間を確保することで、外部基準クロックに追従させる方法がある。この方法では、信号蓄積期間と信号処理・転送期間の和が外部基準クロックの周期より十分短い場合は、待機時間を設けることによって同期をとることができる。逆に、信号蓄期間と信号処理・転送期間の和が、外部基準クロックの周期より長い場合は、たとえば外部基準クロックの2周期毎に1回の信号蓄積および信号処理・転送をするなど、外部基準クロックを間引くことにより、外部基準クロックと同期をとって平面型X線センサを動作させることができる。

【0045】

しかし、外部基準クロックと内部分周クロックがほぼ同じ周期になり内部基準クロックの1周期内の差しかない場合や、外部基準クロックの周期が、信号蓄積時間と信号処理・転送時間の和の周期が整数倍になる場合には、内部処理が外部基準クロックの周期に間に合う場合と間に合わない場合が発生する。間に合う場合には、外部装置から伝達される次の同期信号で次の処理に移ることができるが、間に合わない場合には、次の外部基準クロック1周期分は処理をせず、その次の同期信号で動作が開始することになる。すなわち、同期信号に追従できない期間が発生し、特定のタイミングで1フレーム抜けることになる。

【0046】

つまり、外部基準クロックの周期と内部処理の周期がほぼ一致してしまう場合や外部同期信号が内部処理周期のほぼ整数倍になってしまう場合の問題点は、内部基準クロックの1クロックの期間内で同期ずれが発生するために、固定周期の内部基準クロックでは制御できないことにある。内部基準クロックを分周して作成される内部同期と外部同期では内部クロック1クロックの期間内のずれが発生するため、同期周波数がほぼ一致する場合には、1周期毎、外部基準クロックの周期が内部分周クロックの周期のN倍の場合には、N回の同期ごとに処理が間に合わない期間が発生してしまう。

【0047】

平面センサ内の光電変換素子には、電荷が蓄積される。この電荷は、読み出す必要があるため、TFT構造の素子に接続されている。しかし、TFT構造の半導体を通して電荷が少しずつリークしてしまい、隣接画素や信号線へ電荷が移動してしまう症状が発生する。リーク量は、画素から読み出しをしない場合に発生し、画素によって特性が異なるため、読み出しを行わない時間差が大きいほどリークによる影響が大きくなる。その結果、内部処理が外部基準クロックに追従できない期間が発生した場合、その間でのリーク電荷の影響により、周期内に読み出せる場合と読み出し電荷量が変化し画像輝度が一定にならないという問題が発生する。結果として、特定の周期で動画の画像輝度が揺れる症状となってしまう。

【0048】

しかし、本実施形態では、内部基準クロックを生成する基準クロック生成回路51は、PLL構成をとり、内部基準クロックは電圧制御発振器62により生成される。内部基準クロックは、分周回路63で分周され、外部基準クロックとほぼ同じ周波数の内部分周クロックが生成される。この際、分周回路63の分周比は、外部基準クロックの周期にあわせて電圧制御発振器62の発振範囲を超えないように制御される。

【0049】

その結果、外部基準クロックと内部分周クロックのタイミングが一致し、平面型X線センサ20における処理を開始するタイミング信号であるスタートパルスは、外部基準クロックに対応したタイミングとなる。このように本実施形態によれば、光電変換素子アレイの内部駆動タイミングと外部装置の動作の基準となる外部基準クロックとをできるだけ整合させることができる。

【0050】

したがって、外部基準クロックのある特定期間に平面型X線センサ20が処理できない状況が発生する可能性は極めて小さくなる。動画を撮影している場合には、特定のタイミングで1フレーム抜けてしまう可能性が極めて小さくなる。また、画素34からのリーク電荷の影響を抑制することができる。

【0051】

また、本実施形態によれば、X線発生装置10などの外部装置と平面型X線センサとで同一の基準クロックを用いなくても、フリッカやむらの無い画像を得ることができる。したがって、平面型X線センサとX線発生装置などの外部装置とを独立して設計できる。このため、既存のX線発生装置と本実施形態の平面型X線センサとを組み合わせても、フリッカやむらの無い画像を得ることができる。

【0052】

[第2実施形態]

図8は、第2実施形態による平面型X線センサのブロック図である。

【0053】

本実施形態の平面型X線センサは、第1実施形態の基準クロック生成回路51(図1参照)の代わりに、同期追従回路54を設けたものである。同期追従回路54は、基準発振器72と、周波数判定回路71と、分周回路73と、を有している。

【0054】

基準発振器72は、所定の周波数の固定クロックを生成する。基準発振器72は、たとえば水晶発振器であって、非常に精度の高い周波数の固定クロックを生成する。周波数判定回路71は、外部基準クロックの1周期での固定クロックのクロック数をカウントする。また、周波数判定回路71は、カウントしたクロック数に基づいて分周比を算出する。分周回路73は、基準発振器72が生成した固定クロックをこの分周比で分周して内部基準クロックを生成する。

【0055】

図9は、本実施形態におけるタイミングチャートである。図10は、本実施形態において内部分周クロックの位相が外部基準クロックに対して遅れた場合の変化を示すタイミングチャートである。図11は、本実施形態において内部分周クロックの位相が外部基準クロックに対して進んだ場合の変化を示すタイミングチャートである。

【0056】

周波数判定回路71は、次のようにして分周比を算出する。まず、外部基準クロックの1周期での固定クロックのクロック数をカウントする。次に、ここでカウントしたクロック数を、規定カウント数と比較する。ここで、この規定カウント数とは、内部処理に必要な時間を基準発振器72が発振する固定クロックのクロック数で表したものである。

【0057】

外部基準クロック1周期での固定クロックのカウント数が、規定カウント数で表した値よりも少ない場合を考える。この場合、外部基準クロックの1周期の間に内部処理が完了しないことになる。そこで、このような場合には、外部基準クロックを数パルス間引くことによって、内部処理が可能な最短周期よりも長くなるように外部基準クロックを調整する。たとえば外部基準クロックの2周期毎に、信号蓄積とその信号の読み取り・転送を行うこととする。

【0058】

このようにして、外部基準クロック1周期あるいは所定の周期の間に内部処理が完了するように、内部処理の時間を設定しておく。つまり、外部基準クロック1周期あるいは所定の周期での固定クロックのカウント数が、規定カウント数よりも小さくならないようにしておく。さらに、内部分周クロックの周期を間引かれた外部基準クロックの周期と同一になるように分周比を設定する。

【0059】

次に、外部基準クロック1周期での固定クロックのカウント数が、規定カウント数に比べて多い場合を考える。この場合、基準カウント数を分周比として、内部分周クロックを生成すると、その内部分周クロックの周波数は外部基準クロックの周波数よりも高くなる。したがって、外部基準クロックの1周期よりも短い時間で内部処理は完了する。そこで、内部処理の完了後、基準クロックのいくつかの周期分、次のスタートパルスを遅らせる。つまり分周比を大きくする。これにより、外部基準クロック1周期ごとに、適切に内部処理を完了することができる。

【0060】

外部基準クロックの周期と内部処理の周期とがほぼ一致する場合や、外部基準クロックの周期が内部処理周期のほぼ整数倍する場合以外、つまり、これらの周波数が異なる場合は、周波数の差に応じて、数周期間隔で処理が間に合わないタイミングが発生する。この場合、本実施形態では、内部の基準となるクロックの周波数の調整を行わずに、駆動制御回路24などを制御する。

【0061】

分周回路73は、外部基準クロックにあわせて、基準発振器72が生成した固定クロックを分周して、内部分周クロックを生成する。この内部分周クロックが外部基準クロックと比べて遅れてしまうと、次の外部基準クロック1周期分は処理をせず、その次の同期信号で動作が開始することになる。すなわち、同期信号に追従できない期間が発生し、特定のタイミングで1フレーム抜けることになる。

【0062】

この状態を避けるため、本実施形態では、分周回路73のクロック分周比を必ず外部基準クロックの周期と比べて内部分周クロックの周期が小さくなるように設定する。この分周比を決定するのが、周波数判定回路71である。

【0063】

外部基準クロックの周期が内部処理に要する時間よりも短い場合は、同期信号を数パルス間引くことにより、処理可能な最小周期となるように外部同期信号を調整する。また、内部分周クロックの周期を間引かれた外部同期信号と同一になるように、分周比を調整する。更に、クロック1個分の差によって内部分周クロックに遅れが発生する場合は、分周比を1クロック分少なくすることにより位相遅れが無い様に随時調整を行う。この動作を継続的に行うことによって、外部同期1周期のずれをなくし、1クロック分の時間差で吸収する事ができる。

【0064】

このように本実施形態によれば、光電変換素子アレイの内部駆動タイミングと外部装置の動作の基準となる外部基準クロックとをできるだけ整合させることができる。このときリーク電荷は、同期信号一周期分である数ミリ〜数十ミリ秒の単位から、数十ナノ秒〜数マイクロ秒に圧縮される為、無視できるレベルに低減される。

【0065】

また、本実施形態と第1実施形態を組み合わせてもよい。この場合は、外部基準クロックと内部分周クロックの位相差が固定クロックの1クロック範囲内の違いかどうかを周波数判別回路で判断する。位相差が1クロック範囲外であれば、本実施形態の処理を行い、1クロック内であれば第1実施形態と同様の処理を行う。このような組合せで処理を行うことにより、本実施形態では発生する1クロック分のリーク電荷の影響も避けることができる。

【0066】

[他の実施の形態]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0067】

10…X線発生装置、11…外部基準クロック発生器、12…X線発生器、13…X線、14…撮像対象、20…平面型X線センサ、22…ゲート駆動回路、23…読出回路、24…駆動制御回路、25…画像記憶・転送回路、30…光電変換素子アレイ、31…アレイ基板、32…シンチレータ膜、33…ガラス基板、34…画素、35…薄膜トランジスタ、36…フォトダイオード、37…ゲートライン、38…データライン、39…蓄積キャパシタ、50…内部駆動信号生成回路、51…基準クロック生成回路、52…分周・位相制御回路、53…内部同期信号生成回路、54…同期追従回路、61…位相比較回路、62…電圧制御発振器、63…分周回路、71…周波数判定回路、72…基準発振器、73…分周回路

【特許請求の範囲】

【請求項1】

X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサにおいて、

二次元配列された複数の光電変換素子と前記光電変換素子のそれぞれに対して設けられたスイッチング素子と前記光電変換素子のそれぞれの行に対して設けられて前記スイッチング素子に接続されたゲートラインと前記光電変換素子のそれぞれの列に対して設けられて前記スイッチング素子を介して前記光電変換素子に接続されたデータラインとを有する光電変換素子アレイと、

内部基準クロックを生成する電圧制御発振器と、前記内部基準クロックをあらかじめ定められた分周比で分周して分周クロックを出力する分周回路と、前記外部基準クロックと前記分周クロックとの位相を比較してその位相差を前記電圧制御発振器に入力する位相比較回路と、を備えて前記内部基準クロックに基づいて内部駆動信号を生成する内部駆動信号生成回路と、

前記内部駆動信号に基づいて前記ゲートラインにゲート駆動信号を与えるゲート駆動回路と、

前記内部駆動信号に基づいて前記光電変換素子アレイから前記データラインを介して画素信号を読み出す読出回路と、

を具備することを特徴とする平面型X線センサ。

【請求項2】

前記内部駆動信号生成回路は、所定の周波数の固定クロックを生成する基準発振器と前記外部基準クロックの1周期での前記固定クロックのクロック数をカウントしてそのクロック数に基づいて分周比を算出する周波数判定回路と前記固定クロックを前記分周比で分周して第2内部基準クロックを生成する第2分周回路とを備えた同期追従回路と、をさらに有し、前記周波数判定回路がカウントしたクロック数と所定の規定クロック数との差が所定の値未満であるときは前記内部基準クロックにそれ以外のときは前記第2内部基準クロックに基づいて内部駆動信号を生成することを特徴とする請求項1に記載の平面型X線センサ。

【請求項3】

前記所定の規定クロック数は前記光電変換素子に電荷を蓄積するのに要する時間と前記光電変換素子から画素信号を読み出すのに要する時間を前記固定クロックの数で表した値よりも大きく、前記所定の値は1であることを特徴とする請求項2に記載の平面型X線センサ。

【請求項4】

X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサにおいて、

二次元配列された複数の光電変換素子と前記光電変換素子のそれぞれに対して設けられたスイッチング素子と前記光電変換素子のそれぞれの行に対して設けられて前記スイッチング素子に接続されたゲートラインと前記光電変換素子のそれぞれの列に対して設けられて前記スイッチング素子を介して前記光電変換素子に接続されたデータラインとを有する光電変換素子アレイと、

所定の周波数の固定クロックを生成する基準発振器と、前記外部基準クロックの1周期での前記固定クロックのクロック数をカウントしてそのクロック数に基づいて分周比を算出する周波数判定回路と、前記固定クロックを前記分周比で分周して内部基準クロックを生成する分周回路と、を備えて前記内部基準クロックに基づいて内部駆動信号を生成する内部駆動信号生成回路と、

前記内部駆動信号に基づいて前記ゲートラインにゲート駆動信号を与えるゲート駆動回路と、

前記内部駆動信号に基づいて前記光電変換素子アレイから前記データラインを介して画素信号を読み出す読出回路と、

を具備することを特徴とする平面型X線センサ。

【請求項1】

X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサにおいて、

二次元配列された複数の光電変換素子と前記光電変換素子のそれぞれに対して設けられたスイッチング素子と前記光電変換素子のそれぞれの行に対して設けられて前記スイッチング素子に接続されたゲートラインと前記光電変換素子のそれぞれの列に対して設けられて前記スイッチング素子を介して前記光電変換素子に接続されたデータラインとを有する光電変換素子アレイと、

内部基準クロックを生成する電圧制御発振器と、前記内部基準クロックをあらかじめ定められた分周比で分周して分周クロックを出力する分周回路と、前記外部基準クロックと前記分周クロックとの位相を比較してその位相差を前記電圧制御発振器に入力する位相比較回路と、を備えて前記内部基準クロックに基づいて内部駆動信号を生成する内部駆動信号生成回路と、

前記内部駆動信号に基づいて前記ゲートラインにゲート駆動信号を与えるゲート駆動回路と、

前記内部駆動信号に基づいて前記光電変換素子アレイから前記データラインを介して画素信号を読み出す読出回路と、

を具備することを特徴とする平面型X線センサ。

【請求項2】

前記内部駆動信号生成回路は、所定の周波数の固定クロックを生成する基準発振器と前記外部基準クロックの1周期での前記固定クロックのクロック数をカウントしてそのクロック数に基づいて分周比を算出する周波数判定回路と前記固定クロックを前記分周比で分周して第2内部基準クロックを生成する第2分周回路とを備えた同期追従回路と、をさらに有し、前記周波数判定回路がカウントしたクロック数と所定の規定クロック数との差が所定の値未満であるときは前記内部基準クロックにそれ以外のときは前記第2内部基準クロックに基づいて内部駆動信号を生成することを特徴とする請求項1に記載の平面型X線センサ。

【請求項3】

前記所定の規定クロック数は前記光電変換素子に電荷を蓄積するのに要する時間と前記光電変換素子から画素信号を読み出すのに要する時間を前記固定クロックの数で表した値よりも大きく、前記所定の値は1であることを特徴とする請求項2に記載の平面型X線センサ。

【請求項4】

X線発生装置が外部基準クロックに基づいて所定の時間間隔で発生したX線が被撮影物体を透過したX線画像を撮像する平面型X線センサにおいて、

二次元配列された複数の光電変換素子と前記光電変換素子のそれぞれに対して設けられたスイッチング素子と前記光電変換素子のそれぞれの行に対して設けられて前記スイッチング素子に接続されたゲートラインと前記光電変換素子のそれぞれの列に対して設けられて前記スイッチング素子を介して前記光電変換素子に接続されたデータラインとを有する光電変換素子アレイと、

所定の周波数の固定クロックを生成する基準発振器と、前記外部基準クロックの1周期での前記固定クロックのクロック数をカウントしてそのクロック数に基づいて分周比を算出する周波数判定回路と、前記固定クロックを前記分周比で分周して内部基準クロックを生成する分周回路と、を備えて前記内部基準クロックに基づいて内部駆動信号を生成する内部駆動信号生成回路と、

前記内部駆動信号に基づいて前記ゲートラインにゲート駆動信号を与えるゲート駆動回路と、

前記内部駆動信号に基づいて前記光電変換素子アレイから前記データラインを介して画素信号を読み出す読出回路と、

を具備することを特徴とする平面型X線センサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−70168(P2013−70168A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−206242(P2011−206242)

【出願日】平成23年9月21日(2011.9.21)

【出願人】(000003078)株式会社東芝 (54,554)

【出願人】(503382542)東芝電子管デバイス株式会社 (369)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月21日(2011.9.21)

【出願人】(000003078)株式会社東芝 (54,554)

【出願人】(503382542)東芝電子管デバイス株式会社 (369)

【Fターム(参考)】

[ Back to top ]