広バンドギャップ・バイポーラ・トランジスタ

【課題】ベース・コンタクト(21)が設けられたベース領域(1)と、ベース領域から少数キャリアを抽出するように構成されたエミッタ領域およびコレクタ領域(2、3)と、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための排除構造とを有する縦型構造のバイポーラ・トランジスタを提供する。

【解決手段】ベース領域は、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する。ベースは、ベース・コンタクト(21)からのキャリアの侵入を防止する排除用ヘテロ接合(4)を含むが、その代わりにベース領域は、「高−低」ドーピングホモ接合を備えている。当該構造は、マルチフィンガー・トランジスタにおいてさえも熱暴走に対して改善された抵抗を示す。このことは、高電力、高周波数トランジスタ、例えば、ヒ化ガリウムインジウム上のベース、に対して特に有用である。

【解決手段】ベース領域は、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する。ベースは、ベース・コンタクト(21)からのキャリアの侵入を防止する排除用ヘテロ接合(4)を含むが、その代わりにベース領域は、「高−低」ドーピングホモ接合を備えている。当該構造は、マルチフィンガー・トランジスタにおいてさえも熱暴走に対して改善された抵抗を示す。このことは、高電力、高周波数トランジスタ、例えば、ヒ化ガリウムインジウム上のベース、に対して特に有用である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ベースからの少数キャリアの排除および抽出を行う種類のバイポーラ・トランジスタ、特にベース領域が広いバンドギャップ、すなわち価電子帯と伝導帯の間に広いエネルギー・ギャップを有するトランジスタに関する。

【背景技術】

【0002】

バイポーラ・トランジスタのエミッタ領域とベース領域の間におけるバンドギャップについての相違は、電流増幅率に、そしてfT(fTは、hfcが1より大きくなる最も高い周波数である)の決定に重大な影響を有する。バンドギャップの相違を調整する主たる方法は、ヘテロ接合の片側または両側の半導体組成を変化させることである。

【0003】

ヒ化ガリウムインジウム(GaInAs)材料は、それらがどんなバイポーラ・トランジスタにも最も高いfTを与えるということが示されていることから特に有用である。このタイプのデバイスは、例えばヨーロッパ特許出願第EP0977250号(Daimler Chrysler AG(ダイムラー・クライスラー社))に開示されている。しかしながら、そのようなデバイスにおける開発は性能、例えばfTおよびhfc、を向上させることに集中しており、高周波使用の実用的な限界を扱うことを著しく怠っていた。マイクロ波および無線通信において必要とされるような、高周波動作は、結果として高レベルの熱発生を生じ、そして実際に熱暴走の影響は、動作における制限要素になり得る。

【0004】

よく知られているように、熱暴走は、バイポーラ・デバイスにおいて、エミッタ・コンタクトが順方向にバイアスされているときに起こり得る。例えば、一定不変のベース−エミッタ電圧条件のもとで、デバイスを通る電流が上昇するとき、温度も上昇し、ベース−エミッタのオン電圧を低下させ、それゆえに電流をさらに上昇させることとなる。このタイプの正帰還プロセスは、電流が何らかの方法で制限されない限り、デバイスの損傷を引き起こしかねない。

【0005】

例えば、マルチフィンガー・デバイスにおいて、この熱効果は、実質的にコレクタ電流の全てが一つのフィンガーを通って流れるように、デバイスにおける一つのフィンガーに他のものよりも低いオン電圧を持たせることができる。デバイスの増幅率は、厳しく影響を受けるかもしれず、もし条件が持続することが許されるならば、回復できない損傷が生じ得る。一定不変のベース電流動作においてさえも問題は生じ得る。

【0006】

関連する問題は、一つのフィンガー内にさえもホットスポットが生じ得ることであり、それは、同様に増幅率の激減および/または焼損を引き起こし得る。この現象は、一般に一定不変のベース電圧動作においてのみ生じる。しかしながら、それは、安定化効果、すなわち直列抵抗が不安定状態を減弱させること(例えば、Liou et al.,IEEE Int.Microwave Symp.Dig.,281(1993年)参照)が、存在しないかまたは著しく減弱されている、低いベースおよびエミッタ寄生抵抗を有する最新のデバイスにおいてますます問題となる。

【0007】

上述の考察は、例えば、高電力、高周波信号増幅が、無線周波数信号伝達のために要求される、電話などのモバイル通信デバイスに特に関連性がある。

【0008】

例えば、限定された効果のみを有するが、デバイス内における熱がデバイス全体にわたって均一に広がることを保証することにより(例えば、Bayraktaroglu et al.,IEEE Electron Device Letters,14,493(1993年)を参照)、この問題を緩和する種々の手段が提案されている。提案は、ベースまたはコレクタ安定化抵抗を意図的に組み込むものであり、利得を低減させる所望しない効果を有する。

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明は、そのような制限を克服しようとするものである。

【課題を解決するための手段】

【0010】

本発明は、ベース・コンタクトが設けられたベース領域と、ベース領域から少数キャリアを抽出するように構成されたエミッタ領域およびコレクタ領域と、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための構造とを有し、ベース領域は、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する縦型構造のバイポーラ・トランジスタを提供する。

【0011】

縦型構造のトランジスタにおいては、エミッタとコレクタの間の分離は、材料の成長によって規定され、それゆえ分子線エピタキシーを用いて単分子層の厚みが決定され得る。一実施形態のトランジスタは、ベース層の対向する両側にエミッタ領域およびコレクタ領域を有し、且つ、とりわけ、ベース層の薄さは、高周波動作を、熱暴走の危険のもとではあるが、可能としている。対照的に、水平型構造の(すなわち横型構造の)トランジスタにおけるエミッタ−コレクタ分離は、リソグラフィーによって決定される。結果としての非常に大きい特性長は、エミッタとコレクタの間のはるかに少ない相互作用およびそれゆえに低減された増幅率、ならびに低減されたスピードを提供する。特徴的には、以下に議論されるFujitsuにおけるように、エミッタ領域およびコレクタ領域は、ベース領域の同一の側に横に離間されて配置される。

【0012】

横型構造のトランジスタの例が、JP050114602号公報(Fujitsu)に開示されている。ここでは、ヘテロ構造のベースが、電流増幅率を改善するために設けられているが、しかしながら実際にそれは非常に小さな効果しか持たないであろうと思われる。このトランジスタは、低増幅率のデバイスであろうから、熱暴走の問題が生じると予想されておらず、それはこの特許では扱われていない。唯一の識別し得る材料は、SiC(炭化ケイ素)または「化合物半導体」広ギャップ層を用いる、ケイ素(シリコン)である。

【0013】

記述を簡潔にするために、ベース・コンタクトを経由してベース内への少数キャリアの侵入を妨げるための構造は、今後は、代わりに排除構造と称される。排除構造は、多数キャリアを受け入れるべく作動するが、少数キャリアを供給しない。

【0014】

本発明に従ったトランジスタにおいては、排除構造は、キャリアがベース領域へ侵入するのを防止するための障壁を有する、排除へテロ構造またはヘテロ接合であってもよい。ヘテロ構造は、接合の両側で異なるバンドギャップを有する材料を備えており、例えばこの場合にはp+p+接合(ここで下線は対応するp層のそれよりも広いバンドギャップを示している)である。

【0015】

その代わりに、排除構造は、ベース領域内への少数キャリアの侵入を阻止する、「高−低」差別的にドーピングされたホモ接合(接合の両側で同一のバンドギャップを有し、ドーパントの濃度が、接合の一方の側から他方へ変わる半導体材料)を提供する、ベース領域内に埋め込まれた領域であっても良い。そのような構造は、例えば、同一の半導体材料の隣接する層を構成するが、異なるドーピングまたはキャリアのレベルを有するp++p+接合(+または++は、同一の層タイプに比較して過大ドーピングおよび増大された過大ドーピングを、そして逆に−および−−は、過小ドーピングを示す)であっても良い。理論上では、接合の両側で同一のバンドギャップを有し、そして異なるキャリアのレベルを有する異なる材料を用いることが、少なくとも可能であり、そのためこの構成は、「高−低」ドーピング接合としてより一般的に記述される。しかしながら、異なる材料の格子定数がマッチングさせることは、通常は困難である。

【0016】

ホモ接合の選択肢は、より単純な製作を可能とするだけでなく、所望の場合、ベース領域とエミッタ領域の間に広ギャップパッシベーション層の使用をも可能とする。そのようなパッシベーション層は、さもなければ、漏洩の増大および電流増幅率の低下を生じる、ベース領域内での再結合を低減することによって性能を向上し得る。

【0017】

トランジスタは、高電力III−V族ヘテロ構造バイポーラ・トランジスタ、好ましくは例えば、リン化インジウムおよびヒ化ガリウムインジウムの高周波トランジスタであっても良い。一つの特に適切な形態は、マルチフィンガー・アレイ(すなわちデバイスのボディーは、あらゆる部分からの熱除去を促進すべくフィンガー状に切り分けられており、ベースおよびエミッタ・コンタクトは、電流が、一層容易に入力され且つ出力され得るようにするために、交差指状に互いに入り込んでいる)にレイアウトされたトランジスタである。

【0018】

特に、トランジスタが、III−V族材料に基づいている場合、そのタイプのトランジスタに限定されるわけではないが、エミッタはヘテロ構造であっても良い。そのようなエミッタは、上述されたFujitsuには開示されていない。

【0019】

本発明に従ったデバイスにおいては、熱暴走は、低減され、それゆえ、より高い温度またはより高い電流にて作動される。マルチフィンガー・デバイスの安定性は、例えば安定化抵抗に頼ることなしに、増大する。

【0020】

我々の同時係属中のGB0012925.4号は、ベース領域から少数キャリアを抽出すべく配設されたエミッタ領域およびコレクタ領域と、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための構造(排除構造)とを有し、ベース領域は、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有するバイポーラ・トランジスタを記述し且つ請求の範囲としている。このように、このタイプの構成の使用は、既に知られているが、これは低バンドギャップ材料に関してのみである。しかしながら、この構成は、近年、驚くべきことに、固有伝導が通常の条件下において重要でない、より広いバンドギャップ材料のバイポーラ・トランジスタにおける熱暴走を低減するという予期されていなかった利点を有することが見出された。

【0021】

本発明に使用するのに適する半導体材料は、0.5eVよりも大きいバンドギャップを有し、場合によっては0.52eV、さらには0.55eVまたはそれより大きい値よりも大きいバンドギャップを有する。当該技術において知られているいかなる適切なそのような材料も採用され得るとはいえ、いくつかの望ましい半導体材料は、GaAs、ヒ化ガリウムインジウム(InGaAs)、InGaAsSb、GaN、リン化インジウム(InP)、InGaP、AlGaN、AlGaAs、およびInAlAsである。特に、GaAs、InGaAs、InGaAsSbおよびGaNは、ベース領域に有用な材料であり、そして排除ヘテロ構造においては、InP、InGaP、AlGaN、AlGaAsおよびInAlAsが、有用なワイドギャップ材料である。

【0022】

本発明に従ったトランジスタは、ヘテロ構造またはヘテロ接合デバイスを提供するために、異なるバンドギャップを有する二以上の半導体組成物を備えることが望ましい。ヘテロ構造は、例えば、ベースまたはコレクタ領域において生じ得る。

【0023】

異なるバンドギャップを有して隣接する領域は、異なるドーパント・レベルを有していても良く、例えばヘテロ接合p++p+である。

【0024】

本発明に従ったトランジスタの望ましい形態においては、コレクタ領域は、ヘテロ構造を含んでいる。この構成は、予期されていない程度までの熱暴走を低減することが見出されている。

【0025】

本発明に従ったトランジスタは、当業者に知られている方法を用いて製作され得る。好ましくは、排除構造は、p+p+ヘテロ構造を成長させることの再成長を用いることによって、またはp++p+ホモ構造を生成すべくpタイプのドーパントを注入することによって形成される。

【0026】

本発明に従ったトランジスタは、ベースの上面まで下向きにエッチングする代わりに、エミッタのメサがエッチングされた後に、外因性ベースを覆う適切な場所に広バンドギャップのエミッタ材料を残すことによって、代わりに製作されても良い。そして、広バンドギャップ材料は、(接触抵抗を改善するために)ベース・コンタクトの下側でエッチング除去されるだけであり、および/またはpタイプへタイプ変換するためにベース・コンタクト・インプラントが使用される。広バンドギャップ領域は、外因性ベースの上面に、パッシベーション層を提供し、それは、ベースにおける再結合電流を低減して、電流増幅率を改善する。

【0027】

この出願において提供されている接合の例は、NPNバイポーラ・トランジスタに関連しているけれども、同様の考察は、PNPバイポーラ・トランジスタについて適用されることは理解されるべきである。

【0028】

本発明は、ベース・コンタクトが設けられたベース領域と、ベース領域から少数キャリアを抽出するように構成されたエミッタ領域およびコレクタ領域とを有し、ベース領域が、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する縦型構造のバイポーラ・トランジスタにおいて、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための構造を設けることによって、熱暴走しがちな傾向を低減する方法に及ぶものである。

【0029】

本発明のさらなる特徴および利点は、読者が参照させられる、添付された特許請求の範囲を考察することによって、そして添付図面に関連してなされる以下の本発明の例示的実施の形態のより詳細な説明を読むことによって、明らかになるであろう。

【発明を実施するための最良の形態】

【0030】

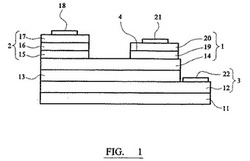

図1は、ベース1、エミッタ2および相対的に大きなコレクタ3を具備するNPNバイポーラ・トランジスタの概略的断面図を示している。排除構造は、p+p+接合へテロ接合4を備えている。この図に関連し且つ図2に使用されている括弧内の数字は、キャリア濃度を示している。

【0031】

nタイプのInGaAs(6×1018)の0.3μm厚のサブコレクタ層12およびnタイプのInGaAs(1×1016)の0.6μmのコレクタ層13は、半絶縁InPの基板層11上に逐次重なっている。pタイプのInGaAs(1×1019)の70nm厚のベース層14は、層13上に重なっており、ベース層14の異なる領域が、nタイプのInP(4×1017)の100nm厚のエミッタ層13およびpタイプのInP(2×1019)の100nm厚の排除ベース・コンタクト層19によって覆われている。層15は、nタイプのInP(2×1018)の100nm厚のエミッタ・キャップ層16、nタイプのInGaAs(1×1019)の150nm厚のエミッタ・コンタクト層17およびエミッタ金属コンタクト層21によって覆われている。層19は、pタイプのInGaAs(2×1019)の100nm厚のベース・キャップ/コンタクト層20およびベース金属コンタクト層21によって覆われている。

【0032】

金属コンタクト層22は、サブコレクタ層12上に設けられている。

【0033】

以下の比較例に使用されている比較デバイスは、上述の図1におけるように構成されているが、ベース・キャップ/コンタクト層20およびベース・コンタクト層19が省略されている。

【0034】

図2は、ベース1、エミッタ2および相対的に大きなコレクタ3を具備するNPNバイポーラ・トランジスタの概略的断面図を示している。排除構造は、p+p+ホモ接合5を備えている。

【0035】

nタイプのInGaAs(6×1018)の0.3μm厚のサブコレクタ層32およびnタイプのInGaAs(1×1016)の0.6μmのコレクタ層33は、半絶縁InPの基板層31上に逐次重なっている。pタイプのInGaAs(1×1019)の70nm厚のベース層34は、層33上に重なっているが、金属ベース・キャップ層41を保持するベース排除コンタクト40を与えるpタイプのInP(2×1019)の局所的な100nm厚の領域を含んでいる。層34は、nタイプのInP(4×1017)の100nm厚のエミッタ層35、nタイプのInP(2×1018)の100nm厚のエミッタ・キャップ層36、nタイプのInGaAs(1×1019)の150nm厚のエミッタ・コンタクト層37およびエミッタ金属コンタクト層38によって覆われている。

【0036】

金属コンタクト層42は、サブコレクタ層12上に設けられている。

【0037】

図3は、二次元(2D)熱/ドリフト拡散モデリングによって得られた通りの、上述された図1のデバイスおよび比較デバイスの熱暴走特性を図解している。図は、Vce=0.8Vにおけるコレクタおよびベース電流(ミクロンあたりアンペア−二次元シミュレーションにおける)対ベース電圧のギュンメル・プロットである。プロットの上側部分51は、コレクタ電流を示し、そして下側部分52は、ベース電流を示しており、そして、排除構造を有する本発明のデバイスは、熱暴走の開始の前に電流のより大きな値を許容していることがわかる。排除コンタクトを有していないデバイスは、Vbeから0.9Vにおけるベースおよびコレクタの両電流における連続する上昇によって示されている通り著しい熱暴走が示されている(デバイスがモデル化されたとき、電流−電圧曲線は、実際に、この点において非常に急峻な勾配を有しており、そして縦軸は、いずれの場合においても指数関数であることが留意されるべきである)。対照的に、本発明のデバイスは、位置55、56によって示される通り少なくとも1.5Vでの安定な出力にとどまる。

【0038】

ベース・コンタクトの付加は、ベース−エミッタ接合の温度係数を著しく低減し、ベース−エミッタの全ての範囲にわたって安定な動作を可能とする。与えられたコレクタ電流のために必要な低減されたベース電流は、電流増幅率が、通常の動作において約10%だけ増大されることも意味している。

【0039】

図4および図5は、0.9Vのベース−エミッタ電圧Vbeにおける図1のトランジスタおよび比較デバイスの温度特性をそれぞれ示す等高線プロットである。カウンターの温度は、矢印AおよびBの方向にそれぞれ増大する。図4においては、図示された最も低い温度領域60は、約330℃におけるものであり、そして図示された最も高い温度領域62は、約375℃におけるものである。図5においては、図示された最も低い温度領域61は、約325℃におけるものであり、そして図示された最も高い温度領域62は、約335℃におけるものである。このように、本発明に従った図5のトランジスタのより低い温度の動作が、明確に説明されている。比較デバイスが非常に高い温度に達し、デバイス故障の頻度を増大させ且つデバイスの耐用年数を著しく低下させることは明らかである。

【図面の簡単な説明】

【0040】

【図1】排除ヘテロ構造を備える本発明のトランジスタの概略的断面図である。

【図2】排除ホモ構造を備える本発明のトランジスタの概略的断面図である。

【図3】図1のトランジスタおよび、排除ヘテロ構造を有さない等価的なデバイスについてのギュンメル・プロットを示すグラフである。

【図4】図1のトランジスタの熱特性を示している。

【図5】排除ヘテロ構造を有さない図1と等価的なデバイスのデバイス熱特性を示している。

【技術分野】

【0001】

本発明は、ベースからの少数キャリアの排除および抽出を行う種類のバイポーラ・トランジスタ、特にベース領域が広いバンドギャップ、すなわち価電子帯と伝導帯の間に広いエネルギー・ギャップを有するトランジスタに関する。

【背景技術】

【0002】

バイポーラ・トランジスタのエミッタ領域とベース領域の間におけるバンドギャップについての相違は、電流増幅率に、そしてfT(fTは、hfcが1より大きくなる最も高い周波数である)の決定に重大な影響を有する。バンドギャップの相違を調整する主たる方法は、ヘテロ接合の片側または両側の半導体組成を変化させることである。

【0003】

ヒ化ガリウムインジウム(GaInAs)材料は、それらがどんなバイポーラ・トランジスタにも最も高いfTを与えるということが示されていることから特に有用である。このタイプのデバイスは、例えばヨーロッパ特許出願第EP0977250号(Daimler Chrysler AG(ダイムラー・クライスラー社))に開示されている。しかしながら、そのようなデバイスにおける開発は性能、例えばfTおよびhfc、を向上させることに集中しており、高周波使用の実用的な限界を扱うことを著しく怠っていた。マイクロ波および無線通信において必要とされるような、高周波動作は、結果として高レベルの熱発生を生じ、そして実際に熱暴走の影響は、動作における制限要素になり得る。

【0004】

よく知られているように、熱暴走は、バイポーラ・デバイスにおいて、エミッタ・コンタクトが順方向にバイアスされているときに起こり得る。例えば、一定不変のベース−エミッタ電圧条件のもとで、デバイスを通る電流が上昇するとき、温度も上昇し、ベース−エミッタのオン電圧を低下させ、それゆえに電流をさらに上昇させることとなる。このタイプの正帰還プロセスは、電流が何らかの方法で制限されない限り、デバイスの損傷を引き起こしかねない。

【0005】

例えば、マルチフィンガー・デバイスにおいて、この熱効果は、実質的にコレクタ電流の全てが一つのフィンガーを通って流れるように、デバイスにおける一つのフィンガーに他のものよりも低いオン電圧を持たせることができる。デバイスの増幅率は、厳しく影響を受けるかもしれず、もし条件が持続することが許されるならば、回復できない損傷が生じ得る。一定不変のベース電流動作においてさえも問題は生じ得る。

【0006】

関連する問題は、一つのフィンガー内にさえもホットスポットが生じ得ることであり、それは、同様に増幅率の激減および/または焼損を引き起こし得る。この現象は、一般に一定不変のベース電圧動作においてのみ生じる。しかしながら、それは、安定化効果、すなわち直列抵抗が不安定状態を減弱させること(例えば、Liou et al.,IEEE Int.Microwave Symp.Dig.,281(1993年)参照)が、存在しないかまたは著しく減弱されている、低いベースおよびエミッタ寄生抵抗を有する最新のデバイスにおいてますます問題となる。

【0007】

上述の考察は、例えば、高電力、高周波信号増幅が、無線周波数信号伝達のために要求される、電話などのモバイル通信デバイスに特に関連性がある。

【0008】

例えば、限定された効果のみを有するが、デバイス内における熱がデバイス全体にわたって均一に広がることを保証することにより(例えば、Bayraktaroglu et al.,IEEE Electron Device Letters,14,493(1993年)を参照)、この問題を緩和する種々の手段が提案されている。提案は、ベースまたはコレクタ安定化抵抗を意図的に組み込むものであり、利得を低減させる所望しない効果を有する。

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明は、そのような制限を克服しようとするものである。

【課題を解決するための手段】

【0010】

本発明は、ベース・コンタクトが設けられたベース領域と、ベース領域から少数キャリアを抽出するように構成されたエミッタ領域およびコレクタ領域と、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための構造とを有し、ベース領域は、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する縦型構造のバイポーラ・トランジスタを提供する。

【0011】

縦型構造のトランジスタにおいては、エミッタとコレクタの間の分離は、材料の成長によって規定され、それゆえ分子線エピタキシーを用いて単分子層の厚みが決定され得る。一実施形態のトランジスタは、ベース層の対向する両側にエミッタ領域およびコレクタ領域を有し、且つ、とりわけ、ベース層の薄さは、高周波動作を、熱暴走の危険のもとではあるが、可能としている。対照的に、水平型構造の(すなわち横型構造の)トランジスタにおけるエミッタ−コレクタ分離は、リソグラフィーによって決定される。結果としての非常に大きい特性長は、エミッタとコレクタの間のはるかに少ない相互作用およびそれゆえに低減された増幅率、ならびに低減されたスピードを提供する。特徴的には、以下に議論されるFujitsuにおけるように、エミッタ領域およびコレクタ領域は、ベース領域の同一の側に横に離間されて配置される。

【0012】

横型構造のトランジスタの例が、JP050114602号公報(Fujitsu)に開示されている。ここでは、ヘテロ構造のベースが、電流増幅率を改善するために設けられているが、しかしながら実際にそれは非常に小さな効果しか持たないであろうと思われる。このトランジスタは、低増幅率のデバイスであろうから、熱暴走の問題が生じると予想されておらず、それはこの特許では扱われていない。唯一の識別し得る材料は、SiC(炭化ケイ素)または「化合物半導体」広ギャップ層を用いる、ケイ素(シリコン)である。

【0013】

記述を簡潔にするために、ベース・コンタクトを経由してベース内への少数キャリアの侵入を妨げるための構造は、今後は、代わりに排除構造と称される。排除構造は、多数キャリアを受け入れるべく作動するが、少数キャリアを供給しない。

【0014】

本発明に従ったトランジスタにおいては、排除構造は、キャリアがベース領域へ侵入するのを防止するための障壁を有する、排除へテロ構造またはヘテロ接合であってもよい。ヘテロ構造は、接合の両側で異なるバンドギャップを有する材料を備えており、例えばこの場合にはp+p+接合(ここで下線は対応するp層のそれよりも広いバンドギャップを示している)である。

【0015】

その代わりに、排除構造は、ベース領域内への少数キャリアの侵入を阻止する、「高−低」差別的にドーピングされたホモ接合(接合の両側で同一のバンドギャップを有し、ドーパントの濃度が、接合の一方の側から他方へ変わる半導体材料)を提供する、ベース領域内に埋め込まれた領域であっても良い。そのような構造は、例えば、同一の半導体材料の隣接する層を構成するが、異なるドーピングまたはキャリアのレベルを有するp++p+接合(+または++は、同一の層タイプに比較して過大ドーピングおよび増大された過大ドーピングを、そして逆に−および−−は、過小ドーピングを示す)であっても良い。理論上では、接合の両側で同一のバンドギャップを有し、そして異なるキャリアのレベルを有する異なる材料を用いることが、少なくとも可能であり、そのためこの構成は、「高−低」ドーピング接合としてより一般的に記述される。しかしながら、異なる材料の格子定数がマッチングさせることは、通常は困難である。

【0016】

ホモ接合の選択肢は、より単純な製作を可能とするだけでなく、所望の場合、ベース領域とエミッタ領域の間に広ギャップパッシベーション層の使用をも可能とする。そのようなパッシベーション層は、さもなければ、漏洩の増大および電流増幅率の低下を生じる、ベース領域内での再結合を低減することによって性能を向上し得る。

【0017】

トランジスタは、高電力III−V族ヘテロ構造バイポーラ・トランジスタ、好ましくは例えば、リン化インジウムおよびヒ化ガリウムインジウムの高周波トランジスタであっても良い。一つの特に適切な形態は、マルチフィンガー・アレイ(すなわちデバイスのボディーは、あらゆる部分からの熱除去を促進すべくフィンガー状に切り分けられており、ベースおよびエミッタ・コンタクトは、電流が、一層容易に入力され且つ出力され得るようにするために、交差指状に互いに入り込んでいる)にレイアウトされたトランジスタである。

【0018】

特に、トランジスタが、III−V族材料に基づいている場合、そのタイプのトランジスタに限定されるわけではないが、エミッタはヘテロ構造であっても良い。そのようなエミッタは、上述されたFujitsuには開示されていない。

【0019】

本発明に従ったデバイスにおいては、熱暴走は、低減され、それゆえ、より高い温度またはより高い電流にて作動される。マルチフィンガー・デバイスの安定性は、例えば安定化抵抗に頼ることなしに、増大する。

【0020】

我々の同時係属中のGB0012925.4号は、ベース領域から少数キャリアを抽出すべく配設されたエミッタ領域およびコレクタ領域と、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための構造(排除構造)とを有し、ベース領域は、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有するバイポーラ・トランジスタを記述し且つ請求の範囲としている。このように、このタイプの構成の使用は、既に知られているが、これは低バンドギャップ材料に関してのみである。しかしながら、この構成は、近年、驚くべきことに、固有伝導が通常の条件下において重要でない、より広いバンドギャップ材料のバイポーラ・トランジスタにおける熱暴走を低減するという予期されていなかった利点を有することが見出された。

【0021】

本発明に使用するのに適する半導体材料は、0.5eVよりも大きいバンドギャップを有し、場合によっては0.52eV、さらには0.55eVまたはそれより大きい値よりも大きいバンドギャップを有する。当該技術において知られているいかなる適切なそのような材料も採用され得るとはいえ、いくつかの望ましい半導体材料は、GaAs、ヒ化ガリウムインジウム(InGaAs)、InGaAsSb、GaN、リン化インジウム(InP)、InGaP、AlGaN、AlGaAs、およびInAlAsである。特に、GaAs、InGaAs、InGaAsSbおよびGaNは、ベース領域に有用な材料であり、そして排除ヘテロ構造においては、InP、InGaP、AlGaN、AlGaAsおよびInAlAsが、有用なワイドギャップ材料である。

【0022】

本発明に従ったトランジスタは、ヘテロ構造またはヘテロ接合デバイスを提供するために、異なるバンドギャップを有する二以上の半導体組成物を備えることが望ましい。ヘテロ構造は、例えば、ベースまたはコレクタ領域において生じ得る。

【0023】

異なるバンドギャップを有して隣接する領域は、異なるドーパント・レベルを有していても良く、例えばヘテロ接合p++p+である。

【0024】

本発明に従ったトランジスタの望ましい形態においては、コレクタ領域は、ヘテロ構造を含んでいる。この構成は、予期されていない程度までの熱暴走を低減することが見出されている。

【0025】

本発明に従ったトランジスタは、当業者に知られている方法を用いて製作され得る。好ましくは、排除構造は、p+p+ヘテロ構造を成長させることの再成長を用いることによって、またはp++p+ホモ構造を生成すべくpタイプのドーパントを注入することによって形成される。

【0026】

本発明に従ったトランジスタは、ベースの上面まで下向きにエッチングする代わりに、エミッタのメサがエッチングされた後に、外因性ベースを覆う適切な場所に広バンドギャップのエミッタ材料を残すことによって、代わりに製作されても良い。そして、広バンドギャップ材料は、(接触抵抗を改善するために)ベース・コンタクトの下側でエッチング除去されるだけであり、および/またはpタイプへタイプ変換するためにベース・コンタクト・インプラントが使用される。広バンドギャップ領域は、外因性ベースの上面に、パッシベーション層を提供し、それは、ベースにおける再結合電流を低減して、電流増幅率を改善する。

【0027】

この出願において提供されている接合の例は、NPNバイポーラ・トランジスタに関連しているけれども、同様の考察は、PNPバイポーラ・トランジスタについて適用されることは理解されるべきである。

【0028】

本発明は、ベース・コンタクトが設けられたベース領域と、ベース領域から少数キャリアを抽出するように構成されたエミッタ領域およびコレクタ領域とを有し、ベース領域が、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する縦型構造のバイポーラ・トランジスタにおいて、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための構造を設けることによって、熱暴走しがちな傾向を低減する方法に及ぶものである。

【0029】

本発明のさらなる特徴および利点は、読者が参照させられる、添付された特許請求の範囲を考察することによって、そして添付図面に関連してなされる以下の本発明の例示的実施の形態のより詳細な説明を読むことによって、明らかになるであろう。

【発明を実施するための最良の形態】

【0030】

図1は、ベース1、エミッタ2および相対的に大きなコレクタ3を具備するNPNバイポーラ・トランジスタの概略的断面図を示している。排除構造は、p+p+接合へテロ接合4を備えている。この図に関連し且つ図2に使用されている括弧内の数字は、キャリア濃度を示している。

【0031】

nタイプのInGaAs(6×1018)の0.3μm厚のサブコレクタ層12およびnタイプのInGaAs(1×1016)の0.6μmのコレクタ層13は、半絶縁InPの基板層11上に逐次重なっている。pタイプのInGaAs(1×1019)の70nm厚のベース層14は、層13上に重なっており、ベース層14の異なる領域が、nタイプのInP(4×1017)の100nm厚のエミッタ層13およびpタイプのInP(2×1019)の100nm厚の排除ベース・コンタクト層19によって覆われている。層15は、nタイプのInP(2×1018)の100nm厚のエミッタ・キャップ層16、nタイプのInGaAs(1×1019)の150nm厚のエミッタ・コンタクト層17およびエミッタ金属コンタクト層21によって覆われている。層19は、pタイプのInGaAs(2×1019)の100nm厚のベース・キャップ/コンタクト層20およびベース金属コンタクト層21によって覆われている。

【0032】

金属コンタクト層22は、サブコレクタ層12上に設けられている。

【0033】

以下の比較例に使用されている比較デバイスは、上述の図1におけるように構成されているが、ベース・キャップ/コンタクト層20およびベース・コンタクト層19が省略されている。

【0034】

図2は、ベース1、エミッタ2および相対的に大きなコレクタ3を具備するNPNバイポーラ・トランジスタの概略的断面図を示している。排除構造は、p+p+ホモ接合5を備えている。

【0035】

nタイプのInGaAs(6×1018)の0.3μm厚のサブコレクタ層32およびnタイプのInGaAs(1×1016)の0.6μmのコレクタ層33は、半絶縁InPの基板層31上に逐次重なっている。pタイプのInGaAs(1×1019)の70nm厚のベース層34は、層33上に重なっているが、金属ベース・キャップ層41を保持するベース排除コンタクト40を与えるpタイプのInP(2×1019)の局所的な100nm厚の領域を含んでいる。層34は、nタイプのInP(4×1017)の100nm厚のエミッタ層35、nタイプのInP(2×1018)の100nm厚のエミッタ・キャップ層36、nタイプのInGaAs(1×1019)の150nm厚のエミッタ・コンタクト層37およびエミッタ金属コンタクト層38によって覆われている。

【0036】

金属コンタクト層42は、サブコレクタ層12上に設けられている。

【0037】

図3は、二次元(2D)熱/ドリフト拡散モデリングによって得られた通りの、上述された図1のデバイスおよび比較デバイスの熱暴走特性を図解している。図は、Vce=0.8Vにおけるコレクタおよびベース電流(ミクロンあたりアンペア−二次元シミュレーションにおける)対ベース電圧のギュンメル・プロットである。プロットの上側部分51は、コレクタ電流を示し、そして下側部分52は、ベース電流を示しており、そして、排除構造を有する本発明のデバイスは、熱暴走の開始の前に電流のより大きな値を許容していることがわかる。排除コンタクトを有していないデバイスは、Vbeから0.9Vにおけるベースおよびコレクタの両電流における連続する上昇によって示されている通り著しい熱暴走が示されている(デバイスがモデル化されたとき、電流−電圧曲線は、実際に、この点において非常に急峻な勾配を有しており、そして縦軸は、いずれの場合においても指数関数であることが留意されるべきである)。対照的に、本発明のデバイスは、位置55、56によって示される通り少なくとも1.5Vでの安定な出力にとどまる。

【0038】

ベース・コンタクトの付加は、ベース−エミッタ接合の温度係数を著しく低減し、ベース−エミッタの全ての範囲にわたって安定な動作を可能とする。与えられたコレクタ電流のために必要な低減されたベース電流は、電流増幅率が、通常の動作において約10%だけ増大されることも意味している。

【0039】

図4および図5は、0.9Vのベース−エミッタ電圧Vbeにおける図1のトランジスタおよび比較デバイスの温度特性をそれぞれ示す等高線プロットである。カウンターの温度は、矢印AおよびBの方向にそれぞれ増大する。図4においては、図示された最も低い温度領域60は、約330℃におけるものであり、そして図示された最も高い温度領域62は、約375℃におけるものである。図5においては、図示された最も低い温度領域61は、約325℃におけるものであり、そして図示された最も高い温度領域62は、約335℃におけるものである。このように、本発明に従った図5のトランジスタのより低い温度の動作が、明確に説明されている。比較デバイスが非常に高い温度に達し、デバイス故障の頻度を増大させ且つデバイスの耐用年数を著しく低下させることは明らかである。

【図面の簡単な説明】

【0040】

【図1】排除ヘテロ構造を備える本発明のトランジスタの概略的断面図である。

【図2】排除ホモ構造を備える本発明のトランジスタの概略的断面図である。

【図3】図1のトランジスタおよび、排除ヘテロ構造を有さない等価的なデバイスについてのギュンメル・プロットを示すグラフである。

【図4】図1のトランジスタの熱特性を示している。

【図5】排除ヘテロ構造を有さない図1と等価的なデバイスのデバイス熱特性を示している。

【特許請求の範囲】

【請求項1】

ベース・コンタクトが設けられたベース領域と、ベース領域から少数キャリアを抽出するように構成されたエミッタ領域およびコレクタ領域と、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための構造とを有する縦型構造のバイポーラ・トランジスタであって、ベース領域は、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する、バイポーラ・トランジスタ。

【請求項2】

少数キャリアの侵入を妨げるための構造は、ヘテロ構造を含んでいる、請求項1に記載のトランジスタ。

【請求項3】

少数キャリアの侵入を妨げるための構造は、差別的なドーピングを伴うホモ構造を含んでいる、請求項1に記載のトランジスタ。

【請求項4】

トランジスタはIII−V族材料に基づく、請求項1から3のいずれか一項に記載のトランジスタ。

【請求項5】

ベース領域は、GaAs、InGaAs、InGaAsSb、またはGaNを含んでいる、請求項1から4のいずれか一項に記載のトランジスタ。

【請求項6】

侵入を妨げるための構造は、InP、InGaP、AlGaN、AlGaAsまたはInAlAsを含んでいる、請求項1から5のいずれか一項に記載のトランジスタ。

【請求項7】

トランジスタはヘテロ構造である、請求項1から6のいずれか一項に記載のトランジスタ。

【請求項8】

トランジスタは高周波トランジスタである、請求項1から7のいずれか一項に記載のトランジスタ。

【請求項9】

トランジスタは、マルチフィンガー・アレイ構造から構成される、請求項1から8のいずれか一項に記載のトランジスタ。

【請求項10】

前記バンドギャップは、0.52eVよりも大きい、請求項1から9のいずれか一項に記載のトランジスタ。

【請求項11】

トランジスタは、ヘテロ構造のエミッタ領域を有する、請求項1から10のいずれか一項に記載のトランジスタ。

【請求項12】

トランジスタは、ヘテロ構造コレクタ領域を有する、請求項1から11のいずれか一項に記載のトランジスタ。

【請求項13】

ヘテロ構造領域は、InP、InGaP、AlGaN、AlGaAsおよびInAlAsから選択された広ギャップ材料を備える、請求項11または12に記載のトランジスタ。

【請求項14】

ベース・コンタクトが設けられたベース領域と、ベース領域から少数キャリアを抽出すべく配設されたエミッタ領域およびコレクタ領域とを有し、ベース領域が、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する、縦型構造のバイポーラ・トランジスタにおいて、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための構造を設けることによって、熱暴走しがちな傾向を低減する方法。

【請求項1】

ベース・コンタクトが設けられたベース領域と、ベース領域から少数キャリアを抽出するように構成されたエミッタ領域およびコレクタ領域と、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための構造とを有する縦型構造のバイポーラ・トランジスタであって、ベース領域は、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する、バイポーラ・トランジスタ。

【請求項2】

少数キャリアの侵入を妨げるための構造は、ヘテロ構造を含んでいる、請求項1に記載のトランジスタ。

【請求項3】

少数キャリアの侵入を妨げるための構造は、差別的なドーピングを伴うホモ構造を含んでいる、請求項1に記載のトランジスタ。

【請求項4】

トランジスタはIII−V族材料に基づく、請求項1から3のいずれか一項に記載のトランジスタ。

【請求項5】

ベース領域は、GaAs、InGaAs、InGaAsSb、またはGaNを含んでいる、請求項1から4のいずれか一項に記載のトランジスタ。

【請求項6】

侵入を妨げるための構造は、InP、InGaP、AlGaN、AlGaAsまたはInAlAsを含んでいる、請求項1から5のいずれか一項に記載のトランジスタ。

【請求項7】

トランジスタはヘテロ構造である、請求項1から6のいずれか一項に記載のトランジスタ。

【請求項8】

トランジスタは高周波トランジスタである、請求項1から7のいずれか一項に記載のトランジスタ。

【請求項9】

トランジスタは、マルチフィンガー・アレイ構造から構成される、請求項1から8のいずれか一項に記載のトランジスタ。

【請求項10】

前記バンドギャップは、0.52eVよりも大きい、請求項1から9のいずれか一項に記載のトランジスタ。

【請求項11】

トランジスタは、ヘテロ構造のエミッタ領域を有する、請求項1から10のいずれか一項に記載のトランジスタ。

【請求項12】

トランジスタは、ヘテロ構造コレクタ領域を有する、請求項1から11のいずれか一項に記載のトランジスタ。

【請求項13】

ヘテロ構造領域は、InP、InGaP、AlGaN、AlGaAsおよびInAlAsから選択された広ギャップ材料を備える、請求項11または12に記載のトランジスタ。

【請求項14】

ベース・コンタクトが設けられたベース領域と、ベース領域から少数キャリアを抽出すべく配設されたエミッタ領域およびコレクタ領域とを有し、ベース領域が、0.5eVよりも大きいバンドギャップおよび1017cm−3よりも大きいドーピング・レベルを有する、縦型構造のバイポーラ・トランジスタにおいて、ベース・コンタクトを経由してベース領域内への少数キャリアの侵入を妨げるための構造を設けることによって、熱暴走しがちな傾向を低減する方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2008−258651(P2008−258651A)

【公開日】平成20年10月23日(2008.10.23)

【国際特許分類】

【外国語出願】

【出願番号】特願2008−154287(P2008−154287)

【出願日】平成20年6月12日(2008.6.12)

【分割の表示】特願2003−557046(P2003−557046)の分割

【原出願日】平成14年12月23日(2002.12.23)

【出願人】(501352882)キネテイツク・リミテツド (93)

【Fターム(参考)】

【公開日】平成20年10月23日(2008.10.23)

【国際特許分類】

【出願番号】特願2008−154287(P2008−154287)

【出願日】平成20年6月12日(2008.6.12)

【分割の表示】特願2003−557046(P2003−557046)の分割

【原出願日】平成14年12月23日(2002.12.23)

【出願人】(501352882)キネテイツク・リミテツド (93)

【Fターム(参考)】

[ Back to top ]