広帯域PLL発振回路

【課題】周波数逓倍回路を含む広帯域PLL発振回路において、逓倍回路出力端に高調波等の不要周波数信号を除去するフィルタを必要とせず、簡単な構成によって不要周波数信号に起因して間違った周波数に同期することなく、安定した動作が得られる広帯域PLL発振回路を提供する。

【解決手段】

逓倍回路に同調周波数制御機能を備え、発振周波数に応じて適切な同調周波数になるように制御する。また、PLLロックインまでの時間短縮のためにメモリに記憶した制御電圧情報をVCOに印加する機能を備え、この制御電圧情報によって同時に逓倍回路の同調周波数を制御する。

【解決手段】

逓倍回路に同調周波数制御機能を備え、発振周波数に応じて適切な同調周波数になるように制御する。また、PLLロックインまでの時間短縮のためにメモリに記憶した制御電圧情報をVCOに印加する機能を備え、この制御電圧情報によって同時に逓倍回路の同調周波数を制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、広帯域PLL発振回路に関し、詳細にはフェーズロックループ中に逓倍回路を挿入したPLL発振回路において、簡単な構成によって、不要周波数信号成分による誤動作を防止したPLL発振回路の改良に関する。

【背景技術】

【0002】

無線通信機では、送受信用に高い周波数安定度をもった発振回路を備えており、この発振回路から出力される周波数信号に基づいて装置各部の制御及び、信号処理のための信号や搬送波信号等を生成している。また、携帯電話機や警察・消防用無線機等に代表される移動用無線通信機においては、頻繁に発振周波数を変更する必要があるものが多く、これらの発振回路としては、従来からフェーズドロックループ発振回路(Phase Locked Loop Oscillator;以下「PLL発振回路」)が使用されている。

図6は、従来のPLL発振回路の一例を示す回路図である。この回路は、位相比較器(Phase Detector:PD)を含むPLL IC101と、位相比較器の出力を直流信号に平滑するループフィルタ102と、平滑された直流信号(電圧)によって発振周波数が制御される電圧制御発振器(Voltage Controlled Oscillator;以下「VCO」)103と、このVCOの出力信号のレベルを安定化させるバッファアンプ(BUFF AMP)104と、バッファアンプ104の出力信号の周波数を、例えば2倍する逓倍回路105と、をループ状に接続したもので、上記PLL IC101には、基準周波数信号(参照周波数信号)として、外部からFrefが供給されるか、又は、PLL ICの内部で、基準周波数信号Frefを発生し、位相比較器に供給するように構成されている。

【0003】

また、周波数を変更する手段として図示を省略した可変分周回路をPLLループ中に設け、その分周比を変更することによって基準周波数に同期した所望の周波数信号を発生するように構成することもできる。更に、この例ではメモリ106と、デジタル信号をアナログ信号に変換するデジタル/アナログ変換器(D/A)107を備えている。破線で囲った逓倍回路を備えたPLL発振回路についての各ブロックの動作や機能については既知であるので詳細な説明は省略するが、PLL回路では、周波数を切替える際や電源投入時に、基準周波数信号にPLLループの動作が同期するまでに若干時間を要する。

そこで、PLLループが基準周波数に同期するまでの時間を短縮するために、ロックスピード高速化手段として、メモリ106にVCO103の制御電圧情報が記録されていて、周波数変更や、電源投入時に上述した周波数変更手段と連動して、メモリ106から読み出したVCO制御電圧情報をD/A107によって所要の直流電圧に変換し、VCOの周波数制御電圧として供給するように構成されている。

【0004】

図7は、ロックスピード高速化のために制御電圧情報をメモリに記録しておき、周波数を切替えた際に強制的にVCOに供給するための周波数制御電圧(Vcont)とVCOの発振周波数(VCOf)との関係の一例を示した図である。この例では、制御電圧(Vcont)がVHと高くなるとVCO発振周波数がfHと高くなり、制御電圧(Vcont)がVLと低くなるとVCO発振周波数がfLと低くなる場合を示している。同期した際の制御電圧を強制的に印加すると、PLL回路は、その制御電圧をスタート電圧として、ロック引き込み動作に移行するので、迅速なPLL同期が達成され直ちに正確な発振周波数信号が得られる。

【特許文献1】特開平6-326606号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、PLLのループ中に逓倍回路が挿入されると、逓倍された所望周波数信号以外に、基本波及び所望周波数信号以外の高調波等の不要周波数成分が発生する。

図8(a)は、逓倍回路出力に含まれる周波数スペクトルの一例を示す図で、この例では逓倍回路が2逓倍回路、発振周波数が受信周波数帯域frと送信周波数帯域ftに分けられている場合を示している。逓倍回路の出力には、基本周波数信号fr、ftと、2倍された帰還信号(PLL ICの位相比較器に帰還させる希望周波数信号)2fr、2ftと、さらに基本周波数信号の高調波信号である3fr、3ft、・・・nfr、nft、・・が含まれる。この逓倍回路の出力信号として必要な成分は図8(b)に示すように、2fr、2ft成分のみであり、それ以外の周波数成分が含まれると、間違った周波数にPLL回路がロックし、あるいはロック外れが発生する。更に、送信周波数と受信周波数との関係によっては、図8(a)に示すように、帰還信号帯域内において送受信周波数帯域の一部に不要波が重なる場合が発生し、所望しない周波数帯域にPLLがロックすることが有り得る。

そこで、これらの不具合に対処する方法として、例えば特許文献1に提案されているように、逓倍回路と位相比較器の間に、所望の逓倍周波数のみを通過するバンドパスフィルタ(BPF)を挿入するものが知られている。更に、広帯域にするために、そのバンドパスフィルタの通過帯域周波数を制御可能に構成することが提案されている。この方法によれば、選択すべき周波数に対応して、バンドパスフィルタの通過域周波数を制御することによって、希望波以外の周波数信号を排除して、安定した正確な発振周波数信号を得ることができる。

【0006】

図9は、特許文献1を参照して構成した逓倍回路を含むPLL発振回路の概要ブロック図であり、この回路が上記図6と異なる点は、逓倍回路105の出力端に、送信用フィルタ108と受信用フィルタ109と、これら二つのフィルタを切替える送信/受信切替制御部110を備えたところである。この構成によれば、送信時と受信時に夫々のフィルタのみを機能させることによって、それ以外の周波数成分が位相比較器を含むPLL IC101に帰還することを防止するので、安定した発振動作を維持できる。

しかしながら、図9からも明らかなように、逓倍回路出力端に送受信フィルタを備え、それらを切替える構成では、回路構成が複雑となり通信機の小型化が妨げられる上、制御が複雑となると云う新たな問題を含むものであった。

本発明は、従来の広帯域PLL発振回路の諸問題を解決するためになされたものであって、簡単な構成によって、広帯域にわたって発振周波数を変化させても、安定した発振出力が得られる広帯域PLL発振回路を提供することを目的としている。

【課題を解決するための手段】

【0007】

本発明はかかる課題を解決するために、請求項1記載の広帯域PLL発振回路は、電圧信号によって発振周波数を制御する電圧制御発振器と、この電圧制御発振器の出力信号と基準周波数信号とを比較して両者の周波数差又は位相差に応じた信号を出力する位相比較器と、上記位相比較器の出力信号から低域信号成分を取り出し電圧制御発振器の制御信号として供給するフィルタと、をループ状に接続したPLL発振回路において、更に、上記電圧制御発振器の制御電圧情報を記憶した制御電圧メモリと、上記電圧制御発振器と位相比較器との間に挿入され、同調周波数を変更する機能をもった逓倍回路と、発振周波数に対応して上記制御電圧メモリから読み出した所要の制御電圧情報に基づいて、電圧制御発振器の発振周波数と逓倍回路の同調周波数を制御する周波数制御手段とを備えたことを特徴としている。

【0008】

請求項2記載の発明は、請求項1記載の広帯域PLL発振回路において、上記逓倍回路は、同調周波数の異なる複数の逓倍回路を備え、発振周波数に応じて、所要の逓倍回路を選択的に機能させる逓倍回路選択手段を備えたことを特徴としている。

請求項3記載の発明は、請求項1又は2記載の広帯域PLL発振回路において、上記逓倍回路は、電圧/電流によってリアクタンス値が変化する可変リアクタンス素子を含み、且つ、上記制御電圧メモリから出力するデジタル信号をアナログ信号に変換するデジタル・アナログ変換器を備え、変換したアナログ信号によって、可変リアクタンス素子を制御するように構成したことを特徴としている。

【発明の効果】

【0009】

本発明は、逓倍回路を備えたPLL発振回路において、逓倍回路に同調周波数を制御する機能を備え、発振周波数に応じて、その同調周波数を制御するように構成したので、従来のように、別途バンドパスフィルタを用いる必要が無く、回路構成が簡単になり装置の小型化が可能となる。更に、PLL回路のロックスピード高速化のためにVCO制御電圧情報メモリのデータを備えたものである場合は、そのVCO制御電圧情報メモリのデータを逓倍回路の同調周波数制御のために利用すれば、新たに付加する回路や部品点数が少なくなる。また、同調周波数帯域が異なる複数の逓倍回路を備えて、選択的に機能させるように構成すれば、更に広帯域のPLL発振回路として機能させることが可能であり、しかも、同調回路の同調帯域を狭帯域にすれば、減衰特性が急峻なものにできるので、不要波の除去能力を高めることもできる。従って、広い範囲にわたって発振周波数を切替える場合であっても、ロックスピードを高速化しつつ、不要周波数に間違ってロックすることなく、安定した発振周波数信号を得ることが可能となる。

【発明を実施するための最良の形態】

【0010】

以下、本発明を図に示した実施形態を用いて詳細に説明する。但し、この実施形態に記載される構成要素、種類、組み合わせ、形状、その相対配置などは特定的な記載がない限り、この発明の範囲をそれのみに限定する主旨ではなく単なる説明例に過ぎない。以下本発明の実施態様例について説明する。

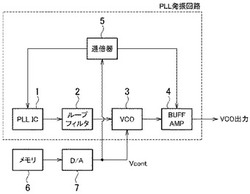

図1は、本発明に係る広帯域PLL発振回路の一実施形態を示すブロック図である。この例に示すPLL発振回路は、図示を省略した位相比較器(Phase Detector:PD)やチャージポンプを含むPLL IC1と、位相比較器の出力を直流信号に平滑するループフィルタ2と、平滑された直流信号(電圧)によって発振周波数が制御される電圧制御発振器(Voltage Controlled Oscillator;以下「VCO」)3と、このVCOの出力信号のレベルを安定化させるバッファアンプ(BUFF AMP)4と、バッファアンプ4の出力信号を例えば2逓倍する逓倍回路5と、を図示したようにループ状に接続したもので、上記PLL IC1には、基準周波数信号として、Frefが供給されるか、又は、PLL ICの内部で、基準周波数信号Frefを発生し、位相比較器に供給するように構成されている。また、上記図6に関連して説明した例と同様に、周波数を変更する手段として図示を省略した可変分周回路をPLLループ中に設け、その分周比を変更することによって基準周波数に同期した所望の周波数信号を発生するように構成することもできる。

【0011】

この構成において特徴的な点は、上記逓倍回路5が同調周波数を変更する機能をもったものであること、及び、発振周波数に対応して所要のVCO制御電圧情報を制御電圧メモリ6から読み出し、アナログ信号に変換して電圧制御発振器(VCO)3と逓倍回路5に供給する周波数制御機能を備えたことである。この特徴によって、逓倍回路5とPLL IC1との間にバンドパスフィルタを不要にすることができる。即ち、図2は、上記図1に示す広帯域PLL発振回路の基本的な動作及び機能を説明する図であって、図2(a)は、上記図8(a)と同様に2逓倍回路内部において発生する周波数成分を示す周波数スペクトル図であるが、図2(b)に示すように、この実施例において使用する逓倍回路5の同調周波数が狭帯域フィルタ機能と同様に動作するとともに、その同調周波数を変更可能とすることによって必要な周波数成分のみが出力されるものである。

なお、同調周波数を変更可能な逓倍回路としては、例えば、可変容量ダイオードのように電流/電圧(電流値や電圧値)によって容量等のリアクタンス値が変化する素子を含む同調回路を、逓倍回路の入力部や出力部の少なくとも一方に備えた構成にするものが考えられる。

図1及び図2(b)に示すように構成すれば、送信周波数帯域及び受信周波数帯域の両方に亘って、その時々において必要な発振周波数に対応する同調特性を選択することが可能であり、不要周波数成分を排除し、必要な周波数成分のみを位相比較器(PLL IC)に導き、間違った周波数にPLL回路がロックすることなく安定した発振周波数を得ることができる。

【0012】

図3は、本発明の変形実施例を示す概要ブロック図である。この構成の特徴は、図1に示した逓倍回路5を、送信用逓倍回路5−1と受信用逓倍回路5−2に分離した点である。

即ち、逓倍回路の同調周波数帯域を広帯域化することには限界があるので、その限界を超えて更に広帯域化する場合に、送信周波数帯域用の逓倍回路と、受信周波数帯域用の逓倍回路として、同調周波数帯域が異なる複数の逓倍回路を使用するものである。なお、この構成においては、複数の逓倍回路のうちから必要なものを選択するために送信/受信切替制御部8を備え、二つの逓倍回路5−1、5−2のいずれか一方を機能させるとともに、メモリ6とD/A7によって発生するVCO制御電圧信号、又はその信号に基づいて生成した制御信号によって、機能させた逓倍回路の同調回路のリアクタンス素子等を制御して、同調特性を所望のものとする。

このように、VCO3の発振周波数を変化させる際に、同一の周波数制御電圧Vcontによって、もしくは、周波数制御電圧Vcontに基づいて作出した逓倍回路の同調周波数制御信号によって、狭帯域同調特性をもった逓倍回路として機能させ、しかも通過帯域を所要値に変更できるように構成したので、急峻な減衰特性により不要周波数成分を十分に除去することができ、従って、簡単な構成によって、広帯域に亘ってPLLにおけるロック周波数を所望値に安定化させることができる。

なお、逓倍回路の入力部にも周波数選択用の同調回路を設ければ、バッファアンプ4において発生するノイズや歪み成分、高調波成分が逓倍回路に入力することを防止できるので、より一層、不要波除去機能が高くなる。

【0013】

図4は、本発明において使用する同調周波数可変機能を備えた逓倍回路の一実施例を示す回路図である。この例に示す逓倍回路10は、増幅素子として使用するトランジスタTr、そのベースバイアス用抵抗R1、R2、コレクタ負荷インダクタンスL、エミッタ抵抗RE、エミッタ容量CEを含む逓倍用の増幅回路と、容量C1、C2、可変容量ダイオードVc1、Vc2、インダクタンス素子(コイル)L1、L2、結合容量Cc、からなる周波数可変型同調回路と、を含んでいる。なお回路中のCは直流阻止用の容量素子(コンデンサ)である。

このように構成した逓倍回路10は、信号入力端INにバッファアンプ4の出力信号を供給すると、トランジスタ増幅回路の非直線成分によって、高調波が発生する。高調波の発生はトランジスタTrのベースバイアスによっても変化するので、所望の逓倍数に応じて適宜バイアス値が設定される。また、同調回路には、所要値の容量素子(コンデンサ)C1、C2と直列に可変容量ダイオードVc1、Vc2が接続されているので、可変容量ダイオードに供給する直流電圧(Vcont)によって、同調周波数が変化する。この例では、上述したVCO周波数制御電圧(Vcont)によって制御するので、VCO制御電圧によって必要な同調周波数となるように同調回路の容量(C1、C2)と可変容量ダイオードVc1、Vc2の関係を設定する必要がある。なお、容量C1、C2を単なる直流阻止用コンデンサとすることもでき、その場合は、可変容量ダイオードVc1、Vc2による容量値の変化が、逓倍回路の同調周波数に対して支配的となる。この回路は図1及び図3に示した、何れの回路にも使用可能である。

【0014】

図5は、更に、本発明において使用する逓倍回路の、他の実施例を示す回路図である。この例が上記図4と相違する点は、入力側にも可変周波数型の同調回路を備えたところである。即ち、逓倍回路の入力端に、結合トランス用のインダクタンスL3と、このトランスの二次側インダクタンスと同調回路を形成するように接続した、容量(コンデンサ)C3と可変容量ダイオードVc3の直列回路を備え、上記可変容量ダイオードVc3にもVCO周波数制御電圧(Vcont)を供給することによって、入力信号として選択すべき周波数信号のみを通過するように、コンデンサC3、可変容量ダイオードVc3の値が設定されている。例えば、VCO3の出力信号に同調するように設定すれば、バッファアンプの歪みによって発生する高調波が逓倍回路に流入しないので、一層、PLL発振回路が安定して動作するようになる。

【0015】

以上、本発明の実施例について説明したが、本発明はこれらの例に限定することなく種々変形が可能である。例えば、逓倍回路の出力端に備える同調回路として、図4、図5に示すように、2段のLC同調回路を接続したが、一つの同調回路にしても良いし、3段以上の同調回路を連結した回路であってもよい。また、図5に示すように入力端に同調回路を挿入する場合においても、複数段の同調回路を連結するものであっても構わない。更に、夫々の可変容量ダイオードの制御信号として、VCO制御電圧信号をそのまま使用する例を示したが、この例に限らず、VCO制御電圧信号に基づいて作出した信号を使用するものであってもよい。

なお、上記制御電圧を記憶したメモリ6には、デジタル信号が記憶されているが、そのデジタル信号からVCO制御用のアナログ信号を作出する手段として、一般的には、制御電圧メモリ内にアナログへの変換データテーブルを備え、そのデータテーブルに基づいて必要なアナログ電圧(直流電圧)を発生する場合が多いが、メモリ6のデータそのものをアナログ電圧に変換する方法を用いることも考えられる。例えば、デジタルデータのビット数に対応して抵抗器を直列に接続するとともに、各抵抗器に並列に、オン・オフ動作を行う制御端子をもった半導体スイッチを備え、各ビットデータ夫々の「0、1」に対応して上記半導体スイッチをオン・オフすると、直列抵抗回路の総合的な抵抗値は、ビット列の「0、1」の並びに対応した値となる。従って、このような抵抗回路を短絡防止用の保護抵抗器を介して電源電圧に接続し、各抵抗器に併設した半導体スイッチを制御電圧メモリのデータで制御すれば、直接的にアナログ電圧/電流を得ることができるので、それを可変リアクタンス素子に印加すればよい。このとき各抵抗値を、段階的に異なる値とすれば、ビットの「0、1」の並べ方によって微小なステップの抵抗値変化を得、従って電圧/電流の変化を微小なものにすることが可能である。

【0016】

また、上述した逓倍回路の概念には周波数低減回路(分周回路)を含んでおり、分周回路を含むPLL発振回路においても本発明を適用することが可能である。この場合は、低減した周波数を希望信号として通過する狭帯域同調回路を備えた周波数逓倍回路を用いる。

【図面の簡単な説明】

【0017】

【図1】本発明の一実施形態に係る広帯域PLL発振回路を示すブロック図。

【図2】本発明の機能を説明するための信号波形図であり、(a)は逓倍回路において発生する信号の周波数スペクトル図、(b)は逓倍回路の同調周波数帯域を示す図。

【図3】本発明の他の実施形態に係る広帯域PLL発振回路を示すブロック図。

【図4】本発明において使用する逓倍回路の一例を示す回路図。

【図5】本発明において使用する逓倍回路の他の例を示す回路図。

【図6】従来の逓倍回路を含むPLL発振回路の一例を示すブロック図。

【図7】ロックスピード高速化のためのVCO制御信号と発振周波数との関係を示す図。

【図8】従来の逓倍回路を含むPLL発振回路の動作を示す図で、(a)は逓倍回路の出力に含まれる信号の周波数スペクトル図、(b)は逓倍回路に必要なフィルタの通過域を示す図。

【図9】従来の逓倍回路を含むPLL発振回路を示すブロック図。

【符号の説明】

【0018】

1 PLL IC、2 ループフィルタ、3 VCO、4 バッファアンプ、5、5−1、5−2、10 逓倍回路、6 メモリ、7 D/A、8 送信/受信切替制御部、Cc、C、C1乃至C3 コンデンサ、L、L1乃至L3 インダクタ(コイル)、Vc1、Vc2、Vc3 可変容量ダイオード(バリアブル・キャパシタ)、R 抵抗

【技術分野】

【0001】

本発明は、広帯域PLL発振回路に関し、詳細にはフェーズロックループ中に逓倍回路を挿入したPLL発振回路において、簡単な構成によって、不要周波数信号成分による誤動作を防止したPLL発振回路の改良に関する。

【背景技術】

【0002】

無線通信機では、送受信用に高い周波数安定度をもった発振回路を備えており、この発振回路から出力される周波数信号に基づいて装置各部の制御及び、信号処理のための信号や搬送波信号等を生成している。また、携帯電話機や警察・消防用無線機等に代表される移動用無線通信機においては、頻繁に発振周波数を変更する必要があるものが多く、これらの発振回路としては、従来からフェーズドロックループ発振回路(Phase Locked Loop Oscillator;以下「PLL発振回路」)が使用されている。

図6は、従来のPLL発振回路の一例を示す回路図である。この回路は、位相比較器(Phase Detector:PD)を含むPLL IC101と、位相比較器の出力を直流信号に平滑するループフィルタ102と、平滑された直流信号(電圧)によって発振周波数が制御される電圧制御発振器(Voltage Controlled Oscillator;以下「VCO」)103と、このVCOの出力信号のレベルを安定化させるバッファアンプ(BUFF AMP)104と、バッファアンプ104の出力信号の周波数を、例えば2倍する逓倍回路105と、をループ状に接続したもので、上記PLL IC101には、基準周波数信号(参照周波数信号)として、外部からFrefが供給されるか、又は、PLL ICの内部で、基準周波数信号Frefを発生し、位相比較器に供給するように構成されている。

【0003】

また、周波数を変更する手段として図示を省略した可変分周回路をPLLループ中に設け、その分周比を変更することによって基準周波数に同期した所望の周波数信号を発生するように構成することもできる。更に、この例ではメモリ106と、デジタル信号をアナログ信号に変換するデジタル/アナログ変換器(D/A)107を備えている。破線で囲った逓倍回路を備えたPLL発振回路についての各ブロックの動作や機能については既知であるので詳細な説明は省略するが、PLL回路では、周波数を切替える際や電源投入時に、基準周波数信号にPLLループの動作が同期するまでに若干時間を要する。

そこで、PLLループが基準周波数に同期するまでの時間を短縮するために、ロックスピード高速化手段として、メモリ106にVCO103の制御電圧情報が記録されていて、周波数変更や、電源投入時に上述した周波数変更手段と連動して、メモリ106から読み出したVCO制御電圧情報をD/A107によって所要の直流電圧に変換し、VCOの周波数制御電圧として供給するように構成されている。

【0004】

図7は、ロックスピード高速化のために制御電圧情報をメモリに記録しておき、周波数を切替えた際に強制的にVCOに供給するための周波数制御電圧(Vcont)とVCOの発振周波数(VCOf)との関係の一例を示した図である。この例では、制御電圧(Vcont)がVHと高くなるとVCO発振周波数がfHと高くなり、制御電圧(Vcont)がVLと低くなるとVCO発振周波数がfLと低くなる場合を示している。同期した際の制御電圧を強制的に印加すると、PLL回路は、その制御電圧をスタート電圧として、ロック引き込み動作に移行するので、迅速なPLL同期が達成され直ちに正確な発振周波数信号が得られる。

【特許文献1】特開平6-326606号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、PLLのループ中に逓倍回路が挿入されると、逓倍された所望周波数信号以外に、基本波及び所望周波数信号以外の高調波等の不要周波数成分が発生する。

図8(a)は、逓倍回路出力に含まれる周波数スペクトルの一例を示す図で、この例では逓倍回路が2逓倍回路、発振周波数が受信周波数帯域frと送信周波数帯域ftに分けられている場合を示している。逓倍回路の出力には、基本周波数信号fr、ftと、2倍された帰還信号(PLL ICの位相比較器に帰還させる希望周波数信号)2fr、2ftと、さらに基本周波数信号の高調波信号である3fr、3ft、・・・nfr、nft、・・が含まれる。この逓倍回路の出力信号として必要な成分は図8(b)に示すように、2fr、2ft成分のみであり、それ以外の周波数成分が含まれると、間違った周波数にPLL回路がロックし、あるいはロック外れが発生する。更に、送信周波数と受信周波数との関係によっては、図8(a)に示すように、帰還信号帯域内において送受信周波数帯域の一部に不要波が重なる場合が発生し、所望しない周波数帯域にPLLがロックすることが有り得る。

そこで、これらの不具合に対処する方法として、例えば特許文献1に提案されているように、逓倍回路と位相比較器の間に、所望の逓倍周波数のみを通過するバンドパスフィルタ(BPF)を挿入するものが知られている。更に、広帯域にするために、そのバンドパスフィルタの通過帯域周波数を制御可能に構成することが提案されている。この方法によれば、選択すべき周波数に対応して、バンドパスフィルタの通過域周波数を制御することによって、希望波以外の周波数信号を排除して、安定した正確な発振周波数信号を得ることができる。

【0006】

図9は、特許文献1を参照して構成した逓倍回路を含むPLL発振回路の概要ブロック図であり、この回路が上記図6と異なる点は、逓倍回路105の出力端に、送信用フィルタ108と受信用フィルタ109と、これら二つのフィルタを切替える送信/受信切替制御部110を備えたところである。この構成によれば、送信時と受信時に夫々のフィルタのみを機能させることによって、それ以外の周波数成分が位相比較器を含むPLL IC101に帰還することを防止するので、安定した発振動作を維持できる。

しかしながら、図9からも明らかなように、逓倍回路出力端に送受信フィルタを備え、それらを切替える構成では、回路構成が複雑となり通信機の小型化が妨げられる上、制御が複雑となると云う新たな問題を含むものであった。

本発明は、従来の広帯域PLL発振回路の諸問題を解決するためになされたものであって、簡単な構成によって、広帯域にわたって発振周波数を変化させても、安定した発振出力が得られる広帯域PLL発振回路を提供することを目的としている。

【課題を解決するための手段】

【0007】

本発明はかかる課題を解決するために、請求項1記載の広帯域PLL発振回路は、電圧信号によって発振周波数を制御する電圧制御発振器と、この電圧制御発振器の出力信号と基準周波数信号とを比較して両者の周波数差又は位相差に応じた信号を出力する位相比較器と、上記位相比較器の出力信号から低域信号成分を取り出し電圧制御発振器の制御信号として供給するフィルタと、をループ状に接続したPLL発振回路において、更に、上記電圧制御発振器の制御電圧情報を記憶した制御電圧メモリと、上記電圧制御発振器と位相比較器との間に挿入され、同調周波数を変更する機能をもった逓倍回路と、発振周波数に対応して上記制御電圧メモリから読み出した所要の制御電圧情報に基づいて、電圧制御発振器の発振周波数と逓倍回路の同調周波数を制御する周波数制御手段とを備えたことを特徴としている。

【0008】

請求項2記載の発明は、請求項1記載の広帯域PLL発振回路において、上記逓倍回路は、同調周波数の異なる複数の逓倍回路を備え、発振周波数に応じて、所要の逓倍回路を選択的に機能させる逓倍回路選択手段を備えたことを特徴としている。

請求項3記載の発明は、請求項1又は2記載の広帯域PLL発振回路において、上記逓倍回路は、電圧/電流によってリアクタンス値が変化する可変リアクタンス素子を含み、且つ、上記制御電圧メモリから出力するデジタル信号をアナログ信号に変換するデジタル・アナログ変換器を備え、変換したアナログ信号によって、可変リアクタンス素子を制御するように構成したことを特徴としている。

【発明の効果】

【0009】

本発明は、逓倍回路を備えたPLL発振回路において、逓倍回路に同調周波数を制御する機能を備え、発振周波数に応じて、その同調周波数を制御するように構成したので、従来のように、別途バンドパスフィルタを用いる必要が無く、回路構成が簡単になり装置の小型化が可能となる。更に、PLL回路のロックスピード高速化のためにVCO制御電圧情報メモリのデータを備えたものである場合は、そのVCO制御電圧情報メモリのデータを逓倍回路の同調周波数制御のために利用すれば、新たに付加する回路や部品点数が少なくなる。また、同調周波数帯域が異なる複数の逓倍回路を備えて、選択的に機能させるように構成すれば、更に広帯域のPLL発振回路として機能させることが可能であり、しかも、同調回路の同調帯域を狭帯域にすれば、減衰特性が急峻なものにできるので、不要波の除去能力を高めることもできる。従って、広い範囲にわたって発振周波数を切替える場合であっても、ロックスピードを高速化しつつ、不要周波数に間違ってロックすることなく、安定した発振周波数信号を得ることが可能となる。

【発明を実施するための最良の形態】

【0010】

以下、本発明を図に示した実施形態を用いて詳細に説明する。但し、この実施形態に記載される構成要素、種類、組み合わせ、形状、その相対配置などは特定的な記載がない限り、この発明の範囲をそれのみに限定する主旨ではなく単なる説明例に過ぎない。以下本発明の実施態様例について説明する。

図1は、本発明に係る広帯域PLL発振回路の一実施形態を示すブロック図である。この例に示すPLL発振回路は、図示を省略した位相比較器(Phase Detector:PD)やチャージポンプを含むPLL IC1と、位相比較器の出力を直流信号に平滑するループフィルタ2と、平滑された直流信号(電圧)によって発振周波数が制御される電圧制御発振器(Voltage Controlled Oscillator;以下「VCO」)3と、このVCOの出力信号のレベルを安定化させるバッファアンプ(BUFF AMP)4と、バッファアンプ4の出力信号を例えば2逓倍する逓倍回路5と、を図示したようにループ状に接続したもので、上記PLL IC1には、基準周波数信号として、Frefが供給されるか、又は、PLL ICの内部で、基準周波数信号Frefを発生し、位相比較器に供給するように構成されている。また、上記図6に関連して説明した例と同様に、周波数を変更する手段として図示を省略した可変分周回路をPLLループ中に設け、その分周比を変更することによって基準周波数に同期した所望の周波数信号を発生するように構成することもできる。

【0011】

この構成において特徴的な点は、上記逓倍回路5が同調周波数を変更する機能をもったものであること、及び、発振周波数に対応して所要のVCO制御電圧情報を制御電圧メモリ6から読み出し、アナログ信号に変換して電圧制御発振器(VCO)3と逓倍回路5に供給する周波数制御機能を備えたことである。この特徴によって、逓倍回路5とPLL IC1との間にバンドパスフィルタを不要にすることができる。即ち、図2は、上記図1に示す広帯域PLL発振回路の基本的な動作及び機能を説明する図であって、図2(a)は、上記図8(a)と同様に2逓倍回路内部において発生する周波数成分を示す周波数スペクトル図であるが、図2(b)に示すように、この実施例において使用する逓倍回路5の同調周波数が狭帯域フィルタ機能と同様に動作するとともに、その同調周波数を変更可能とすることによって必要な周波数成分のみが出力されるものである。

なお、同調周波数を変更可能な逓倍回路としては、例えば、可変容量ダイオードのように電流/電圧(電流値や電圧値)によって容量等のリアクタンス値が変化する素子を含む同調回路を、逓倍回路の入力部や出力部の少なくとも一方に備えた構成にするものが考えられる。

図1及び図2(b)に示すように構成すれば、送信周波数帯域及び受信周波数帯域の両方に亘って、その時々において必要な発振周波数に対応する同調特性を選択することが可能であり、不要周波数成分を排除し、必要な周波数成分のみを位相比較器(PLL IC)に導き、間違った周波数にPLL回路がロックすることなく安定した発振周波数を得ることができる。

【0012】

図3は、本発明の変形実施例を示す概要ブロック図である。この構成の特徴は、図1に示した逓倍回路5を、送信用逓倍回路5−1と受信用逓倍回路5−2に分離した点である。

即ち、逓倍回路の同調周波数帯域を広帯域化することには限界があるので、その限界を超えて更に広帯域化する場合に、送信周波数帯域用の逓倍回路と、受信周波数帯域用の逓倍回路として、同調周波数帯域が異なる複数の逓倍回路を使用するものである。なお、この構成においては、複数の逓倍回路のうちから必要なものを選択するために送信/受信切替制御部8を備え、二つの逓倍回路5−1、5−2のいずれか一方を機能させるとともに、メモリ6とD/A7によって発生するVCO制御電圧信号、又はその信号に基づいて生成した制御信号によって、機能させた逓倍回路の同調回路のリアクタンス素子等を制御して、同調特性を所望のものとする。

このように、VCO3の発振周波数を変化させる際に、同一の周波数制御電圧Vcontによって、もしくは、周波数制御電圧Vcontに基づいて作出した逓倍回路の同調周波数制御信号によって、狭帯域同調特性をもった逓倍回路として機能させ、しかも通過帯域を所要値に変更できるように構成したので、急峻な減衰特性により不要周波数成分を十分に除去することができ、従って、簡単な構成によって、広帯域に亘ってPLLにおけるロック周波数を所望値に安定化させることができる。

なお、逓倍回路の入力部にも周波数選択用の同調回路を設ければ、バッファアンプ4において発生するノイズや歪み成分、高調波成分が逓倍回路に入力することを防止できるので、より一層、不要波除去機能が高くなる。

【0013】

図4は、本発明において使用する同調周波数可変機能を備えた逓倍回路の一実施例を示す回路図である。この例に示す逓倍回路10は、増幅素子として使用するトランジスタTr、そのベースバイアス用抵抗R1、R2、コレクタ負荷インダクタンスL、エミッタ抵抗RE、エミッタ容量CEを含む逓倍用の増幅回路と、容量C1、C2、可変容量ダイオードVc1、Vc2、インダクタンス素子(コイル)L1、L2、結合容量Cc、からなる周波数可変型同調回路と、を含んでいる。なお回路中のCは直流阻止用の容量素子(コンデンサ)である。

このように構成した逓倍回路10は、信号入力端INにバッファアンプ4の出力信号を供給すると、トランジスタ増幅回路の非直線成分によって、高調波が発生する。高調波の発生はトランジスタTrのベースバイアスによっても変化するので、所望の逓倍数に応じて適宜バイアス値が設定される。また、同調回路には、所要値の容量素子(コンデンサ)C1、C2と直列に可変容量ダイオードVc1、Vc2が接続されているので、可変容量ダイオードに供給する直流電圧(Vcont)によって、同調周波数が変化する。この例では、上述したVCO周波数制御電圧(Vcont)によって制御するので、VCO制御電圧によって必要な同調周波数となるように同調回路の容量(C1、C2)と可変容量ダイオードVc1、Vc2の関係を設定する必要がある。なお、容量C1、C2を単なる直流阻止用コンデンサとすることもでき、その場合は、可変容量ダイオードVc1、Vc2による容量値の変化が、逓倍回路の同調周波数に対して支配的となる。この回路は図1及び図3に示した、何れの回路にも使用可能である。

【0014】

図5は、更に、本発明において使用する逓倍回路の、他の実施例を示す回路図である。この例が上記図4と相違する点は、入力側にも可変周波数型の同調回路を備えたところである。即ち、逓倍回路の入力端に、結合トランス用のインダクタンスL3と、このトランスの二次側インダクタンスと同調回路を形成するように接続した、容量(コンデンサ)C3と可変容量ダイオードVc3の直列回路を備え、上記可変容量ダイオードVc3にもVCO周波数制御電圧(Vcont)を供給することによって、入力信号として選択すべき周波数信号のみを通過するように、コンデンサC3、可変容量ダイオードVc3の値が設定されている。例えば、VCO3の出力信号に同調するように設定すれば、バッファアンプの歪みによって発生する高調波が逓倍回路に流入しないので、一層、PLL発振回路が安定して動作するようになる。

【0015】

以上、本発明の実施例について説明したが、本発明はこれらの例に限定することなく種々変形が可能である。例えば、逓倍回路の出力端に備える同調回路として、図4、図5に示すように、2段のLC同調回路を接続したが、一つの同調回路にしても良いし、3段以上の同調回路を連結した回路であってもよい。また、図5に示すように入力端に同調回路を挿入する場合においても、複数段の同調回路を連結するものであっても構わない。更に、夫々の可変容量ダイオードの制御信号として、VCO制御電圧信号をそのまま使用する例を示したが、この例に限らず、VCO制御電圧信号に基づいて作出した信号を使用するものであってもよい。

なお、上記制御電圧を記憶したメモリ6には、デジタル信号が記憶されているが、そのデジタル信号からVCO制御用のアナログ信号を作出する手段として、一般的には、制御電圧メモリ内にアナログへの変換データテーブルを備え、そのデータテーブルに基づいて必要なアナログ電圧(直流電圧)を発生する場合が多いが、メモリ6のデータそのものをアナログ電圧に変換する方法を用いることも考えられる。例えば、デジタルデータのビット数に対応して抵抗器を直列に接続するとともに、各抵抗器に並列に、オン・オフ動作を行う制御端子をもった半導体スイッチを備え、各ビットデータ夫々の「0、1」に対応して上記半導体スイッチをオン・オフすると、直列抵抗回路の総合的な抵抗値は、ビット列の「0、1」の並びに対応した値となる。従って、このような抵抗回路を短絡防止用の保護抵抗器を介して電源電圧に接続し、各抵抗器に併設した半導体スイッチを制御電圧メモリのデータで制御すれば、直接的にアナログ電圧/電流を得ることができるので、それを可変リアクタンス素子に印加すればよい。このとき各抵抗値を、段階的に異なる値とすれば、ビットの「0、1」の並べ方によって微小なステップの抵抗値変化を得、従って電圧/電流の変化を微小なものにすることが可能である。

【0016】

また、上述した逓倍回路の概念には周波数低減回路(分周回路)を含んでおり、分周回路を含むPLL発振回路においても本発明を適用することが可能である。この場合は、低減した周波数を希望信号として通過する狭帯域同調回路を備えた周波数逓倍回路を用いる。

【図面の簡単な説明】

【0017】

【図1】本発明の一実施形態に係る広帯域PLL発振回路を示すブロック図。

【図2】本発明の機能を説明するための信号波形図であり、(a)は逓倍回路において発生する信号の周波数スペクトル図、(b)は逓倍回路の同調周波数帯域を示す図。

【図3】本発明の他の実施形態に係る広帯域PLL発振回路を示すブロック図。

【図4】本発明において使用する逓倍回路の一例を示す回路図。

【図5】本発明において使用する逓倍回路の他の例を示す回路図。

【図6】従来の逓倍回路を含むPLL発振回路の一例を示すブロック図。

【図7】ロックスピード高速化のためのVCO制御信号と発振周波数との関係を示す図。

【図8】従来の逓倍回路を含むPLL発振回路の動作を示す図で、(a)は逓倍回路の出力に含まれる信号の周波数スペクトル図、(b)は逓倍回路に必要なフィルタの通過域を示す図。

【図9】従来の逓倍回路を含むPLL発振回路を示すブロック図。

【符号の説明】

【0018】

1 PLL IC、2 ループフィルタ、3 VCO、4 バッファアンプ、5、5−1、5−2、10 逓倍回路、6 メモリ、7 D/A、8 送信/受信切替制御部、Cc、C、C1乃至C3 コンデンサ、L、L1乃至L3 インダクタ(コイル)、Vc1、Vc2、Vc3 可変容量ダイオード(バリアブル・キャパシタ)、R 抵抗

【特許請求の範囲】

【請求項1】

電圧信号によって発振周波数を制御する電圧制御発振器と、該電圧制御発振器の出力信号と外部から供給される基準周波数信号とを比較して両者の周波数差又は位相差に応じた信号を出力する位相比較器と、該位相比較器の出力信号から低域信号成分を取り出し前記電圧制御発振器の制御信号として供給するフィルタと、をループ状に接続したPLL発振回路において、更に、前記電圧制御発振器の制御電圧情報を記憶した制御電圧メモリと、前記電圧制御発振器と位相比較器との間に挿入され、同調周波数を変更する機能をもった逓倍回路と、発振周波数に対応して前記制御電圧メモリから読み出した所要の制御電圧情報に基づいて、前記電圧制御発振器の発振周波数と前記逓倍回路の同調周波数を制御する周波数制御部とを備えたことを特徴とする広帯域PLL発振回路。

【請求項2】

請求項1記載の広帯域PLL発振回路において、前記逓倍回路は、同調周波数の異なる複数の逓倍回路を備え、発振周波数に応じて、所要の逓倍回路を選択的に機能させる逓倍回路選択手段を備えたことを特徴とする広帯域PLL発振回路。

【請求項3】

請求項1又は2記載の広帯域PLL発振回路において、前記逓倍回路は、電圧/電流によってリアクタンス値が変化する可変リアクタンス素子を含み、且つ、前記制御電圧メモリから出力するデジタル信号をアナログ信号に変換するデジタル・アナログ変換器を備え、変換したアナログ信号によって、前記可変リアクタンス素子を制御するように構成したことを特徴とする広帯域PLL発振回路。

【請求項1】

電圧信号によって発振周波数を制御する電圧制御発振器と、該電圧制御発振器の出力信号と外部から供給される基準周波数信号とを比較して両者の周波数差又は位相差に応じた信号を出力する位相比較器と、該位相比較器の出力信号から低域信号成分を取り出し前記電圧制御発振器の制御信号として供給するフィルタと、をループ状に接続したPLL発振回路において、更に、前記電圧制御発振器の制御電圧情報を記憶した制御電圧メモリと、前記電圧制御発振器と位相比較器との間に挿入され、同調周波数を変更する機能をもった逓倍回路と、発振周波数に対応して前記制御電圧メモリから読み出した所要の制御電圧情報に基づいて、前記電圧制御発振器の発振周波数と前記逓倍回路の同調周波数を制御する周波数制御部とを備えたことを特徴とする広帯域PLL発振回路。

【請求項2】

請求項1記載の広帯域PLL発振回路において、前記逓倍回路は、同調周波数の異なる複数の逓倍回路を備え、発振周波数に応じて、所要の逓倍回路を選択的に機能させる逓倍回路選択手段を備えたことを特徴とする広帯域PLL発振回路。

【請求項3】

請求項1又は2記載の広帯域PLL発振回路において、前記逓倍回路は、電圧/電流によってリアクタンス値が変化する可変リアクタンス素子を含み、且つ、前記制御電圧メモリから出力するデジタル信号をアナログ信号に変換するデジタル・アナログ変換器を備え、変換したアナログ信号によって、前記可変リアクタンス素子を制御するように構成したことを特徴とする広帯域PLL発振回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2010−147583(P2010−147583A)

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願番号】特願2008−319919(P2008−319919)

【出願日】平成20年12月16日(2008.12.16)

【出願人】(000003595)株式会社ケンウッド (1,981)

【Fターム(参考)】

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願日】平成20年12月16日(2008.12.16)

【出願人】(000003595)株式会社ケンウッド (1,981)

【Fターム(参考)】

[ Back to top ]