強化された銅−銅接合を有する三次元(3D)集積回路およびその形成方法

【課題】改良されたCu−Cu接合を実現した三次元(3D)集積回路を提供する。

【解決手段】第一デバイス・ウエハの少なくともCu表面上に少なくとも一つの金属接着層が形成される。別のCu表面を有する第二デバイス・ウエハが、第一デバイス・ウエハのCu表面の上で且つ少なくとも一つの金属接着層上に位置付けられる。次いで、第一および第二デバイス・ウエハが共に接合される。この接合ステップは、外部から加える圧力の使用の有無にかかわらず、これらデバイス・ウエハを400℃未満の温度に加熱するステップを含む。加熱の過程で、2つのCu表面は共に接合され、該少なくとも一つの金属接着層が2つのCu表面から酸素原子を得て、これらCu表面の間に少なくとも一つの金属酸化物接合層を形成する。

【解決手段】第一デバイス・ウエハの少なくともCu表面上に少なくとも一つの金属接着層が形成される。別のCu表面を有する第二デバイス・ウエハが、第一デバイス・ウエハのCu表面の上で且つ少なくとも一つの金属接着層上に位置付けられる。次いで、第一および第二デバイス・ウエハが共に接合される。この接合ステップは、外部から加える圧力の使用の有無にかかわらず、これらデバイス・ウエハを400℃未満の温度に加熱するステップを含む。加熱の過程で、2つのCu表面は共に接合され、該少なくとも一つの金属接着層が2つのCu表面から酸素原子を得て、これらCu表面の間に少なくとも一つの金属酸化物接合層を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、半導体構造体およびそれを形成する方法に関する。さらに具体的には、本開示は、改良されたCu−Cu接合が実現された三次元(3D)集積回路に関する。

【背景技術】

【0002】

現今の電子デバイスに対するスケーリング条件に対処するため、チップ設計者らおよび製造者らは、利用可能なチップ・スペースを最良に最大化する回路設計を工夫するよう常に努めている。その結果得られた設計は、多くの場合いくつかの異なるレベルに展開される。例えば、かかる三次元(3D)回路設計の一つには、積み重ね構造に位置付けされたいくつかの異なるデバイス層を含むものがある。別の事例では、3D設計が、層間の垂直ビアによって共に接続された、複数のデバイス層と相互接続層とから成る垂直スタックを含んでいることがある。

【発明の概要】

【発明が解決しようとする課題】

【0003】

典型的な3D集積回路において、2つの能動デバイス・ウエハが、背合わせに積み重ねられる。これら2つの能動デバイス・ウエハは、次いで、熱圧着を用い、Cu−Cu接合を行って共に接合される。この接合処理には、妥当な高温および圧力両方の印加が必要である。かかる直接的Cu−Cu合では、共に接合されるCu表面にCuOが形成される。Cu表面におけるCuOの存在は、接合構造体の抵抗を増加させ、特に接着性など、接合構造体の信頼性を低下させる。

【0004】

このため、接合されたCu−Cu表面におけるCuOの形成を排除した、改良されたCu表面の共接合の方法が必要とされている。

【課題を解決するための手段】

【0005】

第一デバイス・ウエハの少なくともCu表面、通常はCu接合パッド、上に少なくとも一つの金属接着層が形成される。別のCu表面、通常は別のCu接合パッド、を有する第二デバイス・ウエハが、第一デバイス・ウエハのCu表面の上で且つ少なくとも一つの金属接着層上に位置付けられる。次いで、第一および第二デバイス・ウエハが共に接合される。この接合ステップは、外部から加える圧力の使用の有無にかかわらず、これらデバイス・ウエハを400℃未満の温度に加熱するステップを含む。加熱の過程で、2つのCu表面は共に接合され、該少なくとも一つの金属接着層が2つのCu表面から酸素原子を得て、これらCu表面の間に少なくとも一つ金属酸化物接合層を形成する。

【0006】

本開示の一つの態様において、三次元(3D)集積回路を形成する方法が提供される。本開示の方法は、少なくともCu表面を含む、第一デバイス・ウエハを用意するステップを含む。次に、そのCu表面の上に金属接着層が形成される。別のCu表面を有する第二デバイス・ウエハが、第一デバイス・ウエハの金属接着層上で且つCu表面の上に位置付けられる。第一および第二デバイス・ウエハは、400℃未満の温度で共に接合される。接合の過程で、金属接着層は、2つのCu表面から酸素原子を得て、Cu表面と別のCu表面との間に金属酸化物接合層を形成する。

【0007】

本開示の別の態様は、三次元(3D)集積回路に関する。本3D集積回路は、Cu表面を有する第一デバイス・ウエハと別のCu表面を有する第二デバイス・ウエハとの垂直スタックを含み、金属酸化物接合層が、第一デバイス・ウエハのCu表面と第二デバイス・ウエハの別のCu表面との間に配置される。

【図面の簡単な説明】

【0008】

【図1】3D集積回路を形成するのに用いることのできる、本開示の各種処理ステップを示す、ブロック図様式の概略図である。

【図2】本開示の一つの実施形態において用いることのできる、パターン取りされたCu接合パッドを含む、第一デバイス・ウエハを(断面図を介して)示した図示表現である。

【図3】第一デバイス・ウエハの少なくともCu接合パッド上に金属接着層を形成した後の、図2の第一デバイス・ウエハを(断面図を介して)示した図示表現である。

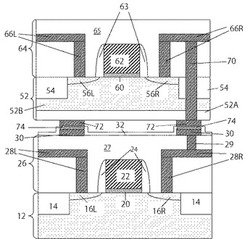

【図4】図3に示された第一デバイス・ウエハの上方に位置付けられた、少なくとも一つ他のCu接合パッドを含む第二デバイス・ウエハを(断面図を介して)示した図示表現である。

【図5】400℃未満の温度で接合した後の、図4の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図6】第二デバイス・ウエハから取扱い用基板を除去した後の、図5の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図7】本開示の一つの実施形態において用いることのできるパターン取りなしCu接合パッドを含む第一デバイス・ウエハを(断面図を介して)示した図示表現である。

【図8】第一デバイス・ウエハのパターン取りなしCu接合パッド上に金属接着層を形成した後の、図7の第一デバイス・ウエハを(断面図を介して)示した図示表現である。

【図9】図8に示された第一デバイス・ウエハの上方に位置付けられた、少なくとも一つの他のCu接合パッドを含む第二デバイス・ウエハを(断面図を介して)示した図示表現である。

【図10】400℃未満の温度で接合した後の、図9の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図11】第二デバイス・ウエハから取扱い基板を除去した後の、図10の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図12】本開示のさらなる実施形態で用いることができる、パターン取りされたCu接合パッドを共に含む2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図13】デバイス・ウエハの少なくとも一つの、パターン取りされたCu接合パッド上に少なくとも一つの金属接着層を形成した後の、図12の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図14】デバイス・ウエハの一つを180°回転させ、一つのデバイス・ウエハのパターン取りされたCu接合パッドを、他方のデバイス・ウエハのパターン取りされたCu接合パッドに整合させた後の、図13の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図15】400℃未満の温度で接合した後の、図14の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図16】金属接着層を形成するのに選択的堆積処理が使われていることを除き、図2〜図6に示された基本的処理ステップを使って形成できる3D集積回路を(断面図を介して)示した図示表現である。

【図17】金属接着層を形成するのに選択的堆積処理が使われていることを除き、図12〜図15に示された基本的処理ステップを使って形成できる3D集積回路を(断面図を介して)示した図示表現である。

【発明を実施するための形態】

【0009】

改良されたCu−Cu接合を有する三次元(3D)集積回路およびこれを形成する方法に関する本開示を、以下の詳解および本出願に添付された図面を参照しながら、以降により詳細に説明する。なお、本出願の図面は、例示目的で提示されており、そのため一定の縮尺では描かれていない。

【0010】

以下の説明において、本発明が十分理解されるように、特定の構造体、コンポーネント、材料、寸法、処理ステップ、および技法など、数々の具体的詳細が示される。しかしながら、当業者は、本開示が、これらの具体的詳細が無くても、実行可能な別の処理オプションを使って実施できることをよく理解していよう。他の例では、本開示の各種実施形態の不明瞭化を避けるために、周知の構造または処理ステップは詳細には説明していない。

【0011】

層、領域、または基板などのエレメントが別のエレメントの「上に(“on”)」ある、または「覆って(“over”)」いると言及された場合、それが別のエレメントの直接上にあることも、介在するエレメントが存在することもあることを理解されたい。これに対し、あるエレメントが別のエレメントの「直接上に(“directly on”)」ある、または「直接覆って(“directly over”)」いると言及された場合、介在するエレメントは存在しない。また、あるエレメントが別のエレメントの「真下に(“beneath”)」または「下に(“under”)」あると言及された場合、それが別のエレメントの直接真下または下にあることも、介在するエレメントが存在することもあることを理解されたい。これに対し、あるエレメントが別のエレメントの「直接真下に(“directly beneath”)」または「直接下に(“directly under”)」あると言及され場合、介在するエレメントは存在しない。

【0012】

前述したように、本開示は、三次元(3D)集積回路を形成する方法を提供する。本開示の方法は、図1に示されたブロック図中に概略的に表されている。本開示の方法は、Cu表面を含む第一デバイス・ウエハを用意するステップを含む(ステップ100)。次に、第一デバイス・ウエハの少なくともCu表面上に金属接着層が形成される(ステップ102)。別のCu表面を有する第二デバイス・ウエハが、第一デバイス・ウエハの金属接着層上で且つCu表面の上に位置付けられる(ステップ104)。第一および第二デバイス・ウエハは、400℃未満の温度で共に接合される(ステップ106)。接合の過程で、金属接着層は、2つのCu表面から酸素原子を得て、第一デバイス・ウエハのCu表面と第二デバイス・ウエハの別のCu表面との間に金属酸化物接合層を形成する。

【0013】

本開示の方法は、Cu表面を含む第一デバイス・ウエハと別のCu表面を含む第二デバイス・ウエハとの垂直スタックを含む三次元(3D)集積回路を提供し、金属酸化物接合層が、第一デバイス・ウエハのCu表面と第二デバイス・ウエハの別のCu表面との間に配置される。この金属酸化物接合層は、Cu−Cu接合面の抵抗を増加させることなく、異なるデバイス・ウエハの間の改良されたCu−Cu接合を提供する。

【0014】

本開示全体を通して使われる「デバイス・ウエハ(“device wafer”)」という用語は、半導体基板と、少なくとも部分的に半導体基板上に配置された少なくとも一つのデバイスと、少なくとも一つの導電機能(ビアもしくはラインまたはその両方)が中に内蔵されている少なくとも一つの相互接続誘電体材料を含む、相互接続レベルと、相互接続レベルの表面に配置され、少なくとも一つの相互接続材料内に配置された導電機能の少なくとも一つと接触しているCu接合パッドと、を含む半導体構造体をいう。いくつかの実施形態において、Cu接合パッドはパターン取りすることができ、しかして、相互接続レベルの一部の部分上にだけ配置される。他の実施形態において、Cu接合パッドをパターン取りせず、しかして相互接続レベル全体の上に配置することができる。

【0015】

この少なくとも一つのデバイスは、電解効果トランジスタ、抵抗、コンデンサ、BiCMOS、ダイオード、導体、マイクロ電気機械(MEM:microelectromechanical)デバイス、熱冷却デバイス、またはこれらの任意の組み合わせとすることができる。これらのデバイスは同じまたは異なる極性を有することができ、同じまたは異なる機能を有することができる。例えば、これらデバイスは、メモリ、マイクロプロセッサ、マイクロコントローラ、センサ、熱冷却エレメント、またはこれらの機能の任意の組み合わせのいずれとしても用いることができる。

【0016】

まず、本開示の方法を使って3D集積回路を作製するための、本開示の一つの実施形態を示している図3〜図6を参照する。なお、以下の詳解および図面では、2つのデバイス・ウエハの垂直積み重ねおよび共接合を説明、図示しているが、本開示は、2つだけのデバイス・ウエハの垂直積み重ねおよび共接合には限定されない。代わりに、本開示は、本開示の方法を使って、n個のデバイス・ウエハが垂直に積み重ねられ共に接合される実施形態においても用いることができ、nは2より大きい整数である。

【0017】

最初に、図2を参照すると、相互接続レベル26の上に配置されパターン取りされたCu接合パッド30を含む第一デバイス・ウエハ10が示されている。また、第一デバイス・ウエハ10は、少なくとも一つの絶縁領域14が中に配置されている半導体基板12の表面上に、少なくとも部分的に配置された少なくとも一つの第一デバイス18も含む。これらの図面および以下の詳解において、この少なくとも一つの第一デバイス18は、少なくとも一つのゲート誘電体20と上に重なるゲート導体22とのゲート・スタックを含む電界効果トランジスタである。ゲート・スタック(20および22)の側壁上に、少なくとも一つのスペーサ24を配置することができる。ソース/ドレイン領域16Lおよび16Rは、ゲート・スタック(20および22)のフットプリントに示されており、半導体基板12の上部内に配置されている。

【0018】

相互接続レベル26は、複数の導電機能28L、28Rが中に配置されている、少なくとも一つの相互接続誘電体材料27を含む。図示のように、複数の導電機能の導電機能28Lの一つは電界効果トランジスタのソース/ドレイン領域16Lに接触しており、一方、複数の導電機能の導電機能28Rの別の一つは電界効果トランジスタのソース/ドレイン領域16Rに接触している。また、図示のように、導電機能28Rは、相互接続レベル26の上に形成されたパターン取りされたCu接合パッド30の一つの表面と接触している導電領域、すなわちビア29を有する。

【0019】

図2に示された第一デバイス・ウエハ10は、当業者に周知の技法を利用して形成することができる。また、第一デバイス・ウエハ10のさまざまなコンポーネントは、これも当業者に周知の材料で形成することができる。

【0020】

以下に、かかる第一デバイス・ウエハ10をどのように作製できるか、並びに、第一デバイス・ウエハ10の中に配置できるコンポーネントの各々に対するいくつかの材料について、一部の詳細を提示する。かかる詳細を提示はするが、当業者に周知の他の方法もしくは材料またはその両方を使って、図2に示された第一デバイス・ウエハ10を形成することも可能である。

【0021】

第一デバイス・ウエハ10の半導体基板12は、以下に限らないが、Si、Ge、SiGe、SiC、SiGeC、GaAs、GaN、InAs、InPおよび他のIII/V族またはII/VI化合物半導体全てを含め、任意の半導体材料で構成することができる。また、半導体基板12には、有機半導体、またはSi/SiGe、シリコン・オン・インシュレータ(SOI:silicon−on−insulator)、SiGeオン・インシュレータ(SGOI:SiGe−on−insulator)またはゲルマニウム・オン・インシュレータ(GOI:germanium−on−insulator)などの層状半導体を含めることもできる。半導体オン・インシュレータ基板は最上部から底部に向けて、最上部半導体デバイス層と、絶縁体層と、底部半導体部分とを含む。本開示のいくつかの実施形態において、半導体基板12は、Si含有半導体材料、すなわちシリコンを含む半導体材料から成る。半導体基板12は、ドープ、非ドープとすることができ、またはその中にドープ領域と非ドープ領域とを含めることができる。半導体基板12には、単一の結晶方位を含めることができ、または種々の結晶方位を含めることもできる。説明の便宜上、第一デバイス・ウエハの半導体基板12はバルク半導体から成るものとする。「バルク(“bulk”)」とは、基板の全体が、半導体材料から成ることをいうものする。

【0022】

また半導体基板12には、第一ドープ(n−またはp−)領域および第二ドープ(n−またはp−)領域を含めることができる。簡明化のため、これらドープ領域は、本出願のどの図面にも具体的には示していない。第一ドープ領域と第二ドープ領域とは同じにすることもでき、またはこれらに異なった伝導性もしくは異なったドーピング濃度またはその両方を持たせることもできる。これらドープ領域は「ウェル(“well”)」として知られており、在来のイオン注入処理を用いて形成することができる。

【0023】

半導体基板12の中に少なくとも一つの絶縁領域14を形成することができる。この少なくとも一つの絶縁領域14は、トレンチ絶縁領域またはフィールド酸化物絶縁領域とすることができる。トレンチ絶縁領域は当業者には周知のトレンチ絶縁処理を用いて形成される。例えば、トレンチ絶縁領域の形成には、リソグラフィ、エッチング、およびトレンチ誘電体でトレンチを満たすステップを使うことができる。随意的に、トレンチ充填の前にトレンチ中にライナを形成することができ、トレンチ充填後に緻密化ステップを実施することができ、トレンチ充填の後で平坦化処理を行うこともできる。フィールド酸化物は、いわゆるシリコンの局所酸化処理を用いて形成することができる。当業者には周知のように、少なくとも一つの絶縁領域14は、隣接するデバイスが反対の伝導性を有する場合、すなわちnFETおよびpFETの場合などに通常必要となる、隣接するデバイスの間の絶縁を提供する。本明細書では、隣接する絶縁領域の間に位置する半導体基板12の部分を、半導体基板12の「活性化領域」という。半導体基板12の活性化領域は、その中にデバイスが少なくとも部分的に形成されることになる領域である。

【0024】

その中にデバイス(群)が形成されることになる活性化領域(群)が画定された後、半導体基板12の該活性化領域(群)中にデバイス(群)が少なくとも部分的に形成される。これら図面において、前述したように、この例示の実施形態で形成される少なくとも一つの第一デバイス18は電界効果トランジスタである。この電界効果トランジスタは少なくとも一つのゲート誘電体20とゲート導電体22とのゲート・スタックを含む。

【0025】

ゲート誘電体20は任意の絶縁材料を含む。一つの実施形態において、ゲート誘電体20は、半導体酸化物、半導体窒化物、もしくは半導体酸窒化物またはこれらの組み合わせを含む。別の実施形態では、ゲート誘電体20は、酸化ケイ素の誘電率の例えば3.9より大きな誘電率を有する誘電体金属酸化物を含む。本明細書では、酸化ケイ素の誘電率より大きな誘電率を有する、かかる誘電体金属酸化物をhigh−k誘電体材料という。典型的には、本開示において採用可能なhigh−kゲート誘電体は4.0より大きな誘電率を有するが、8.0より大きな誘電率であればさらに典型的である。ゲート誘電体20として採用可能な代表的high−k誘電体材料には、以下に限らないが、HfO2、ZrO2、La2O3、Al2O3、TiO2、SrTiO3、LaAlO3、Y2O3、HfOxNy、ZrOxNy、La2OxNy、Al2OxNy、TiOxNy、SrTiOxNy、LaAlOxNy、Y2OxNy、これらのケイ酸塩、およびこれらの合金が含まれる。xの各値は、独立して0.5〜3であり、yの各値は、独立して0〜2である。いくつかのの実施形態において、前述の誘電体材料の少なくとも2つによる多層スタックを用いることができる。例えば、一つの実施形態において、ゲート誘電体20には、半導体酸化物すなわち酸化ケイ素の下部層と、例えばHfO2などのhigh−k誘電体材料の上部層とを含めることができる。

【0026】

ゲート誘電体20の厚さは、これを形成するのに使われる技法によって変わり得る。しかしながら、典型的には、ゲート誘電体20は、0.5nm〜10nmの厚さを有し、1.0nm〜5nmであればさらに典型的である。本開示のいくつかの実施形態において、用いられるゲート誘電体20に1nmまたはそれ以下のオーダーの有効酸化物厚さを持たせることができる。

【0027】

ゲート誘電体20は、例えば、化学気相堆積(CVD:chemical vapor deposition)、物理気相堆積(PVD:physical vapor deposition)、分子ビーム堆積(MBD:molecular beam deposition)、パルス・レーザ堆積(PLD:pulsed laser deposition)、液体ミスト化学堆積(LSMCD:liquid source misted chemical deposition)、原子層堆積(ALD:atomic layer deposition)、および他の類似の堆積処理を含め、当該技術において周知の方法によって形成することができる。いくつかの実施形態において、特に半導体酸化物、窒化物もしくは酸窒化物またはこれらの組み合わせがゲート誘電体20として用いられる場合、ゲート誘電体20は、例えば、熱酸化もしくは熱窒化またはその両方など、熱処理によって形成することができる。かかる事例では、半導体酸化物、窒化物もしくは酸窒化物またはこれらの組み合わせの半導体部分は、下層の半導体基板12のものと同じ半導体材料を含む。

【0028】

図2に示された、少なくとも一つ第一デバイス18、すなわち電界効果トランジスタのゲート・スタックのゲート導体22は、以下に限らないが、多結晶シリコン、多結晶シリコン・ゲルマニウム、元素金属(例えば、タングステン、チタン、タンタル、アルミニウム、ニッケル、ルテニウム、パラジウム、および白金)、少なくとも2つの元素金属の合金、窒化元素金属(例えば、窒化タングステン、窒化アルミニウム、および窒化チタン)、ケイ化元素金属(例えば、ケイ化タングステン、ケイ化ニッケル、ケイ化チタン)およびこれらの多層を含め、任意の伝導性材料を含む。一つの実施形態において、ゲート導体22はnFET金属から成る。別の実施形態では、ゲート導体22は、pFET金属から成る。またさらなる実施形態では、ゲート導体22は多結晶シリコンから成り、下層の伝導性金属部分を有する場合も有しない場合もある。

【0029】

ゲート導体22は、例えば、化学気相堆積(CVD)、プラズマ化学気相堆積(PECVD:plasma enhanced chemical vapor deposition)、蒸着、物理気相堆積(PVD)、スパッタリング、化学溶液堆積、原子層堆積(ALD)および他の類似の堆積処理を含め、在来の堆積処理を用いて形成することができる。ゲート導体22としてSi含有材料が使われる場合、該Si含有材料は、インサイチュ(in−situ)ドーピングの堆積処理を用いるか、もしくは堆積の後でイオン注入またはガス相ドーピングンなどのステップを用い、適切な不純物がSi含有材料中に導入されるようにして、適切な不純度内にドープすることができる。ケイ化金属を形成する場合、在来のケイ化処理を用いることができる。

【0030】

いくつかの実施形態において、ゲート誘電体20およびゲート導体22は、ブランケット層として形成され、然る後、パターン取り処理を使ってこれらを含むゲート・スタックが形成される。このパターン取り処理は、リソグラフィ(ゲート導体22の上面の上にフォトレジストを塗布し、フォトレジストを放射露光させ、在来の現像液を使って露光したレジストを現像する処理)を含む。このリソグラフィ・ステップでは、ゲート導体22のブランケット層の上にパターン取りされたフォトレジストが得られる。次いで、エッチング処理を使って、パターン取りされたフォトレジストから、その下部のゲート誘電体およびゲート導体材料のブランケット層にパターンを転写する。このエッチングには、例えば、反応性イオンエッチング、プラズマエッチング、イオンエッチング、またはレーザ・アブレーションなどドライ・エッチング処理を含めることができる。このエッチングには、ゲート誘電体およびゲート導体材料のブランケット層の、パターン取りされたフォトレジストによって保護されていない部分を除去するために、一つ以上の化学腐食液が使われる湿式化学エッチング処理をさらに含めることができる。パターン取りされたフォトレジストは、アッシング処理を用いて除去することができる。

【0031】

他の実施形態において、ゲート誘電体20とゲート導体22とを含むゲート・スタックは、置換ゲート処理を用いて形成される。かかる処理では、少なくとも犠牲ゲート材料を含むスタックが、平坦化誘電体材料中に存在する開口部の中に形成される。該少なくとも犠牲ゲート材料が除去され、次いで前述したゲート導体材料の一つで置き換えられる。いくつかの実施形態において、置換ゲート処理には、同様に、犠牲ゲート誘電体材料を含めることもできる。かかる実施形態では、犠牲ゲート材料および犠牲ゲート誘電体は両方とも除去され、前述のゲート導体材料の一つと前述のゲート誘電体材料の一つとに置き換えられる。

【0032】

少なくとも一つの第一デバイス18として示された電界効果トランジスタには、少なくとも一つのスペーサ24をさらに含めることができる。いくつかの実施形態において、少なくとも一つのスペーサ24は、少なくともゲート誘電体20とゲート電極22とを含むゲート・スタックの側壁から省くことができる。少なくとも一つのスペーサ24は、存在する場合、例えば、酸化ケイ素、窒化ケイ素、もしくは酸窒化ケイ素またはこれらの組み合わせなど、酸素不浸透性の誘電体材料から成る。少なくとも一つのスペーサ24は、酸素不浸透性の誘電体材料の堆積とその後のエッチングによって形成することができる。いくつかの実施形態において、少なくとも一つのスペーサ24を形成するのに熱処理を用いることができる。

【0033】

また、図2に示された電界効果トランジスタ(すなわち、少なくとも一つの第一デバイス18)は、ソース/ドレイン領域16Lおよび16Rを含む。ソース/ドレイン領域16Lおよび16Rは、ゲート誘電体20とゲート導体22とを含むゲート・スタックの形成の前でもまたは後でも、イオン注入およびアニーリングを用いて形成することができる。イオン注入処理のための条件およびドーパントは当業者には周知である。アニールは、半導体基板12中にイオン注入されたドーパントを活性化するもので、約800℃以上の温度に加熱するステップを含む。ゲート・スタック(20および22)の真下に所在しソース/ドレイン領域16L、16Rによって横方向に境界されている、半導体基板12の部分はトランジスタのチャネル領域である。

【0034】

少なくとも一つの第一デバイス18を形成した後、相互接続レベル26が形成される。相互接続レベル26は、単一の相互接続レベルとすることもでき、または、垂直に積み重ねられ、電気的に接続された複数の相互接続レベル群とすることもできる。相互接続レベル26は、複数の導電機能28Lおよび28Rが中に配置されている、少なくとも一つの相互接続誘電体材料27を含む。複数の導電機能の導電機能28Lの一つは、電界効果トランジスタのソース/ドレイン領域16Lに接触しており、一方、複数の導電機能の導電機能28Rの別の一つは、電界効果トランジスタのソース/ドレイン領域16Rに接触している。導電機能28Rは、相互接続レベル26の上に形成されたパターン取りされたCu接合パッド30の一つ、の表面と接触している導電領域、すなわちビア29を有する。

【0035】

相互接続レベル26は、例えばダマシン処理を含め、当該技術分野で周知の技法を使って形成される。ダマシン処理では、少なくとも一つの相互接続誘電体材料27が最初に形成され、次いで、リソグラフィおよびエッチングを使って、少なくとも一つ相互接続誘電体材料27中に複数の開口部が形成される。複数の開口部は、ビア開口、ライン開口、またはビア開口およびライン開口の組み合わせとすることができる。ビア開口およびライン開口によって開口部が画定されると、2回目の繰り返しリソグラフィおよびエッチングを用いることができる。かかる開口部の組み合わせにおいて、ビアとラインとは相互に連通している。

【0036】

これら開口部は、次いで伝導性材料で充填されて、導電機能28Lおよび28Rを形成する。

【0037】

いくつかの実施形態において、導電領域29は、導電機能28Lおよび28Rと同時に形成することができる。他の実施形態では、導電領域29は、導電機能28Lおよび28Rの後で形成することができる。かかる実施形態では、導電機能28Lおよび28Rの各々は、第一相互接続誘電体材料の上面とほぼ同一平面上にある最上面を有する。次いで第二相互接続誘電体材料(第一相互接続誘電体材料と同じかまたは異なる)が形成され、導電領域29が、導電機能28Lおよび28Rの形成に関して前述したのと同じ技法を使って形成される。この特定の実施形態において、第一および第二相互接続誘電体材料は、本開示のいくつかの実施形態で使用可能な多層レベルの相互接続構造を形成する。

【0038】

相互接続レベル26の少なくとも一つの相互接続誘電体材料27には、無機誘電体または有機誘電体を含む任意のレベル間またはレベル内誘電体を含めることができる。該少なくとも一つの相互接続誘電体材料27は、多孔質であっても非多孔質であってもよい。多孔質の誘電体材料は、一般に、非多孔質のものよりも低い誘電率を有する。この少なくとも一つの相互接続誘電体材料27として使用可能な適切な誘電体の一部の例には、以下に限らないが、SiO2、シルセスキオキサン、Si、C、OおよびH原子を含むCドープ酸化物(すなわち有機シリケート)、熱硬化性ポリアリーレン・エーテル、またはこれらの多層が含まれる。本出願では、「ポリアリーレン(“polyarylene”)」という用語は、結合、縮合環、または 例えば酸素、硫黄、スルホン、スルホキシド、カルボニル等などの不活性連結基で、共に結び付けられた、アリール部分または不活性に置換されたアリール部分をいう。一つの実施形態において、少なくとも一つの相互接続誘電体材料27は、約4.0またはそれ以下の誘電率を有する。別の実施形態では、少なくとも一つの相互接続誘電体材料27は、約2.8またはそれ以下の誘電率を有する。本開示で述べる全ての誘電率は、別途の記載がなければ真空に対するものである。少なくとも一つの相互接続誘電体材料27の厚さは、用いられる誘電体材料、および相互接続レベル26内の誘電体の正確な数の如何によって変わり得る。一般に、通常の相互接続構造に対しては、該少なくとも一つの相互接続誘電体材料27は200nm〜450nmの厚さを有する。

【0039】

導電機能28Lおよび28R並びに導電領域29は、例えば、ポリSi、伝導性金属、少なくとも2つの伝導性金属を含む合金、伝導性金属シリサイド、またはこれらの組み合わせなどの伝導性材料を含む。一つの実施形態において、導電機能28Lおよび28R並びに導電領域29を形成するのに使われる伝導性材料は、Cu、W、またはAlなどの伝導性金属である。導電機能28Lおよび28Rは、導電領域29と同じかまたは異なった伝導性材料で構成することができる。

【0040】

導電機能28Lおよび28R並びに導電領域29を形成するのに使われる伝導性材料は、以下に限らないが、CVD、PECVD、スパッタリング、化学溶液堆積、またはメッキを含め、在来の堆積処理を用いて形成される。堆積の後、例えば化学機械研磨(CMP:chemical mechanical polishing)など、在来式の平坦化処理を使って平坦な相互接続構造体を得ることができる。

【0041】

パターン取りされたCu接合パッド30は、まず、導電機能28Lおよび28R並びに導電領域29の伝導性材料の形成に関して前述した技法の一つを用いて、相互接続レベル26の上にCuまたはCu合金のブランケット層を形成することによって、相互接続レベル26の上に形成される。次に、リソグラフィおよびエッチングを用いてパターン取りされたCu接合パッド30が形成される。図示のように、パターン取りされたCu接合パッド30の一つは、導電領域29の上面に接触している。この実施形態では、パターン取りされたCu接合パッド30が示され説明されているが、パターン取りなしCu接合パッドを用いる実施形態も後記で説明する。

【0042】

ここで図3を参照すると、第一デバイス・ウエハ10の該少なくともCu接合パッド30上に金属接着層32が形成された後の、図2の第一デバイス・ウエハ10が示されている。本実施形態において、金属接着層32は、例えば、蒸着、物理気相堆積、アルゴン・スパッタリング、化学気相堆積、プラズマ化学気相堆積、または原子層堆積などの非選択的堆積処理を用いて形成される。この「非選択的(“non−selective”)」とは、金属接着層32が全露出面に形成される堆積処理をいうものとする。

【0043】

金属接着層32は、CuまたはCu合金よりも酸素に対し高い親和力を有する金属または金属合金から成る。言い換えれば、金属接着層32は、CuまたはCu合金よりも酸素反応性の高い金属または金属合金から成る。具体的には、金属接着層32はMn、Ti、Co、Ta、W、Ru、およびNiの一つを含む。一つの実施形態において、金属接着層32は、Mn、またはTi、Co、Ta、W、Ni、およびRuの少なくとも一つと共に合金化されたMnを含む。別の実施形態では、金属接着層32は、Mn、Ti、Co、Ta、W、Ni、およびRuから選択された2つ以上を包含する金属合金を含む。

【0044】

金属接着層32の厚さは、用いられる金属または金属合金、および接着層を形成する際に使われた処理の条件の如何によって変わり得る。一つの実施形態において、金属接着層32は0.2nm〜20nmの厚さを有する。別の実施形態では、金属接着層32は0.5nm〜5nmの厚さを有する。いくつかの実施形態において、金属接着層32は単一層の材料である。別の実施形態では、金属接着層32は多層構造を含む。多層構造を用いる場合、多層構造体内の各金属接着材料は同じであってもまたは異なっていてもよい。

【0045】

ここで図4を参照すると、図3に示された第一デバイス・ウエハ10の上方に位置付けられた、パターン取りされたCu接合パッド72を含む第二デバイス・ウエハ50が示されている。第二デバイス・ウエハ50は、半導体デバイス層52Bおよび絶縁体層52Aを包含する半導体基板52を含む。半導体デバイス層52Bは、半導体基板12に関して前述した半導体材料の一つを含む。半導体デバイス層52Bの厚さは、通常、5nm〜5000nmの範囲内にある。本開示では、上記の厚さより上または下の他の厚さを用いることもできる。

【0046】

絶縁体層52Aは、半導体酸化物、半導体窒化物、もしくは半導体酸窒化物またはこれらの組み合わせを含む。絶縁体層52Aの厚さは、通常、5nm〜500nmの範囲内である。本開示では、上記の厚さより上または下の他の厚さを用いることもできる。

【0047】

一つの実施形態において、絶縁体層52Aおよび半導体デバイス層52Bは、基板の底部の半導体部分が、図4に示された第二デバイス・ウエハ50の作製の過程で除去された、半導体オン・インシュレータ基板のコンポーネントである。かかる実施形態において、基板の底部の半導体部分は、エッチングによって、または、例えばCMPもしくは研磨またはその両方などの平坦化処理を用いることによって除去することができる。半導体オン・インシュレータ基板の底部半導体部分の除去は、通常、第二デバイス・ウエハ50の上に取扱い基板(または取扱いウエハ)を形成した後で行われる。

【0048】

いくつかの実施形態において、絶縁体層52Aは、バルク半導体基板が処理され、少なくとも一つのデバイス、一つの相互接続レベル、および取扱い基板が含められた後、バルク半導体基板(これは半導体デバイス層52Bを表す)の底面上に形成される。

【0049】

半導体デバイス層52Bは、その中に形成された少なくとも一つの絶縁領域54を含む。この少なくとも一つの絶縁領域54を形成して、少なくとも一つの絶縁領域14に関して前述した材料をこれに含めることができる。

【0050】

第二デバイス・ウエハ50は、少なくとも部分的に半導体デバイス層52Bの上に形成された少なくとも一つの第二デバイス58をさらに含む。本実施形態において、少なくとも一つの第二デバイス58は、少なくともゲート誘電体60とゲート導体62とのゲート・スタックを含む電界効果トランジスタである。ゲート誘電体60およびゲート導体62を形成して、ゲート誘電体20およびゲート導体22に関して前述した材料および厚さを含めることができる。

【0051】

この電界効果トランジスタ(すなわち、少なくとも一つの第二デバイス58)は、半導体デバイス層52B内の、ゲート誘電体60とゲート導体62とを含むゲート・スタックのフットプリントに配置されたソース/ドレイン領域56Lおよび56Rをさらに含む。ソース/ドレイン領域56Lおよび56Rは、ソース/ドレイン領域16Lおよび16Rの形成に関して前述したようにして形成することができる。ゲート・スタック(60および62)の真下に所在し、ソース/ドレイン領域56L、56Rによって横方向に境界されている、半導体デバイス層52Bの領域は少なくとも一つの第二デバイス58のチャネル領域である。

【0052】

少なくとも一つのスペーサ63を、ゲート・スタック(すなわち、60および62)の側壁に配置することができる。少なくとも一つのスペーサ63は、少なくとも一つのスペーサ24に関して前述した材料の一つで構成できる。少なくとも一つのスペーサ63は、少なくとも一つのスペーサ24の形成に関して前述したのと同じ技法を使って形成することができる。

【0053】

第二デバイス・ウエハ50は、少なくとも一つの相互接続誘電体材料65内に配置された複数の導電機能66Lおよび66Rを包含する相互接続レベル64をさらに含む。相互接続誘電体材料65を形成して、相互接続誘電体材料27に関して前述した材料および厚さを含めることができる。導電機能66Lおよび66Rを形成して、導電機能28Lおよび28Rに関して前述した材料を含めることができる。

【0054】

少なくとも一つの第二デバイス58および相互接続レベル64を形成した後、相互接続レベル64の最上面に取扱い基板68が形成される。取扱い基板68は、ガラス、Al2O3、SiN、もしくは、例えば、カーボン、スピンオン有機/無機ポリマー、または軟質テープなど、他の容易に除去できる絶縁材料で構成することができる。取扱い基板68は、層転写処理を含め、当業者に周知の在来技法を用いて形成できる。

【0055】

次に、半導体オン・インシュレータの底部は、存在する場合、前述したように除去することができ、存在しなければ、次いで絶縁体層52Aを、熱成長または、例えば、CVD、PECVD、および化学溶液堆積などの堆積処理を用いて形成することができる。

【0056】

次に、スルー・ビア70は、半導体基板52を貫通し、相互接続誘電体材料65の少なくとも部分を貫通して形成することができる。スルー・ビア70の一つの端部は、導電機能すなわち66Rの少なくとも一つの水平面と接触しており、一方、別の端部は基板52の最底部の表面に配置される。

【0057】

スルー・ビア70は、導電機能28Lおよび28Rに関して前述した伝導性材料の一つを含み、該ビアは、リソグラフィおよびエッチングを用いて形成され、その後に、リソグラフィおよびエッチング処理によって生成されたビアの開口内に伝導性材料が形成される。スルー・ビア70の伝導性材料には、導電機能28Lおよび28Rに関して前述した伝導性材料の一つで構成することができる。スルー・ビア70の伝導性材料は、導電機能28Lおよび28Rに関して前述した技法の一つを使って形成できる。CMPなどの平坦化処理を使って平坦な構造体を得ることができる。

【0058】

スルー・ビア70を形成した後、絶縁体層52Aの表面上にCu接合パッド72が形成される。図示のようにCu接合パッド72の一つはスルー・ビア70の一端部と接触している。本開示のこの実施形態では、Cu接合パッド72はパターン取りされている。いくつかの実施形態では、パターン取りなしCu接合パッド(図示せず)を使うことができる。さらに、本開示の別の実施形態では、少なくともCu接合パッド72の表面上に別の金属接着層を形成することもできる。この実施形態は、本開示の図面中には示されていない。少なくともCu接合パッド72上に別の金属接着層が形成される場合、その別の金属接着層を形成して金属接着層32に関して前述したような材料を包含させることができる。この別の金属接着層は、金属接着層32の金属または金属合金と同一にすることも異ならせることもできるが、通常は同一である。

【0059】

図5を参照すると、2つのデバイス・ウエハ10と50とを相互に緊密に接触させ、2つのウエハを、各Cu接合パッド72のCu表面を各Cu接合パッド30のCu表面の上にほぼ垂直にそろえて整合し、次いで400℃未満の温度で接合した後の、図4の2つのデバイス・ウエハ10および50が示されている。別の実施形態では、この接合は50℃〜375℃の温度で行われる。

【0060】

いくつかの実施形態において、この接合処理の間、人の手、万力または他の類似の機械的手段により供される力など、外部の力をこの2つのデバイス・ウエハに加えることができる。別の実施形態では、接合処理の間、2つのデバイス・ウエハに外部の力は加えられない。

【0061】

この接合は、共に接合される2つのデバイス・ウエハの接合に対し不活性な環境で行うことができる。一つの実施形態において、この接合は、例えば、He、Ar、Ne、Xe、またはこれらの混合ガスを含め、不活性ガス中で行われる。別の実施形態では、接合処理の間の環境として窒素が使用可能である。窒素は単独で使うことも、前述の不活性ガスの一つと混合して使うこともできる。別の実施形態において、接合処理の間の環境として、フォーミング・ガス(すなわち、水素(モル分率は変わる)と窒素との混合ガス)を用いることができる。

【0062】

接合の過程で、Cu接合パッド上に位置する金属接着層32は、2つのCu表面から酸素原子を得て、Cu接合パッド30のCu表面とCu接合パッド72の別のCu表面との間に金属酸化物接合層74を形成する。これにより、接合後のCu接合パッド30およびCu接合パッド72は、接合が行われる前のCu接合パッドに比べて、その中により少ない酸素を有する。本開示において、用いられた金属接着層の種類および接合処理条件の如何により、Cu接合パッド30およびCu接合パッド72の各々で50〜99%の酸素の低減が達成可能である。

【0063】

しかして、金属酸化物接合層74は、金属または金属合金と酸素とを含む。金属酸化物接合層74は、Cu接合パッド30のCu表面とCu接合パッド72のCu表面との間に配置され、Cu接合パッド30およびCu接合パッド72のエッジに垂直に整合されて示されている。金属酸化物接合層74は、初期の金属接着層の厚さおよびCu接合パッドに元々包含されていた酸素の量の如何により、典型的には、0.3nm〜100nmの範囲の厚さを有し、1nm〜10nmの厚さであればさらに典型的である。本開示では、上記の厚さの範囲より大きい、または小さい他の厚さも用いることもできる。いくつかの実施形態において、金属酸化物接合層74は単一層構造である。別の実施形態では、金属酸化物接合層74は多層構造である。金属酸化物接合層74が多層構造の場合、多層構造の各層は、同じ組成または相異なる組成とすることができる。

【0064】

ここで図6を参照すると、第二デバイス・ウエハ50から取扱い基板68を除去した後の、図5の接合された2つのデバイス・ウエハが示されている。一つの実施形態において、取扱い基板68は、例えば、取扱い基板が炭化水素ベースの場合はO2プラズマなど、取扱い基板がSiNの場合は熱リン酸などの選択エッチング処理を用いて除去することができる。別の実施形態において、化学機械平坦化もしくは研磨またはその両方を使って、取扱い基板68を接合された構造体から除去することができる。

【0065】

図6に示された構造体の上にさらなるデバイス・ウエハを積み重ねることができ、前述した基本処理ステップを用いて、該さらなるデバイス・ウエハと接合構造体との間の接合を実現することができる。かくして、垂直に順に積み重ねられた複数のデバイス・ウエハを含む3D集積回路を形成することができる。

【0066】

ここで、本開示の別の実施形態を示している図7〜図11を参照する。図7〜図11に示されたこの実施形態は、パターン取りなしCu接合パッドが用いられることを除いて、上記図2〜図6に示された実施形態と類似である。

【0067】

まず、図7を参照すると、本開示の一つの実施形態において用いることの可能な、パターン取りなしCu接合パッド80を含む第一デバイス・ウエハ10が示されている。具体的には、第一デバイス・ウエハ10は、図2のパターン取りされたCu接合パッド30がパターン取りなしCu接合パッド80に置き換えられていることを除いて、図2に示された第一デバイス・ウエハ10と同じコンポーネントを含む。パターン取りなしCu接合パッド80は、パターン取りされたCu接合パッド30の形成に関して前述した堆積処理を用いて形成することができる。Cu接合パッドのブランケット層の堆積の後で、該ブランケットCu接合パッドのパターン取りは行われない。このパターン取りなしCu接合パッド80の材料および厚さは、パターン取りされたCu接合パッド30に関して前述したものと同じである。

【0068】

ここで図8を参照すると、第一デバイス・ウエハのパターン取りなしCu接合パッド80上に金属接着層82を形成した後の、図7の第一デバイス・ウエハが示されている。金属接着層82を形成して、金属接着層32に関して前述した材料および厚さを含めることができる。

【0069】

図9を参照すると、図8に示された第一デバイス・ウエハ10の上方に位置付けられた、別のパターン取りなしCu接合パッド84を含む第二デバイス・ウエハ50が示されている。第二デバイス・ウエハ50は、パターン取りされたCu接合パッド72がパターン取りなしCu接合パッド84に置き換えられていることを除いて、前述した(図4の)第二デバイス・ウエハ50と同じエレメントを含む。パターン取りなしCu接合パッド84は、パターン取りされたCu接合パッド30に関して前述した堆積処理を用いて形成される。Cu接合パッドのブランケット層の堆積の後で、該ブランケットCu接合パッドのパターン取りは行われない。このパターン取りなしCu接合パッド84の材料および厚さは、パターン取りされたCu接合パッド30に関して前述したものと同じである。

【0070】

ここで図10を参照すると、400℃未満の温度で接合された後の、図9の2つのデバイス・ウエハが示されている。図5に示された接合構造体の形成に関連して説明した接合処理における他の詳細および実施形態は、ここで図10に示された接合構造体の形成のためにも使うことができる。前述の実施形態と違って、金属酸化物接合層74は、パターン取りなしCu接合パッド80とパターン取りなしCu接合パッド84との間に切れ目なく存在している。前述の実施形態と同様に、接合の後のパターン取りなしCu接合パッド80およびパターン取りなしCu接合パッド84は、接合の前のパターン取りなしCu接合パッド80およびパターン取りなしCu接合パッド84と比べて、その中により少ない酸素を有する。

【0071】

ここで図11を参照すると、第二デバイス・ウエハ50から取扱い基板68を除去した後の、図10の2つの接合されたデバイス・ウエハが示されている。取扱い基板68を除去するための詳細は、本開示の前述の実施形態で述べたものと同じである。

【0072】

図11に示された接合構造体の上にさらなるデバイス・ウエハを積み重ねることができ、前述した基本処理ステップを用いて、該さらなるデバイス・ウエハと接合構造体との間の接合を実現することができる。かくして、垂直に順に積み重ねられた複数のデバイス・ウエハを含む3D集積回路を形成することができる。

【0073】

ここで図12〜図15を参照すると、本開示の別の実施形態が示されている。本開示のこの実施形態は、まず、第一デバイス・ウエハ10および第二デバイス・ウエハ10’を用意することから開始される。第一デバイス・ウエハ10のコンポーネントは、図2に示された第一デバイス・ウエハ10中に存在するものと類似である。第二デバイス・ウエハ10’のコンポーネントも、図2に示された第一デバイス・ウエハ10に関して前述したものと同じである。第二デバイス・ウエハ10’のコンポーネントを識別するために主な指定(prime designation)が用いられるが、それでもなお、第一デバイス・ウエハ10のコンポーネントと同等である。

【0074】

ここで図13を参照すると、少なくとも一つのデバイス・ウエハのパターン取りされたCu接合パッドの上に少なくとも一つの金属接着層32が形成された後の、図12の2つのデバイス・ウエハ10および10’が示されている。いくつかの実施形態では、別の金属接着層32を両方のデバイス・ウエハに形成することができる。この少なくとも一つの金属接着層32は、図3に示された構造体に関連して前述したものと同じである。

【0075】

ここで図14を参照すると、デバイス・ウエハの一つ(すなわち、デバイス・ウエハ10’)を反転し、第一デバイス・ウエハ10のパターン取りされたCu接合パッド30を第二デバイス・ウエハ10’のパターン取りされたCu接合パッド30’に整合した後の、図13の2つのデバイス・ウエハ10および10’が示されている。この反転は、デバイス・ウエハの一つ、すなわち第二デバイス・ウエハ10’を180°回転させることによって実現される。

【0076】

図15を参照すると、400℃未満の温度で接合した後の、図14の2つのデバイス・ウエハ10および10’が示されている。図5に示された接合構造体の形成に関連して説明した接合処理の他の詳細および実施形態は、ここで図15に示された接合構造体の形成のためにも使うことができる。

【0077】

図15に示された接合構造体の上にさらなるデバイス・ウエハを積み重ねることができ、前述した基本処理ステップを用いて、該さらなるデバイス・ウエハと接合構造体との間の接合を実現することができる。かくして、垂直に順に積み重ねられた複数のデバイス・ウエハを含む3D集積回路を形成することができる。

【0078】

ここで図16を参照すると、金属接着層を形成するのに選択的堆積処理が使われていることを除き、図2〜図6に示された基本的処理ステップを使って形成できる3D集積回路が示されている。これにおいては、金属接着層は、第一および第二デバイス・ウエハのいずれの相互接続誘電体材料にも接触することはない。選択的堆積は、Cu/誘電体パターンの未処理の表面上または改修された表面上への化学気相堆積、または原子層堆積によって実現することができる。典型的な例は、化学気相堆積処理によるMnまたはCoの選択的堆積である。

【0079】

ここで図17を参照すると、金属接着層を形成するのに選択的堆積処理が使われていることを除き、図12〜図15に示された基本的処理ステップを使って加工できる3D集積回路が示されている。これにおいては、金属接着層は、第一および第二デバイス・ウエハのいずれの相互接続誘電体材料にも接触することはない。選択的堆積は、Cu/誘電体パターンの未処理の表面上または改修された表面上への化学気相堆積、または原子層堆積によって実現することができる。典型的な例は、化学気相堆積処理によるMnまたはCoの選択的堆積である。

【0080】

本開示のいくつかの実施形態において、上記の処理ステップを使って、一つのデバイス・ウエハのパターン取りなしのCu接合パッドを、別のデバイス・ウエハの少なくとも一つのパターン取りされたCu接合パッドに接合することができる。

【0081】

本開示を、その好適な実施形態に関連させて具体的に示し説明してきたが、当然のことながら、当業者は本開示の精神および範囲から逸脱することなく、形態および詳細における前述のまたは他の変更を加えることが可能である。従って、本開示は、説明され提示された通りの形態および詳細に限定されるものでなく、添付の請求項の範囲に含まれることが意図されている。

【符号の説明】

【0082】

12 半導体基板

14 絶縁領域

16L ソース/ドレイン領域

16R ソース/ドレイン領域

20 ゲート誘電体

22 ゲート導体

24 スペーサ

26 相互接続レベル

27 相互接続誘電体材料

28L 導電機能

28R 導電機能

29 ビア

30 パターン取りされたCu接合パッド

32 金属接着層

52 半導体基板

52A 絶縁体層

52B 半導体デバイス層

54 絶縁領域

56L ソース/ドレイン領域

56R ソース/ドレイン領域

60 ゲート誘電体

62 ゲート導体

63 スペーサ

64 相互接続レベル

65 相互接続誘電体材料

66L 導電機能

66R 導電機能

70 スルー・ビア

72 Cu接合パッド

74 金属酸化物接合層

【技術分野】

【0001】

本開示は、半導体構造体およびそれを形成する方法に関する。さらに具体的には、本開示は、改良されたCu−Cu接合が実現された三次元(3D)集積回路に関する。

【背景技術】

【0002】

現今の電子デバイスに対するスケーリング条件に対処するため、チップ設計者らおよび製造者らは、利用可能なチップ・スペースを最良に最大化する回路設計を工夫するよう常に努めている。その結果得られた設計は、多くの場合いくつかの異なるレベルに展開される。例えば、かかる三次元(3D)回路設計の一つには、積み重ね構造に位置付けされたいくつかの異なるデバイス層を含むものがある。別の事例では、3D設計が、層間の垂直ビアによって共に接続された、複数のデバイス層と相互接続層とから成る垂直スタックを含んでいることがある。

【発明の概要】

【発明が解決しようとする課題】

【0003】

典型的な3D集積回路において、2つの能動デバイス・ウエハが、背合わせに積み重ねられる。これら2つの能動デバイス・ウエハは、次いで、熱圧着を用い、Cu−Cu接合を行って共に接合される。この接合処理には、妥当な高温および圧力両方の印加が必要である。かかる直接的Cu−Cu合では、共に接合されるCu表面にCuOが形成される。Cu表面におけるCuOの存在は、接合構造体の抵抗を増加させ、特に接着性など、接合構造体の信頼性を低下させる。

【0004】

このため、接合されたCu−Cu表面におけるCuOの形成を排除した、改良されたCu表面の共接合の方法が必要とされている。

【課題を解決するための手段】

【0005】

第一デバイス・ウエハの少なくともCu表面、通常はCu接合パッド、上に少なくとも一つの金属接着層が形成される。別のCu表面、通常は別のCu接合パッド、を有する第二デバイス・ウエハが、第一デバイス・ウエハのCu表面の上で且つ少なくとも一つの金属接着層上に位置付けられる。次いで、第一および第二デバイス・ウエハが共に接合される。この接合ステップは、外部から加える圧力の使用の有無にかかわらず、これらデバイス・ウエハを400℃未満の温度に加熱するステップを含む。加熱の過程で、2つのCu表面は共に接合され、該少なくとも一つの金属接着層が2つのCu表面から酸素原子を得て、これらCu表面の間に少なくとも一つ金属酸化物接合層を形成する。

【0006】

本開示の一つの態様において、三次元(3D)集積回路を形成する方法が提供される。本開示の方法は、少なくともCu表面を含む、第一デバイス・ウエハを用意するステップを含む。次に、そのCu表面の上に金属接着層が形成される。別のCu表面を有する第二デバイス・ウエハが、第一デバイス・ウエハの金属接着層上で且つCu表面の上に位置付けられる。第一および第二デバイス・ウエハは、400℃未満の温度で共に接合される。接合の過程で、金属接着層は、2つのCu表面から酸素原子を得て、Cu表面と別のCu表面との間に金属酸化物接合層を形成する。

【0007】

本開示の別の態様は、三次元(3D)集積回路に関する。本3D集積回路は、Cu表面を有する第一デバイス・ウエハと別のCu表面を有する第二デバイス・ウエハとの垂直スタックを含み、金属酸化物接合層が、第一デバイス・ウエハのCu表面と第二デバイス・ウエハの別のCu表面との間に配置される。

【図面の簡単な説明】

【0008】

【図1】3D集積回路を形成するのに用いることのできる、本開示の各種処理ステップを示す、ブロック図様式の概略図である。

【図2】本開示の一つの実施形態において用いることのできる、パターン取りされたCu接合パッドを含む、第一デバイス・ウエハを(断面図を介して)示した図示表現である。

【図3】第一デバイス・ウエハの少なくともCu接合パッド上に金属接着層を形成した後の、図2の第一デバイス・ウエハを(断面図を介して)示した図示表現である。

【図4】図3に示された第一デバイス・ウエハの上方に位置付けられた、少なくとも一つ他のCu接合パッドを含む第二デバイス・ウエハを(断面図を介して)示した図示表現である。

【図5】400℃未満の温度で接合した後の、図4の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図6】第二デバイス・ウエハから取扱い用基板を除去した後の、図5の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図7】本開示の一つの実施形態において用いることのできるパターン取りなしCu接合パッドを含む第一デバイス・ウエハを(断面図を介して)示した図示表現である。

【図8】第一デバイス・ウエハのパターン取りなしCu接合パッド上に金属接着層を形成した後の、図7の第一デバイス・ウエハを(断面図を介して)示した図示表現である。

【図9】図8に示された第一デバイス・ウエハの上方に位置付けられた、少なくとも一つの他のCu接合パッドを含む第二デバイス・ウエハを(断面図を介して)示した図示表現である。

【図10】400℃未満の温度で接合した後の、図9の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図11】第二デバイス・ウエハから取扱い基板を除去した後の、図10の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図12】本開示のさらなる実施形態で用いることができる、パターン取りされたCu接合パッドを共に含む2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図13】デバイス・ウエハの少なくとも一つの、パターン取りされたCu接合パッド上に少なくとも一つの金属接着層を形成した後の、図12の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図14】デバイス・ウエハの一つを180°回転させ、一つのデバイス・ウエハのパターン取りされたCu接合パッドを、他方のデバイス・ウエハのパターン取りされたCu接合パッドに整合させた後の、図13の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図15】400℃未満の温度で接合した後の、図14の2つのデバイス・ウエハを(断面図を介して)示した図示表現である。

【図16】金属接着層を形成するのに選択的堆積処理が使われていることを除き、図2〜図6に示された基本的処理ステップを使って形成できる3D集積回路を(断面図を介して)示した図示表現である。

【図17】金属接着層を形成するのに選択的堆積処理が使われていることを除き、図12〜図15に示された基本的処理ステップを使って形成できる3D集積回路を(断面図を介して)示した図示表現である。

【発明を実施するための形態】

【0009】

改良されたCu−Cu接合を有する三次元(3D)集積回路およびこれを形成する方法に関する本開示を、以下の詳解および本出願に添付された図面を参照しながら、以降により詳細に説明する。なお、本出願の図面は、例示目的で提示されており、そのため一定の縮尺では描かれていない。

【0010】

以下の説明において、本発明が十分理解されるように、特定の構造体、コンポーネント、材料、寸法、処理ステップ、および技法など、数々の具体的詳細が示される。しかしながら、当業者は、本開示が、これらの具体的詳細が無くても、実行可能な別の処理オプションを使って実施できることをよく理解していよう。他の例では、本開示の各種実施形態の不明瞭化を避けるために、周知の構造または処理ステップは詳細には説明していない。

【0011】

層、領域、または基板などのエレメントが別のエレメントの「上に(“on”)」ある、または「覆って(“over”)」いると言及された場合、それが別のエレメントの直接上にあることも、介在するエレメントが存在することもあることを理解されたい。これに対し、あるエレメントが別のエレメントの「直接上に(“directly on”)」ある、または「直接覆って(“directly over”)」いると言及された場合、介在するエレメントは存在しない。また、あるエレメントが別のエレメントの「真下に(“beneath”)」または「下に(“under”)」あると言及された場合、それが別のエレメントの直接真下または下にあることも、介在するエレメントが存在することもあることを理解されたい。これに対し、あるエレメントが別のエレメントの「直接真下に(“directly beneath”)」または「直接下に(“directly under”)」あると言及され場合、介在するエレメントは存在しない。

【0012】

前述したように、本開示は、三次元(3D)集積回路を形成する方法を提供する。本開示の方法は、図1に示されたブロック図中に概略的に表されている。本開示の方法は、Cu表面を含む第一デバイス・ウエハを用意するステップを含む(ステップ100)。次に、第一デバイス・ウエハの少なくともCu表面上に金属接着層が形成される(ステップ102)。別のCu表面を有する第二デバイス・ウエハが、第一デバイス・ウエハの金属接着層上で且つCu表面の上に位置付けられる(ステップ104)。第一および第二デバイス・ウエハは、400℃未満の温度で共に接合される(ステップ106)。接合の過程で、金属接着層は、2つのCu表面から酸素原子を得て、第一デバイス・ウエハのCu表面と第二デバイス・ウエハの別のCu表面との間に金属酸化物接合層を形成する。

【0013】

本開示の方法は、Cu表面を含む第一デバイス・ウエハと別のCu表面を含む第二デバイス・ウエハとの垂直スタックを含む三次元(3D)集積回路を提供し、金属酸化物接合層が、第一デバイス・ウエハのCu表面と第二デバイス・ウエハの別のCu表面との間に配置される。この金属酸化物接合層は、Cu−Cu接合面の抵抗を増加させることなく、異なるデバイス・ウエハの間の改良されたCu−Cu接合を提供する。

【0014】

本開示全体を通して使われる「デバイス・ウエハ(“device wafer”)」という用語は、半導体基板と、少なくとも部分的に半導体基板上に配置された少なくとも一つのデバイスと、少なくとも一つの導電機能(ビアもしくはラインまたはその両方)が中に内蔵されている少なくとも一つの相互接続誘電体材料を含む、相互接続レベルと、相互接続レベルの表面に配置され、少なくとも一つの相互接続材料内に配置された導電機能の少なくとも一つと接触しているCu接合パッドと、を含む半導体構造体をいう。いくつかの実施形態において、Cu接合パッドはパターン取りすることができ、しかして、相互接続レベルの一部の部分上にだけ配置される。他の実施形態において、Cu接合パッドをパターン取りせず、しかして相互接続レベル全体の上に配置することができる。

【0015】

この少なくとも一つのデバイスは、電解効果トランジスタ、抵抗、コンデンサ、BiCMOS、ダイオード、導体、マイクロ電気機械(MEM:microelectromechanical)デバイス、熱冷却デバイス、またはこれらの任意の組み合わせとすることができる。これらのデバイスは同じまたは異なる極性を有することができ、同じまたは異なる機能を有することができる。例えば、これらデバイスは、メモリ、マイクロプロセッサ、マイクロコントローラ、センサ、熱冷却エレメント、またはこれらの機能の任意の組み合わせのいずれとしても用いることができる。

【0016】

まず、本開示の方法を使って3D集積回路を作製するための、本開示の一つの実施形態を示している図3〜図6を参照する。なお、以下の詳解および図面では、2つのデバイス・ウエハの垂直積み重ねおよび共接合を説明、図示しているが、本開示は、2つだけのデバイス・ウエハの垂直積み重ねおよび共接合には限定されない。代わりに、本開示は、本開示の方法を使って、n個のデバイス・ウエハが垂直に積み重ねられ共に接合される実施形態においても用いることができ、nは2より大きい整数である。

【0017】

最初に、図2を参照すると、相互接続レベル26の上に配置されパターン取りされたCu接合パッド30を含む第一デバイス・ウエハ10が示されている。また、第一デバイス・ウエハ10は、少なくとも一つの絶縁領域14が中に配置されている半導体基板12の表面上に、少なくとも部分的に配置された少なくとも一つの第一デバイス18も含む。これらの図面および以下の詳解において、この少なくとも一つの第一デバイス18は、少なくとも一つのゲート誘電体20と上に重なるゲート導体22とのゲート・スタックを含む電界効果トランジスタである。ゲート・スタック(20および22)の側壁上に、少なくとも一つのスペーサ24を配置することができる。ソース/ドレイン領域16Lおよび16Rは、ゲート・スタック(20および22)のフットプリントに示されており、半導体基板12の上部内に配置されている。

【0018】

相互接続レベル26は、複数の導電機能28L、28Rが中に配置されている、少なくとも一つの相互接続誘電体材料27を含む。図示のように、複数の導電機能の導電機能28Lの一つは電界効果トランジスタのソース/ドレイン領域16Lに接触しており、一方、複数の導電機能の導電機能28Rの別の一つは電界効果トランジスタのソース/ドレイン領域16Rに接触している。また、図示のように、導電機能28Rは、相互接続レベル26の上に形成されたパターン取りされたCu接合パッド30の一つの表面と接触している導電領域、すなわちビア29を有する。

【0019】

図2に示された第一デバイス・ウエハ10は、当業者に周知の技法を利用して形成することができる。また、第一デバイス・ウエハ10のさまざまなコンポーネントは、これも当業者に周知の材料で形成することができる。

【0020】

以下に、かかる第一デバイス・ウエハ10をどのように作製できるか、並びに、第一デバイス・ウエハ10の中に配置できるコンポーネントの各々に対するいくつかの材料について、一部の詳細を提示する。かかる詳細を提示はするが、当業者に周知の他の方法もしくは材料またはその両方を使って、図2に示された第一デバイス・ウエハ10を形成することも可能である。

【0021】

第一デバイス・ウエハ10の半導体基板12は、以下に限らないが、Si、Ge、SiGe、SiC、SiGeC、GaAs、GaN、InAs、InPおよび他のIII/V族またはII/VI化合物半導体全てを含め、任意の半導体材料で構成することができる。また、半導体基板12には、有機半導体、またはSi/SiGe、シリコン・オン・インシュレータ(SOI:silicon−on−insulator)、SiGeオン・インシュレータ(SGOI:SiGe−on−insulator)またはゲルマニウム・オン・インシュレータ(GOI:germanium−on−insulator)などの層状半導体を含めることもできる。半導体オン・インシュレータ基板は最上部から底部に向けて、最上部半導体デバイス層と、絶縁体層と、底部半導体部分とを含む。本開示のいくつかの実施形態において、半導体基板12は、Si含有半導体材料、すなわちシリコンを含む半導体材料から成る。半導体基板12は、ドープ、非ドープとすることができ、またはその中にドープ領域と非ドープ領域とを含めることができる。半導体基板12には、単一の結晶方位を含めることができ、または種々の結晶方位を含めることもできる。説明の便宜上、第一デバイス・ウエハの半導体基板12はバルク半導体から成るものとする。「バルク(“bulk”)」とは、基板の全体が、半導体材料から成ることをいうものする。

【0022】

また半導体基板12には、第一ドープ(n−またはp−)領域および第二ドープ(n−またはp−)領域を含めることができる。簡明化のため、これらドープ領域は、本出願のどの図面にも具体的には示していない。第一ドープ領域と第二ドープ領域とは同じにすることもでき、またはこれらに異なった伝導性もしくは異なったドーピング濃度またはその両方を持たせることもできる。これらドープ領域は「ウェル(“well”)」として知られており、在来のイオン注入処理を用いて形成することができる。

【0023】

半導体基板12の中に少なくとも一つの絶縁領域14を形成することができる。この少なくとも一つの絶縁領域14は、トレンチ絶縁領域またはフィールド酸化物絶縁領域とすることができる。トレンチ絶縁領域は当業者には周知のトレンチ絶縁処理を用いて形成される。例えば、トレンチ絶縁領域の形成には、リソグラフィ、エッチング、およびトレンチ誘電体でトレンチを満たすステップを使うことができる。随意的に、トレンチ充填の前にトレンチ中にライナを形成することができ、トレンチ充填後に緻密化ステップを実施することができ、トレンチ充填の後で平坦化処理を行うこともできる。フィールド酸化物は、いわゆるシリコンの局所酸化処理を用いて形成することができる。当業者には周知のように、少なくとも一つの絶縁領域14は、隣接するデバイスが反対の伝導性を有する場合、すなわちnFETおよびpFETの場合などに通常必要となる、隣接するデバイスの間の絶縁を提供する。本明細書では、隣接する絶縁領域の間に位置する半導体基板12の部分を、半導体基板12の「活性化領域」という。半導体基板12の活性化領域は、その中にデバイスが少なくとも部分的に形成されることになる領域である。

【0024】

その中にデバイス(群)が形成されることになる活性化領域(群)が画定された後、半導体基板12の該活性化領域(群)中にデバイス(群)が少なくとも部分的に形成される。これら図面において、前述したように、この例示の実施形態で形成される少なくとも一つの第一デバイス18は電界効果トランジスタである。この電界効果トランジスタは少なくとも一つのゲート誘電体20とゲート導電体22とのゲート・スタックを含む。

【0025】

ゲート誘電体20は任意の絶縁材料を含む。一つの実施形態において、ゲート誘電体20は、半導体酸化物、半導体窒化物、もしくは半導体酸窒化物またはこれらの組み合わせを含む。別の実施形態では、ゲート誘電体20は、酸化ケイ素の誘電率の例えば3.9より大きな誘電率を有する誘電体金属酸化物を含む。本明細書では、酸化ケイ素の誘電率より大きな誘電率を有する、かかる誘電体金属酸化物をhigh−k誘電体材料という。典型的には、本開示において採用可能なhigh−kゲート誘電体は4.0より大きな誘電率を有するが、8.0より大きな誘電率であればさらに典型的である。ゲート誘電体20として採用可能な代表的high−k誘電体材料には、以下に限らないが、HfO2、ZrO2、La2O3、Al2O3、TiO2、SrTiO3、LaAlO3、Y2O3、HfOxNy、ZrOxNy、La2OxNy、Al2OxNy、TiOxNy、SrTiOxNy、LaAlOxNy、Y2OxNy、これらのケイ酸塩、およびこれらの合金が含まれる。xの各値は、独立して0.5〜3であり、yの各値は、独立して0〜2である。いくつかのの実施形態において、前述の誘電体材料の少なくとも2つによる多層スタックを用いることができる。例えば、一つの実施形態において、ゲート誘電体20には、半導体酸化物すなわち酸化ケイ素の下部層と、例えばHfO2などのhigh−k誘電体材料の上部層とを含めることができる。

【0026】

ゲート誘電体20の厚さは、これを形成するのに使われる技法によって変わり得る。しかしながら、典型的には、ゲート誘電体20は、0.5nm〜10nmの厚さを有し、1.0nm〜5nmであればさらに典型的である。本開示のいくつかの実施形態において、用いられるゲート誘電体20に1nmまたはそれ以下のオーダーの有効酸化物厚さを持たせることができる。

【0027】

ゲート誘電体20は、例えば、化学気相堆積(CVD:chemical vapor deposition)、物理気相堆積(PVD:physical vapor deposition)、分子ビーム堆積(MBD:molecular beam deposition)、パルス・レーザ堆積(PLD:pulsed laser deposition)、液体ミスト化学堆積(LSMCD:liquid source misted chemical deposition)、原子層堆積(ALD:atomic layer deposition)、および他の類似の堆積処理を含め、当該技術において周知の方法によって形成することができる。いくつかの実施形態において、特に半導体酸化物、窒化物もしくは酸窒化物またはこれらの組み合わせがゲート誘電体20として用いられる場合、ゲート誘電体20は、例えば、熱酸化もしくは熱窒化またはその両方など、熱処理によって形成することができる。かかる事例では、半導体酸化物、窒化物もしくは酸窒化物またはこれらの組み合わせの半導体部分は、下層の半導体基板12のものと同じ半導体材料を含む。

【0028】

図2に示された、少なくとも一つ第一デバイス18、すなわち電界効果トランジスタのゲート・スタックのゲート導体22は、以下に限らないが、多結晶シリコン、多結晶シリコン・ゲルマニウム、元素金属(例えば、タングステン、チタン、タンタル、アルミニウム、ニッケル、ルテニウム、パラジウム、および白金)、少なくとも2つの元素金属の合金、窒化元素金属(例えば、窒化タングステン、窒化アルミニウム、および窒化チタン)、ケイ化元素金属(例えば、ケイ化タングステン、ケイ化ニッケル、ケイ化チタン)およびこれらの多層を含め、任意の伝導性材料を含む。一つの実施形態において、ゲート導体22はnFET金属から成る。別の実施形態では、ゲート導体22は、pFET金属から成る。またさらなる実施形態では、ゲート導体22は多結晶シリコンから成り、下層の伝導性金属部分を有する場合も有しない場合もある。

【0029】

ゲート導体22は、例えば、化学気相堆積(CVD)、プラズマ化学気相堆積(PECVD:plasma enhanced chemical vapor deposition)、蒸着、物理気相堆積(PVD)、スパッタリング、化学溶液堆積、原子層堆積(ALD)および他の類似の堆積処理を含め、在来の堆積処理を用いて形成することができる。ゲート導体22としてSi含有材料が使われる場合、該Si含有材料は、インサイチュ(in−situ)ドーピングの堆積処理を用いるか、もしくは堆積の後でイオン注入またはガス相ドーピングンなどのステップを用い、適切な不純物がSi含有材料中に導入されるようにして、適切な不純度内にドープすることができる。ケイ化金属を形成する場合、在来のケイ化処理を用いることができる。

【0030】

いくつかの実施形態において、ゲート誘電体20およびゲート導体22は、ブランケット層として形成され、然る後、パターン取り処理を使ってこれらを含むゲート・スタックが形成される。このパターン取り処理は、リソグラフィ(ゲート導体22の上面の上にフォトレジストを塗布し、フォトレジストを放射露光させ、在来の現像液を使って露光したレジストを現像する処理)を含む。このリソグラフィ・ステップでは、ゲート導体22のブランケット層の上にパターン取りされたフォトレジストが得られる。次いで、エッチング処理を使って、パターン取りされたフォトレジストから、その下部のゲート誘電体およびゲート導体材料のブランケット層にパターンを転写する。このエッチングには、例えば、反応性イオンエッチング、プラズマエッチング、イオンエッチング、またはレーザ・アブレーションなどドライ・エッチング処理を含めることができる。このエッチングには、ゲート誘電体およびゲート導体材料のブランケット層の、パターン取りされたフォトレジストによって保護されていない部分を除去するために、一つ以上の化学腐食液が使われる湿式化学エッチング処理をさらに含めることができる。パターン取りされたフォトレジストは、アッシング処理を用いて除去することができる。

【0031】

他の実施形態において、ゲート誘電体20とゲート導体22とを含むゲート・スタックは、置換ゲート処理を用いて形成される。かかる処理では、少なくとも犠牲ゲート材料を含むスタックが、平坦化誘電体材料中に存在する開口部の中に形成される。該少なくとも犠牲ゲート材料が除去され、次いで前述したゲート導体材料の一つで置き換えられる。いくつかの実施形態において、置換ゲート処理には、同様に、犠牲ゲート誘電体材料を含めることもできる。かかる実施形態では、犠牲ゲート材料および犠牲ゲート誘電体は両方とも除去され、前述のゲート導体材料の一つと前述のゲート誘電体材料の一つとに置き換えられる。

【0032】

少なくとも一つの第一デバイス18として示された電界効果トランジスタには、少なくとも一つのスペーサ24をさらに含めることができる。いくつかの実施形態において、少なくとも一つのスペーサ24は、少なくともゲート誘電体20とゲート電極22とを含むゲート・スタックの側壁から省くことができる。少なくとも一つのスペーサ24は、存在する場合、例えば、酸化ケイ素、窒化ケイ素、もしくは酸窒化ケイ素またはこれらの組み合わせなど、酸素不浸透性の誘電体材料から成る。少なくとも一つのスペーサ24は、酸素不浸透性の誘電体材料の堆積とその後のエッチングによって形成することができる。いくつかの実施形態において、少なくとも一つのスペーサ24を形成するのに熱処理を用いることができる。

【0033】

また、図2に示された電界効果トランジスタ(すなわち、少なくとも一つの第一デバイス18)は、ソース/ドレイン領域16Lおよび16Rを含む。ソース/ドレイン領域16Lおよび16Rは、ゲート誘電体20とゲート導体22とを含むゲート・スタックの形成の前でもまたは後でも、イオン注入およびアニーリングを用いて形成することができる。イオン注入処理のための条件およびドーパントは当業者には周知である。アニールは、半導体基板12中にイオン注入されたドーパントを活性化するもので、約800℃以上の温度に加熱するステップを含む。ゲート・スタック(20および22)の真下に所在しソース/ドレイン領域16L、16Rによって横方向に境界されている、半導体基板12の部分はトランジスタのチャネル領域である。

【0034】

少なくとも一つの第一デバイス18を形成した後、相互接続レベル26が形成される。相互接続レベル26は、単一の相互接続レベルとすることもでき、または、垂直に積み重ねられ、電気的に接続された複数の相互接続レベル群とすることもできる。相互接続レベル26は、複数の導電機能28Lおよび28Rが中に配置されている、少なくとも一つの相互接続誘電体材料27を含む。複数の導電機能の導電機能28Lの一つは、電界効果トランジスタのソース/ドレイン領域16Lに接触しており、一方、複数の導電機能の導電機能28Rの別の一つは、電界効果トランジスタのソース/ドレイン領域16Rに接触している。導電機能28Rは、相互接続レベル26の上に形成されたパターン取りされたCu接合パッド30の一つ、の表面と接触している導電領域、すなわちビア29を有する。

【0035】

相互接続レベル26は、例えばダマシン処理を含め、当該技術分野で周知の技法を使って形成される。ダマシン処理では、少なくとも一つの相互接続誘電体材料27が最初に形成され、次いで、リソグラフィおよびエッチングを使って、少なくとも一つ相互接続誘電体材料27中に複数の開口部が形成される。複数の開口部は、ビア開口、ライン開口、またはビア開口およびライン開口の組み合わせとすることができる。ビア開口およびライン開口によって開口部が画定されると、2回目の繰り返しリソグラフィおよびエッチングを用いることができる。かかる開口部の組み合わせにおいて、ビアとラインとは相互に連通している。

【0036】

これら開口部は、次いで伝導性材料で充填されて、導電機能28Lおよび28Rを形成する。

【0037】

いくつかの実施形態において、導電領域29は、導電機能28Lおよび28Rと同時に形成することができる。他の実施形態では、導電領域29は、導電機能28Lおよび28Rの後で形成することができる。かかる実施形態では、導電機能28Lおよび28Rの各々は、第一相互接続誘電体材料の上面とほぼ同一平面上にある最上面を有する。次いで第二相互接続誘電体材料(第一相互接続誘電体材料と同じかまたは異なる)が形成され、導電領域29が、導電機能28Lおよび28Rの形成に関して前述したのと同じ技法を使って形成される。この特定の実施形態において、第一および第二相互接続誘電体材料は、本開示のいくつかの実施形態で使用可能な多層レベルの相互接続構造を形成する。

【0038】

相互接続レベル26の少なくとも一つの相互接続誘電体材料27には、無機誘電体または有機誘電体を含む任意のレベル間またはレベル内誘電体を含めることができる。該少なくとも一つの相互接続誘電体材料27は、多孔質であっても非多孔質であってもよい。多孔質の誘電体材料は、一般に、非多孔質のものよりも低い誘電率を有する。この少なくとも一つの相互接続誘電体材料27として使用可能な適切な誘電体の一部の例には、以下に限らないが、SiO2、シルセスキオキサン、Si、C、OおよびH原子を含むCドープ酸化物(すなわち有機シリケート)、熱硬化性ポリアリーレン・エーテル、またはこれらの多層が含まれる。本出願では、「ポリアリーレン(“polyarylene”)」という用語は、結合、縮合環、または 例えば酸素、硫黄、スルホン、スルホキシド、カルボニル等などの不活性連結基で、共に結び付けられた、アリール部分または不活性に置換されたアリール部分をいう。一つの実施形態において、少なくとも一つの相互接続誘電体材料27は、約4.0またはそれ以下の誘電率を有する。別の実施形態では、少なくとも一つの相互接続誘電体材料27は、約2.8またはそれ以下の誘電率を有する。本開示で述べる全ての誘電率は、別途の記載がなければ真空に対するものである。少なくとも一つの相互接続誘電体材料27の厚さは、用いられる誘電体材料、および相互接続レベル26内の誘電体の正確な数の如何によって変わり得る。一般に、通常の相互接続構造に対しては、該少なくとも一つの相互接続誘電体材料27は200nm〜450nmの厚さを有する。

【0039】

導電機能28Lおよび28R並びに導電領域29は、例えば、ポリSi、伝導性金属、少なくとも2つの伝導性金属を含む合金、伝導性金属シリサイド、またはこれらの組み合わせなどの伝導性材料を含む。一つの実施形態において、導電機能28Lおよび28R並びに導電領域29を形成するのに使われる伝導性材料は、Cu、W、またはAlなどの伝導性金属である。導電機能28Lおよび28Rは、導電領域29と同じかまたは異なった伝導性材料で構成することができる。

【0040】

導電機能28Lおよび28R並びに導電領域29を形成するのに使われる伝導性材料は、以下に限らないが、CVD、PECVD、スパッタリング、化学溶液堆積、またはメッキを含め、在来の堆積処理を用いて形成される。堆積の後、例えば化学機械研磨(CMP:chemical mechanical polishing)など、在来式の平坦化処理を使って平坦な相互接続構造体を得ることができる。

【0041】

パターン取りされたCu接合パッド30は、まず、導電機能28Lおよび28R並びに導電領域29の伝導性材料の形成に関して前述した技法の一つを用いて、相互接続レベル26の上にCuまたはCu合金のブランケット層を形成することによって、相互接続レベル26の上に形成される。次に、リソグラフィおよびエッチングを用いてパターン取りされたCu接合パッド30が形成される。図示のように、パターン取りされたCu接合パッド30の一つは、導電領域29の上面に接触している。この実施形態では、パターン取りされたCu接合パッド30が示され説明されているが、パターン取りなしCu接合パッドを用いる実施形態も後記で説明する。

【0042】

ここで図3を参照すると、第一デバイス・ウエハ10の該少なくともCu接合パッド30上に金属接着層32が形成された後の、図2の第一デバイス・ウエハ10が示されている。本実施形態において、金属接着層32は、例えば、蒸着、物理気相堆積、アルゴン・スパッタリング、化学気相堆積、プラズマ化学気相堆積、または原子層堆積などの非選択的堆積処理を用いて形成される。この「非選択的(“non−selective”)」とは、金属接着層32が全露出面に形成される堆積処理をいうものとする。

【0043】

金属接着層32は、CuまたはCu合金よりも酸素に対し高い親和力を有する金属または金属合金から成る。言い換えれば、金属接着層32は、CuまたはCu合金よりも酸素反応性の高い金属または金属合金から成る。具体的には、金属接着層32はMn、Ti、Co、Ta、W、Ru、およびNiの一つを含む。一つの実施形態において、金属接着層32は、Mn、またはTi、Co、Ta、W、Ni、およびRuの少なくとも一つと共に合金化されたMnを含む。別の実施形態では、金属接着層32は、Mn、Ti、Co、Ta、W、Ni、およびRuから選択された2つ以上を包含する金属合金を含む。

【0044】

金属接着層32の厚さは、用いられる金属または金属合金、および接着層を形成する際に使われた処理の条件の如何によって変わり得る。一つの実施形態において、金属接着層32は0.2nm〜20nmの厚さを有する。別の実施形態では、金属接着層32は0.5nm〜5nmの厚さを有する。いくつかの実施形態において、金属接着層32は単一層の材料である。別の実施形態では、金属接着層32は多層構造を含む。多層構造を用いる場合、多層構造体内の各金属接着材料は同じであってもまたは異なっていてもよい。

【0045】

ここで図4を参照すると、図3に示された第一デバイス・ウエハ10の上方に位置付けられた、パターン取りされたCu接合パッド72を含む第二デバイス・ウエハ50が示されている。第二デバイス・ウエハ50は、半導体デバイス層52Bおよび絶縁体層52Aを包含する半導体基板52を含む。半導体デバイス層52Bは、半導体基板12に関して前述した半導体材料の一つを含む。半導体デバイス層52Bの厚さは、通常、5nm〜5000nmの範囲内にある。本開示では、上記の厚さより上または下の他の厚さを用いることもできる。

【0046】

絶縁体層52Aは、半導体酸化物、半導体窒化物、もしくは半導体酸窒化物またはこれらの組み合わせを含む。絶縁体層52Aの厚さは、通常、5nm〜500nmの範囲内である。本開示では、上記の厚さより上または下の他の厚さを用いることもできる。

【0047】

一つの実施形態において、絶縁体層52Aおよび半導体デバイス層52Bは、基板の底部の半導体部分が、図4に示された第二デバイス・ウエハ50の作製の過程で除去された、半導体オン・インシュレータ基板のコンポーネントである。かかる実施形態において、基板の底部の半導体部分は、エッチングによって、または、例えばCMPもしくは研磨またはその両方などの平坦化処理を用いることによって除去することができる。半導体オン・インシュレータ基板の底部半導体部分の除去は、通常、第二デバイス・ウエハ50の上に取扱い基板(または取扱いウエハ)を形成した後で行われる。

【0048】

いくつかの実施形態において、絶縁体層52Aは、バルク半導体基板が処理され、少なくとも一つのデバイス、一つの相互接続レベル、および取扱い基板が含められた後、バルク半導体基板(これは半導体デバイス層52Bを表す)の底面上に形成される。

【0049】

半導体デバイス層52Bは、その中に形成された少なくとも一つの絶縁領域54を含む。この少なくとも一つの絶縁領域54を形成して、少なくとも一つの絶縁領域14に関して前述した材料をこれに含めることができる。

【0050】

第二デバイス・ウエハ50は、少なくとも部分的に半導体デバイス層52Bの上に形成された少なくとも一つの第二デバイス58をさらに含む。本実施形態において、少なくとも一つの第二デバイス58は、少なくともゲート誘電体60とゲート導体62とのゲート・スタックを含む電界効果トランジスタである。ゲート誘電体60およびゲート導体62を形成して、ゲート誘電体20およびゲート導体22に関して前述した材料および厚さを含めることができる。

【0051】

この電界効果トランジスタ(すなわち、少なくとも一つの第二デバイス58)は、半導体デバイス層52B内の、ゲート誘電体60とゲート導体62とを含むゲート・スタックのフットプリントに配置されたソース/ドレイン領域56Lおよび56Rをさらに含む。ソース/ドレイン領域56Lおよび56Rは、ソース/ドレイン領域16Lおよび16Rの形成に関して前述したようにして形成することができる。ゲート・スタック(60および62)の真下に所在し、ソース/ドレイン領域56L、56Rによって横方向に境界されている、半導体デバイス層52Bの領域は少なくとも一つの第二デバイス58のチャネル領域である。

【0052】

少なくとも一つのスペーサ63を、ゲート・スタック(すなわち、60および62)の側壁に配置することができる。少なくとも一つのスペーサ63は、少なくとも一つのスペーサ24に関して前述した材料の一つで構成できる。少なくとも一つのスペーサ63は、少なくとも一つのスペーサ24の形成に関して前述したのと同じ技法を使って形成することができる。

【0053】

第二デバイス・ウエハ50は、少なくとも一つの相互接続誘電体材料65内に配置された複数の導電機能66Lおよび66Rを包含する相互接続レベル64をさらに含む。相互接続誘電体材料65を形成して、相互接続誘電体材料27に関して前述した材料および厚さを含めることができる。導電機能66Lおよび66Rを形成して、導電機能28Lおよび28Rに関して前述した材料を含めることができる。

【0054】

少なくとも一つの第二デバイス58および相互接続レベル64を形成した後、相互接続レベル64の最上面に取扱い基板68が形成される。取扱い基板68は、ガラス、Al2O3、SiN、もしくは、例えば、カーボン、スピンオン有機/無機ポリマー、または軟質テープなど、他の容易に除去できる絶縁材料で構成することができる。取扱い基板68は、層転写処理を含め、当業者に周知の在来技法を用いて形成できる。

【0055】

次に、半導体オン・インシュレータの底部は、存在する場合、前述したように除去することができ、存在しなければ、次いで絶縁体層52Aを、熱成長または、例えば、CVD、PECVD、および化学溶液堆積などの堆積処理を用いて形成することができる。

【0056】

次に、スルー・ビア70は、半導体基板52を貫通し、相互接続誘電体材料65の少なくとも部分を貫通して形成することができる。スルー・ビア70の一つの端部は、導電機能すなわち66Rの少なくとも一つの水平面と接触しており、一方、別の端部は基板52の最底部の表面に配置される。

【0057】

スルー・ビア70は、導電機能28Lおよび28Rに関して前述した伝導性材料の一つを含み、該ビアは、リソグラフィおよびエッチングを用いて形成され、その後に、リソグラフィおよびエッチング処理によって生成されたビアの開口内に伝導性材料が形成される。スルー・ビア70の伝導性材料には、導電機能28Lおよび28Rに関して前述した伝導性材料の一つで構成することができる。スルー・ビア70の伝導性材料は、導電機能28Lおよび28Rに関して前述した技法の一つを使って形成できる。CMPなどの平坦化処理を使って平坦な構造体を得ることができる。

【0058】

スルー・ビア70を形成した後、絶縁体層52Aの表面上にCu接合パッド72が形成される。図示のようにCu接合パッド72の一つはスルー・ビア70の一端部と接触している。本開示のこの実施形態では、Cu接合パッド72はパターン取りされている。いくつかの実施形態では、パターン取りなしCu接合パッド(図示せず)を使うことができる。さらに、本開示の別の実施形態では、少なくともCu接合パッド72の表面上に別の金属接着層を形成することもできる。この実施形態は、本開示の図面中には示されていない。少なくともCu接合パッド72上に別の金属接着層が形成される場合、その別の金属接着層を形成して金属接着層32に関して前述したような材料を包含させることができる。この別の金属接着層は、金属接着層32の金属または金属合金と同一にすることも異ならせることもできるが、通常は同一である。

【0059】

図5を参照すると、2つのデバイス・ウエハ10と50とを相互に緊密に接触させ、2つのウエハを、各Cu接合パッド72のCu表面を各Cu接合パッド30のCu表面の上にほぼ垂直にそろえて整合し、次いで400℃未満の温度で接合した後の、図4の2つのデバイス・ウエハ10および50が示されている。別の実施形態では、この接合は50℃〜375℃の温度で行われる。

【0060】

いくつかの実施形態において、この接合処理の間、人の手、万力または他の類似の機械的手段により供される力など、外部の力をこの2つのデバイス・ウエハに加えることができる。別の実施形態では、接合処理の間、2つのデバイス・ウエハに外部の力は加えられない。

【0061】

この接合は、共に接合される2つのデバイス・ウエハの接合に対し不活性な環境で行うことができる。一つの実施形態において、この接合は、例えば、He、Ar、Ne、Xe、またはこれらの混合ガスを含め、不活性ガス中で行われる。別の実施形態では、接合処理の間の環境として窒素が使用可能である。窒素は単独で使うことも、前述の不活性ガスの一つと混合して使うこともできる。別の実施形態において、接合処理の間の環境として、フォーミング・ガス(すなわち、水素(モル分率は変わる)と窒素との混合ガス)を用いることができる。

【0062】

接合の過程で、Cu接合パッド上に位置する金属接着層32は、2つのCu表面から酸素原子を得て、Cu接合パッド30のCu表面とCu接合パッド72の別のCu表面との間に金属酸化物接合層74を形成する。これにより、接合後のCu接合パッド30およびCu接合パッド72は、接合が行われる前のCu接合パッドに比べて、その中により少ない酸素を有する。本開示において、用いられた金属接着層の種類および接合処理条件の如何により、Cu接合パッド30およびCu接合パッド72の各々で50〜99%の酸素の低減が達成可能である。

【0063】

しかして、金属酸化物接合層74は、金属または金属合金と酸素とを含む。金属酸化物接合層74は、Cu接合パッド30のCu表面とCu接合パッド72のCu表面との間に配置され、Cu接合パッド30およびCu接合パッド72のエッジに垂直に整合されて示されている。金属酸化物接合層74は、初期の金属接着層の厚さおよびCu接合パッドに元々包含されていた酸素の量の如何により、典型的には、0.3nm〜100nmの範囲の厚さを有し、1nm〜10nmの厚さであればさらに典型的である。本開示では、上記の厚さの範囲より大きい、または小さい他の厚さも用いることもできる。いくつかの実施形態において、金属酸化物接合層74は単一層構造である。別の実施形態では、金属酸化物接合層74は多層構造である。金属酸化物接合層74が多層構造の場合、多層構造の各層は、同じ組成または相異なる組成とすることができる。

【0064】

ここで図6を参照すると、第二デバイス・ウエハ50から取扱い基板68を除去した後の、図5の接合された2つのデバイス・ウエハが示されている。一つの実施形態において、取扱い基板68は、例えば、取扱い基板が炭化水素ベースの場合はO2プラズマなど、取扱い基板がSiNの場合は熱リン酸などの選択エッチング処理を用いて除去することができる。別の実施形態において、化学機械平坦化もしくは研磨またはその両方を使って、取扱い基板68を接合された構造体から除去することができる。

【0065】

図6に示された構造体の上にさらなるデバイス・ウエハを積み重ねることができ、前述した基本処理ステップを用いて、該さらなるデバイス・ウエハと接合構造体との間の接合を実現することができる。かくして、垂直に順に積み重ねられた複数のデバイス・ウエハを含む3D集積回路を形成することができる。

【0066】

ここで、本開示の別の実施形態を示している図7〜図11を参照する。図7〜図11に示されたこの実施形態は、パターン取りなしCu接合パッドが用いられることを除いて、上記図2〜図6に示された実施形態と類似である。

【0067】

まず、図7を参照すると、本開示の一つの実施形態において用いることの可能な、パターン取りなしCu接合パッド80を含む第一デバイス・ウエハ10が示されている。具体的には、第一デバイス・ウエハ10は、図2のパターン取りされたCu接合パッド30がパターン取りなしCu接合パッド80に置き換えられていることを除いて、図2に示された第一デバイス・ウエハ10と同じコンポーネントを含む。パターン取りなしCu接合パッド80は、パターン取りされたCu接合パッド30の形成に関して前述した堆積処理を用いて形成することができる。Cu接合パッドのブランケット層の堆積の後で、該ブランケットCu接合パッドのパターン取りは行われない。このパターン取りなしCu接合パッド80の材料および厚さは、パターン取りされたCu接合パッド30に関して前述したものと同じである。

【0068】

ここで図8を参照すると、第一デバイス・ウエハのパターン取りなしCu接合パッド80上に金属接着層82を形成した後の、図7の第一デバイス・ウエハが示されている。金属接着層82を形成して、金属接着層32に関して前述した材料および厚さを含めることができる。

【0069】

図9を参照すると、図8に示された第一デバイス・ウエハ10の上方に位置付けられた、別のパターン取りなしCu接合パッド84を含む第二デバイス・ウエハ50が示されている。第二デバイス・ウエハ50は、パターン取りされたCu接合パッド72がパターン取りなしCu接合パッド84に置き換えられていることを除いて、前述した(図4の)第二デバイス・ウエハ50と同じエレメントを含む。パターン取りなしCu接合パッド84は、パターン取りされたCu接合パッド30に関して前述した堆積処理を用いて形成される。Cu接合パッドのブランケット層の堆積の後で、該ブランケットCu接合パッドのパターン取りは行われない。このパターン取りなしCu接合パッド84の材料および厚さは、パターン取りされたCu接合パッド30に関して前述したものと同じである。

【0070】

ここで図10を参照すると、400℃未満の温度で接合された後の、図9の2つのデバイス・ウエハが示されている。図5に示された接合構造体の形成に関連して説明した接合処理における他の詳細および実施形態は、ここで図10に示された接合構造体の形成のためにも使うことができる。前述の実施形態と違って、金属酸化物接合層74は、パターン取りなしCu接合パッド80とパターン取りなしCu接合パッド84との間に切れ目なく存在している。前述の実施形態と同様に、接合の後のパターン取りなしCu接合パッド80およびパターン取りなしCu接合パッド84は、接合の前のパターン取りなしCu接合パッド80およびパターン取りなしCu接合パッド84と比べて、その中により少ない酸素を有する。

【0071】

ここで図11を参照すると、第二デバイス・ウエハ50から取扱い基板68を除去した後の、図10の2つの接合されたデバイス・ウエハが示されている。取扱い基板68を除去するための詳細は、本開示の前述の実施形態で述べたものと同じである。

【0072】

図11に示された接合構造体の上にさらなるデバイス・ウエハを積み重ねることができ、前述した基本処理ステップを用いて、該さらなるデバイス・ウエハと接合構造体との間の接合を実現することができる。かくして、垂直に順に積み重ねられた複数のデバイス・ウエハを含む3D集積回路を形成することができる。

【0073】

ここで図12〜図15を参照すると、本開示の別の実施形態が示されている。本開示のこの実施形態は、まず、第一デバイス・ウエハ10および第二デバイス・ウエハ10’を用意することから開始される。第一デバイス・ウエハ10のコンポーネントは、図2に示された第一デバイス・ウエハ10中に存在するものと類似である。第二デバイス・ウエハ10’のコンポーネントも、図2に示された第一デバイス・ウエハ10に関して前述したものと同じである。第二デバイス・ウエハ10’のコンポーネントを識別するために主な指定(prime designation)が用いられるが、それでもなお、第一デバイス・ウエハ10のコンポーネントと同等である。

【0074】

ここで図13を参照すると、少なくとも一つのデバイス・ウエハのパターン取りされたCu接合パッドの上に少なくとも一つの金属接着層32が形成された後の、図12の2つのデバイス・ウエハ10および10’が示されている。いくつかの実施形態では、別の金属接着層32を両方のデバイス・ウエハに形成することができる。この少なくとも一つの金属接着層32は、図3に示された構造体に関連して前述したものと同じである。

【0075】

ここで図14を参照すると、デバイス・ウエハの一つ(すなわち、デバイス・ウエハ10’)を反転し、第一デバイス・ウエハ10のパターン取りされたCu接合パッド30を第二デバイス・ウエハ10’のパターン取りされたCu接合パッド30’に整合した後の、図13の2つのデバイス・ウエハ10および10’が示されている。この反転は、デバイス・ウエハの一つ、すなわち第二デバイス・ウエハ10’を180°回転させることによって実現される。

【0076】

図15を参照すると、400℃未満の温度で接合した後の、図14の2つのデバイス・ウエハ10および10’が示されている。図5に示された接合構造体の形成に関連して説明した接合処理の他の詳細および実施形態は、ここで図15に示された接合構造体の形成のためにも使うことができる。

【0077】

図15に示された接合構造体の上にさらなるデバイス・ウエハを積み重ねることができ、前述した基本処理ステップを用いて、該さらなるデバイス・ウエハと接合構造体との間の接合を実現することができる。かくして、垂直に順に積み重ねられた複数のデバイス・ウエハを含む3D集積回路を形成することができる。

【0078】

ここで図16を参照すると、金属接着層を形成するのに選択的堆積処理が使われていることを除き、図2〜図6に示された基本的処理ステップを使って形成できる3D集積回路が示されている。これにおいては、金属接着層は、第一および第二デバイス・ウエハのいずれの相互接続誘電体材料にも接触することはない。選択的堆積は、Cu/誘電体パターンの未処理の表面上または改修された表面上への化学気相堆積、または原子層堆積によって実現することができる。典型的な例は、化学気相堆積処理によるMnまたはCoの選択的堆積である。

【0079】

ここで図17を参照すると、金属接着層を形成するのに選択的堆積処理が使われていることを除き、図12〜図15に示された基本的処理ステップを使って加工できる3D集積回路が示されている。これにおいては、金属接着層は、第一および第二デバイス・ウエハのいずれの相互接続誘電体材料にも接触することはない。選択的堆積は、Cu/誘電体パターンの未処理の表面上または改修された表面上への化学気相堆積、または原子層堆積によって実現することができる。典型的な例は、化学気相堆積処理によるMnまたはCoの選択的堆積である。

【0080】

本開示のいくつかの実施形態において、上記の処理ステップを使って、一つのデバイス・ウエハのパターン取りなしのCu接合パッドを、別のデバイス・ウエハの少なくとも一つのパターン取りされたCu接合パッドに接合することができる。

【0081】

本開示を、その好適な実施形態に関連させて具体的に示し説明してきたが、当然のことながら、当業者は本開示の精神および範囲から逸脱することなく、形態および詳細における前述のまたは他の変更を加えることが可能である。従って、本開示は、説明され提示された通りの形態および詳細に限定されるものでなく、添付の請求項の範囲に含まれることが意図されている。

【符号の説明】

【0082】

12 半導体基板

14 絶縁領域

16L ソース/ドレイン領域

16R ソース/ドレイン領域

20 ゲート誘電体

22 ゲート導体

24 スペーサ

26 相互接続レベル

27 相互接続誘電体材料

28L 導電機能

28R 導電機能

29 ビア

30 パターン取りされたCu接合パッド

32 金属接着層

52 半導体基板

52A 絶縁体層

52B 半導体デバイス層

54 絶縁領域

56L ソース/ドレイン領域

56R ソース/ドレイン領域

60 ゲート誘電体

62 ゲート導体

63 スペーサ

64 相互接続レベル

65 相互接続誘電体材料

66L 導電機能

66R 導電機能

70 スルー・ビア

72 Cu接合パッド

74 金属酸化物接合層

【特許請求の範囲】

【請求項1】

三次元(3D)集積回路を形成する方法であって、前記方法は、

Cu表面を含む第一デバイス・ウエハを用意するステップと、

前記第一デバイス・ウエハの少なくとも前記Cu表面上に金属接着層を形成するステップと、

別のCu表面を含む第二デバイス・ウエハを、前記第一デバイス・ウエハの前記金属接着層上で且つ前記Cu表面の上に位置付けるステップと、

前記第一および第二デバイス・ウエハを400℃未満の温度で共に接合するステップと、

を含み、

前記金属接着層は、前記の2つのCu表面から酸素原子を得て、前記第一デバイス・ウエハの前記Cu表面と前記第二デバイス・ウエハの前記別のCu表面との間に金属酸化物接合層を形成する、

前記方法。

【請求項2】

前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はCu接合パッドであり、各Cu接合パッドはパターン取りされている、請求項1に記載の方法。

【請求項3】

前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はCu接合パッドであり、各Cu接合パッドはパターン取りされていない、請求項1に記載の方法。

【請求項4】

前記金属接着層を前記形成するステップは、非選択的堆積処理を含む、請求項1に記載の方法。

【請求項5】

前記金属接着層を前記形成するステップは、選択的堆積処理を含む、請求項1に記載の方法。

【請求項6】

前記金属接着層を前記形成するステップは、Mn、Ta、Ti、Co、W、Ru、Ni、またはMn、Ta、Ti、Co、W、Ru、およびNiから選択された2つ以上の金属の組み合わせを含む合金、の少なくとも一つを選択するステップを含む、請求項1に記載の方法。

【請求項7】

前記金属酸化物接合層は、前記各Cu接合パッドの側壁と垂直的に一致する、請求項2に記載の方法。

【請求項8】

前記第一デバイス・ウエハは電界効果トランジスタを含み、前記第二デバイス・ウエハは別の電界効果トランジスタを含む、請求項1に記載の方法。

【請求項9】

前記少なくとも一つのCu表面は、相互接続レベルの最上面の上に配置され、前記相互接続レベルは、複数の導電機能が中に配置されている少なくとも一つの相互接続誘電体材料を含み、前記導電機能の少なくとも一つは、前記第一デバイス・ウエハの前記Cu表面の最底部と接触している、請求項1に記載の方法。

【請求項10】

接合ステップの前に、前記デバイス・ウエハの少なくとも一つを反転するステップをさらに含む、請求項1に記載の方法。

【請求項11】

前記金属接着層の一部が、前記デバイス・ウエハの少なくとも一つの上に残存する、請求項1に記載の方法。

【請求項12】

前記金属接着層が多層構造体を含み、前記金属酸化物接合層が多層構造体を含む、請求項1に記載の方法。

【請求項13】

Cu表面を含む第一デバイス・ウエハと、別のCu表面を含む第二デバイス・ウエハとの垂直スタックであって、金属酸化物接合層が、前記第一デバイス・ウエハの前記Cu表面と前記第二デバイス・ウエハの前記別のCu表面との間に配置される、前記垂直スタック、

を含む三次元(3D)集積回路。

【請求項14】

前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はCu接合パッドであり、各Cu接合パッドはパターン取りされている、請求項13に記載の3D集積回路。

【請求項15】

前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はCu接合パッドであり、各Cu接合パッドはパターン取りされていない、請求項13に記載の3D集積回路。

【請求項16】

前記金属酸化物接合層は、前記Cu接合パッドの各々の側壁と垂直的に一致する、請求項13に記載の3D集積回路。

【請求項17】

金属接着層の一部が、前記デバイス・ウエハの少なくとも一つの上に残存する、請求項13に記載の3D集積回路。

【請求項18】

前記金属接着層は、Mn、Ti、Ta、Co、W、Ru、およびNi、またはMn、Ta、Ti、Co、W、Ru、およびNiから選択された2つ以上の金属の組み合わせを含む合金、の一つを含む、請求項17に記載の3D集積回路。

【請求項19】

前記金属酸化物接合層は、Mn、Ti、Ta、Co、W、Ru、およびNi、またはMn、Ta、Ti、Co、W、Ru、およびNiから選択された2つ以上の金属の組み合わせを含む合金、の少なくとも一つの酸化物を含む、請求項13に記載の3D集積回路。

【請求項20】

前記第一デバイス・ウエハは電界効果トランジスタを含み、前記第二デバイス・ウエハは別の電界効果トランジスタを含む、請求項13に記載の3D集積回路。

【請求項21】

少なくとも一つのCu表面は、相互接続レベルの最上面の上に配置され、前記相互接続レベルは、複数の導電機能が中に配置されている少なくとも一つの相互接続誘電体材料を含み、前記導電機能の少なくとも一つは、前記第一デバイス・ウエハの前記Cu表面の最底部と接触している、請求項13に記載の3D集積回路。

【請求項22】

前記第一デバイス・ウエハは、少なくとも一つのデバイスが中に少なくとも部分的に配置されている半導体基板と、前記半導体基板の上に配置された相互接続レベルとを含み、前記相互接続レベルは、少なくとも一つの相互接続誘電体材料内に内蔵された複数の導電機能を含み、導電領域が前記複数の導電機能の一つを前記Cu表面に接続している、請求項13に記載の3D集積回路。

【請求項23】

前記第二デバイス・ウエハは、底部から最上部に向けて、絶縁体層と、半導体デバイス層と、前記半導体デバイス層に少なくとも部分的に配置された少なくとも一つ他のデバイスと、別の相互接続レベルとを含み、前記別の相互接続レベルは、少なくとも一つの他の相互接続誘電体材料内に内蔵された複数の他の導電機能を含み、スルー・ビアが、前記他の導電機能の少なくとも一つを前記別のCu表面の最底部に接続しており、前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はパターン取りされたCu接合パッドである、請求項22に記載の3D集積回路。

【請求項24】

前記第二デバイス・ウエハは、少なくとも一つの他のデバイスが中に少なくとも部分的に配置されている別の半導体基板と、前記別の半導体基板の上に配置された別の相互接続レベルとを含み、前記別の相互接続レベルは、少なくとも一つの他の相互接続誘電体材料内に内蔵された複数の他の導電機能を含み、前記別の半導体基板は前記少なくとも一つの他のデバイスの上に配置され、前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はパターン取りされたCu接合パッドである、請求項22に記載の3D集積回路。

【請求項25】

前記金属接着層が多層構造体であり、前記金属酸化物接合層が多層構造体である、請求項17に記載の3D集積回路。

【請求項1】

三次元(3D)集積回路を形成する方法であって、前記方法は、

Cu表面を含む第一デバイス・ウエハを用意するステップと、

前記第一デバイス・ウエハの少なくとも前記Cu表面上に金属接着層を形成するステップと、

別のCu表面を含む第二デバイス・ウエハを、前記第一デバイス・ウエハの前記金属接着層上で且つ前記Cu表面の上に位置付けるステップと、

前記第一および第二デバイス・ウエハを400℃未満の温度で共に接合するステップと、

を含み、

前記金属接着層は、前記の2つのCu表面から酸素原子を得て、前記第一デバイス・ウエハの前記Cu表面と前記第二デバイス・ウエハの前記別のCu表面との間に金属酸化物接合層を形成する、

前記方法。

【請求項2】

前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はCu接合パッドであり、各Cu接合パッドはパターン取りされている、請求項1に記載の方法。

【請求項3】

前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はCu接合パッドであり、各Cu接合パッドはパターン取りされていない、請求項1に記載の方法。

【請求項4】

前記金属接着層を前記形成するステップは、非選択的堆積処理を含む、請求項1に記載の方法。

【請求項5】

前記金属接着層を前記形成するステップは、選択的堆積処理を含む、請求項1に記載の方法。

【請求項6】

前記金属接着層を前記形成するステップは、Mn、Ta、Ti、Co、W、Ru、Ni、またはMn、Ta、Ti、Co、W、Ru、およびNiから選択された2つ以上の金属の組み合わせを含む合金、の少なくとも一つを選択するステップを含む、請求項1に記載の方法。

【請求項7】

前記金属酸化物接合層は、前記各Cu接合パッドの側壁と垂直的に一致する、請求項2に記載の方法。

【請求項8】

前記第一デバイス・ウエハは電界効果トランジスタを含み、前記第二デバイス・ウエハは別の電界効果トランジスタを含む、請求項1に記載の方法。

【請求項9】

前記少なくとも一つのCu表面は、相互接続レベルの最上面の上に配置され、前記相互接続レベルは、複数の導電機能が中に配置されている少なくとも一つの相互接続誘電体材料を含み、前記導電機能の少なくとも一つは、前記第一デバイス・ウエハの前記Cu表面の最底部と接触している、請求項1に記載の方法。

【請求項10】

接合ステップの前に、前記デバイス・ウエハの少なくとも一つを反転するステップをさらに含む、請求項1に記載の方法。

【請求項11】

前記金属接着層の一部が、前記デバイス・ウエハの少なくとも一つの上に残存する、請求項1に記載の方法。

【請求項12】

前記金属接着層が多層構造体を含み、前記金属酸化物接合層が多層構造体を含む、請求項1に記載の方法。

【請求項13】

Cu表面を含む第一デバイス・ウエハと、別のCu表面を含む第二デバイス・ウエハとの垂直スタックであって、金属酸化物接合層が、前記第一デバイス・ウエハの前記Cu表面と前記第二デバイス・ウエハの前記別のCu表面との間に配置される、前記垂直スタック、

を含む三次元(3D)集積回路。

【請求項14】

前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はCu接合パッドであり、各Cu接合パッドはパターン取りされている、請求項13に記載の3D集積回路。

【請求項15】

前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はCu接合パッドであり、各Cu接合パッドはパターン取りされていない、請求項13に記載の3D集積回路。

【請求項16】

前記金属酸化物接合層は、前記Cu接合パッドの各々の側壁と垂直的に一致する、請求項13に記載の3D集積回路。

【請求項17】

金属接着層の一部が、前記デバイス・ウエハの少なくとも一つの上に残存する、請求項13に記載の3D集積回路。

【請求項18】

前記金属接着層は、Mn、Ti、Ta、Co、W、Ru、およびNi、またはMn、Ta、Ti、Co、W、Ru、およびNiから選択された2つ以上の金属の組み合わせを含む合金、の一つを含む、請求項17に記載の3D集積回路。

【請求項19】

前記金属酸化物接合層は、Mn、Ti、Ta、Co、W、Ru、およびNi、またはMn、Ta、Ti、Co、W、Ru、およびNiから選択された2つ以上の金属の組み合わせを含む合金、の少なくとも一つの酸化物を含む、請求項13に記載の3D集積回路。

【請求項20】

前記第一デバイス・ウエハは電界効果トランジスタを含み、前記第二デバイス・ウエハは別の電界効果トランジスタを含む、請求項13に記載の3D集積回路。

【請求項21】

少なくとも一つのCu表面は、相互接続レベルの最上面の上に配置され、前記相互接続レベルは、複数の導電機能が中に配置されている少なくとも一つの相互接続誘電体材料を含み、前記導電機能の少なくとも一つは、前記第一デバイス・ウエハの前記Cu表面の最底部と接触している、請求項13に記載の3D集積回路。

【請求項22】

前記第一デバイス・ウエハは、少なくとも一つのデバイスが中に少なくとも部分的に配置されている半導体基板と、前記半導体基板の上に配置された相互接続レベルとを含み、前記相互接続レベルは、少なくとも一つの相互接続誘電体材料内に内蔵された複数の導電機能を含み、導電領域が前記複数の導電機能の一つを前記Cu表面に接続している、請求項13に記載の3D集積回路。

【請求項23】

前記第二デバイス・ウエハは、底部から最上部に向けて、絶縁体層と、半導体デバイス層と、前記半導体デバイス層に少なくとも部分的に配置された少なくとも一つ他のデバイスと、別の相互接続レベルとを含み、前記別の相互接続レベルは、少なくとも一つの他の相互接続誘電体材料内に内蔵された複数の他の導電機能を含み、スルー・ビアが、前記他の導電機能の少なくとも一つを前記別のCu表面の最底部に接続しており、前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はパターン取りされたCu接合パッドである、請求項22に記載の3D集積回路。

【請求項24】

前記第二デバイス・ウエハは、少なくとも一つの他のデバイスが中に少なくとも部分的に配置されている別の半導体基板と、前記別の半導体基板の上に配置された別の相互接続レベルとを含み、前記別の相互接続レベルは、少なくとも一つの他の相互接続誘電体材料内に内蔵された複数の他の導電機能を含み、前記別の半導体基板は前記少なくとも一つの他のデバイスの上に配置され、前記第一デバイス・ウエハの前記Cu表面および前記第二デバイス・ウエハの前記別のCu表面はパターン取りされたCu接合パッドである、請求項22に記載の3D集積回路。

【請求項25】

前記金属接着層が多層構造体であり、前記金属酸化物接合層が多層構造体である、請求項17に記載の3D集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−98541(P2013−98541A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2012−197293(P2012−197293)

【出願日】平成24年9月7日(2012.9.7)

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成24年9月7日(2012.9.7)

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

[ Back to top ]