強磁性積層構造及びその製造方法

【課題】良好な界面特性をもつ強磁性薄膜、絶縁性薄膜、及び化合物半導体からなる強磁性積層構造を得る。

【解決手段】この磁性体積層構造10においては、化合物半導体1上に絶縁性薄膜2及び強磁性薄膜3が順次形成されている。絶縁性薄膜2は、蛍石型構造をもつフッ化化合物からなる。強磁性薄膜3は、Fe又はFeCo合金からなる強磁性体である。この強磁性積層構造10は、強磁性薄膜3から絶縁性薄膜2を通して化合物半導体1にスピン偏極電子が注入されて使用される。例えば、この強磁性積層構造10をスピンLEDに用い、化合物半導体1を発光層としても用いることができる。この場合には、この構造における各界面の結晶欠陥が少ないために、スピン偏極電子の発光層への高い注入効率が得られるため、高効率のスピンLEDを得ることができる。

【解決手段】この磁性体積層構造10においては、化合物半導体1上に絶縁性薄膜2及び強磁性薄膜3が順次形成されている。絶縁性薄膜2は、蛍石型構造をもつフッ化化合物からなる。強磁性薄膜3は、Fe又はFeCo合金からなる強磁性体である。この強磁性積層構造10は、強磁性薄膜3から絶縁性薄膜2を通して化合物半導体1にスピン偏極電子が注入されて使用される。例えば、この強磁性積層構造10をスピンLEDに用い、化合物半導体1を発光層としても用いることができる。この場合には、この構造における各界面の結晶欠陥が少ないために、スピン偏極電子の発光層への高い注入効率が得られるため、高効率のスピンLEDを得ることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、強磁性薄膜、絶縁性薄膜、及び化合物半導体からなり、スピンエレクトロニクスデバイスに用いられる強磁性積層構造及びその製造方法に関する。

【背景技術】

【0002】

近年、強磁性体におけるスピンの機能と、電気伝導における電子の機能を共に利用したスピンエレクトロニクスデバイスの研究開発が盛んに行われている。こうしたデバイスの例として、例えばハードディスクドライブにおける磁気ヘッドやMRAM(Magnetic Random Access Memory)がある。

【0003】

例えば、MgO(100)単結晶基板上にFe(100)薄膜とMgO(100)薄膜とFe(100)薄膜が順次形成された単結晶積層構造(以下、Fe/MgO/Feと呼称)では、強磁性体であるFe中のスピン方向に依存してMgO薄膜中を流れるトンネル電流が大きく変化する、いわゆる巨大トンネル磁気抵抗効果が生ずることが非特許文献1及び2に記載されている。特にこの構造においては、各層は単結晶であるため、Fe/MgO薄膜界面及びMgO薄膜/Fe界面の状態が巨大トンネル磁気抵抗効果に大きな影響を与える。つまり、巨大トンネル磁気抵抗効果を発現するためには、界面における格子のミスマッチを小さくして結晶欠陥を少なくし、Feのハーフメタリックな電子軌道を充分に機能させることが必要となる。

【0004】

また、強磁性薄膜、絶縁性薄膜、及び半導体からなる強磁性積層構造を用いたデバイスも提案されている。例えば、非特許文献3では、CoFe/MgO/GaAsの積層構造を用い、化合物半導体であるGaAsへ強磁性体であるCoFeからスピン偏極した電子を注入し、この電子を正孔と再結合させることにより、円偏光の光を発光するスピンLEDが提案されている。このデバイスにおいては、MgO/GaAs界面におけるスピン偏極した電子の注入効率が高いことが必要になる。非特許文献3にて報告されている注入効率は32%であり、まだ改善の余地があるため、更にこの効率を高めることが期待されている。この注入効率を高くするためには、スピン偏極された電子がこの界面で散乱される確率を減少させることが必要である。このためには、やはりその界面の結晶欠陥を減少させることが必要であり、特にこの界面の格子のミスマッチを低減させることが必要になる。

【0005】

従って、スピンエレクトロニクスデバイスにおいて用いられる強磁性積層構造においては、界面における格子のミスマッチを低減させることが、デバイスの特性を向上させる上で重要となる。

【0006】

一方、CaF2はGaAsの良好なパッシベーション膜となることが非特許文献4に記載されている。従って、例えば上記のMgOの代わりに、CaF2を絶縁性薄膜として用いることにより、良好な絶縁性薄膜/GaAs界面の形成が期待される。

【0007】

【非特許文献1】Japanese Journal of Applied Physics 43、L588(2004)

【非特許文献2】Physical Review B、63、054416(2001)

【非特許文献3】Physical Review Letters、94、056601(2005)

【非特許文献4】Applied Surface Science、 117/118、p443〜p446(1997)

【発明の開示】

【発明が解決しようとする課題】

【0008】

前記の強磁性薄膜、絶縁性薄膜、及び半導体からなる積層構造を用いたデバイスにおいて、上記のFe/MgO/GaAs積層構造の場合、通常は基板となるGaAsの結晶面としては(100)面が用いられる。この場合には、エピタキシャル成長により、この上に(100)面配向したMgO及び(100)面配向したFeが得られる。この際、Fe/MgO界面においては、Feの(100)面における[110]方向とMgOの(100)面における[100]方向が平行となる。この界面における格子のミスマッチは−3.8%程度であるため、良好である。しかしながら、MgO/GaAs界面においては、MgOの(100)面における[100]方向とGaAsの(100)面における[100]方向が平行になる。この界面における格子のミスマッチは−25.4%と前記の場合と比べて大きい。従って、この構造においては、MgO/GaAs界面の結晶欠陥が多いため、スピン偏極電子の高い注入効率を得ることはできなかった。

【0009】

一方、CaF2/GaAs界面においては、前記の通り、良好な界面を形成できると期待される。しかしながら、この場合には、GaAs上のCaF2上に更にFeを成長させ、これらの結晶面方位を制御して良好な界面特性を得る方法は知られていない。従って、この構造をもち、良好な界面特性をもつ強磁性積層構造は得られていなかった。

【0010】

従って、良好な界面特性をもつ強磁性薄膜、絶縁性薄膜、及び化合物半導体からなる強磁性積層構造を得ることは困難であった。

【0011】

本発明は、斯かる問題点に鑑みてなされたものであり、上記問題点を解決する発明を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、上記課題を解決すべく、以下に掲げる構成とした。

本発明の強磁性積層構造は、化合物半導体、絶縁性薄膜、及び強磁性薄膜が順次積層された強磁性積層構造であって、前記化合物半導体はGaAs、InAs、またはこれらの混晶であり、前記絶縁性薄膜は蛍石型構造のフッ化化合物からなり、前記強磁性薄膜はFeまたはFeCo合金からなることを特徴とする。

また、この強磁性積層構造は、前記強磁性薄膜から前記絶縁性薄膜を通して前記化合物半導体にスピン偏極電子が注入されて使用されることを特徴とする。

また、この強磁性積層構造において、前記フッ化化合物はCaF2、SrF2のいずれかあるいはこれらの混合物であることを特徴とする。

また、この強磁性積層構造は、前記化合物半導体の(100)面上に前記絶縁性薄膜及び前記強磁性薄膜が順次積層されたことを特徴とする。

また、この強磁性積層構造において、前記絶縁性薄膜の厚さが0.8〜5.0nmの範囲であることを特徴とする。

本発明の強磁性積層構造の製造方法は、前記強磁性積層構造を製造する製造方法であって、前記化合物半導体上に真空中で前記絶縁性薄膜及び前記強磁性薄膜を連続して形成し、前記強磁性薄膜を形成する際の基板温度を400℃以上とすることを特徴とする。

また、この強磁性積層構造の製造方法において、前記絶縁性薄膜及び前記強磁性薄膜の形成は、スパッタリング法によって行うことを特徴とする。

また、この強磁性積層構造の製造方法において、前記絶縁性薄膜及び前記強磁性薄膜の形成は、電子ビーム蒸着法によって行うことを特徴とする。

【発明の効果】

【0013】

本発明は以上のように構成されているので、良好な界面特性をもつ強磁性薄膜、絶縁性薄膜、及び化合物半導体からなる強磁性積層構造を得ることができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明について具体的な実施形態を示しながら説明する。ただし、本発明はこれらの実施形態に限定されるものではない。

【0015】

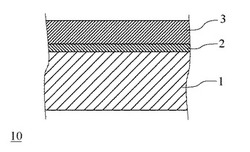

図1は本発明の実施の形態に係る強磁性積層構造10の断面図である。この強磁性積層構造10においては、化合物半導体1上に絶縁性薄膜2及び強磁性薄膜3が順次形成されている。この強磁性積層構造10は、強磁性薄膜3から絶縁性薄膜2を通して化合物半導体1にスピン偏極電子が注入されて使用される。例えば、この強磁性積層構造10をスピンLEDに用い、化合物半導体1を発光層としても用いることができる。この場合には、この構造における各界面の結晶欠陥が少ないために、スピン偏極電子の発光層への高い注入効率が得られるため、高効率のスピンLEDを得ることができる。なお、スピンLED以外にも、化合物半導体1においてこのスピン偏極電子を利用する各種のデバイス、例えば、スピンFETや逆スピンホール効果(スピン流誘起スピンホール効果)を用いる磁気センサーなどにおいても同様に、この強磁性積層構造10を用いることができることは明らかである。

【0016】

ここで、化合物半導体1は、GaAs又はInAs単結晶からなる(100)基板であり、絶縁性薄膜2はこれらの(100)面上に形成される。なお、化合物半導体1の厚さは任意である。なお、これらはエピタキシャル成長した基板、バルク半導体基板のいずれであってもよい。また、GaAsとInAsの混晶を同様に化合物半導体1として用いてもよい。

【0017】

絶縁性薄膜2は、蛍石型構造をもつフッ化化合物からなる。具体的には、蛍石型構造をもつCaF2又はSrF2が好ましい。その成膜法としては、一般的に薄膜形成に用いられるスパッタリング法、電子ビーム蒸着法、抵抗加熱蒸着法、分子線エピタキシー法(MBE法)等を用いることができる。この絶縁性薄膜2は化合物半導体1上にエピタキシャル成長し、その結晶配向面は化合物半導体1と同様に(100)面となる。その厚さは例えば0.8nm〜20nmとすることができるが、特に5nm以下であることが、強磁性薄膜3の結晶配向性を向上させる上で好ましい。なお、この絶縁性薄膜2をCaF2、SrF2のどちらにするかは、化合物半導体1の種類(GaAs、InAs、及びこれらの混晶)に応じて、界面の格子のミスマッチを小さくするべく選択することができる。

【0018】

強磁性薄膜3は、Fe又はFeCo合金からなる強磁性体である。その厚さは例えば50nmとすることができる。その成膜法としては、絶縁性薄膜2と同様にスパッタリング法、電子ビーム蒸着法、抵抗加熱蒸着法、MBE法を用いることができる。特に、強磁性薄膜3の成膜においては、絶縁性薄膜2を成膜した直後に真空中で連続して成膜することが好ましい(なお、ここでいう真空とは上記成膜法における真空度での雰囲気を意味する)。また、その成膜温度は400℃以上とすることが、強磁性薄膜3をエピタキシャル成長させる上で好ましい。

【0019】

以下に、この構造が好ましい理由につき説明する。まず、非特許文献3に記載のMgO/GaAs積層構造において、MgOの(100)面における[110]方位とGaAsの(100)面における[100]方位とが一致した場合には、格子のミスマッチは5.5%程度と小さくなる。すなわち、MgOの(100)面とGaAsの(100)面の間ではミスマッチの小さい接合界面が得られるとも考えられる。しかしながら、実際にはミスマッチの小さい接合界面は得られていない。

【0020】

これは、GaAsの(100)面には極性があることに起因する。すなわち、III−V属化合物半導体であるGaAsの(100)面は、III属元素(Ga)のみ、あるいはV属元素(As)のみからなる。これに対して、MgOの(100)面においては、その結晶構造が異なるため、陽イオン(Mgイオン)と陰イオン(Oイオン)とが混在する。従って、MgOの(100)面がGaAsの(100)面上に積層された場合には、電荷の補償ができないため、実際にはこれらが整合した構造は形成されにくい。従って、実際にMgOをGaAsの(100)面上に成長させた場合には、MgOの(100)面における[100]方位とGaAsの(100)面における[100]方位とが平行となった構造として形成される。この場合の格子のミスマッチは前記の通り、−25.4%と大きな値となる。従って、この界面には多くの結晶欠陥が発生する。

【0021】

これに対して、本発明における絶縁性薄膜2となる蛍石型構造のフッ化化合物においては、その(100)面はGaAsと同様に、単一元素から構成される。従って、格子定数が化合物半導体1と合致すれば、絶縁性薄膜2の(100)面を化合物半導体1の(100)面上に格子のミスマッチが小さくなる方位で成長させることができる。すなわち、絶縁性薄膜2/化合物半導体1の界面の結晶欠陥を少なくすることができる。

【0022】

更に、この構造の絶縁性薄膜2上には、Fe又はFeCoからなる強磁性薄膜3をエピタキシャル成長させることができる。従って、強磁性薄膜3/絶縁性薄膜2界面における結晶欠陥も少なくすることができる。これは、特に強磁性薄膜3の成膜時の基板温度を400℃以上とした場合に顕著となる。また、絶縁性薄膜2の厚さを5nm以下と薄くした場合には、特に強磁性薄膜3のロッキングカーブ半値幅を小さくすることができるため、特に結晶配向性の良好な、結晶欠陥の少ない強磁性積層構造となる。絶縁性薄膜2の厚さが薄い方が好ましい特性が得られることは、特に絶縁性薄膜2をトンネル絶縁膜として使用する上では好ましい。

【0023】

従って、図1の構造の強磁性積層構造においては、絶縁性薄膜2/化合物半導体1、強磁性薄膜3/絶縁性薄膜2のどちらの界面における結晶欠陥も少なくすることができ、良好な界面特性が得られる。従って、強磁性薄膜3から注入されるスピン偏極電子の界面における散乱を抑制することができ、高い電子注入効率をもった強磁性積層構造となる。これを用いて、例えば高効率のスピンLED等、各種のスピントロニクスデバイスを得ることができる。

【0024】

(実施例1)

本発明の実施例(実施例1)として、化合物半導体1としてGaAsの(100)単結晶基板、絶縁性薄膜2として蛍石構造のSrF2、強磁性薄膜3としてFeを用いた強磁性積層構造10(Fe/SrF2/GaAs構造)を製造し、その特性を調べた。

【0025】

まず、GaAs(100)基板をアセトンとイソプロピルアルコールで洗浄後、表面の酸化膜をフッ酸を用いて除去した。その後、このGaAs基板上にスパッタリング法によって厚さ20nmのSrF2層、及び厚さ50nmのFe層を連続して形成した。SrF2層を形成する際には、SrF2ターゲットを用い、基板温度400℃、Arガス圧0.5Paでスパッタリングを行った。Fe層を形成する際には、Feターゲットを用い、基板温度400℃、Arガス圧0.2Paでスパッタリングを行った。なお、この実施例1とは別に、参考のためにSrF2層のみを形成し、Fe層を形成しない試料も作成した。

【0026】

図2は、これらの試料のX線回折(out−of−plane)パターンを測定した結果であり、各ピークには対応する各物質の面方位が記してある。ここで、試料Aは前記のFe層を形成しなかった試料であり、試料Bが実施例1となる、Fe層まで形成した試料である。すなわち、試料AにおいてはSrF2層の結果が強く現れており、試料Bにおいては、Fe層の結果が強く現れている。

【0027】

図2における試料Aの結果より、SrF2層が蛍石型構造の(200)方向に配向し、試料Bの結果から、Fe層も(200)配向していることが確認できる。

【0028】

更に、試料Bについて、X線回折のin−plane測定を行った結果を図3に示す。図3において、(a)はGaAsの(022)面、(b)はSrF2の(022)面、(c)はFeの(002)面に対するそれぞれの極図形である。どの極図形も明確な4回対称性を示していることから、SrF2層及びFe層は、それぞれエピタキシャル成長膜である。

【0029】

また、(a)のGaAsの(022)回折ピークと(b)のSrF2の(022)回折ピークの角度差とブラッグ角の差から求まるそれぞれの面のなす角はほぼ零となることから、GaAsの(022)面とSrF2の(022)面はほぼ平行であることがわかる。すなわち、SrF2/GaAs界面においては、SrF2の(100)面における[100]方向とGaAsの(100)面における[100]方向とが平行に配列されている。

【0030】

また、(b)のSrF2の(022)回折ピークと(c)のFeの(002)回折ピークの角度差とブラッグ角の差から求まるそれぞれの面のなす角はほぼ45°となる。従って、Fe/SrF2界面における面内方向の原子配列は、Feの(100)面における[100]方向とSrF2の(100)面における[100]方向とが平行に配列されている。

【0031】

次に、これらの界面での格子のミスマッチを試料AとBのin−planeの対称測定を行うことにより調べた。その結果が図4である。この結果におけるピーク間距離がこのミスマッチに対応する。この結果より、試料AにおけるSrF2とGaAs間のミスマッチは2.4%と小さな値となっている。また、試料BにおけるFeのピークから、FeとSrF2間のミスマッチは−0.9%と極めて小さくなっている。

【0032】

従って、実施例1においては、化合物半導体1であるGaAs上に絶縁性薄膜2である蛍石型構造のSrF2、さらにその上に強磁性薄膜3であるFeがそれぞれエピタキシャル成長しており、これらの界面における格子ミスマッチが小さな値であることが確認できる。すなわち、上記の通り、この構造によって界面の結晶欠陥が少ない強磁性積層構造が実現できている。

【0033】

(比較例1)

同様にして、比較例1として、Fe/MgO/GaAs構造を作成し、その特性を調べた。

【0034】

ここでは、前記と同様のGaAs(100)基板上に同様の処理を施した後、厚さ20nmのMgO、厚さ50nmのFeをスパッタリング法によって形成した。ここで、MgOの成膜は基板温度400℃、Arガス圧0.2Paで行った。Feの成膜は室温にてArガス圧0.2Paで行った。

【0035】

図5に、比較例1のX線回折(out−of−plane)パターンを測定した結果を示す。この結果より、この場合のMgOは(200)配向であり、Feが(200)配向であることが確認できる。

【0036】

図6に、比較例1について、図3同様にin−plane測定を行った結果を示す。図6において、(a)はGaAsの(022)面、(b)はMgOの(002)面、(c)はFeの(002)面に対するそれぞれの極図形である。ここで、(b)については強度を10倍に拡大している。どの極図形も明確な4回対称性を示していることから、MgO層及びFe層は、それぞれエピタキシャル成長膜である。

【0037】

また、(a)のGaAsの(022)回折ピークと(b)のMgOの(002)回折ピークの角度差とブラッグ角の差から求まるそれぞれの面のなす角はほぼ45°となる。従って、MgO/GaAs界面においては、MgOの(100)面における[100]方向とGaAsの(100)面における[100]方向とが平行に配列されている。

【0038】

同様に、(b)のMgOの(002)回折ピークと(c)のFeの(002)回折ピークの角度差とブラッグ角の差から求まるそれぞれの面のなす角もほぼ45°となる。従って、Fe/MgO界面における面内方向の原子配列は、Feの(100)面における[100]方向とMgOの(100)面における[100]方向とのなす角がほぼ45°となっている。

【0039】

次に、これらの界面での格子のミスマッチをin−planeの対称測定を行うことにより調べた。その結果が図7である。ピーク間の距離が図4と比べて明らかに大きく、この結果から、MgOとGaAs間のミスマッチは−25.4%と極めて大きい。また、FeとMgO間のミスマッチは−3.8%となり、前述のMgOとGaAs間の値より小さいものの、実施例1と比べると大きい。すなわち、比較例1においては、絶縁性薄膜及び強磁性薄膜を化合物半導体上にエピタキシャル成長させることはできたが、各界面のミスマッチは実施例1と比べて大きい。この理由は前記の通りである。

【0040】

(比較例2、3)

同様に、実施例1と同様の構造(Fe/SrF2/GaAs構造)を、Feの成膜を室温で行って作成した場合(比較例2)、200℃で行って作成した場合(比較例3)について調べた。これらの比較例におけるその他の作成条件、各膜厚は実施例1と同様である。

【0041】

比較例2、比較例3のX線回折(out−of−plane)結果を実施例1(試料B)と同時に示したのが図8である。この結果より、実施例1ではFeの(200)面のピークが見られたのに対して、比較例2、3ではいずれもこのピークが見られない。すなわち、Feの成膜温度が400℃であった実施例1に対して、これよりも低い成膜温度でFeを成膜した比較例2、3ではFeの(200)配向が得られない、すなわち、エピタキシャル成長が行われないことがわかる。従って、強磁性薄膜3の成膜時の基板温度を400℃以上とすることにより、エピタキシャル成長した強磁性積層構造が得られる。

【0042】

(実施例2〜5、比較例4〜7)

次に、実施例2〜5として、実施例1と同様の構造、製造方法によって、SrF2の膜厚を0.8nm(実施例2)、1.0nm(実施例3)、2.5nm(実施例4)、5.0nm(実施例5)とした試料をそれぞれ作成した。

【0043】

また、比較例4〜7として、前記の比較例1と同様の構造(Fe/MgO/GaAs構造)、製造方法において、MgOの膜厚を0.8nm(比較例4)、1.0nm(比較例5)、2.5nm(比較例6)、5.0nm(比較例7)とした試料をそれぞれ作成した。

【0044】

実施例1〜5、比較例1、4〜7の試料について、X線回折(out−of−plane)測定を行い、Fe(200)面に対するロッキングカーブの半値幅を求めた。その絶縁性薄膜(SrF2又はMgO)の膜厚依存性を調べた結果が図9である。この結果より、この半値幅の膜厚依存性においては、実施例では膜厚が小さくなるに従って半値幅が小さくなり、比較例では膜厚が小さくなるに従ってやや半値幅が大きくなる。すなわち、実施例と比較例では逆の傾向が見られる。これにより、特にSrF2の膜厚が5nm以下と薄い場合に特にこの半値幅が小さくなることが確認できる。すなわち、SrF2の膜厚が5nm以下と薄い場合には、前記の通りに界面の結晶欠陥が少ないことに加えて、特に結晶配向性の高いFe層(強磁性薄膜)をその上に形成することができる。従って、トンネル絶縁膜として特に好ましい、5nm以下と薄いSrF2を絶縁性薄膜2として用いる場合に、強磁性薄膜3にも特に好ましい特性が得られる。すなわち、絶縁性薄膜2の厚さが0.8〜5nmの場合に特に良好な特性が得られることが確認された。

【0045】

(実施例6)

次に、実施例6として、化合物半導体1をInAsとした場合に同様の構造を同様に作成した。ここで、InAsは、GaAs(100)基板上に予めエピタキシャル成長したInAsを用いた。更に、この実施例では絶縁性薄膜2(SrF2)、強磁性薄膜3(Fe)をスパッタリング法ではなく、電子ビーム蒸着法で成膜した。この電子ビーム蒸着は分子線エピタキシー成膜装置の中で行われ、2.5nmの厚さのSrF2が基板温度300℃で、その後50nmの厚さのFeが基板温度400℃で成膜された。なお、SrF2の蒸着源にはSrF2の単結晶を用いた。

【0046】

この試料の作成時の各段階で、分子線エピタキシー成膜装置中で、反射高速電子線回折(RHEED)パターンを測定した結果を図10に示す。この測定においては、InAsの[110]方向から電子を入射させており、上からInAs表面(SrF2成膜直前)、SrF2表面(Fe成膜直前)、Fe表面のRHEEDパターンを示す。このパターンの周期性が保たれていることから、SrF2、Feはエピタキシャル成長していることがわかる。

【0047】

また、製造後の実施例6のX線回折(out−of−plane)測定結果が図11である。Fe(200)面の強いピークが現れており、Fe層が実施例1〜5と同様に強く(200)配向していることが確認できる。また、界面のミスマッチに起因する結晶欠陥も、実施例1〜5と同様に少ないことが確認できた。従って、化合物半導体1としてGaAsを用いた場合のみならず、InAsを用いた場合においても、同様に良好な特性の強磁性積層構造10を得ることができる。

【0048】

なお、上記の実施例においては、化合物半導体1としてはGaAs、InAsのいずれかが用いられていたが、これに限られるものではない。例えばこれらの混晶であるGa1−xInxAsはこれらと同じ結晶形であり、格子定数がこれらの間の連続的な値をとるため、これを用いた場合でも同様に良好な特性の強磁性積層構造10を得ることができる。

【0049】

また、上記の実施例においてはフッ化化合物である絶縁性薄膜2としてSrF2が用いられていたが、これに限られるものではない。SrF2と同様の結晶構造(蛍石型構造)と、これに近い格子定数をもつ他のフッ化化合物、例えばCaF2も同様に用いることができる。また、化合物半導体1と絶縁性薄膜2の選択においては、これらの界面における格子のミスマッチが最小となるべくこれらを選択することが可能である。例えば、化合物半導体1となるGa1−xInxAsにおけるxの値、絶縁性薄膜2としてSrF2、CaF2のどちらを用いるか等を適宜選択することができる。また、SrF2、CaF2の混合物を用いることもできる。この場合にはこれらの混合物からなるターゲット、あるいは各々の材料からなる2種類のターゲットを用いてスパッタリングによって絶縁性薄膜2を成膜してもよい。

【0050】

また、上記のいずれの実施例においても強磁性薄膜3としてFeが用いられていたが、同様の特性・構造をもつFeCo合金も同様に用いることができる。

【0051】

その他、強磁性薄膜3の厚さ等も、上記の範囲に限定されず、任意である。その他の諸条件も、本発明の要旨を逸脱しない範囲で任意である。

【図面の簡単な説明】

【0052】

【図1】本発明の実施の形態に係る強磁性積層構造の断面図である。

【図2】実施例1のX線回折(out−of−plane)測定結果である。

【図3】実施例1のX線回折(in−plane)測定において、極点測定を(a)GaAsの(022)面、(b)SrF2の(022)面、(c)Feの(002)面に対して行った結果である。

【図4】実施例1のX線回折(in−plane)対称測定結果である。

【図5】比較例1のX線回折(out−of−plane)測定結果である。

【図6】比較例1のX線回折(in−plane)測定において、極点測定を(a)GaAsの(022)面、(b)MgOの(002)面、(c)Feの(002)面に対して行った結果である。

【図7】比較例1のX線回折(in−plane)対称測定結果である。

【図8】比較例2、3のX線回折(out−of−plane)測定結果である。

【図9】実施例1〜5、比較例1、4〜7におけるFe(200)面のロッキングカーブ半値幅の絶縁性薄膜膜厚依存性を示す図である。

【図10】実施例6におけるInAs、SrF2、Fe表面の反射高速電子線回折(RHEED)パターンである。

【図11】実施例6におけるX線回折(out−of−plane)測定結果である。

【符号の説明】

【0053】

1 化合物半導体

2 絶縁性薄膜

3 強磁性薄膜

10 強磁性積層構造

【技術分野】

【0001】

本発明は、強磁性薄膜、絶縁性薄膜、及び化合物半導体からなり、スピンエレクトロニクスデバイスに用いられる強磁性積層構造及びその製造方法に関する。

【背景技術】

【0002】

近年、強磁性体におけるスピンの機能と、電気伝導における電子の機能を共に利用したスピンエレクトロニクスデバイスの研究開発が盛んに行われている。こうしたデバイスの例として、例えばハードディスクドライブにおける磁気ヘッドやMRAM(Magnetic Random Access Memory)がある。

【0003】

例えば、MgO(100)単結晶基板上にFe(100)薄膜とMgO(100)薄膜とFe(100)薄膜が順次形成された単結晶積層構造(以下、Fe/MgO/Feと呼称)では、強磁性体であるFe中のスピン方向に依存してMgO薄膜中を流れるトンネル電流が大きく変化する、いわゆる巨大トンネル磁気抵抗効果が生ずることが非特許文献1及び2に記載されている。特にこの構造においては、各層は単結晶であるため、Fe/MgO薄膜界面及びMgO薄膜/Fe界面の状態が巨大トンネル磁気抵抗効果に大きな影響を与える。つまり、巨大トンネル磁気抵抗効果を発現するためには、界面における格子のミスマッチを小さくして結晶欠陥を少なくし、Feのハーフメタリックな電子軌道を充分に機能させることが必要となる。

【0004】

また、強磁性薄膜、絶縁性薄膜、及び半導体からなる強磁性積層構造を用いたデバイスも提案されている。例えば、非特許文献3では、CoFe/MgO/GaAsの積層構造を用い、化合物半導体であるGaAsへ強磁性体であるCoFeからスピン偏極した電子を注入し、この電子を正孔と再結合させることにより、円偏光の光を発光するスピンLEDが提案されている。このデバイスにおいては、MgO/GaAs界面におけるスピン偏極した電子の注入効率が高いことが必要になる。非特許文献3にて報告されている注入効率は32%であり、まだ改善の余地があるため、更にこの効率を高めることが期待されている。この注入効率を高くするためには、スピン偏極された電子がこの界面で散乱される確率を減少させることが必要である。このためには、やはりその界面の結晶欠陥を減少させることが必要であり、特にこの界面の格子のミスマッチを低減させることが必要になる。

【0005】

従って、スピンエレクトロニクスデバイスにおいて用いられる強磁性積層構造においては、界面における格子のミスマッチを低減させることが、デバイスの特性を向上させる上で重要となる。

【0006】

一方、CaF2はGaAsの良好なパッシベーション膜となることが非特許文献4に記載されている。従って、例えば上記のMgOの代わりに、CaF2を絶縁性薄膜として用いることにより、良好な絶縁性薄膜/GaAs界面の形成が期待される。

【0007】

【非特許文献1】Japanese Journal of Applied Physics 43、L588(2004)

【非特許文献2】Physical Review B、63、054416(2001)

【非特許文献3】Physical Review Letters、94、056601(2005)

【非特許文献4】Applied Surface Science、 117/118、p443〜p446(1997)

【発明の開示】

【発明が解決しようとする課題】

【0008】

前記の強磁性薄膜、絶縁性薄膜、及び半導体からなる積層構造を用いたデバイスにおいて、上記のFe/MgO/GaAs積層構造の場合、通常は基板となるGaAsの結晶面としては(100)面が用いられる。この場合には、エピタキシャル成長により、この上に(100)面配向したMgO及び(100)面配向したFeが得られる。この際、Fe/MgO界面においては、Feの(100)面における[110]方向とMgOの(100)面における[100]方向が平行となる。この界面における格子のミスマッチは−3.8%程度であるため、良好である。しかしながら、MgO/GaAs界面においては、MgOの(100)面における[100]方向とGaAsの(100)面における[100]方向が平行になる。この界面における格子のミスマッチは−25.4%と前記の場合と比べて大きい。従って、この構造においては、MgO/GaAs界面の結晶欠陥が多いため、スピン偏極電子の高い注入効率を得ることはできなかった。

【0009】

一方、CaF2/GaAs界面においては、前記の通り、良好な界面を形成できると期待される。しかしながら、この場合には、GaAs上のCaF2上に更にFeを成長させ、これらの結晶面方位を制御して良好な界面特性を得る方法は知られていない。従って、この構造をもち、良好な界面特性をもつ強磁性積層構造は得られていなかった。

【0010】

従って、良好な界面特性をもつ強磁性薄膜、絶縁性薄膜、及び化合物半導体からなる強磁性積層構造を得ることは困難であった。

【0011】

本発明は、斯かる問題点に鑑みてなされたものであり、上記問題点を解決する発明を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、上記課題を解決すべく、以下に掲げる構成とした。

本発明の強磁性積層構造は、化合物半導体、絶縁性薄膜、及び強磁性薄膜が順次積層された強磁性積層構造であって、前記化合物半導体はGaAs、InAs、またはこれらの混晶であり、前記絶縁性薄膜は蛍石型構造のフッ化化合物からなり、前記強磁性薄膜はFeまたはFeCo合金からなることを特徴とする。

また、この強磁性積層構造は、前記強磁性薄膜から前記絶縁性薄膜を通して前記化合物半導体にスピン偏極電子が注入されて使用されることを特徴とする。

また、この強磁性積層構造において、前記フッ化化合物はCaF2、SrF2のいずれかあるいはこれらの混合物であることを特徴とする。

また、この強磁性積層構造は、前記化合物半導体の(100)面上に前記絶縁性薄膜及び前記強磁性薄膜が順次積層されたことを特徴とする。

また、この強磁性積層構造において、前記絶縁性薄膜の厚さが0.8〜5.0nmの範囲であることを特徴とする。

本発明の強磁性積層構造の製造方法は、前記強磁性積層構造を製造する製造方法であって、前記化合物半導体上に真空中で前記絶縁性薄膜及び前記強磁性薄膜を連続して形成し、前記強磁性薄膜を形成する際の基板温度を400℃以上とすることを特徴とする。

また、この強磁性積層構造の製造方法において、前記絶縁性薄膜及び前記強磁性薄膜の形成は、スパッタリング法によって行うことを特徴とする。

また、この強磁性積層構造の製造方法において、前記絶縁性薄膜及び前記強磁性薄膜の形成は、電子ビーム蒸着法によって行うことを特徴とする。

【発明の効果】

【0013】

本発明は以上のように構成されているので、良好な界面特性をもつ強磁性薄膜、絶縁性薄膜、及び化合物半導体からなる強磁性積層構造を得ることができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明について具体的な実施形態を示しながら説明する。ただし、本発明はこれらの実施形態に限定されるものではない。

【0015】

図1は本発明の実施の形態に係る強磁性積層構造10の断面図である。この強磁性積層構造10においては、化合物半導体1上に絶縁性薄膜2及び強磁性薄膜3が順次形成されている。この強磁性積層構造10は、強磁性薄膜3から絶縁性薄膜2を通して化合物半導体1にスピン偏極電子が注入されて使用される。例えば、この強磁性積層構造10をスピンLEDに用い、化合物半導体1を発光層としても用いることができる。この場合には、この構造における各界面の結晶欠陥が少ないために、スピン偏極電子の発光層への高い注入効率が得られるため、高効率のスピンLEDを得ることができる。なお、スピンLED以外にも、化合物半導体1においてこのスピン偏極電子を利用する各種のデバイス、例えば、スピンFETや逆スピンホール効果(スピン流誘起スピンホール効果)を用いる磁気センサーなどにおいても同様に、この強磁性積層構造10を用いることができることは明らかである。

【0016】

ここで、化合物半導体1は、GaAs又はInAs単結晶からなる(100)基板であり、絶縁性薄膜2はこれらの(100)面上に形成される。なお、化合物半導体1の厚さは任意である。なお、これらはエピタキシャル成長した基板、バルク半導体基板のいずれであってもよい。また、GaAsとInAsの混晶を同様に化合物半導体1として用いてもよい。

【0017】

絶縁性薄膜2は、蛍石型構造をもつフッ化化合物からなる。具体的には、蛍石型構造をもつCaF2又はSrF2が好ましい。その成膜法としては、一般的に薄膜形成に用いられるスパッタリング法、電子ビーム蒸着法、抵抗加熱蒸着法、分子線エピタキシー法(MBE法)等を用いることができる。この絶縁性薄膜2は化合物半導体1上にエピタキシャル成長し、その結晶配向面は化合物半導体1と同様に(100)面となる。その厚さは例えば0.8nm〜20nmとすることができるが、特に5nm以下であることが、強磁性薄膜3の結晶配向性を向上させる上で好ましい。なお、この絶縁性薄膜2をCaF2、SrF2のどちらにするかは、化合物半導体1の種類(GaAs、InAs、及びこれらの混晶)に応じて、界面の格子のミスマッチを小さくするべく選択することができる。

【0018】

強磁性薄膜3は、Fe又はFeCo合金からなる強磁性体である。その厚さは例えば50nmとすることができる。その成膜法としては、絶縁性薄膜2と同様にスパッタリング法、電子ビーム蒸着法、抵抗加熱蒸着法、MBE法を用いることができる。特に、強磁性薄膜3の成膜においては、絶縁性薄膜2を成膜した直後に真空中で連続して成膜することが好ましい(なお、ここでいう真空とは上記成膜法における真空度での雰囲気を意味する)。また、その成膜温度は400℃以上とすることが、強磁性薄膜3をエピタキシャル成長させる上で好ましい。

【0019】

以下に、この構造が好ましい理由につき説明する。まず、非特許文献3に記載のMgO/GaAs積層構造において、MgOの(100)面における[110]方位とGaAsの(100)面における[100]方位とが一致した場合には、格子のミスマッチは5.5%程度と小さくなる。すなわち、MgOの(100)面とGaAsの(100)面の間ではミスマッチの小さい接合界面が得られるとも考えられる。しかしながら、実際にはミスマッチの小さい接合界面は得られていない。

【0020】

これは、GaAsの(100)面には極性があることに起因する。すなわち、III−V属化合物半導体であるGaAsの(100)面は、III属元素(Ga)のみ、あるいはV属元素(As)のみからなる。これに対して、MgOの(100)面においては、その結晶構造が異なるため、陽イオン(Mgイオン)と陰イオン(Oイオン)とが混在する。従って、MgOの(100)面がGaAsの(100)面上に積層された場合には、電荷の補償ができないため、実際にはこれらが整合した構造は形成されにくい。従って、実際にMgOをGaAsの(100)面上に成長させた場合には、MgOの(100)面における[100]方位とGaAsの(100)面における[100]方位とが平行となった構造として形成される。この場合の格子のミスマッチは前記の通り、−25.4%と大きな値となる。従って、この界面には多くの結晶欠陥が発生する。

【0021】

これに対して、本発明における絶縁性薄膜2となる蛍石型構造のフッ化化合物においては、その(100)面はGaAsと同様に、単一元素から構成される。従って、格子定数が化合物半導体1と合致すれば、絶縁性薄膜2の(100)面を化合物半導体1の(100)面上に格子のミスマッチが小さくなる方位で成長させることができる。すなわち、絶縁性薄膜2/化合物半導体1の界面の結晶欠陥を少なくすることができる。

【0022】

更に、この構造の絶縁性薄膜2上には、Fe又はFeCoからなる強磁性薄膜3をエピタキシャル成長させることができる。従って、強磁性薄膜3/絶縁性薄膜2界面における結晶欠陥も少なくすることができる。これは、特に強磁性薄膜3の成膜時の基板温度を400℃以上とした場合に顕著となる。また、絶縁性薄膜2の厚さを5nm以下と薄くした場合には、特に強磁性薄膜3のロッキングカーブ半値幅を小さくすることができるため、特に結晶配向性の良好な、結晶欠陥の少ない強磁性積層構造となる。絶縁性薄膜2の厚さが薄い方が好ましい特性が得られることは、特に絶縁性薄膜2をトンネル絶縁膜として使用する上では好ましい。

【0023】

従って、図1の構造の強磁性積層構造においては、絶縁性薄膜2/化合物半導体1、強磁性薄膜3/絶縁性薄膜2のどちらの界面における結晶欠陥も少なくすることができ、良好な界面特性が得られる。従って、強磁性薄膜3から注入されるスピン偏極電子の界面における散乱を抑制することができ、高い電子注入効率をもった強磁性積層構造となる。これを用いて、例えば高効率のスピンLED等、各種のスピントロニクスデバイスを得ることができる。

【0024】

(実施例1)

本発明の実施例(実施例1)として、化合物半導体1としてGaAsの(100)単結晶基板、絶縁性薄膜2として蛍石構造のSrF2、強磁性薄膜3としてFeを用いた強磁性積層構造10(Fe/SrF2/GaAs構造)を製造し、その特性を調べた。

【0025】

まず、GaAs(100)基板をアセトンとイソプロピルアルコールで洗浄後、表面の酸化膜をフッ酸を用いて除去した。その後、このGaAs基板上にスパッタリング法によって厚さ20nmのSrF2層、及び厚さ50nmのFe層を連続して形成した。SrF2層を形成する際には、SrF2ターゲットを用い、基板温度400℃、Arガス圧0.5Paでスパッタリングを行った。Fe層を形成する際には、Feターゲットを用い、基板温度400℃、Arガス圧0.2Paでスパッタリングを行った。なお、この実施例1とは別に、参考のためにSrF2層のみを形成し、Fe層を形成しない試料も作成した。

【0026】

図2は、これらの試料のX線回折(out−of−plane)パターンを測定した結果であり、各ピークには対応する各物質の面方位が記してある。ここで、試料Aは前記のFe層を形成しなかった試料であり、試料Bが実施例1となる、Fe層まで形成した試料である。すなわち、試料AにおいてはSrF2層の結果が強く現れており、試料Bにおいては、Fe層の結果が強く現れている。

【0027】

図2における試料Aの結果より、SrF2層が蛍石型構造の(200)方向に配向し、試料Bの結果から、Fe層も(200)配向していることが確認できる。

【0028】

更に、試料Bについて、X線回折のin−plane測定を行った結果を図3に示す。図3において、(a)はGaAsの(022)面、(b)はSrF2の(022)面、(c)はFeの(002)面に対するそれぞれの極図形である。どの極図形も明確な4回対称性を示していることから、SrF2層及びFe層は、それぞれエピタキシャル成長膜である。

【0029】

また、(a)のGaAsの(022)回折ピークと(b)のSrF2の(022)回折ピークの角度差とブラッグ角の差から求まるそれぞれの面のなす角はほぼ零となることから、GaAsの(022)面とSrF2の(022)面はほぼ平行であることがわかる。すなわち、SrF2/GaAs界面においては、SrF2の(100)面における[100]方向とGaAsの(100)面における[100]方向とが平行に配列されている。

【0030】

また、(b)のSrF2の(022)回折ピークと(c)のFeの(002)回折ピークの角度差とブラッグ角の差から求まるそれぞれの面のなす角はほぼ45°となる。従って、Fe/SrF2界面における面内方向の原子配列は、Feの(100)面における[100]方向とSrF2の(100)面における[100]方向とが平行に配列されている。

【0031】

次に、これらの界面での格子のミスマッチを試料AとBのin−planeの対称測定を行うことにより調べた。その結果が図4である。この結果におけるピーク間距離がこのミスマッチに対応する。この結果より、試料AにおけるSrF2とGaAs間のミスマッチは2.4%と小さな値となっている。また、試料BにおけるFeのピークから、FeとSrF2間のミスマッチは−0.9%と極めて小さくなっている。

【0032】

従って、実施例1においては、化合物半導体1であるGaAs上に絶縁性薄膜2である蛍石型構造のSrF2、さらにその上に強磁性薄膜3であるFeがそれぞれエピタキシャル成長しており、これらの界面における格子ミスマッチが小さな値であることが確認できる。すなわち、上記の通り、この構造によって界面の結晶欠陥が少ない強磁性積層構造が実現できている。

【0033】

(比較例1)

同様にして、比較例1として、Fe/MgO/GaAs構造を作成し、その特性を調べた。

【0034】

ここでは、前記と同様のGaAs(100)基板上に同様の処理を施した後、厚さ20nmのMgO、厚さ50nmのFeをスパッタリング法によって形成した。ここで、MgOの成膜は基板温度400℃、Arガス圧0.2Paで行った。Feの成膜は室温にてArガス圧0.2Paで行った。

【0035】

図5に、比較例1のX線回折(out−of−plane)パターンを測定した結果を示す。この結果より、この場合のMgOは(200)配向であり、Feが(200)配向であることが確認できる。

【0036】

図6に、比較例1について、図3同様にin−plane測定を行った結果を示す。図6において、(a)はGaAsの(022)面、(b)はMgOの(002)面、(c)はFeの(002)面に対するそれぞれの極図形である。ここで、(b)については強度を10倍に拡大している。どの極図形も明確な4回対称性を示していることから、MgO層及びFe層は、それぞれエピタキシャル成長膜である。

【0037】

また、(a)のGaAsの(022)回折ピークと(b)のMgOの(002)回折ピークの角度差とブラッグ角の差から求まるそれぞれの面のなす角はほぼ45°となる。従って、MgO/GaAs界面においては、MgOの(100)面における[100]方向とGaAsの(100)面における[100]方向とが平行に配列されている。

【0038】

同様に、(b)のMgOの(002)回折ピークと(c)のFeの(002)回折ピークの角度差とブラッグ角の差から求まるそれぞれの面のなす角もほぼ45°となる。従って、Fe/MgO界面における面内方向の原子配列は、Feの(100)面における[100]方向とMgOの(100)面における[100]方向とのなす角がほぼ45°となっている。

【0039】

次に、これらの界面での格子のミスマッチをin−planeの対称測定を行うことにより調べた。その結果が図7である。ピーク間の距離が図4と比べて明らかに大きく、この結果から、MgOとGaAs間のミスマッチは−25.4%と極めて大きい。また、FeとMgO間のミスマッチは−3.8%となり、前述のMgOとGaAs間の値より小さいものの、実施例1と比べると大きい。すなわち、比較例1においては、絶縁性薄膜及び強磁性薄膜を化合物半導体上にエピタキシャル成長させることはできたが、各界面のミスマッチは実施例1と比べて大きい。この理由は前記の通りである。

【0040】

(比較例2、3)

同様に、実施例1と同様の構造(Fe/SrF2/GaAs構造)を、Feの成膜を室温で行って作成した場合(比較例2)、200℃で行って作成した場合(比較例3)について調べた。これらの比較例におけるその他の作成条件、各膜厚は実施例1と同様である。

【0041】

比較例2、比較例3のX線回折(out−of−plane)結果を実施例1(試料B)と同時に示したのが図8である。この結果より、実施例1ではFeの(200)面のピークが見られたのに対して、比較例2、3ではいずれもこのピークが見られない。すなわち、Feの成膜温度が400℃であった実施例1に対して、これよりも低い成膜温度でFeを成膜した比較例2、3ではFeの(200)配向が得られない、すなわち、エピタキシャル成長が行われないことがわかる。従って、強磁性薄膜3の成膜時の基板温度を400℃以上とすることにより、エピタキシャル成長した強磁性積層構造が得られる。

【0042】

(実施例2〜5、比較例4〜7)

次に、実施例2〜5として、実施例1と同様の構造、製造方法によって、SrF2の膜厚を0.8nm(実施例2)、1.0nm(実施例3)、2.5nm(実施例4)、5.0nm(実施例5)とした試料をそれぞれ作成した。

【0043】

また、比較例4〜7として、前記の比較例1と同様の構造(Fe/MgO/GaAs構造)、製造方法において、MgOの膜厚を0.8nm(比較例4)、1.0nm(比較例5)、2.5nm(比較例6)、5.0nm(比較例7)とした試料をそれぞれ作成した。

【0044】

実施例1〜5、比較例1、4〜7の試料について、X線回折(out−of−plane)測定を行い、Fe(200)面に対するロッキングカーブの半値幅を求めた。その絶縁性薄膜(SrF2又はMgO)の膜厚依存性を調べた結果が図9である。この結果より、この半値幅の膜厚依存性においては、実施例では膜厚が小さくなるに従って半値幅が小さくなり、比較例では膜厚が小さくなるに従ってやや半値幅が大きくなる。すなわち、実施例と比較例では逆の傾向が見られる。これにより、特にSrF2の膜厚が5nm以下と薄い場合に特にこの半値幅が小さくなることが確認できる。すなわち、SrF2の膜厚が5nm以下と薄い場合には、前記の通りに界面の結晶欠陥が少ないことに加えて、特に結晶配向性の高いFe層(強磁性薄膜)をその上に形成することができる。従って、トンネル絶縁膜として特に好ましい、5nm以下と薄いSrF2を絶縁性薄膜2として用いる場合に、強磁性薄膜3にも特に好ましい特性が得られる。すなわち、絶縁性薄膜2の厚さが0.8〜5nmの場合に特に良好な特性が得られることが確認された。

【0045】

(実施例6)

次に、実施例6として、化合物半導体1をInAsとした場合に同様の構造を同様に作成した。ここで、InAsは、GaAs(100)基板上に予めエピタキシャル成長したInAsを用いた。更に、この実施例では絶縁性薄膜2(SrF2)、強磁性薄膜3(Fe)をスパッタリング法ではなく、電子ビーム蒸着法で成膜した。この電子ビーム蒸着は分子線エピタキシー成膜装置の中で行われ、2.5nmの厚さのSrF2が基板温度300℃で、その後50nmの厚さのFeが基板温度400℃で成膜された。なお、SrF2の蒸着源にはSrF2の単結晶を用いた。

【0046】

この試料の作成時の各段階で、分子線エピタキシー成膜装置中で、反射高速電子線回折(RHEED)パターンを測定した結果を図10に示す。この測定においては、InAsの[110]方向から電子を入射させており、上からInAs表面(SrF2成膜直前)、SrF2表面(Fe成膜直前)、Fe表面のRHEEDパターンを示す。このパターンの周期性が保たれていることから、SrF2、Feはエピタキシャル成長していることがわかる。

【0047】

また、製造後の実施例6のX線回折(out−of−plane)測定結果が図11である。Fe(200)面の強いピークが現れており、Fe層が実施例1〜5と同様に強く(200)配向していることが確認できる。また、界面のミスマッチに起因する結晶欠陥も、実施例1〜5と同様に少ないことが確認できた。従って、化合物半導体1としてGaAsを用いた場合のみならず、InAsを用いた場合においても、同様に良好な特性の強磁性積層構造10を得ることができる。

【0048】

なお、上記の実施例においては、化合物半導体1としてはGaAs、InAsのいずれかが用いられていたが、これに限られるものではない。例えばこれらの混晶であるGa1−xInxAsはこれらと同じ結晶形であり、格子定数がこれらの間の連続的な値をとるため、これを用いた場合でも同様に良好な特性の強磁性積層構造10を得ることができる。

【0049】

また、上記の実施例においてはフッ化化合物である絶縁性薄膜2としてSrF2が用いられていたが、これに限られるものではない。SrF2と同様の結晶構造(蛍石型構造)と、これに近い格子定数をもつ他のフッ化化合物、例えばCaF2も同様に用いることができる。また、化合物半導体1と絶縁性薄膜2の選択においては、これらの界面における格子のミスマッチが最小となるべくこれらを選択することが可能である。例えば、化合物半導体1となるGa1−xInxAsにおけるxの値、絶縁性薄膜2としてSrF2、CaF2のどちらを用いるか等を適宜選択することができる。また、SrF2、CaF2の混合物を用いることもできる。この場合にはこれらの混合物からなるターゲット、あるいは各々の材料からなる2種類のターゲットを用いてスパッタリングによって絶縁性薄膜2を成膜してもよい。

【0050】

また、上記のいずれの実施例においても強磁性薄膜3としてFeが用いられていたが、同様の特性・構造をもつFeCo合金も同様に用いることができる。

【0051】

その他、強磁性薄膜3の厚さ等も、上記の範囲に限定されず、任意である。その他の諸条件も、本発明の要旨を逸脱しない範囲で任意である。

【図面の簡単な説明】

【0052】

【図1】本発明の実施の形態に係る強磁性積層構造の断面図である。

【図2】実施例1のX線回折(out−of−plane)測定結果である。

【図3】実施例1のX線回折(in−plane)測定において、極点測定を(a)GaAsの(022)面、(b)SrF2の(022)面、(c)Feの(002)面に対して行った結果である。

【図4】実施例1のX線回折(in−plane)対称測定結果である。

【図5】比較例1のX線回折(out−of−plane)測定結果である。

【図6】比較例1のX線回折(in−plane)測定において、極点測定を(a)GaAsの(022)面、(b)MgOの(002)面、(c)Feの(002)面に対して行った結果である。

【図7】比較例1のX線回折(in−plane)対称測定結果である。

【図8】比較例2、3のX線回折(out−of−plane)測定結果である。

【図9】実施例1〜5、比較例1、4〜7におけるFe(200)面のロッキングカーブ半値幅の絶縁性薄膜膜厚依存性を示す図である。

【図10】実施例6におけるInAs、SrF2、Fe表面の反射高速電子線回折(RHEED)パターンである。

【図11】実施例6におけるX線回折(out−of−plane)測定結果である。

【符号の説明】

【0053】

1 化合物半導体

2 絶縁性薄膜

3 強磁性薄膜

10 強磁性積層構造

【特許請求の範囲】

【請求項1】

化合物半導体、絶縁性薄膜、及び強磁性薄膜が順次積層された強磁性積層構造であって、

前記化合物半導体はGaAs、InAs、またはこれらの混晶であり、

前記絶縁性薄膜は蛍石型構造のフッ化化合物からなり、

前記強磁性薄膜はFeまたはFeCo合金からなることを特徴とする強磁性積層構造。

【請求項2】

前記強磁性薄膜から前記絶縁性薄膜を通して前記化合物半導体にスピン偏極電子が注入されて使用されることを特徴とする請求項1に記載の強磁性積層構造。

【請求項3】

前記フッ化化合物はCaF2、SrF2のいずれかあるいはこれらの混合物であることを特徴とする請求項1又は2に記載の強磁性積層構造。

【請求項4】

前記化合物半導体の(100)面上に前記絶縁性薄膜及び前記強磁性薄膜が順次積層されたことを特徴とする請求項1から請求項3までのいずれか1項に記載の強磁性積層構造。

【請求項5】

前記絶縁性薄膜の厚さが0.8〜5.0nmの範囲であることを特徴とする請求項1から請求項4までのいずれか1項に記載の強磁性積層構造。

【請求項6】

請求項1から請求項5までのいずれか1項に記載の強磁性積層構造を製造する製造方法であって、

前記化合物半導体上に真空中で前記絶縁性薄膜及び前記強磁性薄膜を連続して形成し、前記強磁性薄膜を形成する際の基板温度を400℃以上とすることを特徴とする強磁性積層構造の製造方法。

【請求項7】

前記絶縁性薄膜及び前記強磁性薄膜の形成は、スパッタリング法によって行うことを特徴とする請求項6に記載の強磁性積層構造の製造方法。

【請求項8】

前記絶縁性薄膜及び前記強磁性薄膜の形成は、電子ビーム蒸着法によって行うことを特徴とする請求項6に記載の強磁性積層構造の製造方法。

【請求項1】

化合物半導体、絶縁性薄膜、及び強磁性薄膜が順次積層された強磁性積層構造であって、

前記化合物半導体はGaAs、InAs、またはこれらの混晶であり、

前記絶縁性薄膜は蛍石型構造のフッ化化合物からなり、

前記強磁性薄膜はFeまたはFeCo合金からなることを特徴とする強磁性積層構造。

【請求項2】

前記強磁性薄膜から前記絶縁性薄膜を通して前記化合物半導体にスピン偏極電子が注入されて使用されることを特徴とする請求項1に記載の強磁性積層構造。

【請求項3】

前記フッ化化合物はCaF2、SrF2のいずれかあるいはこれらの混合物であることを特徴とする請求項1又は2に記載の強磁性積層構造。

【請求項4】

前記化合物半導体の(100)面上に前記絶縁性薄膜及び前記強磁性薄膜が順次積層されたことを特徴とする請求項1から請求項3までのいずれか1項に記載の強磁性積層構造。

【請求項5】

前記絶縁性薄膜の厚さが0.8〜5.0nmの範囲であることを特徴とする請求項1から請求項4までのいずれか1項に記載の強磁性積層構造。

【請求項6】

請求項1から請求項5までのいずれか1項に記載の強磁性積層構造を製造する製造方法であって、

前記化合物半導体上に真空中で前記絶縁性薄膜及び前記強磁性薄膜を連続して形成し、前記強磁性薄膜を形成する際の基板温度を400℃以上とすることを特徴とする強磁性積層構造の製造方法。

【請求項7】

前記絶縁性薄膜及び前記強磁性薄膜の形成は、スパッタリング法によって行うことを特徴とする請求項6に記載の強磁性積層構造の製造方法。

【請求項8】

前記絶縁性薄膜及び前記強磁性薄膜の形成は、電子ビーム蒸着法によって行うことを特徴とする請求項6に記載の強磁性積層構造の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【公開番号】特開2009−246082(P2009−246082A)

【公開日】平成21年10月22日(2009.10.22)

【国際特許分類】

【出願番号】特願2008−89702(P2008−89702)

【出願日】平成20年3月31日(2008.3.31)

【出願人】(591108178)秋田県 (126)

【Fターム(参考)】

【公開日】平成21年10月22日(2009.10.22)

【国際特許分類】

【出願日】平成20年3月31日(2008.3.31)

【出願人】(591108178)秋田県 (126)

【Fターム(参考)】

[ Back to top ]