微小試料台、微小試料台作成用基板および微小試料台を用いた分析方法

【課題】分析時におけるバックグラウンドノイズを大幅に低減することが可能な微小試料台を提供すること。

【解決手段】微小試料台100は、半導体基板よりなる微小試料台基部10の一面に成膜により一体化された微小試料搭載用薄膜20を有する。微小試料台基部10はV字形状の溝11を有し、微小試料搭載用薄膜20は溝11の上面と溝11の最深部との間に設けられた上端面21を有する。V字形状の溝の両側面は(111)面である。微小試料台基部10の上面13と微小試料搭載用薄膜20の上端面21との間の部分が微小試料70のガード部となる。

【解決手段】微小試料台100は、半導体基板よりなる微小試料台基部10の一面に成膜により一体化された微小試料搭載用薄膜20を有する。微小試料台基部10はV字形状の溝11を有し、微小試料搭載用薄膜20は溝11の上面と溝11の最深部との間に設けられた上端面21を有する。V字形状の溝の両側面は(111)面である。微小試料台基部10の上面13と微小試料搭載用薄膜20の上端面21との間の部分が微小試料70のガード部となる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、電子顕微鏡等により分析を行う試料を固定する微小試料台、微小試料台作成用基板および微小試料台を用いた分析方法に関する。

【背景技術】

【0002】

半導体ウエハの上面に形成された半導体素子やディスクリートの半導体デバイスを透過型電子顕微鏡(TEM)等により、分析あるいは観察(以下、観察を含めて分析という)を行うには、半導体素子や半導体デバイス等の分析エリアをエッチング法やFIB(Focused Ion Beam)により加工して微小試料を形成し、該微小試料を切り取ったうえ、該微小試料よりも大幅に大きい厚さの微小試料台に固定し、さらに、微小試料が固定された微小試料台を、上部にガード部が設けられたほぼ半円弧状のメッシュといわれる試料ホルダに固定したものを準備する。そして、微小試料台を介して微小試料が固定された試料ホルダをピンセット等により把持して、TEMのステージに取り付けて分析を行う。

【0003】

通常、微小試料台は金属製の基板を用い、試料ホルダは、シリコン基板や金属製の基板等を用いる。この、微小試料は、例えば、10μm×10μm×1μm(厚さ)程度のサイズにしたうえ、微小試料台の側面に固定される。

そして、微小試料台に微小試料を固定した後、Ga+イオン等の荷電粒子イオンを用いたFIB法にて微小試料を、一般的には、100nm程度の厚さにまで薄片化する。

【0004】

微小試料台または試料ホルダが金属製の場合、試料固定面の粗さが試料のサイズに対して、凹凸が大きいので、固定した試料の位置を確認するのが困難とあり、また、固定した試料が傾くために観察面を正確に位置あわせするのが困難となる。

そこで、微小試料台をシリコン基板で形成するようにしたものも知られている。(例えば、特許文献1参照)

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−185338号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記微小試料を薄片化する工程では、微小試料と共に微小試料台にもGaイオンビームが照射される。微小試料は厚さ1μmのものをほぼ0.1μm程度の厚さにする。これに対し、固定される試料ホルダは、100μm程度であり、微小試料の厚さとは桁違いに厚い。このため、イオンビームによってスパッタされた試料台の微粉が微小試料の表面に付着する。付着した微粉は、TEM分析時に斑点となり、バックグラウンドノイズとなって解像度低下等の原因となる。

試料台の厚さが厚いほど微小試料の表面に付着する微粉の量は増大するので、微小試料の厚さが厚いほどバックグラウンドノイズは大きくなって、分析におおきな障害となる。

【課題を解決するための手段】

【0007】

請求項1に記載の微小試料台は、突出し状のガード部および該ガード部の上面から没入した溝部を有する半導体基板と、前記半導体基板の一面に成膜により一体化され、前記半導体基板における前記溝部の最深部と前記ガード部の上面との中間に上端面を有する微小試料搭載用薄膜と、を具備し、前記半導体基板の前記溝部はV字形状であり、前記V字形状の溝の両側面は(111)面であることを特徴とする。

請求項2に記載の微小試料台は、請求項1に記載の微小試料台において、前記半導体基板はシリコン基板であり、前記微小試料搭載用薄膜はシリコンを含む無機材料からなることを特徴とする。

請求項3に記載の微小試料台は、請求項2に記載の微小試料台において、前記微小試料搭載用薄膜は、窒化シリコンからなることを特徴とする。

請求項4に記載の微小試料台は、請求項1乃至3のいずれか1項に記載の微小試料台において、前記微小試料搭載用薄膜は、その厚さが数百nm以下であることを特徴とする。

請求項5に記載の微小試料台は、請求項4に記載の微小試料台において、前記微小試料搭載用薄膜は、その厚さが百nm以下であることを特徴とする。

【0008】

請求項6に記載の微小試料台作成用基板は、半導体ウエハに複数の微小試料台が形成された微小試料台作成用基板であって、前記微小試料台は、突出し状のガード部および該ガード部の上面から没入した溝部を有する前記半導体ウエハの一部により構成される半導体基板と、前記半導体基板の一面に成膜により一体化され、前記半導体基板における前記溝部の最深部と前記ガード部の上面との中間に上端面を有する微小試料搭載用薄膜と、を具備し、前記半導体基板の前記溝部はV字形状であり、前記V字形状の溝の両側面は(111)面であることを特徴とする。

【0009】

請求項7に記載の微小試料台作成用基板は、請求項6に記載の微小試料台用作成基板において、前記微小試料台は、前記ガード部の上面を対向して、線対称に対として半導体ウエハに配列されていることを特徴とする。

【0010】

請求項8に記載の微小試料台作成用基板は請求項7に記載の微小試料台作成基板において、前記半導体ウエハは、外周面に(110)面のフラット面を有し、前記微小試料台は、対として配置された前記微小試料台の線対称軸が前記フラット面に対して45度傾斜するように配列されていることを特徴とする。

【0011】

請求項9に記載の微小試料台を用いた分析方法は、請求項1乃至5のいずれか1項に記載の微小試料台を準備するステップと、前記微小試料台の前記微小試料搭載用薄膜に前記微小試料搭載用薄膜より厚さが厚い微小試料を固定するステップと、前記微小試料が固定された微小試料台を、直接、分析用装置の分析ステージに取り付けるステップと、を具備することを特徴とする。

請求項10に記載の微小試料台の分析方法は、請求項9に記載の微小試料台を用いた分析方法において、前記微小試料台の前記微小試料搭載用薄膜に前記微小試料搭載用薄膜より厚さが厚い微小試料を固定するステップは、前記微小試料搭載用薄膜の前記上端面上に前記微小試料を固定する工程を含むことを特徴とする。

【発明の効果】

【0012】

この発明によれば、半導体基板の一面に成膜により該半導体基板に一体化された微小試料搭載用薄膜を形成するので、微小試料の固定部を該微小試料よりも薄いものとすることが可能となり、微小試料を薄片化するために荷電粒子ビームを照射しても、微小試料台がスパッタされて微小試料に付着する異物を低減する効果を奏する。

【図面の簡単な説明】

【0013】

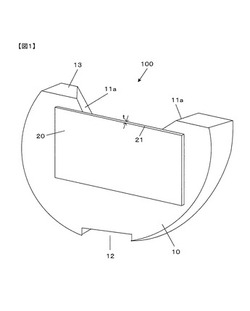

【図1】この発明の微小試料台を表面側からみた拡大斜視図。

【図2】図1の微小試料台を裏面側からみた拡大斜視図

【図3】(a)〜(f)は、図1および図2に示す微小試料台の製造方法を説明するための拡大断面図。

【図4】(g)〜(k)は、図3(f)に続く微小試料台の製造方法を説明するための拡大断面図。

【図5】(a)〜(c)は、図1および図2に示す微小試料台の製造方法を説明するための拡大平面図であり、それぞれ、図3(a)〜(c)に対応する。

【図6】(d)〜(f)は、図5(c)に続く微小試料台の製造方法を説明するための拡大平面図であり、それぞれ、図3(d)〜(f)に対応する。

【図7】(g)および(h)は、図5(f)に続く微小試料台の製造方法を説明するための拡大平面図であり、それぞれ、図4(g)および(h)に対応する。

【図8】(i)〜(k)は、図5(h)に続く微小試料台の製造方法を説明するための拡大平面図であり、それぞれ、図4(i)〜(k)に対応する。

【図9】図7(h)に図示された微小試料台を裏面側からみた拡大平面図。

【図10】図8(i)に図示された微小試料台を裏面側からみた拡大平面図。

【図11】図8(j)に図示された微小試料台を裏面側からみた拡大平面図。

【図12】図8(k)に図示された微小試料台を裏面側からみた拡大平面図。

【図13】図1および図2に示す微小試料台を半導体ウエハから分離する直前の状態を示す平面図。

【図14】この発明の変形例を示す拡大斜視図

【図15】この発明の微小試料にマイクロプローブを固定し、さらに微小試料台に固定した状態の一例を示す斜視図。

【図16】図15に示す状態からマイクロプローブを分離した状態の一例を示す斜視図。

【図17】この発明の微小試料台に微小試料を固定する一例を説明するための側面図。

【図18】この発明の微小試料台に微小試料を固定する第二の例を説明するための側面図。

【図19】この発明の微小試料台に微小試料を固定する第三の例を説明するための側面図。

【図20】この発明の微小試料台に微小試料を固定する第四の例を説明するための側面図。

【図21】この発明の微小試料台に微小試料を固定する第五の例を説明するための側面図。

【発明を実施するための形態】

【0014】

以下、この発明の微小試料台の実施形態の一例について、図1、図2を参照して説明する。

図1および図2はこの発明の微小試料台の実施の形態の一例を示す拡大斜視図であり、図1は表面側からみた斜視図、図2は図1を裏面側からみた斜視図である。

微小試料台100は、シリコン基板等の半導体基板からなる微小試料台基部10および窒化シリコン(SiN)等の無機材料からなる試料搭載用薄膜20からなっている。 微小試料台基部10は、平面視で、直径2〜4mmのほぼ半円弧形状をなしている。半円弧形状部の上部には、頂角θが90度のV字形状の溝11が形成されている。また、半円弧形状部の下面には、凹部12が形成されている。V字形状の溝11の頂部と凹部12の中心を結ぶ直線は、試料台基部10の中心を通る。この凹部12は、詳細は後述するが、半導体ウエハからこの微小試料台を分離する際、分離を容易にするために形成されたものである。

【0015】

試料搭載用薄膜20は、試料台基部の表面(一面)に、CVD(Chemical Vapor Deposition)法により形成されたものである。半導体基板からなる微小試料台基部10は、表面の平坦性が良好であり、この微小試料台基部10にCVD法により形成される微小試料搭載用薄膜20は、平坦性が高く、且つ、大変、薄く形成することができる。

限定する意味ではないが、微小試料搭載用薄膜20の厚さtは数百nm以下、特に、百nm程度以下とすることが可能であり、この微小試料台100に固定される微小試料の厚さよりも薄くすることが可能である。

【0016】

通常、微小試料は、微小試料台100に固定する前には、5μm程度の厚さを有しており、微小試料台に固定した後、Ga+ビーム等の荷電粒子ビームを照射して、0.1μm程度の厚さにする薄片化処理を行う。この際、微小試料台がスパッタされて微小試料の表面に異物として付着して、分析をする際のバックグラウンドノイズとなる。しかし、この発明では、微小試料搭載用薄膜20が大変薄いので、微小試料に付着する異物の量を大幅に抑止することができる。

【0017】

V字形状の溝11の上側面11a、11aは、シリコンの(111)面となっており、微小試料搭載用薄膜20側に向かって上昇する傾斜面となっている。微小試料台基部10の上面13は、微小試料搭載用薄膜20の上端面21よりも高い位置にある。換言すれば、微小試料搭載用薄膜20の上端面21は、V字形状の溝11の最深部である頂部と上面13の中間に位置づけられている。

微小試料台基部10が微小試料搭載用薄膜20の上端面21よりも突き出して形成された突出し部を有するのは、微小試料搭載用薄膜20に固定された微小試料を分析する作業において、微小試料に分析装置等が衝突するのをガードするためである。すなわち、微小試料台基部10の微小試料搭載用薄膜20よりも高い部分はガード部となっている。

【0018】

そして、この微小試料台は、微小試料を固定した状態で、直接、分析装置等の分析のためのステージ上に取り付けられるもので、微小試料台を微小試料台ホルダに固定した上、分析装置等のステージ上に取り付ける従来のものとは全く相違する。

このように、本発明の微小試料台は、従来のものに比して、単一のディスクリート部材として構成され、それゆえに、微小部材を微小試料台ホルダに固定する作業がないので、きわめて効率的に生産をすることが可能であり、また、コスト的なメリットを得ることもできる。

【0019】

図13は、シリコン基板からなる半導体ウエハ1に本発明の微小試料台100が多数形成され、半導体ウエハ1から分離する直前の状態を示す。半導体ウエハ1から分離する直前の各微小試料台100は、その周囲が半導体ウエハ1に形成された貫通溝2により該半導体ウエハ1の周囲の領域と分離されており、それぞれ、1箇所の支持部3によってのみ、半導体ウエハ1の周囲と連結されている。

【0020】

半導体ウエハから分離する前の各微小試料台100は、それぞれ、上下2個を一対として配列されており、各一対の微小試料台100、100は、貫通溝2の中心線、換言すれば、微小試料台基部10、10の上面13側の中心線、を対称軸とする線対称に形成されている。

半導体ウエハ1は、上面が(110)面であり、(110)面のフラット面4を有しており、各一対の微小試料台100は、フラット面4に対して45度傾斜した軸と平行に配列されている。

次に、図1および図2に図示された微小試料台100を製造する方法の一例を図3乃至図8を参照して説明する。

【0021】

図3(a)〜(f)および図4(g)〜(k)は、それぞれ、図13における一対の微小試料台100、100が形成された領域を含む二点差線で囲む領域A付近におけるIII―III線切断断面図であり、図5(a)〜(c)、図6(d)〜(f)、図7(g)および(h)、図8(i)〜(k)は、領域A近傍の平面図である。図3(a)〜(f)および図4(g)〜(k)は、それぞれ、図5(a)〜(c)、図6(d)〜(f)、図7(g)および(h)、図8(i)〜(k)と対応する図面である。

【0022】

先ず、半導体ウエハ(以下、半導体基板という)1の裏面(他面)および表面(一面)に窒化シリコン等の無機材料からなる薄膜31、32をCVD法により成膜する(図3(a)および図5(a)参照)。

【0023】

次に、半導体基板1の裏面に形成された薄膜31の全面にフォトレジストを塗布し、露光用マスクを介して露光し、その後、現像を行って、第1のマスク41を形成する。(図3(b)および図5(b)参照)。第1のマスク41の形状は、図5(b)に図示される如く円形である。なお、フォトレジストの塗布からマスクを形成するまでの方法はフォトリソグラフ法として知られているものであり、以下、単にフォトリソグラフ法と記載して、その説明を、適宜、省略する。

【0024】

次に、第1のマスク41をマスクとして、C2F6を主ガスとするRIE(Reactive Ion Etching)法により、第1のマスク41の周囲の薄膜31を除去し、第1のマスク41下に第1のマスク41と同形状の基板エッチング用マスク51を形成する(図3(c)および図5(c)参照)。

【0025】

次に、第1のマスク41を除去する。第1のマスク41の除去は、例えば、酸素ガスを含むRIE法を用いる。そして、半導体基板1の上下を反転して、薄膜32を上方に向ける。この状態を、図3(d)および図6(d)に示す。

【0026】

次に、フォトリソグラフ法により薄膜32上に一対の第2のマスク42、42を形成し、該第2のマスク42、42をマスクとして薄膜32をパターニングして微小試料搭載用薄膜20、20を形成する。

この場合、基板エッチング用マスク51と微小試料搭載用薄膜20、20とを、図3(e)および図6(e)に図示される如く、基板エッチング用マスク51が一対の微小試料搭載用薄膜20の中の、一方の微小試料搭載用薄膜20の内部に対応する領域から、他方の微小試料搭載用薄膜20の内部に対応する領域に達するような大きさおよび位置関係にする。この後、第2のマスク42を、酸素ガスを用いたRIEにより除去して、図3(f)および図6(f)に図示されるように微小試料搭載用薄膜20、20を半導体基板1の表面側に露出する。

【0027】

次に、フォトリソグラフィ法を用いて、貫通溝2を形成する領域を除く半導体基板1の表面全体に第3のフォトレジスト43を形成し、ICP(Inductively Coupled Plasma)−RIE法により半導体基板1を厚さ方向に切断し、支持部3のみで周囲の半導体基板1と連結された微小試料台基部10を形成する(図4(g)および図7(g)参照)。

但し、この時点では、図7(g)に図示される如く、各微小試料台基部10は、対となる微小試料台基部10の上面13の間では連結されている。

そして、酸素ガスを用いたRIE法により第3のマスク43を除去する。

【0028】

次に、熱酸化炉に収容し、熱酸化を行うと、図4(h)および図7(h)に図示される如く、表面側の微小試料搭載用薄膜20を除く領域に酸化シリコン膜からなる第1のエッチングストッパ52(51、52は図4(h)参照)が形成され、裏面側の基板エッチング用マスク51を除く領域に酸化シリコン膜からなる第2のエッチングストッパ53(が形成され、また、試料台基部10の外周側面に酸化シリコン膜からなる第3のエッチングストッパ54が形成され、支持部3の周囲に第4のエッチングストッパ55が形成される。図9は、図7(h)を裏面側からみた拡大平面図である。

【0029】

次に、C2F6を主ガスとするRIE法により、裏面側の基板エッチング用マスク51を除去し、基板エッチング用マスク51下の半導体基板1の領域を露出する(図4(i)および図8(i)参照)。図10は、図8(i)を裏面側からみた拡大平面図である。

【0030】

この状態で、水酸化カリウム(KOH)の20〜30重量%水溶液中に浸漬すると基板エッチング用マスク51下の半導体基板1の領域がエッチングされる。このエッチングは、(111)面が残存する異方性エッチングである。

ここで、(111)面は、(110)面と平行な辺を有し、z軸(図10において紙面と垂直な方向)と交差する方向に傾斜する傾斜面となる面であり、フラット面4が(110)面であることから、フラット面4と垂直な面および平行な面に対し傾斜する斜面となる。また、対となる微小試料基部10、10は、(110)面に対し、45度傾斜した軸に平行な方向に配列され、基板エッチング用マスク51は、平面視で円弧状としたので、フラット面4と垂直方向および平行方向に拡大して進行する。

【0031】

すなわち、図2に示す如く、微小試料台基部10のV字状の溝11を形成する上側面11a、11aは(111)面であり、その頂角θは90度である。異方性エッチングは、微小試料搭載用薄膜20、20を裏出するように進行し、第1のエッチングストッパ52で規制される。この状態を、図4(j)および図8(j)に示す。また、図11は、図8(j)を裏面側からみた拡大平面図である。

なお、基板エッチング用マスク51は、平面視で円弧状なく、方形としてもよく、この場合も、異方性エッチングは、フラット面4と垂直方向および平行方向に拡大して進行する。

【0032】

この後、リンスをして、バッファード弗酸(BHF)で第1、第2、第3および第4のエッチングストッパ52、43、54、55を除去すると、図4(k)および図8(k)に図示するように、対となっている微小試料台基部10、10の間の部分が除去され、各微小試料台基部10が分離し、支持部3のみで半導体基板1と連結された図13に図示された状態となる。

なお、図12は図8(k)の状態を裏面側からみた拡大平面図である。

【0033】

この後、リンス、乾燥し、各微小試料台基部10の支持部3をエッチング等適宜な方法で切断することにより、図1および図2に示す微小試料台100が、同時に多数個得られる。

【0034】

以上の通り、この発明の微小試料台100は、半導体基板1の表面に成膜により微小試料搭載用薄膜20を形成するので、数百nm以下、特に、百nm以下の厚さに形成することができる。このため、微小試料を微小試料台に固定した後、Ga+ビーム等の荷電粒子ビームを照射して、0.1μm程度の厚さにする薄片化処理を行う際、微小試料台がスパッタされて、微小試料の表面に付着する異物の量を大幅に抑止することができる。

また、表面の凹凸が殆どない半導体基板1の表面に形成するので、その側面を平坦度の高いものとすることができる。

また、従来の如く、微小試料台100を試料台ホルダに固定することなく、直接、分析装置のステージに取り付けることができる構造に形成したので、生産性を大幅に向上することが可能であり、コスト的なメリットを得ることもできる、という効果を奏するものである。

【0035】

なお、上記実施形態では、各微小試料台基部10を(110)フラット面4に対し45度傾斜した方向に配列されるように形成する場合で説明した。

しかし、この発明は、各微小試料台基部10を(110)フラット面4に垂直または平行に配列されるように形成することもできる。

次に、そのような変形例について説明する。

【0036】

(変形例)

図14は、本発明の微小試料台の変形例を示す拡大斜視図である。

微小試料台200は、シリコン基板等の半導体基板からなる微小試料台基部60および試料搭載用薄膜20からなっている。試料搭載用薄膜20は、図1および図2に関して説明したものとほぼ同じであり、以下、同一の部材には、同一の参照番号を付してその説明を省略する。

【0037】

微小試料台基部60は、平面視で、方形形状の溝61をしている。この微小試料台基部60もシリコン基板で形成されており、溝61の上側面61aおよび左右の側面61b、61bは(111)面である。

すなわち、微小試料台基部60の裏面60aから微小試料搭載用薄膜20側に向かうに従い、徐々に、上昇または中心側に向かう傾斜面なっている。

【0038】

このような、微小試料台200を形成するには、微小試料台基部60が(110)フラット面4に対し、垂直方向または平行方向に配列されるように位置づければよい。

この変形例に示す微小試料台200も、半導体基板1の表面に成膜により微小試料搭載用薄膜60を形成するので、数百nm以下、特に、百nm以下の厚さに形成することができる。このため、微小試料を微小試料台に固定した後、Ga+ビーム等の荷電粒子ビームを照射して、0.1μm程度の厚さにする薄片化処理を行う際、微小試料台がスパッタされて、微小試料の表面に付着する異物の量を大幅に抑止することができる。

また、表面の凹凸が殆どない半導体基板1の表面に形成するので、その側面を平坦度の高いものとすることができる。

また、従来の如く、微小試料台200を試料台ホルダに固定することなく、直接、分析装置のステージに取り付けることができる構造に形成したので、生産性を大幅に向上することが可能であり、コスト的なメリットを得ることもできる、という効果を奏するものである。

【0039】

次に、上述した微小試料台100および200に微小試料を固定する方法につき、図15〜19と共に説明する。

図15において、70はシリコン基板等からなる微小試料である。微小試料70は、分析領域73の周囲をGaイオンビーム等で除去して溝72を形成したものである。この微小試料の上面には、マイクロプローブ75が固定されている。マイクロプローブ75は、微小試料を、母材であるデバイスから分離する前に、微小試料70の上面にマイクロプローブ75を押し当てた状態で、CVD方によりカーボン76を成膜して固定される。

【0040】

マイクロプローブ75が固定された状態で、微小試料70は、微小試料台100または200の微小試料搭載用薄膜20の上端面21に固定される。

微小試料台100または200と微小試料搭載用薄膜20との固定も、上記と同様に、CVD方により成膜したカーボン77によって行うことができる。

【0041】

なお、上記においては、微小試料70をマイクロプローブ75に固定した後、微小試料台100または200の微小試料搭載用薄膜20の上端面21に固定する方法で説明したが、微小試料70を、直接、ナノピンセットにより把持し、この状態のまま、微小試料搭載用薄膜20の上端面21に固定するようにしてもよい。

【0042】

図15に図示される如く、微小試料70が、微小試料台100または200の微小試料搭載用薄膜20の上端面21に固定されたら、イオンビームを照射してマイクロプローブを分離して図16の状態とする。

そして、この後、図示はしないが、微小試料70にGa+イオン等の荷電粒子をFIB法により照射して微小試料70を0.1μm程度の厚さになるまで薄片化する。

この薄片化工程において、本発明では、微小試料搭載用薄膜20が数百nm以下、特に、百nm程度以下の厚さしかないため、微小試料搭載用薄膜20がイオンビームによってスパッタされることがなく、したがって、異物が微小試料の表面に付着することが全くないか、あるいは少量しかない。

よって、分析時のバックグラウンドノイズを大幅に低減することが可能である。

【0043】

図17は、微小試料70を微小試料搭載用薄膜20の上端面に固定した状態の側面図である。

微小試料70は、を微小試料搭載用薄膜20の側面に固定することも可能である。

図18は、微小試料70を、微小試料搭載用薄膜20の、微小試料台基部10(または60)と反対面側の側面に固定した状態の側面図を示す。

また、図19は、微小試料70を、微小試料搭載用薄膜20の、微小試料台基部10(または60)側の側面に固定した状態の側面図を示す。

図18および図19においては、微小試料70は微小試料搭載用薄膜20の状端面よりも低い位置に固定されているものである。

図20は、微小試料70を、微小試料搭載用薄膜20の、微小試料台基部10(または60)と反対面側の側面に固定した場合において、微小試料70を微小試料搭載用薄膜20の上端面21よりも突き出して固定した状態の側面図である。

また、図21は、微小試料70を、微小試料搭載用薄膜20の、微小試料台基部10(または60)側の側面に固定した場合において、微小試料70を微小試料搭載用薄膜20の上端面21よりも突き出して固定した状態の側面図である。

【0044】

本発明の製造方法によれば、微小試料の薄片化工程において、微小試料の表面には、微小試料台の微粉が殆ど付着することはないが、仮に付着した場合には、例えば、Ar+ビームを微小試料台100または200の下方から微小試料70へ照射するイオンミリングにより除去することができる。この場合、微小試料の表面に付着する微粉の量はきわめて少ないので、この微小試料の表面からの異物除去工程は、従来よりも、遥かに短時間とすることができる。

【0045】

なお、上記実施形態では、半導体基板としてシリコン基板を用いた場合で出説明したが、半導体基板として、Ge等の元素半導体、あるいはGaAs、InP等の化合物半導体基板を用いることができる。

また、2個を一対として生産する方法で説明したが、個々に独立して形成することもできる。また、微小試料搭載用薄膜を窒化シリコン(SiN)により形成した場合で説明したが、SiO2、SiON等他の無機材料で形成することも可能である。この場合、半導体基板を構成する元素と同一の元素を有する無機材料で形成すると接着強度が大きくなりより好ましい。

【0046】

また、微小試料台基部10の外形を形成する工程を、半導体基板1の一面および他面に、微小試料搭載用マスク20および基板エッチング用マスク51を形成した後として説明したが、外形形状に切断した後、微小試料搭載用マスク20および基板エッチング用マスク51あるいはいずれか一方を形成するようにしてもよい。この場合、支持部が1箇所では後工程において強度が不足するようであれば、適宜、支持部の数を増加すればよい。

【0047】

また、本発明の微小試料台は、突出し状のガード部および該ガード部の上面から没入した溝部を有する半導体基板と、該半導体基板の一面に成膜により一体化され、半導体基板における溝部の最深部とガード部の上面との中間に上端面を有する微小試料搭載用薄膜と、を具備するものであればよい。

【0048】

また、本発明の微小試料台作成用基板は、それぞれが支持部において連結された多数の微小試料台基部を有する半導体ウエハと、各微小試料台基部の一面に成膜により形成され、少なくとも対応する微小試料基部の少なくとも一部の端面より突出す部分を有する微小試料搭載用薄膜と、を具備するものであればよい。

【0049】

また、本発明の微小試料台の製造方法は、半導体基板の一面に無機材料からなる薄膜を形成する工程と、薄膜を平坦な上端面を有する形状にパターニングして微小試料搭載用薄膜を形成する工程と、半導体基板を、微小試料搭載用薄膜の上端面よりも没入する溝部を有する形状にパターニングする工程と、を具備するものであればよい。

また、本発明の微小試料台の製造方法は、半導体基板の一面および他面に無機材料からなる薄膜を成膜する工程と、半導体基板の一面に成膜された薄膜をパターニングして微小試料搭載用薄膜を形成する工程と、半導体基板の他面に成膜された薄膜をパターニングして微小試料搭載用薄膜の内部に対応する領域から外部に対応する領域に配置された基板エッチング用マスクを形成する工程と、微小試料搭載用薄膜および基板エッチング用マスクを除く半導体基板の一面および他面にエッチングストッパを形成する工程と、基板エッチング用マスクを除去して他面の半導体基板を露出する工程と、該露出された半導体基板を半導体基板の他面側からエッチングする工程と、を具備するものであればよい。

【0050】

さらに、本発明の微小試料台の分析方法は、ガード部および該ガード部の上面から没入した溝部を有する半導体基板および該半導体基板の一面に成膜により一体化され、半導体基板における溝部の最深部とガード部の上面との中間に上端面を有する微小試料搭載用薄膜とを有する微小試料台を準備するステップと、微小試料台の微小試料搭載用薄膜に微小試料搭載用薄膜より厚さが厚い微小試料を固定するステップと、微小試料が固定された微小試料台を、直接、分析用装置の分析ステージに取り付けるステップと、を具備するものであればよい。

【符号の説明】

【0051】

半導体ウエハ(半導体基板) 1

貫通溝 2

支持部 3

フラット面 4

10、60 微小試料台基部

11 溝

11a、61a 上側面

13 上面(ガード部)

20 微小試料搭載用薄膜

21 上端面

31、32 薄膜

41 第1のマスク

42 第2のマスク

43 第3のマスク

51 基板エッチング用マスク

61 溝

61a、61b 側面

70 微小試料

100、200 微小試料台

【技術分野】

【0001】

この発明は、電子顕微鏡等により分析を行う試料を固定する微小試料台、微小試料台作成用基板および微小試料台を用いた分析方法に関する。

【背景技術】

【0002】

半導体ウエハの上面に形成された半導体素子やディスクリートの半導体デバイスを透過型電子顕微鏡(TEM)等により、分析あるいは観察(以下、観察を含めて分析という)を行うには、半導体素子や半導体デバイス等の分析エリアをエッチング法やFIB(Focused Ion Beam)により加工して微小試料を形成し、該微小試料を切り取ったうえ、該微小試料よりも大幅に大きい厚さの微小試料台に固定し、さらに、微小試料が固定された微小試料台を、上部にガード部が設けられたほぼ半円弧状のメッシュといわれる試料ホルダに固定したものを準備する。そして、微小試料台を介して微小試料が固定された試料ホルダをピンセット等により把持して、TEMのステージに取り付けて分析を行う。

【0003】

通常、微小試料台は金属製の基板を用い、試料ホルダは、シリコン基板や金属製の基板等を用いる。この、微小試料は、例えば、10μm×10μm×1μm(厚さ)程度のサイズにしたうえ、微小試料台の側面に固定される。

そして、微小試料台に微小試料を固定した後、Ga+イオン等の荷電粒子イオンを用いたFIB法にて微小試料を、一般的には、100nm程度の厚さにまで薄片化する。

【0004】

微小試料台または試料ホルダが金属製の場合、試料固定面の粗さが試料のサイズに対して、凹凸が大きいので、固定した試料の位置を確認するのが困難とあり、また、固定した試料が傾くために観察面を正確に位置あわせするのが困難となる。

そこで、微小試料台をシリコン基板で形成するようにしたものも知られている。(例えば、特許文献1参照)

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−185338号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記微小試料を薄片化する工程では、微小試料と共に微小試料台にもGaイオンビームが照射される。微小試料は厚さ1μmのものをほぼ0.1μm程度の厚さにする。これに対し、固定される試料ホルダは、100μm程度であり、微小試料の厚さとは桁違いに厚い。このため、イオンビームによってスパッタされた試料台の微粉が微小試料の表面に付着する。付着した微粉は、TEM分析時に斑点となり、バックグラウンドノイズとなって解像度低下等の原因となる。

試料台の厚さが厚いほど微小試料の表面に付着する微粉の量は増大するので、微小試料の厚さが厚いほどバックグラウンドノイズは大きくなって、分析におおきな障害となる。

【課題を解決するための手段】

【0007】

請求項1に記載の微小試料台は、突出し状のガード部および該ガード部の上面から没入した溝部を有する半導体基板と、前記半導体基板の一面に成膜により一体化され、前記半導体基板における前記溝部の最深部と前記ガード部の上面との中間に上端面を有する微小試料搭載用薄膜と、を具備し、前記半導体基板の前記溝部はV字形状であり、前記V字形状の溝の両側面は(111)面であることを特徴とする。

請求項2に記載の微小試料台は、請求項1に記載の微小試料台において、前記半導体基板はシリコン基板であり、前記微小試料搭載用薄膜はシリコンを含む無機材料からなることを特徴とする。

請求項3に記載の微小試料台は、請求項2に記載の微小試料台において、前記微小試料搭載用薄膜は、窒化シリコンからなることを特徴とする。

請求項4に記載の微小試料台は、請求項1乃至3のいずれか1項に記載の微小試料台において、前記微小試料搭載用薄膜は、その厚さが数百nm以下であることを特徴とする。

請求項5に記載の微小試料台は、請求項4に記載の微小試料台において、前記微小試料搭載用薄膜は、その厚さが百nm以下であることを特徴とする。

【0008】

請求項6に記載の微小試料台作成用基板は、半導体ウエハに複数の微小試料台が形成された微小試料台作成用基板であって、前記微小試料台は、突出し状のガード部および該ガード部の上面から没入した溝部を有する前記半導体ウエハの一部により構成される半導体基板と、前記半導体基板の一面に成膜により一体化され、前記半導体基板における前記溝部の最深部と前記ガード部の上面との中間に上端面を有する微小試料搭載用薄膜と、を具備し、前記半導体基板の前記溝部はV字形状であり、前記V字形状の溝の両側面は(111)面であることを特徴とする。

【0009】

請求項7に記載の微小試料台作成用基板は、請求項6に記載の微小試料台用作成基板において、前記微小試料台は、前記ガード部の上面を対向して、線対称に対として半導体ウエハに配列されていることを特徴とする。

【0010】

請求項8に記載の微小試料台作成用基板は請求項7に記載の微小試料台作成基板において、前記半導体ウエハは、外周面に(110)面のフラット面を有し、前記微小試料台は、対として配置された前記微小試料台の線対称軸が前記フラット面に対して45度傾斜するように配列されていることを特徴とする。

【0011】

請求項9に記載の微小試料台を用いた分析方法は、請求項1乃至5のいずれか1項に記載の微小試料台を準備するステップと、前記微小試料台の前記微小試料搭載用薄膜に前記微小試料搭載用薄膜より厚さが厚い微小試料を固定するステップと、前記微小試料が固定された微小試料台を、直接、分析用装置の分析ステージに取り付けるステップと、を具備することを特徴とする。

請求項10に記載の微小試料台の分析方法は、請求項9に記載の微小試料台を用いた分析方法において、前記微小試料台の前記微小試料搭載用薄膜に前記微小試料搭載用薄膜より厚さが厚い微小試料を固定するステップは、前記微小試料搭載用薄膜の前記上端面上に前記微小試料を固定する工程を含むことを特徴とする。

【発明の効果】

【0012】

この発明によれば、半導体基板の一面に成膜により該半導体基板に一体化された微小試料搭載用薄膜を形成するので、微小試料の固定部を該微小試料よりも薄いものとすることが可能となり、微小試料を薄片化するために荷電粒子ビームを照射しても、微小試料台がスパッタされて微小試料に付着する異物を低減する効果を奏する。

【図面の簡単な説明】

【0013】

【図1】この発明の微小試料台を表面側からみた拡大斜視図。

【図2】図1の微小試料台を裏面側からみた拡大斜視図

【図3】(a)〜(f)は、図1および図2に示す微小試料台の製造方法を説明するための拡大断面図。

【図4】(g)〜(k)は、図3(f)に続く微小試料台の製造方法を説明するための拡大断面図。

【図5】(a)〜(c)は、図1および図2に示す微小試料台の製造方法を説明するための拡大平面図であり、それぞれ、図3(a)〜(c)に対応する。

【図6】(d)〜(f)は、図5(c)に続く微小試料台の製造方法を説明するための拡大平面図であり、それぞれ、図3(d)〜(f)に対応する。

【図7】(g)および(h)は、図5(f)に続く微小試料台の製造方法を説明するための拡大平面図であり、それぞれ、図4(g)および(h)に対応する。

【図8】(i)〜(k)は、図5(h)に続く微小試料台の製造方法を説明するための拡大平面図であり、それぞれ、図4(i)〜(k)に対応する。

【図9】図7(h)に図示された微小試料台を裏面側からみた拡大平面図。

【図10】図8(i)に図示された微小試料台を裏面側からみた拡大平面図。

【図11】図8(j)に図示された微小試料台を裏面側からみた拡大平面図。

【図12】図8(k)に図示された微小試料台を裏面側からみた拡大平面図。

【図13】図1および図2に示す微小試料台を半導体ウエハから分離する直前の状態を示す平面図。

【図14】この発明の変形例を示す拡大斜視図

【図15】この発明の微小試料にマイクロプローブを固定し、さらに微小試料台に固定した状態の一例を示す斜視図。

【図16】図15に示す状態からマイクロプローブを分離した状態の一例を示す斜視図。

【図17】この発明の微小試料台に微小試料を固定する一例を説明するための側面図。

【図18】この発明の微小試料台に微小試料を固定する第二の例を説明するための側面図。

【図19】この発明の微小試料台に微小試料を固定する第三の例を説明するための側面図。

【図20】この発明の微小試料台に微小試料を固定する第四の例を説明するための側面図。

【図21】この発明の微小試料台に微小試料を固定する第五の例を説明するための側面図。

【発明を実施するための形態】

【0014】

以下、この発明の微小試料台の実施形態の一例について、図1、図2を参照して説明する。

図1および図2はこの発明の微小試料台の実施の形態の一例を示す拡大斜視図であり、図1は表面側からみた斜視図、図2は図1を裏面側からみた斜視図である。

微小試料台100は、シリコン基板等の半導体基板からなる微小試料台基部10および窒化シリコン(SiN)等の無機材料からなる試料搭載用薄膜20からなっている。 微小試料台基部10は、平面視で、直径2〜4mmのほぼ半円弧形状をなしている。半円弧形状部の上部には、頂角θが90度のV字形状の溝11が形成されている。また、半円弧形状部の下面には、凹部12が形成されている。V字形状の溝11の頂部と凹部12の中心を結ぶ直線は、試料台基部10の中心を通る。この凹部12は、詳細は後述するが、半導体ウエハからこの微小試料台を分離する際、分離を容易にするために形成されたものである。

【0015】

試料搭載用薄膜20は、試料台基部の表面(一面)に、CVD(Chemical Vapor Deposition)法により形成されたものである。半導体基板からなる微小試料台基部10は、表面の平坦性が良好であり、この微小試料台基部10にCVD法により形成される微小試料搭載用薄膜20は、平坦性が高く、且つ、大変、薄く形成することができる。

限定する意味ではないが、微小試料搭載用薄膜20の厚さtは数百nm以下、特に、百nm程度以下とすることが可能であり、この微小試料台100に固定される微小試料の厚さよりも薄くすることが可能である。

【0016】

通常、微小試料は、微小試料台100に固定する前には、5μm程度の厚さを有しており、微小試料台に固定した後、Ga+ビーム等の荷電粒子ビームを照射して、0.1μm程度の厚さにする薄片化処理を行う。この際、微小試料台がスパッタされて微小試料の表面に異物として付着して、分析をする際のバックグラウンドノイズとなる。しかし、この発明では、微小試料搭載用薄膜20が大変薄いので、微小試料に付着する異物の量を大幅に抑止することができる。

【0017】

V字形状の溝11の上側面11a、11aは、シリコンの(111)面となっており、微小試料搭載用薄膜20側に向かって上昇する傾斜面となっている。微小試料台基部10の上面13は、微小試料搭載用薄膜20の上端面21よりも高い位置にある。換言すれば、微小試料搭載用薄膜20の上端面21は、V字形状の溝11の最深部である頂部と上面13の中間に位置づけられている。

微小試料台基部10が微小試料搭載用薄膜20の上端面21よりも突き出して形成された突出し部を有するのは、微小試料搭載用薄膜20に固定された微小試料を分析する作業において、微小試料に分析装置等が衝突するのをガードするためである。すなわち、微小試料台基部10の微小試料搭載用薄膜20よりも高い部分はガード部となっている。

【0018】

そして、この微小試料台は、微小試料を固定した状態で、直接、分析装置等の分析のためのステージ上に取り付けられるもので、微小試料台を微小試料台ホルダに固定した上、分析装置等のステージ上に取り付ける従来のものとは全く相違する。

このように、本発明の微小試料台は、従来のものに比して、単一のディスクリート部材として構成され、それゆえに、微小部材を微小試料台ホルダに固定する作業がないので、きわめて効率的に生産をすることが可能であり、また、コスト的なメリットを得ることもできる。

【0019】

図13は、シリコン基板からなる半導体ウエハ1に本発明の微小試料台100が多数形成され、半導体ウエハ1から分離する直前の状態を示す。半導体ウエハ1から分離する直前の各微小試料台100は、その周囲が半導体ウエハ1に形成された貫通溝2により該半導体ウエハ1の周囲の領域と分離されており、それぞれ、1箇所の支持部3によってのみ、半導体ウエハ1の周囲と連結されている。

【0020】

半導体ウエハから分離する前の各微小試料台100は、それぞれ、上下2個を一対として配列されており、各一対の微小試料台100、100は、貫通溝2の中心線、換言すれば、微小試料台基部10、10の上面13側の中心線、を対称軸とする線対称に形成されている。

半導体ウエハ1は、上面が(110)面であり、(110)面のフラット面4を有しており、各一対の微小試料台100は、フラット面4に対して45度傾斜した軸と平行に配列されている。

次に、図1および図2に図示された微小試料台100を製造する方法の一例を図3乃至図8を参照して説明する。

【0021】

図3(a)〜(f)および図4(g)〜(k)は、それぞれ、図13における一対の微小試料台100、100が形成された領域を含む二点差線で囲む領域A付近におけるIII―III線切断断面図であり、図5(a)〜(c)、図6(d)〜(f)、図7(g)および(h)、図8(i)〜(k)は、領域A近傍の平面図である。図3(a)〜(f)および図4(g)〜(k)は、それぞれ、図5(a)〜(c)、図6(d)〜(f)、図7(g)および(h)、図8(i)〜(k)と対応する図面である。

【0022】

先ず、半導体ウエハ(以下、半導体基板という)1の裏面(他面)および表面(一面)に窒化シリコン等の無機材料からなる薄膜31、32をCVD法により成膜する(図3(a)および図5(a)参照)。

【0023】

次に、半導体基板1の裏面に形成された薄膜31の全面にフォトレジストを塗布し、露光用マスクを介して露光し、その後、現像を行って、第1のマスク41を形成する。(図3(b)および図5(b)参照)。第1のマスク41の形状は、図5(b)に図示される如く円形である。なお、フォトレジストの塗布からマスクを形成するまでの方法はフォトリソグラフ法として知られているものであり、以下、単にフォトリソグラフ法と記載して、その説明を、適宜、省略する。

【0024】

次に、第1のマスク41をマスクとして、C2F6を主ガスとするRIE(Reactive Ion Etching)法により、第1のマスク41の周囲の薄膜31を除去し、第1のマスク41下に第1のマスク41と同形状の基板エッチング用マスク51を形成する(図3(c)および図5(c)参照)。

【0025】

次に、第1のマスク41を除去する。第1のマスク41の除去は、例えば、酸素ガスを含むRIE法を用いる。そして、半導体基板1の上下を反転して、薄膜32を上方に向ける。この状態を、図3(d)および図6(d)に示す。

【0026】

次に、フォトリソグラフ法により薄膜32上に一対の第2のマスク42、42を形成し、該第2のマスク42、42をマスクとして薄膜32をパターニングして微小試料搭載用薄膜20、20を形成する。

この場合、基板エッチング用マスク51と微小試料搭載用薄膜20、20とを、図3(e)および図6(e)に図示される如く、基板エッチング用マスク51が一対の微小試料搭載用薄膜20の中の、一方の微小試料搭載用薄膜20の内部に対応する領域から、他方の微小試料搭載用薄膜20の内部に対応する領域に達するような大きさおよび位置関係にする。この後、第2のマスク42を、酸素ガスを用いたRIEにより除去して、図3(f)および図6(f)に図示されるように微小試料搭載用薄膜20、20を半導体基板1の表面側に露出する。

【0027】

次に、フォトリソグラフィ法を用いて、貫通溝2を形成する領域を除く半導体基板1の表面全体に第3のフォトレジスト43を形成し、ICP(Inductively Coupled Plasma)−RIE法により半導体基板1を厚さ方向に切断し、支持部3のみで周囲の半導体基板1と連結された微小試料台基部10を形成する(図4(g)および図7(g)参照)。

但し、この時点では、図7(g)に図示される如く、各微小試料台基部10は、対となる微小試料台基部10の上面13の間では連結されている。

そして、酸素ガスを用いたRIE法により第3のマスク43を除去する。

【0028】

次に、熱酸化炉に収容し、熱酸化を行うと、図4(h)および図7(h)に図示される如く、表面側の微小試料搭載用薄膜20を除く領域に酸化シリコン膜からなる第1のエッチングストッパ52(51、52は図4(h)参照)が形成され、裏面側の基板エッチング用マスク51を除く領域に酸化シリコン膜からなる第2のエッチングストッパ53(が形成され、また、試料台基部10の外周側面に酸化シリコン膜からなる第3のエッチングストッパ54が形成され、支持部3の周囲に第4のエッチングストッパ55が形成される。図9は、図7(h)を裏面側からみた拡大平面図である。

【0029】

次に、C2F6を主ガスとするRIE法により、裏面側の基板エッチング用マスク51を除去し、基板エッチング用マスク51下の半導体基板1の領域を露出する(図4(i)および図8(i)参照)。図10は、図8(i)を裏面側からみた拡大平面図である。

【0030】

この状態で、水酸化カリウム(KOH)の20〜30重量%水溶液中に浸漬すると基板エッチング用マスク51下の半導体基板1の領域がエッチングされる。このエッチングは、(111)面が残存する異方性エッチングである。

ここで、(111)面は、(110)面と平行な辺を有し、z軸(図10において紙面と垂直な方向)と交差する方向に傾斜する傾斜面となる面であり、フラット面4が(110)面であることから、フラット面4と垂直な面および平行な面に対し傾斜する斜面となる。また、対となる微小試料基部10、10は、(110)面に対し、45度傾斜した軸に平行な方向に配列され、基板エッチング用マスク51は、平面視で円弧状としたので、フラット面4と垂直方向および平行方向に拡大して進行する。

【0031】

すなわち、図2に示す如く、微小試料台基部10のV字状の溝11を形成する上側面11a、11aは(111)面であり、その頂角θは90度である。異方性エッチングは、微小試料搭載用薄膜20、20を裏出するように進行し、第1のエッチングストッパ52で規制される。この状態を、図4(j)および図8(j)に示す。また、図11は、図8(j)を裏面側からみた拡大平面図である。

なお、基板エッチング用マスク51は、平面視で円弧状なく、方形としてもよく、この場合も、異方性エッチングは、フラット面4と垂直方向および平行方向に拡大して進行する。

【0032】

この後、リンスをして、バッファード弗酸(BHF)で第1、第2、第3および第4のエッチングストッパ52、43、54、55を除去すると、図4(k)および図8(k)に図示するように、対となっている微小試料台基部10、10の間の部分が除去され、各微小試料台基部10が分離し、支持部3のみで半導体基板1と連結された図13に図示された状態となる。

なお、図12は図8(k)の状態を裏面側からみた拡大平面図である。

【0033】

この後、リンス、乾燥し、各微小試料台基部10の支持部3をエッチング等適宜な方法で切断することにより、図1および図2に示す微小試料台100が、同時に多数個得られる。

【0034】

以上の通り、この発明の微小試料台100は、半導体基板1の表面に成膜により微小試料搭載用薄膜20を形成するので、数百nm以下、特に、百nm以下の厚さに形成することができる。このため、微小試料を微小試料台に固定した後、Ga+ビーム等の荷電粒子ビームを照射して、0.1μm程度の厚さにする薄片化処理を行う際、微小試料台がスパッタされて、微小試料の表面に付着する異物の量を大幅に抑止することができる。

また、表面の凹凸が殆どない半導体基板1の表面に形成するので、その側面を平坦度の高いものとすることができる。

また、従来の如く、微小試料台100を試料台ホルダに固定することなく、直接、分析装置のステージに取り付けることができる構造に形成したので、生産性を大幅に向上することが可能であり、コスト的なメリットを得ることもできる、という効果を奏するものである。

【0035】

なお、上記実施形態では、各微小試料台基部10を(110)フラット面4に対し45度傾斜した方向に配列されるように形成する場合で説明した。

しかし、この発明は、各微小試料台基部10を(110)フラット面4に垂直または平行に配列されるように形成することもできる。

次に、そのような変形例について説明する。

【0036】

(変形例)

図14は、本発明の微小試料台の変形例を示す拡大斜視図である。

微小試料台200は、シリコン基板等の半導体基板からなる微小試料台基部60および試料搭載用薄膜20からなっている。試料搭載用薄膜20は、図1および図2に関して説明したものとほぼ同じであり、以下、同一の部材には、同一の参照番号を付してその説明を省略する。

【0037】

微小試料台基部60は、平面視で、方形形状の溝61をしている。この微小試料台基部60もシリコン基板で形成されており、溝61の上側面61aおよび左右の側面61b、61bは(111)面である。

すなわち、微小試料台基部60の裏面60aから微小試料搭載用薄膜20側に向かうに従い、徐々に、上昇または中心側に向かう傾斜面なっている。

【0038】

このような、微小試料台200を形成するには、微小試料台基部60が(110)フラット面4に対し、垂直方向または平行方向に配列されるように位置づければよい。

この変形例に示す微小試料台200も、半導体基板1の表面に成膜により微小試料搭載用薄膜60を形成するので、数百nm以下、特に、百nm以下の厚さに形成することができる。このため、微小試料を微小試料台に固定した後、Ga+ビーム等の荷電粒子ビームを照射して、0.1μm程度の厚さにする薄片化処理を行う際、微小試料台がスパッタされて、微小試料の表面に付着する異物の量を大幅に抑止することができる。

また、表面の凹凸が殆どない半導体基板1の表面に形成するので、その側面を平坦度の高いものとすることができる。

また、従来の如く、微小試料台200を試料台ホルダに固定することなく、直接、分析装置のステージに取り付けることができる構造に形成したので、生産性を大幅に向上することが可能であり、コスト的なメリットを得ることもできる、という効果を奏するものである。

【0039】

次に、上述した微小試料台100および200に微小試料を固定する方法につき、図15〜19と共に説明する。

図15において、70はシリコン基板等からなる微小試料である。微小試料70は、分析領域73の周囲をGaイオンビーム等で除去して溝72を形成したものである。この微小試料の上面には、マイクロプローブ75が固定されている。マイクロプローブ75は、微小試料を、母材であるデバイスから分離する前に、微小試料70の上面にマイクロプローブ75を押し当てた状態で、CVD方によりカーボン76を成膜して固定される。

【0040】

マイクロプローブ75が固定された状態で、微小試料70は、微小試料台100または200の微小試料搭載用薄膜20の上端面21に固定される。

微小試料台100または200と微小試料搭載用薄膜20との固定も、上記と同様に、CVD方により成膜したカーボン77によって行うことができる。

【0041】

なお、上記においては、微小試料70をマイクロプローブ75に固定した後、微小試料台100または200の微小試料搭載用薄膜20の上端面21に固定する方法で説明したが、微小試料70を、直接、ナノピンセットにより把持し、この状態のまま、微小試料搭載用薄膜20の上端面21に固定するようにしてもよい。

【0042】

図15に図示される如く、微小試料70が、微小試料台100または200の微小試料搭載用薄膜20の上端面21に固定されたら、イオンビームを照射してマイクロプローブを分離して図16の状態とする。

そして、この後、図示はしないが、微小試料70にGa+イオン等の荷電粒子をFIB法により照射して微小試料70を0.1μm程度の厚さになるまで薄片化する。

この薄片化工程において、本発明では、微小試料搭載用薄膜20が数百nm以下、特に、百nm程度以下の厚さしかないため、微小試料搭載用薄膜20がイオンビームによってスパッタされることがなく、したがって、異物が微小試料の表面に付着することが全くないか、あるいは少量しかない。

よって、分析時のバックグラウンドノイズを大幅に低減することが可能である。

【0043】

図17は、微小試料70を微小試料搭載用薄膜20の上端面に固定した状態の側面図である。

微小試料70は、を微小試料搭載用薄膜20の側面に固定することも可能である。

図18は、微小試料70を、微小試料搭載用薄膜20の、微小試料台基部10(または60)と反対面側の側面に固定した状態の側面図を示す。

また、図19は、微小試料70を、微小試料搭載用薄膜20の、微小試料台基部10(または60)側の側面に固定した状態の側面図を示す。

図18および図19においては、微小試料70は微小試料搭載用薄膜20の状端面よりも低い位置に固定されているものである。

図20は、微小試料70を、微小試料搭載用薄膜20の、微小試料台基部10(または60)と反対面側の側面に固定した場合において、微小試料70を微小試料搭載用薄膜20の上端面21よりも突き出して固定した状態の側面図である。

また、図21は、微小試料70を、微小試料搭載用薄膜20の、微小試料台基部10(または60)側の側面に固定した場合において、微小試料70を微小試料搭載用薄膜20の上端面21よりも突き出して固定した状態の側面図である。

【0044】

本発明の製造方法によれば、微小試料の薄片化工程において、微小試料の表面には、微小試料台の微粉が殆ど付着することはないが、仮に付着した場合には、例えば、Ar+ビームを微小試料台100または200の下方から微小試料70へ照射するイオンミリングにより除去することができる。この場合、微小試料の表面に付着する微粉の量はきわめて少ないので、この微小試料の表面からの異物除去工程は、従来よりも、遥かに短時間とすることができる。

【0045】

なお、上記実施形態では、半導体基板としてシリコン基板を用いた場合で出説明したが、半導体基板として、Ge等の元素半導体、あるいはGaAs、InP等の化合物半導体基板を用いることができる。

また、2個を一対として生産する方法で説明したが、個々に独立して形成することもできる。また、微小試料搭載用薄膜を窒化シリコン(SiN)により形成した場合で説明したが、SiO2、SiON等他の無機材料で形成することも可能である。この場合、半導体基板を構成する元素と同一の元素を有する無機材料で形成すると接着強度が大きくなりより好ましい。

【0046】

また、微小試料台基部10の外形を形成する工程を、半導体基板1の一面および他面に、微小試料搭載用マスク20および基板エッチング用マスク51を形成した後として説明したが、外形形状に切断した後、微小試料搭載用マスク20および基板エッチング用マスク51あるいはいずれか一方を形成するようにしてもよい。この場合、支持部が1箇所では後工程において強度が不足するようであれば、適宜、支持部の数を増加すればよい。

【0047】

また、本発明の微小試料台は、突出し状のガード部および該ガード部の上面から没入した溝部を有する半導体基板と、該半導体基板の一面に成膜により一体化され、半導体基板における溝部の最深部とガード部の上面との中間に上端面を有する微小試料搭載用薄膜と、を具備するものであればよい。

【0048】

また、本発明の微小試料台作成用基板は、それぞれが支持部において連結された多数の微小試料台基部を有する半導体ウエハと、各微小試料台基部の一面に成膜により形成され、少なくとも対応する微小試料基部の少なくとも一部の端面より突出す部分を有する微小試料搭載用薄膜と、を具備するものであればよい。

【0049】

また、本発明の微小試料台の製造方法は、半導体基板の一面に無機材料からなる薄膜を形成する工程と、薄膜を平坦な上端面を有する形状にパターニングして微小試料搭載用薄膜を形成する工程と、半導体基板を、微小試料搭載用薄膜の上端面よりも没入する溝部を有する形状にパターニングする工程と、を具備するものであればよい。

また、本発明の微小試料台の製造方法は、半導体基板の一面および他面に無機材料からなる薄膜を成膜する工程と、半導体基板の一面に成膜された薄膜をパターニングして微小試料搭載用薄膜を形成する工程と、半導体基板の他面に成膜された薄膜をパターニングして微小試料搭載用薄膜の内部に対応する領域から外部に対応する領域に配置された基板エッチング用マスクを形成する工程と、微小試料搭載用薄膜および基板エッチング用マスクを除く半導体基板の一面および他面にエッチングストッパを形成する工程と、基板エッチング用マスクを除去して他面の半導体基板を露出する工程と、該露出された半導体基板を半導体基板の他面側からエッチングする工程と、を具備するものであればよい。

【0050】

さらに、本発明の微小試料台の分析方法は、ガード部および該ガード部の上面から没入した溝部を有する半導体基板および該半導体基板の一面に成膜により一体化され、半導体基板における溝部の最深部とガード部の上面との中間に上端面を有する微小試料搭載用薄膜とを有する微小試料台を準備するステップと、微小試料台の微小試料搭載用薄膜に微小試料搭載用薄膜より厚さが厚い微小試料を固定するステップと、微小試料が固定された微小試料台を、直接、分析用装置の分析ステージに取り付けるステップと、を具備するものであればよい。

【符号の説明】

【0051】

半導体ウエハ(半導体基板) 1

貫通溝 2

支持部 3

フラット面 4

10、60 微小試料台基部

11 溝

11a、61a 上側面

13 上面(ガード部)

20 微小試料搭載用薄膜

21 上端面

31、32 薄膜

41 第1のマスク

42 第2のマスク

43 第3のマスク

51 基板エッチング用マスク

61 溝

61a、61b 側面

70 微小試料

100、200 微小試料台

【特許請求の範囲】

【請求項1】

突出し状のガード部および該ガード部の上面から没入した溝部を有する半導体基板と、

前記半導体基板の一面に成膜により一体化され、前記半導体基板における前記溝部の最深部と前記ガード部の上面との中間に上端面を有する微小試料搭載用薄膜と、を具備し、

前記半導体基板の前記溝部はV字形状であり、前記V字形状の溝の両側面は(111)面であることを特徴とする微小試料台。

【請求項2】

請求項1に記載の微小試料台において、前記半導体基板はシリコン基板であり、前記微小試料搭載用薄膜はシリコンを含む無機材料からなることを特徴とする微小試料台。

【請求項3】

請求項2に記載の微小試料台において、前記微小試料搭載用薄膜は、窒化シリコンからなることを特徴とする微小試料台。

【請求項4】

請求項1乃至3のいずれか1項に記載の微小試料台において、前記微小試料搭載用薄膜は、その厚さが数百nm以下であることを特徴とする微小試料台。

【請求項5】

請求項4に記載の微小試料台において、前記微小試料搭載用薄膜は、その厚さが百nm以下であることを特徴とする微小試料台。

【請求項6】

半導体ウエハに複数の微小試料台が形成された微小試料台作成用基板であって、前記微小試料台は、

突出し状のガード部および該ガード部の上面から没入した溝部を有する前記半導体ウエハの一部により構成される半導体基板と、

前記半導体基板の一面に成膜により一体化され、前記半導体基板における前記溝部の最深部と前記ガード部の上面との中間に上端面を有する微小試料搭載用薄膜と、を具備し、

前記半導体基板の前記溝部はV字形状であり、前記V字形状の溝の両側面は(111)面であることを特徴とする微小試料台用作成基板。

【請求項7】

請求項6に記載の微小試料台用作成基板において、前記微小試料台は、前記ガード部の上面を対向して、線対称に対として半導体ウエハに配列されていることを特徴とする微小試料台作成用基板。

【請求項8】

請求項7に記載の微小試料台作成基板において、前記半導体ウエハは、外周面に(110)面のフラット面を有し、前記微小試料台は、対として配置された前記微小試料台の線対称軸が前記フラット面に対して45度傾斜するように配列されていることを特徴とする微小試料台作成基板。

【請求項9】

請求項1乃至5のいずれか1項に記載の微小試料台を準備するステップと、

前記微小試料台の前記微小試料搭載用薄膜に前記微小試料搭載用薄膜より厚さが厚い微小試料を固定するステップと、

前記微小試料が固定された微小試料台を、直接、分析用装置の分析ステージに取り付けるステップと、

を具備することを特徴とする微小試料台を用いた分析方法。

【請求項10】

請求項9に記載の微小試料台を用いた分析方法において、前記微小試料台の前記微小試料搭載用薄膜に前記微小試料搭載用薄膜より厚さが厚い微小試料を固定するステップは、前記微小試料搭載用薄膜の前記上端面上に前記微小試料を固定する工程を含むことを特徴とする微小試料台を用いた分析方法。

【請求項1】

突出し状のガード部および該ガード部の上面から没入した溝部を有する半導体基板と、

前記半導体基板の一面に成膜により一体化され、前記半導体基板における前記溝部の最深部と前記ガード部の上面との中間に上端面を有する微小試料搭載用薄膜と、を具備し、

前記半導体基板の前記溝部はV字形状であり、前記V字形状の溝の両側面は(111)面であることを特徴とする微小試料台。

【請求項2】

請求項1に記載の微小試料台において、前記半導体基板はシリコン基板であり、前記微小試料搭載用薄膜はシリコンを含む無機材料からなることを特徴とする微小試料台。

【請求項3】

請求項2に記載の微小試料台において、前記微小試料搭載用薄膜は、窒化シリコンからなることを特徴とする微小試料台。

【請求項4】

請求項1乃至3のいずれか1項に記載の微小試料台において、前記微小試料搭載用薄膜は、その厚さが数百nm以下であることを特徴とする微小試料台。

【請求項5】

請求項4に記載の微小試料台において、前記微小試料搭載用薄膜は、その厚さが百nm以下であることを特徴とする微小試料台。

【請求項6】

半導体ウエハに複数の微小試料台が形成された微小試料台作成用基板であって、前記微小試料台は、

突出し状のガード部および該ガード部の上面から没入した溝部を有する前記半導体ウエハの一部により構成される半導体基板と、

前記半導体基板の一面に成膜により一体化され、前記半導体基板における前記溝部の最深部と前記ガード部の上面との中間に上端面を有する微小試料搭載用薄膜と、を具備し、

前記半導体基板の前記溝部はV字形状であり、前記V字形状の溝の両側面は(111)面であることを特徴とする微小試料台用作成基板。

【請求項7】

請求項6に記載の微小試料台用作成基板において、前記微小試料台は、前記ガード部の上面を対向して、線対称に対として半導体ウエハに配列されていることを特徴とする微小試料台作成用基板。

【請求項8】

請求項7に記載の微小試料台作成基板において、前記半導体ウエハは、外周面に(110)面のフラット面を有し、前記微小試料台は、対として配置された前記微小試料台の線対称軸が前記フラット面に対して45度傾斜するように配列されていることを特徴とする微小試料台作成基板。

【請求項9】

請求項1乃至5のいずれか1項に記載の微小試料台を準備するステップと、

前記微小試料台の前記微小試料搭載用薄膜に前記微小試料搭載用薄膜より厚さが厚い微小試料を固定するステップと、

前記微小試料が固定された微小試料台を、直接、分析用装置の分析ステージに取り付けるステップと、

を具備することを特徴とする微小試料台を用いた分析方法。

【請求項10】

請求項9に記載の微小試料台を用いた分析方法において、前記微小試料台の前記微小試料搭載用薄膜に前記微小試料搭載用薄膜より厚さが厚い微小試料を固定するステップは、前記微小試料搭載用薄膜の前記上端面上に前記微小試料を固定する工程を含むことを特徴とする微小試料台を用いた分析方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2013−11610(P2013−11610A)

【公開日】平成25年1月17日(2013.1.17)

【国際特許分類】

【出願番号】特願2012−184171(P2012−184171)

【出願日】平成24年8月23日(2012.8.23)

【分割の表示】特願2009−121623(P2009−121623)の分割

【原出願日】平成21年5月20日(2009.5.20)

【出願人】(390022471)アオイ電子株式会社 (85)

【Fターム(参考)】

【公開日】平成25年1月17日(2013.1.17)

【国際特許分類】

【出願日】平成24年8月23日(2012.8.23)

【分割の表示】特願2009−121623(P2009−121623)の分割

【原出願日】平成21年5月20日(2009.5.20)

【出願人】(390022471)アオイ電子株式会社 (85)

【Fターム(参考)】

[ Back to top ]