微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子

【課題】10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供すること。

【解決手段】本発明の微細構造物の製造方法は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする。

【解決手段】本発明の微細構造物の製造方法は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トップダウン形成法とボトムアップ形成法とを併用して、10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能とする微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子に関する。

【背景技術】

【0002】

近年、ナノテクノロジーで総称される微細加工技術が大きく注目され、ナノサイズの微細構造物を加工する方法として、幾つかの方法が実用化されてきている。

例えば、大きなサイズの材料から始めてナノサイズの構造を生み出す形成法であるトップダウン形成法においては、超高電圧電子ビーム露光装置等を用いたリソグラフィ技術やAFM微細加工技術により、10nm程度の微細構造物を加工することができる(例えば、非特許文献1参照)。

また、小さなサイズの材料から始めてナノサイズの構造を生み出す形成法であるボトムアップ形成法においては、分子の堆積法により、数nm程度の微細構造物を加工することができる(例えば、非特許文献2参照)。

【0003】

しかしながら、前記トップダウン形成法により10nm程度の微細構造物を加工する場合、用いる装置が非常に高価となり、実施が容易でないという問題がある。

また、前記ボトムアップ形成法により微細構造物を加工する場合、前記微細構造物がある程度大きな加工領域を有するようになると、それら全体を加工することが容易でないという問題がある。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】E.B.Cooper,et.al,Appl.Phys.Lett.,75,3566(1999)

【非特許文献2】A.Hatzor et al.Science291 1019(2001)

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は、従来における前記諸問題を解決し、以下の目的を達成することを課題とする。即ち、本発明は、10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供することを目的とする。

【課題を解決するための手段】

【0006】

前記課題を解決するための手段としては、以下の通りである。即ち、

<1> トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする微細構造物の製造方法。

<2> 隣接する第1の構造体の間の最短距離をLとし、第2の構造体の堆積厚みをaとしたとき、L−2aで表される溝幅を有する溝を形成する前記<1>に記載の微細構造物の製造方法。

<3> Lが1nm〜1,000nmである前記<2>に記載の微細構造物の製造方法。

<4> aが、次式、0.1nm≦a<0.5Lの関係を満たす前記<2>から<3>のいずれかに記載の微細構造物の製造方法。

<5> トップダウン形成法が電子線リソグラフィ法である前記<1>から<4>のいずれかに記載の微細構造物の製造方法。

<6> ボトムアップ形成法が原子層堆積法である前記<1>から<5>のいずれかに記載の微細構造物の製造方法。

<7> 第1の構造体が金属電極である前記<1>から<6>のいずれかに記載の微細構造物の製造方法。

<8> 第2の構造体が絶縁膜である前記<1>から<7>のいずれかに記載の微細構造物の製造方法。

<9> 基板上に、第1の構造体と第2の構造体とを有する微細構造物であって、前記第1の構造体と前記第2の構造体とが、前記<1>から<8>のいずれかに記載の微細構造物の製造方法により製造されることを特徴とする微細構造物。

<10> 前記<9>に記載の微細構造物を有する電界効果型半導体素子であって、2つの第1の構造体が一対のソース電極とドレイン電極をなし、第2の構造体がゲート絶縁膜をなし、前記第2の構造体が有する溝にゲート電極が配されることを特徴とする電界効果型半導体素子。

【発明の効果】

【0007】

本発明によれば、従来技術における前記諸問題を解決することができ、10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供することができる。

【図面の簡単な説明】

【0008】

【図1】微細構造物の製造方法の概要を示す説明図(1)である。

【図2】微細構造物の製造方法の概要を示す説明図(2)である。

【図3】微細構造物の製造方法の概要を示す説明図(3)である。

【図4】微細構造物の製造方法の概要を示す説明図(4)である。

【図5】ソース電極及びドレイン電極が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真である。

【図6(a)】絶縁膜が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真である。

【図6(b)】図6(a)における微細構造物の俯瞰像を撮像した電子顕微鏡写真である。

【図7(a)】ゲート電極が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真である。

【図7(b)】図7(a)における微細構造物の俯瞰像を撮像した電子顕微鏡写真である。

【発明を実施するための形態】

【0009】

(微細構造物の製造方法)

本発明の微細構造物の製造方法は、少なくとも、第1の構造体形成工程と、第2の構造体形成工程とを含む。

【0010】

<第1の構造体形成工程>

前記第1の構造体形成工程は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する工程である。

【0011】

前記トップダウン形成法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、電子線リソグラフィー法、光露光法、液浸露光法、ナノインプリント法、AFM微細加工法等が挙げられるが、優れた位置精度で前記第1の構造体を容易に形成することができる観点から、電子線リソグラフィー法が好ましい。なお、この電子線リソグラフィー法による第1の構造体の形成は、例えば、公知の電子線描画装置を用いて実施することができる。

【0012】

前記基板としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、シリコン基板、ガリウムヒ素等の半導体基板、サファイア、石英等の絶縁基板が挙げられる。

【0013】

前記第1の構造体による構築物としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、金属電極が挙げられる。

前記第1の構造体の形成材料としては、前記トップダウン形成法による加工が可能である限り特に制限はなく、目的に応じて適宜選択することができ、例えば、前記構築物が金属電極である場合には、Al、Ag、Au、Ti、Pt、Ni、Pd、Pb、Co、Fe、Cu等を挙げることができる。

【0014】

前記基板上に前記第1の構造体を形成する間隔としては、特に制限はなく、目的に応じて適宜選択することができるが、隣接する前記第1の構造体の間の最短距離をLとしたとき、Lが1nm〜1,000nmである間隔とされることが好ましい。

Lを前記数値範囲に設定することで、後述する第2の構造体に形成される凹状の溝の溝幅を狭小化して調整することができるとともに、前記溝幅に対して比較的大きな数値範囲であることから、前記間隔をもって配される前記第1の構造体を、前記トップダウン形成法により位置精度良く、容易に形成することができる。

【0015】

<第2の構造体形成工程>

前記第2の構造体形成工程は、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する工程である。

【0016】

前記ボトムアップ形成法としては、前記基板上に形成材料を堆積させる方法であれば、特に制限はなく、目的に応じて適宜選択することができ、例えば、原子層堆積法(ALD法)、真空蒸着法、化学気相成長法(CVD法)、スパッタ堆積法等が挙げられるが、前記形成材料の堆積厚みを原子レベルの正確さで容易に制御可能である観点から、原子層堆積法が好ましい。なお、この原子層堆積法による第2の構造体の形成は、例えば、公知の原子層堆積装置を用いて実施することができる。

【0017】

前記第2の構造体による構築物としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、絶縁膜が挙げられる。

前記第2の構造体の形成材料としては、前記ボトムアップ形成法による堆積が可能である限り特に制限はなく、前記目的に応じて適宜選択することができ、例えば、前記構築物が絶縁膜である場合には、酸化アルミ、酸化シリコン、窒化シリコン、酸化ハフニウム等を挙げることができる。

【0018】

本発明の前記微細構造物の製造方法は、凸状に形成される前記第1の構造体と、隣接する前記第1の構造体の間に位置する前記基板とで凹状の形状をなす谷状の微細構造に対し、その形状に追従させるように前記第2の構造体の形成材料を堆積させることで、前記第2の構造体に溝を形成する。

このように形成される前記第2の構造体の溝としては、隣接する前記第1の構造体の間の間隔と、前記第2の構造体の堆積厚みとを調整することで、容易に10nmオーダーの溝幅を有するように形成することができる。

即ち、本発明の前記微細構造物の製造方法においては、前記トップダウン形成法又は前記ボトムアップ形成法により、直接的に10nmオーダーの溝幅を有する微細構造物を形成する必要はなく、この溝幅よりも大きなサイズで隣接する前記第1の構造体の間の間隔と、前記第2の構造体の堆積厚みとを調整することで、間接的に10nmオーダーの溝幅を有する前記第2の構造体を形成することが可能となる。

【0019】

前記溝の形成は、特に制限はないが、隣接する前記第1の構造体の間の最短距離(隣接する前記第1の構造体間の間隔)をLとし、前記第2の構造体の堆積厚みをaとしたとき、L−2aで表される溝幅を有するように実施することが好ましい。このように溝の形成を実施すれば、前記溝幅よりも大きなサイズで、前記Lと前記aとを調整することで、間接的に目的とする溝幅を容易に得ることができる。

このような溝の形成方法としては、前記基板に対して略垂直(厳密に垂直である必要はなく、テーパ状、逆テーパ状を含む)に立ち上がるように前記第1の構造体を形成し、形成される前記谷状の微細構造の形状に追従するように前記第2の構造体を形成することが挙げられ、前記トップダウン形成法及び前記ボトムアップ形成法によって実施することができる。

中でも、前記ボトムアップ形成法による前記第2の構造体の形成に関し、前記第2の構造体を前記原子層堆積法(ALD法)により形成することとすれば、堆積対象となる前記谷状の微細構造の表面に前記第2の構造体の形成材料を吸着させて、原子層を1層ずつ成長させることができ、つまり、前記谷状の微細構造における深さ方向及び幅方向のいずれの方向に対しても、前記第2の構造体を一様の堆積厚みで前記原子層を成長させることができ、前記第2の構造体を前記谷状の微細構造の形状に追従させ、これに沿う形で溝を形成することができる。

【0020】

前記aの大きさとしては、前記溝の溝幅に応じて、適宜選択することができるが、前記溝を微細な溝幅で形成する観点から、0.1nm≦a<0.5L(nm)の範囲で調整されることが好ましい。

【0021】

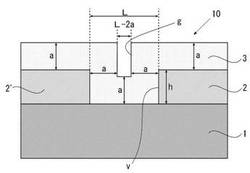

前記微細構造物の製造方法の概略を図1〜図4を用いて説明する。

先ず、基板1上に形成高さをhとして被加工層2Aを形成する(図1参照)。

【0022】

この基板1に対して、トップダウン形成法により、被加工層2Aを加工して2つの凸状の形状からなる第1の構造体2,2’を形成する(第1の構造体形成工程、図2参照)。

ここで、第1の構造体2,2’の形成は、公知のエッチング形成法により、第1の構造体2,2’を残すように被加工層2Aの一部をエッチング除去することで実施してもよいし、公知のリフトオフ形成法により、第1の構造体2,2’をリフトオフ形成して実施してもよい。

これにより、凸状に形成される2つの第1の構造体2,2’と、それらの間に位置する基板1の部分とで凹状の形状をなす谷状の微細構造vが形成される。ここでは、第1の構造体2,2’間の最短距離をLとして、第1の構造体2,2’の形成位置の調整を行う。

【0023】

次いで、ボトムアップ形成法により、第1の構造体2,2’が形成された基板1上に形成材料を堆積させ、第1の構造体2,2’の中間位置に凹状の溝gを有する第2の構造体3を形成する(第2の構造体形成工程、図3参照)。ここでは、第2の構造体3の堆積厚みをaとし、このaが0.5L(nm)未満であり、また、第1の構造体2,2’の形成高さhよりも小さくなるように調整している。

これにより、第2の構造体3において、L−2aの溝幅を有する溝gが形成される。

なお、第2の構造体3の堆積厚みaは、図3に示すように、谷状の微細構造vの深さ方向及び幅方向における第2の構造体3の堆積厚みを示す。

以上により、微細構造物10を製造する。

【0024】

更に微細構造物10から電界効果型半導体素子20を形成する場合について説明する(図4参照)。ここでは、基板1が半導体基板であり、第1の構造体2がドレイン電極であり、第1の構造体2’がソース電極であり、第2の構造体3がゲート絶縁膜であるように、微細構造物10が構成されている。

電界効果型半導体素子20は、この微細構造物10に対し、第2の構造体3に形成された溝gに電極材料を堆積させてゲート電極4を形成することで製造する。

これにより、ゲート長が極めて狭い電界効果型半導体素子20を容易に製造することができる。

【0025】

(微細構造物)

本発明の微細構造物は、少なくとも、基板上に、第1の構造体と第2の構造体とを有する。前記第1の構造体と、前記第2の構造体とは、前記本発明の微細構造物の製造方法により製造されることを特徴とする。

【0026】

(電界効果型半導体素子)

本発明の電界効果型半導体素子は、少なくとも本発明の前記微細構造物を有する。

前記微細構造物において、2つの前記第1の構造体が一対のソース電極とドレイン電極をなし、前記第2の構造体がゲート絶縁膜をなし、前記第2の構造体が有する溝にゲート電極が配されることを特徴とする。

【0027】

前記ゲート電極の形成方法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、真空蒸着法、化学気相成長法(CVD法)、原子層堆積法(ALD法)、スパッタリング法等が挙げられる。

また、ゲート電極の形成材料としては、特に制限はなく、目的に応じて適宜選択することができ、公知の電極材料を適用することができる。

【0028】

前記電界効果型半導体としては、極めて狭いゲート長で製造することが可能であるため、単電荷トランジスタ、単電荷メモリ等の単電荷デバイス(単電子デバイスと呼ばれることもある)として用いることに適している。このような単電荷デバイスとしては、チャネル部にカーボンナノチューブやグラフェンを適用したものが適用されてもよい。

【0029】

前記単電荷デバイスの一例として、単電荷メモリについて簡単に説明をする。

前記単電荷メモリとしては、通常、基板上にソース電極とドレイン電極とを有し、これらの電極の間にゲート絶縁膜を介して、極めて狭いゲート長を有するゲート電極とが配されてなり、前記ソース電極と前記ドレイン電極との間にチャネル部が形成される。

このような単電荷メモリにおいては、前記チャネル部近傍に電荷捕獲サイトが形成され、該電荷捕獲サイトに蓄積された電荷の影響により前記チャネル部の電気特性が制御可能とされる。即ち、前記電荷捕獲サイトへ電荷を注入を、前記ゲート電極のゲート長を極めて狭くすることで、クーロン反発作用により1つ1つ制御することができる。

前記チャネル部の電気特性は、ゲート電圧を高くしていくと、該チャネルを流れる電子がトンネル効果により前記電荷捕獲サイトに注入され、該チャネルに流れる電流値がシフトするように観察される。この1つ電荷の蓄積によりもたらされる電気特性の変化に基づき、メモリ動作が可能とされる。

以上のように、前記電界効果型半導体素子は、極めて狭いゲート長を有するため、そのようなゲート長を必要とする前記単電荷デバイスに特に有用に適用することができる。

【実施例】

【0030】

本発明の一実施例として、本発明の微細構造物の製造方法を適用して製造する電界効果型半導体素子を説明する。特に、前記電界効果型半導体素子の一種として、単層のカーボンナノチューブをチャネルとした単電荷メモリの実施例を説明する。

【0031】

<シリコン基板>

先ず、面方位が(100)のシリコン結晶に、1×1018cm−3の濃度で不純物(燐)を加えてあるシリコン基板を用意した。

このシリコン基板を熱酸化炉(光洋サーモシステムM270)で酸化し、表面に厚み315nmのSiO2酸化膜を形成した。

熱酸化炉による酸化条件としては、温度を1,000℃とし、炉内の雰囲気をwet酸化とし、酸化時間を35分とした。

【0032】

<カーボンナノチューブの形成>

次に、フォトレジスト材料(シプレイ社製、S1818)を前記シリコン基板のSiO2酸化膜上にスピンコート塗布してフォトレジスト層を形成した。スピンコート塗布の条件としては、回転数を4,000rpmとし、時間を30秒とした。

このフォトレジスト層に対して、露光機(Canon社製、1/4縮小投影露光器)を用いて露光した後、現像液(AZエレクトロニックマテリアルズ社製、AZ300MIF)により現像してレジストパターンを形成した。なお、現像時間は50秒とした。

【0033】

このレジストパターンが形成されたシリコン基板上に、真空蒸着装置(ノアシステムズ社製)を用いて触媒金属を一様に蒸着させた。前記触媒金属は、前記シリコン基板側からシリコン(厚み40nm)、モリブデン(厚み20nm)、鉄(厚み2nm)の順で形成したものである。

この状態で、フォトレジスト材料の剥離液(東京応化工業社製、ハクリ液106)に浸漬し、前記レジストパターンの凹部に形成された前記触媒金属を残して、前記シリコン基板の前記SiO2酸化膜上から前記フォトレジスト層及び該フォトレジスト層上の前記触媒金属を除去した。

【0034】

前記SiO2酸化膜上には、2つの前記触媒金属が凸状に形成されており、該触媒金属を触媒として、隣接する前記触媒金属間に架け渡されるようにカーボンナノチューブを成長させ、前記触媒金属間に単層のカーボンナノチューブを形成した。

具体的には、前記触媒金属が形成されたシリコン基板をカーボンナノチューブを成長させるための炉(Nano Device社製、Easy Tube System)内に配置した後、成長ガスとして、アルゴンでバブリングさせたエタノールを750sccm及び水素を500sccmの条件で導入し、成長温度を900℃として5分間、前記カーボンナノチューブを成長させた。

なお、「単層」とは、カーボンナノチューブの管構造が1層のカーボン層からなる状態を指す。また、「1sccm」は、Si単位で、1.69×10−4Pa・m3/secに換算される。

【0035】

<ソース電極及びドレイン電極の形成>

前記カーボンナノチューブを形成した前記シリコン基板上に、電子線レジスト(日本ゼオン社製、ZEP520A)をスピンコート塗布して電子線レジスト層を形成した。スピンコート塗布の条件としては、回転数を5,000rpmとし、時間を60秒とした。

この電子線レジスト層に対して、電子線描画装置(クレステック社製、CABL−9410TFNA)を用いて電子線描画を行った後、現像液(日本ゼオン社製、ZED−N50)により現像してレジストパターンを形成した。前記電子線描画は、一部の前記レジスト層を除去して、前記凸状の触媒金属の上面が前記電子レジスト層から露出するように実施した。なお、現像時間は60秒とした。

【0036】

このレジストパターンが形成されたシリコン基板上に、真空蒸着装置(ノアシステムズ社製)を用いて金属電極を一様に蒸着させた。前記金属電極は、前記シリコン基板側からチタン(厚み3nm)、金(厚み27nm)の順で形成したものである。

この状態で、前記電子線レジスト材料の剥離液(日本ゼオン社製、ZDMAC)に浸漬し、前記触媒金属の上面に形成された前記金属電極を残して、前記SiO2酸化膜上から前記電子線レジスト層及び該電子線レジスト層上の前記金属電極を除去し、前記シリコン基板上に2つの凸状の金属電極を形成した(第1の構造体形成工程)。ここでは、前記2つの金属電極間の最短距離Lを70nmとし、前記2つの金属電極をそれぞれ、ソース電極、ドレイン電極とした。

この様子を図5に示す。なお、図5は、ソース電極及びドレイン電極が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真である。

【0037】

<絶縁膜の形成>

この2つの金属電極が形成されたシリコン基板上に、原子層堆積装置(オックスフォードインスツルメンツ社製、FlexAl)を用いて絶縁膜を一様に堆積させた。前記絶縁膜は、前記シリコン基板側から酸化アルミニウム(厚み3nm)、窒化シリコン(厚み27nm)の順で形成し、堆積厚みaを30nmとしたものである。

その結果、前記2つの金属電極間の中間位置に、10nm(L−2a=10nm)の溝幅を有する溝が形成された前記絶縁膜を、前記シリコン基板上に形成した(第2の構造体形成工程)。

この様子を図6(a)、(b)に示す。なお、図6(a)は、絶縁膜が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真であり、図6(b)は、図6(a)における微細構造物の俯瞰像を撮像した電子顕微鏡写真である。

【0038】

<ゲート電極の形成>

前記絶縁膜上にフォトレジスト材料(シプレイ社製、S1818)をスピンコート塗布してフォトレジスト層を形成した。スピンコート塗布の条件としては、回転数を4,000rpmとし、時間を30秒とした。

このフォトレジスト層に対して、露光機(Canon社製、1/4縮小投影露光器)を用いて露光した後、現像液(AZエレクトロニックマテリアルズ社製、AZ300MIF)により現像してレジストパターンを形成した。前記レジストパターンの形成は、前記絶縁膜の溝を中心とした周辺部分における前記フォトレジスト層を除去し、前記絶縁膜の溝が露出するように実施した。なお、現像時間は50秒とした。

【0039】

このレジストパターンが形成された前記絶縁膜上に、真空蒸着装置(ノアシステムズ社製)を用いて金属電極を蒸着した。前記金属電極は、前記絶縁膜側からチタン、金の順で形成したものであり、一部が前記絶縁膜の溝に充填されるように配して、前記溝の溝幅(L−2a)をゲート長とするゲート電極とした。

この状態で、フォトレジスト材料の剥離液(東京応化工業社製、ハクリ液106)に浸漬し、前記溝に形成された前記ゲート電極を残して、前記絶縁膜上から前記フォトレジスト層及び該フォトレジスト層上の前記金属電極を除去した。

この様子を図7(a)、(b)に示す。なお、図7(a)は、ゲート電極が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真であり、図7(b)は、図7(a)における微細構造物の俯瞰像を撮像した電子顕微鏡写真である。

【0040】

以上により、実施例に係る電界効果型半導体素子として単電荷メモリを製造した。この単電荷メモリにおいては、ゲート長(L−2a)が10nmと、極めて微細に加工されているため、前記ゲート電極に対する電圧印可により1つ1つの電荷を制御して、チャネルとしての前記カーボンナノチューブに流れる電流の電流レベルをシフトさせることができ、単電荷のメモリ動作を可能とする。

【符号の説明】

【0041】

1 基板(半導体基板)

2A 被加工層

2 第1の構造体(ドレイン電極)

2’ 第1の構造体(ソース電極)

3 第2の構造体(ゲート絶縁膜)

4 ゲート電極

v 谷状の微細構造

g 溝

【技術分野】

【0001】

本発明は、トップダウン形成法とボトムアップ形成法とを併用して、10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能とする微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子に関する。

【背景技術】

【0002】

近年、ナノテクノロジーで総称される微細加工技術が大きく注目され、ナノサイズの微細構造物を加工する方法として、幾つかの方法が実用化されてきている。

例えば、大きなサイズの材料から始めてナノサイズの構造を生み出す形成法であるトップダウン形成法においては、超高電圧電子ビーム露光装置等を用いたリソグラフィ技術やAFM微細加工技術により、10nm程度の微細構造物を加工することができる(例えば、非特許文献1参照)。

また、小さなサイズの材料から始めてナノサイズの構造を生み出す形成法であるボトムアップ形成法においては、分子の堆積法により、数nm程度の微細構造物を加工することができる(例えば、非特許文献2参照)。

【0003】

しかしながら、前記トップダウン形成法により10nm程度の微細構造物を加工する場合、用いる装置が非常に高価となり、実施が容易でないという問題がある。

また、前記ボトムアップ形成法により微細構造物を加工する場合、前記微細構造物がある程度大きな加工領域を有するようになると、それら全体を加工することが容易でないという問題がある。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】E.B.Cooper,et.al,Appl.Phys.Lett.,75,3566(1999)

【非特許文献2】A.Hatzor et al.Science291 1019(2001)

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は、従来における前記諸問題を解決し、以下の目的を達成することを課題とする。即ち、本発明は、10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供することを目的とする。

【課題を解決するための手段】

【0006】

前記課題を解決するための手段としては、以下の通りである。即ち、

<1> トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする微細構造物の製造方法。

<2> 隣接する第1の構造体の間の最短距離をLとし、第2の構造体の堆積厚みをaとしたとき、L−2aで表される溝幅を有する溝を形成する前記<1>に記載の微細構造物の製造方法。

<3> Lが1nm〜1,000nmである前記<2>に記載の微細構造物の製造方法。

<4> aが、次式、0.1nm≦a<0.5Lの関係を満たす前記<2>から<3>のいずれかに記載の微細構造物の製造方法。

<5> トップダウン形成法が電子線リソグラフィ法である前記<1>から<4>のいずれかに記載の微細構造物の製造方法。

<6> ボトムアップ形成法が原子層堆積法である前記<1>から<5>のいずれかに記載の微細構造物の製造方法。

<7> 第1の構造体が金属電極である前記<1>から<6>のいずれかに記載の微細構造物の製造方法。

<8> 第2の構造体が絶縁膜である前記<1>から<7>のいずれかに記載の微細構造物の製造方法。

<9> 基板上に、第1の構造体と第2の構造体とを有する微細構造物であって、前記第1の構造体と前記第2の構造体とが、前記<1>から<8>のいずれかに記載の微細構造物の製造方法により製造されることを特徴とする微細構造物。

<10> 前記<9>に記載の微細構造物を有する電界効果型半導体素子であって、2つの第1の構造体が一対のソース電極とドレイン電極をなし、第2の構造体がゲート絶縁膜をなし、前記第2の構造体が有する溝にゲート電極が配されることを特徴とする電界効果型半導体素子。

【発明の効果】

【0007】

本発明によれば、従来技術における前記諸問題を解決することができ、10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供することができる。

【図面の簡単な説明】

【0008】

【図1】微細構造物の製造方法の概要を示す説明図(1)である。

【図2】微細構造物の製造方法の概要を示す説明図(2)である。

【図3】微細構造物の製造方法の概要を示す説明図(3)である。

【図4】微細構造物の製造方法の概要を示す説明図(4)である。

【図5】ソース電極及びドレイン電極が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真である。

【図6(a)】絶縁膜が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真である。

【図6(b)】図6(a)における微細構造物の俯瞰像を撮像した電子顕微鏡写真である。

【図7(a)】ゲート電極が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真である。

【図7(b)】図7(a)における微細構造物の俯瞰像を撮像した電子顕微鏡写真である。

【発明を実施するための形態】

【0009】

(微細構造物の製造方法)

本発明の微細構造物の製造方法は、少なくとも、第1の構造体形成工程と、第2の構造体形成工程とを含む。

【0010】

<第1の構造体形成工程>

前記第1の構造体形成工程は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する工程である。

【0011】

前記トップダウン形成法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、電子線リソグラフィー法、光露光法、液浸露光法、ナノインプリント法、AFM微細加工法等が挙げられるが、優れた位置精度で前記第1の構造体を容易に形成することができる観点から、電子線リソグラフィー法が好ましい。なお、この電子線リソグラフィー法による第1の構造体の形成は、例えば、公知の電子線描画装置を用いて実施することができる。

【0012】

前記基板としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、シリコン基板、ガリウムヒ素等の半導体基板、サファイア、石英等の絶縁基板が挙げられる。

【0013】

前記第1の構造体による構築物としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、金属電極が挙げられる。

前記第1の構造体の形成材料としては、前記トップダウン形成法による加工が可能である限り特に制限はなく、目的に応じて適宜選択することができ、例えば、前記構築物が金属電極である場合には、Al、Ag、Au、Ti、Pt、Ni、Pd、Pb、Co、Fe、Cu等を挙げることができる。

【0014】

前記基板上に前記第1の構造体を形成する間隔としては、特に制限はなく、目的に応じて適宜選択することができるが、隣接する前記第1の構造体の間の最短距離をLとしたとき、Lが1nm〜1,000nmである間隔とされることが好ましい。

Lを前記数値範囲に設定することで、後述する第2の構造体に形成される凹状の溝の溝幅を狭小化して調整することができるとともに、前記溝幅に対して比較的大きな数値範囲であることから、前記間隔をもって配される前記第1の構造体を、前記トップダウン形成法により位置精度良く、容易に形成することができる。

【0015】

<第2の構造体形成工程>

前記第2の構造体形成工程は、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する工程である。

【0016】

前記ボトムアップ形成法としては、前記基板上に形成材料を堆積させる方法であれば、特に制限はなく、目的に応じて適宜選択することができ、例えば、原子層堆積法(ALD法)、真空蒸着法、化学気相成長法(CVD法)、スパッタ堆積法等が挙げられるが、前記形成材料の堆積厚みを原子レベルの正確さで容易に制御可能である観点から、原子層堆積法が好ましい。なお、この原子層堆積法による第2の構造体の形成は、例えば、公知の原子層堆積装置を用いて実施することができる。

【0017】

前記第2の構造体による構築物としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、絶縁膜が挙げられる。

前記第2の構造体の形成材料としては、前記ボトムアップ形成法による堆積が可能である限り特に制限はなく、前記目的に応じて適宜選択することができ、例えば、前記構築物が絶縁膜である場合には、酸化アルミ、酸化シリコン、窒化シリコン、酸化ハフニウム等を挙げることができる。

【0018】

本発明の前記微細構造物の製造方法は、凸状に形成される前記第1の構造体と、隣接する前記第1の構造体の間に位置する前記基板とで凹状の形状をなす谷状の微細構造に対し、その形状に追従させるように前記第2の構造体の形成材料を堆積させることで、前記第2の構造体に溝を形成する。

このように形成される前記第2の構造体の溝としては、隣接する前記第1の構造体の間の間隔と、前記第2の構造体の堆積厚みとを調整することで、容易に10nmオーダーの溝幅を有するように形成することができる。

即ち、本発明の前記微細構造物の製造方法においては、前記トップダウン形成法又は前記ボトムアップ形成法により、直接的に10nmオーダーの溝幅を有する微細構造物を形成する必要はなく、この溝幅よりも大きなサイズで隣接する前記第1の構造体の間の間隔と、前記第2の構造体の堆積厚みとを調整することで、間接的に10nmオーダーの溝幅を有する前記第2の構造体を形成することが可能となる。

【0019】

前記溝の形成は、特に制限はないが、隣接する前記第1の構造体の間の最短距離(隣接する前記第1の構造体間の間隔)をLとし、前記第2の構造体の堆積厚みをaとしたとき、L−2aで表される溝幅を有するように実施することが好ましい。このように溝の形成を実施すれば、前記溝幅よりも大きなサイズで、前記Lと前記aとを調整することで、間接的に目的とする溝幅を容易に得ることができる。

このような溝の形成方法としては、前記基板に対して略垂直(厳密に垂直である必要はなく、テーパ状、逆テーパ状を含む)に立ち上がるように前記第1の構造体を形成し、形成される前記谷状の微細構造の形状に追従するように前記第2の構造体を形成することが挙げられ、前記トップダウン形成法及び前記ボトムアップ形成法によって実施することができる。

中でも、前記ボトムアップ形成法による前記第2の構造体の形成に関し、前記第2の構造体を前記原子層堆積法(ALD法)により形成することとすれば、堆積対象となる前記谷状の微細構造の表面に前記第2の構造体の形成材料を吸着させて、原子層を1層ずつ成長させることができ、つまり、前記谷状の微細構造における深さ方向及び幅方向のいずれの方向に対しても、前記第2の構造体を一様の堆積厚みで前記原子層を成長させることができ、前記第2の構造体を前記谷状の微細構造の形状に追従させ、これに沿う形で溝を形成することができる。

【0020】

前記aの大きさとしては、前記溝の溝幅に応じて、適宜選択することができるが、前記溝を微細な溝幅で形成する観点から、0.1nm≦a<0.5L(nm)の範囲で調整されることが好ましい。

【0021】

前記微細構造物の製造方法の概略を図1〜図4を用いて説明する。

先ず、基板1上に形成高さをhとして被加工層2Aを形成する(図1参照)。

【0022】

この基板1に対して、トップダウン形成法により、被加工層2Aを加工して2つの凸状の形状からなる第1の構造体2,2’を形成する(第1の構造体形成工程、図2参照)。

ここで、第1の構造体2,2’の形成は、公知のエッチング形成法により、第1の構造体2,2’を残すように被加工層2Aの一部をエッチング除去することで実施してもよいし、公知のリフトオフ形成法により、第1の構造体2,2’をリフトオフ形成して実施してもよい。

これにより、凸状に形成される2つの第1の構造体2,2’と、それらの間に位置する基板1の部分とで凹状の形状をなす谷状の微細構造vが形成される。ここでは、第1の構造体2,2’間の最短距離をLとして、第1の構造体2,2’の形成位置の調整を行う。

【0023】

次いで、ボトムアップ形成法により、第1の構造体2,2’が形成された基板1上に形成材料を堆積させ、第1の構造体2,2’の中間位置に凹状の溝gを有する第2の構造体3を形成する(第2の構造体形成工程、図3参照)。ここでは、第2の構造体3の堆積厚みをaとし、このaが0.5L(nm)未満であり、また、第1の構造体2,2’の形成高さhよりも小さくなるように調整している。

これにより、第2の構造体3において、L−2aの溝幅を有する溝gが形成される。

なお、第2の構造体3の堆積厚みaは、図3に示すように、谷状の微細構造vの深さ方向及び幅方向における第2の構造体3の堆積厚みを示す。

以上により、微細構造物10を製造する。

【0024】

更に微細構造物10から電界効果型半導体素子20を形成する場合について説明する(図4参照)。ここでは、基板1が半導体基板であり、第1の構造体2がドレイン電極であり、第1の構造体2’がソース電極であり、第2の構造体3がゲート絶縁膜であるように、微細構造物10が構成されている。

電界効果型半導体素子20は、この微細構造物10に対し、第2の構造体3に形成された溝gに電極材料を堆積させてゲート電極4を形成することで製造する。

これにより、ゲート長が極めて狭い電界効果型半導体素子20を容易に製造することができる。

【0025】

(微細構造物)

本発明の微細構造物は、少なくとも、基板上に、第1の構造体と第2の構造体とを有する。前記第1の構造体と、前記第2の構造体とは、前記本発明の微細構造物の製造方法により製造されることを特徴とする。

【0026】

(電界効果型半導体素子)

本発明の電界効果型半導体素子は、少なくとも本発明の前記微細構造物を有する。

前記微細構造物において、2つの前記第1の構造体が一対のソース電極とドレイン電極をなし、前記第2の構造体がゲート絶縁膜をなし、前記第2の構造体が有する溝にゲート電極が配されることを特徴とする。

【0027】

前記ゲート電極の形成方法としては、特に制限はなく、目的に応じて適宜選択することができ、例えば、真空蒸着法、化学気相成長法(CVD法)、原子層堆積法(ALD法)、スパッタリング法等が挙げられる。

また、ゲート電極の形成材料としては、特に制限はなく、目的に応じて適宜選択することができ、公知の電極材料を適用することができる。

【0028】

前記電界効果型半導体としては、極めて狭いゲート長で製造することが可能であるため、単電荷トランジスタ、単電荷メモリ等の単電荷デバイス(単電子デバイスと呼ばれることもある)として用いることに適している。このような単電荷デバイスとしては、チャネル部にカーボンナノチューブやグラフェンを適用したものが適用されてもよい。

【0029】

前記単電荷デバイスの一例として、単電荷メモリについて簡単に説明をする。

前記単電荷メモリとしては、通常、基板上にソース電極とドレイン電極とを有し、これらの電極の間にゲート絶縁膜を介して、極めて狭いゲート長を有するゲート電極とが配されてなり、前記ソース電極と前記ドレイン電極との間にチャネル部が形成される。

このような単電荷メモリにおいては、前記チャネル部近傍に電荷捕獲サイトが形成され、該電荷捕獲サイトに蓄積された電荷の影響により前記チャネル部の電気特性が制御可能とされる。即ち、前記電荷捕獲サイトへ電荷を注入を、前記ゲート電極のゲート長を極めて狭くすることで、クーロン反発作用により1つ1つ制御することができる。

前記チャネル部の電気特性は、ゲート電圧を高くしていくと、該チャネルを流れる電子がトンネル効果により前記電荷捕獲サイトに注入され、該チャネルに流れる電流値がシフトするように観察される。この1つ電荷の蓄積によりもたらされる電気特性の変化に基づき、メモリ動作が可能とされる。

以上のように、前記電界効果型半導体素子は、極めて狭いゲート長を有するため、そのようなゲート長を必要とする前記単電荷デバイスに特に有用に適用することができる。

【実施例】

【0030】

本発明の一実施例として、本発明の微細構造物の製造方法を適用して製造する電界効果型半導体素子を説明する。特に、前記電界効果型半導体素子の一種として、単層のカーボンナノチューブをチャネルとした単電荷メモリの実施例を説明する。

【0031】

<シリコン基板>

先ず、面方位が(100)のシリコン結晶に、1×1018cm−3の濃度で不純物(燐)を加えてあるシリコン基板を用意した。

このシリコン基板を熱酸化炉(光洋サーモシステムM270)で酸化し、表面に厚み315nmのSiO2酸化膜を形成した。

熱酸化炉による酸化条件としては、温度を1,000℃とし、炉内の雰囲気をwet酸化とし、酸化時間を35分とした。

【0032】

<カーボンナノチューブの形成>

次に、フォトレジスト材料(シプレイ社製、S1818)を前記シリコン基板のSiO2酸化膜上にスピンコート塗布してフォトレジスト層を形成した。スピンコート塗布の条件としては、回転数を4,000rpmとし、時間を30秒とした。

このフォトレジスト層に対して、露光機(Canon社製、1/4縮小投影露光器)を用いて露光した後、現像液(AZエレクトロニックマテリアルズ社製、AZ300MIF)により現像してレジストパターンを形成した。なお、現像時間は50秒とした。

【0033】

このレジストパターンが形成されたシリコン基板上に、真空蒸着装置(ノアシステムズ社製)を用いて触媒金属を一様に蒸着させた。前記触媒金属は、前記シリコン基板側からシリコン(厚み40nm)、モリブデン(厚み20nm)、鉄(厚み2nm)の順で形成したものである。

この状態で、フォトレジスト材料の剥離液(東京応化工業社製、ハクリ液106)に浸漬し、前記レジストパターンの凹部に形成された前記触媒金属を残して、前記シリコン基板の前記SiO2酸化膜上から前記フォトレジスト層及び該フォトレジスト層上の前記触媒金属を除去した。

【0034】

前記SiO2酸化膜上には、2つの前記触媒金属が凸状に形成されており、該触媒金属を触媒として、隣接する前記触媒金属間に架け渡されるようにカーボンナノチューブを成長させ、前記触媒金属間に単層のカーボンナノチューブを形成した。

具体的には、前記触媒金属が形成されたシリコン基板をカーボンナノチューブを成長させるための炉(Nano Device社製、Easy Tube System)内に配置した後、成長ガスとして、アルゴンでバブリングさせたエタノールを750sccm及び水素を500sccmの条件で導入し、成長温度を900℃として5分間、前記カーボンナノチューブを成長させた。

なお、「単層」とは、カーボンナノチューブの管構造が1層のカーボン層からなる状態を指す。また、「1sccm」は、Si単位で、1.69×10−4Pa・m3/secに換算される。

【0035】

<ソース電極及びドレイン電極の形成>

前記カーボンナノチューブを形成した前記シリコン基板上に、電子線レジスト(日本ゼオン社製、ZEP520A)をスピンコート塗布して電子線レジスト層を形成した。スピンコート塗布の条件としては、回転数を5,000rpmとし、時間を60秒とした。

この電子線レジスト層に対して、電子線描画装置(クレステック社製、CABL−9410TFNA)を用いて電子線描画を行った後、現像液(日本ゼオン社製、ZED−N50)により現像してレジストパターンを形成した。前記電子線描画は、一部の前記レジスト層を除去して、前記凸状の触媒金属の上面が前記電子レジスト層から露出するように実施した。なお、現像時間は60秒とした。

【0036】

このレジストパターンが形成されたシリコン基板上に、真空蒸着装置(ノアシステムズ社製)を用いて金属電極を一様に蒸着させた。前記金属電極は、前記シリコン基板側からチタン(厚み3nm)、金(厚み27nm)の順で形成したものである。

この状態で、前記電子線レジスト材料の剥離液(日本ゼオン社製、ZDMAC)に浸漬し、前記触媒金属の上面に形成された前記金属電極を残して、前記SiO2酸化膜上から前記電子線レジスト層及び該電子線レジスト層上の前記金属電極を除去し、前記シリコン基板上に2つの凸状の金属電極を形成した(第1の構造体形成工程)。ここでは、前記2つの金属電極間の最短距離Lを70nmとし、前記2つの金属電極をそれぞれ、ソース電極、ドレイン電極とした。

この様子を図5に示す。なお、図5は、ソース電極及びドレイン電極が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真である。

【0037】

<絶縁膜の形成>

この2つの金属電極が形成されたシリコン基板上に、原子層堆積装置(オックスフォードインスツルメンツ社製、FlexAl)を用いて絶縁膜を一様に堆積させた。前記絶縁膜は、前記シリコン基板側から酸化アルミニウム(厚み3nm)、窒化シリコン(厚み27nm)の順で形成し、堆積厚みaを30nmとしたものである。

その結果、前記2つの金属電極間の中間位置に、10nm(L−2a=10nm)の溝幅を有する溝が形成された前記絶縁膜を、前記シリコン基板上に形成した(第2の構造体形成工程)。

この様子を図6(a)、(b)に示す。なお、図6(a)は、絶縁膜が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真であり、図6(b)は、図6(a)における微細構造物の俯瞰像を撮像した電子顕微鏡写真である。

【0038】

<ゲート電極の形成>

前記絶縁膜上にフォトレジスト材料(シプレイ社製、S1818)をスピンコート塗布してフォトレジスト層を形成した。スピンコート塗布の条件としては、回転数を4,000rpmとし、時間を30秒とした。

このフォトレジスト層に対して、露光機(Canon社製、1/4縮小投影露光器)を用いて露光した後、現像液(AZエレクトロニックマテリアルズ社製、AZ300MIF)により現像してレジストパターンを形成した。前記レジストパターンの形成は、前記絶縁膜の溝を中心とした周辺部分における前記フォトレジスト層を除去し、前記絶縁膜の溝が露出するように実施した。なお、現像時間は50秒とした。

【0039】

このレジストパターンが形成された前記絶縁膜上に、真空蒸着装置(ノアシステムズ社製)を用いて金属電極を蒸着した。前記金属電極は、前記絶縁膜側からチタン、金の順で形成したものであり、一部が前記絶縁膜の溝に充填されるように配して、前記溝の溝幅(L−2a)をゲート長とするゲート電極とした。

この状態で、フォトレジスト材料の剥離液(東京応化工業社製、ハクリ液106)に浸漬し、前記溝に形成された前記ゲート電極を残して、前記絶縁膜上から前記フォトレジスト層及び該フォトレジスト層上の前記金属電極を除去した。

この様子を図7(a)、(b)に示す。なお、図7(a)は、ゲート電極が形成された状態の微細構造物の上面像を撮像した電子顕微鏡写真であり、図7(b)は、図7(a)における微細構造物の俯瞰像を撮像した電子顕微鏡写真である。

【0040】

以上により、実施例に係る電界効果型半導体素子として単電荷メモリを製造した。この単電荷メモリにおいては、ゲート長(L−2a)が10nmと、極めて微細に加工されているため、前記ゲート電極に対する電圧印可により1つ1つの電荷を制御して、チャネルとしての前記カーボンナノチューブに流れる電流の電流レベルをシフトさせることができ、単電荷のメモリ動作を可能とする。

【符号の説明】

【0041】

1 基板(半導体基板)

2A 被加工層

2 第1の構造体(ドレイン電極)

2’ 第1の構造体(ソース電極)

3 第2の構造体(ゲート絶縁膜)

4 ゲート電極

v 谷状の微細構造

g 溝

【特許請求の範囲】

【請求項1】

トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、

ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、

を含むことを特徴とする微細構造物の製造方法。

【請求項2】

隣接する第1の構造体の間の最短距離をLとし、第2の構造体の堆積厚みをaとしたとき、L−2aで表される溝幅を有する溝を形成する請求項1に記載の微細構造物の製造方法。

【請求項3】

Lが1nm〜1,000nmである請求項2に記載の微細構造物の製造方法。

【請求項4】

aが、次式、0.1nm≦a<0.5Lの関係を満たす請求項2から3のいずれかに記載の微細構造物の製造方法。

【請求項5】

トップダウン形成法が電子線リソグラフィ法である請求項1から4のいずれかに記載の微細構造物の製造方法。

【請求項6】

ボトムアップ形成法が原子層堆積法である請求項1から5のいずれかに記載の微細構造物の製造方法。

【請求項7】

第1の構造体が金属電極である請求項1から6のいずれかに記載の微細構造物の製造方法。

【請求項8】

第2の構造体が絶縁膜である請求項1から7のいずれかに記載の微細構造物の製造方法。

【請求項9】

基板上に、第1の構造体と第2の構造体とを有する微細構造物であって、

前記第1の構造体と前記第2の構造体とが、請求項1から8のいずれかに記載の微細構造物の製造方法により製造されることを特徴とする微細構造物。

【請求項10】

請求項9に記載の微細構造物を有する電界効果型半導体素子であって、

2つの第1の構造体が一対のソース電極とドレイン電極をなし、

第2の構造体がゲート絶縁膜をなし、

前記第2の構造体が有する溝にゲート電極が配されることを特徴とする電界効果型半導体素子。

【請求項1】

トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、

ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、

を含むことを特徴とする微細構造物の製造方法。

【請求項2】

隣接する第1の構造体の間の最短距離をLとし、第2の構造体の堆積厚みをaとしたとき、L−2aで表される溝幅を有する溝を形成する請求項1に記載の微細構造物の製造方法。

【請求項3】

Lが1nm〜1,000nmである請求項2に記載の微細構造物の製造方法。

【請求項4】

aが、次式、0.1nm≦a<0.5Lの関係を満たす請求項2から3のいずれかに記載の微細構造物の製造方法。

【請求項5】

トップダウン形成法が電子線リソグラフィ法である請求項1から4のいずれかに記載の微細構造物の製造方法。

【請求項6】

ボトムアップ形成法が原子層堆積法である請求項1から5のいずれかに記載の微細構造物の製造方法。

【請求項7】

第1の構造体が金属電極である請求項1から6のいずれかに記載の微細構造物の製造方法。

【請求項8】

第2の構造体が絶縁膜である請求項1から7のいずれかに記載の微細構造物の製造方法。

【請求項9】

基板上に、第1の構造体と第2の構造体とを有する微細構造物であって、

前記第1の構造体と前記第2の構造体とが、請求項1から8のいずれかに記載の微細構造物の製造方法により製造されることを特徴とする微細構造物。

【請求項10】

請求項9に記載の微細構造物を有する電界効果型半導体素子であって、

2つの第1の構造体が一対のソース電極とドレイン電極をなし、

第2の構造体がゲート絶縁膜をなし、

前記第2の構造体が有する溝にゲート電極が配されることを特徴とする電界効果型半導体素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6(a)】

【図6(b)】

【図7(a)】

【図7(b)】

【図2】

【図3】

【図4】

【図5】

【図6(a)】

【図6(b)】

【図7(a)】

【図7(b)】

【公開番号】特開2012−212796(P2012−212796A)

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願番号】特願2011−77839(P2011−77839)

【出願日】平成23年3月31日(2011.3.31)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成22年度独立行政法人科学技術振興機構「シリコン系量子ナノメモリの開発」委託研究 産業技術力強化法第19条の適用を受ける特許出願

【出願人】(301021533)独立行政法人産業技術総合研究所 (6,529)

【Fターム(参考)】

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願日】平成23年3月31日(2011.3.31)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成22年度独立行政法人科学技術振興機構「シリコン系量子ナノメモリの開発」委託研究 産業技術力強化法第19条の適用を受ける特許出願

【出願人】(301021533)独立行政法人産業技術総合研究所 (6,529)

【Fターム(参考)】

[ Back to top ]