情報再生装置

【課題】本発明は、イネーブル信号発生手段の回路構成を簡単にできるとともに、安定した動作を得られる情報再生装置を提供する。

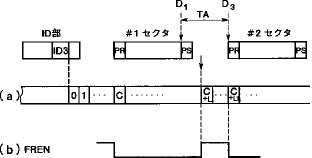

【解決手段】トラック上に、プリアンブルPR、データ部本体およびポストアンブルPSを有する複数のセクタを形成する光カードのトラックに対し斜めに位置をずらしてマルチトラックリード用ビームの反射光を受光する複数のディテクタD1 〜D3 を配置し、これら複数のディテクタD1 〜D3 のうち、光カードの移動方向に対し少なくとも先頭ディテクタD1 が#1セクタのポストアンブルの検出を開始してから最後尾のディテクタD3 が#2セクタのプリアンブルの検出を開始するまでの期間TA でインアクティブとなる信号をディテクタD1 〜D3 のリードイネーブル信号FRENとする。

【解決手段】トラック上に、プリアンブルPR、データ部本体およびポストアンブルPSを有する複数のセクタを形成する光カードのトラックに対し斜めに位置をずらしてマルチトラックリード用ビームの反射光を受光する複数のディテクタD1 〜D3 を配置し、これら複数のディテクタD1 〜D3 のうち、光カードの移動方向に対し少なくとも先頭ディテクタD1 が#1セクタのポストアンブルの検出を開始してから最後尾のディテクタD3 が#2セクタのプリアンブルの検出を開始するまでの期間TA でインアクティブとなる信号をディテクタD1 〜D3 のリードイネーブル信号FRENとする。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、光学的に記録可能な媒体領域を備えたカード状記録媒体に対し情報の光学的再生を行う情報再生装置に関するものである。

【0002】

【従来の技術】従来、光学的に記録可能な媒体領域を備えたカード状記録媒体として、光カードが知られている。この光カードは、図11(a)に示すようにカード本体100の一方面にレーザ光を用いて光学的に情報の記録再生を行う光記録部100aを有し、この光記録部100aは、同図(b)に示すように、互いに並行な複数のトラック100bを備え、そのトラック100b上にマーク(ピットとも言う)100cを形成し、このマーク100cの長さあるいは間隔に意味を持たせることにより情報を記録するようにしている。

【0003】また、各トラック100bは、それぞれ固有、かつ隣接トラック間では連続したトラック番号を与えられており、そのトラック番号の情報は、図12(a)に示すように各トラック100b両端の前後ID部100dに、製造時に版を押すような手法でプリレコードされている。

【0004】図12(b)は、プリレコードされたID部100dの内部構成を示すもので、両端部に位置される最小周期の固定パターンからなるプリアンブル100d1とポストアンブル100d2と、これらプリアンブル100d1とポストアンブル100d2の間に設けられる2つのトラック番号情報部100d3、これらトラック番号情報部100d3を挟む3つのSYNC(同期符号)100d4からなっている。また、2つのトラック番号情報部100d3には、全く同一の情報が記録されており、その内容はトラック番号にエラー訂正符号を付与され、8−10変調などを施されたものである。ここで、プリアンブル100d1とポストアンブル100d2は、ビット同期を取るためのパターンであり、セクタの始まりと終りをそれぞれが表している。

【0005】また、図12(a)に示すように各トラック100bの前後ID部100dの間にデータ部100eを有している。このデータ部100eは、一般的にはID部100dと同じエラー訂正符号化および変調方式を用いて記録される。また、このデータ部100eでの情報の記録単位は、セクタと呼ばれ、必ず1トラック上で完結する。ここでのセクタは、8種類定義されており(セクタタイプと呼ぶ)、1トラック100b上に如何なる容量のセクタを何個まで形成してよいかが規定されている。図12(a)では、例として、1セクタ/トラック、2セクタ/トラック、8セクタ/トラックの各セクタタイプを示している。なお、図示はしていないが、各セクタの先端と後端には、ID部と同様にプリアンブルとポストアンブルが設けられている。

【0006】そして、このように構成された光カードに対する情報の再生は、光ピックアップと光カードのトラック100bを相対的に一定速度で往復運動させることによって行う。ここで、ユーザが指定した任意のセクタを再生するために、光カード上において、読もうとするセクタが存在する領域のみを読み出す必要がある。このために、光カードのトラック100b上での情報再生のためのリードビームの位置の正確な認識が重要となる。

【0007】そこで、従来は、光カードを搬送台に搭載し、固定側の搬送台機構にリニアスケールを取り付け、搬送台の移動にともないリニアスケールのエンコーダから出力されるパルス出力をアップ/ダウンカウントすることにより、光カードと光ピックアップとの相対位置を検出し、トラック100b上でのリードビームの正確な位置認識を行うようにしている。この場合、例えば、搬送台の可動限界位置でカウンタをゼロクリアするといった、ある特定位置でカウンタをプリセットすることによって、カウント値とトラック100b上のID部100dやデータ部1eの各セクタの開始/終了点を1:1に対応させ、さらに、これらセクタ形成区間でのみ情報の記録再生を行わせるようにリード信号からデータを復調し、エラー訂正、バッファへの格納などの信号処理を行うタイミングを決定するゲート信号(以下、リードイネーブル信号と称する。)を生成させるのが一般的である。

【0008】ところが、このようにカウント値の基準点を搬送台の可動限界位置にしたものでは、搬送台に搭載される光カードの収まり具合を始めとして、光カード自身の製造時誤差によりID部100dやデータ部100eの各セクタに位置誤差があると、カウント値とトラック100b上のID部100dやデータ部100eの各セクタの開始/終了点が1:1に対応しなくなって、リードイネーブル信号が不安定なものとなり、正確な情報の再生が困難になる。

【0009】さらに、最近、情報の再生については、再生速度の向上を図るため、複数のディテクタを備え、隣接した複数のトラックを1回のスキャンで同時に再生する、いわゆるマルチトラックリード法が採用されている。

【0010】そして、このようなマルチトラックリードを採用したものでは、光学系の設計上の制約から、必ずしもトラックに対して垂直な方向に、その反射光を受光するディテクタを配列できないことがあり、そこで、従来、特開平08−287512号公報にも見られるように、トラックに対して斜め方向にディテクタを配置することがある。

【0011】図13に示す一例では、3本のリードビームB1 、B2 、B3 をトラック100bに対して斜め方向に配置している。また、他のリードビームB4 、B5 、B6 も同様に斜め方向に配置する。なお、B0 はライトビームである。このように、リードビームを斜めに配列した場合、これらのリードビームを検出するディテクタの配列もトラック100bの向きに対して斜めになるが、そうすると、各リード用ディテクタから検出されるリード信号の発生タイミングがずれてくる。すなわち、B3 のビームが例えば#3SYNCを検出すると、隣のトラックの#3SYNCはB2 のビームにより遅れて検出される。次に、さらに隣のトラックの#3SYNCが、さらに遅れてB1 のビームにより検出される。以下、同様にB6 、B5 、B4 と検出される。ここで、リード信号の検出タイミングのずれに伴い、リードイネーブル信号をリードビームB1 〜B6 に対応するそれぞれのディテクタ毎に発生させていたのが、特開平08−287512号公報にあるように、従来のやり方である。

【0012】

【発明が解決しようとする課題】リードイネーブル信号をディテクタ毎にタイミングを変えて発生させるので、その分イネーブル信号発生手段の構成が複雑となり、これが原因して安定した動作が得られないという問題があった。

【0013】本発明は、上記事情に鑑みてなされたもので、イネーブル信号発生手段の構成を簡単にできるとともに、安定した動作が得られる情ような報再生装置を提供することを目的とする。

【0014】

【課題を解決するための手段】請求項1記載の発明は、トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらして照射したマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段と、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの間に前記複数のディテクタの出力に用いられるリードイネーブル信号をインアクティブとするリードイネーブル信号発生手段とにより構成している。

【0015】請求項2記載の発明は、請求項1記載において、リードイネーブル信号発生手段は、先のセクタと次のセクタとの間のギャップでアクティブからインアクティブへ変化するようなリードイネーブル信号を発生するようにしている。

【0016】請求項3記載の発明は、トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらして照射したマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段を具備し、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの範囲に前記複数のディテクタの分散範囲が収まるようにしている。

【0017】この結果、請求項1記載の発明によれば、マルチトラックリードのための複数のディテクタに共通のリードイネーブル信号を用いることができる。請求項2記載の発明によれば、セクタからのデータを余裕を持って取り込んだのちにリードイネーブル信号をインアクティブにするようにできる。請求項3記載の発明によれば、共通のリードイネーブル信号を用いることができるのに加えて、複数のディテクタの分散範囲を最小限にできる。

【0018】

【発明の実施の形態】以下、本発明の実施の形態を図面に従い説明する。図1は、本発明が適用される情報再生装置の概略構成を示している。図において、1は搬送台駆動回路で、この搬送台駆動回路1は、コントローラ2の指示により、搬送台(可動部)301を矢印の方向、すなわち同搬送台301上に載置した光カード4のトラックに平行な方向に往復運動させる。また、5はピックアップ駆動回路で、このピックアップ駆動回路5は、コントローラ2の指示により、光カード4に対応するピックアップ6を、光カード4のトラックを横切るようにトラックに対して垂直方向に往復運動させる。これらを組み合わせることによって、光カード4とピックアップ6は2次元の相対運動が可能となる。

【0019】7はフォーカス/サーボ回路で、このフォーカス/サーボ回路7は、コントローラ2の指示により、光カード4のトラック上にフォーカシングおよびトラッキングを行うようになっていて、これらの動きを適切に制御することで、特定のトラック上の特定のセクタ位置に対して、情報の再生が可能となる。

【0020】搬送台(可動部)301は、搬送台(駆動部)302を有しており、この搬送台(駆動部)302には、リニアスケール8を取り付け、搬送台(可動部)301にはリニアスケール8用のエンコーダ91を取り付けることによって、搬送台301が往復運動するとエンコーダ91からスケール分解能に応じたパルスが出力される。

【0021】このエンコーダパルスは、イネーブル信号生成回路9に入力される。このイネーブル信号生成回路9は、コントローラ2の制御のもとエンコーダパルスを利用して、複数種類のイネーブル信号を生成して出力するものである。このイネーブル信号生成回路9の内部構成については後述するが、以下、説明のために4種類のイネーブル信号をFREN、BREN、WEN、VENと呼ぶ。

【0022】このうちのイネーブル信号FREN、BREN、VENは、選択回路13に入力される。この選択回路13は、コントローラ2の指示により、#1リード回路11用のリードイネーブル信号および#2リード回路12用のリードイネーブル信号を選択出力するものである。

【0023】これら#1リード回路11および#2リード回路12は、コントローラ2からのリード指示を受け取ると、各々に入力されているリードイネーブル信号がアクティブな区間に入力されるリード信号を元に、データの復調、エラー訂正、バッファへの格納等の処理を行うようにしている。

【0024】この場合、ディテクタD1 〜D3 、D4 〜D6 は、図3に示すように光カードのトラックに対して斜め方向にマルチトラックリード用のリードビームB1 〜B3 、B4 〜B6 の反射光を受光するものとして配置され、ここでのディテクタD1 〜D3 に対応するリード信号は、#1リード回路11に入力され、D4 〜D6に対応するリード信号は、#2リード回路12に入力されるようになっている。

【0025】なお、イネーブル信号WENは、情報記録に用いられるもので、イネーブル信号WENのアクティブな区間でピックアップ6を介しライトパルスのON/OFFに応じてライト用LDをマークを形成できる強度でON/OFFさせ、光カード4のトラック上にマークを形成するのに用いられる。

【0026】次に、イネーブル信号生成回路9について説明する。この場合、図2は、イネーブル信号生成回路9の内部ブロック図を示し、図3は、イネーブル信号FREN、BREN、WEN、VENの果たす役割を示している。

【0027】まず、図3を用いて、イネーブル信号FREN、BREN、WEN、VENの果たす役割を説明する。なお、ここでは、光カード4とピックアップ6の相対運動において、ピックアップ6が光カード4上のトラック4b上を左から右にスキャンする方向を順方向と呼び、逆の場合を逆方向と呼ぶ。

【0028】順方向はトラック4b上を左→右にスキャンしてリードするため、各ディテクタD1 〜D6 が最初に到達するマークは前側ID部左端であり、その地点への到達する順序は、D3 →D2 →D1 →D6 →D5 →D4 である。一方、逆方向は、トラック4b上を右→左にリードしてゆくため、各ディテクタD1 〜D6 が最初に到達するマークは後側ID部右端であり、到達順はD4 →D5 →D6 →D1 →D2 →D3 となる。ここで、B0 は、イネーブル信号WENのアクティブ区間にトラック4b上に形成されるべきライトビームである。

【0029】そして、順方向の場合、イネーブル信号FRENは、最も早くマークに到達するディテクタD3 が特定のセクタ(またはID)へ到達する以前(後述するスケールの誤差マージン分早く)にアクティブとなり、その後、インアクティブになって、再び次のセクタへ到達する以前にアクティブになるが、このうちのインアクティブは、光カード4の移動方向に対しディテクタD1 が先のセクタのポストアンブルの検出を開始してディテクタD3 が次のセクタのプリアンブルの検出を開始するまでの間に行われるようにして、イネーブル信号FRENがディテクタD1 〜D3 共通のリードイネーブル信号になるようにしている。また、イネーブル信号VENはディテクタD6 用のリードイネーブルとして用い、ディテクタD6 が特定のIDまたはセクタに到達する前にアクティブになり、イネーブル信号BRENはディテクタD4 が特定のセクタに到達した後にアクティブになるようにしている。また、イネーブル信号WENは、D0 が特定のセクタ位置に到達する直後にアクティブになるようにしている。

【0030】一方、逆方向の場合は、リードイネーブル信号FRENに代わってリードイネーブル信号BRENを用い、このリードイネーブル信号BRENは、最も早くマークに到達するディテクタD4 特定のセクタ(またはID)へ到達する以前にアクティブとなり、その後、インアクティブになって、再び次のセクタへ到達する以前にアクティブになるが、このうちのインアクティブは、ディテクタD6 が前のセクタのポストアンブルの検出を開始してディテクタD4 が次のセクタのプリアンブルの検出を開始するまでの間に行われるようにして、イネーブル信号BRENがディテクタD4 〜D6 共通のリードイネーブル信号になるようにしている。また、イネーブル信号VENはディテクタD1 用のリードイネーブルとして用い、ディテクタD1 が特定のIDまたはセクタに到達する前にアクティブになり、イネーブル信号FRENはディテクタD3 が特定のセクタに到達した後にアクティブになるようにしている。

【0031】次に、図2に示すイネーブル信号生成回路9によるイネーブル信号FREN、WEN、VEN、BRENの生成方法を、さらに図4および図5を用いて説明する。なお、図4におけるディテクタD1 〜D3 、D4 〜D6 の配列は、時間軸との整合のため、図3と異なりカードを裏面から見た状態で配列にしてある。

【0032】まず、特定の位置として、例えば前側IDの#3SYNCの位置を原点とし、エンコーダ91の分解能を単位として、トラック方向のIDまたはセクタの開始位置および終了位置の座標を設定する。スケール分解能の方がセクタの規定位置の要求精度より粗いのが普通であるので、座標はセクタの規定形成範囲を内包する。ただし、スケールの分解能は、セクタ間の最小ギャップよりも小さく、かつ規定値が含むマージン幅よりも細かい精度とする。

【0033】また、順方向駆動の場合に、カウント値が増加するように設計したものとし、また、ここでは説明上、後述する位置カウンタのプリセットが成功しているものと仮定する。

【0034】まず、図5に示すようにRAM20のデータとして前側IDの#3SYNCを基準にしてRAMアドレス生成回路21にアドレスが与えられ、RAM20は、データCに設定される。このデータCは、#1セクタの開始位置に相当するものである。

【0035】そして、図1に示す搬送台301が駆動されると、図4(b)に示すエンコーダパルスにより同図(c)に示す位置カウンタ23の値は増加し、この位置カウンタ23の値が同図(d)に示すRAM20のデータCと一致すると、同図(f)に示す#1コンパレータ24が一致検出パルスを出力し、この#1一致検出パルスが#1トグルFF22を叩くことによって同図(m)に示すFRENの極性が反転し、アクティブ状態となる。つまり、この場合、図5(a)に示す位置カウンタ23の値が、データCに達すると、図5(b)に示すイネーブル信号FRENがアクティブとなる。

【0036】一方、図4において、#1コンパレータ24の#1一致検出パルスは、ディレイカウンタリセット信号生成回路241を介してディレイカウンタ25に入力される。ディレイカウンタ25は、#1一致検出パルスが入力されるとディレイカウンタリセット信号生成回路241のリセット信号によりリセットされた後、同図(h)に示すようにエンコーダパルスに比べて高い周波数で動作し、アップカウントを開始する。

【0037】また、予めB3 とB0 の間隔をカードが通過する時間をディレイカウンタ25の動作クロックに換算した値を、例えば、#1ディレイ値(16)として#3コンパレータ26に与えておく。ディレイカウンタ25がアクティブになってカウント値が増加してゆき、#1ディレイ値と一致すると、#3コンパレータ26は#3一致検出パルスを出力し、この#3一致検出パルスが#3トグルFF27を叩く事によりイネーブル信号WENの極性が反転するが、そのタイミングは図1に示す搬送台301がB3 →B0 の距離移動するのに要する時間以上、FRENの変化よりも遅れることになる。

【0038】ここで、#1ディレイ値は、(B3 〜B0 距離)+αの値を設定する。これは、前述したように、入手できるスケールの分解能の粗さから、図3に示すようにD3 の特定位置到達時点とエンコーダパルスが同期しないため、位置カウンタ23の変化、ひいてはFRENの変化点が、正規の座標に対してスケールの誤差マージンを含まざるを得ないからである。ここで、B0 は、ライトビームであるから、ライト動作をスケールの誤差マージンを含んだ座標系に則って行うと、実際には所定のセクタ形成位置(規定自体がマージンを含んでいる)到達より早くWENがアクティブとなるため、その結果形成されるセクタの位置は規定を満足しなくなるからである。誤差マージンは最大でスケール分解能と一致するから、αはスケールの分解能に当たる距離を搬送台301が移動するのに要する時間に相当するディレイカウント値を設定すればよい。

【0039】WEN生成の原理と同様に、D3 とD6 の間隔を#2ディレイ値(19)とすることにより、VENが生成できることは明らかである。また、#2ディレイ値は+αは不要である。これはD6 がリードビーム/ディテクタであるから、セクタ位置に到達する前にアクティブになる必要があるからである。つまり、この場合もディレイカウンタ25がアクティブになってカウント値が増加し、#2ディレイ値と一致すると、#4コンパレータ28は#4一致検出パルスを出力し、この#4一致検出パルスが#4トグルFF29を叩くことによりイネーブル信号VENの極性が反転するまた、図1に示すコントローラ2はオフセット値として、トラック方向に最も離れているD3 とD4 の間隔をスケールの分解能を単位として換算し、切り上げた値を、オフセット加算回路31より#2コンパレータ30に与えておく。オフセット値は、図4(e)に示す(4)となる。FRENが変化した後、さらに搬送台301が移動して、位置カウンタ23がオフセット分だけアップすると、#2コンパレータ30は図4(g)に示す#2一致検出パルスを出力し、この#2一致検出パルスが#2トグルFF32を叩くことにより、BRENの極性が変化する。

【0040】#1一致検出パルスおよび#2一致検出パルスは、RAMアドレス更新パルス生成回路33にも入力される。このRAMアドレス更新パルス生成回路33は、順方向であればBRENの変化後、すなわち#2一致検出パルスが入力されてからアドレス更新パルスを生成する。これは、FRENの変化で直ちに更新すると、BRENの変化点までカウンタが達しないうちに、BREN用の参照座標が更新されてしまうのを防ぐためである。

【0041】アドレス更新パルスがRAMアドレス生成回路21に入力され、RAM20は、データC+Lに設定される。このデータC+Lは、#1セクタの終了直後(この場合のデータC+Lは、#1セクタと#2セクタとの間のギャップ上)の位置に相当するものである。

【0042】そして、図5(a)に示す位置カウンタ23の値がさらにカウントアップされ、位置カウンタ23がRAMデータC+Lに一致すると、図5(b)に示すイネーブル信号FRENはインアクティブとなる。

【0043】さらに、アドレス更新パルスがRAMアドレス生成回路21に入力され、RAM20は、データC+L1 に設定される。このデータC+L1 は、#2セクタの開始位置に相当するものである。そして、さらに図5R>5(a)に示す位置カウンタ23の値がカウントアップされ、位置カウンタ23がRAMデータC+L1 に一致すると、図5(b)に示すイネーブル信号FRENは再びアクティブとなる。

【0044】この場合のイネーブル信号FRENのインアクティブは、光カード4の移動方向に対しディテクタD1 が先の#1セクタのポストアンブルPSの検出を開始してディテクタD3 が次の#2セクタのプリアンブルPRの検出を開始するまでの期間tA 中に行われる。

【0045】以下、イネーブル信号FRENについて、アクティブとインアクティブが全セクタに対して繰り返され、また、このようなイネーブル信号FRENとともに、WEN、VEN、BRENの各イネーブル信号の変化点がFREN→WEN→VEN→BRENの順に推移される。

【0046】一方、逆方向の場合は、FRENをD4 に対応させてRAM20の内容を書き換えれば、時間軸上で順方向と全く同順で各イネーブル信号を生成できるが、CPUの負荷が増えてしまう。このため、位置カウンタ23は、光カード4とピックアップ6の相対移動に対して可逆なアップ/ダウンカウントを行い、RAMアドレスの初期値を後側IDの右端とし、WEN、VENを生成するための基準をBRENとすることにより、順方向と同一のRAMテーブルを用いて、各イネーブル信号を生成できる。このとき、時間軸上の変化順は、BREN→WEN→VEN→FRENとなるので、RAMアドレスの更新はFRENの変化、すなわち#1一致検出パルスで行えばよい。

【0047】以上述べたように、FRENとBRENと位相関係は、順方向、逆方向いずれの場合においてもオフセット分だけ同一方向にずれるようになり、またFRENは、IDまたはセクタの規定位置に対して、少なくとも左側に常にマージンを持ち、BRENは少なくとも右側にマージンを持つようになる。

【0048】また、WEN、VENはコントローラ2の指示により、ディレイの基準をFRENかBRENか選択できる。よって、時間軸上で考えれば、FREN→WEN→VEN→BRENの順で変化させる場合とBREN→WEN→VEN→FRENの順で変化させる場合の2通りをコントローラは切り替えることができる。

【0049】なお、本実施の形態では、FRENの生成にRAM20とそのアドレス生成回路21を使用しているが、コントローラ2が直に変化点座標をデータ与えてもよい。

【0050】以上により、4種類のイネーブル信号FREN、WEN、VEN、BRENを生成する方法について説明した。次にこれらの利用法を説明する。以下では説明のため、RAMテーブルを書き換えない方法、すなわち、順方向ではFREN→WEN→VEN→BRENの順に変化し、逆方向ではBREN→WEN→VEN→FRENの順で変化する場合を用いている。RAMデータを書き換える場合は、逆方向でもFREN→WEN→VEN→BRENの順に変化するものとして考えればよい。

【0051】これまで説明した通り、本実施例に用いている光学系では、順方向と逆方向では先行するディテクタが異なり、それらが距離をもって配置されているため、リニアスケールなどの位置情報を元にリードイネーブル信号を生成する場合には、位置的に同一のリードイネーブル信号を、順方向/逆方向に共用できない。

【0052】本実施の形態では、順方向で先行するD3 に対応するリードイネーブルをFRENとし、逆方向で先行するD4 に対応するリードイネーブルをBRENとする。このとき、従来の手法を用いれば、本実施の形態でWEN、VENを元にD5、D4 用のリードイネーブル信号を生成、すなわち、WEN、VENの生成回路と同様な回路を、更に4系統設ける必要があった。

【0053】しかしながら、本実施の形態においては、D1 〜D3 の分散範囲、つまり図4に示すD3 有効受光範囲左端〜D1 有効受光範囲右端間の距離S1 を、隣り合うIDとセクタ、または隣り合うセクタ間の最小ギャップよりも小さくしている。これにより、D1 、D2 、D3 のリードイネーブル信号としてFRENを共用しても、D3 がリード対象セクタの先頭位置に達したときに、D1 がその前のIDまたはセクタのデータ領域にかかる事が無くなるため、D1 が所定のセクタのみをリードできる。

【0054】同様に、図4に示すD4 〜D3 間の距離S2 が最小ギャップよりも小さくなるように構成すれば、VENをD4 、D5 、D6 のリードイネーブル信号として共用できる。逆方向の場合は、D4 、D5 、D6 のリードイネーブルとしてBRENを用い、D1 、D2 、D3 のリードイネーブルとして、BRENを基準に時間的にディレイさせたVENを用いればよい。

【0055】さらに、図4に示すD3 〜D4 間の距離S1 を、最小ギャップよりも小さくなるように偏位させて構成すれば、順方向ではFRENをD1 〜D6 のリードイネーブル信号とし、逆方向ではBRENをD1 〜D6 のリードイネーブル信号としてよい。

【0056】また、本実施例ではD1 、D2 、D3 が入力される#1リード回路11と、D4 、D5 、D6 が入力される#2リード回路12を分けている。各リード回路11、12の内部は各ディテクタからの信号をパラレルに処理してもよいし、シリアルにしてもよいが、いずれにしても同一のスキャンでD3 とD4 が同一のトラック上のデータをリードする。コントローラ2は、通常のリード状態ではD1 、D2 、D3 、D5 、D6 のリードデータとしてもよいし、順方向はD1 、D2 、D3 、D5 、D6 とし、逆方向はD1 、D2 、D4 、D5 、D6 を使用するものとしてもよい。さらに、ライト時にライト直後のデータを、ライトビームよりも後行するディテクタ、すなわち順方向ライトではD4 、逆方向ではD3 をリードすることによって、同時ベリファイを実施して、ライトスピードを向上させることができる。

【0057】なお、本実施の形態では、光学系の構成上D0 とD6 、またはD1 とD0 の間隔が短いので、VENもWENと同様にディレイカウンタを使用しているが、BRENと同様にFRENにエンコーダ91の分解能単位のオフセットを加えて生成してもよい。

【0058】次に、本実施の形態における、位置カウンタ23のプリセットについて説明する。これまで述べてきた、リニアスケール8からの位置情報をもとにIDやセクタの位置決めを行う方法では、既知の場所を、座標軸上の特定の基準点としなければならない(原点にする必要はない)。本装置では、カード4を搬送台301に搭載しているので、搭載時のカードの収まり具合や、カード製造上の誤差などにより、例えば搬送台の可動限界位置〜前側ID左端までの距離は一定にならないため、カード上の特定の点を基準とする必要がある。カードはプリレコード部の形成を、版を押すようにして実施するため、前側ID〜後側IDの間隔は、温度変化による媒体の伸縮を考えても、規格値に対する誤差は非常に少ない。これに比べ、前述のような可動限界位置〜前側ID左端の距離は、カード毎に一定にならず、しかも非常に大きい。

【0059】このため、本実施の形態では、図12(b)で述べた光カードのID部100dの構成において、図6に示すように、順方向にスキャンする際には#1トラック番号情報部100d3をリードし、エラー訂正等を施してトラックと特定した後、同一のスキャンでの#3SYNC100d4の検出時点でプリセットを行う。逆方向であれば、#1SYNC100d4の検出で行う。プリセットしていない状態でリードすることになるが、このときはセクタをリードしないので、リードイネーブルは、IDを十分マージンを持たせてアクティブにすればよい。例えば、可動限界でオールゼロにプリセットし、カードの収まり等の誤差を考慮して十分な程度ID部を内包してインアクティブになるように、RAMのデータを設定しておけばよい。このとき、プリセットに成功すれば、同一のスキャンで直ちにリードやライトを実施してもよい。

【0060】ここで、マルチトラックリードでは、同時に複数のID部100dをリード可能であるため、各ディテクタ毎の読み取ったトラック番号を組み合わせて判断すれば、トラックの認識をより正確に行うことができる。例えば、図3において、D1 、D2 、D3 を利用して行う場合、トラック番号の特定に多数決論理を取り入れるなどの方法である。同様に、プリセットの検出タイミングとするSYNCの検出も、複数のトラックからの情報を取り入れれば、より正確になる。

【0061】しかしながら、例えば、D1 、D2 、D3 を利用してプリセットを実施する場合、共通のリードイネーブルを使用するので、各リード回路が動作し始めるのは同時であるのに対し、ディテクタはトラック方向に偏位しているため、ID部の例えば#3SYNCの検出は同時にならないことになる。このため、多数決判定を実施する場合は、図3でD1 とD2 で検出された場合とD1 とD3 で検出した場合では、プリセットのタイミングが異なってしまう。

【0062】このため、本実施の形態では、プリセットのためのSYNC検出において、図7のようにSYNC検出回路41〜43、ディレイ回路44、45を有する回路を用いる。図8は図7の動作を説明する図である。なお、図7の回路は、図1における#1リード回路11および/または#2リード回路12に含まれるものとする。

【0063】順方向でD1 、D2 、D3 による#3SYNC検出を組み合わせてプリセットを行う場合、検出タイミングはD3 →D2 →D1 となる。このとき、D3 で#3SYNCを検出した場合に限り、直ちにステータスをセットせずに#1ディレイ回路44を通してD1 で#3SYNCを検出するタイミングまで遅らせる。遅らせる時間は、D1 〜D3 間の距離をカードが移動するのに要する時間で一定である。同様に、D2 で#3SYNCを検出した場合に限り、直ちにステータスを立てずに#2ディレイ回路45を通してD1 で#3SYNCを検出するタイミングまで遅らせる。遅らせる時間は、D2 〜D3 間の距離をカードが移動するのに要する時間で一定である。

【0064】これによって、コントローラは、SYNC検出ステータスをポーリングするだけで、いずれかのディテクタで#3SYNCが検出されればD1 のSYNCステータスと同時にD2 、D3 のステータスが変化するので、例えば多数決判定など、所定のアルゴリズムで#3SYNC検出を判定できる。#3SYNCの検出ステータスは、あたかもトラックに垂直方向にD1 と整列してD2 、D3 が存在する場合と同様に変化するからである。

【0065】逆方向の場合は、検出タイミングはD1 →D2 →D3 であるから、#1ディレイ回路44を通す信号を#1SYNC検出信号として、#3SYNC検出信号は直にステータスFFに出力すればよい。

【0066】なお、本回路におけるディレイ回路44、45は、図2に開示したように、ディレイカウンタとコンパレータを用いれば簡単に実現でき、ディレイ量をコントローラが任意に設定できるようにして、意図的にSYNCステータスのタイミングをずらす事も可能である。

【0067】従って、このようにすれば、トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードのトラックに対し斜めに位置をずらしてマルチトラックリード用ビームの反射光を受光する複数のディテクタD1 〜D3 を配置し、これら複数のディテクタD1 〜D3 のうち、光カードの移動方向に対し少なくとも先頭ディテクタD1 が#1セクタのポストアンブルの検出を開始してから最後尾のディテクタD3 が#2セクタのプリアンブルの検出を開始するまでの期間TA でインアクティブとなる信号を複数のディテクタD1 〜D3 のリードイネーブル信号FRENとすることにより、ディテクタD1 〜D3 に共通のリードイネーブル信号FRENを用いることができ、マルチトラックリード用のイネーブル信号発生手段の回路構成を簡単にできるとともに、安定した動作を得られ、さらに、期間TA の範囲に複数のディテクタD1 〜D3の分散範囲が収まるようにすることで、複数のディテクタD1 〜D3 の分散範囲を最小限にできるので、マルチトラックリード用の光ピックアップを小型にでき、装置の小形化を実現できる。

【0068】ところで、図9に示すように光カードのトラックのID部に対するイネーブル信号が同図(b)に示すようにID部の直前に出力される場合は、同図(a)に示すようにエンベローブが正しくアクティブとなるが、例えば、イネーブル信号が同図(c)に示すように位置決めの誤りなどでずれるか、あるいはID部(またはセクタ)がもともと位置ずれを起こしているような場合、ブロックずれが発生し、本来、バッファメモリに図10(a)に示すように#1ブロック、#2ブロック、#3ブロックの順に格納されるものが、図10(b)に示すように#2ブロック、#3ブロック、#4ブロックの順となり、格納場所が誤ってしまう。これは、#1SYNC〜#3SYNCは、いずれも見た目に違いがなく、各ブロックにもブロック番号が付いていないためである。

【0069】そして、図10(b)に示すように誤ってバッファメモリに格納されると、データによっては、エラー訂正ができてしまうことがあり、誤訂正に陥ってしまうことがある。これは、エラー訂正不能よりはるかに深刻な問題でもある。

【0070】そこで、この他の実施の形態では、図1に示すように#1リード回路11および#2リード回路12に、さらにプリアンプル検出回路51を接続し、図9に示すID部のプリアンブルPRを検出したか否かのステータスを立てるようにしている。ここで、プリアンブルPRは、所定の“1”“0”のパターンからなるものである。そして、プリアンプル検出回路51では、プリアンブルPRに対し、例えば96ビットのうちの32ビットのパターンで検出するように設定する。このパターンは、可変にしてもよい。

【0071】このような構成において、プリアンプル検出回路51が#1SYNCを検出した時点でプリアンブルパターンが見付かっていれば、通常の復調動作を続けるが、プリアンブルパターンが見付かっていなければ、最初に検出したSYNCが#2でブロックずれを発生した可能性があるため、プリアンプル検出回路51よりコントローラ2に対しプリアンブルPRが検出できなかったことを通知し、復調動作や図示しないホストコンピュータへの転送などを中止させるようにする。

【0072】なお、#1ブロックにプリアンブルPRと認識できるパターンがデータとして記録されており、なおかつ、ブロックずれを起こす場合に備えて、さらにエンベローブがアクティブになってから、一定範囲でのみプリアンブル検出をアクティブにしたり、最終ブロックの後にポストアンブルがあることを確認するなどすることで、さらにブロックずれの発生確率を減らすようにもしている。

【0073】このように、この他の実施の形態では、再生情報の復調に当たり、本来ビットクロックの引き込み用途しかないプリアンブルパターンを使用して、#1SYNC検出前にプリアンブルが検出されない場合は、この旨をコントローラに通知して復調動作などのを中止させるようにしたので、ブロックずれによる誤動作を確実に防止することができる。

【0074】以上、実施の形態に基づいて説明したが、本発明中には、以下の発明が含まれる。

(1)トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらしてマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段と、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの間に前記複数のディテクタの出力に用いられるリードイネーブル信号をインアクティブとするリードイネーブル信号発生手段とを具備したことを特徴とする情報再生装置。

【0075】このようにすれば、マルチトラックリードのための複数のディテクタに共通のリードイネーブル信号を用いることができるので、マルチトラックリード用のイネーブル信号発生手段の回路構成を簡単にできるとともに、安定した動作を得られる。

【0076】(2)(1)記載の情報再生装置において、リードイネーブル信号発生手段は、先のセクタと次のセクタとの間のギャップでアクティブからインアクティブへ変化するようなリードイネーブル信号を発生するようにしている。

【0077】このようにすれば、セクタからのデータを余裕を持って取り込んだのちにリードイネーブル信号をインアクティブにするようにできので、安定した情報の再生を行うことができる。

【0078】(3)トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらしてマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段を具備し、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの範囲に前記複数のディテクタの分散範囲が収まるようにしたことを特徴とする情報再生装置。

【0079】このようにすれば、共通のリードイネーブル信号を用いることができるのに加え、複数のディテクタの分散範囲を最小限にできるので、さらにマルチトラックリード用の光ピックアップを小型にでき、装置の小形化を実現できる。

【0080】(4)リードイネーブル信号発生手段より発生されるリードイネーブル信号は、リードしようとするセクタの規定開始位置よりも早く、かつ、規定終了位置よりも遅いタイミングでアクティブになる。このようにすれば、セクタからのリードを確実なものにできる。

【0081】

【発明の効果】以上述べたように本発明によれば、マルチトラックリードのための複数のディテクタに共通のリードイネーブル信号を用いることができ、マルチトラックリード用のイネーブル信号発生手段の回路構成を簡単にできるとともに、安定した動作を得られる。また、複数のディテクタの分散範囲を最小限にできるので、光ピックアップを小型にでき、装置の小形化を実現できる。

【図面の簡単な説明】

【図1】本発明の一実施の形態の概略構成を示す図。

【図2】一実施の形態に用いられるイネーブル信号生成回路の概略構成を示す図。

【図3】一実施の形態に用いられるイネーブル信号の役割を説明するための図。

【図4】一実施の形態の動作を説明するためのタイムチャート。

【図5】一実施の形態の動作を説明するための図。

【図6】一実施の形態の位置カウンタのプリセットについて説明するための図。

【図7】一実施の形態の位置カウンタのプリセットのためのSYNC検出を説明するための図。

【図8】一実施の形態の位置カウンタのプリセットのためのSYNC検出を説明するためのフローチャート。

【図9】本発明の他の実施の形態を説明するための図。

【図10】同他の実施の形態を説明するための図。

【図11】光カードの概略構成を示す図。

【図12】光カードのトラック部の概略構成を示す図。

【図13】マルチトラックリード用のディテクタの配置例を示す図。

【符号の説明】

1…搬送台駆動回路、

2…コントローラ、

301…搬送台(可動部)、

302…搬送台(駆動部)、

4…光カード、

5…ピックアップ駆動回路、

6…ピックアップ、

7…フォーカス/サーボ回路、

8…リニアスケール、

9…イネーブル信号生成回路

91…エンコーダ、

11…#1リード回路、

12…#2リード回路、

13…選択回路、

20…RAM、

21…RAMアドレス生成回路、

22…#1トグルFF、

23…位置カウンタ、

24…#1コンパレータ、

241…ディレイカウンタリセット信号生成回路、

25…ディレイカウンタ、

26…#3コンパレータ、

27…#3トグルFF、

28…#4コンパレータ、

29…#4トグルFF、

30…#2コンパレータ、

31…オフセット加算回路、

32…#2トグルFF、

33…RAMアドレス更新パルス生成回路、

41〜43…SYNC検出回路、

44、45…ディレイ回路、

51…プリアンプル検出回路。

【0001】

【発明の属する技術分野】本発明は、光学的に記録可能な媒体領域を備えたカード状記録媒体に対し情報の光学的再生を行う情報再生装置に関するものである。

【0002】

【従来の技術】従来、光学的に記録可能な媒体領域を備えたカード状記録媒体として、光カードが知られている。この光カードは、図11(a)に示すようにカード本体100の一方面にレーザ光を用いて光学的に情報の記録再生を行う光記録部100aを有し、この光記録部100aは、同図(b)に示すように、互いに並行な複数のトラック100bを備え、そのトラック100b上にマーク(ピットとも言う)100cを形成し、このマーク100cの長さあるいは間隔に意味を持たせることにより情報を記録するようにしている。

【0003】また、各トラック100bは、それぞれ固有、かつ隣接トラック間では連続したトラック番号を与えられており、そのトラック番号の情報は、図12(a)に示すように各トラック100b両端の前後ID部100dに、製造時に版を押すような手法でプリレコードされている。

【0004】図12(b)は、プリレコードされたID部100dの内部構成を示すもので、両端部に位置される最小周期の固定パターンからなるプリアンブル100d1とポストアンブル100d2と、これらプリアンブル100d1とポストアンブル100d2の間に設けられる2つのトラック番号情報部100d3、これらトラック番号情報部100d3を挟む3つのSYNC(同期符号)100d4からなっている。また、2つのトラック番号情報部100d3には、全く同一の情報が記録されており、その内容はトラック番号にエラー訂正符号を付与され、8−10変調などを施されたものである。ここで、プリアンブル100d1とポストアンブル100d2は、ビット同期を取るためのパターンであり、セクタの始まりと終りをそれぞれが表している。

【0005】また、図12(a)に示すように各トラック100bの前後ID部100dの間にデータ部100eを有している。このデータ部100eは、一般的にはID部100dと同じエラー訂正符号化および変調方式を用いて記録される。また、このデータ部100eでの情報の記録単位は、セクタと呼ばれ、必ず1トラック上で完結する。ここでのセクタは、8種類定義されており(セクタタイプと呼ぶ)、1トラック100b上に如何なる容量のセクタを何個まで形成してよいかが規定されている。図12(a)では、例として、1セクタ/トラック、2セクタ/トラック、8セクタ/トラックの各セクタタイプを示している。なお、図示はしていないが、各セクタの先端と後端には、ID部と同様にプリアンブルとポストアンブルが設けられている。

【0006】そして、このように構成された光カードに対する情報の再生は、光ピックアップと光カードのトラック100bを相対的に一定速度で往復運動させることによって行う。ここで、ユーザが指定した任意のセクタを再生するために、光カード上において、読もうとするセクタが存在する領域のみを読み出す必要がある。このために、光カードのトラック100b上での情報再生のためのリードビームの位置の正確な認識が重要となる。

【0007】そこで、従来は、光カードを搬送台に搭載し、固定側の搬送台機構にリニアスケールを取り付け、搬送台の移動にともないリニアスケールのエンコーダから出力されるパルス出力をアップ/ダウンカウントすることにより、光カードと光ピックアップとの相対位置を検出し、トラック100b上でのリードビームの正確な位置認識を行うようにしている。この場合、例えば、搬送台の可動限界位置でカウンタをゼロクリアするといった、ある特定位置でカウンタをプリセットすることによって、カウント値とトラック100b上のID部100dやデータ部1eの各セクタの開始/終了点を1:1に対応させ、さらに、これらセクタ形成区間でのみ情報の記録再生を行わせるようにリード信号からデータを復調し、エラー訂正、バッファへの格納などの信号処理を行うタイミングを決定するゲート信号(以下、リードイネーブル信号と称する。)を生成させるのが一般的である。

【0008】ところが、このようにカウント値の基準点を搬送台の可動限界位置にしたものでは、搬送台に搭載される光カードの収まり具合を始めとして、光カード自身の製造時誤差によりID部100dやデータ部100eの各セクタに位置誤差があると、カウント値とトラック100b上のID部100dやデータ部100eの各セクタの開始/終了点が1:1に対応しなくなって、リードイネーブル信号が不安定なものとなり、正確な情報の再生が困難になる。

【0009】さらに、最近、情報の再生については、再生速度の向上を図るため、複数のディテクタを備え、隣接した複数のトラックを1回のスキャンで同時に再生する、いわゆるマルチトラックリード法が採用されている。

【0010】そして、このようなマルチトラックリードを採用したものでは、光学系の設計上の制約から、必ずしもトラックに対して垂直な方向に、その反射光を受光するディテクタを配列できないことがあり、そこで、従来、特開平08−287512号公報にも見られるように、トラックに対して斜め方向にディテクタを配置することがある。

【0011】図13に示す一例では、3本のリードビームB1 、B2 、B3 をトラック100bに対して斜め方向に配置している。また、他のリードビームB4 、B5 、B6 も同様に斜め方向に配置する。なお、B0 はライトビームである。このように、リードビームを斜めに配列した場合、これらのリードビームを検出するディテクタの配列もトラック100bの向きに対して斜めになるが、そうすると、各リード用ディテクタから検出されるリード信号の発生タイミングがずれてくる。すなわち、B3 のビームが例えば#3SYNCを検出すると、隣のトラックの#3SYNCはB2 のビームにより遅れて検出される。次に、さらに隣のトラックの#3SYNCが、さらに遅れてB1 のビームにより検出される。以下、同様にB6 、B5 、B4 と検出される。ここで、リード信号の検出タイミングのずれに伴い、リードイネーブル信号をリードビームB1 〜B6 に対応するそれぞれのディテクタ毎に発生させていたのが、特開平08−287512号公報にあるように、従来のやり方である。

【0012】

【発明が解決しようとする課題】リードイネーブル信号をディテクタ毎にタイミングを変えて発生させるので、その分イネーブル信号発生手段の構成が複雑となり、これが原因して安定した動作が得られないという問題があった。

【0013】本発明は、上記事情に鑑みてなされたもので、イネーブル信号発生手段の構成を簡単にできるとともに、安定した動作が得られる情ような報再生装置を提供することを目的とする。

【0014】

【課題を解決するための手段】請求項1記載の発明は、トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらして照射したマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段と、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの間に前記複数のディテクタの出力に用いられるリードイネーブル信号をインアクティブとするリードイネーブル信号発生手段とにより構成している。

【0015】請求項2記載の発明は、請求項1記載において、リードイネーブル信号発生手段は、先のセクタと次のセクタとの間のギャップでアクティブからインアクティブへ変化するようなリードイネーブル信号を発生するようにしている。

【0016】請求項3記載の発明は、トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらして照射したマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段を具備し、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの範囲に前記複数のディテクタの分散範囲が収まるようにしている。

【0017】この結果、請求項1記載の発明によれば、マルチトラックリードのための複数のディテクタに共通のリードイネーブル信号を用いることができる。請求項2記載の発明によれば、セクタからのデータを余裕を持って取り込んだのちにリードイネーブル信号をインアクティブにするようにできる。請求項3記載の発明によれば、共通のリードイネーブル信号を用いることができるのに加えて、複数のディテクタの分散範囲を最小限にできる。

【0018】

【発明の実施の形態】以下、本発明の実施の形態を図面に従い説明する。図1は、本発明が適用される情報再生装置の概略構成を示している。図において、1は搬送台駆動回路で、この搬送台駆動回路1は、コントローラ2の指示により、搬送台(可動部)301を矢印の方向、すなわち同搬送台301上に載置した光カード4のトラックに平行な方向に往復運動させる。また、5はピックアップ駆動回路で、このピックアップ駆動回路5は、コントローラ2の指示により、光カード4に対応するピックアップ6を、光カード4のトラックを横切るようにトラックに対して垂直方向に往復運動させる。これらを組み合わせることによって、光カード4とピックアップ6は2次元の相対運動が可能となる。

【0019】7はフォーカス/サーボ回路で、このフォーカス/サーボ回路7は、コントローラ2の指示により、光カード4のトラック上にフォーカシングおよびトラッキングを行うようになっていて、これらの動きを適切に制御することで、特定のトラック上の特定のセクタ位置に対して、情報の再生が可能となる。

【0020】搬送台(可動部)301は、搬送台(駆動部)302を有しており、この搬送台(駆動部)302には、リニアスケール8を取り付け、搬送台(可動部)301にはリニアスケール8用のエンコーダ91を取り付けることによって、搬送台301が往復運動するとエンコーダ91からスケール分解能に応じたパルスが出力される。

【0021】このエンコーダパルスは、イネーブル信号生成回路9に入力される。このイネーブル信号生成回路9は、コントローラ2の制御のもとエンコーダパルスを利用して、複数種類のイネーブル信号を生成して出力するものである。このイネーブル信号生成回路9の内部構成については後述するが、以下、説明のために4種類のイネーブル信号をFREN、BREN、WEN、VENと呼ぶ。

【0022】このうちのイネーブル信号FREN、BREN、VENは、選択回路13に入力される。この選択回路13は、コントローラ2の指示により、#1リード回路11用のリードイネーブル信号および#2リード回路12用のリードイネーブル信号を選択出力するものである。

【0023】これら#1リード回路11および#2リード回路12は、コントローラ2からのリード指示を受け取ると、各々に入力されているリードイネーブル信号がアクティブな区間に入力されるリード信号を元に、データの復調、エラー訂正、バッファへの格納等の処理を行うようにしている。

【0024】この場合、ディテクタD1 〜D3 、D4 〜D6 は、図3に示すように光カードのトラックに対して斜め方向にマルチトラックリード用のリードビームB1 〜B3 、B4 〜B6 の反射光を受光するものとして配置され、ここでのディテクタD1 〜D3 に対応するリード信号は、#1リード回路11に入力され、D4 〜D6に対応するリード信号は、#2リード回路12に入力されるようになっている。

【0025】なお、イネーブル信号WENは、情報記録に用いられるもので、イネーブル信号WENのアクティブな区間でピックアップ6を介しライトパルスのON/OFFに応じてライト用LDをマークを形成できる強度でON/OFFさせ、光カード4のトラック上にマークを形成するのに用いられる。

【0026】次に、イネーブル信号生成回路9について説明する。この場合、図2は、イネーブル信号生成回路9の内部ブロック図を示し、図3は、イネーブル信号FREN、BREN、WEN、VENの果たす役割を示している。

【0027】まず、図3を用いて、イネーブル信号FREN、BREN、WEN、VENの果たす役割を説明する。なお、ここでは、光カード4とピックアップ6の相対運動において、ピックアップ6が光カード4上のトラック4b上を左から右にスキャンする方向を順方向と呼び、逆の場合を逆方向と呼ぶ。

【0028】順方向はトラック4b上を左→右にスキャンしてリードするため、各ディテクタD1 〜D6 が最初に到達するマークは前側ID部左端であり、その地点への到達する順序は、D3 →D2 →D1 →D6 →D5 →D4 である。一方、逆方向は、トラック4b上を右→左にリードしてゆくため、各ディテクタD1 〜D6 が最初に到達するマークは後側ID部右端であり、到達順はD4 →D5 →D6 →D1 →D2 →D3 となる。ここで、B0 は、イネーブル信号WENのアクティブ区間にトラック4b上に形成されるべきライトビームである。

【0029】そして、順方向の場合、イネーブル信号FRENは、最も早くマークに到達するディテクタD3 が特定のセクタ(またはID)へ到達する以前(後述するスケールの誤差マージン分早く)にアクティブとなり、その後、インアクティブになって、再び次のセクタへ到達する以前にアクティブになるが、このうちのインアクティブは、光カード4の移動方向に対しディテクタD1 が先のセクタのポストアンブルの検出を開始してディテクタD3 が次のセクタのプリアンブルの検出を開始するまでの間に行われるようにして、イネーブル信号FRENがディテクタD1 〜D3 共通のリードイネーブル信号になるようにしている。また、イネーブル信号VENはディテクタD6 用のリードイネーブルとして用い、ディテクタD6 が特定のIDまたはセクタに到達する前にアクティブになり、イネーブル信号BRENはディテクタD4 が特定のセクタに到達した後にアクティブになるようにしている。また、イネーブル信号WENは、D0 が特定のセクタ位置に到達する直後にアクティブになるようにしている。

【0030】一方、逆方向の場合は、リードイネーブル信号FRENに代わってリードイネーブル信号BRENを用い、このリードイネーブル信号BRENは、最も早くマークに到達するディテクタD4 特定のセクタ(またはID)へ到達する以前にアクティブとなり、その後、インアクティブになって、再び次のセクタへ到達する以前にアクティブになるが、このうちのインアクティブは、ディテクタD6 が前のセクタのポストアンブルの検出を開始してディテクタD4 が次のセクタのプリアンブルの検出を開始するまでの間に行われるようにして、イネーブル信号BRENがディテクタD4 〜D6 共通のリードイネーブル信号になるようにしている。また、イネーブル信号VENはディテクタD1 用のリードイネーブルとして用い、ディテクタD1 が特定のIDまたはセクタに到達する前にアクティブになり、イネーブル信号FRENはディテクタD3 が特定のセクタに到達した後にアクティブになるようにしている。

【0031】次に、図2に示すイネーブル信号生成回路9によるイネーブル信号FREN、WEN、VEN、BRENの生成方法を、さらに図4および図5を用いて説明する。なお、図4におけるディテクタD1 〜D3 、D4 〜D6 の配列は、時間軸との整合のため、図3と異なりカードを裏面から見た状態で配列にしてある。

【0032】まず、特定の位置として、例えば前側IDの#3SYNCの位置を原点とし、エンコーダ91の分解能を単位として、トラック方向のIDまたはセクタの開始位置および終了位置の座標を設定する。スケール分解能の方がセクタの規定位置の要求精度より粗いのが普通であるので、座標はセクタの規定形成範囲を内包する。ただし、スケールの分解能は、セクタ間の最小ギャップよりも小さく、かつ規定値が含むマージン幅よりも細かい精度とする。

【0033】また、順方向駆動の場合に、カウント値が増加するように設計したものとし、また、ここでは説明上、後述する位置カウンタのプリセットが成功しているものと仮定する。

【0034】まず、図5に示すようにRAM20のデータとして前側IDの#3SYNCを基準にしてRAMアドレス生成回路21にアドレスが与えられ、RAM20は、データCに設定される。このデータCは、#1セクタの開始位置に相当するものである。

【0035】そして、図1に示す搬送台301が駆動されると、図4(b)に示すエンコーダパルスにより同図(c)に示す位置カウンタ23の値は増加し、この位置カウンタ23の値が同図(d)に示すRAM20のデータCと一致すると、同図(f)に示す#1コンパレータ24が一致検出パルスを出力し、この#1一致検出パルスが#1トグルFF22を叩くことによって同図(m)に示すFRENの極性が反転し、アクティブ状態となる。つまり、この場合、図5(a)に示す位置カウンタ23の値が、データCに達すると、図5(b)に示すイネーブル信号FRENがアクティブとなる。

【0036】一方、図4において、#1コンパレータ24の#1一致検出パルスは、ディレイカウンタリセット信号生成回路241を介してディレイカウンタ25に入力される。ディレイカウンタ25は、#1一致検出パルスが入力されるとディレイカウンタリセット信号生成回路241のリセット信号によりリセットされた後、同図(h)に示すようにエンコーダパルスに比べて高い周波数で動作し、アップカウントを開始する。

【0037】また、予めB3 とB0 の間隔をカードが通過する時間をディレイカウンタ25の動作クロックに換算した値を、例えば、#1ディレイ値(16)として#3コンパレータ26に与えておく。ディレイカウンタ25がアクティブになってカウント値が増加してゆき、#1ディレイ値と一致すると、#3コンパレータ26は#3一致検出パルスを出力し、この#3一致検出パルスが#3トグルFF27を叩く事によりイネーブル信号WENの極性が反転するが、そのタイミングは図1に示す搬送台301がB3 →B0 の距離移動するのに要する時間以上、FRENの変化よりも遅れることになる。

【0038】ここで、#1ディレイ値は、(B3 〜B0 距離)+αの値を設定する。これは、前述したように、入手できるスケールの分解能の粗さから、図3に示すようにD3 の特定位置到達時点とエンコーダパルスが同期しないため、位置カウンタ23の変化、ひいてはFRENの変化点が、正規の座標に対してスケールの誤差マージンを含まざるを得ないからである。ここで、B0 は、ライトビームであるから、ライト動作をスケールの誤差マージンを含んだ座標系に則って行うと、実際には所定のセクタ形成位置(規定自体がマージンを含んでいる)到達より早くWENがアクティブとなるため、その結果形成されるセクタの位置は規定を満足しなくなるからである。誤差マージンは最大でスケール分解能と一致するから、αはスケールの分解能に当たる距離を搬送台301が移動するのに要する時間に相当するディレイカウント値を設定すればよい。

【0039】WEN生成の原理と同様に、D3 とD6 の間隔を#2ディレイ値(19)とすることにより、VENが生成できることは明らかである。また、#2ディレイ値は+αは不要である。これはD6 がリードビーム/ディテクタであるから、セクタ位置に到達する前にアクティブになる必要があるからである。つまり、この場合もディレイカウンタ25がアクティブになってカウント値が増加し、#2ディレイ値と一致すると、#4コンパレータ28は#4一致検出パルスを出力し、この#4一致検出パルスが#4トグルFF29を叩くことによりイネーブル信号VENの極性が反転するまた、図1に示すコントローラ2はオフセット値として、トラック方向に最も離れているD3 とD4 の間隔をスケールの分解能を単位として換算し、切り上げた値を、オフセット加算回路31より#2コンパレータ30に与えておく。オフセット値は、図4(e)に示す(4)となる。FRENが変化した後、さらに搬送台301が移動して、位置カウンタ23がオフセット分だけアップすると、#2コンパレータ30は図4(g)に示す#2一致検出パルスを出力し、この#2一致検出パルスが#2トグルFF32を叩くことにより、BRENの極性が変化する。

【0040】#1一致検出パルスおよび#2一致検出パルスは、RAMアドレス更新パルス生成回路33にも入力される。このRAMアドレス更新パルス生成回路33は、順方向であればBRENの変化後、すなわち#2一致検出パルスが入力されてからアドレス更新パルスを生成する。これは、FRENの変化で直ちに更新すると、BRENの変化点までカウンタが達しないうちに、BREN用の参照座標が更新されてしまうのを防ぐためである。

【0041】アドレス更新パルスがRAMアドレス生成回路21に入力され、RAM20は、データC+Lに設定される。このデータC+Lは、#1セクタの終了直後(この場合のデータC+Lは、#1セクタと#2セクタとの間のギャップ上)の位置に相当するものである。

【0042】そして、図5(a)に示す位置カウンタ23の値がさらにカウントアップされ、位置カウンタ23がRAMデータC+Lに一致すると、図5(b)に示すイネーブル信号FRENはインアクティブとなる。

【0043】さらに、アドレス更新パルスがRAMアドレス生成回路21に入力され、RAM20は、データC+L1 に設定される。このデータC+L1 は、#2セクタの開始位置に相当するものである。そして、さらに図5R>5(a)に示す位置カウンタ23の値がカウントアップされ、位置カウンタ23がRAMデータC+L1 に一致すると、図5(b)に示すイネーブル信号FRENは再びアクティブとなる。

【0044】この場合のイネーブル信号FRENのインアクティブは、光カード4の移動方向に対しディテクタD1 が先の#1セクタのポストアンブルPSの検出を開始してディテクタD3 が次の#2セクタのプリアンブルPRの検出を開始するまでの期間tA 中に行われる。

【0045】以下、イネーブル信号FRENについて、アクティブとインアクティブが全セクタに対して繰り返され、また、このようなイネーブル信号FRENとともに、WEN、VEN、BRENの各イネーブル信号の変化点がFREN→WEN→VEN→BRENの順に推移される。

【0046】一方、逆方向の場合は、FRENをD4 に対応させてRAM20の内容を書き換えれば、時間軸上で順方向と全く同順で各イネーブル信号を生成できるが、CPUの負荷が増えてしまう。このため、位置カウンタ23は、光カード4とピックアップ6の相対移動に対して可逆なアップ/ダウンカウントを行い、RAMアドレスの初期値を後側IDの右端とし、WEN、VENを生成するための基準をBRENとすることにより、順方向と同一のRAMテーブルを用いて、各イネーブル信号を生成できる。このとき、時間軸上の変化順は、BREN→WEN→VEN→FRENとなるので、RAMアドレスの更新はFRENの変化、すなわち#1一致検出パルスで行えばよい。

【0047】以上述べたように、FRENとBRENと位相関係は、順方向、逆方向いずれの場合においてもオフセット分だけ同一方向にずれるようになり、またFRENは、IDまたはセクタの規定位置に対して、少なくとも左側に常にマージンを持ち、BRENは少なくとも右側にマージンを持つようになる。

【0048】また、WEN、VENはコントローラ2の指示により、ディレイの基準をFRENかBRENか選択できる。よって、時間軸上で考えれば、FREN→WEN→VEN→BRENの順で変化させる場合とBREN→WEN→VEN→FRENの順で変化させる場合の2通りをコントローラは切り替えることができる。

【0049】なお、本実施の形態では、FRENの生成にRAM20とそのアドレス生成回路21を使用しているが、コントローラ2が直に変化点座標をデータ与えてもよい。

【0050】以上により、4種類のイネーブル信号FREN、WEN、VEN、BRENを生成する方法について説明した。次にこれらの利用法を説明する。以下では説明のため、RAMテーブルを書き換えない方法、すなわち、順方向ではFREN→WEN→VEN→BRENの順に変化し、逆方向ではBREN→WEN→VEN→FRENの順で変化する場合を用いている。RAMデータを書き換える場合は、逆方向でもFREN→WEN→VEN→BRENの順に変化するものとして考えればよい。

【0051】これまで説明した通り、本実施例に用いている光学系では、順方向と逆方向では先行するディテクタが異なり、それらが距離をもって配置されているため、リニアスケールなどの位置情報を元にリードイネーブル信号を生成する場合には、位置的に同一のリードイネーブル信号を、順方向/逆方向に共用できない。

【0052】本実施の形態では、順方向で先行するD3 に対応するリードイネーブルをFRENとし、逆方向で先行するD4 に対応するリードイネーブルをBRENとする。このとき、従来の手法を用いれば、本実施の形態でWEN、VENを元にD5、D4 用のリードイネーブル信号を生成、すなわち、WEN、VENの生成回路と同様な回路を、更に4系統設ける必要があった。

【0053】しかしながら、本実施の形態においては、D1 〜D3 の分散範囲、つまり図4に示すD3 有効受光範囲左端〜D1 有効受光範囲右端間の距離S1 を、隣り合うIDとセクタ、または隣り合うセクタ間の最小ギャップよりも小さくしている。これにより、D1 、D2 、D3 のリードイネーブル信号としてFRENを共用しても、D3 がリード対象セクタの先頭位置に達したときに、D1 がその前のIDまたはセクタのデータ領域にかかる事が無くなるため、D1 が所定のセクタのみをリードできる。

【0054】同様に、図4に示すD4 〜D3 間の距離S2 が最小ギャップよりも小さくなるように構成すれば、VENをD4 、D5 、D6 のリードイネーブル信号として共用できる。逆方向の場合は、D4 、D5 、D6 のリードイネーブルとしてBRENを用い、D1 、D2 、D3 のリードイネーブルとして、BRENを基準に時間的にディレイさせたVENを用いればよい。

【0055】さらに、図4に示すD3 〜D4 間の距離S1 を、最小ギャップよりも小さくなるように偏位させて構成すれば、順方向ではFRENをD1 〜D6 のリードイネーブル信号とし、逆方向ではBRENをD1 〜D6 のリードイネーブル信号としてよい。

【0056】また、本実施例ではD1 、D2 、D3 が入力される#1リード回路11と、D4 、D5 、D6 が入力される#2リード回路12を分けている。各リード回路11、12の内部は各ディテクタからの信号をパラレルに処理してもよいし、シリアルにしてもよいが、いずれにしても同一のスキャンでD3 とD4 が同一のトラック上のデータをリードする。コントローラ2は、通常のリード状態ではD1 、D2 、D3 、D5 、D6 のリードデータとしてもよいし、順方向はD1 、D2 、D3 、D5 、D6 とし、逆方向はD1 、D2 、D4 、D5 、D6 を使用するものとしてもよい。さらに、ライト時にライト直後のデータを、ライトビームよりも後行するディテクタ、すなわち順方向ライトではD4 、逆方向ではD3 をリードすることによって、同時ベリファイを実施して、ライトスピードを向上させることができる。

【0057】なお、本実施の形態では、光学系の構成上D0 とD6 、またはD1 とD0 の間隔が短いので、VENもWENと同様にディレイカウンタを使用しているが、BRENと同様にFRENにエンコーダ91の分解能単位のオフセットを加えて生成してもよい。

【0058】次に、本実施の形態における、位置カウンタ23のプリセットについて説明する。これまで述べてきた、リニアスケール8からの位置情報をもとにIDやセクタの位置決めを行う方法では、既知の場所を、座標軸上の特定の基準点としなければならない(原点にする必要はない)。本装置では、カード4を搬送台301に搭載しているので、搭載時のカードの収まり具合や、カード製造上の誤差などにより、例えば搬送台の可動限界位置〜前側ID左端までの距離は一定にならないため、カード上の特定の点を基準とする必要がある。カードはプリレコード部の形成を、版を押すようにして実施するため、前側ID〜後側IDの間隔は、温度変化による媒体の伸縮を考えても、規格値に対する誤差は非常に少ない。これに比べ、前述のような可動限界位置〜前側ID左端の距離は、カード毎に一定にならず、しかも非常に大きい。

【0059】このため、本実施の形態では、図12(b)で述べた光カードのID部100dの構成において、図6に示すように、順方向にスキャンする際には#1トラック番号情報部100d3をリードし、エラー訂正等を施してトラックと特定した後、同一のスキャンでの#3SYNC100d4の検出時点でプリセットを行う。逆方向であれば、#1SYNC100d4の検出で行う。プリセットしていない状態でリードすることになるが、このときはセクタをリードしないので、リードイネーブルは、IDを十分マージンを持たせてアクティブにすればよい。例えば、可動限界でオールゼロにプリセットし、カードの収まり等の誤差を考慮して十分な程度ID部を内包してインアクティブになるように、RAMのデータを設定しておけばよい。このとき、プリセットに成功すれば、同一のスキャンで直ちにリードやライトを実施してもよい。

【0060】ここで、マルチトラックリードでは、同時に複数のID部100dをリード可能であるため、各ディテクタ毎の読み取ったトラック番号を組み合わせて判断すれば、トラックの認識をより正確に行うことができる。例えば、図3において、D1 、D2 、D3 を利用して行う場合、トラック番号の特定に多数決論理を取り入れるなどの方法である。同様に、プリセットの検出タイミングとするSYNCの検出も、複数のトラックからの情報を取り入れれば、より正確になる。

【0061】しかしながら、例えば、D1 、D2 、D3 を利用してプリセットを実施する場合、共通のリードイネーブルを使用するので、各リード回路が動作し始めるのは同時であるのに対し、ディテクタはトラック方向に偏位しているため、ID部の例えば#3SYNCの検出は同時にならないことになる。このため、多数決判定を実施する場合は、図3でD1 とD2 で検出された場合とD1 とD3 で検出した場合では、プリセットのタイミングが異なってしまう。

【0062】このため、本実施の形態では、プリセットのためのSYNC検出において、図7のようにSYNC検出回路41〜43、ディレイ回路44、45を有する回路を用いる。図8は図7の動作を説明する図である。なお、図7の回路は、図1における#1リード回路11および/または#2リード回路12に含まれるものとする。

【0063】順方向でD1 、D2 、D3 による#3SYNC検出を組み合わせてプリセットを行う場合、検出タイミングはD3 →D2 →D1 となる。このとき、D3 で#3SYNCを検出した場合に限り、直ちにステータスをセットせずに#1ディレイ回路44を通してD1 で#3SYNCを検出するタイミングまで遅らせる。遅らせる時間は、D1 〜D3 間の距離をカードが移動するのに要する時間で一定である。同様に、D2 で#3SYNCを検出した場合に限り、直ちにステータスを立てずに#2ディレイ回路45を通してD1 で#3SYNCを検出するタイミングまで遅らせる。遅らせる時間は、D2 〜D3 間の距離をカードが移動するのに要する時間で一定である。

【0064】これによって、コントローラは、SYNC検出ステータスをポーリングするだけで、いずれかのディテクタで#3SYNCが検出されればD1 のSYNCステータスと同時にD2 、D3 のステータスが変化するので、例えば多数決判定など、所定のアルゴリズムで#3SYNC検出を判定できる。#3SYNCの検出ステータスは、あたかもトラックに垂直方向にD1 と整列してD2 、D3 が存在する場合と同様に変化するからである。

【0065】逆方向の場合は、検出タイミングはD1 →D2 →D3 であるから、#1ディレイ回路44を通す信号を#1SYNC検出信号として、#3SYNC検出信号は直にステータスFFに出力すればよい。

【0066】なお、本回路におけるディレイ回路44、45は、図2に開示したように、ディレイカウンタとコンパレータを用いれば簡単に実現でき、ディレイ量をコントローラが任意に設定できるようにして、意図的にSYNCステータスのタイミングをずらす事も可能である。

【0067】従って、このようにすれば、トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードのトラックに対し斜めに位置をずらしてマルチトラックリード用ビームの反射光を受光する複数のディテクタD1 〜D3 を配置し、これら複数のディテクタD1 〜D3 のうち、光カードの移動方向に対し少なくとも先頭ディテクタD1 が#1セクタのポストアンブルの検出を開始してから最後尾のディテクタD3 が#2セクタのプリアンブルの検出を開始するまでの期間TA でインアクティブとなる信号を複数のディテクタD1 〜D3 のリードイネーブル信号FRENとすることにより、ディテクタD1 〜D3 に共通のリードイネーブル信号FRENを用いることができ、マルチトラックリード用のイネーブル信号発生手段の回路構成を簡単にできるとともに、安定した動作を得られ、さらに、期間TA の範囲に複数のディテクタD1 〜D3の分散範囲が収まるようにすることで、複数のディテクタD1 〜D3 の分散範囲を最小限にできるので、マルチトラックリード用の光ピックアップを小型にでき、装置の小形化を実現できる。

【0068】ところで、図9に示すように光カードのトラックのID部に対するイネーブル信号が同図(b)に示すようにID部の直前に出力される場合は、同図(a)に示すようにエンベローブが正しくアクティブとなるが、例えば、イネーブル信号が同図(c)に示すように位置決めの誤りなどでずれるか、あるいはID部(またはセクタ)がもともと位置ずれを起こしているような場合、ブロックずれが発生し、本来、バッファメモリに図10(a)に示すように#1ブロック、#2ブロック、#3ブロックの順に格納されるものが、図10(b)に示すように#2ブロック、#3ブロック、#4ブロックの順となり、格納場所が誤ってしまう。これは、#1SYNC〜#3SYNCは、いずれも見た目に違いがなく、各ブロックにもブロック番号が付いていないためである。

【0069】そして、図10(b)に示すように誤ってバッファメモリに格納されると、データによっては、エラー訂正ができてしまうことがあり、誤訂正に陥ってしまうことがある。これは、エラー訂正不能よりはるかに深刻な問題でもある。

【0070】そこで、この他の実施の形態では、図1に示すように#1リード回路11および#2リード回路12に、さらにプリアンプル検出回路51を接続し、図9に示すID部のプリアンブルPRを検出したか否かのステータスを立てるようにしている。ここで、プリアンブルPRは、所定の“1”“0”のパターンからなるものである。そして、プリアンプル検出回路51では、プリアンブルPRに対し、例えば96ビットのうちの32ビットのパターンで検出するように設定する。このパターンは、可変にしてもよい。

【0071】このような構成において、プリアンプル検出回路51が#1SYNCを検出した時点でプリアンブルパターンが見付かっていれば、通常の復調動作を続けるが、プリアンブルパターンが見付かっていなければ、最初に検出したSYNCが#2でブロックずれを発生した可能性があるため、プリアンプル検出回路51よりコントローラ2に対しプリアンブルPRが検出できなかったことを通知し、復調動作や図示しないホストコンピュータへの転送などを中止させるようにする。

【0072】なお、#1ブロックにプリアンブルPRと認識できるパターンがデータとして記録されており、なおかつ、ブロックずれを起こす場合に備えて、さらにエンベローブがアクティブになってから、一定範囲でのみプリアンブル検出をアクティブにしたり、最終ブロックの後にポストアンブルがあることを確認するなどすることで、さらにブロックずれの発生確率を減らすようにもしている。

【0073】このように、この他の実施の形態では、再生情報の復調に当たり、本来ビットクロックの引き込み用途しかないプリアンブルパターンを使用して、#1SYNC検出前にプリアンブルが検出されない場合は、この旨をコントローラに通知して復調動作などのを中止させるようにしたので、ブロックずれによる誤動作を確実に防止することができる。

【0074】以上、実施の形態に基づいて説明したが、本発明中には、以下の発明が含まれる。

(1)トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらしてマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段と、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの間に前記複数のディテクタの出力に用いられるリードイネーブル信号をインアクティブとするリードイネーブル信号発生手段とを具備したことを特徴とする情報再生装置。

【0075】このようにすれば、マルチトラックリードのための複数のディテクタに共通のリードイネーブル信号を用いることができるので、マルチトラックリード用のイネーブル信号発生手段の回路構成を簡単にできるとともに、安定した動作を得られる。

【0076】(2)(1)記載の情報再生装置において、リードイネーブル信号発生手段は、先のセクタと次のセクタとの間のギャップでアクティブからインアクティブへ変化するようなリードイネーブル信号を発生するようにしている。

【0077】このようにすれば、セクタからのデータを余裕を持って取り込んだのちにリードイネーブル信号をインアクティブにするようにできので、安定した情報の再生を行うことができる。

【0078】(3)トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらしてマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段を具備し、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの範囲に前記複数のディテクタの分散範囲が収まるようにしたことを特徴とする情報再生装置。

【0079】このようにすれば、共通のリードイネーブル信号を用いることができるのに加え、複数のディテクタの分散範囲を最小限にできるので、さらにマルチトラックリード用の光ピックアップを小型にでき、装置の小形化を実現できる。

【0080】(4)リードイネーブル信号発生手段より発生されるリードイネーブル信号は、リードしようとするセクタの規定開始位置よりも早く、かつ、規定終了位置よりも遅いタイミングでアクティブになる。このようにすれば、セクタからのリードを確実なものにできる。

【0081】

【発明の効果】以上述べたように本発明によれば、マルチトラックリードのための複数のディテクタに共通のリードイネーブル信号を用いることができ、マルチトラックリード用のイネーブル信号発生手段の回路構成を簡単にできるとともに、安定した動作を得られる。また、複数のディテクタの分散範囲を最小限にできるので、光ピックアップを小型にでき、装置の小形化を実現できる。

【図面の簡単な説明】

【図1】本発明の一実施の形態の概略構成を示す図。

【図2】一実施の形態に用いられるイネーブル信号生成回路の概略構成を示す図。

【図3】一実施の形態に用いられるイネーブル信号の役割を説明するための図。

【図4】一実施の形態の動作を説明するためのタイムチャート。

【図5】一実施の形態の動作を説明するための図。

【図6】一実施の形態の位置カウンタのプリセットについて説明するための図。

【図7】一実施の形態の位置カウンタのプリセットのためのSYNC検出を説明するための図。

【図8】一実施の形態の位置カウンタのプリセットのためのSYNC検出を説明するためのフローチャート。

【図9】本発明の他の実施の形態を説明するための図。

【図10】同他の実施の形態を説明するための図。

【図11】光カードの概略構成を示す図。

【図12】光カードのトラック部の概略構成を示す図。

【図13】マルチトラックリード用のディテクタの配置例を示す図。

【符号の説明】

1…搬送台駆動回路、

2…コントローラ、

301…搬送台(可動部)、

302…搬送台(駆動部)、

4…光カード、

5…ピックアップ駆動回路、

6…ピックアップ、

7…フォーカス/サーボ回路、

8…リニアスケール、

9…イネーブル信号生成回路

91…エンコーダ、

11…#1リード回路、

12…#2リード回路、

13…選択回路、

20…RAM、

21…RAMアドレス生成回路、

22…#1トグルFF、

23…位置カウンタ、

24…#1コンパレータ、

241…ディレイカウンタリセット信号生成回路、

25…ディレイカウンタ、

26…#3コンパレータ、

27…#3トグルFF、

28…#4コンパレータ、

29…#4トグルFF、

30…#2コンパレータ、

31…オフセット加算回路、

32…#2トグルFF、

33…RAMアドレス更新パルス生成回路、

41〜43…SYNC検出回路、

44、45…ディレイ回路、

51…プリアンプル検出回路。

【特許請求の範囲】

【請求項1】 トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらして照射したマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段と、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの間に前記複数のディテクタの出力に用いられるリードイネーブル信号をインアクティブとするリードイネーブル信号発生手段とを具備したことを特徴とする情報再生装置。

【請求項2】 リードイネーブル信号発生手段は、先のセクタと次のセクタとの間のギャップでアクティブからインアクティブへ変化するようなリードイネーブル信号を発生することを特徴とする請求項1記載の情報再生装置。

【請求項3】 トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらして照射したマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段を具備し、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの範囲に前記複数のディテクタの分散範囲が収まるようにしたことを特徴とする情報再生装置。

【請求項1】 トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらして照射したマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段と、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの間に前記複数のディテクタの出力に用いられるリードイネーブル信号をインアクティブとするリードイネーブル信号発生手段とを具備したことを特徴とする情報再生装置。

【請求項2】 リードイネーブル信号発生手段は、先のセクタと次のセクタとの間のギャップでアクティブからインアクティブへ変化するようなリードイネーブル信号を発生することを特徴とする請求項1記載の情報再生装置。

【請求項3】 トラック上に、プリアンブル、データ部本体およびポストアンブルを有する複数のセクタを形成する光カードに対し、トラック方向に互いの位置をずらして照射したマルチトラックリード用のリードビームの反射光を受光する複数のディテクタを配置した光カードの情報再生装置において、前記複数のディテクタの出力により前記セクタのデータ部本体の信号を再生する再生手段を具備し、前記マルチトラックリードのための複数のディテクタのうち、前記光カードの移動方向に対し少なくとも先頭ディテクタが先のセクタのポストアンブルの検出を開始してから最後尾のディテクタが次のセクタのプリアンブルの検出を開始するまでの範囲に前記複数のディテクタの分散範囲が収まるようにしたことを特徴とする情報再生装置。

【図1】

【図3】

【図5】

【図6】

【図2】

【図4】

【図8】

【図10】

【図7】

【図9】

【図11】

【図13】

【図12】

【図3】

【図5】

【図6】

【図2】

【図4】

【図8】

【図10】

【図7】

【図9】

【図11】

【図13】

【図12】

【公開番号】特開平10−334466

【公開日】平成10年(1998)12月18日

【国際特許分類】

【出願番号】特願平9−136754

【出願日】平成9年(1997)5月27日

【出願人】(000000376)オリンパス光学工業株式会社 (11,466)

【公開日】平成10年(1998)12月18日

【国際特許分類】

【出願日】平成9年(1997)5月27日

【出願人】(000000376)オリンパス光学工業株式会社 (11,466)

[ Back to top ]