情報処理システム、情報処理装置、情報保持装置および情報処理方法

【課題】 紙に置き換えることが可能な利便性を有する情報表示装置を実現すること。

【解決手段】 情報処理システム1は、記憶性の表示パネル14を備える情報担体10と、バッテリ27を含む処理ユニット20とを別体の構成としながら、表示パネル14に表示された情報の更新や、表示された情報に対する操作等、処理を行う必要が生じた場合には、処理ユニット20を情報担体10と接続することにより、所望の処理を行うことが可能となる。そのため、「紙」に近い表示装置として本来的に必要な機能である「表示」を維持する以外の構成物を、通常の使用時において、情報処理システム1から切り離すことが可能となる。したがって、紙に置き換えることが可能な利便性を有する情報表示装置を実現することが可能となる。

【解決手段】 情報処理システム1は、記憶性の表示パネル14を備える情報担体10と、バッテリ27を含む処理ユニット20とを別体の構成としながら、表示パネル14に表示された情報の更新や、表示された情報に対する操作等、処理を行う必要が生じた場合には、処理ユニット20を情報担体10と接続することにより、所望の処理を行うことが可能となる。そのため、「紙」に近い表示装置として本来的に必要な機能である「表示」を維持する以外の構成物を、通常の使用時において、情報処理システム1から切り離すことが可能となる。したがって、紙に置き換えることが可能な利便性を有する情報表示装置を実現することが可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の装置が連携して処理を実行する情報処理システム、情報処理装置、情報保持装置および情報処理方法に関する。

【背景技術】

【0002】

従来、PC(Personal Computer)等の情報処理装置は、処理対象のデータを装置内部に備えたり、処理対象のデータを記憶している記憶媒体あるいはネットワーク上のリソースと接続したりすることで、その処理過程において、処理対象となる情報を包括的に保持した状態で処理を行っている。即ち、従来の情報処理装置は、処理すべき情報を装置上に集約する形態のシステム構成とされている。

【0003】

そして、従来の情報処理装置においては、複数の処理対象情報を並行して処理するためのマルチタスク機能が備えられ、タスクの優先度や処理経過に応じてスケジューリングし、マルチタスク処理を実行している(例えば、特許文献1参照)。

【特許文献1】特開2004−220070号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、従来の情報処理装置においては、処理すべき情報を装置上に集約する形態のシステム構成であるため、情報処理装置の性能や特性の制約を免れず、例えば、ユーザインターフェースとしても、情報処理装置が小型のものであれば、ユーザは狭い画面を凝視しつつ、姿勢を制限された状態で操作することを余儀なくされる。

また、処理対象の情報が装置に集約され、無体化した状態となっているため、処理装置の操作時以外は、ユーザにとって処理対象の情報を認識し難いものとなる。したがって、処理対象の情報に対する現実感が喪失され易く、重要な処理対象の存在を忘れてしまう等の事態を生じ得る。反対に、このような事態を懸念するあまり、いわゆるサイバーストレスといった負担をユーザに与えることもあり得る。

【0005】

さらに、例えば商品の伝票の情報のように、処理対象の情報が物品に伴われる等して移動する場合もあり、このような状況においては、処理対象の情報を、複数の処理装置によって断続的に取り扱うこととなる。そして、このような場合には、処理対象の情報を装置上に集約することは適切でない。

一方、上述のような問題を単純に解決しようとする場合、処理対象の情報毎に情報処理装置を用意しておくことが考えられるが、それぞれの情報処理装置に電源を用意する必要がある等、コストおよび省資源の面から不適当な対策であると考えられる。

【0006】

即ち、従来の情報処理装置にように、処理すべき情報を装置上に集約する形態の情報処理装置においては、情報処理装置ではなく処理対象の情報を主体として取り扱うことが困難であり、有体物として情報を認識し難く、ユーザにとって必ずしも利便性の高くないものとなる場合があった。

本発明の課題は、装置によって情報を取り扱う上で、処理対象の情報を主体として取り扱うことを容易とすると共に、有体物として情報を認識し易く、ユーザにとって利便性の高いものとすることである。

【課題を解決するための手段】

【0007】

以上の課題を解決するため、本発明は、

所定の接続動作によって互いに通信可能となる情報処理装置(例えば、図1の処理ユニット20あるいは図7の処理ユニット120)と情報保持装置(例えば、図1の情報担体10あるいは図7の情報担体110)とを含む情報処理システムであって、前記情報保持装置は、所定の情報処理に係る処理コンテキストを記憶する処理コンテキスト記憶手段(例えば、図2のNVRAM12あるいは図7のNVRAM112)を備え、前記情報処理装置は、通信可能となった前記情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに所定処理を施し、処理結果である処理コンテキストを前記情報保持装置の処理コンテキスト記憶手段に記憶する情報処理手段(例えば、図2のCPU22あるいは図7のCPU122)を備えることを特徴としている。

【0008】

このような構成により、情報処理装置が情報保持装置に接続されると、その都度、情報保持装置の処理コンテキストが情報処理装置に復帰され、情報処理装置は、所定処理を実行する。その後、情報処理装置は、処理結果の処理コンテキストを情報保持装置に退避した後、情報保持装置との接続を解除される。

そのため、処理対象の情報が、情報保持装置と一体化したものとして認識され、複数の情報処理装置によって、いずれの情報処理装置も区別することなく情報を取り扱うこと等が可能となる。

【0009】

したがって、装置によって情報を取り扱う上で、処理対象の情報を主体として取り扱うことが容易となると共に、有体物として情報を認識し易く、ユーザにとって利便性の高いものとすることができる。

また、前記情報保持装置は、所定のアプリケーションプログラムを記憶するアプリケーション記憶手段(例えば、図7のROM115)をさらに備え、前記処理コンテキスト記憶手段は、前記アプリケーションプログラムに係る処理コンテキストを記憶することを特徴としている。

【0010】

このような構成により、情報保持装置に所定の機能を持たせることが可能となり、ユーザに対し、情報保持装置を所定のアプリケーションと一体的なものと認識させることが可能となる。

また、前記情報保持装置は、所定処理にそれぞれ対応した、前記情報処理装置と接続するための接続手段(例えば、図2の接続部17あるいは図7の接続部116)を複数備え、前記情報処理手段は、自装置が接続された前記接続手段が対応している所定処理を判定する判定手段(例えば、図2のCPU22あるいは図7のCPU122)を備え、該接続手段に接続された前記情報処理装置の情報処理手段は、前記判定手段によって判定された所定処理を行い、その処理結果である処理コンテキストを前記処理コンテキスト記憶手段に記憶することを特徴としている。

【0011】

このような構成により、ユーザは、接続手段を選択して情報処理装置を接続させることで、意図する処理を行わせることが可能となる。

また、前記情報処理装置と前記情報保持装置との接続を解除可能であることを報知する報知手段(例えば、図7の振動素子124)をさらに備え、前記情報処理装置の情報処理手段は、所定処理を施した結果である前記処理コンテキストを前記処理コンテキスト記憶手段に記憶した後、前記報知手段によって、前記情報保持装置との接続を解除可能であることを報知することを特徴としている。

【0012】

このような構成により、ユーザに対し、情報保持装置と情報処理装置との接続を解除可能なタイミングを知らせることが可能となる。

また、前記情報保持装置は、前記情報処理装置の電源から電力の供給を受けて動作することを特徴としている。

このような構成により、情報保持装置に重量の比較的大きい電源を備える必要がなくなり、情報保持装置を軽量なものとすることができる。

【0013】

また、前記情報保持装置は、表示状態を不揮発的に保持可能な記憶性の表示装置を備えることを特徴としている。

このような構成により、情報保持装置は、情報処理装置と接続されていない場合にも、処理状態を不揮発的に表示することが可能となり、情報保持装置を、記憶している情報と一体の有体物として認識させることが容易となる。

【0014】

また、本発明は、

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを含む情報処理システムにおける情報処理装置であって、所定の情報処理に係る処理コンテキストを記憶する前記情報保持装置と通信可能となった場合に、該情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに対し、前記所定処理を施し、処理結果である処理コンテキストを前記情報保持装置の処理コンテキスト記憶手段に記憶する情報処理手段を備えることを特徴としている。

【0015】

また、本発明は、

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを含む情報処理システムにおける情報保持装置であって、所定の情報処理に係る処理コンテキストを記憶する処理コンテキスト記憶手段を備え、通信可能となった前記情報処理装置に対し、前記処理コンテキスト記憶手段に記憶された処理コンテキストを出力すると共に、前記情報処理装置の処理結果である処理コンテキストを前記処理コンテキスト記憶手段に記憶することを特徴としている。

【0016】

また、本発明は、

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを用いた情報処理方法であって、前記情報保持装置が、所定の情報処理に係る処理コンテキストを記憶し、前記情報処理装置が、通信可能となった前記情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに所定処理を施し、処理結果である処理コンテキストを前記情報保持装置に記憶させることを特徴としている。

【0017】

このように、本発明によれば、装置によって情報を取り扱う上で、処理対象の情報を主体として取り扱うことを容易とすると共に、有体物として情報を認識し易く、ユーザにとって利便性の高いものとすることが可能となる。

より具体的には、紙と同様な自由な使用形態で、紙と同様の安心感のある形態で情報を取り扱うことが可能な情報表示装置を、比較的安価に実現することが可能となる。

【発明を実施するための最良の形態】

【0018】

以下、図を参照して本発明に係る情報表示装置の実施の形態を説明する。

(第1の実施の形態)

本実施の形態においては、情報表示装置を電子ブックとして使用し、電子ブックのコンテンツを、情報担体に具現化された有体物として取り扱う場合を例に挙げて説明する。

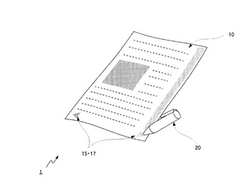

図1は、本発明の第1の実施の形態に係る情報処理システム1の外観構成を示す図であり、図2は、情報処理システム1の機能構成を示すブロック図である。

【0019】

図1および図2において、情報処理システム1は、紙のように軽薄な形態を有する情報担体10と、ペン型の処理ユニット20とによって構成されている。

情報担体10は、データ記憶部11と、NVRAM(Non-Volatile Random Access Memory)12と、表示駆動部13と、表示パネル14と、指示入力部15と、接続制御部16と、接続部17とを含んで構成され、これらはバス18によって通信可能に接続されている。

【0020】

データ記憶部11は、フラッシュメモリ等の不揮発性のメモリによって構成され、後述する接続部17を介してデータインターフェース(以下、「データI/F」と称する。)21から入力されたデータを記憶可能である。

NVRAM12は、FeRAM/FRAM(Ferroelectric Random Access Memory)、MRAM(Magnetoresistive Random Access Memory)等のメモリによって構成され、CPU22が処理を実行する際にワークエリアを形成すると共に、その処理結果を記憶する。

【0021】

表示駆動部13は、表示パネル14を直接制御し、後述するグラフィックアクセラレータ(以下、「GA」と称する。)24から入力された描画データを表示パネル14に表示させる。具体的には、表示駆動部13は、GA24によって図形データが入力される描画データ書き込み部13aを備えている。そして、表示駆動部13は、描画データ書き込み部13aに入力された描画データを参照して、表示パネル14のXドライバおよびYドライバを駆動することにより、描画対象であるラスタ図形を表示パネル14に表示させる。

【0022】

なお、表示パネル14を駆動する方式として、例えば、パッシブマトリクス駆動方式、TFT(Thin Film Transistor)方式、TFD(Thin Film Diode)方式、D−TFD(Digital Thin Film Diode)方式等が採用可能である。

表示パネル14は、A4サイズの高画素密度(多ピクセル)である表示装置によって構成され、表示駆動部13の制御に応じて、所定画素に画素データを表示する。

【0023】

また、表示パネル14として、記憶性の表示装置(電源を切断しても表示画面が維持される表示装置)が使用される。したがって、表示画面の状態を維持するためには電力が不要となることから、情報処理システム1を低消費電力化することができる。

なお、表示パネル14として、例えば、電気泳動ディスプレイ、コレステリック液晶ディスプレイ、帯電トナーを利用したディスプレイ、ツイストボールを利用したディスプレイあるいはエレクトロデポジションディスプレイ等が採用可能である。

【0024】

指示入力部15は、所定のユーザインターフェースを備え、ユーザによる指示入力を受け付ける。この指示入力部15としては、押しボタン等の機械的なインターフェースや、後述する接続部17の機能を兼ね備えた電磁的なインターフェースとすることが可能である(図3参照)。

接続制御部16は、接続部17を介して行われる情報および電力の入出力を制御する。

【0025】

即ち、接続制御部16は、表示駆動部13あるいは指示入力部15から入力されるパラレルデータをシリアルデータに変換して、接続部17に出力したり、接続部17から入力されるシリアルデータをパラレルデータに変換して、データ記憶部11、NVRAM12、表示駆動部13あるいは指示入力部15に出力したりする。接続制御部16がこのような処理を行い、後述するように、処理ユニット20側の接続制御部25が同様の処理を行うことにより、バス18と処理ユニット20のバス28との間で送受信される情報が、双方向にシリアル変換され、バス18と処理ユニット20のバス28とがバス間接続された状態となる。

【0026】

また、接続制御部16は、接続部17を介して処理ユニット20から電力が供給されていることを検出し、接続部17を介して入力された交流電力を整流した上で、データ記憶部11、NVRAM12、表示駆動部13あるいは指示入力部15に出力する。

接続部17は、情報担体10と処理ユニット20との間で情報および電力を入出力するためのインターフェースである。具体的には、接続部17は、情報の入出力を行うためのコイルと、電力の入出力を行うためのコイルとを備えており、処理ユニット20の接続部26に同様に備えられている2つのコイルそれぞれと電磁的に結合することによって、情報および電力を入出力する。なお、接続部17と接続部26との間においては、上述のコイルによって情報および電力を同時に入出力することや、情報および電力を伝達する際に、互いに干渉することを確実に防ぐため、時分割により、それぞれを切り替えて入出力することが可能である。

【0027】

なお、異なる指示入力内容それぞれに対応する接続部17を備えることにより、接続部17が、電磁的なユーザインターフェースからなる指示入力部15の機能を兼ね備える構成とすることが可能である。

図3は、接続部17が、電磁的なユーザインターフェースからなる指示入力部15の機能を兼ね備える構成例を示す図である。

【0028】

図3において、左側の接続部17は、図2におけるページ捲りボタンに対応する指示入力部15の機能を備え、処理ユニット20が左側の接続部17に接続されると、電力の供給および情報の入出力が行われると共に、ページを捲る旨の指示入力が行われる。同様に、右側の接続部17は、図2におけるページ戻りボタンに対応する指示入力部15の機能を備え、処理ユニット20が右側の接続部17に接続されると、電力の供給および情報の入出力が行われると共に、ページを戻す旨の指示入力が行われる。

【0029】

なお、図3においては、各ボタンに対応する位置に接続部17が備えられる例について説明したが、情報担体10の全面にわたって、接続部17をマトリクス状に備えておくことも可能である。このような構成により、処理ユニット20が接続された情報担体10上の位置を把握できるため、表示された文書を選択する等、多様な処理を行うことが可能となる。

【0030】

次に、処理ユニット20は、データI/F21と、CPU22と、記憶部23と、GA24と、接続制御部25と、接続部26と、バッテリ27とを含んで構成され、これらはバス28によって通信可能に構成されている。

データI/F21は、処理ユニット20外部からデータを入力することが可能なインターフェースであり、例えば、通信インターフェースあるいは記憶メディアのスロット等によって構成される。そして、データI/F21を介して入力されたデータは、接続部26から情報担体10に出力され、情報担体10のデータ記憶部11に記憶される。

【0031】

CPU22は、情報処理システム1全体を制御するもので、指示入力部15から入力される各種の指示信号に従って、記憶部23のプログラム記憶部23aに記憶された各種処理に関するプログラムを読み出して実行する。また、CPU22は、データ記憶部11あるいはデータI/F21に差し込まれた記憶メディアに記憶されているコンテンツデータを表示パネル14に表示するための処理を行う。そして、CPU22は、各種処理結果を記憶部23のRAM23bに格納する。

【0032】

記憶部23は、フラッシュメモリ等の不揮発性のメモリからなるプログラム記憶部23aを備えており、このプログラム記憶部23aは、情報処理システム1を制御するための各種プログラムを記憶している。

また、記憶部23は、DRAM(Dynamic Random Access Memory)あるいはSRAM(Static Random Access Memory)等の揮発性のメモリからなるRAM23bを備え、RAM23bは、CPU22が処理を実行する際に生成される各種データを一時的に保持することが可能である。RAM23bとしては、低消費電力でデータを保持可能なSRAM等が望ましく、不揮発性のFeRAM/FRAMやMRAM等がより望ましい。

【0033】

GA24は、CPU22の命令に従って、表示パネル14に表示する画像の描画処理を高速に行うことが可能なハードウェアである。具体的には、GA24は、CPU22から入力されたベクトル図形をラスタ図形に展開するといった処理を行う。そして、GA24は、描画処理を行った図形を表示パネル14に描画するための描画データを表示駆動部13に出力する。

【0034】

接続制御部25は、接続部26を介して行われる情報および電力の入出力を制御する。即ち、接続制御部25は、CPU22、記憶部23、GA24あるいはバッテリ27から入力されるパラレルデータをシリアルデータに変換して、接続部26に出力したり、接続部26から入力されるシリアルデータをパラレルデータに変換して、CPU22、記憶部23、GA24あるいはバッテリ27に出力したりする。また、接続制御部25は、バッテリ27から入力された直流電力を交流化し、接続部26に出力する。

【0035】

接続部26は、情報担体10と処理ユニット20との間で情報および電力を入出力するためのインターフェースである。具体的には、接続部26は、情報の入出力を行うためのコイルと、電力の入出力を行うためのコイルとを備えており、情報担体10の接続部17に同様に備えられている2つのコイルそれぞれと電磁的に結合することによって、情報および電力を入出力する。

【0036】

バッテリ27は、一次電池あるいは二次電池によって構成され、情報処理システム1の各部に電力を供給する。

上述のような構成の下、情報処理システム1が所定のプログラムを実行することにより、図2に示す解析・整形部110および描画処理部120を実現することが可能となる。

解析・整形部110は、データ記憶部11に記憶された文書データを中間形式に変換する。具体的には、文書データを描画要素に分解し、高速に表示処理できる形式(中間形式)で記述する。

【0037】

描画処理部120は、解析・整形部110によって中間形式とされたデータを、表示パネル14に表示するための描画処理を行う。例えば、描画処理部120は、中間形式に含まれる描画要素をラスタ化する処理等を行う。

次に、動作を説明する。

本実施の形態に係る情報処理システム1は、情報担体10の接続部17と処理ユニット20の接続部26とが電磁的に結合されることにより、処理ユニット20から情報担体10に電力が供給されると共に情報の入出力が可能な状態となり、情報処理システム1全体として動作可能となる。

【0038】

そして、処理ユニット20のデータI/F21を介して文書データが入力されると、その文書データが情報担体10のデータ記憶部11に記憶される。なお、データI/F21が記憶メディアのスロットである場合、データ記憶部11にデータを記憶することなく、スロットに差し込まれた記憶メディアから直接データを読み出して利用することとしてもよい。

【0039】

すると、処理ユニット20上に構成された解析・整形部110が、文書データの処理を開始する。即ち、解析・整形部110は、文書データの文書構造を解釈し、その構造に従って、画面表示のためのレイアウト処理を行う。そして、解析・整形部110は、レイアウト処理された文書データを中間形式のデータとしてNVRAM12に記憶する。

なお、このとき、情報担体10のNVRAM12は、スタティックデータ領域(処理中のページ番号等、処理の状態を表すデータを記憶する領域)としても使用される。

【0040】

次に、描画処理部120は、NVRAM12に記憶された中間形式のデータから描画データを生成し、表示駆動部13の描画データ書き込み部13aに書き込む。

すると、表示駆動部13は、描画データ書き込み部13aに書き込まれた描画データに応じて表示パネル14を駆動し、表示パネル14に文書が表示される。

また、処理ユニット20が接続部17から切り離されると、情報担体10には電力が供給されない状態となり、各部の動作が停止する。

【0041】

ただし、表示パネル14は記憶性を有することから、処理ユニット20から電力の供給が停止された後も、引き続き、表示された状態が維持され、同様に、NVRAM12に記憶されたスタティックデータおよび中間形式のデータも、NVRAM12の不揮発性により保持される。さらに、データ記憶部11も不揮発性のメモリであることから、データ記憶部11に記憶された文書データも保持される。

【0042】

このように、情報担体10は、電力の供給が行われていない状態、即ち、処理ユニット20から切り離され、情報担体10単独の状態でも、情報を表示し続けることが可能であるため、紙と同様の操作性を実現することができる。

さらに、一旦切り離された処理ユニット20を、情報担体10に再度接続すると、CPU22は、NVRAM12に記憶されたスタティックデータを確認し、有効なデータであると判定した場合には、文書データの表示処理を、現在の表示状態から継続させる。なお、NVRAM12に記憶されたスタティックデータが有効なものであるか否かは、データ形式が処理ユニット20の処理対象として適合するものかどうかによって判定したり、スタティックデータにチェックサムを付加しておき、そのチェックサムによって判定したりすることが可能である。

【0043】

また、本実施の形態においては、処理ユニット20が情報担体10に対する操作子となっているため、ユーザがページを捲る等の操作を行う場合、上述のように、処理ユニット20が情報担体10から切り離され、再度接続される動作が逐次行われる。即ち、ユーザが操作を行う場合、処理ユニット20を情報担体10に接続することにより、指示入力部15を介してページを捲る旨の指示信号を入力したり、あるいは、処理ユニット20に備えられた不図示の指示ボタン等からページを捲る旨の指示信号を入力したりする。

【0044】

すると、入力された指示信号は、CPU22に入力され、CPU22が、指示に応じた処理を行う。

また、本実施の形態においては、処理ユニット20が情報担体10に対する操作子となっているため、ユーザがページを捲る等の操作を行う場合、上述のように、処理ユニット20が情報担体10から切り離され、再度接続される動作が逐次行われる。即ち、ユーザが操作を行う場合、処理ユニット20を情報担体10に接続することにより、指示入力部15を介してページを捲る旨の指示信号を入力したり、あるいは、処理ユニット20に備えられた不図示の指示ボタン等からページを捲る旨の指示信号を入力したりする。

【0045】

すると、入力された指示信号は、CPU22に入力され、CPU22が、指示に応じた処理を行う。

このように、表示される文書に関連する情報(文書データ、中間形式のデータおよびスタティックデータ)を情報担体10側に記憶しておくことにより、処理ユニット20には、接続された情報担体10と不可分のデータが残されないため、接続する情報担体10を任意のタイミングで異なるものに変更することが可能となる。

【0046】

以上のように、本実施の形態に係る情報処理システム1は、記憶性の表示パネル14を備える情報担体10と、バッテリ27を含む処理ユニット20とを別体の構成としながら、表示パネル14に表示された情報の更新や、表示された情報に対する操作等、処理を行う必要が生じた場合には、処理ユニット20を情報担体10と接続することにより、所望の処理を行うことが可能となる。

【0047】

そのため、「紙」に近い表示装置として本来的に必要な機能である「表示」を維持する以外の構成物を、通常の使用時において、情報処理システム1から切り離すことが可能となる。

したがって、「紙」に近い良好な表示品質と、情報の再利用性(表示された情報を電子データとして取り扱う機能)とを兼ね備えつつ、装置自体を軽装化することができるため、従来の情報表示装置に比べ、操作性を大幅に向上させることが可能となる。

【0048】

なお、本実施の形態における情報担体10を図4に示す構成とすることによって、複数の情報担体10それぞれを識別して取り扱うことも可能である。

図4は、情報担体10それぞれが、個々の情報担体10を識別するためのID記憶部10Pを備える構成を示している。

このような構成とした場合、IDによって種々の管理を行いつつ、1つの処理ユニット20が複数の情報担体10を操作することが可能となる。具体的には、表示対象であるデータが処理ユニット20に記憶されている場合あるいはネットワーク上のサーバに記憶されている場合等であっても、情報担体10と対応付けることが可能となる。したがって、情報処理システム1の用途の幅を広げることができる。

【0049】

また、本実施の形態においては、表示パネル14が記憶性の表示体を備える例について説明したが、記憶性を有する表示体に代えて、記憶性を有しない表示体と、その表示状態を維持するための小規模な電源とを併せ持つ構成とすることも可能である。

図5は、記憶性の表示体に代えて、記憶性を有しない表示体と、その表示状態を維持するための小規模な電源(保持電源10Q)とを併せ持つ情報担体10の構成を示す図である。

【0050】

このような構成により、非記憶性の表示体を用いる場合でも、実質的に記憶性を有する表示体として利用することができる。

また、本実施の形態においては、CPU22、記憶部23、GA24が処理ユニット20に備えられる構成について説明したが、バッテリ27以外の構成部分については、処理ユニット20あるいは情報担体10のいずれに備えられることとしても良い。

(第2の実施の形態)

次に、本発明の第2の実施の形態について説明する。

【0051】

本実施の形態においては、情報表示装置を電卓として使用し、情報処理におけるコンテキストを、情報担体に具現化された有体物として取り扱う場合を例に挙げて説明する。

図6は、本発明の第2の実施の形態に係る情報処理システム2(情報担体側)の外観構成を示す図であり、図7は、情報処理システム2の機能構成を示すブロック図である。

図6および図7において、情報処理システム2は、紙のように軽薄な形態を有する情報担体110と、ペン型の処理ユニット120とによって構成されている。

【0052】

情報担体110は、データ記憶部111と、NVRAM112と、表示駆動部113と、表示パネル114と、ROM(Read Only Memory)115と、接続部116とを含んで構成され、これらはバス118によって通信可能に接続されている。

データ記憶部111は、フラッシュメモリ等の不揮発性のメモリによって構成され、後述する接続部116を介して処理ユニット120から入力されたデータや、情報担体110上に表示可能な各種書類データを記憶する。

【0053】

NVRAM112は、FeRAM/FRAM、MRAM等のメモリによって構成され、CPU122が処理を実行する際に生成されたコンテキストや、情報担体110側に保持されるコンテキスト(以下、これらを「処理コンテキスト」と称する。)を記憶する。

図8は、NVRAM112に記憶される処理コンテキストの一例を示す図である。

図8においては、処理コンテキストとして、情報担体110を電卓として機能させるプログラムにおける各種変数を示している。

【0054】

なお、このような処理コンテキストは、処理ユニット120が接続されている場合には、CPU122内のレジスタやRAM123に記憶することも可能である。ただし、この場合、処理ユニット120と情報担体110との接続が解除される際に、処理ユニット120側に記憶されているコンテキストは、情報担体110のNVRAM112に退避される。

【0055】

表示駆動部113は、表示パネル114を直接制御し、CPU122から入力された描画データを表示パネル114に表示させる。

表示パネル114は、高画素密度(多ピクセル)である表示装置によって構成され、表示駆動部113の制御に応じて、所定画素に画素データを表示する。

また、表示パネル114として、記憶性の表示装置(電源を切断しても表示画面が維持される表示装置)が使用される。したがって、表示画面の状態を維持するためには電力が不要となることから、情報処理システム1を低消費電力化することができる。

【0056】

ROM115は、EEPROM(Electrically Erasable Programmable Read-Only Memory)等の不揮発性の半導体メモリによって構成され、情報担体110におけるコンテンツを実現するためのアプリケーションプログラムを記憶している。

接続部116は、情報担体110と処理ユニット120との間で情報および電力を入出力するためのインターフェースである。具体的には、接続部116は、超広帯域の近接無線(例えば、UWB:Ultra Wide Band等)による通信装置と、電力の入出力を行うためのコイルとを備えており、処理ユニット120の接続部126に同様に備えられている通信装置と無線により接続し、また、接続部126のコイルと電磁的に結合することによって、情報および電力を入出力する。

【0057】

また、接続部116は、異なる指示入力内容それぞれに対応して備えられており、それぞれの接続部116を識別するためのID記憶素子が、各接続部116に備えられている。

即ち、図6に示すように、情報担体110は、電卓のユーザインターフェースを表示しており、各ボタン部分に、各ボタンを識別するID記憶素子を備えた接続部116が設けられている。

【0058】

そのため、例えば、“1”のボタンに対応する接続部116に処理ユニット120を接続すると、電力の供給および情報の入出力が行われると共に、ボタン“1”の接続部116を識別するIDがCPU122に入力される。そして、CPU122がボタン“1”に対応するアプリケーションを実行する。

なお、ここでは、各ボタンに対応する位置に接続部116が備えられる例について説明したが、情報担体10の全面にわたって、接続部116をマトリクス状に備えておくことも可能である。このような構成により、処理ユニット120が接続された情報担体110上の位置を把握できるため、表示された領域を選択する等、多様な処理を行うことが可能となる。

【0059】

次に、処理ユニット120は、ROM121と、CPU122と、RAM123と、振動素子124と、バッテリ125と、接続部126とを含んで構成され、バッテリ125以外の各部はバス127によって通信可能に構成されている。

ROM121は、EEPROM等の不揮発性の半導体メモリによって構成され、オペレーティングシステムプログラム(OS)等、処理ユニット120を制御するための各種プログラムを記憶している。

【0060】

CPU122は、情報処理システム2全体を制御するもので、接続部126によって情報担体110との接続が検出されると、その検出信号を割り込み信号として起動され、ROM121に記憶されたOSを読み出して実行する。そして、CPU122は、OSの制御内容に従って、情報担体110のROM115に記憶された各種処理に関するアプリケーションプログラムを読み出して実行する。そして、CPU122は、各種処理結果をCPU122内のレジスタやRAM123に記憶しつつ処理を行い、処理が終了する際に、処理結果(処理コンテキスト)を情報担体110のNVRAM112に格納する。なお、この処理コンテキストは、CPU122におけるプログラムカウンタやステータスレジスタの値およびレジスタに記憶されているコンテキストを含むものである。

【0061】

RAM123は、DRAM(Dynamic Random Access Memory)あるいはSRAM(Static Random Access Memory)等の揮発性のメモリによって構成され、CPU122が処理を実行する際に生成される各種データを一時的に保持する。

振動素子124は、例えば小型のモータ等によって構成され、CPU122の指示に応じて振動する。

【0062】

バッテリ125は、一次電池あるいは二次電池によって構成され、情報処理システム2の各部に電力を供給する。

接続部126は、処理ユニット120と情報担体110との間で情報および電力を入出力するためのインターフェースである。具体的には、接続部126は、超広帯域の近接無線(例えば、UWB等)による通信装置と、電力の入出力を行うためのコイルとを備えており、情報担体110の接続部116に同様に備えられている通信装置と無線により接続し、また、接続部116のコイルと電磁的に結合することによって、情報および電力を入出力する。

【0063】

上述のような構成の下、ユーザによって、処理ユニット120が情報担体110のいずれかの接続部116に当接されると、処理ユニット120から情報担体110に電力が供給され、情報処理装置2は、動作可能な状態となる。

このとき、処理ユニット120のCPU122は、処理ユニット120および情報担体110を一体とするメモリ空間を形成し、1つの装置として動作する。

【0064】

図9は、情報処理装置2におけるメモリ空間のメモリマップを示す図である。

図9において、情報処理装置2におけるメモリ空間は、処理ユニット120および情報担体110によって構成され、ROM121におけるOSプログラム等を記憶する領域、RAM123におけるOSプログラムのデータ格納領域およびアプリケーションプログラムのスタック領域、振動素子124等のデバイスに関するI/O領域と、ROM115におけるアプリケーションプログラム等を記憶する領域、NVRAM112における処理コンテキストの保持領域および表示パネル114等のデバイスに関するI/O領域と含んでいる。

【0065】

なお、処理ユニット120が他の情報担体Xと接続された場合には、その情報担体Xと一体となり、図9に示すメモリ空間を形成する。

次に、動作を説明する。

まず、情報処理装置2が使用される際の手順について説明する。

図10は、情報処理装置2の使用手順を示すフローチャートである。

【0066】

図10において、情報処理装置2が使用される場合、ユーザが処理ユニット120の接続部126を情報担体110のいずれかの接続部116に当接させる(ステップS1)。

すると、電磁誘導により、コイルを介して処理ユニット120から情報担体110に電力が供給され(ステップS2)、次に、近接無線により、情報担体110と処理ユニット120のバスが接続される(ステップS3)。

【0067】

そして、CPU122に割り込み信号が入力され(ステップS4)、処理ユニット120と情報担体110とが一体として動作可能な状態になる。

すると、CPU122は、情報担体110の接続部116からIDを取得し(ステップS5)、そのIDが、リセットを指示するボタン(例えばオールクリアを意味する“AC”ボタン等)のIDであるか否かの判定を行う(ステップS6)。

【0068】

ステップS6において、取得したIDがリセットを指示するボタンのIDであると判定した場合、CPU122は、情報担体110のNVRAM112の記憶された処理コンテキストを初期化し(ステップS7)、ステップS12の処理に移行する。

一方、ステップS6において、取得したIDがリセットを指示するボタンのIDでないと判定した場合、CPU122は、情報担体110のNVRAM112に退避されているコンテキストを復元し(ステップS8)、取得したIDに対応するアプリケーションプログラム(1操作に対応するプログラム)を実行する(ステップS9)。

【0069】

次いで、CPU122は、ステップS9において実行されたアプリケーションプログラムから、処理の終了を示す休止コールがOSに対して発行されたか否かの判定を行い(ステップS10)、休止コールが発行されていないと判定した場合、ステップS9の処理に移行する。

一方、ステップS10において、休止コールが発行されたと判定した場合、CPU122は、終了した処理に関連するコンテキストを情報担体110のNVRAM112に退避し(ステップS11)、振動素子124に対する動作の指示を出力し、情報担体110と処理ユニット120とを切断可能である旨をユーザに通知する(ステップS12)。

【0070】

そして、CPU122は、休止状態(割り込み待ち状態)に移行し(ステップS13)、ユーザが情報担体110から処理ユニット120を離すことにより、バスの接続および電力の供給が停止される(ステップS14)。

なお、図10に示すフローチャートのうち、ステップS9を除くステップS5〜S13の処理はOSによる処理であり、ステップS9の処理はアプリケーションによる処理である。

【0071】

続いて、情報担体110に処理ユニット120が接続された際の、アプリケーションプログラムに基づくCPU122の処理について説明する。

図11は、アプリケーションプログラムに基づくCPU122の処理を示すフローチャートである。なお、図11において、“C[n]”(nは自然数)は、入力された数字列を保持するための文字配列、“O”は、現在指示されている四則演算の種類を保持する変数、“N”は確定された演算数、“A”は被演算数であり、最新の演算経過を示している。

【0072】

図11において、情報担体110に処理ユニット120が接続されると、CPU122は、情報担体110の接続部116から取得したIDの内容を判定する(ステップS101)。

ステップS101において、取得したIDが数字(“0”〜“9”)あるいは小数点(“.”)を示すボタンのIDであると判定した場合、CPU122は、文字配列C[n]に、IDに対応する数字あるいは小数点を追加する(ステップS102)。

【0073】

そして、CPU122は、文字配列C[n]を表示パネル114に表示し(ステップS103)、さらに、文字配列C[n]を数値Nに変換した後(ステップS104)、OSに対して休止コールを発行する(ステップS105)。

ステップS105の後、図11に示す処理は終了し、OSに処理が返される。

また、ステップS101において、取得したIDが数値Nの百分率、開平あるいはクリアを示すボタンのIDであると判定した場合、CPU122は、取得したIDに対応する変換処理Tを選択し(ステップS106)、N=T(A,N,O)の演算を実行する(ステップS107)。

【0074】

そして、CPU122は、演算結果である“N”を表示パネル114に表示し(ステップS108)、文字配列C[n]をクリアする(ステップS109)。

ステップS109の後、CPU122は、ステップS105の処理に移行する。

また、ステップS101において、取得したIDが四則演算(“+”、“−”、“×”、“÷”)あるいは等号(“=”)を示すボタンのIDであると判定した場合、CPU122は、保持中の“O”の内容に基づいて、A=O(A,N)の演算を実行する(ステップS110)。

【0075】

そして、CPU122は、演算結果である“A”を表示パネル114に表示し(ステップS111)、取得したIDに対応して演算内容“O”を更新した後(ステップS112)、文字配列C[n]をクリアする(ステップS113)。

ステップS113の後、CPU122は、ステップS105の処理に移行する。

次に、情報処理装置2が、上述のような処理に従って動作する具体例について説明する。

【0076】

ここでは、“12−9√=”と入力し、演算結果を得る場合について説明する。

このとき、ユーザが、ボタン“1”の接続部116に処理ユニットを当接すると、図10の手順に従って、図11の処理が呼び出される。

そして、接続部116のIDにより数字入力に分岐し、C[n]に“1”を追加して、情報担体110の表示パネル114に“1”を表示する。

【0077】

次いで、Nを数値の1にした後、休止コールを発行して、ボタン“1”の接続処理は終了する。

この後、OSの処理により、処理ユニット120は振動し、ユーザはボタンから処理ユニット120を離すことができる。

次に、ボタン“2”に接続する場合も同様の処理を経て、C[n]は文字列“12”を格納し、表示パネル114の表示を数値の12とした後、Nに数値の12が格納される。

【0078】

さらに、ボタン“−”に接続すると、図10の処理は演算子(“−”)の処理に分岐する。

ここで、演算内容は保持されていなかったため、最初のステップでは、Aには無演算のまま12が格納される。

続いて、“12”および“−”の記号を表示し、Oに減算を登録して、C[n]をクリアした後、休止コールを発行して、ボタン“−”の接続処理は終了する。

【0079】

この後、ボタン“9”に接続すると、C[n]に“9”、Nに数値9が入力された状態となり、表示パネル114における表示に“9”が加えられる。

次に、ボタン“√”に接続すると、図11において変換処理に分岐し、処理として開平が選択されて、Nが数値3に変換される。

そして、表示パネル114における“9”の表示が“3”に改められ、C[n]がクリアされた後、休止コールが発行される。

【0080】

最後に、ボタン“=”に接続すると、図10の処理は演算子(“=”)に分岐し、保持中の減算に基づき、A(12)−N(5)が演算され、Aに結果の7が格納される。

この結果を表示パネル114に表示し、Oに無変換を登録し、C[n]をクリアした後、休止コールが発行される。

このように、処理ユニット120が情報担体110に接続された際に行うべき処理の要素のみが、それぞれの接触において行われ、これらが連続の操作により組合わされることにより、全体の処理が遂行される。

【0081】

連続するボタン操作間では、情報担体110上に処理のコンテキストが保持されているので、矛盾を生じることなく一連の処理を行うことが可能である。

また、連続するボタン操作の間では、処理ユニット120内には必要な情報(処理コンテキスト)が残されていないので、処理ユニット120が、別の情報担体110との間における処理を任意のタイミングで行うことも可能である。

【0082】

また、1つのボタン操作が終了した後であれば、ある時点から別の処理ユニット120に換えて情報担体110を操作することも可能である。

なお、情報担体110に記憶されるアプリケーションプログラムは、上記の形態に限られるものでなく、OSとアプリケーションとの役割の分担は様々な形態とすることが可能である。例えば、一連の関数(統合した1つのプログラム)にまとまっておらず、接続部116のID毎に処理を記述したルーチンの集合体のような形態としても良い。この場合、接続部116のID毎の処理のディスパッチはOSが行うこととなる。

【0083】

以上のように、本実施の形態に係る情報処理装置2は、不揮発的に処理コンテキストを記憶可能な情報担体110と、演算処理機能を備えた処理ユニット120とが別体の構成とされている。そして、処理ユニット120が情報担体110の接続部116に接続されると、その都度、情報担体110の処理コンテキストが処理ユニット120に復帰され、処理ユニット120は、接続された接続部116に対応する処理を実行する。その後、処理ユニット120は、処理結果の処理コンテキストを情報担体110に退避した後、情報担体110との接続を解除される。

【0084】

そのため、処理対象の情報が、情報担体110と一体化したものとして認識され、複数の処理ユニット120によって、いずれの処理ユニット120も区別することなく情報を取り扱うことができることとなる。

したがって、情報処理システムにおいて情報を取り扱う上で、処理対象の情報を主体として取り扱うことが容易となると共に、有体物として情報を認識し易く、ユーザにとって利便性の高いものとすることができる。

【0085】

また、処理ユニット120は、それぞれ固有の処理コンテキストを記憶している複数の情報担体110に対し、いずれの情報担体110とも特定の関係を有することなく演算処理能力を提供するものとなるため、処理コンテキストを情報担体110に具現化した形態の、一種のマルチタスク処理システムを構築することができる。

なお、本実施の形態においては、処理ユニット120が、情報担体110と接続している間のみ処理を行うものとして説明したが、処理ユニット120において、情報担体110に関連したプログラムを実行するほかに、システムサービスを維持するためのシステムタスクを動作させることとしてもよい。このようなシステムタスクとしては、例えばファイルサービスのためのタスクや、ネットワーク通信のタスク、タスク間の情報のコピー&ペースト、すなわちクリップボードサービス等が挙げられる。

【0086】

このようなシステムタスクは、従来のマルチタスクシステムと同様の制御方法で、情報担体110に関連したプログラムを実行するタスクと並列動作させることが可能である。この場合、本実施の形態のOSのプログラムは、それらと並列な1つのタスクとして実現し、そのタスクに図10の処理を行わせるように構成すれば良い。

また、本発明は、上記実施の形態に記載した以外の処理を行う構成とすることも可能である。

【0087】

図12は、本発明の他の実施の形態を示す図であり、情報のスクラップブック機能を実現する構成例を示す図である。

図12において、処理ユニットがメニュー表示用の接続部に接続すると、情報担体上のプログラムは、「ルートメニュー」を表示する処理を行って休止する。

次いで、ユーザが、メニューで示された処理を選択し、対応する接続部(選択ボタン)に接続すると、情報担体上のプログラムはそのコンテキストに応じて指定の処理を行う。

【0088】

例えば、「ルートメニュー」が表示された状態で、新規ページへのペーストに対応する接続部(選択ボタン)への接続操作をした際には、処理ユニットのクリップボードザービスにコピー格納された画像・テキスト・音声等の情報を取得して、新規ページに関連付けて記憶するといった動作を行って休止する。

このようにページに関連付けて記憶された情報は、接続部(ページ送りボタン)に接続した際に動作する情報担体上のプログラムにおいて、順次、表示パネルに表示されるように構成することができる。

【0089】

また、「ルートメニュー」から選択可能となる「このページをコピー」の動作により、表示中の情報を、処理ユニットのクリップボードサービスに送出するように構成することができる。

このように、本発明においては、対話的な処理を行う情報担体を構成して、より複雑な処理を行わせることも可能となる。

【0090】

さらに、上記第1および第2の実施の形態において、処理ユニット20,120をペン型とする場合を例に挙げて説明したが、処理ユニット20,120の形態としては、これに限られず、種々の形態とすることが可能である。

【図面の簡単な説明】

【0091】

【図1】第1の実施の形態に係る情報処理システム1の外観構成を示す図である。

【図2】情報処理システム1の機能構成を示すブロック図である。

【図3】接続部17が、電磁的なユーザインターフェースからなる指示入力部15の機能を兼ね備える構成例を示す図である。

【図4】情報担体10それぞれが、個々の情報担体10を識別するためのID記憶部を備える構成を示す図である。

【図5】記憶性の表示体に代えて、記憶性を有しない表示体と、その表示状態を維持するための小規模な電源とを併せ持つ情報担体10の構成を示す図である。

【図6】本発明の第2の実施の形態に係る情報処理システム2(情報担体側)の外観構成を示す図である。

【図7】情報処理システム2の機能構成を示すブロック図である。

【図8】NVRAM112に記憶される処理コンテキストの一例を示す図である。

【図9】情報処理装置2におけるメモリ空間のメモリマップを示す図である。

【図10】情報処理装置2の使用手順を示すフローチャートである。

【図11】アプリケーションプログラムに基づくCPU122の処理を示すフローチャートである。

【図12】本発明の他の実施の形態を示す図であり、情報のスクラップブック機能を実現する構成例を示す図である。

【符号の説明】

【0092】

1,2 情報処理システム、10,110 情報担体、10P ID記憶部、10Q 保持電源、11,111 データ記憶部、12,112 NVRAM、13,113 表示駆動部,13a 描画データ書き込み部,14,114 表示パネル、15,29 指示入力部、115,121 ROM、16 接続制御部、17,116,26,126 接続部,18,28,118,127 バス、20,120 処理ユニット、21 データI/F、22,122 CPU、23 記憶部、23a プログラム記憶部、23b,123 RAM、24 GA、25 接続制御部、27,125 バッテリ、30 電源ユニット,110 解析・整形部,120 描画処理部,130 抽出処理部

【技術分野】

【0001】

本発明は、複数の装置が連携して処理を実行する情報処理システム、情報処理装置、情報保持装置および情報処理方法に関する。

【背景技術】

【0002】

従来、PC(Personal Computer)等の情報処理装置は、処理対象のデータを装置内部に備えたり、処理対象のデータを記憶している記憶媒体あるいはネットワーク上のリソースと接続したりすることで、その処理過程において、処理対象となる情報を包括的に保持した状態で処理を行っている。即ち、従来の情報処理装置は、処理すべき情報を装置上に集約する形態のシステム構成とされている。

【0003】

そして、従来の情報処理装置においては、複数の処理対象情報を並行して処理するためのマルチタスク機能が備えられ、タスクの優先度や処理経過に応じてスケジューリングし、マルチタスク処理を実行している(例えば、特許文献1参照)。

【特許文献1】特開2004−220070号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、従来の情報処理装置においては、処理すべき情報を装置上に集約する形態のシステム構成であるため、情報処理装置の性能や特性の制約を免れず、例えば、ユーザインターフェースとしても、情報処理装置が小型のものであれば、ユーザは狭い画面を凝視しつつ、姿勢を制限された状態で操作することを余儀なくされる。

また、処理対象の情報が装置に集約され、無体化した状態となっているため、処理装置の操作時以外は、ユーザにとって処理対象の情報を認識し難いものとなる。したがって、処理対象の情報に対する現実感が喪失され易く、重要な処理対象の存在を忘れてしまう等の事態を生じ得る。反対に、このような事態を懸念するあまり、いわゆるサイバーストレスといった負担をユーザに与えることもあり得る。

【0005】

さらに、例えば商品の伝票の情報のように、処理対象の情報が物品に伴われる等して移動する場合もあり、このような状況においては、処理対象の情報を、複数の処理装置によって断続的に取り扱うこととなる。そして、このような場合には、処理対象の情報を装置上に集約することは適切でない。

一方、上述のような問題を単純に解決しようとする場合、処理対象の情報毎に情報処理装置を用意しておくことが考えられるが、それぞれの情報処理装置に電源を用意する必要がある等、コストおよび省資源の面から不適当な対策であると考えられる。

【0006】

即ち、従来の情報処理装置にように、処理すべき情報を装置上に集約する形態の情報処理装置においては、情報処理装置ではなく処理対象の情報を主体として取り扱うことが困難であり、有体物として情報を認識し難く、ユーザにとって必ずしも利便性の高くないものとなる場合があった。

本発明の課題は、装置によって情報を取り扱う上で、処理対象の情報を主体として取り扱うことを容易とすると共に、有体物として情報を認識し易く、ユーザにとって利便性の高いものとすることである。

【課題を解決するための手段】

【0007】

以上の課題を解決するため、本発明は、

所定の接続動作によって互いに通信可能となる情報処理装置(例えば、図1の処理ユニット20あるいは図7の処理ユニット120)と情報保持装置(例えば、図1の情報担体10あるいは図7の情報担体110)とを含む情報処理システムであって、前記情報保持装置は、所定の情報処理に係る処理コンテキストを記憶する処理コンテキスト記憶手段(例えば、図2のNVRAM12あるいは図7のNVRAM112)を備え、前記情報処理装置は、通信可能となった前記情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに所定処理を施し、処理結果である処理コンテキストを前記情報保持装置の処理コンテキスト記憶手段に記憶する情報処理手段(例えば、図2のCPU22あるいは図7のCPU122)を備えることを特徴としている。

【0008】

このような構成により、情報処理装置が情報保持装置に接続されると、その都度、情報保持装置の処理コンテキストが情報処理装置に復帰され、情報処理装置は、所定処理を実行する。その後、情報処理装置は、処理結果の処理コンテキストを情報保持装置に退避した後、情報保持装置との接続を解除される。

そのため、処理対象の情報が、情報保持装置と一体化したものとして認識され、複数の情報処理装置によって、いずれの情報処理装置も区別することなく情報を取り扱うこと等が可能となる。

【0009】

したがって、装置によって情報を取り扱う上で、処理対象の情報を主体として取り扱うことが容易となると共に、有体物として情報を認識し易く、ユーザにとって利便性の高いものとすることができる。

また、前記情報保持装置は、所定のアプリケーションプログラムを記憶するアプリケーション記憶手段(例えば、図7のROM115)をさらに備え、前記処理コンテキスト記憶手段は、前記アプリケーションプログラムに係る処理コンテキストを記憶することを特徴としている。

【0010】

このような構成により、情報保持装置に所定の機能を持たせることが可能となり、ユーザに対し、情報保持装置を所定のアプリケーションと一体的なものと認識させることが可能となる。

また、前記情報保持装置は、所定処理にそれぞれ対応した、前記情報処理装置と接続するための接続手段(例えば、図2の接続部17あるいは図7の接続部116)を複数備え、前記情報処理手段は、自装置が接続された前記接続手段が対応している所定処理を判定する判定手段(例えば、図2のCPU22あるいは図7のCPU122)を備え、該接続手段に接続された前記情報処理装置の情報処理手段は、前記判定手段によって判定された所定処理を行い、その処理結果である処理コンテキストを前記処理コンテキスト記憶手段に記憶することを特徴としている。

【0011】

このような構成により、ユーザは、接続手段を選択して情報処理装置を接続させることで、意図する処理を行わせることが可能となる。

また、前記情報処理装置と前記情報保持装置との接続を解除可能であることを報知する報知手段(例えば、図7の振動素子124)をさらに備え、前記情報処理装置の情報処理手段は、所定処理を施した結果である前記処理コンテキストを前記処理コンテキスト記憶手段に記憶した後、前記報知手段によって、前記情報保持装置との接続を解除可能であることを報知することを特徴としている。

【0012】

このような構成により、ユーザに対し、情報保持装置と情報処理装置との接続を解除可能なタイミングを知らせることが可能となる。

また、前記情報保持装置は、前記情報処理装置の電源から電力の供給を受けて動作することを特徴としている。

このような構成により、情報保持装置に重量の比較的大きい電源を備える必要がなくなり、情報保持装置を軽量なものとすることができる。

【0013】

また、前記情報保持装置は、表示状態を不揮発的に保持可能な記憶性の表示装置を備えることを特徴としている。

このような構成により、情報保持装置は、情報処理装置と接続されていない場合にも、処理状態を不揮発的に表示することが可能となり、情報保持装置を、記憶している情報と一体の有体物として認識させることが容易となる。

【0014】

また、本発明は、

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを含む情報処理システムにおける情報処理装置であって、所定の情報処理に係る処理コンテキストを記憶する前記情報保持装置と通信可能となった場合に、該情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに対し、前記所定処理を施し、処理結果である処理コンテキストを前記情報保持装置の処理コンテキスト記憶手段に記憶する情報処理手段を備えることを特徴としている。

【0015】

また、本発明は、

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを含む情報処理システムにおける情報保持装置であって、所定の情報処理に係る処理コンテキストを記憶する処理コンテキスト記憶手段を備え、通信可能となった前記情報処理装置に対し、前記処理コンテキスト記憶手段に記憶された処理コンテキストを出力すると共に、前記情報処理装置の処理結果である処理コンテキストを前記処理コンテキスト記憶手段に記憶することを特徴としている。

【0016】

また、本発明は、

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを用いた情報処理方法であって、前記情報保持装置が、所定の情報処理に係る処理コンテキストを記憶し、前記情報処理装置が、通信可能となった前記情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに所定処理を施し、処理結果である処理コンテキストを前記情報保持装置に記憶させることを特徴としている。

【0017】

このように、本発明によれば、装置によって情報を取り扱う上で、処理対象の情報を主体として取り扱うことを容易とすると共に、有体物として情報を認識し易く、ユーザにとって利便性の高いものとすることが可能となる。

より具体的には、紙と同様な自由な使用形態で、紙と同様の安心感のある形態で情報を取り扱うことが可能な情報表示装置を、比較的安価に実現することが可能となる。

【発明を実施するための最良の形態】

【0018】

以下、図を参照して本発明に係る情報表示装置の実施の形態を説明する。

(第1の実施の形態)

本実施の形態においては、情報表示装置を電子ブックとして使用し、電子ブックのコンテンツを、情報担体に具現化された有体物として取り扱う場合を例に挙げて説明する。

図1は、本発明の第1の実施の形態に係る情報処理システム1の外観構成を示す図であり、図2は、情報処理システム1の機能構成を示すブロック図である。

【0019】

図1および図2において、情報処理システム1は、紙のように軽薄な形態を有する情報担体10と、ペン型の処理ユニット20とによって構成されている。

情報担体10は、データ記憶部11と、NVRAM(Non-Volatile Random Access Memory)12と、表示駆動部13と、表示パネル14と、指示入力部15と、接続制御部16と、接続部17とを含んで構成され、これらはバス18によって通信可能に接続されている。

【0020】

データ記憶部11は、フラッシュメモリ等の不揮発性のメモリによって構成され、後述する接続部17を介してデータインターフェース(以下、「データI/F」と称する。)21から入力されたデータを記憶可能である。

NVRAM12は、FeRAM/FRAM(Ferroelectric Random Access Memory)、MRAM(Magnetoresistive Random Access Memory)等のメモリによって構成され、CPU22が処理を実行する際にワークエリアを形成すると共に、その処理結果を記憶する。

【0021】

表示駆動部13は、表示パネル14を直接制御し、後述するグラフィックアクセラレータ(以下、「GA」と称する。)24から入力された描画データを表示パネル14に表示させる。具体的には、表示駆動部13は、GA24によって図形データが入力される描画データ書き込み部13aを備えている。そして、表示駆動部13は、描画データ書き込み部13aに入力された描画データを参照して、表示パネル14のXドライバおよびYドライバを駆動することにより、描画対象であるラスタ図形を表示パネル14に表示させる。

【0022】

なお、表示パネル14を駆動する方式として、例えば、パッシブマトリクス駆動方式、TFT(Thin Film Transistor)方式、TFD(Thin Film Diode)方式、D−TFD(Digital Thin Film Diode)方式等が採用可能である。

表示パネル14は、A4サイズの高画素密度(多ピクセル)である表示装置によって構成され、表示駆動部13の制御に応じて、所定画素に画素データを表示する。

【0023】

また、表示パネル14として、記憶性の表示装置(電源を切断しても表示画面が維持される表示装置)が使用される。したがって、表示画面の状態を維持するためには電力が不要となることから、情報処理システム1を低消費電力化することができる。

なお、表示パネル14として、例えば、電気泳動ディスプレイ、コレステリック液晶ディスプレイ、帯電トナーを利用したディスプレイ、ツイストボールを利用したディスプレイあるいはエレクトロデポジションディスプレイ等が採用可能である。

【0024】

指示入力部15は、所定のユーザインターフェースを備え、ユーザによる指示入力を受け付ける。この指示入力部15としては、押しボタン等の機械的なインターフェースや、後述する接続部17の機能を兼ね備えた電磁的なインターフェースとすることが可能である(図3参照)。

接続制御部16は、接続部17を介して行われる情報および電力の入出力を制御する。

【0025】

即ち、接続制御部16は、表示駆動部13あるいは指示入力部15から入力されるパラレルデータをシリアルデータに変換して、接続部17に出力したり、接続部17から入力されるシリアルデータをパラレルデータに変換して、データ記憶部11、NVRAM12、表示駆動部13あるいは指示入力部15に出力したりする。接続制御部16がこのような処理を行い、後述するように、処理ユニット20側の接続制御部25が同様の処理を行うことにより、バス18と処理ユニット20のバス28との間で送受信される情報が、双方向にシリアル変換され、バス18と処理ユニット20のバス28とがバス間接続された状態となる。

【0026】

また、接続制御部16は、接続部17を介して処理ユニット20から電力が供給されていることを検出し、接続部17を介して入力された交流電力を整流した上で、データ記憶部11、NVRAM12、表示駆動部13あるいは指示入力部15に出力する。

接続部17は、情報担体10と処理ユニット20との間で情報および電力を入出力するためのインターフェースである。具体的には、接続部17は、情報の入出力を行うためのコイルと、電力の入出力を行うためのコイルとを備えており、処理ユニット20の接続部26に同様に備えられている2つのコイルそれぞれと電磁的に結合することによって、情報および電力を入出力する。なお、接続部17と接続部26との間においては、上述のコイルによって情報および電力を同時に入出力することや、情報および電力を伝達する際に、互いに干渉することを確実に防ぐため、時分割により、それぞれを切り替えて入出力することが可能である。

【0027】

なお、異なる指示入力内容それぞれに対応する接続部17を備えることにより、接続部17が、電磁的なユーザインターフェースからなる指示入力部15の機能を兼ね備える構成とすることが可能である。

図3は、接続部17が、電磁的なユーザインターフェースからなる指示入力部15の機能を兼ね備える構成例を示す図である。

【0028】

図3において、左側の接続部17は、図2におけるページ捲りボタンに対応する指示入力部15の機能を備え、処理ユニット20が左側の接続部17に接続されると、電力の供給および情報の入出力が行われると共に、ページを捲る旨の指示入力が行われる。同様に、右側の接続部17は、図2におけるページ戻りボタンに対応する指示入力部15の機能を備え、処理ユニット20が右側の接続部17に接続されると、電力の供給および情報の入出力が行われると共に、ページを戻す旨の指示入力が行われる。

【0029】

なお、図3においては、各ボタンに対応する位置に接続部17が備えられる例について説明したが、情報担体10の全面にわたって、接続部17をマトリクス状に備えておくことも可能である。このような構成により、処理ユニット20が接続された情報担体10上の位置を把握できるため、表示された文書を選択する等、多様な処理を行うことが可能となる。

【0030】

次に、処理ユニット20は、データI/F21と、CPU22と、記憶部23と、GA24と、接続制御部25と、接続部26と、バッテリ27とを含んで構成され、これらはバス28によって通信可能に構成されている。

データI/F21は、処理ユニット20外部からデータを入力することが可能なインターフェースであり、例えば、通信インターフェースあるいは記憶メディアのスロット等によって構成される。そして、データI/F21を介して入力されたデータは、接続部26から情報担体10に出力され、情報担体10のデータ記憶部11に記憶される。

【0031】

CPU22は、情報処理システム1全体を制御するもので、指示入力部15から入力される各種の指示信号に従って、記憶部23のプログラム記憶部23aに記憶された各種処理に関するプログラムを読み出して実行する。また、CPU22は、データ記憶部11あるいはデータI/F21に差し込まれた記憶メディアに記憶されているコンテンツデータを表示パネル14に表示するための処理を行う。そして、CPU22は、各種処理結果を記憶部23のRAM23bに格納する。

【0032】

記憶部23は、フラッシュメモリ等の不揮発性のメモリからなるプログラム記憶部23aを備えており、このプログラム記憶部23aは、情報処理システム1を制御するための各種プログラムを記憶している。

また、記憶部23は、DRAM(Dynamic Random Access Memory)あるいはSRAM(Static Random Access Memory)等の揮発性のメモリからなるRAM23bを備え、RAM23bは、CPU22が処理を実行する際に生成される各種データを一時的に保持することが可能である。RAM23bとしては、低消費電力でデータを保持可能なSRAM等が望ましく、不揮発性のFeRAM/FRAMやMRAM等がより望ましい。

【0033】

GA24は、CPU22の命令に従って、表示パネル14に表示する画像の描画処理を高速に行うことが可能なハードウェアである。具体的には、GA24は、CPU22から入力されたベクトル図形をラスタ図形に展開するといった処理を行う。そして、GA24は、描画処理を行った図形を表示パネル14に描画するための描画データを表示駆動部13に出力する。

【0034】

接続制御部25は、接続部26を介して行われる情報および電力の入出力を制御する。即ち、接続制御部25は、CPU22、記憶部23、GA24あるいはバッテリ27から入力されるパラレルデータをシリアルデータに変換して、接続部26に出力したり、接続部26から入力されるシリアルデータをパラレルデータに変換して、CPU22、記憶部23、GA24あるいはバッテリ27に出力したりする。また、接続制御部25は、バッテリ27から入力された直流電力を交流化し、接続部26に出力する。

【0035】

接続部26は、情報担体10と処理ユニット20との間で情報および電力を入出力するためのインターフェースである。具体的には、接続部26は、情報の入出力を行うためのコイルと、電力の入出力を行うためのコイルとを備えており、情報担体10の接続部17に同様に備えられている2つのコイルそれぞれと電磁的に結合することによって、情報および電力を入出力する。

【0036】

バッテリ27は、一次電池あるいは二次電池によって構成され、情報処理システム1の各部に電力を供給する。

上述のような構成の下、情報処理システム1が所定のプログラムを実行することにより、図2に示す解析・整形部110および描画処理部120を実現することが可能となる。

解析・整形部110は、データ記憶部11に記憶された文書データを中間形式に変換する。具体的には、文書データを描画要素に分解し、高速に表示処理できる形式(中間形式)で記述する。

【0037】

描画処理部120は、解析・整形部110によって中間形式とされたデータを、表示パネル14に表示するための描画処理を行う。例えば、描画処理部120は、中間形式に含まれる描画要素をラスタ化する処理等を行う。

次に、動作を説明する。

本実施の形態に係る情報処理システム1は、情報担体10の接続部17と処理ユニット20の接続部26とが電磁的に結合されることにより、処理ユニット20から情報担体10に電力が供給されると共に情報の入出力が可能な状態となり、情報処理システム1全体として動作可能となる。

【0038】

そして、処理ユニット20のデータI/F21を介して文書データが入力されると、その文書データが情報担体10のデータ記憶部11に記憶される。なお、データI/F21が記憶メディアのスロットである場合、データ記憶部11にデータを記憶することなく、スロットに差し込まれた記憶メディアから直接データを読み出して利用することとしてもよい。

【0039】

すると、処理ユニット20上に構成された解析・整形部110が、文書データの処理を開始する。即ち、解析・整形部110は、文書データの文書構造を解釈し、その構造に従って、画面表示のためのレイアウト処理を行う。そして、解析・整形部110は、レイアウト処理された文書データを中間形式のデータとしてNVRAM12に記憶する。

なお、このとき、情報担体10のNVRAM12は、スタティックデータ領域(処理中のページ番号等、処理の状態を表すデータを記憶する領域)としても使用される。

【0040】

次に、描画処理部120は、NVRAM12に記憶された中間形式のデータから描画データを生成し、表示駆動部13の描画データ書き込み部13aに書き込む。

すると、表示駆動部13は、描画データ書き込み部13aに書き込まれた描画データに応じて表示パネル14を駆動し、表示パネル14に文書が表示される。

また、処理ユニット20が接続部17から切り離されると、情報担体10には電力が供給されない状態となり、各部の動作が停止する。

【0041】

ただし、表示パネル14は記憶性を有することから、処理ユニット20から電力の供給が停止された後も、引き続き、表示された状態が維持され、同様に、NVRAM12に記憶されたスタティックデータおよび中間形式のデータも、NVRAM12の不揮発性により保持される。さらに、データ記憶部11も不揮発性のメモリであることから、データ記憶部11に記憶された文書データも保持される。

【0042】

このように、情報担体10は、電力の供給が行われていない状態、即ち、処理ユニット20から切り離され、情報担体10単独の状態でも、情報を表示し続けることが可能であるため、紙と同様の操作性を実現することができる。

さらに、一旦切り離された処理ユニット20を、情報担体10に再度接続すると、CPU22は、NVRAM12に記憶されたスタティックデータを確認し、有効なデータであると判定した場合には、文書データの表示処理を、現在の表示状態から継続させる。なお、NVRAM12に記憶されたスタティックデータが有効なものであるか否かは、データ形式が処理ユニット20の処理対象として適合するものかどうかによって判定したり、スタティックデータにチェックサムを付加しておき、そのチェックサムによって判定したりすることが可能である。

【0043】

また、本実施の形態においては、処理ユニット20が情報担体10に対する操作子となっているため、ユーザがページを捲る等の操作を行う場合、上述のように、処理ユニット20が情報担体10から切り離され、再度接続される動作が逐次行われる。即ち、ユーザが操作を行う場合、処理ユニット20を情報担体10に接続することにより、指示入力部15を介してページを捲る旨の指示信号を入力したり、あるいは、処理ユニット20に備えられた不図示の指示ボタン等からページを捲る旨の指示信号を入力したりする。

【0044】

すると、入力された指示信号は、CPU22に入力され、CPU22が、指示に応じた処理を行う。

また、本実施の形態においては、処理ユニット20が情報担体10に対する操作子となっているため、ユーザがページを捲る等の操作を行う場合、上述のように、処理ユニット20が情報担体10から切り離され、再度接続される動作が逐次行われる。即ち、ユーザが操作を行う場合、処理ユニット20を情報担体10に接続することにより、指示入力部15を介してページを捲る旨の指示信号を入力したり、あるいは、処理ユニット20に備えられた不図示の指示ボタン等からページを捲る旨の指示信号を入力したりする。

【0045】

すると、入力された指示信号は、CPU22に入力され、CPU22が、指示に応じた処理を行う。

このように、表示される文書に関連する情報(文書データ、中間形式のデータおよびスタティックデータ)を情報担体10側に記憶しておくことにより、処理ユニット20には、接続された情報担体10と不可分のデータが残されないため、接続する情報担体10を任意のタイミングで異なるものに変更することが可能となる。

【0046】

以上のように、本実施の形態に係る情報処理システム1は、記憶性の表示パネル14を備える情報担体10と、バッテリ27を含む処理ユニット20とを別体の構成としながら、表示パネル14に表示された情報の更新や、表示された情報に対する操作等、処理を行う必要が生じた場合には、処理ユニット20を情報担体10と接続することにより、所望の処理を行うことが可能となる。

【0047】

そのため、「紙」に近い表示装置として本来的に必要な機能である「表示」を維持する以外の構成物を、通常の使用時において、情報処理システム1から切り離すことが可能となる。

したがって、「紙」に近い良好な表示品質と、情報の再利用性(表示された情報を電子データとして取り扱う機能)とを兼ね備えつつ、装置自体を軽装化することができるため、従来の情報表示装置に比べ、操作性を大幅に向上させることが可能となる。

【0048】

なお、本実施の形態における情報担体10を図4に示す構成とすることによって、複数の情報担体10それぞれを識別して取り扱うことも可能である。

図4は、情報担体10それぞれが、個々の情報担体10を識別するためのID記憶部10Pを備える構成を示している。

このような構成とした場合、IDによって種々の管理を行いつつ、1つの処理ユニット20が複数の情報担体10を操作することが可能となる。具体的には、表示対象であるデータが処理ユニット20に記憶されている場合あるいはネットワーク上のサーバに記憶されている場合等であっても、情報担体10と対応付けることが可能となる。したがって、情報処理システム1の用途の幅を広げることができる。

【0049】

また、本実施の形態においては、表示パネル14が記憶性の表示体を備える例について説明したが、記憶性を有する表示体に代えて、記憶性を有しない表示体と、その表示状態を維持するための小規模な電源とを併せ持つ構成とすることも可能である。

図5は、記憶性の表示体に代えて、記憶性を有しない表示体と、その表示状態を維持するための小規模な電源(保持電源10Q)とを併せ持つ情報担体10の構成を示す図である。

【0050】

このような構成により、非記憶性の表示体を用いる場合でも、実質的に記憶性を有する表示体として利用することができる。

また、本実施の形態においては、CPU22、記憶部23、GA24が処理ユニット20に備えられる構成について説明したが、バッテリ27以外の構成部分については、処理ユニット20あるいは情報担体10のいずれに備えられることとしても良い。

(第2の実施の形態)

次に、本発明の第2の実施の形態について説明する。

【0051】

本実施の形態においては、情報表示装置を電卓として使用し、情報処理におけるコンテキストを、情報担体に具現化された有体物として取り扱う場合を例に挙げて説明する。

図6は、本発明の第2の実施の形態に係る情報処理システム2(情報担体側)の外観構成を示す図であり、図7は、情報処理システム2の機能構成を示すブロック図である。

図6および図7において、情報処理システム2は、紙のように軽薄な形態を有する情報担体110と、ペン型の処理ユニット120とによって構成されている。

【0052】

情報担体110は、データ記憶部111と、NVRAM112と、表示駆動部113と、表示パネル114と、ROM(Read Only Memory)115と、接続部116とを含んで構成され、これらはバス118によって通信可能に接続されている。

データ記憶部111は、フラッシュメモリ等の不揮発性のメモリによって構成され、後述する接続部116を介して処理ユニット120から入力されたデータや、情報担体110上に表示可能な各種書類データを記憶する。

【0053】

NVRAM112は、FeRAM/FRAM、MRAM等のメモリによって構成され、CPU122が処理を実行する際に生成されたコンテキストや、情報担体110側に保持されるコンテキスト(以下、これらを「処理コンテキスト」と称する。)を記憶する。

図8は、NVRAM112に記憶される処理コンテキストの一例を示す図である。

図8においては、処理コンテキストとして、情報担体110を電卓として機能させるプログラムにおける各種変数を示している。

【0054】

なお、このような処理コンテキストは、処理ユニット120が接続されている場合には、CPU122内のレジスタやRAM123に記憶することも可能である。ただし、この場合、処理ユニット120と情報担体110との接続が解除される際に、処理ユニット120側に記憶されているコンテキストは、情報担体110のNVRAM112に退避される。

【0055】

表示駆動部113は、表示パネル114を直接制御し、CPU122から入力された描画データを表示パネル114に表示させる。

表示パネル114は、高画素密度(多ピクセル)である表示装置によって構成され、表示駆動部113の制御に応じて、所定画素に画素データを表示する。

また、表示パネル114として、記憶性の表示装置(電源を切断しても表示画面が維持される表示装置)が使用される。したがって、表示画面の状態を維持するためには電力が不要となることから、情報処理システム1を低消費電力化することができる。

【0056】

ROM115は、EEPROM(Electrically Erasable Programmable Read-Only Memory)等の不揮発性の半導体メモリによって構成され、情報担体110におけるコンテンツを実現するためのアプリケーションプログラムを記憶している。

接続部116は、情報担体110と処理ユニット120との間で情報および電力を入出力するためのインターフェースである。具体的には、接続部116は、超広帯域の近接無線(例えば、UWB:Ultra Wide Band等)による通信装置と、電力の入出力を行うためのコイルとを備えており、処理ユニット120の接続部126に同様に備えられている通信装置と無線により接続し、また、接続部126のコイルと電磁的に結合することによって、情報および電力を入出力する。

【0057】

また、接続部116は、異なる指示入力内容それぞれに対応して備えられており、それぞれの接続部116を識別するためのID記憶素子が、各接続部116に備えられている。

即ち、図6に示すように、情報担体110は、電卓のユーザインターフェースを表示しており、各ボタン部分に、各ボタンを識別するID記憶素子を備えた接続部116が設けられている。

【0058】

そのため、例えば、“1”のボタンに対応する接続部116に処理ユニット120を接続すると、電力の供給および情報の入出力が行われると共に、ボタン“1”の接続部116を識別するIDがCPU122に入力される。そして、CPU122がボタン“1”に対応するアプリケーションを実行する。

なお、ここでは、各ボタンに対応する位置に接続部116が備えられる例について説明したが、情報担体10の全面にわたって、接続部116をマトリクス状に備えておくことも可能である。このような構成により、処理ユニット120が接続された情報担体110上の位置を把握できるため、表示された領域を選択する等、多様な処理を行うことが可能となる。

【0059】

次に、処理ユニット120は、ROM121と、CPU122と、RAM123と、振動素子124と、バッテリ125と、接続部126とを含んで構成され、バッテリ125以外の各部はバス127によって通信可能に構成されている。

ROM121は、EEPROM等の不揮発性の半導体メモリによって構成され、オペレーティングシステムプログラム(OS)等、処理ユニット120を制御するための各種プログラムを記憶している。

【0060】

CPU122は、情報処理システム2全体を制御するもので、接続部126によって情報担体110との接続が検出されると、その検出信号を割り込み信号として起動され、ROM121に記憶されたOSを読み出して実行する。そして、CPU122は、OSの制御内容に従って、情報担体110のROM115に記憶された各種処理に関するアプリケーションプログラムを読み出して実行する。そして、CPU122は、各種処理結果をCPU122内のレジスタやRAM123に記憶しつつ処理を行い、処理が終了する際に、処理結果(処理コンテキスト)を情報担体110のNVRAM112に格納する。なお、この処理コンテキストは、CPU122におけるプログラムカウンタやステータスレジスタの値およびレジスタに記憶されているコンテキストを含むものである。

【0061】

RAM123は、DRAM(Dynamic Random Access Memory)あるいはSRAM(Static Random Access Memory)等の揮発性のメモリによって構成され、CPU122が処理を実行する際に生成される各種データを一時的に保持する。

振動素子124は、例えば小型のモータ等によって構成され、CPU122の指示に応じて振動する。

【0062】

バッテリ125は、一次電池あるいは二次電池によって構成され、情報処理システム2の各部に電力を供給する。

接続部126は、処理ユニット120と情報担体110との間で情報および電力を入出力するためのインターフェースである。具体的には、接続部126は、超広帯域の近接無線(例えば、UWB等)による通信装置と、電力の入出力を行うためのコイルとを備えており、情報担体110の接続部116に同様に備えられている通信装置と無線により接続し、また、接続部116のコイルと電磁的に結合することによって、情報および電力を入出力する。

【0063】

上述のような構成の下、ユーザによって、処理ユニット120が情報担体110のいずれかの接続部116に当接されると、処理ユニット120から情報担体110に電力が供給され、情報処理装置2は、動作可能な状態となる。

このとき、処理ユニット120のCPU122は、処理ユニット120および情報担体110を一体とするメモリ空間を形成し、1つの装置として動作する。

【0064】

図9は、情報処理装置2におけるメモリ空間のメモリマップを示す図である。

図9において、情報処理装置2におけるメモリ空間は、処理ユニット120および情報担体110によって構成され、ROM121におけるOSプログラム等を記憶する領域、RAM123におけるOSプログラムのデータ格納領域およびアプリケーションプログラムのスタック領域、振動素子124等のデバイスに関するI/O領域と、ROM115におけるアプリケーションプログラム等を記憶する領域、NVRAM112における処理コンテキストの保持領域および表示パネル114等のデバイスに関するI/O領域と含んでいる。

【0065】

なお、処理ユニット120が他の情報担体Xと接続された場合には、その情報担体Xと一体となり、図9に示すメモリ空間を形成する。

次に、動作を説明する。

まず、情報処理装置2が使用される際の手順について説明する。

図10は、情報処理装置2の使用手順を示すフローチャートである。

【0066】

図10において、情報処理装置2が使用される場合、ユーザが処理ユニット120の接続部126を情報担体110のいずれかの接続部116に当接させる(ステップS1)。

すると、電磁誘導により、コイルを介して処理ユニット120から情報担体110に電力が供給され(ステップS2)、次に、近接無線により、情報担体110と処理ユニット120のバスが接続される(ステップS3)。

【0067】

そして、CPU122に割り込み信号が入力され(ステップS4)、処理ユニット120と情報担体110とが一体として動作可能な状態になる。

すると、CPU122は、情報担体110の接続部116からIDを取得し(ステップS5)、そのIDが、リセットを指示するボタン(例えばオールクリアを意味する“AC”ボタン等)のIDであるか否かの判定を行う(ステップS6)。

【0068】

ステップS6において、取得したIDがリセットを指示するボタンのIDであると判定した場合、CPU122は、情報担体110のNVRAM112の記憶された処理コンテキストを初期化し(ステップS7)、ステップS12の処理に移行する。

一方、ステップS6において、取得したIDがリセットを指示するボタンのIDでないと判定した場合、CPU122は、情報担体110のNVRAM112に退避されているコンテキストを復元し(ステップS8)、取得したIDに対応するアプリケーションプログラム(1操作に対応するプログラム)を実行する(ステップS9)。

【0069】

次いで、CPU122は、ステップS9において実行されたアプリケーションプログラムから、処理の終了を示す休止コールがOSに対して発行されたか否かの判定を行い(ステップS10)、休止コールが発行されていないと判定した場合、ステップS9の処理に移行する。

一方、ステップS10において、休止コールが発行されたと判定した場合、CPU122は、終了した処理に関連するコンテキストを情報担体110のNVRAM112に退避し(ステップS11)、振動素子124に対する動作の指示を出力し、情報担体110と処理ユニット120とを切断可能である旨をユーザに通知する(ステップS12)。

【0070】

そして、CPU122は、休止状態(割り込み待ち状態)に移行し(ステップS13)、ユーザが情報担体110から処理ユニット120を離すことにより、バスの接続および電力の供給が停止される(ステップS14)。

なお、図10に示すフローチャートのうち、ステップS9を除くステップS5〜S13の処理はOSによる処理であり、ステップS9の処理はアプリケーションによる処理である。

【0071】

続いて、情報担体110に処理ユニット120が接続された際の、アプリケーションプログラムに基づくCPU122の処理について説明する。

図11は、アプリケーションプログラムに基づくCPU122の処理を示すフローチャートである。なお、図11において、“C[n]”(nは自然数)は、入力された数字列を保持するための文字配列、“O”は、現在指示されている四則演算の種類を保持する変数、“N”は確定された演算数、“A”は被演算数であり、最新の演算経過を示している。

【0072】

図11において、情報担体110に処理ユニット120が接続されると、CPU122は、情報担体110の接続部116から取得したIDの内容を判定する(ステップS101)。

ステップS101において、取得したIDが数字(“0”〜“9”)あるいは小数点(“.”)を示すボタンのIDであると判定した場合、CPU122は、文字配列C[n]に、IDに対応する数字あるいは小数点を追加する(ステップS102)。

【0073】

そして、CPU122は、文字配列C[n]を表示パネル114に表示し(ステップS103)、さらに、文字配列C[n]を数値Nに変換した後(ステップS104)、OSに対して休止コールを発行する(ステップS105)。

ステップS105の後、図11に示す処理は終了し、OSに処理が返される。

また、ステップS101において、取得したIDが数値Nの百分率、開平あるいはクリアを示すボタンのIDであると判定した場合、CPU122は、取得したIDに対応する変換処理Tを選択し(ステップS106)、N=T(A,N,O)の演算を実行する(ステップS107)。

【0074】

そして、CPU122は、演算結果である“N”を表示パネル114に表示し(ステップS108)、文字配列C[n]をクリアする(ステップS109)。

ステップS109の後、CPU122は、ステップS105の処理に移行する。

また、ステップS101において、取得したIDが四則演算(“+”、“−”、“×”、“÷”)あるいは等号(“=”)を示すボタンのIDであると判定した場合、CPU122は、保持中の“O”の内容に基づいて、A=O(A,N)の演算を実行する(ステップS110)。

【0075】

そして、CPU122は、演算結果である“A”を表示パネル114に表示し(ステップS111)、取得したIDに対応して演算内容“O”を更新した後(ステップS112)、文字配列C[n]をクリアする(ステップS113)。

ステップS113の後、CPU122は、ステップS105の処理に移行する。

次に、情報処理装置2が、上述のような処理に従って動作する具体例について説明する。

【0076】

ここでは、“12−9√=”と入力し、演算結果を得る場合について説明する。

このとき、ユーザが、ボタン“1”の接続部116に処理ユニットを当接すると、図10の手順に従って、図11の処理が呼び出される。

そして、接続部116のIDにより数字入力に分岐し、C[n]に“1”を追加して、情報担体110の表示パネル114に“1”を表示する。

【0077】

次いで、Nを数値の1にした後、休止コールを発行して、ボタン“1”の接続処理は終了する。

この後、OSの処理により、処理ユニット120は振動し、ユーザはボタンから処理ユニット120を離すことができる。

次に、ボタン“2”に接続する場合も同様の処理を経て、C[n]は文字列“12”を格納し、表示パネル114の表示を数値の12とした後、Nに数値の12が格納される。

【0078】

さらに、ボタン“−”に接続すると、図10の処理は演算子(“−”)の処理に分岐する。

ここで、演算内容は保持されていなかったため、最初のステップでは、Aには無演算のまま12が格納される。

続いて、“12”および“−”の記号を表示し、Oに減算を登録して、C[n]をクリアした後、休止コールを発行して、ボタン“−”の接続処理は終了する。

【0079】

この後、ボタン“9”に接続すると、C[n]に“9”、Nに数値9が入力された状態となり、表示パネル114における表示に“9”が加えられる。

次に、ボタン“√”に接続すると、図11において変換処理に分岐し、処理として開平が選択されて、Nが数値3に変換される。

そして、表示パネル114における“9”の表示が“3”に改められ、C[n]がクリアされた後、休止コールが発行される。

【0080】

最後に、ボタン“=”に接続すると、図10の処理は演算子(“=”)に分岐し、保持中の減算に基づき、A(12)−N(5)が演算され、Aに結果の7が格納される。

この結果を表示パネル114に表示し、Oに無変換を登録し、C[n]をクリアした後、休止コールが発行される。

このように、処理ユニット120が情報担体110に接続された際に行うべき処理の要素のみが、それぞれの接触において行われ、これらが連続の操作により組合わされることにより、全体の処理が遂行される。

【0081】

連続するボタン操作間では、情報担体110上に処理のコンテキストが保持されているので、矛盾を生じることなく一連の処理を行うことが可能である。

また、連続するボタン操作の間では、処理ユニット120内には必要な情報(処理コンテキスト)が残されていないので、処理ユニット120が、別の情報担体110との間における処理を任意のタイミングで行うことも可能である。

【0082】

また、1つのボタン操作が終了した後であれば、ある時点から別の処理ユニット120に換えて情報担体110を操作することも可能である。

なお、情報担体110に記憶されるアプリケーションプログラムは、上記の形態に限られるものでなく、OSとアプリケーションとの役割の分担は様々な形態とすることが可能である。例えば、一連の関数(統合した1つのプログラム)にまとまっておらず、接続部116のID毎に処理を記述したルーチンの集合体のような形態としても良い。この場合、接続部116のID毎の処理のディスパッチはOSが行うこととなる。

【0083】

以上のように、本実施の形態に係る情報処理装置2は、不揮発的に処理コンテキストを記憶可能な情報担体110と、演算処理機能を備えた処理ユニット120とが別体の構成とされている。そして、処理ユニット120が情報担体110の接続部116に接続されると、その都度、情報担体110の処理コンテキストが処理ユニット120に復帰され、処理ユニット120は、接続された接続部116に対応する処理を実行する。その後、処理ユニット120は、処理結果の処理コンテキストを情報担体110に退避した後、情報担体110との接続を解除される。

【0084】

そのため、処理対象の情報が、情報担体110と一体化したものとして認識され、複数の処理ユニット120によって、いずれの処理ユニット120も区別することなく情報を取り扱うことができることとなる。

したがって、情報処理システムにおいて情報を取り扱う上で、処理対象の情報を主体として取り扱うことが容易となると共に、有体物として情報を認識し易く、ユーザにとって利便性の高いものとすることができる。

【0085】

また、処理ユニット120は、それぞれ固有の処理コンテキストを記憶している複数の情報担体110に対し、いずれの情報担体110とも特定の関係を有することなく演算処理能力を提供するものとなるため、処理コンテキストを情報担体110に具現化した形態の、一種のマルチタスク処理システムを構築することができる。

なお、本実施の形態においては、処理ユニット120が、情報担体110と接続している間のみ処理を行うものとして説明したが、処理ユニット120において、情報担体110に関連したプログラムを実行するほかに、システムサービスを維持するためのシステムタスクを動作させることとしてもよい。このようなシステムタスクとしては、例えばファイルサービスのためのタスクや、ネットワーク通信のタスク、タスク間の情報のコピー&ペースト、すなわちクリップボードサービス等が挙げられる。

【0086】

このようなシステムタスクは、従来のマルチタスクシステムと同様の制御方法で、情報担体110に関連したプログラムを実行するタスクと並列動作させることが可能である。この場合、本実施の形態のOSのプログラムは、それらと並列な1つのタスクとして実現し、そのタスクに図10の処理を行わせるように構成すれば良い。

また、本発明は、上記実施の形態に記載した以外の処理を行う構成とすることも可能である。

【0087】

図12は、本発明の他の実施の形態を示す図であり、情報のスクラップブック機能を実現する構成例を示す図である。

図12において、処理ユニットがメニュー表示用の接続部に接続すると、情報担体上のプログラムは、「ルートメニュー」を表示する処理を行って休止する。

次いで、ユーザが、メニューで示された処理を選択し、対応する接続部(選択ボタン)に接続すると、情報担体上のプログラムはそのコンテキストに応じて指定の処理を行う。

【0088】

例えば、「ルートメニュー」が表示された状態で、新規ページへのペーストに対応する接続部(選択ボタン)への接続操作をした際には、処理ユニットのクリップボードザービスにコピー格納された画像・テキスト・音声等の情報を取得して、新規ページに関連付けて記憶するといった動作を行って休止する。

このようにページに関連付けて記憶された情報は、接続部(ページ送りボタン)に接続した際に動作する情報担体上のプログラムにおいて、順次、表示パネルに表示されるように構成することができる。

【0089】

また、「ルートメニュー」から選択可能となる「このページをコピー」の動作により、表示中の情報を、処理ユニットのクリップボードサービスに送出するように構成することができる。

このように、本発明においては、対話的な処理を行う情報担体を構成して、より複雑な処理を行わせることも可能となる。

【0090】

さらに、上記第1および第2の実施の形態において、処理ユニット20,120をペン型とする場合を例に挙げて説明したが、処理ユニット20,120の形態としては、これに限られず、種々の形態とすることが可能である。

【図面の簡単な説明】

【0091】

【図1】第1の実施の形態に係る情報処理システム1の外観構成を示す図である。

【図2】情報処理システム1の機能構成を示すブロック図である。

【図3】接続部17が、電磁的なユーザインターフェースからなる指示入力部15の機能を兼ね備える構成例を示す図である。

【図4】情報担体10それぞれが、個々の情報担体10を識別するためのID記憶部を備える構成を示す図である。

【図5】記憶性の表示体に代えて、記憶性を有しない表示体と、その表示状態を維持するための小規模な電源とを併せ持つ情報担体10の構成を示す図である。

【図6】本発明の第2の実施の形態に係る情報処理システム2(情報担体側)の外観構成を示す図である。

【図7】情報処理システム2の機能構成を示すブロック図である。

【図8】NVRAM112に記憶される処理コンテキストの一例を示す図である。

【図9】情報処理装置2におけるメモリ空間のメモリマップを示す図である。

【図10】情報処理装置2の使用手順を示すフローチャートである。

【図11】アプリケーションプログラムに基づくCPU122の処理を示すフローチャートである。

【図12】本発明の他の実施の形態を示す図であり、情報のスクラップブック機能を実現する構成例を示す図である。

【符号の説明】

【0092】

1,2 情報処理システム、10,110 情報担体、10P ID記憶部、10Q 保持電源、11,111 データ記憶部、12,112 NVRAM、13,113 表示駆動部,13a 描画データ書き込み部,14,114 表示パネル、15,29 指示入力部、115,121 ROM、16 接続制御部、17,116,26,126 接続部,18,28,118,127 バス、20,120 処理ユニット、21 データI/F、22,122 CPU、23 記憶部、23a プログラム記憶部、23b,123 RAM、24 GA、25 接続制御部、27,125 バッテリ、30 電源ユニット,110 解析・整形部,120 描画処理部,130 抽出処理部

【特許請求の範囲】

【請求項1】

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを含む情報処理システムであって、

前記情報保持装置は、

所定の情報処理に係る処理コンテキストを記憶する処理コンテキスト記憶手段を備え、

前記情報処理装置は、

通信可能となった前記情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに所定処理を施し、処理結果である処理コンテキストを前記情報保持装置の処理コンテキスト記憶手段に記憶する情報処理手段を備えることを特徴とする情報処理システム。

【請求項2】

前記情報保持装置は、

所定のアプリケーションプログラムを記憶するアプリケーション記憶手段をさらに備え、

前記処理コンテキスト記憶手段は、前記アプリケーションプログラムに係る処理コンテキストを記憶することを特徴とする請求項1記載の情報処理システム。

【請求項3】

前記情報保持装置は、所定処理にそれぞれ対応した、前記情報処理装置と接続するための接続手段を複数備え、

前記情報処理手段は、自装置が接続された前記接続手段が対応している所定処理を判定する判定手段を備え、

該接続手段に接続された前記情報処理装置の情報処理手段は、前記判定手段によって判定された所定処理を行い、その処理結果である処理コンテキストを前記処理コンテキスト記憶手段に記憶することを特徴とする請求項1または2記載の情報処理システム。

【請求項4】

前記情報処理装置と前記情報保持装置との接続を解除可能であることを報知する報知手段をさらに備え、

前記情報処理装置の情報処理手段は、所定処理を施した結果である前記処理コンテキストを前記処理コンテキスト記憶手段に記憶した後、前記報知手段によって、前記情報保持装置との接続を解除可能であることを報知することを特徴とする請求項1から3のいずれか1項に記載の情報処理システム。

【請求項5】

前記情報保持装置は、前記情報処理装置の電源から電力の供給を受けて動作することを特徴とする請求項1から4のいずれか1項に記載の情報処理システム。

【請求項6】

前記情報保持装置は、表示状態を不揮発的に保持可能な記憶性の表示装置を備えることを特徴とする請求項1から5のいずれか1項に記載の情報処理システム。

【請求項7】

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを含む情報処理システムにおける情報処理装置であって、

所定の情報処理に係る処理コンテキストを記憶する前記情報保持装置と通信可能となった場合に、該情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに対し、前記所定処理を施し、処理結果である処理コンテキストを前記情報保持装置の処理コンテキスト記憶手段に記憶する情報処理手段を備えることを特徴とする情報処理装置。

【請求項8】

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを含む情報処理システムにおける情報保持装置であって、

所定の情報処理に係る処理コンテキストを記憶する処理コンテキスト記憶手段を備え、

通信可能となった前記情報処理装置に対し、前記処理コンテキスト記憶手段に記憶された処理コンテキストを出力すると共に、前記情報処理装置の処理結果である処理コンテキストを前記処理コンテキスト記憶手段に記憶することを特徴とする情報保持装置。

【請求項9】

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを用いた情報処理方法であって、

前記情報保持装置が、所定の情報処理に係る処理コンテキストを記憶し、

前記情報処理装置が、通信可能となった前記情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに所定処理を施し、処理結果である処理コンテキストを前記情報保持装置に記憶させることを特徴とする情報処理方法。

【請求項1】

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを含む情報処理システムであって、

前記情報保持装置は、

所定の情報処理に係る処理コンテキストを記憶する処理コンテキスト記憶手段を備え、

前記情報処理装置は、

通信可能となった前記情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに所定処理を施し、処理結果である処理コンテキストを前記情報保持装置の処理コンテキスト記憶手段に記憶する情報処理手段を備えることを特徴とする情報処理システム。

【請求項2】

前記情報保持装置は、

所定のアプリケーションプログラムを記憶するアプリケーション記憶手段をさらに備え、

前記処理コンテキスト記憶手段は、前記アプリケーションプログラムに係る処理コンテキストを記憶することを特徴とする請求項1記載の情報処理システム。

【請求項3】

前記情報保持装置は、所定処理にそれぞれ対応した、前記情報処理装置と接続するための接続手段を複数備え、

前記情報処理手段は、自装置が接続された前記接続手段が対応している所定処理を判定する判定手段を備え、

該接続手段に接続された前記情報処理装置の情報処理手段は、前記判定手段によって判定された所定処理を行い、その処理結果である処理コンテキストを前記処理コンテキスト記憶手段に記憶することを特徴とする請求項1または2記載の情報処理システム。

【請求項4】

前記情報処理装置と前記情報保持装置との接続を解除可能であることを報知する報知手段をさらに備え、

前記情報処理装置の情報処理手段は、所定処理を施した結果である前記処理コンテキストを前記処理コンテキスト記憶手段に記憶した後、前記報知手段によって、前記情報保持装置との接続を解除可能であることを報知することを特徴とする請求項1から3のいずれか1項に記載の情報処理システム。

【請求項5】

前記情報保持装置は、前記情報処理装置の電源から電力の供給を受けて動作することを特徴とする請求項1から4のいずれか1項に記載の情報処理システム。

【請求項6】

前記情報保持装置は、表示状態を不揮発的に保持可能な記憶性の表示装置を備えることを特徴とする請求項1から5のいずれか1項に記載の情報処理システム。

【請求項7】

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを含む情報処理システムにおける情報処理装置であって、

所定の情報処理に係る処理コンテキストを記憶する前記情報保持装置と通信可能となった場合に、該情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに対し、前記所定処理を施し、処理結果である処理コンテキストを前記情報保持装置の処理コンテキスト記憶手段に記憶する情報処理手段を備えることを特徴とする情報処理装置。

【請求項8】

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを含む情報処理システムにおける情報保持装置であって、

所定の情報処理に係る処理コンテキストを記憶する処理コンテキスト記憶手段を備え、

通信可能となった前記情報処理装置に対し、前記処理コンテキスト記憶手段に記憶された処理コンテキストを出力すると共に、前記情報処理装置の処理結果である処理コンテキストを前記処理コンテキスト記憶手段に記憶することを特徴とする情報保持装置。

【請求項9】

所定の接続動作によって互いに通信可能となる情報処理装置と情報保持装置とを用いた情報処理方法であって、

前記情報保持装置が、所定の情報処理に係る処理コンテキストを記憶し、

前記情報処理装置が、通信可能となった前記情報保持装置から処理コンテキストを取得し、取得した処理コンテキストに所定処理を施し、処理結果である処理コンテキストを前記情報保持装置に記憶させることを特徴とする情報処理方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2006−277261(P2006−277261A)

【公開日】平成18年10月12日(2006.10.12)

【国際特許分類】

【出願番号】特願2005−94760(P2005−94760)

【出願日】平成17年3月29日(2005.3.29)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.FRAM

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成18年10月12日(2006.10.12)

【国際特許分類】

【出願日】平成17年3月29日(2005.3.29)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.FRAM

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]