情報処理装置、その制御方法、および制御プログラム

【課題】ソフトウェアを更新している際に、ジョブ処理要求を受信した場合においても、当該ジョブがキャンセルされることがなく、ユーザの利便性を向上させる。

【解決手段】画像形成装置は、互いに独立して動作する複数のモジュールと、モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたフラッシュROMを備えている。モジュールのいずれかでソフトウェアの更新が行われている際、ジョブを受け付けると、メインCPU201は当該ジョブで用いるモジュールがソフトウェアの更新中であるか否かを判定する。そして、ジョブで用いるモジュールがソフトウェアの更新中であると判定すると、メインCPUはソフトウェアの更新が終了するまで、ジョブの実行を待機する。

【解決手段】画像形成装置は、互いに独立して動作する複数のモジュールと、モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたフラッシュROMを備えている。モジュールのいずれかでソフトウェアの更新が行われている際、ジョブを受け付けると、メインCPU201は当該ジョブで用いるモジュールがソフトウェアの更新中であるか否かを判定する。そして、ジョブで用いるモジュールがソフトウェアの更新中であると判定すると、メインCPUはソフトウェアの更新が終了するまで、ジョブの実行を待機する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、情報処理装置、その制御方法、および制御プログラムに関し、特に、電子写真方式又は静電記録方式などを用いた画像形成装置に関する。

【背景技術】

【0002】

一般に、情報処理装置の一つとして所謂画像形成装置が知られている。そして、クライアントPCなどの外部装置と複合機などの画像形成装置とをLANなどのネットワークで接続された印刷システムが知られている。ここでは、画像形成装置は外部装置からプリントジョブなどの画像処理ジョブを受けて当該画像処理ジョブを実行する。

【0003】

画像形成装置で実行可能な処理は、当該画像形成装置に備えられたハードウェアリソースの範囲内であれば、CPUが実行するプログラム(ファームウェア)を更新すれば、容易に変更および追加することができる。

【0004】

ところで、ファームウェアの削除・更新を高速にするとともに、タイマジョブとして実行待ちとなっている予約画像処理ジョブを遂行するソフトウェアパーツを、通常のジョブに支障をきさない範囲で適宜削除・更新するため、予約画像処理ジョブに更新対象となるソフトウェアパーツを用いる処理が含まれているか否かを判定するようにしたものがある。そして、ここでは、予約画像処理ジョブに更新対象となるソフトウェアパーツを用いる処理が含まれていないと判定した場合には、当該更新対象のソフトウェアパーツの更新処理を行う(特許文献1参照)。

【0005】

そして、特許文献1においては、予約ジョブ中に当該ソフトウェアパーツが含まれているが、ネットワーク上の他の画像形成装置が備えるソフトウェアパーツで代替することができると判断した場合には、当該他の画像形成装置を用いるように再スケジューリングを行う。一方、代替する画像形成装置が存在しないと判断した場合には、当該更新要求を保留にしている。

【0006】

さらに、ファームウェアのバージョンアップを行う際、新しいファームウェアをダウンロードして、このファームウェアをRAM領域に一時記憶するようにしたものがある(特許文献2参照)。ここでは、電源オンの際にプログラムが動作を開始するプログラムリセットベクタに分岐して、RAM領域にロードされたファームウェアを読み出して、このファームウェアを従来のファームウェアが存在していたPROM領域に書き込んでいる。そして、特許文献2では、実行中および実行待機中の画像処理ジョブを検知して、これらジョブが存在すると、前述のファームウェア更新動作を保留するようにしている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−108957号公報

【特許文献2】特開2001−273143号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところが、上述の特許文献1では、更新すべきソフトウェアパーツがある場合において、その更新と予約画像処理ジョブとをスケジューリングしているだけであって、例えば、ソフトウェアパーツの更新中にプリント処理要求コマンドを受信した場合には処理を行うことが困難となってしまう。

【0009】

つまり、特許文献1に記載の画像形成装置では、ソフトウェアパーツを更新している際に、当該ソフトウェアパーツを用いるプリント処理要求などのジョブを受信しても、当該ジョブを実行することができず、このジョブはキャンセルせざるを得ない。よって、ユーザは再度ジョブを投入しなければならず、ユーザにとっては使い勝手が極めて悪い。

【0010】

同様に、特許文献2においても、画像処理ジョブの実行中にファームウェアをダウンロードすべきタイミングが到来した際の処理を行っているのみで、ファームウェアのダウンロード中にプリント処理要求コマンドを受けた際には処理を行うことが困難となってしまう。

【0011】

従って、特許文献2に記載の画像形成装置においても、ファームウェアのダウンロード中にプリント処理要求などのジョブを受信しても、当該ジョブを実行することができず、このジョブはキャンセルせざるを得ない。よって、ユーザは再度ジョブを投入しなければならず、ユーザにとっては使い勝手が極めて悪い。

【0012】

よって、本発明の目的は、ソフトウェアパーツ(プログラム)を更新している際に、ジョブ処理要求を受信した場合においても、当該ジョブがキャンセルされることがなく、ユーザにとって利便性の向上した情報処理装置、その制御方法、および制御プログラムを提供することにある。

【課題を解決するための手段】

【0013】

上記の目的を達成するため、本発明による情報処理装置は、互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置であって、前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新手段と、前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定手段と、前記判定手段によって前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御手段とを有することを特徴とする。

【0014】

本発明による制御方法は、互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置の制御方法であって、前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新ステップと、前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定ステップと、前記判定ステップで前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御ステップとを有することを特徴とする。

【0015】

本発明による制御プログラムは、互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置で用いられる制御プログラムであって、前記情報処理装置に備えられたコンピュータに、前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新ステップと、前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定ステップと、前記判定ステップで前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御ステップとを実行させることを特徴とする。

【発明の効果】

【0016】

本発明よれば、ソフトウェアが更新中であるモジュールを用いるジョブを受けても、当該ジョブをキャンセルすることなく待機させるようにしたので、ユーザにとって利便性が向上する。

【図面の簡単な説明】

【0017】

【図1】本発明の実施の形態による情報処理装置の一つである画像形成装置の一例についてその構成を概略的に示す断面図である。

【図2】図1に示す画像形成装置の制御系(制御部)の一例を示すブロック図である。

【図3】図2に示すYMCドラムモータ/高圧ドライバ、Kドラム/高圧・ITBモータ・二次転写高圧ドライバ、両面/反転ユニットドライバ、オプションカセットドライバ、およびバッファパス/フィニッシャドライバについて説明するためのブロック図である。

【図4】図1に示す画像形成装置に備えられたユーザ操作部401の一例を示す図である。

【図5】図4に示すユーザ操作部401に表示された表示画面の一例を示す図である。

【図6】図3に示すメインCPUとサブCPUとの接続形態の一例を示すブロック図である。

【図7】図6に示すメインCPUとサブCPUとにおいて行われるモード切り替え処理を説明するためのフローチャートである。

【図8】プログラムモードの際に図6に示すメインCPUとサブCPUとの間で行われる通信について説明するためのフローチャートである。

【図9】プログラムモードの際に図6に示すメインCPUとサブCPUとの間で行われる通信について説明するためのシーケンス図である。

【図10】図6に示すメインCPUとサブCPUとの間でファームウェア更新を行った際の信号波形を説明するためのタイムチャートである。

【図11】図3に示すRAMに保持されるサブCPU状態テーブルの一例を示す図である。

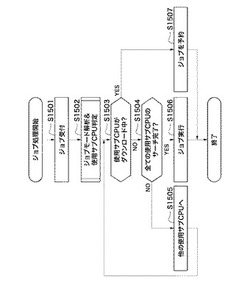

【図12】図3に示すいずれかのサブCPUにおいてファームウェアの更新中である場合にスタートキーが押し下げられた際のメインCPUの動作の一例を説明するためのフローチャートである。

【図13】図3に示すメインCPUがユーザ操作部401から受けるジョブモード情報の一例を示す図である。

【図14】図3に示すROMに格納されたサブCPU関連付けテーブルの一例を示す図である。

【図15】図12に示す使用サブCPU判定処理の一例を詳細に説明するためのフローチャートである。

【図16】図5に示すジョブモードの設定(ジョブ設定)が行われた際の使用サブCPU判定処理における判定結果を示す図である。

【図17】図12で説明した予約ジョブの実行を説明するためのフローチャートである。

【図18】図3に示すいずれかのサブCPUにおいてファームウェアの更新中である場合にスタートキーが押し下げられた際のメインCPUの動作の他の例を説明するためのフローチャートである。

【図19】図18に示すジョブキャンセル判定処理の際にユーザ操作部401に表示されるポップアップウィンドウの一例を示す図である。

【発明を実施するための形態】

【0018】

以下、本発明の実施の形態による情報処理装置の一例について図面を参照して説明する。

【0019】

図1は、本発明の実施の形態による情報処理装置の一つである画像形成装置の一例についてその構成を概略的に示す断面図である。

【0020】

図1において、図示の画像形成装置は、所謂カラー複合機であり、画像形成装置本体100、画像読取装置140、および後処理装置160を備えている。

【0021】

いま、図示の画像形成装置を用いてコピーを行おうとする際には、読み取りガラス142上に原稿が配置される。そして、スキャナーユニット143によって原稿上の画像が光学的に読み取られて、光学像として光電変換部(例えば、CCD)144に与えられる。光電変換部114は光学像を電気信号(画像信号)に変換する。そして、この電気信号は制御装置(図示せず)に与えられて、ここで、所定の処理が施されて、画像データとされる。

【0022】

画像形成装置本体100は、イエロー(Y)プロセスユニット101y、マゼンダ(M)プロセスユニット101m、シアン(C)プロセスユニット101c、およびブラック(K)プロセスユニット101kを備えている。そして、これらプロセスユニットの各々は感光ドラム、現像器、および帯電ローラなどを有している。

【0023】

ここで、Kプロセスユニット101kに注目して、Kプロセスユニット101kには感光ドラム102kが収納されている。この感光ドラム102kはドラムモータ(図示せず)によって回転駆動される。感光ドラム102kの表面は帯電ローラ103kによって一様に帯電される。レーザスキャナユニット104kは、画像データに応じて変調されたレーザ光を、ポリゴンミラー回転体(図示せず)によって感光ドラム102kをその長手方向に走査する。

【0024】

レーザ光の走査によって、感光ドラム102kの表面には画像データに応じた静電潜像が形成される。現像器105kには、例えば、Kトナーおよびキャリアを有する二成分現像剤が収納されている。この現像器105kには、トナーが充填されたトナーボトル106kが連結され、トナーボトル106kからKトナーが現像器105kに供給される。現像器105kは感光ドラム102k上の静電潜像をKトナーで現像してKトナー像とする。

【0025】

Kプロセスユニット101kには、補助帯電ブラシ109kが備えられており、中間転写ベルト(中間転写体)108にKトナー像を転写した際に感光ドラム102kに残留する転写残トナーを一様に帯電させる。そして、この転写残トナーは感光ドラム102kから除去されて回収される。

【0026】

なお、Yプロセスユニット101y、Mプロセスユニット101m、Cプロセスユニット101cはKプロセスユニット101kと同様の構成を有している。

【0027】

Yプロセスユニット101y、Mプロセスユニット101m、Cプロセスユニット101c、およびKプロセスユニット101kに中間転写ベルト108を介してそれぞれ一次転写ローラ107y、107m、107c、および107kが対向している。そして、一次転写107y、107m、107c、および107kによってYプロセスユニット101y、Mプロセスユニット101m、Cプロセスユニット101c、およびKプロセスユニット101kから順次Yトナー像、Mトナー像、Cトナー像、およびKトナー像が中間転写ベルト108に転写されて重ね合わされる。これによって、中間転写ベルト108にはカラートナー像が形成される。

【0028】

中間転写ベルト108上のカラートナー像は、中間転写ベルト108の回転によって二次転写位置に搬送される。

【0029】

一方、用紙カセット(給紙カセット又は単にカセットともいう)113、125、および126から選択的に給紙ローラ114、127、および128によって用紙が用紙搬送路に搬送される。そして、用紙はレジストローラ115によって斜行を補正された後、二次転写位置に送られる。二次転写位置において、中間転写ベルト108上のカラートナー像は二次転写ローラ110によって用紙に転写される。その後、用紙は定着器に送られて、ここで、定着ローラ117および加圧ローラ118によって用紙上のカラートナー像が熱定着される。

【0030】

なお、トナー濃度補正を行うため、Kプロセスユニット101kの出口近傍にはパターン濃度検知センサ112が配置されている。トナー濃度補正を行う際には、予め定めらたれパターンを有する濃度補正用パターンが中間転写ベルト108上に形成される。そして、濃度検知センサ112によって濃度補正用パターンを検知してその検知結果に応じて濃度補正が行われる。

【0031】

また、中間転写ベルト108に残留した転写残トナーは中間転写体クリーナ111によって回収される。

【0032】

片面印刷の際には、定着器を出た用紙は、排紙フラッパ119によって排紙ローラ120を備える排紙経路に送られる。そして、後処理を行う際には、用紙は後処理フラッパ152によって、バッファパス搬送ローラ151を備えるバッファパスユニット150に搬送されて、ここから後処理装置(フィニッシャ)160に送られる。後処理装置160は用紙又は用紙束に対して所定の後処理を行った後、フィニッシャトレイ161又は162に用紙又は用紙束を排紙する。

【0033】

後処理を行わない場合には、用紙は後処理フラッパ152によって、排紙トレイ121に排紙される(洞内排紙)。

【0034】

両面印刷を行う場合には、定着器を出た用紙は排紙フラッパ119によって両面反転フラッパ123を介して両面反転駆動ローラ122に送られる。続いて、両面判定駆動ローラ122によって用紙は逆方向に搬送されて、反転フラッパ123によって、両面再給紙駆動ローラ124を備える両面印刷搬送路に送られる。そして、用紙は再度レジストローラ115に送られて、前述のようにして、裏面側に印刷が行われることになる。

【0035】

なお、モノクロ印刷の際には、Kプロセスユニット101kのみが用いられ、Kプロセスユニット101kから中間転写ベルト108にKトナー像が転写される。

【0036】

図2は、図1に示す画像形成装置の制御系(制御部)の一例を示すブロック図である。

【0037】

次に、本画像形成装置の制御回路構成について、図2のブロック図を用いて説明する。

【0038】

図示の制御部はメインCPU201を備えており、このメインCPU201は画像形成装置全体の制御を司る。ROM202にはメインCPU201上で動作する制御プログラムなどが格納され、RAM203はメインCPU201が一時的にデータなどを記憶するために用いられる。バックアップRAM204は画像形成装置が動作する際に設定された設定情報などが記憶される。バックアップRAM204にはバックアップバッテリ(図示せず)によって電源が供給され、画像形成装置のメイン電源を断としても、バックアップRAM204に記憶された設定情報は保持される。

【0039】

モータドライバ205は、図1に示す給紙ローラ114およびレジストローラ115などの回転制御を行う。メインCPU201にはシリアルインターフェイス(SCI)206が備えられており、SCI206は8CH(8チャンネル)の信号線によってメインCPU201に接続された各種モジュールと通信を行う。各チャンネルは2本の信号線を備え、これによって全二重通信が行われる。そして、メインCPU201は後述するモジュールを制御する。

【0040】

ネットワークインターフェイス(I/F)207は画像データを供給するプリンタコントローラ(システムコントローラ:図示せず)と接続される。レーザドライバ208は、図1に示すレーザスキャナユニット104y、104m、104c、および104kを制御する。YMCドラムモータ/高圧ドライバ209はYプロセスユニット101y、Mプロセスユニット101m、およびCプロセスユニット101cの各々に備えられた感光ドラム駆動モータ(図示せず)を駆動制御するとともに、帯電、現像、および一次転写に係る電圧制御を行う。

【0041】

Kドラム/高圧・ITBモータ・二次転写高圧ドライバ210はKプロセスユニット101kに備えられた感光ドラム駆動モータ(図示せず)を駆動制御するとともに、帯電、現像、および一次転写に係る電圧制御を行う。さらに、Kドラム/高圧・ITBモータ・二次転写高圧ドライバ210は中間転写体108の駆動モータを駆動制御するとともに、二次転写ローラ110に係る二次転写電圧制御を行う。

【0042】

両面・反転ユニットドライバ211は。両面反転駆動ローラ122および両面再給紙駆動ローラ124を駆動制御するとともに、両面反転フラッパ123の回動制御を行う。オプションカセットドライバ212は増設給紙カセットである用紙カセット125および126において給紙ローラ127および128を駆動制御する。

【0043】

バッファパス/フィニッシャドライバ213はバッファパスユニット150およびフィニッシャ160を制御する。つまり、バッファパス/フィニッシャドライバ213はバッファパス搬送ローラ151を駆動制御するとともに、フィニッシャ上トレイ161およびフィニッシャ下トレイ162の昇降制御を行う。

【0044】

図3は、図2に示すYMCドラムモータ/高圧ドライバ209、Kドラム/高圧・ITBモータ・二次転写高圧ドライバ210、両面/反転ユニットドライバ211、オプションカセットドライバ212、およびバッファパス/フィニッシャドライバ213について説明するためのブロック図である。

【0045】

図2で説明したCPU201、ROM202、RAM203、およびバックアップRAM204はメインエンジンコントローラボード201aに搭載されている。YMCドラムモータ/高圧ドライバ209は、サブCPU301、フラッシュROM302、およびSRAM303を備えている。フラッシュROM302にはサブCPU301上で動作する制御プログラムが格納されている。SRAM303は、例えば、サブCPU301の作業領域として用いられる。そして、サブCPU301はCPU201の制御下でYMCドラムモータ304およびYMC高圧ユニット305を制御する。

【0046】

Kドラム/高圧・ITBモータ・二次転写高圧ドライバ210は、サブCPU311、フラッシュROM312、およびSRAM313を備えている。フラッシュROM312にはサブCPU311上で動作する制御プログラムが格納されている。SRAM313は、サブCPU311の作業領域として用いられる。そして、サブCPU311は、CPU201の制御下でKドラムITBモータ314、K高圧ユニット315、および二次転写高圧ユニット316を制御する。

【0047】

両面/反転ユニットドライバ211は、サブCPU321、フラッシュROM322、およびSRAM323を備えている。フラッシュROM322にはサブCPU321上で動作する制御プログラムが格納されている。SRAM323は、サブCPU321の作業領域として用いられる。そして、サブCPU321はCPU201の制御下で両面反転モータ324および両面再給紙モータ325を制御する。

【0048】

オプションカセットドライバ212は、サブCPU331、フラッシュROM332、およびSRAM333を備えている。フラッシュROM332にはサブCPU331上で動作する制御プログラムが格納されている。SRAM333は、サブCPU331の作業領域として用いられる。そして、サブCPU331は、CPU201の制御下で増設カセット給紙モータ334および335を制御する。

【0049】

バッファパス/フィニッシャドライバ213は、サブCPU341、フラッシュROM342、およびSRAM343を備えている。フラッシュROM342にはサブCPU341上で動作する制御プログラムが格納されている。SRAM343は、サブCPU341の作業領域として用いられる。そして、サブCPU341は、CPU201の制御下でバッファパスモータ344、フィニッシャ上トレイ161およびフィニッシャ下トレイ162を駆動する昇降モータ345、およびフィニッシャ160が備えるステイプル機構346を制御する。

【0050】

図4は、図1に示す画像形成装置に備えられたユーザ操作部401の一例を示す図である。

【0051】

ユーザ操作部401は電源スイッチ404を備えており、電源スイッチ404の操作によって画像形成装置の主電源がオン又はオフされる。節電ボタン403の操作によって画像形成装置は所定の節電モードに移行する。電源LED404は主電源がオンの場合に、例えば、緑色に点灯する。また、電源LED404はユーザの操作で選択された機能が動作中であると緑色に点滅する。さらに、電源LED404は画像形成装置においてエラーなどが発生した際には赤色に点灯して、ユーザに異常を報知する。

【0052】

液晶表示部(LCD)501は、例えば、タッチパネル式のTFTドットマトリクス型の液晶パネルによって構成される。そして、LCD501において画像形成装置における各モードの操作・表示が行われ、各モードの切り替えが行われる。

【0053】

テンキー406は、例えば、コピー枚数およびFAX送信先などの数字を入力する際に用いられる。リセットキー407は入力した数値をクリアする際に用いられ、さらに現在選択中のモードにおいて初期状態に戻る際に用いられる。スタートキー408は、液晶表示部501又はテンキー406による入力操作に応じた動作を開始するためのキーである。

【0054】

ストップキー409は、スタートキー408によって開始された動作を、動作途中でキャンセルするためのキーである。ヘルプキー410はユーザの操作によって表示画面に対する説明文章を表示するためのキーである。ユーザモードボタン411はユーザが予めユーザ設定を行うためのキーである。

【0055】

図5は、図4に示すユーザ操作部401に表示された表示画面の一例を示す図である。

【0056】

図5に示す表示画面はLCD501に表示される。ここでは、ユーザによってコピーモードが詮索された際の表示画面(つまり、コピーモード画面)が示されている。コピーモード画面は、ファンクション選択ボタン画面501、操作パネル画面502、およびステータス表示画面511を有する。

【0057】

ファンクション選択ボタン画面502において、ユーザが所望のファンクションキーをタッチすると、CPU201は当該タッチされたキーに応じた動作(つまり、機能)に切り替える。機能が切り替わると、CPU201は当該切り替わった機能を表示する表示画面をLCD501に表示する。図示の例では、コピーモードであるから、”COPY”が点灯しているが、ユーザが、例えば、”FAX”をタッチすると、FAX動作モード画面がLCD501に表示される。この際には、ファンクション選択ボタン画面502において、”FAX”が点灯する。

【0058】

操作パネル画面503には、コピーが実行可能であるか否かを示す情報が表示され、さらに、用紙サイズの設定などのモード設定およびコピー枚数などが表示される。コピー枚数はテンキー406からの入力によって設定され、操作パネル画面503に表示される。

【0059】

さらに、操作パネル画面503には、色モード設定504、倍率設定505、片面・両面設定506、用紙選択設定507、および排紙トレイ設定508が表示される。そして、ユーザはタッチ操作によって色モード、倍率、片面・両面設定、用紙選択、および排紙トレイの設定を行う。

【0060】

つまり、色モード設定504では白黒モード又はカラーモードのいずれかを選択することができる。倍率設定505では、縮小、等倍、又は拡大の設定を行うことができ、選択された倍率は、前述のように、操作パネル画面503に表示される。

【0061】

片面・両面設定506では、片面コピー又は両面コピーのいずれかを選択することができる。用紙選択設定507ではいずれの給紙カセットに収納された用紙を用いるかを選択することができる。排紙トレイ設定508では、プリント後の用紙をいずれのトレイに排紙するかを設定する。

【0062】

ステータス表示画面511には、画像形成装置の状態が変化した際に、その状態変化の旨がメッセージとして表示される。

【0063】

図6は、図3に示すメインCPU201とサブCPU301との接続形態の一例を示すブロック図である。図6においては、メインCPU201とサブCPU301との接続形態について説明するが、メインCPU301とサブCPU311〜341との接続形態についてもサブCPU301と同様である。

【0064】

メインCPU201はリセット信号線(RESET)601、ブートモード信号線(BOOTMODE)602、送信信号線(TxD)信号線603、および受信信号線(RxD)信号線604によってサブCPU301に接続されている。

【0065】

RESET601は、メインCPU201が出力側となって、サブCPU301が入力側となって、メインCPU201によって所定のタイミングでサブCPU301をリセットする際に用いられる。そして、RESET601は動作時にH(ハイ)レベルとなり、リセット時にはL(ロー)レベルとなる。

【0066】

BOOTMODE602は、メインCPU201が出力側、サブCPU301が入力側となって、サブCPU301がリセットして再起動した後の動作モードを決定するために用いられる。BOOTMODE602は通常時にHレベルとなり、ファームウェア更新モード時にはLレベルとなる。

【0067】

TxD603は、メインCPU201からサブCPU301にシリアル通信信号を送信するためのものである。TxD603においては、TTLレベルの調歩同期で8ビットずつ情報が送信される。RxD604は、サブCPU301からメインCPU201にシリアル通信信号を送信するためのものである。RxD604においても同様にTTLレベルの調歩同期で8ビットずつ情報が送信される。

【0068】

続いて、図3に示すサブCPU301〜341におけるファームウェアの更新処理について説明する。ここでは、サブCPU301におけるファームウェアの更新処理を例に挙げて説明するが、サブCPU311〜341におけるファームウェアの更新処理についても同様である。

【0069】

サブCPU301の制御プログラムが格納されたフラッシュROM302は、例えば、32kバイトの容量を備えている。そして、このフラッシュROM302は所定の手順に応じてアクセスを行って書き込み処理を行うことができる。サブCPU301に係る制御プログラムの更新中においては、更新対象であるフラッシュROM302にプログラムコード(つまり、制御プログラム)が存在すると、書き換えプログラムが動作することができない。

【0070】

よって、まず、サブCPU301のワーク領域であるSRAM303に書き換えプログラムを保存して、書き換えプログラムをサブCPU301で動作させるためのプログラムモードに移行する(つまり、モード切り替え処理を行う必要がある)。

【0071】

図7は、図6に示すメインCPU201とサブCPU301とにおいて行われるモード切り替え処理を説明するためのフローチャートである。

【0072】

ファームウェア更新処理を開始すると、メインCPU201はファームウェア更新対象であるサブCPU301についてRESET601をオン(Lレベル)して、サブCPU301をリセットする(ステップS702)。そして、メインCPU201はBOOTMODE602をアクティブ(Lレベル)に設定する。つまり、メインCPU201はBOOTMODE602をプログラムモードに設定する(ステップS703)。

【0073】

サブCPU301は、BOOTMODE602がアクティブの状態でリセットを解除が行われると(ステップS704)、フラッシュROM302のプログラムモードで起動される。プログラムモードにおいては、サブCPU301はTxD603からの通信待ちとなってフラッシュROM302の書き換えプログラムをワークメモリであるSRAM303に展開する。

【0074】

以後、メインCPU201とサブCPU301との通信およびフラッシュROM302の書き換え制御は、SRAM303上に展開されたプログラムに応じて行われる。

【0075】

後述するようにして、サブCPU301において、フラッシュROM302の書き換え(書き込み)が行われた後(ステップS705)、メインCPU201はサブCPU301を再度リセットする(ステップS706)。そして、メインCPU201はBOOTMODE602をインアクティブに設定する。つまり、メインCPU201はBOOTMODE602を通常モードに設定する(ステップS707)。その後、メインCPU201はサブCPU302のリセットを解除して(ステップS708)、ファームウェア更新処理を終了する。

【0076】

図8は、プログラムモードの際に図6に示すメインCPU201とサブCPU301との間で行われる通信について説明するためのフローチャートである。

【0077】

フラッシュROM302の書き換えを行う際、まず、メインCPU201は書き換えを行うためのネゴシエーション情報(ファーム更新リクエスト)をサブCPU301に送信する(ステップS802)。続いて、メインCPU201はファーム更新リクエストに対する応答(書き換え可能応答)をサブCPU301から受信したか否かを判定する(ステップ803)。

【0078】

書き換え可能応答を受信しないと(ステップS803において、NO)、メインCPU201は待機する。一方、書き換え可能応答を受信すると(ステップS803において、YES)、メインCPU201はフラッシュROM302を直接書き換えることができないため、書き換えに先立ってサブCPU301に対してフラッシュメモリ消去要求を発行する(ステップ804)。

【0079】

続いて、メインCPU201は、フラッシュROM302の消去を行ったことを示す応答(フラッシュメモリ消去応答)をサブCPU301から受信したか否かを判定する(ステップS805)。フラッシュメモリ消去応答を受信しないと(ステップS805において、NO)、メインCPU201は待機する。

【0080】

フラッシュメモリ消去要求を受けると、サブCPU301はフラッシュROM302の全ブロックの消去を行う。そして、全ブロックの消去が完了すると、サブCPU302はフラッシュメモリ消去応答をメインCPU201に返信する(ステップ804)。

【0081】

フラッシュメモリ消去応答を受信すると(ステップS805において、YES)、メインCPU201は内蔵するブロックカウンタにn=0を設定する(ステップS806)。ここで、フラッシュROM302のブロック数は256であるとする。つまり、フラッシュROM302には第0〜第255のブロックがあるものとする。

【0082】

続いて、メインCPU201はフラッシュROM301の第0のブロックに書き込むファームウェアイメージを128バイトずつに分割してパケットを生成する。そして、メインCPU201は先頭のパケット(ファームウェア更新データ)をサブCPU301に送信する(ステップ807)。パケットには先頭マーカー又は終端マーカーがヘッダ部に設けられており、先頭のパケットは先頭マーカーで識別される。また、最後のパケットは終端マーカーで識別が可能である。

【0083】

パケットを送信した後、メインCPU201は、サブCPU301からブロックへの書込みが完了したことを示すブロック書込み応答を受信したか否かを判定する(ステップS808)。ブロック書込み応答を受信しないと(ステップS808において、NO)、メインCPU201は待機する。

【0084】

サブCPU302はパケットを受信すると、ファーム更新データをフラッシュROM302に書き込む。1つのブロックの書き込みが完了すると、サブCPU301はブロック書き込み完了応答をメインCPU201に返信する。ブロック書き込み応答を受信すると(ステップS808において、YES)、メインCPU201はブロックカウンタをインクリメント(+1)する(ステップS809)。そして、メインCPU201はブロックカウンタが256未満であるか否かを判定する(ステップS810)。

【0085】

ブロックカウンタが256未満であると(ステップS810において、YES)、メインCPU201はステップS807の処理に戻って、次のブロックに対するファーム更新データを送信する。

【0086】

このようにして、フラッシュROM302に対する書き込みはブロックごとに繰り返されて、サブCPU301は合計256個のパケットを受信して、フラッシュROM302の全てのブロックについてファームウェアの更新が終了する。

【0087】

ブロックカウンタが256となると(ステップS810において、NO)、メインCPU201はサブCPU301にチェックサムの取得要求を送信する(ステップ811)。このチェックサムは、例えば、フラッシュROM302の全領域について奇数アドレスおよび偶数アドレスの値を総計した結果の下位16ビットを用いる。

【0088】

メインCPU201はサブCPU301からチェックサム値を受信したか否かを判定する(ステップS812)。チェックサム値を受信しないと(ステップS812において、NO)、メインCPU201は待機する。

【0089】

サブCPU301はチェックサム取得要求に応答して、メインCPU201に対して奇数アドレスおよび偶数アドレスのチェックサム値を返信する。メインCPU201は、送信したファームウェアイメージのチェックサム値を保持チェックサム値として保持している。チェックサム値を受信チェックサム値として受信すると(ステップ812において、YES)、サブCPUから受信チェックサム値と保持チェックサム値とが一致するか否かを判定する(ステップ813)。

【0090】

受信チェックサム値と保持チェックサム値とが一致しないと(ステップS813において、NO)、メインCPU201はフラッシュROM302に書き込まれたファームウェアが送信したファームウェアイメージと一致していないとして、ステップS806の処理に戻る。そして、メインCPU201はリトライ制御によって先頭パケットから再度送信する。

【0091】

受信チェックサム値と保持チェックサム値とが一致すると(ステップS813において、YES)、メインCPU201はフラッシュROM302の更新は正常に終了したとして、ファームウェア更新を終了する。

【0092】

ここで、プログラムモードにおけるメインCPU201とサブCPU301との通信について図9に示すシーケンス図を用いて説明する。

【0093】

図9は、プログラムモードの際に図6に示すメインCPU201とサブCPU301との間で行われる通信について説明するためのシーケンス図である。

【0094】

まず、メインCPU201がフラッシュ更新リクエスト(Flash Update Req)をサブCPU301に送信する(S901)。このフラッシュ更新リクエストに応答して、サブCPU301はメインCPU201にフラッシュ書き換え可能応答(Flash Update Ack OK)を返す(S902)。

【0095】

次に、メインCPU201はサブCPU301にフラッシュ消去要求(Flash Erase Req)を送信する(S903)。フラッシュ消去要求に応答して、サブCPU301はフラッシュROM302の全ブロックの消去を行い、消去が完了すると、サブCPU302はメインCPU201にフラッシュ消去応答(Flash Erase Ack OK)を返す(S904)。

【0096】

続いて、メインCPU201は、ファームウェアイメージを先頭ブロックであるID=0から順番に送信する(Flash Data Send ID=0(Top):S905)。サブCPU301は該当ブロックに対するファームウェアイメージの書き込みが完了すると、メインCPU201にブロック書き込み完了応答(Flash Data Received ID=0 OK)を返す(S906)。

【0097】

さらに、メインCPU201はブロックカウンタを+1インクリメントして、ID=1のブロックにファームウェアイメージを送信する(Flash Data Send ID=1:S907)。サブCPU301は当該ブロックに対する書き込みが完了すると、メインCPU201にブロック書き込み完了応答(Flash Data Received ID=1)を返す(S908)。

【0098】

この処理を繰り返して、メインCPU201はID=255の最終ブロックに対するファームウェアイメージを送信する(Flash Data Send ID=255:S909)。そして、サブCPU301は当該ブロックに対する書き込みが完了すると、メインCPU201にブロック書き込み完了応答(Flash Data Received ID=255 OK)を返す(S910)。

【0099】

最後に、メインCPU201はサブCPU301に対してチェックサムの取得要求(Flash Check Sum Req)を送信する(S911)。これに応答して、サブCPU301はチェックサムを求めて、メインCPU201にチェックサム値を返信する(Flash Check Sum Report:S912)。

【0100】

図10は、図6に示すメインCPU201とサブCPU301との間でファームウェア更新を行った際の信号波形を説明するためのタイムチャートである。

【0101】

前述したように、メインCPU201はRESET601をLレベルとした後(S702)、BOOTMODE602をLレベルとする(S703)。その後、メインCPU201はRESET601をHレベルとして(S704)、TxD603でファーム更新リクエストを送信する(S802)。サブCPU301からRxD604で応答を受信すると(S803)、メインCPU201はTxD603でフラッシュメモリ消去要求を送信する(S804)。

【0102】

サブCPU301からRxD604で応答を受信すると(S805)、メインCPU201は前述のようにして、TXD603でファーム更新データを送信する(S807)。サブCPU301からRxD604で応答を受信すると(S808)、全てのブロックについて更新が終了していれば、メインCPU201はチェックサムを行う(チェックサムについては図10には示されていない)。

【0103】

その後、メインCPU201はRESET601をLレベルとした後(S706)、BOOTMODE602をHレベルとする(S707)。そして、メインCPU201はRESET601をHレベルとする。このように、ファームウェアの更新を完了した後、メインCPU201は一旦サブCPU301をリセットした後、BOOTMODE602をインアクティブに設定する。そして、メインCPU201はサブCPU301のリセット解除を行う。

【0104】

前述のように、メインCPU201にはサブCPU301、311、321、331、および341が互いに独立したシリアル信号線によって接続されている。このため、メインCPU201はサブCPU301、311、321、331、および341の各々に対して同時に通信を行うことができる。

【0105】

従って、サブCPU301、311、321、331、および341のうちいずれかにおいてファームウェアが更新中であっても、他のサブCPUにおいては動作を継続することができる。ここでは、いずれのサブCPUが司る機能がファームウェアの更新中のために使用不能であるか知る必要があるため、メインCPU201はRAM203にサブCPU状態テーブルを保持する。

【0106】

図11は、図3に示すRAM203に保持されるサブCPU状態テーブルの一例を示す図である。

【0107】

図11において、サブCPU状態テーブル(モジュール状態テーブル)1101にはモジュール(Module)欄、状態(Status)欄、および残量(Remain)欄が備えられている。Module欄には、サブCPU301〜341が記載される。図示の例では、サブCPU301、311、331、321、および341に対応して、そのStatusがそれぞれファームウェア更新中(Updating)、動作中(Active)、動作中、ファームウェア更新中、および動作中となっている。そして、ファームウェア更新中である場合には、Remain欄に残り更新サイズ(残量)がバイトで示される。

【0108】

ここで、サブCPU状態テーブルが図11に示す状態である場合に、スタートキー408が押し下げられた際のメインCPU201の動作について説明する。

【0109】

図12は、図3に示すいずれかのサブCPUにおいてファームウェアの更新中である場合にスタートキー408が押し下げられた際のメインCPU201の動作を説明するためのフローチャートである。

【0110】

ここでは、サブCPU状態テーブルは図11に示す状態であるとする。また、ジョブとしてコピーが行われるものとする。そして、図5に示すように、ジョブ設定において、カラー、等倍、片面、カセット113(用紙サイズA4)、およびトレイ121が選択されたものとする。

【0111】

スタートキー408が押し下げられると、メインCPU201は当該ジョブを受け付ける(ステップS1501)。続いて、メインCPU201は受け付けたジョブのモード解析(つまり、ジョブ設定)を行って、当該解析結果に応じて使用するモジュールのサブCPUを判定する(ステップS1502)。

【0112】

例えば、メインCPU201はジョブを受付けた際、ユーザ操作部401(図4)からジョブモード情報を受信する。

【0113】

図13は、図3に示すメインCPU201がユーザ操作部401から受けるジョブモード情報の一例を示す図である。

【0114】

図13において、ジョブモード情報は、給紙段ID、カラー/モノクロ、片面/両面、排紙先ID、および後処理モードなどのモード情報を有している。図示の例では、給紙段ID=”カセット113”、カラー/モノクロ=”カラー”、片面/両面=”片面”、排紙先ID=”トレイ121”、そして、後処理モード=”ノンソート”となっている。

【0115】

メインCPU201はジョブモード情報に応じて、予め定められたサブCPU関連付けテーブル(モジュール関連付けテーブル)を参照して、受け付けたジョブがいずれのサブCPUを使用するかについて判定する。このサブCPU関連付けテーブルは、例えば、ROM202に格納される。

【0116】

図14は、図3に示すROM202に格納されたサブCPU関連付けテーブルの一例を示す図である。

【0117】

図示のサブCPU関連付けテーブルは、ジョブモード情報とサブCPUとを関連付けるためのテーブルである。サブCPU関連付けテーブルには、給紙段ID、カラー/モノクロ、片面/両面、および排紙先IDの項目が規定され、これら項目毎に選択肢が設定されている。そして、選択肢毎に使用するサブCPU、つまり、ドライバが設定されている。

【0118】

このサブCPU関連付けテーブルは、予め製品構成のラインナップに応じてROM202に記録するようにする。なお、画像形成装置立上げの際におけるモジュール接続情報に応じてメインCPU201がサブCPU関連付けテーブルを生成して、このサブCPU関連付けテーブルをRAM203に記録するようにしてもよい。

【0119】

図15は、図12に示す使用サブCPU判定処理(ステップS1502)の一例を詳細に説明するためのフローチャートである。

【0120】

使用サブCPU判定処理を開始すると、まず、メインCPU201はジョブモード情報において給紙段IDに用紙カセット113が設定されているか否かを確認する(ステップS1510)。カセット113が設定されていない場合(ステップS1510において、NO)、メインCPU201はサブCPU関連付けテーブルを参照して、増設給紙カセット125および126を制御するオプションカセットドライバのサブCPU331が使用されると判定する(ステップS1511)。

【0121】

続いて、メインCPU201はジョブモード情報においてカラー/モノクロがカラーモードに設定されているか否かを確認する(ステップS1512)。なお、カセット113が設定されていると(ステップS1510において、YES)、処理はステップS1512に進む。

【0122】

カラーモードであれば(ステップS1512において、YES)、メインCPU201はサブCPU関連付けテーブルを参照して、YMCドラムモータ304およびYMC高圧ユニット305を制御するYMCドラムモータ/高圧ドライバのサブCPU301が使用されると判定する(ステップS1513)。

【0123】

続いて、メインCPU201はサブCPU関連付けテーブルを参照して、KドラムITBモータ314、K高圧ユニット315、および二次転写高圧ユニット316を制御するKドラム/高圧・ITBモータ・二次転写高圧ドライバのサブCPU311が使用されると判定する(ステップS1514)なお、カラーモードでなくても(ステップS1512において、NO)、Kドラム/高圧・ITBモータ・二次転写高圧ドライバのサブCPU311が使用されるので、処理はステップS1514に進む。

【0124】

次に、メインCPU201は、ジョブモード情報において片面/両面が片面モードに設定されているか否かを確認する(ステップS1515)。両面モードであると(ステップS1515において、NO)、メインCPU201はサブCPU関連付けテーブルを参照して、両面反転駆動ローラ122、両面再給紙駆動ローラ124、および両面反転フラッパ123を制御する両面/反転ユニットドライバのサブCPU321を使用すると判定する(ステップS1516)。

【0125】

次に、メインCPU201は、ジョブモード情報において排紙先IDがトレイ121に設定されているか否かを確認する(ステップS1517)。排紙先IDがトレイ121でない場合(ステップS1517において、NO)、メインCPU201は用紙がバッファパスユニット150を介してフィニッシャ上トレイ161又はフィニッシャ下トレイ162に排出されると判定する。

【0126】

これによって、メインCPU201はサブCPU関連付けテーブルを参照して、バッファパスユニット150を制御するバッファパス/フィニッシャドライバのサブCPU341を使用すると判定する(ステップS1518)。そして、メインCPU201は使用サブCPU判定処理を終了する。一方、排紙先IDがトレイ121であると(ステップS1517において、YES)、メインCPU201は使用サブCPU判定処理を終了する。

【0127】

なお、画像形成装置に備えられたモジュールが多いほど、サブCPU関連付けテーブルは細分化され、図15で説明した使用サブCPU判定処理におけるステップ数は増加する。

【0128】

再び、図12を参照して、上述のようにして、使用サブCPU判定処理が終了すると、続いて、メインCPU201はサブCPU状態テーブルを参照して、使用すると判定されたサブCPU(使用サブCPU)についてファームウェアの更新中(ダウンロード中)であるか否かを判定する(ステップS1503)。ファームウェアのダウンロード中でない場合(ステップS1503において、NO)、メインCPU201は使用すると判定した全てのサブCPUについて更新中であるかのサーチが完了したかを確認する(ステップS1504)。

【0129】

使用すると判定した全てのサブCPUについて更新中であるかのサーチが完了していないと(ステップS1504において、NO)、メインCPU201は他に使用すると判定したサブCPUに移行して(ステップS1505)、ステップS1503の処理を行う。

【0130】

一方、使用すると判定した全てのサブCPUについて更新中であるかのサーチが完了すると(ステップS1504において、YES)、メインCPU201は受け付けたジョブを実行して(ステップS1506)、ジョブ処理を終了する。

【0131】

使用すると判定したサブCPUがファームウェアのダウンロード中であると(ステップS1503において、YES)、メインCPU201は受け付けたジョブを予約ジョブとして(ステップS1507)、ジョブ処理を終了する。

【0132】

このように、使用すると判定されたサブCPUのいずれか1つがファームウェアをダウンロード中であれば、メインCPU201は受け付けたジョブを実行を待機する。そして、メインCPU201は受け付けたジョブに係るジョブモード情報をRAM203に格納する。

【0133】

図16は、図5に示すジョブモードの設定(ジョブ設定)が行われた際の使用サブCPU判定処理における判定結果を示す図である。

【0134】

図5に示すジョブ設定を行うと、図16にグレーアウトして示すように、Kドラム/高圧・ITBモータ・二次転写高圧ドライバ、YMCドラムモータ/高圧ドライバ、およびバッファパス/フィニッシャドライバに係るサブCPUが使用サブCPUとされる。そして、図11に示す例では、サブCPU301および321がファームウェアの更新中であるので、メインCPU201は受け付けたジョブを待機する。つまり、予約ジョブとする。

【0135】

図17は、図12で説明した予約ジョブの実行を説明するためのフローチャートである。

【0136】

前述のように、予約ジョブとされると、当該予約ジョブに係るジョブモード情報はRAM203に格納される。予約ジョブの処理が開始されると、メインCPU201はサブCPUにおけるファームウェアの更新終了を検知したか否かを確認する(ステップS1530)。ここでは、図8に示すステップS812およびS813において、サブCPUからチェックサム値の応答を受けて、チェックサム値が一致すると、メインCPU201は当該サブCPUにおけるファームウェアの更新が終了したとする。

【0137】

ファームウェアの更新終了を検知しないと(ステップS1530において、NO)、メインCPU201は待機する。一方、ファームウェアの更新終了を検知すると(ステップS1530において、YES)、メインCPU201は予約ジョブがあるか否かを確認する(ステップS1531)。ここでは、メインCPU201はRAM203にジョブモード情報が格納されているか否かを確認することになる。

【0138】

予約ジョブが存在しないと(ステップS1531において、NO)、メインCPU201は予約ジョブ処理を終了して、図12に示すステップS1501の処理に戻る。予約ジョブが存在すると(ステップS1531において、YES)、メインCPU201はジョブモード情報に基づいてジョブの再投入を行う(ステップ1532)。そして、メインCPU201は予約ジョブ処理を終了して、図12に示すステップ1501の処理に戻る。

【0139】

図5に示すジョブ設定では、YMCドラムモータ/高圧ドライバのサブCPU301がファームウェアの更新を終了すると、メインCPU201は予約ジョブを再投入することになる。

【0140】

続いて、ジョブ投入の投入後、使用サブCPUがファームウェアの更新中であった際のジョブのキャンセルについて説明する。

【0141】

図18は、図3に示すいずれかのサブCPUにおいてファームウェアの更新中である場合にスタートキーが押し下げられた際のメインCPUの動作の他の例を説明するためのフローチャートである。

【0142】

なお、図3に示す処理と同一の処理については同一の参照符号を付して、説明を省略する。

【0143】

ステップS1503において、使用すると判定したサブCPUがファームウェアのダウンロード中であると、メインCPU210は受け付けたジョブをキャンセルするか否かを判定する(ステップS1508)。ここでは、まず、メインCPU201はダウンロード中である旨の状態通知を行うとともに、ジョブを継続するか否かを決定する画面をユーザ操作部401に表示する。

【0144】

図19は、図18に示すジョブキャンセル判定処理の際にユーザ操作部401に表示されるポップアップウィンドウの一例を示す図である。

【0145】

使用すると判定したサブCPUがファームウェアのダウンロード中であると、メインCPU210は、図19に示すように、操作パネル画面503上にポップアップウィンドウ509に表示する。このポップアップウィンドウ509には、ファームウェアが更新中でありジョブに待機時間が生じる旨の文言とキャンセルするか否かを問う文言が表示される。

【0146】

ユーザが”Yes”ボタン510を押し下げると、メインCPU201は受け付けたジョブをキャンセルすると判定する。一方、ユーザ”No”ボタンを押し下げると、メインCPU201は受け付けたジョブをキャンセルしないと判定する。

【0147】

受け付けたジョブをキャンセルしないと判定すると(ステップS1508において、NO)、メインCPU201はステップS1507の処理に進んで、当該受け付けたジョブを予約ジョブとする。受け付けたジョブをキャンセルすると判定すると(ステップS1508において、YES)、メインCPU201は当該受け付けたジョブをキャンセルする(ステップS1509)。そして、メインCPU201はジョブ処理を終了する。

【0148】

以上のように、本発明の実施の形態によれば、ファームウェアのダウンロード中にジョブ処理要求を受信した際に、当該ジョブ処理要求に係るジョブを予約ジョブとして、当該予約ジョブで使用するモジュールにおいてファームウェアのダウンロードが終了すると、当該予約ジョブを実行するようにしたので、ファームウェアのダウンロードに起因してジョブ処理要求がキャンセルされることがない。従って、ユーザは再度ジョブを投入するという手間が省け、ユーザの利便性が向上する。

【0149】

上述の説明から明らかなように、図3に示す例では、メインCPU201およびサブCPU301〜341が更新手段として機能する。また、メインCPU201は判定手段および制御手段として機能する。なお、フラッシュROM302〜342の各々はモジュール記憶手段として用いられる。また、メインCPU201およびユーザ操作部401は報知手段として機能する。

【0150】

上述の実施の形態では、情報処理装置の一例として、画像形成装置を例に挙げて説明したが、画像形成装置に限らず他の情報処理装置、例えば、画像処理装置においても複数モジュールが互いに独立して動作する構成であれば同様にして本発明を適用することができる。また、上述の実施の形態では、ファームウェアを更新する場合については説明したが、ファームウェアに限らずソフトウェアの更新を行う場合であれば同様にして適用することができる。

【0151】

以上、本発明について実施の形態に基づいて説明したが、本発明は、これらの実施の形態に限定されるものではなく、この発明の要旨を逸脱しない範囲の様々な形態も本発明に含まれる。

【0152】

例えば、上記の実施の形態の機能を制御方法として、この制御方法を情報処理装置に実行させるようにすればよい。また、上述の実施の形態の機能を有するプログラムを制御プログラムとして、この制御プログラムを情報処理装置が備えるコンピュータに実行させるようにしてもよい。なお、制御プログラムは、例えば、コンピュータに読み取り可能な記録媒体に記録される。

【0153】

この際、制御方法および制御プログラムの各々は、少なくとも更新ステップ、判定ステップ、および制御ステップを有することになる。

【0154】

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記録媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【符号の説明】

【0155】

201 メインCPU

209 YMCドラムモータ/高圧ドライバ

210 Kドラム/高圧・ITBモータ・二次転写高圧ドライバ

211 両面/反転ユニットドライバ

212 オプションカセットドライバ

213バッファパス/フィニッシャドライバ

301,311,321,331,341 サブCPU

302,312,322,332,342 フラッシュROM

303,313,323,333,343 SRAM

【技術分野】

【0001】

本発明は、情報処理装置、その制御方法、および制御プログラムに関し、特に、電子写真方式又は静電記録方式などを用いた画像形成装置に関する。

【背景技術】

【0002】

一般に、情報処理装置の一つとして所謂画像形成装置が知られている。そして、クライアントPCなどの外部装置と複合機などの画像形成装置とをLANなどのネットワークで接続された印刷システムが知られている。ここでは、画像形成装置は外部装置からプリントジョブなどの画像処理ジョブを受けて当該画像処理ジョブを実行する。

【0003】

画像形成装置で実行可能な処理は、当該画像形成装置に備えられたハードウェアリソースの範囲内であれば、CPUが実行するプログラム(ファームウェア)を更新すれば、容易に変更および追加することができる。

【0004】

ところで、ファームウェアの削除・更新を高速にするとともに、タイマジョブとして実行待ちとなっている予約画像処理ジョブを遂行するソフトウェアパーツを、通常のジョブに支障をきさない範囲で適宜削除・更新するため、予約画像処理ジョブに更新対象となるソフトウェアパーツを用いる処理が含まれているか否かを判定するようにしたものがある。そして、ここでは、予約画像処理ジョブに更新対象となるソフトウェアパーツを用いる処理が含まれていないと判定した場合には、当該更新対象のソフトウェアパーツの更新処理を行う(特許文献1参照)。

【0005】

そして、特許文献1においては、予約ジョブ中に当該ソフトウェアパーツが含まれているが、ネットワーク上の他の画像形成装置が備えるソフトウェアパーツで代替することができると判断した場合には、当該他の画像形成装置を用いるように再スケジューリングを行う。一方、代替する画像形成装置が存在しないと判断した場合には、当該更新要求を保留にしている。

【0006】

さらに、ファームウェアのバージョンアップを行う際、新しいファームウェアをダウンロードして、このファームウェアをRAM領域に一時記憶するようにしたものがある(特許文献2参照)。ここでは、電源オンの際にプログラムが動作を開始するプログラムリセットベクタに分岐して、RAM領域にロードされたファームウェアを読み出して、このファームウェアを従来のファームウェアが存在していたPROM領域に書き込んでいる。そして、特許文献2では、実行中および実行待機中の画像処理ジョブを検知して、これらジョブが存在すると、前述のファームウェア更新動作を保留するようにしている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−108957号公報

【特許文献2】特開2001−273143号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところが、上述の特許文献1では、更新すべきソフトウェアパーツがある場合において、その更新と予約画像処理ジョブとをスケジューリングしているだけであって、例えば、ソフトウェアパーツの更新中にプリント処理要求コマンドを受信した場合には処理を行うことが困難となってしまう。

【0009】

つまり、特許文献1に記載の画像形成装置では、ソフトウェアパーツを更新している際に、当該ソフトウェアパーツを用いるプリント処理要求などのジョブを受信しても、当該ジョブを実行することができず、このジョブはキャンセルせざるを得ない。よって、ユーザは再度ジョブを投入しなければならず、ユーザにとっては使い勝手が極めて悪い。

【0010】

同様に、特許文献2においても、画像処理ジョブの実行中にファームウェアをダウンロードすべきタイミングが到来した際の処理を行っているのみで、ファームウェアのダウンロード中にプリント処理要求コマンドを受けた際には処理を行うことが困難となってしまう。

【0011】

従って、特許文献2に記載の画像形成装置においても、ファームウェアのダウンロード中にプリント処理要求などのジョブを受信しても、当該ジョブを実行することができず、このジョブはキャンセルせざるを得ない。よって、ユーザは再度ジョブを投入しなければならず、ユーザにとっては使い勝手が極めて悪い。

【0012】

よって、本発明の目的は、ソフトウェアパーツ(プログラム)を更新している際に、ジョブ処理要求を受信した場合においても、当該ジョブがキャンセルされることがなく、ユーザにとって利便性の向上した情報処理装置、その制御方法、および制御プログラムを提供することにある。

【課題を解決するための手段】

【0013】

上記の目的を達成するため、本発明による情報処理装置は、互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置であって、前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新手段と、前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定手段と、前記判定手段によって前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御手段とを有することを特徴とする。

【0014】

本発明による制御方法は、互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置の制御方法であって、前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新ステップと、前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定ステップと、前記判定ステップで前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御ステップとを有することを特徴とする。

【0015】

本発明による制御プログラムは、互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置で用いられる制御プログラムであって、前記情報処理装置に備えられたコンピュータに、前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新ステップと、前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定ステップと、前記判定ステップで前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御ステップとを実行させることを特徴とする。

【発明の効果】

【0016】

本発明よれば、ソフトウェアが更新中であるモジュールを用いるジョブを受けても、当該ジョブをキャンセルすることなく待機させるようにしたので、ユーザにとって利便性が向上する。

【図面の簡単な説明】

【0017】

【図1】本発明の実施の形態による情報処理装置の一つである画像形成装置の一例についてその構成を概略的に示す断面図である。

【図2】図1に示す画像形成装置の制御系(制御部)の一例を示すブロック図である。

【図3】図2に示すYMCドラムモータ/高圧ドライバ、Kドラム/高圧・ITBモータ・二次転写高圧ドライバ、両面/反転ユニットドライバ、オプションカセットドライバ、およびバッファパス/フィニッシャドライバについて説明するためのブロック図である。

【図4】図1に示す画像形成装置に備えられたユーザ操作部401の一例を示す図である。

【図5】図4に示すユーザ操作部401に表示された表示画面の一例を示す図である。

【図6】図3に示すメインCPUとサブCPUとの接続形態の一例を示すブロック図である。

【図7】図6に示すメインCPUとサブCPUとにおいて行われるモード切り替え処理を説明するためのフローチャートである。

【図8】プログラムモードの際に図6に示すメインCPUとサブCPUとの間で行われる通信について説明するためのフローチャートである。

【図9】プログラムモードの際に図6に示すメインCPUとサブCPUとの間で行われる通信について説明するためのシーケンス図である。

【図10】図6に示すメインCPUとサブCPUとの間でファームウェア更新を行った際の信号波形を説明するためのタイムチャートである。

【図11】図3に示すRAMに保持されるサブCPU状態テーブルの一例を示す図である。

【図12】図3に示すいずれかのサブCPUにおいてファームウェアの更新中である場合にスタートキーが押し下げられた際のメインCPUの動作の一例を説明するためのフローチャートである。

【図13】図3に示すメインCPUがユーザ操作部401から受けるジョブモード情報の一例を示す図である。

【図14】図3に示すROMに格納されたサブCPU関連付けテーブルの一例を示す図である。

【図15】図12に示す使用サブCPU判定処理の一例を詳細に説明するためのフローチャートである。

【図16】図5に示すジョブモードの設定(ジョブ設定)が行われた際の使用サブCPU判定処理における判定結果を示す図である。

【図17】図12で説明した予約ジョブの実行を説明するためのフローチャートである。

【図18】図3に示すいずれかのサブCPUにおいてファームウェアの更新中である場合にスタートキーが押し下げられた際のメインCPUの動作の他の例を説明するためのフローチャートである。

【図19】図18に示すジョブキャンセル判定処理の際にユーザ操作部401に表示されるポップアップウィンドウの一例を示す図である。

【発明を実施するための形態】

【0018】

以下、本発明の実施の形態による情報処理装置の一例について図面を参照して説明する。

【0019】

図1は、本発明の実施の形態による情報処理装置の一つである画像形成装置の一例についてその構成を概略的に示す断面図である。

【0020】

図1において、図示の画像形成装置は、所謂カラー複合機であり、画像形成装置本体100、画像読取装置140、および後処理装置160を備えている。

【0021】

いま、図示の画像形成装置を用いてコピーを行おうとする際には、読み取りガラス142上に原稿が配置される。そして、スキャナーユニット143によって原稿上の画像が光学的に読み取られて、光学像として光電変換部(例えば、CCD)144に与えられる。光電変換部114は光学像を電気信号(画像信号)に変換する。そして、この電気信号は制御装置(図示せず)に与えられて、ここで、所定の処理が施されて、画像データとされる。

【0022】

画像形成装置本体100は、イエロー(Y)プロセスユニット101y、マゼンダ(M)プロセスユニット101m、シアン(C)プロセスユニット101c、およびブラック(K)プロセスユニット101kを備えている。そして、これらプロセスユニットの各々は感光ドラム、現像器、および帯電ローラなどを有している。

【0023】

ここで、Kプロセスユニット101kに注目して、Kプロセスユニット101kには感光ドラム102kが収納されている。この感光ドラム102kはドラムモータ(図示せず)によって回転駆動される。感光ドラム102kの表面は帯電ローラ103kによって一様に帯電される。レーザスキャナユニット104kは、画像データに応じて変調されたレーザ光を、ポリゴンミラー回転体(図示せず)によって感光ドラム102kをその長手方向に走査する。

【0024】

レーザ光の走査によって、感光ドラム102kの表面には画像データに応じた静電潜像が形成される。現像器105kには、例えば、Kトナーおよびキャリアを有する二成分現像剤が収納されている。この現像器105kには、トナーが充填されたトナーボトル106kが連結され、トナーボトル106kからKトナーが現像器105kに供給される。現像器105kは感光ドラム102k上の静電潜像をKトナーで現像してKトナー像とする。

【0025】

Kプロセスユニット101kには、補助帯電ブラシ109kが備えられており、中間転写ベルト(中間転写体)108にKトナー像を転写した際に感光ドラム102kに残留する転写残トナーを一様に帯電させる。そして、この転写残トナーは感光ドラム102kから除去されて回収される。

【0026】

なお、Yプロセスユニット101y、Mプロセスユニット101m、Cプロセスユニット101cはKプロセスユニット101kと同様の構成を有している。

【0027】

Yプロセスユニット101y、Mプロセスユニット101m、Cプロセスユニット101c、およびKプロセスユニット101kに中間転写ベルト108を介してそれぞれ一次転写ローラ107y、107m、107c、および107kが対向している。そして、一次転写107y、107m、107c、および107kによってYプロセスユニット101y、Mプロセスユニット101m、Cプロセスユニット101c、およびKプロセスユニット101kから順次Yトナー像、Mトナー像、Cトナー像、およびKトナー像が中間転写ベルト108に転写されて重ね合わされる。これによって、中間転写ベルト108にはカラートナー像が形成される。

【0028】

中間転写ベルト108上のカラートナー像は、中間転写ベルト108の回転によって二次転写位置に搬送される。

【0029】

一方、用紙カセット(給紙カセット又は単にカセットともいう)113、125、および126から選択的に給紙ローラ114、127、および128によって用紙が用紙搬送路に搬送される。そして、用紙はレジストローラ115によって斜行を補正された後、二次転写位置に送られる。二次転写位置において、中間転写ベルト108上のカラートナー像は二次転写ローラ110によって用紙に転写される。その後、用紙は定着器に送られて、ここで、定着ローラ117および加圧ローラ118によって用紙上のカラートナー像が熱定着される。

【0030】

なお、トナー濃度補正を行うため、Kプロセスユニット101kの出口近傍にはパターン濃度検知センサ112が配置されている。トナー濃度補正を行う際には、予め定めらたれパターンを有する濃度補正用パターンが中間転写ベルト108上に形成される。そして、濃度検知センサ112によって濃度補正用パターンを検知してその検知結果に応じて濃度補正が行われる。

【0031】

また、中間転写ベルト108に残留した転写残トナーは中間転写体クリーナ111によって回収される。

【0032】

片面印刷の際には、定着器を出た用紙は、排紙フラッパ119によって排紙ローラ120を備える排紙経路に送られる。そして、後処理を行う際には、用紙は後処理フラッパ152によって、バッファパス搬送ローラ151を備えるバッファパスユニット150に搬送されて、ここから後処理装置(フィニッシャ)160に送られる。後処理装置160は用紙又は用紙束に対して所定の後処理を行った後、フィニッシャトレイ161又は162に用紙又は用紙束を排紙する。

【0033】

後処理を行わない場合には、用紙は後処理フラッパ152によって、排紙トレイ121に排紙される(洞内排紙)。

【0034】

両面印刷を行う場合には、定着器を出た用紙は排紙フラッパ119によって両面反転フラッパ123を介して両面反転駆動ローラ122に送られる。続いて、両面判定駆動ローラ122によって用紙は逆方向に搬送されて、反転フラッパ123によって、両面再給紙駆動ローラ124を備える両面印刷搬送路に送られる。そして、用紙は再度レジストローラ115に送られて、前述のようにして、裏面側に印刷が行われることになる。

【0035】

なお、モノクロ印刷の際には、Kプロセスユニット101kのみが用いられ、Kプロセスユニット101kから中間転写ベルト108にKトナー像が転写される。

【0036】

図2は、図1に示す画像形成装置の制御系(制御部)の一例を示すブロック図である。

【0037】

次に、本画像形成装置の制御回路構成について、図2のブロック図を用いて説明する。

【0038】

図示の制御部はメインCPU201を備えており、このメインCPU201は画像形成装置全体の制御を司る。ROM202にはメインCPU201上で動作する制御プログラムなどが格納され、RAM203はメインCPU201が一時的にデータなどを記憶するために用いられる。バックアップRAM204は画像形成装置が動作する際に設定された設定情報などが記憶される。バックアップRAM204にはバックアップバッテリ(図示せず)によって電源が供給され、画像形成装置のメイン電源を断としても、バックアップRAM204に記憶された設定情報は保持される。

【0039】

モータドライバ205は、図1に示す給紙ローラ114およびレジストローラ115などの回転制御を行う。メインCPU201にはシリアルインターフェイス(SCI)206が備えられており、SCI206は8CH(8チャンネル)の信号線によってメインCPU201に接続された各種モジュールと通信を行う。各チャンネルは2本の信号線を備え、これによって全二重通信が行われる。そして、メインCPU201は後述するモジュールを制御する。

【0040】

ネットワークインターフェイス(I/F)207は画像データを供給するプリンタコントローラ(システムコントローラ:図示せず)と接続される。レーザドライバ208は、図1に示すレーザスキャナユニット104y、104m、104c、および104kを制御する。YMCドラムモータ/高圧ドライバ209はYプロセスユニット101y、Mプロセスユニット101m、およびCプロセスユニット101cの各々に備えられた感光ドラム駆動モータ(図示せず)を駆動制御するとともに、帯電、現像、および一次転写に係る電圧制御を行う。

【0041】

Kドラム/高圧・ITBモータ・二次転写高圧ドライバ210はKプロセスユニット101kに備えられた感光ドラム駆動モータ(図示せず)を駆動制御するとともに、帯電、現像、および一次転写に係る電圧制御を行う。さらに、Kドラム/高圧・ITBモータ・二次転写高圧ドライバ210は中間転写体108の駆動モータを駆動制御するとともに、二次転写ローラ110に係る二次転写電圧制御を行う。

【0042】

両面・反転ユニットドライバ211は。両面反転駆動ローラ122および両面再給紙駆動ローラ124を駆動制御するとともに、両面反転フラッパ123の回動制御を行う。オプションカセットドライバ212は増設給紙カセットである用紙カセット125および126において給紙ローラ127および128を駆動制御する。

【0043】

バッファパス/フィニッシャドライバ213はバッファパスユニット150およびフィニッシャ160を制御する。つまり、バッファパス/フィニッシャドライバ213はバッファパス搬送ローラ151を駆動制御するとともに、フィニッシャ上トレイ161およびフィニッシャ下トレイ162の昇降制御を行う。

【0044】

図3は、図2に示すYMCドラムモータ/高圧ドライバ209、Kドラム/高圧・ITBモータ・二次転写高圧ドライバ210、両面/反転ユニットドライバ211、オプションカセットドライバ212、およびバッファパス/フィニッシャドライバ213について説明するためのブロック図である。

【0045】

図2で説明したCPU201、ROM202、RAM203、およびバックアップRAM204はメインエンジンコントローラボード201aに搭載されている。YMCドラムモータ/高圧ドライバ209は、サブCPU301、フラッシュROM302、およびSRAM303を備えている。フラッシュROM302にはサブCPU301上で動作する制御プログラムが格納されている。SRAM303は、例えば、サブCPU301の作業領域として用いられる。そして、サブCPU301はCPU201の制御下でYMCドラムモータ304およびYMC高圧ユニット305を制御する。

【0046】

Kドラム/高圧・ITBモータ・二次転写高圧ドライバ210は、サブCPU311、フラッシュROM312、およびSRAM313を備えている。フラッシュROM312にはサブCPU311上で動作する制御プログラムが格納されている。SRAM313は、サブCPU311の作業領域として用いられる。そして、サブCPU311は、CPU201の制御下でKドラムITBモータ314、K高圧ユニット315、および二次転写高圧ユニット316を制御する。

【0047】

両面/反転ユニットドライバ211は、サブCPU321、フラッシュROM322、およびSRAM323を備えている。フラッシュROM322にはサブCPU321上で動作する制御プログラムが格納されている。SRAM323は、サブCPU321の作業領域として用いられる。そして、サブCPU321はCPU201の制御下で両面反転モータ324および両面再給紙モータ325を制御する。

【0048】

オプションカセットドライバ212は、サブCPU331、フラッシュROM332、およびSRAM333を備えている。フラッシュROM332にはサブCPU331上で動作する制御プログラムが格納されている。SRAM333は、サブCPU331の作業領域として用いられる。そして、サブCPU331は、CPU201の制御下で増設カセット給紙モータ334および335を制御する。

【0049】

バッファパス/フィニッシャドライバ213は、サブCPU341、フラッシュROM342、およびSRAM343を備えている。フラッシュROM342にはサブCPU341上で動作する制御プログラムが格納されている。SRAM343は、サブCPU341の作業領域として用いられる。そして、サブCPU341は、CPU201の制御下でバッファパスモータ344、フィニッシャ上トレイ161およびフィニッシャ下トレイ162を駆動する昇降モータ345、およびフィニッシャ160が備えるステイプル機構346を制御する。

【0050】

図4は、図1に示す画像形成装置に備えられたユーザ操作部401の一例を示す図である。

【0051】

ユーザ操作部401は電源スイッチ404を備えており、電源スイッチ404の操作によって画像形成装置の主電源がオン又はオフされる。節電ボタン403の操作によって画像形成装置は所定の節電モードに移行する。電源LED404は主電源がオンの場合に、例えば、緑色に点灯する。また、電源LED404はユーザの操作で選択された機能が動作中であると緑色に点滅する。さらに、電源LED404は画像形成装置においてエラーなどが発生した際には赤色に点灯して、ユーザに異常を報知する。

【0052】

液晶表示部(LCD)501は、例えば、タッチパネル式のTFTドットマトリクス型の液晶パネルによって構成される。そして、LCD501において画像形成装置における各モードの操作・表示が行われ、各モードの切り替えが行われる。

【0053】

テンキー406は、例えば、コピー枚数およびFAX送信先などの数字を入力する際に用いられる。リセットキー407は入力した数値をクリアする際に用いられ、さらに現在選択中のモードにおいて初期状態に戻る際に用いられる。スタートキー408は、液晶表示部501又はテンキー406による入力操作に応じた動作を開始するためのキーである。

【0054】

ストップキー409は、スタートキー408によって開始された動作を、動作途中でキャンセルするためのキーである。ヘルプキー410はユーザの操作によって表示画面に対する説明文章を表示するためのキーである。ユーザモードボタン411はユーザが予めユーザ設定を行うためのキーである。

【0055】

図5は、図4に示すユーザ操作部401に表示された表示画面の一例を示す図である。

【0056】

図5に示す表示画面はLCD501に表示される。ここでは、ユーザによってコピーモードが詮索された際の表示画面(つまり、コピーモード画面)が示されている。コピーモード画面は、ファンクション選択ボタン画面501、操作パネル画面502、およびステータス表示画面511を有する。

【0057】

ファンクション選択ボタン画面502において、ユーザが所望のファンクションキーをタッチすると、CPU201は当該タッチされたキーに応じた動作(つまり、機能)に切り替える。機能が切り替わると、CPU201は当該切り替わった機能を表示する表示画面をLCD501に表示する。図示の例では、コピーモードであるから、”COPY”が点灯しているが、ユーザが、例えば、”FAX”をタッチすると、FAX動作モード画面がLCD501に表示される。この際には、ファンクション選択ボタン画面502において、”FAX”が点灯する。

【0058】

操作パネル画面503には、コピーが実行可能であるか否かを示す情報が表示され、さらに、用紙サイズの設定などのモード設定およびコピー枚数などが表示される。コピー枚数はテンキー406からの入力によって設定され、操作パネル画面503に表示される。

【0059】

さらに、操作パネル画面503には、色モード設定504、倍率設定505、片面・両面設定506、用紙選択設定507、および排紙トレイ設定508が表示される。そして、ユーザはタッチ操作によって色モード、倍率、片面・両面設定、用紙選択、および排紙トレイの設定を行う。

【0060】

つまり、色モード設定504では白黒モード又はカラーモードのいずれかを選択することができる。倍率設定505では、縮小、等倍、又は拡大の設定を行うことができ、選択された倍率は、前述のように、操作パネル画面503に表示される。

【0061】

片面・両面設定506では、片面コピー又は両面コピーのいずれかを選択することができる。用紙選択設定507ではいずれの給紙カセットに収納された用紙を用いるかを選択することができる。排紙トレイ設定508では、プリント後の用紙をいずれのトレイに排紙するかを設定する。

【0062】

ステータス表示画面511には、画像形成装置の状態が変化した際に、その状態変化の旨がメッセージとして表示される。

【0063】

図6は、図3に示すメインCPU201とサブCPU301との接続形態の一例を示すブロック図である。図6においては、メインCPU201とサブCPU301との接続形態について説明するが、メインCPU301とサブCPU311〜341との接続形態についてもサブCPU301と同様である。

【0064】

メインCPU201はリセット信号線(RESET)601、ブートモード信号線(BOOTMODE)602、送信信号線(TxD)信号線603、および受信信号線(RxD)信号線604によってサブCPU301に接続されている。

【0065】

RESET601は、メインCPU201が出力側となって、サブCPU301が入力側となって、メインCPU201によって所定のタイミングでサブCPU301をリセットする際に用いられる。そして、RESET601は動作時にH(ハイ)レベルとなり、リセット時にはL(ロー)レベルとなる。

【0066】

BOOTMODE602は、メインCPU201が出力側、サブCPU301が入力側となって、サブCPU301がリセットして再起動した後の動作モードを決定するために用いられる。BOOTMODE602は通常時にHレベルとなり、ファームウェア更新モード時にはLレベルとなる。

【0067】

TxD603は、メインCPU201からサブCPU301にシリアル通信信号を送信するためのものである。TxD603においては、TTLレベルの調歩同期で8ビットずつ情報が送信される。RxD604は、サブCPU301からメインCPU201にシリアル通信信号を送信するためのものである。RxD604においても同様にTTLレベルの調歩同期で8ビットずつ情報が送信される。

【0068】

続いて、図3に示すサブCPU301〜341におけるファームウェアの更新処理について説明する。ここでは、サブCPU301におけるファームウェアの更新処理を例に挙げて説明するが、サブCPU311〜341におけるファームウェアの更新処理についても同様である。

【0069】

サブCPU301の制御プログラムが格納されたフラッシュROM302は、例えば、32kバイトの容量を備えている。そして、このフラッシュROM302は所定の手順に応じてアクセスを行って書き込み処理を行うことができる。サブCPU301に係る制御プログラムの更新中においては、更新対象であるフラッシュROM302にプログラムコード(つまり、制御プログラム)が存在すると、書き換えプログラムが動作することができない。

【0070】

よって、まず、サブCPU301のワーク領域であるSRAM303に書き換えプログラムを保存して、書き換えプログラムをサブCPU301で動作させるためのプログラムモードに移行する(つまり、モード切り替え処理を行う必要がある)。

【0071】

図7は、図6に示すメインCPU201とサブCPU301とにおいて行われるモード切り替え処理を説明するためのフローチャートである。

【0072】

ファームウェア更新処理を開始すると、メインCPU201はファームウェア更新対象であるサブCPU301についてRESET601をオン(Lレベル)して、サブCPU301をリセットする(ステップS702)。そして、メインCPU201はBOOTMODE602をアクティブ(Lレベル)に設定する。つまり、メインCPU201はBOOTMODE602をプログラムモードに設定する(ステップS703)。

【0073】

サブCPU301は、BOOTMODE602がアクティブの状態でリセットを解除が行われると(ステップS704)、フラッシュROM302のプログラムモードで起動される。プログラムモードにおいては、サブCPU301はTxD603からの通信待ちとなってフラッシュROM302の書き換えプログラムをワークメモリであるSRAM303に展開する。

【0074】

以後、メインCPU201とサブCPU301との通信およびフラッシュROM302の書き換え制御は、SRAM303上に展開されたプログラムに応じて行われる。

【0075】

後述するようにして、サブCPU301において、フラッシュROM302の書き換え(書き込み)が行われた後(ステップS705)、メインCPU201はサブCPU301を再度リセットする(ステップS706)。そして、メインCPU201はBOOTMODE602をインアクティブに設定する。つまり、メインCPU201はBOOTMODE602を通常モードに設定する(ステップS707)。その後、メインCPU201はサブCPU302のリセットを解除して(ステップS708)、ファームウェア更新処理を終了する。

【0076】

図8は、プログラムモードの際に図6に示すメインCPU201とサブCPU301との間で行われる通信について説明するためのフローチャートである。

【0077】

フラッシュROM302の書き換えを行う際、まず、メインCPU201は書き換えを行うためのネゴシエーション情報(ファーム更新リクエスト)をサブCPU301に送信する(ステップS802)。続いて、メインCPU201はファーム更新リクエストに対する応答(書き換え可能応答)をサブCPU301から受信したか否かを判定する(ステップ803)。

【0078】

書き換え可能応答を受信しないと(ステップS803において、NO)、メインCPU201は待機する。一方、書き換え可能応答を受信すると(ステップS803において、YES)、メインCPU201はフラッシュROM302を直接書き換えることができないため、書き換えに先立ってサブCPU301に対してフラッシュメモリ消去要求を発行する(ステップ804)。

【0079】

続いて、メインCPU201は、フラッシュROM302の消去を行ったことを示す応答(フラッシュメモリ消去応答)をサブCPU301から受信したか否かを判定する(ステップS805)。フラッシュメモリ消去応答を受信しないと(ステップS805において、NO)、メインCPU201は待機する。

【0080】

フラッシュメモリ消去要求を受けると、サブCPU301はフラッシュROM302の全ブロックの消去を行う。そして、全ブロックの消去が完了すると、サブCPU302はフラッシュメモリ消去応答をメインCPU201に返信する(ステップ804)。

【0081】

フラッシュメモリ消去応答を受信すると(ステップS805において、YES)、メインCPU201は内蔵するブロックカウンタにn=0を設定する(ステップS806)。ここで、フラッシュROM302のブロック数は256であるとする。つまり、フラッシュROM302には第0〜第255のブロックがあるものとする。

【0082】

続いて、メインCPU201はフラッシュROM301の第0のブロックに書き込むファームウェアイメージを128バイトずつに分割してパケットを生成する。そして、メインCPU201は先頭のパケット(ファームウェア更新データ)をサブCPU301に送信する(ステップ807)。パケットには先頭マーカー又は終端マーカーがヘッダ部に設けられており、先頭のパケットは先頭マーカーで識別される。また、最後のパケットは終端マーカーで識別が可能である。

【0083】

パケットを送信した後、メインCPU201は、サブCPU301からブロックへの書込みが完了したことを示すブロック書込み応答を受信したか否かを判定する(ステップS808)。ブロック書込み応答を受信しないと(ステップS808において、NO)、メインCPU201は待機する。

【0084】

サブCPU302はパケットを受信すると、ファーム更新データをフラッシュROM302に書き込む。1つのブロックの書き込みが完了すると、サブCPU301はブロック書き込み完了応答をメインCPU201に返信する。ブロック書き込み応答を受信すると(ステップS808において、YES)、メインCPU201はブロックカウンタをインクリメント(+1)する(ステップS809)。そして、メインCPU201はブロックカウンタが256未満であるか否かを判定する(ステップS810)。

【0085】

ブロックカウンタが256未満であると(ステップS810において、YES)、メインCPU201はステップS807の処理に戻って、次のブロックに対するファーム更新データを送信する。

【0086】

このようにして、フラッシュROM302に対する書き込みはブロックごとに繰り返されて、サブCPU301は合計256個のパケットを受信して、フラッシュROM302の全てのブロックについてファームウェアの更新が終了する。

【0087】

ブロックカウンタが256となると(ステップS810において、NO)、メインCPU201はサブCPU301にチェックサムの取得要求を送信する(ステップ811)。このチェックサムは、例えば、フラッシュROM302の全領域について奇数アドレスおよび偶数アドレスの値を総計した結果の下位16ビットを用いる。

【0088】

メインCPU201はサブCPU301からチェックサム値を受信したか否かを判定する(ステップS812)。チェックサム値を受信しないと(ステップS812において、NO)、メインCPU201は待機する。

【0089】

サブCPU301はチェックサム取得要求に応答して、メインCPU201に対して奇数アドレスおよび偶数アドレスのチェックサム値を返信する。メインCPU201は、送信したファームウェアイメージのチェックサム値を保持チェックサム値として保持している。チェックサム値を受信チェックサム値として受信すると(ステップ812において、YES)、サブCPUから受信チェックサム値と保持チェックサム値とが一致するか否かを判定する(ステップ813)。

【0090】

受信チェックサム値と保持チェックサム値とが一致しないと(ステップS813において、NO)、メインCPU201はフラッシュROM302に書き込まれたファームウェアが送信したファームウェアイメージと一致していないとして、ステップS806の処理に戻る。そして、メインCPU201はリトライ制御によって先頭パケットから再度送信する。

【0091】

受信チェックサム値と保持チェックサム値とが一致すると(ステップS813において、YES)、メインCPU201はフラッシュROM302の更新は正常に終了したとして、ファームウェア更新を終了する。

【0092】

ここで、プログラムモードにおけるメインCPU201とサブCPU301との通信について図9に示すシーケンス図を用いて説明する。

【0093】

図9は、プログラムモードの際に図6に示すメインCPU201とサブCPU301との間で行われる通信について説明するためのシーケンス図である。

【0094】

まず、メインCPU201がフラッシュ更新リクエスト(Flash Update Req)をサブCPU301に送信する(S901)。このフラッシュ更新リクエストに応答して、サブCPU301はメインCPU201にフラッシュ書き換え可能応答(Flash Update Ack OK)を返す(S902)。

【0095】

次に、メインCPU201はサブCPU301にフラッシュ消去要求(Flash Erase Req)を送信する(S903)。フラッシュ消去要求に応答して、サブCPU301はフラッシュROM302の全ブロックの消去を行い、消去が完了すると、サブCPU302はメインCPU201にフラッシュ消去応答(Flash Erase Ack OK)を返す(S904)。

【0096】

続いて、メインCPU201は、ファームウェアイメージを先頭ブロックであるID=0から順番に送信する(Flash Data Send ID=0(Top):S905)。サブCPU301は該当ブロックに対するファームウェアイメージの書き込みが完了すると、メインCPU201にブロック書き込み完了応答(Flash Data Received ID=0 OK)を返す(S906)。

【0097】

さらに、メインCPU201はブロックカウンタを+1インクリメントして、ID=1のブロックにファームウェアイメージを送信する(Flash Data Send ID=1:S907)。サブCPU301は当該ブロックに対する書き込みが完了すると、メインCPU201にブロック書き込み完了応答(Flash Data Received ID=1)を返す(S908)。

【0098】

この処理を繰り返して、メインCPU201はID=255の最終ブロックに対するファームウェアイメージを送信する(Flash Data Send ID=255:S909)。そして、サブCPU301は当該ブロックに対する書き込みが完了すると、メインCPU201にブロック書き込み完了応答(Flash Data Received ID=255 OK)を返す(S910)。

【0099】

最後に、メインCPU201はサブCPU301に対してチェックサムの取得要求(Flash Check Sum Req)を送信する(S911)。これに応答して、サブCPU301はチェックサムを求めて、メインCPU201にチェックサム値を返信する(Flash Check Sum Report:S912)。

【0100】

図10は、図6に示すメインCPU201とサブCPU301との間でファームウェア更新を行った際の信号波形を説明するためのタイムチャートである。

【0101】

前述したように、メインCPU201はRESET601をLレベルとした後(S702)、BOOTMODE602をLレベルとする(S703)。その後、メインCPU201はRESET601をHレベルとして(S704)、TxD603でファーム更新リクエストを送信する(S802)。サブCPU301からRxD604で応答を受信すると(S803)、メインCPU201はTxD603でフラッシュメモリ消去要求を送信する(S804)。

【0102】

サブCPU301からRxD604で応答を受信すると(S805)、メインCPU201は前述のようにして、TXD603でファーム更新データを送信する(S807)。サブCPU301からRxD604で応答を受信すると(S808)、全てのブロックについて更新が終了していれば、メインCPU201はチェックサムを行う(チェックサムについては図10には示されていない)。

【0103】

その後、メインCPU201はRESET601をLレベルとした後(S706)、BOOTMODE602をHレベルとする(S707)。そして、メインCPU201はRESET601をHレベルとする。このように、ファームウェアの更新を完了した後、メインCPU201は一旦サブCPU301をリセットした後、BOOTMODE602をインアクティブに設定する。そして、メインCPU201はサブCPU301のリセット解除を行う。

【0104】

前述のように、メインCPU201にはサブCPU301、311、321、331、および341が互いに独立したシリアル信号線によって接続されている。このため、メインCPU201はサブCPU301、311、321、331、および341の各々に対して同時に通信を行うことができる。

【0105】

従って、サブCPU301、311、321、331、および341のうちいずれかにおいてファームウェアが更新中であっても、他のサブCPUにおいては動作を継続することができる。ここでは、いずれのサブCPUが司る機能がファームウェアの更新中のために使用不能であるか知る必要があるため、メインCPU201はRAM203にサブCPU状態テーブルを保持する。

【0106】

図11は、図3に示すRAM203に保持されるサブCPU状態テーブルの一例を示す図である。

【0107】

図11において、サブCPU状態テーブル(モジュール状態テーブル)1101にはモジュール(Module)欄、状態(Status)欄、および残量(Remain)欄が備えられている。Module欄には、サブCPU301〜341が記載される。図示の例では、サブCPU301、311、331、321、および341に対応して、そのStatusがそれぞれファームウェア更新中(Updating)、動作中(Active)、動作中、ファームウェア更新中、および動作中となっている。そして、ファームウェア更新中である場合には、Remain欄に残り更新サイズ(残量)がバイトで示される。

【0108】

ここで、サブCPU状態テーブルが図11に示す状態である場合に、スタートキー408が押し下げられた際のメインCPU201の動作について説明する。

【0109】

図12は、図3に示すいずれかのサブCPUにおいてファームウェアの更新中である場合にスタートキー408が押し下げられた際のメインCPU201の動作を説明するためのフローチャートである。

【0110】

ここでは、サブCPU状態テーブルは図11に示す状態であるとする。また、ジョブとしてコピーが行われるものとする。そして、図5に示すように、ジョブ設定において、カラー、等倍、片面、カセット113(用紙サイズA4)、およびトレイ121が選択されたものとする。

【0111】

スタートキー408が押し下げられると、メインCPU201は当該ジョブを受け付ける(ステップS1501)。続いて、メインCPU201は受け付けたジョブのモード解析(つまり、ジョブ設定)を行って、当該解析結果に応じて使用するモジュールのサブCPUを判定する(ステップS1502)。

【0112】

例えば、メインCPU201はジョブを受付けた際、ユーザ操作部401(図4)からジョブモード情報を受信する。

【0113】

図13は、図3に示すメインCPU201がユーザ操作部401から受けるジョブモード情報の一例を示す図である。

【0114】

図13において、ジョブモード情報は、給紙段ID、カラー/モノクロ、片面/両面、排紙先ID、および後処理モードなどのモード情報を有している。図示の例では、給紙段ID=”カセット113”、カラー/モノクロ=”カラー”、片面/両面=”片面”、排紙先ID=”トレイ121”、そして、後処理モード=”ノンソート”となっている。

【0115】

メインCPU201はジョブモード情報に応じて、予め定められたサブCPU関連付けテーブル(モジュール関連付けテーブル)を参照して、受け付けたジョブがいずれのサブCPUを使用するかについて判定する。このサブCPU関連付けテーブルは、例えば、ROM202に格納される。

【0116】

図14は、図3に示すROM202に格納されたサブCPU関連付けテーブルの一例を示す図である。

【0117】

図示のサブCPU関連付けテーブルは、ジョブモード情報とサブCPUとを関連付けるためのテーブルである。サブCPU関連付けテーブルには、給紙段ID、カラー/モノクロ、片面/両面、および排紙先IDの項目が規定され、これら項目毎に選択肢が設定されている。そして、選択肢毎に使用するサブCPU、つまり、ドライバが設定されている。

【0118】

このサブCPU関連付けテーブルは、予め製品構成のラインナップに応じてROM202に記録するようにする。なお、画像形成装置立上げの際におけるモジュール接続情報に応じてメインCPU201がサブCPU関連付けテーブルを生成して、このサブCPU関連付けテーブルをRAM203に記録するようにしてもよい。

【0119】

図15は、図12に示す使用サブCPU判定処理(ステップS1502)の一例を詳細に説明するためのフローチャートである。

【0120】

使用サブCPU判定処理を開始すると、まず、メインCPU201はジョブモード情報において給紙段IDに用紙カセット113が設定されているか否かを確認する(ステップS1510)。カセット113が設定されていない場合(ステップS1510において、NO)、メインCPU201はサブCPU関連付けテーブルを参照して、増設給紙カセット125および126を制御するオプションカセットドライバのサブCPU331が使用されると判定する(ステップS1511)。

【0121】

続いて、メインCPU201はジョブモード情報においてカラー/モノクロがカラーモードに設定されているか否かを確認する(ステップS1512)。なお、カセット113が設定されていると(ステップS1510において、YES)、処理はステップS1512に進む。

【0122】

カラーモードであれば(ステップS1512において、YES)、メインCPU201はサブCPU関連付けテーブルを参照して、YMCドラムモータ304およびYMC高圧ユニット305を制御するYMCドラムモータ/高圧ドライバのサブCPU301が使用されると判定する(ステップS1513)。

【0123】

続いて、メインCPU201はサブCPU関連付けテーブルを参照して、KドラムITBモータ314、K高圧ユニット315、および二次転写高圧ユニット316を制御するKドラム/高圧・ITBモータ・二次転写高圧ドライバのサブCPU311が使用されると判定する(ステップS1514)なお、カラーモードでなくても(ステップS1512において、NO)、Kドラム/高圧・ITBモータ・二次転写高圧ドライバのサブCPU311が使用されるので、処理はステップS1514に進む。

【0124】

次に、メインCPU201は、ジョブモード情報において片面/両面が片面モードに設定されているか否かを確認する(ステップS1515)。両面モードであると(ステップS1515において、NO)、メインCPU201はサブCPU関連付けテーブルを参照して、両面反転駆動ローラ122、両面再給紙駆動ローラ124、および両面反転フラッパ123を制御する両面/反転ユニットドライバのサブCPU321を使用すると判定する(ステップS1516)。

【0125】

次に、メインCPU201は、ジョブモード情報において排紙先IDがトレイ121に設定されているか否かを確認する(ステップS1517)。排紙先IDがトレイ121でない場合(ステップS1517において、NO)、メインCPU201は用紙がバッファパスユニット150を介してフィニッシャ上トレイ161又はフィニッシャ下トレイ162に排出されると判定する。

【0126】

これによって、メインCPU201はサブCPU関連付けテーブルを参照して、バッファパスユニット150を制御するバッファパス/フィニッシャドライバのサブCPU341を使用すると判定する(ステップS1518)。そして、メインCPU201は使用サブCPU判定処理を終了する。一方、排紙先IDがトレイ121であると(ステップS1517において、YES)、メインCPU201は使用サブCPU判定処理を終了する。

【0127】

なお、画像形成装置に備えられたモジュールが多いほど、サブCPU関連付けテーブルは細分化され、図15で説明した使用サブCPU判定処理におけるステップ数は増加する。

【0128】

再び、図12を参照して、上述のようにして、使用サブCPU判定処理が終了すると、続いて、メインCPU201はサブCPU状態テーブルを参照して、使用すると判定されたサブCPU(使用サブCPU)についてファームウェアの更新中(ダウンロード中)であるか否かを判定する(ステップS1503)。ファームウェアのダウンロード中でない場合(ステップS1503において、NO)、メインCPU201は使用すると判定した全てのサブCPUについて更新中であるかのサーチが完了したかを確認する(ステップS1504)。

【0129】

使用すると判定した全てのサブCPUについて更新中であるかのサーチが完了していないと(ステップS1504において、NO)、メインCPU201は他に使用すると判定したサブCPUに移行して(ステップS1505)、ステップS1503の処理を行う。

【0130】

一方、使用すると判定した全てのサブCPUについて更新中であるかのサーチが完了すると(ステップS1504において、YES)、メインCPU201は受け付けたジョブを実行して(ステップS1506)、ジョブ処理を終了する。

【0131】

使用すると判定したサブCPUがファームウェアのダウンロード中であると(ステップS1503において、YES)、メインCPU201は受け付けたジョブを予約ジョブとして(ステップS1507)、ジョブ処理を終了する。

【0132】

このように、使用すると判定されたサブCPUのいずれか1つがファームウェアをダウンロード中であれば、メインCPU201は受け付けたジョブを実行を待機する。そして、メインCPU201は受け付けたジョブに係るジョブモード情報をRAM203に格納する。

【0133】

図16は、図5に示すジョブモードの設定(ジョブ設定)が行われた際の使用サブCPU判定処理における判定結果を示す図である。

【0134】

図5に示すジョブ設定を行うと、図16にグレーアウトして示すように、Kドラム/高圧・ITBモータ・二次転写高圧ドライバ、YMCドラムモータ/高圧ドライバ、およびバッファパス/フィニッシャドライバに係るサブCPUが使用サブCPUとされる。そして、図11に示す例では、サブCPU301および321がファームウェアの更新中であるので、メインCPU201は受け付けたジョブを待機する。つまり、予約ジョブとする。

【0135】

図17は、図12で説明した予約ジョブの実行を説明するためのフローチャートである。

【0136】

前述のように、予約ジョブとされると、当該予約ジョブに係るジョブモード情報はRAM203に格納される。予約ジョブの処理が開始されると、メインCPU201はサブCPUにおけるファームウェアの更新終了を検知したか否かを確認する(ステップS1530)。ここでは、図8に示すステップS812およびS813において、サブCPUからチェックサム値の応答を受けて、チェックサム値が一致すると、メインCPU201は当該サブCPUにおけるファームウェアの更新が終了したとする。

【0137】

ファームウェアの更新終了を検知しないと(ステップS1530において、NO)、メインCPU201は待機する。一方、ファームウェアの更新終了を検知すると(ステップS1530において、YES)、メインCPU201は予約ジョブがあるか否かを確認する(ステップS1531)。ここでは、メインCPU201はRAM203にジョブモード情報が格納されているか否かを確認することになる。

【0138】

予約ジョブが存在しないと(ステップS1531において、NO)、メインCPU201は予約ジョブ処理を終了して、図12に示すステップS1501の処理に戻る。予約ジョブが存在すると(ステップS1531において、YES)、メインCPU201はジョブモード情報に基づいてジョブの再投入を行う(ステップ1532)。そして、メインCPU201は予約ジョブ処理を終了して、図12に示すステップ1501の処理に戻る。

【0139】

図5に示すジョブ設定では、YMCドラムモータ/高圧ドライバのサブCPU301がファームウェアの更新を終了すると、メインCPU201は予約ジョブを再投入することになる。

【0140】

続いて、ジョブ投入の投入後、使用サブCPUがファームウェアの更新中であった際のジョブのキャンセルについて説明する。

【0141】

図18は、図3に示すいずれかのサブCPUにおいてファームウェアの更新中である場合にスタートキーが押し下げられた際のメインCPUの動作の他の例を説明するためのフローチャートである。

【0142】

なお、図3に示す処理と同一の処理については同一の参照符号を付して、説明を省略する。

【0143】

ステップS1503において、使用すると判定したサブCPUがファームウェアのダウンロード中であると、メインCPU210は受け付けたジョブをキャンセルするか否かを判定する(ステップS1508)。ここでは、まず、メインCPU201はダウンロード中である旨の状態通知を行うとともに、ジョブを継続するか否かを決定する画面をユーザ操作部401に表示する。

【0144】

図19は、図18に示すジョブキャンセル判定処理の際にユーザ操作部401に表示されるポップアップウィンドウの一例を示す図である。

【0145】

使用すると判定したサブCPUがファームウェアのダウンロード中であると、メインCPU210は、図19に示すように、操作パネル画面503上にポップアップウィンドウ509に表示する。このポップアップウィンドウ509には、ファームウェアが更新中でありジョブに待機時間が生じる旨の文言とキャンセルするか否かを問う文言が表示される。

【0146】

ユーザが”Yes”ボタン510を押し下げると、メインCPU201は受け付けたジョブをキャンセルすると判定する。一方、ユーザ”No”ボタンを押し下げると、メインCPU201は受け付けたジョブをキャンセルしないと判定する。

【0147】

受け付けたジョブをキャンセルしないと判定すると(ステップS1508において、NO)、メインCPU201はステップS1507の処理に進んで、当該受け付けたジョブを予約ジョブとする。受け付けたジョブをキャンセルすると判定すると(ステップS1508において、YES)、メインCPU201は当該受け付けたジョブをキャンセルする(ステップS1509)。そして、メインCPU201はジョブ処理を終了する。

【0148】

以上のように、本発明の実施の形態によれば、ファームウェアのダウンロード中にジョブ処理要求を受信した際に、当該ジョブ処理要求に係るジョブを予約ジョブとして、当該予約ジョブで使用するモジュールにおいてファームウェアのダウンロードが終了すると、当該予約ジョブを実行するようにしたので、ファームウェアのダウンロードに起因してジョブ処理要求がキャンセルされることがない。従って、ユーザは再度ジョブを投入するという手間が省け、ユーザの利便性が向上する。

【0149】

上述の説明から明らかなように、図3に示す例では、メインCPU201およびサブCPU301〜341が更新手段として機能する。また、メインCPU201は判定手段および制御手段として機能する。なお、フラッシュROM302〜342の各々はモジュール記憶手段として用いられる。また、メインCPU201およびユーザ操作部401は報知手段として機能する。

【0150】

上述の実施の形態では、情報処理装置の一例として、画像形成装置を例に挙げて説明したが、画像形成装置に限らず他の情報処理装置、例えば、画像処理装置においても複数モジュールが互いに独立して動作する構成であれば同様にして本発明を適用することができる。また、上述の実施の形態では、ファームウェアを更新する場合については説明したが、ファームウェアに限らずソフトウェアの更新を行う場合であれば同様にして適用することができる。

【0151】

以上、本発明について実施の形態に基づいて説明したが、本発明は、これらの実施の形態に限定されるものではなく、この発明の要旨を逸脱しない範囲の様々な形態も本発明に含まれる。

【0152】

例えば、上記の実施の形態の機能を制御方法として、この制御方法を情報処理装置に実行させるようにすればよい。また、上述の実施の形態の機能を有するプログラムを制御プログラムとして、この制御プログラムを情報処理装置が備えるコンピュータに実行させるようにしてもよい。なお、制御プログラムは、例えば、コンピュータに読み取り可能な記録媒体に記録される。

【0153】

この際、制御方法および制御プログラムの各々は、少なくとも更新ステップ、判定ステップ、および制御ステップを有することになる。

【0154】

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記録媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【符号の説明】

【0155】

201 メインCPU

209 YMCドラムモータ/高圧ドライバ

210 Kドラム/高圧・ITBモータ・二次転写高圧ドライバ

211 両面/反転ユニットドライバ

212 オプションカセットドライバ

213バッファパス/フィニッシャドライバ

301,311,321,331,341 サブCPU

302,312,322,332,342 フラッシュROM

303,313,323,333,343 SRAM

【特許請求の範囲】

【請求項1】

互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置であって、

前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新手段と、

前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定手段と、

前記判定手段によって前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御手段とを有することを特徴とする情報処理装置。

【請求項2】

前記モジュールの各々について前記ソフトウェアが更新中であるか否かを示すステータスが記録されたモジュール状態テーブルを有し、

前記判定手段は、前記ジョブで用いるモジュールで前記ソフトウェアの更新が行なわれているか否かについて前記モジュール状態テーブルを参照して判定することを特徴とする請求項1に記載の情報処理装置。

【請求項3】

前記制御手段は、実行を待機させたジョブを予約ジョブとして、前記判定手段によって前記予約ジョブで用いるモジュールにおいて前記ソフトウェアの更新が終了したと判定されると、前記予約ジョブを実行することを特徴とする請求項1又は2に記載の情報処理装置。

【請求項4】

前記ジョブにおけるジョブ設定に関連付けてモジュールが規定されたモジュール関連付けテーブルを備え、

前記判定手段は、前記ジョブに備えられたジョブ設定に応じて前記モジュール関連付けテーブルを参照して、当該ジョブで用いるモジュールを判定することを特徴とする請求項1〜3のいずれか1項に記載の情報処理装置。

【請求項5】

前記判定手段によって前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、ユーザに当該ジョブが待機となる旨の報知を行う報知手段を有することを特徴とする請求項1〜4のいずれか1項に記載の情報処理装置。

【請求項6】

前記報知に応じてユーザがキャンセルの旨を入力すると、前記制御手段は前記ジョブをキャンセルすることを特徴とする請求項5に記載の情報処理装置。

【請求項7】

互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置の制御方法であって、

前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新ステップと、

前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定ステップと、

前記判定ステップで前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御ステップとを有することを特徴とする制御方法。

【請求項8】

互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置で用いられる制御プログラムであって、

前記情報処理装置に備えられたコンピュータに、

前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新ステップと、

前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定ステップと、

前記判定ステップで前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御ステップとを実行させることを特徴とする制御プログラム。

【請求項1】

互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置であって、

前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新手段と、

前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定手段と、

前記判定手段によって前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御手段とを有することを特徴とする情報処理装置。

【請求項2】

前記モジュールの各々について前記ソフトウェアが更新中であるか否かを示すステータスが記録されたモジュール状態テーブルを有し、

前記判定手段は、前記ジョブで用いるモジュールで前記ソフトウェアの更新が行なわれているか否かについて前記モジュール状態テーブルを参照して判定することを特徴とする請求項1に記載の情報処理装置。

【請求項3】

前記制御手段は、実行を待機させたジョブを予約ジョブとして、前記判定手段によって前記予約ジョブで用いるモジュールにおいて前記ソフトウェアの更新が終了したと判定されると、前記予約ジョブを実行することを特徴とする請求項1又は2に記載の情報処理装置。

【請求項4】

前記ジョブにおけるジョブ設定に関連付けてモジュールが規定されたモジュール関連付けテーブルを備え、

前記判定手段は、前記ジョブに備えられたジョブ設定に応じて前記モジュール関連付けテーブルを参照して、当該ジョブで用いるモジュールを判定することを特徴とする請求項1〜3のいずれか1項に記載の情報処理装置。

【請求項5】

前記判定手段によって前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、ユーザに当該ジョブが待機となる旨の報知を行う報知手段を有することを特徴とする請求項1〜4のいずれか1項に記載の情報処理装置。

【請求項6】

前記報知に応じてユーザがキャンセルの旨を入力すると、前記制御手段は前記ジョブをキャンセルすることを特徴とする請求項5に記載の情報処理装置。

【請求項7】

互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置の制御方法であって、

前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新ステップと、

前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定ステップと、

前記判定ステップで前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御ステップとを有することを特徴とする制御方法。

【請求項8】

互いに独立して動作する複数のモジュールと、前記モジュールの各々に備えられ当該モジュールで動作するソフトウェアが格納されたモジュール記憶手段とを有し、前記複数のモジュールを選択的に用いてジョブを実行する情報処理装置で用いられる制御プログラムであって、

前記情報処理装置に備えられたコンピュータに、

前記モジュール記憶手段に格納された前記ソフトウェアを更新する更新ステップと、

前記モジュールのいずれかで前記ソフトウェアの更新が行われている際、前記ジョブを受け付けると、当該ジョブで用いるモジュールが前記ソフトウェアの更新中であるか否かを判定する判定ステップと、

前記判定ステップで前記ジョブで用いるモジュールが前記ソフトウェアの更新中であると判定されると、前記ソフトウェアの更新が終了するまで、前記ジョブの実行を待機させる制御ステップとを実行させることを特徴とする制御プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−97515(P2013−97515A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−238793(P2011−238793)

【出願日】平成23年10月31日(2011.10.31)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月31日(2011.10.31)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]