情報処理装置、情報処理システムおよび認証方法

【課題】コスト上昇を抑制しつつ、情報処理装置に着脱される記憶装置の認証を行うことを目的とする。

【解決手段】記憶装置が装着される情報処理装置に、情報処理装置の制御部から独立して動作する認証部14を設ける。認証部14には、認証用の基準値145を格納するROM140、時間を計測するための遅延回路142、記憶装置から固定値(基準値145と等しい値)を読み出すためのコマンドを発行するコマンド発行回路146、記憶装置から読み出された値が受信値148として格納される受信バッファ147および比較回路144を設ける。記憶装置の認証を行う場合には、コマンド発行回路146が記憶装置に読み取りコマンドを発行し、正規の記憶装置のレイテンシ以内の時間に得られた受信値148と、基準値145とを比較回路144が比較する。

【解決手段】記憶装置が装着される情報処理装置に、情報処理装置の制御部から独立して動作する認証部14を設ける。認証部14には、認証用の基準値145を格納するROM140、時間を計測するための遅延回路142、記憶装置から固定値(基準値145と等しい値)を読み出すためのコマンドを発行するコマンド発行回路146、記憶装置から読み出された値が受信値148として格納される受信バッファ147および比較回路144を設ける。記憶装置の認証を行う場合には、コマンド発行回路146が記憶装置に読み取りコマンドを発行し、正規の記憶装置のレイテンシ以内の時間に得られた受信値148と、基準値145とを比較回路144が比較する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、着脱自在に装着される記憶装置を情報処理装置において認証する技術に関する。

【背景技術】

【0002】

ゲーム機本体(情報処理装置)にゲームプログラムを格納したメモリカード(記憶装置)を装着して、ゲーム機本体において当該ゲームプログラムを実行するような情報処理システムが知られている。このようなシステムでは、不正にコピーされたゲームプログラムが不正に使用されることを防止する必要がある。したがって、従来より、様々なセキュリティ技術が提案されており、例えば、そのようなセキュリティ技術が特許文献1に記載されている。

【0003】

【特許文献1】特開2007−133892号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところが、一般に、ソフトウェアで実現されるセキュリティ機能は、ゲームプログラムとともに容易にコピーされ回避されるという問題があり、ハードウェアで実現されるセキュリティ機能は、システム全体のコスト上昇を招くという問題があった。

【0005】

本発明は、上記課題に鑑みなされたものであり、システム全体のコスト上昇を抑制しつつ、記憶装置の認証を行うことを目的とする。

【課題を解決するための手段】

【0006】

上記の課題を解決するため、請求項1の発明は、記憶装置に格納されたプログラムを実行する情報処理装置であって、記憶装置が着脱自在に装着されるインターフェース手段と、前記インターフェース手段に装着された記憶装置に格納されているプログラムを実行する制御手段と、前記プログラムと独立して動作し、前記インターフェース手段に装着された記憶装置からのデータの読み出し時間に基づいて前記記憶装置の真偽を判定する認証手段とを備えることを特徴とする。

【0007】

また、請求項2の発明は、請求項1の発明に係る情報処理装置であって、前記認証手段は、認証用の基準値を格納する記憶部と、前記インターフェース手段に装着された記憶装置に対して読み出し要求を行い、前記読み出し要求に応じて前記記憶装置から得られた値を格納する読み出し部と、前記読み出し部に格納されている値を、前記読み出し部による読み出し要求がされてから所定の時間内に認証値として取得し、前記記憶部に記憶されている基準値と前記認証値とを比較する比較手段とを備え、前記認証手段は、前記比較手段の比較結果に応じて前記記憶装置の真偽を判定することを特徴とする。

【0008】

また、請求項3の発明は、請求項1または2の発明に係る情報処理装置であって、前記認証手段は、前記インターフェース手段に装着された記憶装置の真偽を判定する論理回路を備えることを特徴とする。

【0009】

また、請求項4の発明は、請求項1または2の発明に係る情報処理装置であって、前記認証手段は、前記インターフェース手段に装着された記憶装置の真偽を判定するための認証プログラムを格納するROMを備えることを特徴とする。

【0010】

また、請求項5の発明は、装着された記憶装置に格納されたプログラムを情報処理装置において実行する情報処理システムであって、前記情報処理装置は、記憶装置が着脱自在に装着されるインターフェース手段と、前記インターフェース手段に装着された記憶装置に格納されているプログラムを実行する制御手段と、前記プログラムと独立して動作し、前記インターフェース手段に装着された記憶装置からのデータの読み出し時間に基づいて前記記憶装置の真偽を判定する認証手段とを備えることを特徴とする。

【0011】

また、請求項6の発明は、プログラムを格納した記憶装置が着脱自在に装着される情報処理装置において前記記憶装置を認証する認証方法であって、(a)前記情報処理装置が備える記憶部に認証用の基準値を格納する工程と、(b)前記プログラムから独立して動作する読み取り部によって前記記憶装置からの値の読み出し要求を行う工程と、(c)前記(b)工程において前記記憶装置から読み出された値を受信バッファに格納する工程と、(d)前記(b)工程における読み出し要求を行ってから所定の時間内に、前記受信バッファに格納されている値を認証値として取得する工程と、(e)前記(a)工程において前記記憶部に格納された基準値と前記(d)工程において取得された認証値とを比較する工程と、(f)前記(e)工程における比較結果に基づいて前記記憶装置の真偽を判定する工程とを有し、前記所定の時間は前記記憶装置が真である場合の読み出し時間に応じて決定されることを特徴とする。

【0012】

また、請求項7の発明は、請求項6の発明に係る認証方法であって、(g)少なくとも前記(b)工程を実行する前に、前記記憶装置の固定位置に固定値を格納する工程をさらに有し、前記(a)工程において前記記憶部は前記固定値と同じ値を前記基準値として格納し、前記(b)工程における読み出し要求は前記(g)工程において前記固定値を格納した前記固定位置から値を読み出す要求であることを特徴とする。

【0013】

また、請求項8の発明は、請求項6の発明に係る認証方法であって、前記(a)工程は、(a-1)前記記憶装置の所定の位置に格納された値を読み出す工程と、(a-2)前記(a-1)工程において読み出された値を基準値として前記記憶部に格納する工程とを有し、前記(b)工程における読み出し部は、前記所定の位置からの読み出し要求を行うことを特徴とする。

【0014】

また、請求項9の発明は、請求項8の発明に係る認証方法であって、前記(a-1)工程における値の読み出しは、前記読み出し部によって実行され、前記(a-1)工程において読み出された値は、前記読み出し部による読み出し要求を行ってから前記所定の時間内に前記記憶装置から得られた値であることを特徴とする。

【0015】

また、請求項10の発明は、請求項6の発明に係る認証方法であって、(h)前記記憶装置から値の読み出しが行われたことを検出して、そのとき読み出された値と前記値の前記記憶装置における格納位置とを取得する工程をさらに有し、前記(a)工程における前記記憶部は、前記(h)工程において取得された値を前記基準値として格納し、前記(b)工程における前記読み出し部は、前記(h)工程において取得された格納位置からの読み出し要求を行うことを特徴とする。

【0016】

また、請求項11の発明は、請求項8ないし10のいずれかの発明に係る認証方法であって、前記(b)工程は、前記(a)工程が実行された後において、前記記憶装置から読み出される値が格納される受信バッファと前記記憶部とが参照され、前記受信バッファに格納されている値と、前記記憶部に格納されている基準値とが不一致であることが確認されてから実行されることを特徴とする。

【0017】

また、請求項12の発明は、請求項6ないし11のいずれかの発明に係る認証方法であって、(i)前記所定の時間を変更する工程をさらに有し、前記(b)工程は、前記(i)工程が実行されるたびに実行されることを特徴とする。

【発明の効果】

【0018】

請求項1ないし5に記載の発明では、記憶装置が着脱自在に装着されるインターフェース手段と、インターフェース手段に装着された記憶装置に格納されているプログラムを実行する制御手段と、プログラムと独立して動作し、インターフェース手段に装着された記憶装置からのデータの読み出し時間に基づいて記憶装置の真偽を判定する認証手段とを備えることにより、認証を容易に実現できる。

【0019】

請求項3に記載の発明では、インターフェース手段に装着された記憶装置の真偽を判定する論理回路を備えることにより、記憶装置との独立性が高く、改変される危険性も低いため、セキュリティが向上する。

【0020】

請求項4に記載の発明では、インターフェース手段に装着された記憶装置の真偽を判定するための認証プログラムを格納するROMを備えることにより、記憶装置のプログラムとの独立を確保しつつ、回路で実現する場合に比べてコストを抑制することができる。

【0021】

請求項6ないし12に記載の発明では、情報処理装置が備える記憶部に認証用の基準値を格納する工程と、プログラムから独立して動作する読み取り部によって記憶装置からの値の読み出し要求を行う工程と、記憶装置から読み出された値を受信バッファに格納する工程と、読み出し要求を行ってから所定の時間内に、受信バッファに格納されている値を認証値として取得する工程と、記憶部に格納された基準値と取得された認証値とを比較する工程と、比較結果に基づいて記憶装置の真偽を判定する工程とを有し、所定の時間は記憶装置が真である場合の読み出し時間に応じて決定されることにより、コストを抑制しつつ、認証を行うことができる。

【0022】

請求項7に記載の発明では、少なくとも認証を実行する前に、記憶装置の固定位置に固定値を格納するとともに、記憶部は固定値と同じ値を基準値として格納する。そして、認証のための読み出し要求は固定値を格納した固定位置から値を読み出す要求とすることにより、認証のための読み出しを行うタイミングにかかわらず、一回読み出すだけで、真偽判定が可能である。

【0023】

請求項8に記載の発明では、記憶装置の所定の位置に格納された値を読み出し、読み出された値を基準値として記憶部に格納し、当該所定の位置からの読み出し要求により取得された値と基準値とを比較することにより認証を行うことにより、記憶装置および情報処理装置に共通の固定値を予め格納しておく必要がない。

【0024】

請求項10に記載の発明では、記憶装置から値の読み出しが行われたことを検出して、そのとき読み出された値と当該値の記憶装置における格納位置とを取得し、取得した値を基準値として格納するとともに、取得された格納位置からの読み出し要求により認証のための認証値となる値を取得することにより、認証のための読み出しを一回行うだけで認証が可能である。また、記憶装置および情報処理装置に共通の固定値を予め格納しておく必要がない。

【0025】

請求項11に記載の発明では、基準値の取得が実行された後において、記憶装置から読み出される値が格納される受信バッファと記憶部とが参照され、受信バッファに格納されている値と、記憶部に格納されている基準値とが不一致であることが確認されてから認証を実行することにより、受信バッファに格納されている値がクリアされているか否かを確認してから認証を行うため、誤って認証に成功することが防止される。したがって、セキュリティレベルが向上する。

【0026】

請求項12に記載の発明では、所定の時間を変更する工程をさらに有し、当該所定の時間の変更が実行されるたびに認証を行うことにより、記憶装置のレイテンシを検出することができ、認証の確実性が向上する。

【発明を実施するための最良の形態】

【0027】

以下、本発明の好適な実施の形態について、添付の図面を参照しつつ、詳細に説明する。

【0028】

<1. 第1の実施の形態>

図1は、本発明に係る情報処理システム100を示す図である。図1に示すように、情報処理システム100は情報処理装置1および記憶装置7を備え、情報処理装置1に装着された記憶装置7に格納されたプログラム3を、情報処理装置1において実行するシステムとして構成されている。

【0029】

なお、図1に示す記憶装置8は、情報処理システム100における正規品である記憶装置7を模した模倣品(不正規品あるいは非ライセンス品)であり、記憶装置7に格納されているプログラム3に相当するプログラム9を格納している。詳細は後述するが、情報処理システム100は、正規品である記憶装置7と、不正規品である記憶装置8とを見分けて(真偽を判定して)、情報処理装置1がプログラム9を実行することのないように構成されている。

【0030】

また、記憶装置7の模倣品として製造される記憶装置8は、情報処理装置1に装着可能となることを意図してその形状等が設計されている。以下の説明において、記憶装置2とは、情報処理装置1に装着されている記憶装置7または記憶装置8であって、記憶装置7であるか記憶装置8であるかが未だ判定されていないもの(真偽不明の状態のもの)を指すものとする。

【0031】

また、図1において詳細を図示していないが、記憶装置7は、プログラム3を格納する記憶部と、記憶部へのアクセスを制御する制御部と、記憶部から読み出された値が一時的に格納されるバッファとを備えている。

【0032】

記憶装置7の制御部は、情報処理装置1から読み取りコマンドを受信すると、記憶部の指定位置(読み取りコマンドに含まれるアドレス値によって指定される位置)に格納されている値をバッファに格納する。そして、当該バッファに格納された値が、記憶装置7から読み出された値として情報処理装置1に転送される。

【0033】

記憶装置7の記憶部を構成する不揮発性の記憶素子は、情報処理システム100が保証する速度で読み出し可能な記憶素子である。以下の説明では、記憶装置7のレイテンシを「時間T」とする。

【0034】

一方、不正規品である記憶装置8もプログラム9を格納する記憶部と、記憶部へのアクセスを制御する制御部と、記憶部から読み出された値が一時的に格納されるバッファとを備えている。しかし、記憶装置8では、記憶部を構成する不揮発性の記憶素子として、安価な記憶素子が採用されている場合が多い。このような安価な記憶素子を用いた記憶装置8は、アクセス速度が遅い等、記憶装置7に比べてハードウェア性能が劣るものである。以下の説明では、記憶装置8のレイテンシを「時間TX」とし、T<TXであるとして説明する。

【0035】

図2は、第1の実施の形態における情報処理装置1の構成を示す図である。図2に示すように、情報処理装置1は、制御部10、操作部11、表示部12、インターフェース部13および認証部14を備え、これらの構成がバス配線19を介して互いに接続されている。このような構成により、情報処理装置1は、一般的なコンピュータとしての機能を有している。

【0036】

なお、情報処理装置1は、図2に示す構成の他に、大容量のデータを記憶するハードディスクや、音声を再生するスピーカ、紙媒体にデータを印刷するプリンタ等の各種ハードウェアを備えていてもよい。すなわち、情報処理装置1は、プログラム3あるいはプログラム4を実行することによって提供されるアプリケーションを実現するためのハードウェアを適宜備えている。

【0037】

制御部10は、各種データの演算を行うCPU15と、プログラム4が格納されたROM16と、CPU15の一時的なワーキングエリアとして使用されるRAM17とを備えている。図2において、便宜上、CPU15、ROM16およびRAM17はいずれも1つの装置から構成されているかのように図示しているが、もちろん複数の装置が協働してそれぞれを構成していてもよい。

【0038】

CPU15は、ROM16に格納されたプログラム4を実行するとともに、インターフェース部13に装着された記憶装置7に格納されているプログラム3を実行する。

【0039】

ROM16は、読み取り専用の不揮発性の記憶素子からなる記憶装置であり、先述のように、プログラム4が格納される。プログラム4としては、主にBIOSやOS等の基本プログラムが該当するが、もちろんこれに限定されるものではなく、アプリケーションプログラムが含まれていてもよい。本実施の形態における情報処理システム100では、プログラム4は情報処理装置1側において提供されるプログラムであり、例えば、記憶装置2から転送されるプログラム(プログラム3またはプログラム9)を含まないものとして説明する。

【0040】

RAM17は、比較的高速にデータの読み書きが可能な揮発性の記憶素子からなる記憶装置であり、CPU15によってアクセスされる。制御部10がプログラム3を実行する際には、プログラム3の一部又は全部がRAM17にロードされ、CPU15によって実行される。

【0041】

本実施の形態における情報処理システム100では、記憶装置7が情報処理装置1に装着されたときに(より詳しくはロード処理が実行されたときに)、プログラム3の一部であるライブラリ(関数)が情報処理装置1によって読み出されRAM17に格納される。そして、RAM17上に読み出されたライブラリをCPU15が使用しつつ、適宜、記憶装置7にアクセスすることによって、プログラム3が実行される。

【0042】

このようなアーキテクチャを採用することにより、情報処理装置1は、プログラム3の全部を記憶装置7に格納したままで実行する場合に比べて、記憶装置7へのアクセス回数を減らすことができ、プログラム3の実行速度を向上させることが可能となる。また、プログラム3に特化したライブラリを準備してプログラム3自体に含めておくことによって、プログラム3の実行効率が向上する。

【0043】

記憶装置8も、記憶装置7と同様に、情報処理装置1からのロード要求に応じて、格納しているプログラム9の一部であるライブラリを情報処理装置1に転送する。

【0044】

先述のように、記憶装置8の記憶部は、記憶装置7の記憶部よりもアクセス速度が遅い記憶素子で構成されている。以下、情報処理装置1から要求されたデータを記憶装置8が読み出す場合を例に、アクセス速度の遅い記憶素子を用いた記憶装置8が情報処理装置1において使用可能となる仕組みについて説明する。

【0045】

記憶装置8では、情報処理装置1からの読み出し要求に応じて制御部が記憶部からデータを読み出そうとしても、所定の時間内(情報処理装置1にデータを渡すときまで)に、記憶装置8のバッファに所望のデータを格納することができない。そして、記憶装置8のバッファへの格納が間に合わなかった場合、たまたまそのとき記憶装置8のバッファ上に格納されていた残余のデータが情報処理装置1に渡される。この残余のデータは、当該読み出し要求以前の処理で読み出されたデータであるため、一般に当該読み出し要求によって要求されているデータではない。したがって、記憶装置8に対して通常の読み出し要求を実行すると、情報処理装置1は誤ったデータを取得することとなり、所望したデータを得ることはできない。

【0046】

しかし、情報処理装置1から記憶装置8に対する読み出し要求は、記憶装置7に対する読み出し要求と同様に、予め情報処理装置1に転送されたライブラリを実行する形で実行される。

【0047】

そこで、プログラム9のライブラリでは、プログラム3における読み出し要求(通常の読み出し要求)を行う前段階として、当該読み出し要求で所望されるデータを予め記憶装置8のバッファに読み出しておく処理を実行するように、プログラム3のライブラリを改変している。以下、通常の読み出し処理の前段階として実行される処理を「プレ読み出し処理」と称する。

【0048】

より具体的には、記憶装置7からの読み出し処理を行うライブラリ(プログラム3におけるライブラリ)は、プログラム9では、記憶装置8に対するプレ読み出し処理と、それに続く読み出し処理とを行うライブラリとして書き換えられている。すなわち、当該ライブラリに、プレ読み出し処理を行う部分が、いわゆるパッチとして当てられたように、プログラム3が改変されている。

【0049】

情報処理システム100は、記憶装置2の装着後、瞬時に認証が完了するわけではない。そのため、記憶装置8に格納されているプログラム9も、記憶装置8が情報処理装置1に装着されたときに、先述のように、その一部がRAM17にロードされる。したがって、記憶装置7ではなく記憶装置8が装着された場合であっても、記憶装置8であることが判明するまでの間、制御部10(CPU15)は、情報処理システム100の設計者の意に反して、プログラム9の一部を実行することとなる。

【0050】

装着されている記憶装置2が記憶装置8であると認識していない情報処理装置1の制御部10が、RAM17に格納されているライブラリ(記憶装置8由来のライブラリ)を実行すると、まず、記憶装置8に対して、プレ読み出し処理を実行させる独自のコマンド(以下、「プレ読み出しコマンド」と称する)を発行することとなる。

【0051】

なお、このプレ読み出しコマンドには、引き続き実行される読み出し処理において所望されるデータの記憶装置8におけるアドレスが含まれている。このアドレスは、本来、記憶装置7のアドレスとして与えられるものであるが、本実施の形態では、記憶装置8が記憶装置7と同じアドレスに同じデータを格納するように設計されているものと想定しているため、そのままの値を用いる例で説明する。ただし、記憶装置8におけるデータの格納状況に応じて、例えば、記憶装置7におけるアドレスをオフセットさせて用いていてもよい。

【0052】

情報処理装置1からプレ読み出しコマンドを受信した記憶装置8の制御部は、当該コマンドに含まれるアドレスに基づいて、所望のデータを記憶装置8の記憶部から読み出して、記憶装置8のバッファに格納する。

【0053】

この間、情報処理装置1は、プレ読み出し処理に続く読み出し処理を開始することなく待機している。このような情報処理装置1側の待機時間は、プレ読み出し処理に、記憶装置8側の読み出し完了を確認する処理(例えばレディ・ビジー処理等)を含めるか、あるいは、記憶装置8のレイテンシ(時間TX)に応じて充分なウェイト処理を含める等によって容易に設けることができる。

【0054】

そして、記憶装置8のバッファに所望のデータが格納された時点で、引き続き、通常の読み出し処理が実行される。すなわち、情報処理装置1から読み出しコマンドが発行され、記憶装置8の制御部が当該コマンドに応じて、指定されたアドレスに格納されているデータを記憶部から読み出してバッファに格納する。

【0055】

先述のように、読み出し要求に対して、情報処理装置1には記憶装置8のバッファに格納されているデータが渡される。通常の読み出し要求がされたとき、既に実行されたプレ読み出し処理によって記憶装置8のバッファには所望のデータが格納されている。したがって、バッファに格納されているデータが、プレ読み出し処理で格納された残余のデータであるか、その後の読み出し処理で格納された所望のデータであるかに関わらず、結局、情報処理装置1は所望のデータを得ることができるのである。

【0056】

このように、記憶装置8は、プログラム3を改変したプログラム9を予め情報処理装置1に転送することにより、本来の情報処理装置1が保証するレイテンシ内でアクセスを完了する必要がないように構成されている。これによって、不正規品である記憶装置8の製造業者は、記憶装置8の記憶部としてアクセス速度の遅い記憶素子を採用して、製造コストを抑制している。

【0057】

図2に戻って、操作部11は、ボタン、キーボード、マウス、コントローラ、ジョイスティック、タッチパネル等の各種ハードウェアから構成されており、ユーザが情報処理装置1に対して指示を入力するために使用される。ユーザが操作部11を操作することにより指示を入力した際には、操作部11からバス配線19を介して制御部10(CPU15)に対してハードウェア割り込み信号が伝達される。

【0058】

表示部12は、例えば、液晶ディスプレイやCRT、ランプ、LED等であり、制御部10からの制御信号に応じて、各種データや状態を表示する。なお、表示部12としては、情報処理装置1にケーブル等で外部接続されるテレビ受像器であってもよい。

【0059】

インターフェース部13は、記憶装置7と接続されるコネクタ等から構成され、当該コネクタには記憶装置7が着脱自在に装着される。すなわち、インターフェース部13に記憶装置7が装着されることによって、情報処理装置1は記憶装置7との間でデータ通信が可能となり、情報処理装置1は記憶装置7を自らが備える記憶装置として使用することが可能となる。

【0060】

また、情報処理装置1に装着可能となることを意図し、記憶装置7の模倣品として製造される記憶装置8も同様にインターフェース部13に適合するように製造される。したがって、先述のように、インターフェース部13には記憶装置8を装着することも可能である。

【0061】

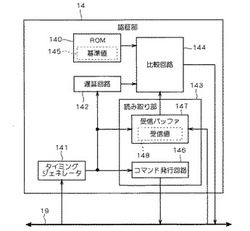

図3は、第1の実施の形態における認証部14を示す図である。本実施の形態における認証部14は、ROM140、タイミングジェネレータ141、遅延回路142、読み取り部143および比較回路144を備える。また、認証部14は、制御部10とは別に設けられる独立したハードウェア(論理回路)として構成されており、プログラム3(プログラム9)と独立して動作する。そして、認証部14は、インターフェース部13に装着された記憶装置2からのデータの読み出し時間に基づいて記憶装置2の真偽(記憶装置7であるか記憶装置8であるかの別)を判定する機能を有する。

【0062】

ROM140には認証用の基準値145が格納される。本実施の形態における基準値145は、例えば情報処理装置1の製造段階で予めROM140に格納される。すなわち、本実施の形態における基準値145は、情報処理装置1において一定の値(固定値)である。ROM140に格納された基準値145は、必要に応じて比較回路144によって読み出される。

【0063】

タイミングジェネレータ141は、コマンド発行回路146を駆動するタイミングを決定して、コマンド発行回路146にタイミング信号を出力する機能を有する。言い換えれば、タイミングジェネレータ141は、コマンド発行回路146に対して、コマンド発行の許可を与える。

【0064】

タイミングジェネレータ141からコマンド発行回路146に向けて出力されたタイミング信号は、同時に遅延回路142および受信バッファ147にも伝達される。タイミングジェネレータ141がタイミング信号を出力するタイミングを決定する手法は後述する。

【0065】

遅延回路142は、タイミングジェネレータ141から伝達されるタイミング信号を、所定の時間tだけ遅延させて比較回路144に向けて出力する回路である。以下、遅延回路142から比較回路144に向けて出力される信号を「遅延信号」と称する。

【0066】

本実施の形態における時間tは、記憶装置7のレイテンシ(時間T)に応じて予め決定されている固定の値である。時間tは、情報処理システム100の保証値として決定される値であるが、例えば記憶装置7のレイテンシが230マイクロ秒程度であれば、時間tはそれよりも大きい値(ただし大きすぎない値であって、例えば250マイクロ秒程度)に決定される。

【0067】

なお、時間tは、記憶装置8のレイテンシ(時間TX)よりも小さい値であることが好ましい。時間TXは不正規品である記憶装置8の性能に関するパラメータであるから、厳密には不知の値である。しかし、一般に供給されている安価な記憶素子を用いた場合、あるいは市場に流通している模倣品(記憶装置8)に基づいて、予め、ある程度の数値範囲として予測することは可能である。したがって、本実施の形態における情報処理システム100では、T<t<TXとなるように、時間tを決定する。

【0068】

読み取り部143は、コマンド発行回路146および受信バッファ147から構成される。

【0069】

コマンド発行回路146は、タイミングジェネレータ141から伝達されるタイミング信号に応じて、インターフェース部13に装着されている記憶装置2に対して読み取り要求を行う(読み取りコマンドを発行する)。

【0070】

受信バッファ147は、コマンド発行回路146が発行した読み取りコマンドに対するレスポンス(記憶装置2から読み出された値)を受信値148として格納する。

【0071】

本実施の形態における読み取り部143において、受信バッファ147に格納されている値は、タイミングジェネレータ141から伝達されるタイミング信号によって初期値にクリアされる。この初期値は記憶装置2から受信される値ではないが、便宜上、この初期値も含めて「受信値148」と称する。受信値148の初期値は、ROM140に格納される基準値145とは異なる値として予め設定されているものとする。

【0072】

このように本実施の形態における情報処理装置1では、コマンド発行回路146が読み取りコマンドを発行すると同時に受信バッファ147に格納されている受信値148が初期値にクリアされる。そして、当該読み取りコマンドに応じて何らかの値が記憶装置2から得られると、得られた値によって初期値が上書きされ、新たな受信値148として格納される。

【0073】

情報処理装置1は、制御部10とは別に、独立して動作する認証部14を備えていることにより、制御部10からの直接的な制御を受けることなく、記憶装置2からの値(受信値148として格納する値)の読み出しを行う。

【0074】

なお、認証部14は、受信値148となる値を記憶装置2から読み出す機能を最小限備えていればよいので、コマンド発行回路146は読み取りコマンドのみを発行し、その他のコマンド(例えば書き込みコマンドや消去コマンド等)を発行する必要はない。また、本実施の形態では、受信値148となる値の記憶装置2における格納位置(アドレス)は予め決められているので、読み取りコマンドにセットされるアドレスは固定の値でよい。すなわち、コマンド発行回路146は任意の信号を出力する機能を備えている必要はなく、タイミング信号が入力されたタイミングに応じて、固定の出力信号を、インターフェース部13を介して、記憶装置2に向けて送信する回路として構成されていれば充分である。

【0075】

比較回路144は、遅延回路142から遅延信号が伝達されると、ROM140から基準値145を取得するとともに、受信バッファ147から受信値148を認証値として取得する。そして、取得した基準値145と認証値とを比較して、これらが一致したか否かを示す信号(以下、「判定信号」と称する)を制御部10に出力する。

【0076】

詳細は後述するが、本実施の形態における情報処理システム100において、基準値145と認証値とが一致する場合とは、記憶装置2が正規品の記憶装置7であると判定されたことを意味する。一方、基準値145と認証値とが一致しない場合とは、記憶装置2が不正規品の記憶装置8であると判定されたことを意味する。すなわち、認証部14は、ROM140に記憶されている基準値145と認証値とを比較し、その比較結果に基づいて記憶装置2の真偽を判定する機能を有している。

【0077】

以上が情報処理システム100の構成および機能の説明である。

【0078】

次に、プログラム3(あるいはプログラム9)を格納した記憶装置2が着脱自在に装着される情報処理装置1において記憶装置2を認証する認証方法について説明する。

【0079】

図4は、第1の実施の形態における認証方法を示す流れ図である。

【0080】

なお、第1の実施の形態では、図4に示す各工程が実行される前に、情報処理装置1が備えるROM140に認証用の基準値145を格納する工程と、記憶装置7の固定位置に基準値145と同じ値(固定値)を格納する工程とが既に実行されているものとする。例えば、これらの値は、これらの装置が出荷される際に既に格納されているものとする。また、記憶装置7に格納されている固定値が誤って書き換えられると、正常な認証が行えなくなるため、固定値は書き換え不可(読み取り専用)とされていることが好ましい。

【0081】

まず、情報処理装置1に電源が投入されると、情報処理装置1は制御部10のCPU15がROM16に格納されているプログラム4に従って制御を開始することによって動作を開始する。

【0082】

このようにして動作を開始した情報処理装置1は、インターフェース部13を監視することによって記憶装置2が検出されたか否かを監視する(ステップS1)。また、認証部14による認証を行うか否かについても監視する(ステップS3)。そして、これらを監視しつつ、必要なプログラムを実行する(ステップS11)。

【0083】

なお、ステップS11におけるプログラムは、情報処理装置1においてそのとき実行可能な全てのプログラムを含むものであり、プログラム4に限られるものではなく、プログラム3やプログラム9が実行される場合もある。

【0084】

情報処理装置1の動作が開始され、ステップS11によってプログラムが順次実行されているときに、記憶装置2が検出されると、制御部10はステップS1においてYesと判定し、初期設定(ステップS2)を実行する。

【0085】

なお、ステップS1においてYesと判定されるのは、情報処理装置1の電源投入時に既に記憶装置2が装着されていたときと、記憶装置2が装着されていない状態から新たに記憶装置2が装着されたときである。すなわち、装着された状態の記憶装置2に対して、1回だけステップS2が実行される。

【0086】

ステップS2の初期設定では、情報処理装置1の制御部10が、インターフェース部13に装着されている記憶装置2に対して、格納しているプログラムをロードするように要求する。装着されている記憶装置2が記憶装置7である場合には、このロード要求に応じて、記憶装置7からプログラム3のロードが行われ、プログラム3の一部を構成するライブラリが制御部10のRAM17に転送される。一方、装着されている記憶装置2が記憶装置8である場合にも、このロード要求に応じて、記憶装置8からプログラム9のロードが行われ、プログラム9の一部を構成するライブラリが制御部10のRAM17に転送される。

【0087】

このように初期設定(ステップS2)が実行されることによって、必要なライブラリがRAM17に転送される。そして、以後、これらのライブラリをCPU15が使用することにより、プログラム3(あるいはプログラム9)が実行可能となる。

【0088】

情報処理装置1の動作が開始され、ステップS11によってプログラムが順次実行されているときに、所定の条件が満たされると、認証部14がステップS3においてYesと判定する。本実施の形態では、当該条件の判定を認証部14のタイミングジェネレータ141が行う。

【0089】

ここで、認証は、記憶装置2が装着されていない状態で行う必要はないので、本実施の形態におけるタイミングジェネレータ141が認証を行うと判定する条件(ステップS3においてYesと判定する条件)の1つは、記憶装置2がインターフェース部13に装着されていることである。

【0090】

また、認証は、一旦装着された記憶装置2に対して、少なくとも1回行うべきであり、かつ、定期的に複数回行ってもよい。本実施の形態におけるタイミングジェネレータ141が認証を行うと判定する条件の1つは、ステップS2が実行された後であって、かつ、前回の認証から所定の時間(予めセットされた時間)が経過したことである。ただし、認証を行った回数情報を保持しておき、予め決められた回数の認証をクリアした場合には、以後、当該記憶装置2に対する認証を行わないように構成してもよい。

【0091】

また、認証は、制御部10によるプログラム3の実行を妨害しないタイミングで行うことが好ましい。特に、認証部14による認証は記憶装置2に対するアクセスを伴うため、制御部10によるアクセスと認証部14によるアクセスとが干渉しないように実行する必要がある。したがって、本実施の形態におけるタイミングジェネレータ141が認証を行うと判定する条件の1つは、制御部10が記憶装置2にアクセスしていないことである。そして、制御部10が記憶装置2にアクセスしていないタイミングは、タイミングジェネレータ141がバス配線19上の各種信号を監視することにより検出可能である。

【0092】

本実施の形態では、タイミングジェネレータ141が制御部10に対してハードウェア割り込み信号を送信することによって、いわば制御部10に対して認証を行うための許可を求める。これに対して制御部10から許可信号が得られた場合に、タイミングジェネレータ141は、制御部10が記憶装置2にアクセスしていないと判定する。

【0093】

すなわち、本実施の形態では、インターフェース部13に記憶装置2が装着されており、装着されている記憶装置2に対してステップS2が実行された後において、所定の時間が経過するたびにタイミングジェネレータ141が制御部10に対してハードウェア割り込み信号を送信する。そして、当該ハードウェア割り込み信号に対して制御部10から許可信号が送信された場合に、タイミングジェネレータ141は認証を行う(ステップS3においてYes)と判定する。

【0094】

なお、制御部10において、情報処理装置1が備えるハードウェア(操作部11や認証部14)からのハードウェア割り込み信号に対する処理は、通常、情報処理装置1のBIOSやOS(すなわちプログラム4)に基づいて行われる。したがって、認証部14がハードウェア割り込み信号によって、制御部10に対して認証を行う許可を求めるように構成したとしても、記憶装置8のプログラム9による影響(例えば、いかなる場合も認証を許可しない等の制御)を受ける危険性は低い。

【0095】

図4に戻って、タイミングジェネレータ141が認証を行うと判定すると(ステップS3においてYes)、タイミングジェネレータ141が、読み取り部143(コマンド発行回路146および受信バッファ147)と遅延回路142にタイミング信号を出力する。

【0096】

このタイミング信号に応じて、受信バッファ147に格納されている値が初期値にクリアされる(受信値148が初期化される)。また、コマンド発行回路146が、記憶装置2の固定位置に格納されている固定値を読み取るための、読み取りコマンドを記憶装置2に向けて発行することにより、読み取り部143が読み出し要求を行う(ステップS4)。すなわち、情報処理装置1は、プログラム3(プログラム9)から独立して動作する読み取り部143によって記憶装置2からの値の読み出し要求を行う。

【0097】

読み取り部143による読み出し要求は、制御部10による読み出し要求と異なるところはない。したがって、この読み取りコマンドを受信した記憶装置2の制御部は、当該コマンドに含まれるアドレス(固定位置)からデータ(固定値)を読み出して、記憶装置2のバッファに格納する。

【0098】

認証方法としては、情報処理装置と記憶装置との間で、共通のパスワード(固定値)を記憶しておいて照合する方法が広く提案されている。しかし、パスワードも他のデータ(プログラム本体)と同じく情報であるため、記憶装置においてプログラムとパスワードとを同等に格納していれば、プログラムをコピーするのと同じ要領でパスワードもコピーされてしまうおそれが高い。このような不正コピーを防止しようとすれば、プログラムとは別に、パスワードをより高度にガードする仕組みが記憶装置に必要となり、正規品の記憶装置におけるコスト上昇を招くこととなる。しかも、例え、パスワードを何らかの方法でガードしていたとしても、一旦、ガードが破られ、パスワードがコピーされると、その後は、まったく不正規品を区別することができなくなるという問題もある。

【0099】

したがって、プログラム3を模しているプログラム9には、固定値も含まれている(コピーされている)危険性が高く、そのような場合には、記憶装置2に固定値が格納されているか否かだけでは、記憶装置7と記憶装置8とを区別することはできない。本実施の形態における情報処理システム100は、記憶装置8の固定位置にも基準値145と同じ値(固定値)が格納されているものとして以下の処理を行う。

【0100】

情報処理装置1の認証部14は、遅延回路142がタイミング信号を遅延させることによって時間tが経過するまで待機しつつ(ステップS7)、その間に、記憶装置2から固定値を受信したか否かを監視する(ステップS5)。時間t内に、ステップS4における読み出し要求に対する値を記憶装置2から受信すると、その値が受信値148として受信バッファ147に格納される(ステップS6)。

【0101】

記憶装置2として、正規品の記憶装置7が装着されていた場合、時間T<時間tであるから、記憶装置7は読み出し部143による読み出し要求に対する値を時間t内に記憶部から読み出してバッファに格納することが可能である。したがって、記憶装置2として、正規品の記憶装置7が装着されていた場合には、読み取り部143による読み出し要求によって要求された値が、ステップS6によって正しくバッファに格納される。すなわち、記憶装置2のレイテンシが時間t内であれば、所望した固定値が受信値148として格納される。

【0102】

一方、記憶装置2として、不正規品の記憶装置8が装着されていた場合、時間t<時間TXであるから、記憶装置8は読み出し部143による読み出し要求に対する値を時間t内に読み出してバッファに格納することができない。また、認証部14は記憶装置2から転送されたライブラリから独立して動作しているため、例え記憶装置8が装着されている場合でも、ステップS4における読み出し要求の前に、プレ読み出し処理を行うことができない。したがって、記憶装置8は、例え固定値を正確にコピーして格納していたとしても、読み取り部143から所望されたときに、当該固定値をバッファに格納する処理が間に合わず、かつ、予め格納しておくこともできない。したがって、記憶装置8は、読み取り部143に対して、値の保証されない、バッファ上の残余のデータを受け渡すこととなり、これが受信バッファ147に受信値148として格納される。すなわち、記憶装置2のレイテンシが時間t内でなければ、所望した固定値が受信値148として格納されない。

【0103】

なお、本実施の形態は、情報処理装置1と記憶装置7との間では、レディ・ビジー機能を実現していない。したがって、認証部14と模倣品である記憶装置8との間でもレディ・ビジー処理は行われず、記憶装置8がレディ状態になったか否かにかかわらず、記憶装置8のバッファから情報処理装置1側に残余のデータ(固定値と異なる値)が取得される。一方、このような機能を持たせていた場合、時間t内に記憶装置8がレディとなることはないので、時間t内に記憶装置8からデータを受信することはなくなる。その場合でも、情報処理装置1側の受信バッファ147には、受信値148として初期値が格納されているため、やはり、固定値とは異なる値が受信値148となる。

【0104】

時間tが経過して(ステップS7においてYes)、遅延回路142が遅延信号を比較回路144に向けて出力すると、比較回路144が基準値145をROM140から取得する。また、その時点で受信バッファ147に格納されている受信値148を認証値として受信バッファ147から取得する(ステップS8)。すなわち、情報処理装置1は、ステップS4における読み出し要求を行ってから所定の時間内に、受信バッファ147に格納されている受信値148を認証値として取得する。

【0105】

次に、比較回路144によって取得した基準値145と取得した認証値とを比較し(ステップS9)、比較回路144からの出力信号(比較結果)に応じて、装着されている記憶装置2が正規品(記憶装置7)であるか、不正規品(記憶装置8)であるかを判定する(ステップS10)。

【0106】

装着されている記憶装置2が記憶装置7である場合、時間t内に固定値が得られ、この固定値が受信値148として格納されている。この場合、ステップS8において取得される認証値は固定値であるから、ROM140に格納されていた基準値145と一致する。すなわち、比較回路144からの出力信号が、基準値145と認証値との一致を示している場合、ステップS10ではYesと判定される。この場合、情報処理システム100は処理を終了することなく、プログラムの実行を継続する(ステップS11)。

【0107】

一方、装着されている記憶装置2が記憶装置8である場合、時間t内に固定値を得ることができず、この固定値と異なる値が受信値148として格納されている。したがって、取得された認証値は固定値とは異なるので、ROM140に格納されていた基準値145と一致しない。すなわち、比較回路144からの出力信号が、基準値145と認証値との不一致を示している場合、ステップS10ではNoと判定される。この場合、情報処理システム100は処理を終了し、プログラム9の実行を停止する。

【0108】

以上のように、本実施の形態における情報処理装置1は、記憶装置2が着脱自在に装着されるインターフェース部13と、インターフェース部13に装着された記憶装置2に格納されているプログラム3,9を実行する制御部10と、プログラム3,9と独立して動作し、インターフェース部13に装着された記憶装置2からのデータの読み出し時間に基づいて記憶装置2の真偽を判定する認証部14とを備えることにより、正規品である記憶装置7のハードウェア構成を変更することなく、記憶装置2のハードウェア特性に基づく認証を容易に実現できる。

【0109】

また、認証部14は、インターフェース部13に装着された記憶装置2の真偽を判定する比較回路144を備えることにより、記憶装置2との独立性が高く、改変される危険性も低いため、セキュリティが向上する。

【0110】

なお、先述のように、本実施の形態では認証を実行する条件が整う限り、認証部14による認証が何回でも行われる(特に回数制限は設けていない)。一方で、図4から明らかなように、基準値145と認証値とが一致しない事態(認証失敗)が1回でも発生すると、情報処理システム100における処理を終了する。しかし、認証失敗の回数制限を予め設けておき、当該回数制限を超えるまでは処理を続行するように構成してもよい。また、この場合、回数制限以内であっても、警告等を表示するようにしてもよい。

【0111】

また、記憶装置7に格納される固定値はプログラム3,4が実行される過程で書き換えられることのない値であればよい。したがって、認証のためだけに格納される値でなくてもよく、例えば、CPU15によって実行される指令の一部であってもよい。

【0112】

<2. 第2の実施の形態>

第1の実施の形態における認証部14は、主に回路(ハードウェア)で構成されていたが、その一部をプログラムで実現することも可能である。

【0113】

図5は、第2の実施の形態における情報処理装置1aの認証部14aを示す図である。また、図6は、第2の実施の形態における認証部14aが備える機能ブロックをデータの流れとともに示す図である。

【0114】

なお、第2の実施の形態における情報処理装置1aは、認証部14の代わりに認証部14aを備えている点を除いて、ほぼ第1の実施の形態における情報処理装置1と同様の構成を備えている。以下の説明では、第1の実施の形態と同様の構成については同符号を付し、適宜説明を省略する。

【0115】

認証部14aは、図5に示すように、基準値145を格納するROM140aと、CPU150と、RAM151とを備えている。

【0116】

ROM140aは、第1の実施の形態におけるROM140と同様に基準値145を格納する。また、インターフェース部13に装着された記憶装置2の真偽を判定するためのプログラム149を格納する。

【0117】

CPU150は、RAM151を一時的なワーキングエリアとして使用しつつ、主にプログラム149に従って動作する。図6に示す、タイミング決定部152、読み取り部153、比較部154および判定部155は、CPU150がプログラム149に従って(プログラム3,9から独立して)動作することにより実現される機能ブロックである。

【0118】

タイミング決定部152は、制御部10との間でデータのやり取りを行いつつ、認証部14aによる認証を行うタイミングを決定し、読み取り部153および比較部154に伝達する機能を有する。

【0119】

読み取り部153は、タイミング決定部152から認証部14aによる認証を行うタイミングが通知されると、読み取りコマンドを生成して記憶装置2に向けて送信する。読み取り部153から発行される読み取りコマンドは、記憶装置2の固定位置から固定値を読み出すためのコマンドである。また、当該読み取りコマンドに応じて記憶装置2から得られた値に基づいて認証値情報156を生成し、RAM151に転送する。

【0120】

比較部154は、タイミング決定部152から認証部14aによる認証を行うタイミングが通知されると、時間tだけ待機した後、基準値145をROM140aから取得するとともに、その時点で認証値情報156が生成されていればRAM151から認証値情報156を取得する。さらに、比較部154は、基準値145と認証値情報156の値とを比較し、その比較結果(一致・不一致)に基づいて比較結果情報157を生成し、RAM151に転送する。

【0121】

判定部155は、比較結果情報157に基づいて、記憶装置2の真偽を判定し、その判定結果を制御部10に伝達する。

【0122】

なお、第2の実施の形態における認証部14aによる認証方法は、第1の実施の形態における認証方法と同様に実現できるため、説明を省略する。

【0123】

このように第2の実施の形態における情報処理システム100は、情報処理装置1aを備えることにより、第1の実施の形態における情報処理システム100と同様の効果を得ることができる。

【0124】

また、情報処理装置1aは、インターフェース部13に装着された記憶装置2の真偽を判定するためのプログラム149を記憶するROM140aを備えることにより、記憶装置2のプログラム3,9との独立を確保しつつ、認証を行うことができる。すなわち、第1の実施の形態における情報処理装置1のように認証部14をハードウェア回路で実現する場合に比べて、コストを抑制できる。

【0125】

<3. 第3の実施の形態>

第1の実施の形態では、制御部10のハードウェア構成と、認証部14のハードウェア構成とが別々(独立)に設けられていた。しかし、記憶装置8に格納されているプログラム9(RAM17に転送されるライブラリ)の影響を受けることなく認証が行われるならば、これらの構成は一部兼用されてもよい。

【0126】

図7は、第3の実施の形態における情報処理装置1bの制御部10bおよび認証部14bを示す図である。

【0127】

第3の実施の形態における情報処理装置1bは、制御部10の代わりに制御部10bを備えるとともに、認証部14の代わりに認証部14bを備える点が、第1の実施の形態における情報処理装置1と異なっている。以下の説明では、第1の実施の形態と同様の構成については同符号を付し、適宜説明を省略する。

【0128】

制御部10bは、CPU15の他に、ROM16b、RAM17bおよびコマンド発行回路18を備えている。ROM16bは第1の実施の形態におけるROM16と同様にプログラム4を格納するとともに、基準値145を格納している。

【0129】

また、RAM17bは、第1の実施の形態におけるRAM17の機能に加えて、記憶装置2から受信した値を受信値148として格納する機能を有している。すなわち、RAM17bは、第1の実施の形態における受信バッファ147の機能を有している。

【0130】

コマンド発行回路18は、CPU15からの制御に応じて、CPU15によって指定されたコマンドを生成し、当該コマンドを示すコマンド信号をインターフェース部13に伝達する。すなわち、本実施の形態におけるCPU15はコマンド信号の生成を行わず、コマンド信号を生成するための専用のハードウェアであるコマンド発行回路18を制御してコマンド信号を生成させる。このように、専用のハードウェアでコマンド信号を生成するこにより、情報処理装置1bはコマンド信号を発行する速度が向上する。

【0131】

また、コマンド発行回路18は、認証部14b(タイミングジェネレータ141b)から指定されたコマンドを、CPU15に指定された場合と同様に生成し、当該コマンドを示すコマンド信号をインターフェース部13に伝達する機能も有している。ただし、認証部14bがコマンド発行回路18に指定するコマンドは読み取りコマンドに限定されており、かつ、当該読み取りコマンドに含まれるアドレス(値を読み出す記憶装置2の位置を示す)は、第1の実施の形態と同様に「固定位置(固定値が格納されている位置)」に限定されている。

【0132】

なお、コマンド発行回路18からインターフェース部13に伝達されたコマンド信号は記憶装置2に向けて送信される。そして、記憶装置2の制御部によって解析され、当該コマンドが記憶装置2において実行される。

【0133】

本実施の形態における認証部14bは、タイミングジェネレータ141b、遅延回路142および比較回路144bを備えている。

【0134】

タイミングジェネレータ141bは、第1の実施の形態におけるタイミングジェネレータ141と同様に、認証を行うタイミングを決定して、タイミング信号を遅延回路142に伝達する。また、タイミング信号を出力するのと同時に、制御部10bのコマンド発行回路18に、記憶装置2の固定位置に格納されている固定値を読み出すためのコマンドを発行するように、指定信号を伝達する。この指定信号には、発行するべきコマンドが読み取りコマンドであることを示す信号と、読み出す固定値の格納位置(固定位置)を示す信号とが含まれている。

【0135】

遅延回路142は、タイミングジェネレータ141bからのタイミング信号を時間tだけ遅延させてから、遅延信号を比較回路144bに伝達する。

【0136】

比較回路144bは、遅延回路142から遅延信号が入力されると、ROM16bから基準値145を取得するとともに、RAM17bから受信値148を認証値として取得する。そして、取得した基準値145と認証値とを比較し、比較結果をCPU15に伝達する。

【0137】

なお、第3の実施の形態における情報処理装置1bによる認証方法は、第1の実施の形態における認証方法と同様に実現できるため、説明を省略する。

【0138】

以上のように、第3の実施の形態における情報処理装置1bのように、制御部10bが備えるROM16b、RAM17bおよびコマンド発行回路18を、第1の実施の形態におけるROM140、読み取り部143(コマンド発行回路146および受信バッファ147)と同様に使用することによって、第1の実施の形態と同様の効果を得ることができる。

【0139】

情報処理システム100として、情報処理装置が専用のゲーム機本体であり、記憶装置が当該ゲーム機本体用のゲームプログラムを格納したメモリカードである場合を想定すると、情報処理装置において最も利用頻度の高いプログラムは記憶装置に格納されていることになる。このような情報処理システム100では、情報処理装置が汎用コンピュータであってゲームのみならず様々な情報を処理する場合に比べて、記憶装置へのアクセス頻度が高く、記憶装置へのコマンドの発行頻度が高いという事情がある。

【0140】

このようなゲーム機本体では、頻度の高い処理(記憶装置へのアクセス処理)を高速化させるために、専用のコマンド発行回路を備えた構成が採用される。したがって、情報処理装置1bのように、制御部10bがハードウェアとしてのコマンド発行回路18を既に備えている場合には、認証部14bのように、当該コマンド発行回路18を認証に使用してハードウェアを兼用することにより、コストを抑制することができる。すなわち、本実施の形態における情報処理装置1bのように構成することは、情報処理装置として専用のゲーム機本体を想定した場合に、特に効果的である。

【0141】

<4. 第4の実施の形態>

上記実施の形態における情報処理システム100では、予め、情報処理装置1,1a,1bに基準値145を格納しておくとともに、記憶装置7の固定位置に基準値145と等しい値(固定値)を格納しておく必要があった。しかし、本発明はこのような構成に限定されるものではない。

【0142】

図8は、第4の実施の形態における情報処理装置1cの制御部10cを示す図である。

【0143】

第4の実施の形態における情報処理装置1cは、制御部10bの代わりに制御部10cを備える点が、第3の実施の形態における情報処理装置1bと異なっている。以下の説明では、第3の実施の形態と同様の構成については同符号を付し、適宜説明を省略する。

【0144】

第4の実施の形態における制御部10cは、第3の実施の形態におけるROM16bの代わりに第1の実施の形態におけるROM16を備えている。

【0145】

また、制御部10cは、第3の実施の形態におけるRAM17bの代わりにRAM17cを備えている。制御部10cでは、コマンド発行回路18が発行した読み取りコマンドに応じて記憶装置2から受信された値が、RAM17cに受信値148として格納される。すなわち、RAM17cの所定の格納領域が、記憶装置2から取得されるデータ(値)の受信バッファとして使用される。さらに、RAM17cは遅延回路142cから伝達される複写信号(後述)に応じて、そのとき格納されている受信値148を複写して新たに基準値145として格納する機能も有している。

【0146】

認証部14cのタイミングジェネレータ141cは、認証を行うか否かを判定するための所定の条件(以下、「第1条件」と称する)を検出して、第1タイミング信号を生成し、遅延回路142cに出力する。本実施の形態における第1条件は、第1の実施の形態においてタイミングジェネレータ141が認証を行うか否かを判定するために検出する条件と同じ条件とするが、もちろんこれに限定されるものではない。本実施の形態における第1条件は、制御部10cの動作を妨害しないタイミングを決定するものであればどのような条件が選択されてもよい。

【0147】

また、タイミングジェネレータ141cは、比較を行うための所定の条件(以下、「第2条件」と称する)を検出して、第2タイミング信号を生成して遅延回路142cに出力する。第2条件については後述する。

【0148】

さらに、タイミングジェネレータ141cは、第1タイミング信号または第2タイミング信号を遅延回路142cに出力した場合には、当該出力と同時に、記憶装置2の固定位置に格納されている固定値を読み出すためのコマンドを発行するように、制御部10cのコマンド発行回路18に指定信号を伝達する。この指定信号には、発行するべきコマンドが読み取りコマンドであることを示す信号と、読み出す固定値の格納位置(固定位置)を示す信号とが含まれている。ただし、指定信号は固定の信号であり、状況に応じて変化することのない信号である。

【0149】

なお、本実施の形態では、タイミングジェネレータ141cが直接指定信号をコマンド発行回路18に出力するように説明するが、例えば、タイミングジェネレータ141cが指定信号を出力するすべきタイミングだけを割り込み信号等でCPU15に通知し、これに応じて、CPU15が指定信号を生成してコマンド発行回路18に出力するように構成してもよい。ただし、この場合のCPU15の動作は、ライブラリ(プログラム9の一部)に従って実現されるものでないことが好ましい。例えば、タイミングジェネレータ141cから通知を受けた場合には、プログラム4に含まれるライブラリによってCPU15が指定信号を出力するように構成することが好ましい。

【0150】

遅延回路142cは、入力された第1タイミング信号を所定の時間tだけ遅延させることにより複写信号を生成し、制御部10cに伝達する。先述のように、複写信号が伝達されると、制御部10cのRAM17cにおいて、そのときRAM17cに格納されている受信値148が新たに基準値145として格納される。すなわち、詳細は後述するが、遅延回路142cが複写信号を制御部10cに伝達することにより、第4の実施の形態における情報処理装置1cにおいて、基準値145を格納する工程が行われる。なお、第1タイミング信号に応じて生成される複写信号は、比較を行うための前段階として、基準値145を格納するタイミングを決定するための信号であるため、比較回路144bには伝達されない。

【0151】

また、遅延回路142cは、入力された第2タイミング信号を所定の時間tだけ遅延させることにより遅延信号を生成し、比較回路144bに伝達する。第2タイミング信号に応じて生成される遅延信号は、比較回路144bによる比較(認証)を実行させる信号であるため、制御部10cには伝達されない。

【0152】

以上が第4の実施の形態における情報処理装置1cの構成および機能の説明である。次に、情報処理装置1cを用いた情報処理システム100における認証方法を説明する。

【0153】

図9および図10は、第4の実施の形態における認証方法を示す流れ図である。

【0154】

なお、第1の実施の形態では、図9および図10に示す各工程が実行される前に、記憶装置7の固定位置に固定値(変更されない値であればよい)を格納する工程が既に実行されているものとする。また、図9に示すステップS21,S22,S23,S29の各工程は、図4に示すステップS1,S2,S3,S11の各工程とほぼ同様の工程であるため、ここでは説明を省略する。

【0155】

第1条件が満たされたことを検出し、認証を行うと判定すると(ステップS23においてYes)、タイミングジェネレータ141cは第1タイミング信号を遅延回路142cに伝達する。また、この第1タイミング信号を出力すると同時に、タイミングジェネレータ141cは制御部10cのコマンド発行回路18に指定信号を伝達する。この指定信号に応じて、コマンド発行回路18が記憶装置2に対して読み取りコマンドを発行することにより、読み出し要求を行う(ステップS24)。

【0156】

ステップS24において発行される読み取りコマンドには、記憶装置2において、固定値が格納された固定位置を示す情報が含まれている。したがって、この読み取りコマンドに応じて、記憶装置2の記憶部の固定位置から値(固定値)が読み出され、記憶装置2のバッファに格納され、インターフェース部13を介してRAM17cに格納される。

【0157】

情報処理装置1cの認証部14cは、遅延回路142cが第1タイミング信号を遅延させることによって時間tが経過するまで待機しつつ(ステップS27)、その間に、記憶装置2から固定値を受信したか否かを監視する(ステップS25)。時間t内に、ステップS24における読み出し要求に対する値を記憶装置2から受信すると、その値が受信値148としてRAM17cに格納される(ステップS26)。

【0158】

記憶装置2として、正規品の記憶装置7が装着されていた場合、時間T<時間tであるから、記憶装置7はステップS24の読み出し要求に対する値を時間t内に記憶部から読み出してバッファに格納することが可能である。したがって、記憶装置2として、正規品の記憶装置7が装着されていた場合には、読み出し要求によって要求された値が、ステップS26によって正しくバッファに格納される。すなわち、記憶装置2のレイテンシが時間t内であれば、ステップS26が実行されることにより所望した固定値が受信値148として格納される。

【0159】

一方、記憶装置2として、不正規品の記憶装置8が装着されていた場合、時間t<時間TXであるから、記憶装置8はステップS24の読み出し要求に対する値を時間t内に読み出してバッファに格納することができない。また、認証部14cは記憶装置2から転送されたライブラリから独立して動作しているため、例え記憶装置8が装着されている場合でも、ステップS24における読み出し要求の前に、プレ読み出し処理を行うことができない。したがって、記憶装置8は、例え固定値を正確にコピーして記憶部に格納していたとしても、当該固定値をバッファに格納する処理が間に合わず、かつ、予め格納しておくこともできない。したがって、記憶装置8は、ステップS24の読み出し要求に対して、値の保証されない、バッファ上の残余のデータを受け渡すこととなり、これがRAM17cに受信値148として格納される。すなわち、記憶装置2のレイテンシが時間t内でなければ、所望した固定値が受信値148として格納されない。

【0160】

タイミングジェネレータ141cが指定信号を伝達してから時間tが経過すると(ステップS27においてYes)、遅延回路142cが複写信号を生成して、当該複写信号を制御部10cとタイミングジェネレータ141cとに出力する。

【0161】

制御部10cは、この複写信号に応じて、そのときRAM17cに格納されている受信値148を、新たに基準値145としてRAM17cに格納する(ステップS28)。

【0162】

このように本実施の形態における情報処理システム100では、認証を行うときには、少なくとも認証値を取得するための読み出し要求(後述するステップS32)が実行される前に、ステップS28によって基準値145の格納が行われる。

【0163】

なお、ステップS24における読み出し要求に対して正常に読み出しが行われ、記憶装置2に格納されていた固定値が正常に受信値148として格納されていれば、ステップS28によって基準値145は固定値と等しい値となる。一方、ステップS24における読み出し要求に対して正常な読み出しが行われず、記憶装置2に格納されていた固定値が正常に受信値148として格納されていなければ、ステップS28が実行されることによって基準値145は保証されない値(一般に固定値と異なる値)となる。

【0164】

複写信号を受け取ることにより、タイミングジェネレータ141cは、制御部10cにおいて認証用の基準値145のRAM17cへの格納が行われたことを検出し、比較を行うタイミングを監視する状態となる(ステップS31)。

【0165】

なお、図示の都合上、図9および図10では、ステップS24ないしS28およびステップS31ないしS38が実行されている間、ステップS29(プログラムの実行)が実行されていないかのように示している。しかし、ステップS24ないしS28およびステップS31ないしS38の各工程は制御部10cとは独立して動作する認証部14cの動作であり、ステップS29は制御部10cの動作である。したがって、ステップS24ないしS28およびステップS31ないしS38の各工程が認証部14cによって実行されている間においても、制御部10cはプログラムの実行を行うことが可能である。本実施の形態では、ステップS24ないしS28およびステップS31ないしS38の各工程と、ステップS29の工程とは、適宜、並行して実行されており、ステップS31によって認証部14cが待機状態にある間もプログラムの実行(ステップS29)は行われている。

【0166】

情報処理システム100では、正常に読み出しが行われなかった(読み出しが間に合わなかった)場合であっても、何らかの値が取得される。この値は、そのときたまたまバッファ等に残留していた値であり、一般に、それまでの処理で読み出された値である。したがって、基準値145として読み出した値(固定値とは限らない)が、RAM17cに受信値148として残留していたり、記憶装置2のバッファに残留している間に認証値を取得しようとすると、読み出しに失敗しているにも関わらず、認証に成功する事態を招くおそれがある。

【0167】

RAM17cは情報処理装置1c側の構成であるため、RAM17c上の受信値148は、第1の実施の形態における受信バッファ147のように、適当なタイミングで初期値によって上書きすることも可能である。例えば、ステップS28を実行して受信値148を基準値145として格納した後に、受信値148を初期値で上書きしておく等が考えられる。しかし、一般に、記憶装置2のバッファ上に残留する値を情報処理装置1cから直接クリアすることはできない。

【0168】

そこで、タイミングジェネレータ141cは、制御部10cがステップS29を実行する過程で、これらの値が他の値で更新されるタイミングを検出してから、認証値の取得を行うようにステップS31において第2条件を監視している。

【0169】

本実施の形態における第2条件は、CPU15からコマンド発行回路18に対する読み取り要求がされたこととする。この読み取り要求はプログラム3(プログラム9)によって要求されるため正常に実行される。したがって、プログラム3(プログラム9)が所望する値(一般に固定値とは異なる値)が記憶装置2から取得され、この値に受信値148が更新される。またこのときには、記憶装置2のバッファにもこの値が格納されていることが期待される。

【0170】

なお、第2条件としては、RAM17cに格納されている受信値148と基準値145との不一致検出等を第2条件としてもよい。すなわち、現実に受信値148が他の値でクリアされたことを検出してから認証値の取得を行うようにしてもよい。また、詳細は省略したが、第2条件には、当然ながら、CPU15によるプログラムの実行を妨げないことも含まれる。

【0171】

ステップS31によって認証部14cが待機状態にあるときに、制御部10cが記憶装置2に対して読み取り要求を行うと、タイミングジェネレータ141cは、第2タイミング信号を遅延回路142cに出力するとともに、指定信号をコマンド発行回路18に出力する。この指定信号により、コマンド発行回路18が記憶装置2に対して読み取りコマンドを発行し、固定位置に格納されている固定値の読み出し要求を行う(ステップS32)。

【0172】

なお、ステップS33ないしS38の各工程は、図4に示した第1の実施の形態におけるステップS5ないしS10の各工程とほぼ同じであるため説明を省略する。

【0173】

以上のように、第4の実施の形態における情報処理システム100においても上記実施の形態と同様の効果を得ることができる。

【0174】

また、記憶装置2の所定の位置(固定位置)に格納された値を読み出し(ステップS24)、ステップS24において読み出された値を基準値145としてRAM17cに格納する(ステップS28)。そして、認証値を取得する際にも、同じく固定位置からの読み出し要求を行って(ステップS32)、認証値を取得する(ステップS36)。このように構成することによって、記憶装置7および情報処理装置1cに共通の固定値を予め格納しておく必要がない。

【0175】

なお、本実施の形態では、ステップS23において認証を行うと判定した場合に、必ず、ステップS24が実行され基準値145の取得が実行されるように構成した。しかし、認証を複数回行う場合(ステップS37を1回実行しただけで、真偽を判定しない場合)であっても、基準値145の取得は一度だけで充分である。したがって、このような場合には、例えば、基準値145を取得する処理を初期設定(ステップS22)において実行するように構成してもよい。

【0176】

<5. 第5の実施の形態>

第4の実施の形態では、基準値145となる値の読み出しを、独立して動作する認証部14cによって実行し、これによって読み出され格納された値は、当該読み出し要求を行ってから所定の時間内に記憶装置2から得られた値である。しかし、基準値145は、装着されている記憶装置2が記憶装置7であるか記憶装置8であるかに関わらず、必ず、正しい固定値を読み出して格納するように構成してもよい。

【0177】

図11は、第5の実施の形態における情報処理装置1dの認証部14dを示す図である。第5の実施の形態における情報処理装置1dは、認証部14cの代わりに認証部14dを備える点が第4の実施の形態における情報処理装置1cと異なっている。

【0178】

第5の実施の形態における認証部14dは、タイミングジェネレータ141d、遅延回路142、比較回路144bおよびバッファ158を備えている。

【0179】

タイミングジェネレータ141dは、制御部10cがプログラムを実行する過程で生じる記憶装置2への読み出し要求(読み取りコマンド)を監視し、読み取りコマンドを検出した場合には、当該読み取りコマンドに含まれるアドレス(当該読み出し要求により取得される値の格納位置)を取得してバッファ158にアドレス値159として格納する。そして、検出した読み取りコマンドに応じて、記憶装置2から得られた値を基準値145として格納するようにRAM17cを制御する。

【0180】

また、タイミングジェネレータ141dは、認証を行うか否かを判定し、認証を行うと判定した場合には、タイミング信号を遅延回路142に出力する。なお、本実施の形態におけるタイミングジェネレータ141dは、第4の実施の形態における第2条件と同様の条件によって認証を行うか否かを判定するが、もちろんこれに限定されるものではない。

【0181】

さらに、タイミングジェネレータ141dは、タイミング信号を出力すると同時に、バッファ158に格納されているアドレス値159を取得して、当該アドレス値159で示される位置から値を読み出すよう指定信号を生成し、コマンド発行回路18に出力する。すなわち、本実施の形態におけるタイミングジェネレータ141dは指定信号に含めるアドレスとして任意の値を指定できるように構成されている。

【0182】

図11に示すように、第5の実施の形態における認証部14dは、遅延回路142cの代わりに、第1および第3の実施の形態における認証部14,14bと同様の遅延回路142を備えている。すなわち、本実施の形態における遅延回路142は、タイミングジェネレータ141dからのタイミング信号を時間tだけ遅延させることにより遅延信号を生成し、比較回路144bに出力する。

【0183】

以上が本実施の形態における情報処理装置1dの構成および機能の説明である。次に、第5の実施の形態における情報処理システム100の認証方法について説明する。

【0184】

図12および図13は、第5の実施の形態における認証方法を示す流れ図である。なお、図12に示すステップS41,S42,S47,S48の各工程は、図9に示す第4の実施の形態におけるステップS21,S22,S23,S29の各工程とほぼ同じ工程であるので説明を省略する。ただし、ステップS47においてYesと判定されるための条件は、後述するステップS46が既に実行されていることも条件となる。

【0185】

認証部14d(タイミングジェネレータ141d)が、制御部10cがステップS48を実行(プログラムを実行)する過程で生じる読み出し要求を検出すると、読み取りコマンドからアドレスを取得して、バッファ158にアドレス値159として格納する(ステップS44)。

【0186】

次に、タイミングジェネレータ141dは、受信値148がRAM17cに格納されるまで待機する(ステップS45)。

【0187】

制御部10cがプログラムを実行する過程で生じる読み出し要求に対しては、例え記憶装置8が装着されている場合であっても、当該読み出し要求によって要求された値が、当該読み出し要求によって指定されるアドレスから読み出される。したがって、記憶装置2の当該アドレスに格納されている値が受信値148となる。

【0188】

ステップS43で検出した読み出し要求に対して、記憶装置2から得られた値が受信値148としてRAM17cに格納されると、格納された受信値148を基準値145としてRAM17cに新たに格納する(ステップS46)。これにより、認証用の基準値145の格納が完了する。

【0189】

ステップS46が完了した後、ステップS47においてYesと判定されると、タイミングジェネレータ141dはタイミング信号を遅延回路142に出力する。これと同時に、タイミングジェネレータ141dはバッファ158からアドレス値159を取得して、指定信号を生成し、コマンド発行回路18に出力する。この指定信号に応じて、コマンド発行回路18が読み取りコマンドを記憶装置2に発行することにより読み出し要求を行う(ステップS51)。

【0190】

ステップS51において発行される読み取りコマンドには、基準値145となった値を読み出したときのアドレス値159が指定されているため、当該読み出し要求に対して、正常に読み出しが行われれば、基準値145となっている値と同じ値が記憶装置2から得られるはずである。一方、記憶装置2のレイテンシが低く、ステップS51における読み出し要求に対する読み出しが間に合わなかった場合には、基準値145となった値を正しく読み出すことができず、基準値145と異なる値が受信値148として記憶装置2から得られるはずである。

【0191】

以下、ステップS52ないしS57の各工程は、図10に示す第4の実施の形態におけるステップS33ないしS38の各工程と同様であるため説明を省略する。

【0192】

以上のように、第5の実施の形態における情報処理装置1dのように構成しても、上記実施の形態と同様の効果を得ることができる。

【0193】

また、本実施の形態では、基準値145を取得する際には、制御部10cがプログラムを実行する過程で生じる読み出し要求を検出して、当該読み出し要求における受信値148を基準値145として格納しておくとともに、当該読み出し要求におけるアドレスを認証値を取得する際のアドレスとして格納しておく。これにより、第4の実施の形態における認証方法のように、認証を行うための読み出し要求(ステップS24,S32)を2回行う必要がなくなる。また、認証に用いる値の格納位置を限定する必要もない。

【0194】

<6. 第6の実施の形態>

上記実施の形態では、時間t(認証のための読み取りコマンドを発行してから基準値と認証値との比較を行うまでの時間を決定する際の基準となる時間)は一定であった。しかし、認証を行うたびにこれを変更するように構成してもよい。

【0195】

第6の実施の形態における情報処理装置1は、基準値145と認証値との比較結果と、このときの時間tとを関連付けて認証履歴情報として保存する。そして、認証を行うたびに、認証履歴情報を参照しつつ、時間tを変更する。すなわち、第6の実施の形態における情報処理システム100では、基準値145と認証値とが不一致であっても、直ちに、記憶装置2が記憶装置8であると判定することはない。

【0196】

例えば、時間tの初期値を、時間t<時間Tを満たす値から認証を開始し、認証を行うたびに、順次、所定値Δtだけ時間tの値を増加させる。このように構成すると、記憶装置2のレイテンシ(時間τ)<時間tとなった時点で、基準値145と認証値とが一致するようになる。

【0197】

すなわち、第6の実施の形態における情報処理装置1は、時間tを変更することによって記憶装置2のレイテンシ(時間τ)を検出する機能を有する。そして、τ≒Tであれば、装着されている記憶装置2が正規品の記憶装置7であると判定する。一方、τ≠Tであれば、装着されている記憶装置2が不正規品の記憶装置8であると判定する。

【0198】

上記実施の形態における情報処理装置1では、記憶装置8のレイテンシ(時間TX)をある程度、予測して時間tを決定する必要があった。しかし、第6の実施の形態における情報処理装置1は、不正業者によって製造される記憶装置8のレイテンシが不明であっても、時間tを変更することによって、記憶装置7と記憶装置8との性能差を検出して、これらを見分ける(認証する)ことが可能である。

【0199】

<7. 変形例>

以上、本発明の実施の形態について説明してきたが、本発明は上記実施の形態に限定されるものではなく様々な変形が可能である。

【0200】

例えば、第2の実施の形態における認証部14aは、制御部10とハードウェアが兼用されてもよい。すなわち、プログラム4がマイクロプログラムとしてのプログラム149を含んでおり、CPU15が、RAM17を一時的なワーキングエリアとして使用しつつ、ROM16に格納されたプログラム4(プログラム149)に従って動作することにより、タイミング決定部152、読み取り部153、比較部154および判定部155に相当する機能ブロックが実現されていてもよい。その場合には、さらにハードウェア構成を減らすことができるため、情報処理装置1の製造コストを抑制できる。

【0201】

また、第6の実施の形態における情報処理装置1において、時間tの初期値を、時間T,TX<時間tを満たす値から認証を開始し、認証を行うたびに(比較結果が不一致となるたびに)、順次、所定値Δτだけ時間tの値を減少させてもよい。このように構成した場合、時間t<時間τとなった時点で、基準値145と認証値とが一致しなくなり、記憶装置2のレイテンシを検出することができる。

【0202】

また、上記実施の形態に示した各工程はあくまでも例示であって、これに限定されるものではない。例えば、同様の効果が得られるのであれば、各工程における処理内容や各工程の順序が適宜変更されてもよい。

【図面の簡単な説明】

【0203】

【図1】本発明に係る情報処理システムを示す図である。

【図2】第1の実施の形態における情報処理装置1の構成を示す図である。

【図3】第1の実施の形態における認証部を示す図である。

【図4】第1の実施の形態における認証方法を示す流れ図である。

【図5】第2の実施の形態における情報処理装置の認証部を示す図である。

【図6】第2の実施の形態における認証部が備える機能ブロックをデータの流れとともに示す図である。

【図7】第3の実施の形態における情報処理装置の制御部および認証部を示す図である。

【図8】第3の実施の形態における情報処理装置の制御部および認証部を示す図である。

【図9】第4の実施の形態における認証方法を示す流れ図である。

【図10】第4の実施の形態における認証方法を示す流れ図である。

【図11】第5の実施の形態における情報処理装置の認証部を示す図である。

【図12】第5の実施の形態における認証方法を示す流れ図である。

【図13】第5の実施の形態における認証方法を示す流れ図である。

【符号の説明】

【0204】

1,1a,1b,1c,1d 情報処理装置

10,10b,10c 制御部

100 情報処理システム

11 操作部

12 表示部

13 インターフェース部

14,14a,14b,14c,14d 認証部

15,150 CPU

16,16b,140,140a ROM

17,17b,17c,151 RAM

141,141b,141c,141d タイミングジェネレータ

142,142c 遅延回路

143,153 読み取り部

144,144b 比較回路

145 基準値

18,146 コマンド発行回路

147 受信バッファ

148 受信値

152 タイミング決定部

154 比較部

155 判定部

156 認証値情報

157 比較結果情報

158 バッファ

159 アドレス値

2,7,8 記憶装置

3,4,9 プログラム

【技術分野】

【0001】

本発明は、着脱自在に装着される記憶装置を情報処理装置において認証する技術に関する。

【背景技術】

【0002】

ゲーム機本体(情報処理装置)にゲームプログラムを格納したメモリカード(記憶装置)を装着して、ゲーム機本体において当該ゲームプログラムを実行するような情報処理システムが知られている。このようなシステムでは、不正にコピーされたゲームプログラムが不正に使用されることを防止する必要がある。したがって、従来より、様々なセキュリティ技術が提案されており、例えば、そのようなセキュリティ技術が特許文献1に記載されている。

【0003】

【特許文献1】特開2007−133892号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところが、一般に、ソフトウェアで実現されるセキュリティ機能は、ゲームプログラムとともに容易にコピーされ回避されるという問題があり、ハードウェアで実現されるセキュリティ機能は、システム全体のコスト上昇を招くという問題があった。

【0005】

本発明は、上記課題に鑑みなされたものであり、システム全体のコスト上昇を抑制しつつ、記憶装置の認証を行うことを目的とする。

【課題を解決するための手段】

【0006】

上記の課題を解決するため、請求項1の発明は、記憶装置に格納されたプログラムを実行する情報処理装置であって、記憶装置が着脱自在に装着されるインターフェース手段と、前記インターフェース手段に装着された記憶装置に格納されているプログラムを実行する制御手段と、前記プログラムと独立して動作し、前記インターフェース手段に装着された記憶装置からのデータの読み出し時間に基づいて前記記憶装置の真偽を判定する認証手段とを備えることを特徴とする。

【0007】

また、請求項2の発明は、請求項1の発明に係る情報処理装置であって、前記認証手段は、認証用の基準値を格納する記憶部と、前記インターフェース手段に装着された記憶装置に対して読み出し要求を行い、前記読み出し要求に応じて前記記憶装置から得られた値を格納する読み出し部と、前記読み出し部に格納されている値を、前記読み出し部による読み出し要求がされてから所定の時間内に認証値として取得し、前記記憶部に記憶されている基準値と前記認証値とを比較する比較手段とを備え、前記認証手段は、前記比較手段の比較結果に応じて前記記憶装置の真偽を判定することを特徴とする。

【0008】

また、請求項3の発明は、請求項1または2の発明に係る情報処理装置であって、前記認証手段は、前記インターフェース手段に装着された記憶装置の真偽を判定する論理回路を備えることを特徴とする。

【0009】

また、請求項4の発明は、請求項1または2の発明に係る情報処理装置であって、前記認証手段は、前記インターフェース手段に装着された記憶装置の真偽を判定するための認証プログラムを格納するROMを備えることを特徴とする。

【0010】

また、請求項5の発明は、装着された記憶装置に格納されたプログラムを情報処理装置において実行する情報処理システムであって、前記情報処理装置は、記憶装置が着脱自在に装着されるインターフェース手段と、前記インターフェース手段に装着された記憶装置に格納されているプログラムを実行する制御手段と、前記プログラムと独立して動作し、前記インターフェース手段に装着された記憶装置からのデータの読み出し時間に基づいて前記記憶装置の真偽を判定する認証手段とを備えることを特徴とする。

【0011】

また、請求項6の発明は、プログラムを格納した記憶装置が着脱自在に装着される情報処理装置において前記記憶装置を認証する認証方法であって、(a)前記情報処理装置が備える記憶部に認証用の基準値を格納する工程と、(b)前記プログラムから独立して動作する読み取り部によって前記記憶装置からの値の読み出し要求を行う工程と、(c)前記(b)工程において前記記憶装置から読み出された値を受信バッファに格納する工程と、(d)前記(b)工程における読み出し要求を行ってから所定の時間内に、前記受信バッファに格納されている値を認証値として取得する工程と、(e)前記(a)工程において前記記憶部に格納された基準値と前記(d)工程において取得された認証値とを比較する工程と、(f)前記(e)工程における比較結果に基づいて前記記憶装置の真偽を判定する工程とを有し、前記所定の時間は前記記憶装置が真である場合の読み出し時間に応じて決定されることを特徴とする。

【0012】

また、請求項7の発明は、請求項6の発明に係る認証方法であって、(g)少なくとも前記(b)工程を実行する前に、前記記憶装置の固定位置に固定値を格納する工程をさらに有し、前記(a)工程において前記記憶部は前記固定値と同じ値を前記基準値として格納し、前記(b)工程における読み出し要求は前記(g)工程において前記固定値を格納した前記固定位置から値を読み出す要求であることを特徴とする。

【0013】

また、請求項8の発明は、請求項6の発明に係る認証方法であって、前記(a)工程は、(a-1)前記記憶装置の所定の位置に格納された値を読み出す工程と、(a-2)前記(a-1)工程において読み出された値を基準値として前記記憶部に格納する工程とを有し、前記(b)工程における読み出し部は、前記所定の位置からの読み出し要求を行うことを特徴とする。

【0014】

また、請求項9の発明は、請求項8の発明に係る認証方法であって、前記(a-1)工程における値の読み出しは、前記読み出し部によって実行され、前記(a-1)工程において読み出された値は、前記読み出し部による読み出し要求を行ってから前記所定の時間内に前記記憶装置から得られた値であることを特徴とする。

【0015】

また、請求項10の発明は、請求項6の発明に係る認証方法であって、(h)前記記憶装置から値の読み出しが行われたことを検出して、そのとき読み出された値と前記値の前記記憶装置における格納位置とを取得する工程をさらに有し、前記(a)工程における前記記憶部は、前記(h)工程において取得された値を前記基準値として格納し、前記(b)工程における前記読み出し部は、前記(h)工程において取得された格納位置からの読み出し要求を行うことを特徴とする。

【0016】

また、請求項11の発明は、請求項8ないし10のいずれかの発明に係る認証方法であって、前記(b)工程は、前記(a)工程が実行された後において、前記記憶装置から読み出される値が格納される受信バッファと前記記憶部とが参照され、前記受信バッファに格納されている値と、前記記憶部に格納されている基準値とが不一致であることが確認されてから実行されることを特徴とする。

【0017】

また、請求項12の発明は、請求項6ないし11のいずれかの発明に係る認証方法であって、(i)前記所定の時間を変更する工程をさらに有し、前記(b)工程は、前記(i)工程が実行されるたびに実行されることを特徴とする。

【発明の効果】

【0018】

請求項1ないし5に記載の発明では、記憶装置が着脱自在に装着されるインターフェース手段と、インターフェース手段に装着された記憶装置に格納されているプログラムを実行する制御手段と、プログラムと独立して動作し、インターフェース手段に装着された記憶装置からのデータの読み出し時間に基づいて記憶装置の真偽を判定する認証手段とを備えることにより、認証を容易に実現できる。

【0019】

請求項3に記載の発明では、インターフェース手段に装着された記憶装置の真偽を判定する論理回路を備えることにより、記憶装置との独立性が高く、改変される危険性も低いため、セキュリティが向上する。

【0020】

請求項4に記載の発明では、インターフェース手段に装着された記憶装置の真偽を判定するための認証プログラムを格納するROMを備えることにより、記憶装置のプログラムとの独立を確保しつつ、回路で実現する場合に比べてコストを抑制することができる。

【0021】

請求項6ないし12に記載の発明では、情報処理装置が備える記憶部に認証用の基準値を格納する工程と、プログラムから独立して動作する読み取り部によって記憶装置からの値の読み出し要求を行う工程と、記憶装置から読み出された値を受信バッファに格納する工程と、読み出し要求を行ってから所定の時間内に、受信バッファに格納されている値を認証値として取得する工程と、記憶部に格納された基準値と取得された認証値とを比較する工程と、比較結果に基づいて記憶装置の真偽を判定する工程とを有し、所定の時間は記憶装置が真である場合の読み出し時間に応じて決定されることにより、コストを抑制しつつ、認証を行うことができる。

【0022】

請求項7に記載の発明では、少なくとも認証を実行する前に、記憶装置の固定位置に固定値を格納するとともに、記憶部は固定値と同じ値を基準値として格納する。そして、認証のための読み出し要求は固定値を格納した固定位置から値を読み出す要求とすることにより、認証のための読み出しを行うタイミングにかかわらず、一回読み出すだけで、真偽判定が可能である。

【0023】

請求項8に記載の発明では、記憶装置の所定の位置に格納された値を読み出し、読み出された値を基準値として記憶部に格納し、当該所定の位置からの読み出し要求により取得された値と基準値とを比較することにより認証を行うことにより、記憶装置および情報処理装置に共通の固定値を予め格納しておく必要がない。

【0024】

請求項10に記載の発明では、記憶装置から値の読み出しが行われたことを検出して、そのとき読み出された値と当該値の記憶装置における格納位置とを取得し、取得した値を基準値として格納するとともに、取得された格納位置からの読み出し要求により認証のための認証値となる値を取得することにより、認証のための読み出しを一回行うだけで認証が可能である。また、記憶装置および情報処理装置に共通の固定値を予め格納しておく必要がない。

【0025】

請求項11に記載の発明では、基準値の取得が実行された後において、記憶装置から読み出される値が格納される受信バッファと記憶部とが参照され、受信バッファに格納されている値と、記憶部に格納されている基準値とが不一致であることが確認されてから認証を実行することにより、受信バッファに格納されている値がクリアされているか否かを確認してから認証を行うため、誤って認証に成功することが防止される。したがって、セキュリティレベルが向上する。

【0026】

請求項12に記載の発明では、所定の時間を変更する工程をさらに有し、当該所定の時間の変更が実行されるたびに認証を行うことにより、記憶装置のレイテンシを検出することができ、認証の確実性が向上する。

【発明を実施するための最良の形態】

【0027】

以下、本発明の好適な実施の形態について、添付の図面を参照しつつ、詳細に説明する。

【0028】

<1. 第1の実施の形態>

図1は、本発明に係る情報処理システム100を示す図である。図1に示すように、情報処理システム100は情報処理装置1および記憶装置7を備え、情報処理装置1に装着された記憶装置7に格納されたプログラム3を、情報処理装置1において実行するシステムとして構成されている。

【0029】

なお、図1に示す記憶装置8は、情報処理システム100における正規品である記憶装置7を模した模倣品(不正規品あるいは非ライセンス品)であり、記憶装置7に格納されているプログラム3に相当するプログラム9を格納している。詳細は後述するが、情報処理システム100は、正規品である記憶装置7と、不正規品である記憶装置8とを見分けて(真偽を判定して)、情報処理装置1がプログラム9を実行することのないように構成されている。

【0030】

また、記憶装置7の模倣品として製造される記憶装置8は、情報処理装置1に装着可能となることを意図してその形状等が設計されている。以下の説明において、記憶装置2とは、情報処理装置1に装着されている記憶装置7または記憶装置8であって、記憶装置7であるか記憶装置8であるかが未だ判定されていないもの(真偽不明の状態のもの)を指すものとする。

【0031】

また、図1において詳細を図示していないが、記憶装置7は、プログラム3を格納する記憶部と、記憶部へのアクセスを制御する制御部と、記憶部から読み出された値が一時的に格納されるバッファとを備えている。

【0032】

記憶装置7の制御部は、情報処理装置1から読み取りコマンドを受信すると、記憶部の指定位置(読み取りコマンドに含まれるアドレス値によって指定される位置)に格納されている値をバッファに格納する。そして、当該バッファに格納された値が、記憶装置7から読み出された値として情報処理装置1に転送される。

【0033】

記憶装置7の記憶部を構成する不揮発性の記憶素子は、情報処理システム100が保証する速度で読み出し可能な記憶素子である。以下の説明では、記憶装置7のレイテンシを「時間T」とする。

【0034】

一方、不正規品である記憶装置8もプログラム9を格納する記憶部と、記憶部へのアクセスを制御する制御部と、記憶部から読み出された値が一時的に格納されるバッファとを備えている。しかし、記憶装置8では、記憶部を構成する不揮発性の記憶素子として、安価な記憶素子が採用されている場合が多い。このような安価な記憶素子を用いた記憶装置8は、アクセス速度が遅い等、記憶装置7に比べてハードウェア性能が劣るものである。以下の説明では、記憶装置8のレイテンシを「時間TX」とし、T<TXであるとして説明する。

【0035】

図2は、第1の実施の形態における情報処理装置1の構成を示す図である。図2に示すように、情報処理装置1は、制御部10、操作部11、表示部12、インターフェース部13および認証部14を備え、これらの構成がバス配線19を介して互いに接続されている。このような構成により、情報処理装置1は、一般的なコンピュータとしての機能を有している。

【0036】

なお、情報処理装置1は、図2に示す構成の他に、大容量のデータを記憶するハードディスクや、音声を再生するスピーカ、紙媒体にデータを印刷するプリンタ等の各種ハードウェアを備えていてもよい。すなわち、情報処理装置1は、プログラム3あるいはプログラム4を実行することによって提供されるアプリケーションを実現するためのハードウェアを適宜備えている。

【0037】

制御部10は、各種データの演算を行うCPU15と、プログラム4が格納されたROM16と、CPU15の一時的なワーキングエリアとして使用されるRAM17とを備えている。図2において、便宜上、CPU15、ROM16およびRAM17はいずれも1つの装置から構成されているかのように図示しているが、もちろん複数の装置が協働してそれぞれを構成していてもよい。

【0038】

CPU15は、ROM16に格納されたプログラム4を実行するとともに、インターフェース部13に装着された記憶装置7に格納されているプログラム3を実行する。

【0039】

ROM16は、読み取り専用の不揮発性の記憶素子からなる記憶装置であり、先述のように、プログラム4が格納される。プログラム4としては、主にBIOSやOS等の基本プログラムが該当するが、もちろんこれに限定されるものではなく、アプリケーションプログラムが含まれていてもよい。本実施の形態における情報処理システム100では、プログラム4は情報処理装置1側において提供されるプログラムであり、例えば、記憶装置2から転送されるプログラム(プログラム3またはプログラム9)を含まないものとして説明する。

【0040】

RAM17は、比較的高速にデータの読み書きが可能な揮発性の記憶素子からなる記憶装置であり、CPU15によってアクセスされる。制御部10がプログラム3を実行する際には、プログラム3の一部又は全部がRAM17にロードされ、CPU15によって実行される。

【0041】

本実施の形態における情報処理システム100では、記憶装置7が情報処理装置1に装着されたときに(より詳しくはロード処理が実行されたときに)、プログラム3の一部であるライブラリ(関数)が情報処理装置1によって読み出されRAM17に格納される。そして、RAM17上に読み出されたライブラリをCPU15が使用しつつ、適宜、記憶装置7にアクセスすることによって、プログラム3が実行される。

【0042】

このようなアーキテクチャを採用することにより、情報処理装置1は、プログラム3の全部を記憶装置7に格納したままで実行する場合に比べて、記憶装置7へのアクセス回数を減らすことができ、プログラム3の実行速度を向上させることが可能となる。また、プログラム3に特化したライブラリを準備してプログラム3自体に含めておくことによって、プログラム3の実行効率が向上する。

【0043】

記憶装置8も、記憶装置7と同様に、情報処理装置1からのロード要求に応じて、格納しているプログラム9の一部であるライブラリを情報処理装置1に転送する。

【0044】

先述のように、記憶装置8の記憶部は、記憶装置7の記憶部よりもアクセス速度が遅い記憶素子で構成されている。以下、情報処理装置1から要求されたデータを記憶装置8が読み出す場合を例に、アクセス速度の遅い記憶素子を用いた記憶装置8が情報処理装置1において使用可能となる仕組みについて説明する。

【0045】

記憶装置8では、情報処理装置1からの読み出し要求に応じて制御部が記憶部からデータを読み出そうとしても、所定の時間内(情報処理装置1にデータを渡すときまで)に、記憶装置8のバッファに所望のデータを格納することができない。そして、記憶装置8のバッファへの格納が間に合わなかった場合、たまたまそのとき記憶装置8のバッファ上に格納されていた残余のデータが情報処理装置1に渡される。この残余のデータは、当該読み出し要求以前の処理で読み出されたデータであるため、一般に当該読み出し要求によって要求されているデータではない。したがって、記憶装置8に対して通常の読み出し要求を実行すると、情報処理装置1は誤ったデータを取得することとなり、所望したデータを得ることはできない。

【0046】

しかし、情報処理装置1から記憶装置8に対する読み出し要求は、記憶装置7に対する読み出し要求と同様に、予め情報処理装置1に転送されたライブラリを実行する形で実行される。

【0047】

そこで、プログラム9のライブラリでは、プログラム3における読み出し要求(通常の読み出し要求)を行う前段階として、当該読み出し要求で所望されるデータを予め記憶装置8のバッファに読み出しておく処理を実行するように、プログラム3のライブラリを改変している。以下、通常の読み出し処理の前段階として実行される処理を「プレ読み出し処理」と称する。

【0048】

より具体的には、記憶装置7からの読み出し処理を行うライブラリ(プログラム3におけるライブラリ)は、プログラム9では、記憶装置8に対するプレ読み出し処理と、それに続く読み出し処理とを行うライブラリとして書き換えられている。すなわち、当該ライブラリに、プレ読み出し処理を行う部分が、いわゆるパッチとして当てられたように、プログラム3が改変されている。

【0049】

情報処理システム100は、記憶装置2の装着後、瞬時に認証が完了するわけではない。そのため、記憶装置8に格納されているプログラム9も、記憶装置8が情報処理装置1に装着されたときに、先述のように、その一部がRAM17にロードされる。したがって、記憶装置7ではなく記憶装置8が装着された場合であっても、記憶装置8であることが判明するまでの間、制御部10(CPU15)は、情報処理システム100の設計者の意に反して、プログラム9の一部を実行することとなる。

【0050】

装着されている記憶装置2が記憶装置8であると認識していない情報処理装置1の制御部10が、RAM17に格納されているライブラリ(記憶装置8由来のライブラリ)を実行すると、まず、記憶装置8に対して、プレ読み出し処理を実行させる独自のコマンド(以下、「プレ読み出しコマンド」と称する)を発行することとなる。

【0051】

なお、このプレ読み出しコマンドには、引き続き実行される読み出し処理において所望されるデータの記憶装置8におけるアドレスが含まれている。このアドレスは、本来、記憶装置7のアドレスとして与えられるものであるが、本実施の形態では、記憶装置8が記憶装置7と同じアドレスに同じデータを格納するように設計されているものと想定しているため、そのままの値を用いる例で説明する。ただし、記憶装置8におけるデータの格納状況に応じて、例えば、記憶装置7におけるアドレスをオフセットさせて用いていてもよい。

【0052】

情報処理装置1からプレ読み出しコマンドを受信した記憶装置8の制御部は、当該コマンドに含まれるアドレスに基づいて、所望のデータを記憶装置8の記憶部から読み出して、記憶装置8のバッファに格納する。

【0053】

この間、情報処理装置1は、プレ読み出し処理に続く読み出し処理を開始することなく待機している。このような情報処理装置1側の待機時間は、プレ読み出し処理に、記憶装置8側の読み出し完了を確認する処理(例えばレディ・ビジー処理等)を含めるか、あるいは、記憶装置8のレイテンシ(時間TX)に応じて充分なウェイト処理を含める等によって容易に設けることができる。

【0054】

そして、記憶装置8のバッファに所望のデータが格納された時点で、引き続き、通常の読み出し処理が実行される。すなわち、情報処理装置1から読み出しコマンドが発行され、記憶装置8の制御部が当該コマンドに応じて、指定されたアドレスに格納されているデータを記憶部から読み出してバッファに格納する。

【0055】

先述のように、読み出し要求に対して、情報処理装置1には記憶装置8のバッファに格納されているデータが渡される。通常の読み出し要求がされたとき、既に実行されたプレ読み出し処理によって記憶装置8のバッファには所望のデータが格納されている。したがって、バッファに格納されているデータが、プレ読み出し処理で格納された残余のデータであるか、その後の読み出し処理で格納された所望のデータであるかに関わらず、結局、情報処理装置1は所望のデータを得ることができるのである。

【0056】

このように、記憶装置8は、プログラム3を改変したプログラム9を予め情報処理装置1に転送することにより、本来の情報処理装置1が保証するレイテンシ内でアクセスを完了する必要がないように構成されている。これによって、不正規品である記憶装置8の製造業者は、記憶装置8の記憶部としてアクセス速度の遅い記憶素子を採用して、製造コストを抑制している。

【0057】

図2に戻って、操作部11は、ボタン、キーボード、マウス、コントローラ、ジョイスティック、タッチパネル等の各種ハードウェアから構成されており、ユーザが情報処理装置1に対して指示を入力するために使用される。ユーザが操作部11を操作することにより指示を入力した際には、操作部11からバス配線19を介して制御部10(CPU15)に対してハードウェア割り込み信号が伝達される。

【0058】

表示部12は、例えば、液晶ディスプレイやCRT、ランプ、LED等であり、制御部10からの制御信号に応じて、各種データや状態を表示する。なお、表示部12としては、情報処理装置1にケーブル等で外部接続されるテレビ受像器であってもよい。

【0059】

インターフェース部13は、記憶装置7と接続されるコネクタ等から構成され、当該コネクタには記憶装置7が着脱自在に装着される。すなわち、インターフェース部13に記憶装置7が装着されることによって、情報処理装置1は記憶装置7との間でデータ通信が可能となり、情報処理装置1は記憶装置7を自らが備える記憶装置として使用することが可能となる。

【0060】

また、情報処理装置1に装着可能となることを意図し、記憶装置7の模倣品として製造される記憶装置8も同様にインターフェース部13に適合するように製造される。したがって、先述のように、インターフェース部13には記憶装置8を装着することも可能である。

【0061】

図3は、第1の実施の形態における認証部14を示す図である。本実施の形態における認証部14は、ROM140、タイミングジェネレータ141、遅延回路142、読み取り部143および比較回路144を備える。また、認証部14は、制御部10とは別に設けられる独立したハードウェア(論理回路)として構成されており、プログラム3(プログラム9)と独立して動作する。そして、認証部14は、インターフェース部13に装着された記憶装置2からのデータの読み出し時間に基づいて記憶装置2の真偽(記憶装置7であるか記憶装置8であるかの別)を判定する機能を有する。

【0062】

ROM140には認証用の基準値145が格納される。本実施の形態における基準値145は、例えば情報処理装置1の製造段階で予めROM140に格納される。すなわち、本実施の形態における基準値145は、情報処理装置1において一定の値(固定値)である。ROM140に格納された基準値145は、必要に応じて比較回路144によって読み出される。

【0063】

タイミングジェネレータ141は、コマンド発行回路146を駆動するタイミングを決定して、コマンド発行回路146にタイミング信号を出力する機能を有する。言い換えれば、タイミングジェネレータ141は、コマンド発行回路146に対して、コマンド発行の許可を与える。

【0064】

タイミングジェネレータ141からコマンド発行回路146に向けて出力されたタイミング信号は、同時に遅延回路142および受信バッファ147にも伝達される。タイミングジェネレータ141がタイミング信号を出力するタイミングを決定する手法は後述する。

【0065】

遅延回路142は、タイミングジェネレータ141から伝達されるタイミング信号を、所定の時間tだけ遅延させて比較回路144に向けて出力する回路である。以下、遅延回路142から比較回路144に向けて出力される信号を「遅延信号」と称する。

【0066】

本実施の形態における時間tは、記憶装置7のレイテンシ(時間T)に応じて予め決定されている固定の値である。時間tは、情報処理システム100の保証値として決定される値であるが、例えば記憶装置7のレイテンシが230マイクロ秒程度であれば、時間tはそれよりも大きい値(ただし大きすぎない値であって、例えば250マイクロ秒程度)に決定される。

【0067】

なお、時間tは、記憶装置8のレイテンシ(時間TX)よりも小さい値であることが好ましい。時間TXは不正規品である記憶装置8の性能に関するパラメータであるから、厳密には不知の値である。しかし、一般に供給されている安価な記憶素子を用いた場合、あるいは市場に流通している模倣品(記憶装置8)に基づいて、予め、ある程度の数値範囲として予測することは可能である。したがって、本実施の形態における情報処理システム100では、T<t<TXとなるように、時間tを決定する。

【0068】

読み取り部143は、コマンド発行回路146および受信バッファ147から構成される。

【0069】

コマンド発行回路146は、タイミングジェネレータ141から伝達されるタイミング信号に応じて、インターフェース部13に装着されている記憶装置2に対して読み取り要求を行う(読み取りコマンドを発行する)。

【0070】

受信バッファ147は、コマンド発行回路146が発行した読み取りコマンドに対するレスポンス(記憶装置2から読み出された値)を受信値148として格納する。

【0071】

本実施の形態における読み取り部143において、受信バッファ147に格納されている値は、タイミングジェネレータ141から伝達されるタイミング信号によって初期値にクリアされる。この初期値は記憶装置2から受信される値ではないが、便宜上、この初期値も含めて「受信値148」と称する。受信値148の初期値は、ROM140に格納される基準値145とは異なる値として予め設定されているものとする。

【0072】

このように本実施の形態における情報処理装置1では、コマンド発行回路146が読み取りコマンドを発行すると同時に受信バッファ147に格納されている受信値148が初期値にクリアされる。そして、当該読み取りコマンドに応じて何らかの値が記憶装置2から得られると、得られた値によって初期値が上書きされ、新たな受信値148として格納される。

【0073】

情報処理装置1は、制御部10とは別に、独立して動作する認証部14を備えていることにより、制御部10からの直接的な制御を受けることなく、記憶装置2からの値(受信値148として格納する値)の読み出しを行う。

【0074】

なお、認証部14は、受信値148となる値を記憶装置2から読み出す機能を最小限備えていればよいので、コマンド発行回路146は読み取りコマンドのみを発行し、その他のコマンド(例えば書き込みコマンドや消去コマンド等)を発行する必要はない。また、本実施の形態では、受信値148となる値の記憶装置2における格納位置(アドレス)は予め決められているので、読み取りコマンドにセットされるアドレスは固定の値でよい。すなわち、コマンド発行回路146は任意の信号を出力する機能を備えている必要はなく、タイミング信号が入力されたタイミングに応じて、固定の出力信号を、インターフェース部13を介して、記憶装置2に向けて送信する回路として構成されていれば充分である。

【0075】

比較回路144は、遅延回路142から遅延信号が伝達されると、ROM140から基準値145を取得するとともに、受信バッファ147から受信値148を認証値として取得する。そして、取得した基準値145と認証値とを比較して、これらが一致したか否かを示す信号(以下、「判定信号」と称する)を制御部10に出力する。

【0076】

詳細は後述するが、本実施の形態における情報処理システム100において、基準値145と認証値とが一致する場合とは、記憶装置2が正規品の記憶装置7であると判定されたことを意味する。一方、基準値145と認証値とが一致しない場合とは、記憶装置2が不正規品の記憶装置8であると判定されたことを意味する。すなわち、認証部14は、ROM140に記憶されている基準値145と認証値とを比較し、その比較結果に基づいて記憶装置2の真偽を判定する機能を有している。

【0077】

以上が情報処理システム100の構成および機能の説明である。

【0078】

次に、プログラム3(あるいはプログラム9)を格納した記憶装置2が着脱自在に装着される情報処理装置1において記憶装置2を認証する認証方法について説明する。

【0079】

図4は、第1の実施の形態における認証方法を示す流れ図である。

【0080】

なお、第1の実施の形態では、図4に示す各工程が実行される前に、情報処理装置1が備えるROM140に認証用の基準値145を格納する工程と、記憶装置7の固定位置に基準値145と同じ値(固定値)を格納する工程とが既に実行されているものとする。例えば、これらの値は、これらの装置が出荷される際に既に格納されているものとする。また、記憶装置7に格納されている固定値が誤って書き換えられると、正常な認証が行えなくなるため、固定値は書き換え不可(読み取り専用)とされていることが好ましい。

【0081】

まず、情報処理装置1に電源が投入されると、情報処理装置1は制御部10のCPU15がROM16に格納されているプログラム4に従って制御を開始することによって動作を開始する。

【0082】

このようにして動作を開始した情報処理装置1は、インターフェース部13を監視することによって記憶装置2が検出されたか否かを監視する(ステップS1)。また、認証部14による認証を行うか否かについても監視する(ステップS3)。そして、これらを監視しつつ、必要なプログラムを実行する(ステップS11)。

【0083】

なお、ステップS11におけるプログラムは、情報処理装置1においてそのとき実行可能な全てのプログラムを含むものであり、プログラム4に限られるものではなく、プログラム3やプログラム9が実行される場合もある。

【0084】

情報処理装置1の動作が開始され、ステップS11によってプログラムが順次実行されているときに、記憶装置2が検出されると、制御部10はステップS1においてYesと判定し、初期設定(ステップS2)を実行する。

【0085】

なお、ステップS1においてYesと判定されるのは、情報処理装置1の電源投入時に既に記憶装置2が装着されていたときと、記憶装置2が装着されていない状態から新たに記憶装置2が装着されたときである。すなわち、装着された状態の記憶装置2に対して、1回だけステップS2が実行される。

【0086】

ステップS2の初期設定では、情報処理装置1の制御部10が、インターフェース部13に装着されている記憶装置2に対して、格納しているプログラムをロードするように要求する。装着されている記憶装置2が記憶装置7である場合には、このロード要求に応じて、記憶装置7からプログラム3のロードが行われ、プログラム3の一部を構成するライブラリが制御部10のRAM17に転送される。一方、装着されている記憶装置2が記憶装置8である場合にも、このロード要求に応じて、記憶装置8からプログラム9のロードが行われ、プログラム9の一部を構成するライブラリが制御部10のRAM17に転送される。

【0087】

このように初期設定(ステップS2)が実行されることによって、必要なライブラリがRAM17に転送される。そして、以後、これらのライブラリをCPU15が使用することにより、プログラム3(あるいはプログラム9)が実行可能となる。

【0088】

情報処理装置1の動作が開始され、ステップS11によってプログラムが順次実行されているときに、所定の条件が満たされると、認証部14がステップS3においてYesと判定する。本実施の形態では、当該条件の判定を認証部14のタイミングジェネレータ141が行う。

【0089】

ここで、認証は、記憶装置2が装着されていない状態で行う必要はないので、本実施の形態におけるタイミングジェネレータ141が認証を行うと判定する条件(ステップS3においてYesと判定する条件)の1つは、記憶装置2がインターフェース部13に装着されていることである。

【0090】

また、認証は、一旦装着された記憶装置2に対して、少なくとも1回行うべきであり、かつ、定期的に複数回行ってもよい。本実施の形態におけるタイミングジェネレータ141が認証を行うと判定する条件の1つは、ステップS2が実行された後であって、かつ、前回の認証から所定の時間(予めセットされた時間)が経過したことである。ただし、認証を行った回数情報を保持しておき、予め決められた回数の認証をクリアした場合には、以後、当該記憶装置2に対する認証を行わないように構成してもよい。

【0091】

また、認証は、制御部10によるプログラム3の実行を妨害しないタイミングで行うことが好ましい。特に、認証部14による認証は記憶装置2に対するアクセスを伴うため、制御部10によるアクセスと認証部14によるアクセスとが干渉しないように実行する必要がある。したがって、本実施の形態におけるタイミングジェネレータ141が認証を行うと判定する条件の1つは、制御部10が記憶装置2にアクセスしていないことである。そして、制御部10が記憶装置2にアクセスしていないタイミングは、タイミングジェネレータ141がバス配線19上の各種信号を監視することにより検出可能である。

【0092】

本実施の形態では、タイミングジェネレータ141が制御部10に対してハードウェア割り込み信号を送信することによって、いわば制御部10に対して認証を行うための許可を求める。これに対して制御部10から許可信号が得られた場合に、タイミングジェネレータ141は、制御部10が記憶装置2にアクセスしていないと判定する。

【0093】

すなわち、本実施の形態では、インターフェース部13に記憶装置2が装着されており、装着されている記憶装置2に対してステップS2が実行された後において、所定の時間が経過するたびにタイミングジェネレータ141が制御部10に対してハードウェア割り込み信号を送信する。そして、当該ハードウェア割り込み信号に対して制御部10から許可信号が送信された場合に、タイミングジェネレータ141は認証を行う(ステップS3においてYes)と判定する。

【0094】

なお、制御部10において、情報処理装置1が備えるハードウェア(操作部11や認証部14)からのハードウェア割り込み信号に対する処理は、通常、情報処理装置1のBIOSやOS(すなわちプログラム4)に基づいて行われる。したがって、認証部14がハードウェア割り込み信号によって、制御部10に対して認証を行う許可を求めるように構成したとしても、記憶装置8のプログラム9による影響(例えば、いかなる場合も認証を許可しない等の制御)を受ける危険性は低い。

【0095】

図4に戻って、タイミングジェネレータ141が認証を行うと判定すると(ステップS3においてYes)、タイミングジェネレータ141が、読み取り部143(コマンド発行回路146および受信バッファ147)と遅延回路142にタイミング信号を出力する。

【0096】

このタイミング信号に応じて、受信バッファ147に格納されている値が初期値にクリアされる(受信値148が初期化される)。また、コマンド発行回路146が、記憶装置2の固定位置に格納されている固定値を読み取るための、読み取りコマンドを記憶装置2に向けて発行することにより、読み取り部143が読み出し要求を行う(ステップS4)。すなわち、情報処理装置1は、プログラム3(プログラム9)から独立して動作する読み取り部143によって記憶装置2からの値の読み出し要求を行う。

【0097】

読み取り部143による読み出し要求は、制御部10による読み出し要求と異なるところはない。したがって、この読み取りコマンドを受信した記憶装置2の制御部は、当該コマンドに含まれるアドレス(固定位置)からデータ(固定値)を読み出して、記憶装置2のバッファに格納する。

【0098】

認証方法としては、情報処理装置と記憶装置との間で、共通のパスワード(固定値)を記憶しておいて照合する方法が広く提案されている。しかし、パスワードも他のデータ(プログラム本体)と同じく情報であるため、記憶装置においてプログラムとパスワードとを同等に格納していれば、プログラムをコピーするのと同じ要領でパスワードもコピーされてしまうおそれが高い。このような不正コピーを防止しようとすれば、プログラムとは別に、パスワードをより高度にガードする仕組みが記憶装置に必要となり、正規品の記憶装置におけるコスト上昇を招くこととなる。しかも、例え、パスワードを何らかの方法でガードしていたとしても、一旦、ガードが破られ、パスワードがコピーされると、その後は、まったく不正規品を区別することができなくなるという問題もある。

【0099】

したがって、プログラム3を模しているプログラム9には、固定値も含まれている(コピーされている)危険性が高く、そのような場合には、記憶装置2に固定値が格納されているか否かだけでは、記憶装置7と記憶装置8とを区別することはできない。本実施の形態における情報処理システム100は、記憶装置8の固定位置にも基準値145と同じ値(固定値)が格納されているものとして以下の処理を行う。

【0100】

情報処理装置1の認証部14は、遅延回路142がタイミング信号を遅延させることによって時間tが経過するまで待機しつつ(ステップS7)、その間に、記憶装置2から固定値を受信したか否かを監視する(ステップS5)。時間t内に、ステップS4における読み出し要求に対する値を記憶装置2から受信すると、その値が受信値148として受信バッファ147に格納される(ステップS6)。

【0101】

記憶装置2として、正規品の記憶装置7が装着されていた場合、時間T<時間tであるから、記憶装置7は読み出し部143による読み出し要求に対する値を時間t内に記憶部から読み出してバッファに格納することが可能である。したがって、記憶装置2として、正規品の記憶装置7が装着されていた場合には、読み取り部143による読み出し要求によって要求された値が、ステップS6によって正しくバッファに格納される。すなわち、記憶装置2のレイテンシが時間t内であれば、所望した固定値が受信値148として格納される。

【0102】

一方、記憶装置2として、不正規品の記憶装置8が装着されていた場合、時間t<時間TXであるから、記憶装置8は読み出し部143による読み出し要求に対する値を時間t内に読み出してバッファに格納することができない。また、認証部14は記憶装置2から転送されたライブラリから独立して動作しているため、例え記憶装置8が装着されている場合でも、ステップS4における読み出し要求の前に、プレ読み出し処理を行うことができない。したがって、記憶装置8は、例え固定値を正確にコピーして格納していたとしても、読み取り部143から所望されたときに、当該固定値をバッファに格納する処理が間に合わず、かつ、予め格納しておくこともできない。したがって、記憶装置8は、読み取り部143に対して、値の保証されない、バッファ上の残余のデータを受け渡すこととなり、これが受信バッファ147に受信値148として格納される。すなわち、記憶装置2のレイテンシが時間t内でなければ、所望した固定値が受信値148として格納されない。

【0103】

なお、本実施の形態は、情報処理装置1と記憶装置7との間では、レディ・ビジー機能を実現していない。したがって、認証部14と模倣品である記憶装置8との間でもレディ・ビジー処理は行われず、記憶装置8がレディ状態になったか否かにかかわらず、記憶装置8のバッファから情報処理装置1側に残余のデータ(固定値と異なる値)が取得される。一方、このような機能を持たせていた場合、時間t内に記憶装置8がレディとなることはないので、時間t内に記憶装置8からデータを受信することはなくなる。その場合でも、情報処理装置1側の受信バッファ147には、受信値148として初期値が格納されているため、やはり、固定値とは異なる値が受信値148となる。

【0104】

時間tが経過して(ステップS7においてYes)、遅延回路142が遅延信号を比較回路144に向けて出力すると、比較回路144が基準値145をROM140から取得する。また、その時点で受信バッファ147に格納されている受信値148を認証値として受信バッファ147から取得する(ステップS8)。すなわち、情報処理装置1は、ステップS4における読み出し要求を行ってから所定の時間内に、受信バッファ147に格納されている受信値148を認証値として取得する。

【0105】

次に、比較回路144によって取得した基準値145と取得した認証値とを比較し(ステップS9)、比較回路144からの出力信号(比較結果)に応じて、装着されている記憶装置2が正規品(記憶装置7)であるか、不正規品(記憶装置8)であるかを判定する(ステップS10)。

【0106】

装着されている記憶装置2が記憶装置7である場合、時間t内に固定値が得られ、この固定値が受信値148として格納されている。この場合、ステップS8において取得される認証値は固定値であるから、ROM140に格納されていた基準値145と一致する。すなわち、比較回路144からの出力信号が、基準値145と認証値との一致を示している場合、ステップS10ではYesと判定される。この場合、情報処理システム100は処理を終了することなく、プログラムの実行を継続する(ステップS11)。

【0107】

一方、装着されている記憶装置2が記憶装置8である場合、時間t内に固定値を得ることができず、この固定値と異なる値が受信値148として格納されている。したがって、取得された認証値は固定値とは異なるので、ROM140に格納されていた基準値145と一致しない。すなわち、比較回路144からの出力信号が、基準値145と認証値との不一致を示している場合、ステップS10ではNoと判定される。この場合、情報処理システム100は処理を終了し、プログラム9の実行を停止する。

【0108】

以上のように、本実施の形態における情報処理装置1は、記憶装置2が着脱自在に装着されるインターフェース部13と、インターフェース部13に装着された記憶装置2に格納されているプログラム3,9を実行する制御部10と、プログラム3,9と独立して動作し、インターフェース部13に装着された記憶装置2からのデータの読み出し時間に基づいて記憶装置2の真偽を判定する認証部14とを備えることにより、正規品である記憶装置7のハードウェア構成を変更することなく、記憶装置2のハードウェア特性に基づく認証を容易に実現できる。

【0109】

また、認証部14は、インターフェース部13に装着された記憶装置2の真偽を判定する比較回路144を備えることにより、記憶装置2との独立性が高く、改変される危険性も低いため、セキュリティが向上する。

【0110】

なお、先述のように、本実施の形態では認証を実行する条件が整う限り、認証部14による認証が何回でも行われる(特に回数制限は設けていない)。一方で、図4から明らかなように、基準値145と認証値とが一致しない事態(認証失敗)が1回でも発生すると、情報処理システム100における処理を終了する。しかし、認証失敗の回数制限を予め設けておき、当該回数制限を超えるまでは処理を続行するように構成してもよい。また、この場合、回数制限以内であっても、警告等を表示するようにしてもよい。

【0111】

また、記憶装置7に格納される固定値はプログラム3,4が実行される過程で書き換えられることのない値であればよい。したがって、認証のためだけに格納される値でなくてもよく、例えば、CPU15によって実行される指令の一部であってもよい。

【0112】

<2. 第2の実施の形態>

第1の実施の形態における認証部14は、主に回路(ハードウェア)で構成されていたが、その一部をプログラムで実現することも可能である。

【0113】

図5は、第2の実施の形態における情報処理装置1aの認証部14aを示す図である。また、図6は、第2の実施の形態における認証部14aが備える機能ブロックをデータの流れとともに示す図である。

【0114】

なお、第2の実施の形態における情報処理装置1aは、認証部14の代わりに認証部14aを備えている点を除いて、ほぼ第1の実施の形態における情報処理装置1と同様の構成を備えている。以下の説明では、第1の実施の形態と同様の構成については同符号を付し、適宜説明を省略する。

【0115】

認証部14aは、図5に示すように、基準値145を格納するROM140aと、CPU150と、RAM151とを備えている。

【0116】

ROM140aは、第1の実施の形態におけるROM140と同様に基準値145を格納する。また、インターフェース部13に装着された記憶装置2の真偽を判定するためのプログラム149を格納する。

【0117】

CPU150は、RAM151を一時的なワーキングエリアとして使用しつつ、主にプログラム149に従って動作する。図6に示す、タイミング決定部152、読み取り部153、比較部154および判定部155は、CPU150がプログラム149に従って(プログラム3,9から独立して)動作することにより実現される機能ブロックである。

【0118】

タイミング決定部152は、制御部10との間でデータのやり取りを行いつつ、認証部14aによる認証を行うタイミングを決定し、読み取り部153および比較部154に伝達する機能を有する。

【0119】

読み取り部153は、タイミング決定部152から認証部14aによる認証を行うタイミングが通知されると、読み取りコマンドを生成して記憶装置2に向けて送信する。読み取り部153から発行される読み取りコマンドは、記憶装置2の固定位置から固定値を読み出すためのコマンドである。また、当該読み取りコマンドに応じて記憶装置2から得られた値に基づいて認証値情報156を生成し、RAM151に転送する。

【0120】

比較部154は、タイミング決定部152から認証部14aによる認証を行うタイミングが通知されると、時間tだけ待機した後、基準値145をROM140aから取得するとともに、その時点で認証値情報156が生成されていればRAM151から認証値情報156を取得する。さらに、比較部154は、基準値145と認証値情報156の値とを比較し、その比較結果(一致・不一致)に基づいて比較結果情報157を生成し、RAM151に転送する。

【0121】

判定部155は、比較結果情報157に基づいて、記憶装置2の真偽を判定し、その判定結果を制御部10に伝達する。

【0122】

なお、第2の実施の形態における認証部14aによる認証方法は、第1の実施の形態における認証方法と同様に実現できるため、説明を省略する。

【0123】

このように第2の実施の形態における情報処理システム100は、情報処理装置1aを備えることにより、第1の実施の形態における情報処理システム100と同様の効果を得ることができる。

【0124】

また、情報処理装置1aは、インターフェース部13に装着された記憶装置2の真偽を判定するためのプログラム149を記憶するROM140aを備えることにより、記憶装置2のプログラム3,9との独立を確保しつつ、認証を行うことができる。すなわち、第1の実施の形態における情報処理装置1のように認証部14をハードウェア回路で実現する場合に比べて、コストを抑制できる。

【0125】

<3. 第3の実施の形態>

第1の実施の形態では、制御部10のハードウェア構成と、認証部14のハードウェア構成とが別々(独立)に設けられていた。しかし、記憶装置8に格納されているプログラム9(RAM17に転送されるライブラリ)の影響を受けることなく認証が行われるならば、これらの構成は一部兼用されてもよい。

【0126】

図7は、第3の実施の形態における情報処理装置1bの制御部10bおよび認証部14bを示す図である。

【0127】

第3の実施の形態における情報処理装置1bは、制御部10の代わりに制御部10bを備えるとともに、認証部14の代わりに認証部14bを備える点が、第1の実施の形態における情報処理装置1と異なっている。以下の説明では、第1の実施の形態と同様の構成については同符号を付し、適宜説明を省略する。

【0128】

制御部10bは、CPU15の他に、ROM16b、RAM17bおよびコマンド発行回路18を備えている。ROM16bは第1の実施の形態におけるROM16と同様にプログラム4を格納するとともに、基準値145を格納している。

【0129】

また、RAM17bは、第1の実施の形態におけるRAM17の機能に加えて、記憶装置2から受信した値を受信値148として格納する機能を有している。すなわち、RAM17bは、第1の実施の形態における受信バッファ147の機能を有している。

【0130】

コマンド発行回路18は、CPU15からの制御に応じて、CPU15によって指定されたコマンドを生成し、当該コマンドを示すコマンド信号をインターフェース部13に伝達する。すなわち、本実施の形態におけるCPU15はコマンド信号の生成を行わず、コマンド信号を生成するための専用のハードウェアであるコマンド発行回路18を制御してコマンド信号を生成させる。このように、専用のハードウェアでコマンド信号を生成するこにより、情報処理装置1bはコマンド信号を発行する速度が向上する。

【0131】

また、コマンド発行回路18は、認証部14b(タイミングジェネレータ141b)から指定されたコマンドを、CPU15に指定された場合と同様に生成し、当該コマンドを示すコマンド信号をインターフェース部13に伝達する機能も有している。ただし、認証部14bがコマンド発行回路18に指定するコマンドは読み取りコマンドに限定されており、かつ、当該読み取りコマンドに含まれるアドレス(値を読み出す記憶装置2の位置を示す)は、第1の実施の形態と同様に「固定位置(固定値が格納されている位置)」に限定されている。

【0132】

なお、コマンド発行回路18からインターフェース部13に伝達されたコマンド信号は記憶装置2に向けて送信される。そして、記憶装置2の制御部によって解析され、当該コマンドが記憶装置2において実行される。

【0133】

本実施の形態における認証部14bは、タイミングジェネレータ141b、遅延回路142および比較回路144bを備えている。

【0134】

タイミングジェネレータ141bは、第1の実施の形態におけるタイミングジェネレータ141と同様に、認証を行うタイミングを決定して、タイミング信号を遅延回路142に伝達する。また、タイミング信号を出力するのと同時に、制御部10bのコマンド発行回路18に、記憶装置2の固定位置に格納されている固定値を読み出すためのコマンドを発行するように、指定信号を伝達する。この指定信号には、発行するべきコマンドが読み取りコマンドであることを示す信号と、読み出す固定値の格納位置(固定位置)を示す信号とが含まれている。

【0135】

遅延回路142は、タイミングジェネレータ141bからのタイミング信号を時間tだけ遅延させてから、遅延信号を比較回路144bに伝達する。

【0136】

比較回路144bは、遅延回路142から遅延信号が入力されると、ROM16bから基準値145を取得するとともに、RAM17bから受信値148を認証値として取得する。そして、取得した基準値145と認証値とを比較し、比較結果をCPU15に伝達する。

【0137】

なお、第3の実施の形態における情報処理装置1bによる認証方法は、第1の実施の形態における認証方法と同様に実現できるため、説明を省略する。

【0138】

以上のように、第3の実施の形態における情報処理装置1bのように、制御部10bが備えるROM16b、RAM17bおよびコマンド発行回路18を、第1の実施の形態におけるROM140、読み取り部143(コマンド発行回路146および受信バッファ147)と同様に使用することによって、第1の実施の形態と同様の効果を得ることができる。

【0139】

情報処理システム100として、情報処理装置が専用のゲーム機本体であり、記憶装置が当該ゲーム機本体用のゲームプログラムを格納したメモリカードである場合を想定すると、情報処理装置において最も利用頻度の高いプログラムは記憶装置に格納されていることになる。このような情報処理システム100では、情報処理装置が汎用コンピュータであってゲームのみならず様々な情報を処理する場合に比べて、記憶装置へのアクセス頻度が高く、記憶装置へのコマンドの発行頻度が高いという事情がある。

【0140】

このようなゲーム機本体では、頻度の高い処理(記憶装置へのアクセス処理)を高速化させるために、専用のコマンド発行回路を備えた構成が採用される。したがって、情報処理装置1bのように、制御部10bがハードウェアとしてのコマンド発行回路18を既に備えている場合には、認証部14bのように、当該コマンド発行回路18を認証に使用してハードウェアを兼用することにより、コストを抑制することができる。すなわち、本実施の形態における情報処理装置1bのように構成することは、情報処理装置として専用のゲーム機本体を想定した場合に、特に効果的である。

【0141】

<4. 第4の実施の形態>

上記実施の形態における情報処理システム100では、予め、情報処理装置1,1a,1bに基準値145を格納しておくとともに、記憶装置7の固定位置に基準値145と等しい値(固定値)を格納しておく必要があった。しかし、本発明はこのような構成に限定されるものではない。

【0142】

図8は、第4の実施の形態における情報処理装置1cの制御部10cを示す図である。

【0143】

第4の実施の形態における情報処理装置1cは、制御部10bの代わりに制御部10cを備える点が、第3の実施の形態における情報処理装置1bと異なっている。以下の説明では、第3の実施の形態と同様の構成については同符号を付し、適宜説明を省略する。

【0144】

第4の実施の形態における制御部10cは、第3の実施の形態におけるROM16bの代わりに第1の実施の形態におけるROM16を備えている。

【0145】

また、制御部10cは、第3の実施の形態におけるRAM17bの代わりにRAM17cを備えている。制御部10cでは、コマンド発行回路18が発行した読み取りコマンドに応じて記憶装置2から受信された値が、RAM17cに受信値148として格納される。すなわち、RAM17cの所定の格納領域が、記憶装置2から取得されるデータ(値)の受信バッファとして使用される。さらに、RAM17cは遅延回路142cから伝達される複写信号(後述)に応じて、そのとき格納されている受信値148を複写して新たに基準値145として格納する機能も有している。

【0146】

認証部14cのタイミングジェネレータ141cは、認証を行うか否かを判定するための所定の条件(以下、「第1条件」と称する)を検出して、第1タイミング信号を生成し、遅延回路142cに出力する。本実施の形態における第1条件は、第1の実施の形態においてタイミングジェネレータ141が認証を行うか否かを判定するために検出する条件と同じ条件とするが、もちろんこれに限定されるものではない。本実施の形態における第1条件は、制御部10cの動作を妨害しないタイミングを決定するものであればどのような条件が選択されてもよい。

【0147】

また、タイミングジェネレータ141cは、比較を行うための所定の条件(以下、「第2条件」と称する)を検出して、第2タイミング信号を生成して遅延回路142cに出力する。第2条件については後述する。

【0148】

さらに、タイミングジェネレータ141cは、第1タイミング信号または第2タイミング信号を遅延回路142cに出力した場合には、当該出力と同時に、記憶装置2の固定位置に格納されている固定値を読み出すためのコマンドを発行するように、制御部10cのコマンド発行回路18に指定信号を伝達する。この指定信号には、発行するべきコマンドが読み取りコマンドであることを示す信号と、読み出す固定値の格納位置(固定位置)を示す信号とが含まれている。ただし、指定信号は固定の信号であり、状況に応じて変化することのない信号である。

【0149】

なお、本実施の形態では、タイミングジェネレータ141cが直接指定信号をコマンド発行回路18に出力するように説明するが、例えば、タイミングジェネレータ141cが指定信号を出力するすべきタイミングだけを割り込み信号等でCPU15に通知し、これに応じて、CPU15が指定信号を生成してコマンド発行回路18に出力するように構成してもよい。ただし、この場合のCPU15の動作は、ライブラリ(プログラム9の一部)に従って実現されるものでないことが好ましい。例えば、タイミングジェネレータ141cから通知を受けた場合には、プログラム4に含まれるライブラリによってCPU15が指定信号を出力するように構成することが好ましい。

【0150】

遅延回路142cは、入力された第1タイミング信号を所定の時間tだけ遅延させることにより複写信号を生成し、制御部10cに伝達する。先述のように、複写信号が伝達されると、制御部10cのRAM17cにおいて、そのときRAM17cに格納されている受信値148が新たに基準値145として格納される。すなわち、詳細は後述するが、遅延回路142cが複写信号を制御部10cに伝達することにより、第4の実施の形態における情報処理装置1cにおいて、基準値145を格納する工程が行われる。なお、第1タイミング信号に応じて生成される複写信号は、比較を行うための前段階として、基準値145を格納するタイミングを決定するための信号であるため、比較回路144bには伝達されない。

【0151】

また、遅延回路142cは、入力された第2タイミング信号を所定の時間tだけ遅延させることにより遅延信号を生成し、比較回路144bに伝達する。第2タイミング信号に応じて生成される遅延信号は、比較回路144bによる比較(認証)を実行させる信号であるため、制御部10cには伝達されない。

【0152】

以上が第4の実施の形態における情報処理装置1cの構成および機能の説明である。次に、情報処理装置1cを用いた情報処理システム100における認証方法を説明する。

【0153】

図9および図10は、第4の実施の形態における認証方法を示す流れ図である。

【0154】

なお、第1の実施の形態では、図9および図10に示す各工程が実行される前に、記憶装置7の固定位置に固定値(変更されない値であればよい)を格納する工程が既に実行されているものとする。また、図9に示すステップS21,S22,S23,S29の各工程は、図4に示すステップS1,S2,S3,S11の各工程とほぼ同様の工程であるため、ここでは説明を省略する。

【0155】

第1条件が満たされたことを検出し、認証を行うと判定すると(ステップS23においてYes)、タイミングジェネレータ141cは第1タイミング信号を遅延回路142cに伝達する。また、この第1タイミング信号を出力すると同時に、タイミングジェネレータ141cは制御部10cのコマンド発行回路18に指定信号を伝達する。この指定信号に応じて、コマンド発行回路18が記憶装置2に対して読み取りコマンドを発行することにより、読み出し要求を行う(ステップS24)。

【0156】

ステップS24において発行される読み取りコマンドには、記憶装置2において、固定値が格納された固定位置を示す情報が含まれている。したがって、この読み取りコマンドに応じて、記憶装置2の記憶部の固定位置から値(固定値)が読み出され、記憶装置2のバッファに格納され、インターフェース部13を介してRAM17cに格納される。

【0157】

情報処理装置1cの認証部14cは、遅延回路142cが第1タイミング信号を遅延させることによって時間tが経過するまで待機しつつ(ステップS27)、その間に、記憶装置2から固定値を受信したか否かを監視する(ステップS25)。時間t内に、ステップS24における読み出し要求に対する値を記憶装置2から受信すると、その値が受信値148としてRAM17cに格納される(ステップS26)。

【0158】

記憶装置2として、正規品の記憶装置7が装着されていた場合、時間T<時間tであるから、記憶装置7はステップS24の読み出し要求に対する値を時間t内に記憶部から読み出してバッファに格納することが可能である。したがって、記憶装置2として、正規品の記憶装置7が装着されていた場合には、読み出し要求によって要求された値が、ステップS26によって正しくバッファに格納される。すなわち、記憶装置2のレイテンシが時間t内であれば、ステップS26が実行されることにより所望した固定値が受信値148として格納される。

【0159】

一方、記憶装置2として、不正規品の記憶装置8が装着されていた場合、時間t<時間TXであるから、記憶装置8はステップS24の読み出し要求に対する値を時間t内に読み出してバッファに格納することができない。また、認証部14cは記憶装置2から転送されたライブラリから独立して動作しているため、例え記憶装置8が装着されている場合でも、ステップS24における読み出し要求の前に、プレ読み出し処理を行うことができない。したがって、記憶装置8は、例え固定値を正確にコピーして記憶部に格納していたとしても、当該固定値をバッファに格納する処理が間に合わず、かつ、予め格納しておくこともできない。したがって、記憶装置8は、ステップS24の読み出し要求に対して、値の保証されない、バッファ上の残余のデータを受け渡すこととなり、これがRAM17cに受信値148として格納される。すなわち、記憶装置2のレイテンシが時間t内でなければ、所望した固定値が受信値148として格納されない。

【0160】

タイミングジェネレータ141cが指定信号を伝達してから時間tが経過すると(ステップS27においてYes)、遅延回路142cが複写信号を生成して、当該複写信号を制御部10cとタイミングジェネレータ141cとに出力する。

【0161】

制御部10cは、この複写信号に応じて、そのときRAM17cに格納されている受信値148を、新たに基準値145としてRAM17cに格納する(ステップS28)。

【0162】

このように本実施の形態における情報処理システム100では、認証を行うときには、少なくとも認証値を取得するための読み出し要求(後述するステップS32)が実行される前に、ステップS28によって基準値145の格納が行われる。

【0163】

なお、ステップS24における読み出し要求に対して正常に読み出しが行われ、記憶装置2に格納されていた固定値が正常に受信値148として格納されていれば、ステップS28によって基準値145は固定値と等しい値となる。一方、ステップS24における読み出し要求に対して正常な読み出しが行われず、記憶装置2に格納されていた固定値が正常に受信値148として格納されていなければ、ステップS28が実行されることによって基準値145は保証されない値(一般に固定値と異なる値)となる。

【0164】

複写信号を受け取ることにより、タイミングジェネレータ141cは、制御部10cにおいて認証用の基準値145のRAM17cへの格納が行われたことを検出し、比較を行うタイミングを監視する状態となる(ステップS31)。

【0165】

なお、図示の都合上、図9および図10では、ステップS24ないしS28およびステップS31ないしS38が実行されている間、ステップS29(プログラムの実行)が実行されていないかのように示している。しかし、ステップS24ないしS28およびステップS31ないしS38の各工程は制御部10cとは独立して動作する認証部14cの動作であり、ステップS29は制御部10cの動作である。したがって、ステップS24ないしS28およびステップS31ないしS38の各工程が認証部14cによって実行されている間においても、制御部10cはプログラムの実行を行うことが可能である。本実施の形態では、ステップS24ないしS28およびステップS31ないしS38の各工程と、ステップS29の工程とは、適宜、並行して実行されており、ステップS31によって認証部14cが待機状態にある間もプログラムの実行(ステップS29)は行われている。

【0166】

情報処理システム100では、正常に読み出しが行われなかった(読み出しが間に合わなかった)場合であっても、何らかの値が取得される。この値は、そのときたまたまバッファ等に残留していた値であり、一般に、それまでの処理で読み出された値である。したがって、基準値145として読み出した値(固定値とは限らない)が、RAM17cに受信値148として残留していたり、記憶装置2のバッファに残留している間に認証値を取得しようとすると、読み出しに失敗しているにも関わらず、認証に成功する事態を招くおそれがある。

【0167】

RAM17cは情報処理装置1c側の構成であるため、RAM17c上の受信値148は、第1の実施の形態における受信バッファ147のように、適当なタイミングで初期値によって上書きすることも可能である。例えば、ステップS28を実行して受信値148を基準値145として格納した後に、受信値148を初期値で上書きしておく等が考えられる。しかし、一般に、記憶装置2のバッファ上に残留する値を情報処理装置1cから直接クリアすることはできない。

【0168】

そこで、タイミングジェネレータ141cは、制御部10cがステップS29を実行する過程で、これらの値が他の値で更新されるタイミングを検出してから、認証値の取得を行うようにステップS31において第2条件を監視している。

【0169】

本実施の形態における第2条件は、CPU15からコマンド発行回路18に対する読み取り要求がされたこととする。この読み取り要求はプログラム3(プログラム9)によって要求されるため正常に実行される。したがって、プログラム3(プログラム9)が所望する値(一般に固定値とは異なる値)が記憶装置2から取得され、この値に受信値148が更新される。またこのときには、記憶装置2のバッファにもこの値が格納されていることが期待される。

【0170】

なお、第2条件としては、RAM17cに格納されている受信値148と基準値145との不一致検出等を第2条件としてもよい。すなわち、現実に受信値148が他の値でクリアされたことを検出してから認証値の取得を行うようにしてもよい。また、詳細は省略したが、第2条件には、当然ながら、CPU15によるプログラムの実行を妨げないことも含まれる。

【0171】

ステップS31によって認証部14cが待機状態にあるときに、制御部10cが記憶装置2に対して読み取り要求を行うと、タイミングジェネレータ141cは、第2タイミング信号を遅延回路142cに出力するとともに、指定信号をコマンド発行回路18に出力する。この指定信号により、コマンド発行回路18が記憶装置2に対して読み取りコマンドを発行し、固定位置に格納されている固定値の読み出し要求を行う(ステップS32)。

【0172】

なお、ステップS33ないしS38の各工程は、図4に示した第1の実施の形態におけるステップS5ないしS10の各工程とほぼ同じであるため説明を省略する。

【0173】

以上のように、第4の実施の形態における情報処理システム100においても上記実施の形態と同様の効果を得ることができる。

【0174】

また、記憶装置2の所定の位置(固定位置)に格納された値を読み出し(ステップS24)、ステップS24において読み出された値を基準値145としてRAM17cに格納する(ステップS28)。そして、認証値を取得する際にも、同じく固定位置からの読み出し要求を行って(ステップS32)、認証値を取得する(ステップS36)。このように構成することによって、記憶装置7および情報処理装置1cに共通の固定値を予め格納しておく必要がない。

【0175】

なお、本実施の形態では、ステップS23において認証を行うと判定した場合に、必ず、ステップS24が実行され基準値145の取得が実行されるように構成した。しかし、認証を複数回行う場合(ステップS37を1回実行しただけで、真偽を判定しない場合)であっても、基準値145の取得は一度だけで充分である。したがって、このような場合には、例えば、基準値145を取得する処理を初期設定(ステップS22)において実行するように構成してもよい。

【0176】

<5. 第5の実施の形態>

第4の実施の形態では、基準値145となる値の読み出しを、独立して動作する認証部14cによって実行し、これによって読み出され格納された値は、当該読み出し要求を行ってから所定の時間内に記憶装置2から得られた値である。しかし、基準値145は、装着されている記憶装置2が記憶装置7であるか記憶装置8であるかに関わらず、必ず、正しい固定値を読み出して格納するように構成してもよい。

【0177】

図11は、第5の実施の形態における情報処理装置1dの認証部14dを示す図である。第5の実施の形態における情報処理装置1dは、認証部14cの代わりに認証部14dを備える点が第4の実施の形態における情報処理装置1cと異なっている。

【0178】

第5の実施の形態における認証部14dは、タイミングジェネレータ141d、遅延回路142、比較回路144bおよびバッファ158を備えている。

【0179】

タイミングジェネレータ141dは、制御部10cがプログラムを実行する過程で生じる記憶装置2への読み出し要求(読み取りコマンド)を監視し、読み取りコマンドを検出した場合には、当該読み取りコマンドに含まれるアドレス(当該読み出し要求により取得される値の格納位置)を取得してバッファ158にアドレス値159として格納する。そして、検出した読み取りコマンドに応じて、記憶装置2から得られた値を基準値145として格納するようにRAM17cを制御する。

【0180】

また、タイミングジェネレータ141dは、認証を行うか否かを判定し、認証を行うと判定した場合には、タイミング信号を遅延回路142に出力する。なお、本実施の形態におけるタイミングジェネレータ141dは、第4の実施の形態における第2条件と同様の条件によって認証を行うか否かを判定するが、もちろんこれに限定されるものではない。

【0181】

さらに、タイミングジェネレータ141dは、タイミング信号を出力すると同時に、バッファ158に格納されているアドレス値159を取得して、当該アドレス値159で示される位置から値を読み出すよう指定信号を生成し、コマンド発行回路18に出力する。すなわち、本実施の形態におけるタイミングジェネレータ141dは指定信号に含めるアドレスとして任意の値を指定できるように構成されている。

【0182】

図11に示すように、第5の実施の形態における認証部14dは、遅延回路142cの代わりに、第1および第3の実施の形態における認証部14,14bと同様の遅延回路142を備えている。すなわち、本実施の形態における遅延回路142は、タイミングジェネレータ141dからのタイミング信号を時間tだけ遅延させることにより遅延信号を生成し、比較回路144bに出力する。

【0183】

以上が本実施の形態における情報処理装置1dの構成および機能の説明である。次に、第5の実施の形態における情報処理システム100の認証方法について説明する。

【0184】

図12および図13は、第5の実施の形態における認証方法を示す流れ図である。なお、図12に示すステップS41,S42,S47,S48の各工程は、図9に示す第4の実施の形態におけるステップS21,S22,S23,S29の各工程とほぼ同じ工程であるので説明を省略する。ただし、ステップS47においてYesと判定されるための条件は、後述するステップS46が既に実行されていることも条件となる。

【0185】

認証部14d(タイミングジェネレータ141d)が、制御部10cがステップS48を実行(プログラムを実行)する過程で生じる読み出し要求を検出すると、読み取りコマンドからアドレスを取得して、バッファ158にアドレス値159として格納する(ステップS44)。

【0186】

次に、タイミングジェネレータ141dは、受信値148がRAM17cに格納されるまで待機する(ステップS45)。

【0187】

制御部10cがプログラムを実行する過程で生じる読み出し要求に対しては、例え記憶装置8が装着されている場合であっても、当該読み出し要求によって要求された値が、当該読み出し要求によって指定されるアドレスから読み出される。したがって、記憶装置2の当該アドレスに格納されている値が受信値148となる。

【0188】

ステップS43で検出した読み出し要求に対して、記憶装置2から得られた値が受信値148としてRAM17cに格納されると、格納された受信値148を基準値145としてRAM17cに新たに格納する(ステップS46)。これにより、認証用の基準値145の格納が完了する。

【0189】

ステップS46が完了した後、ステップS47においてYesと判定されると、タイミングジェネレータ141dはタイミング信号を遅延回路142に出力する。これと同時に、タイミングジェネレータ141dはバッファ158からアドレス値159を取得して、指定信号を生成し、コマンド発行回路18に出力する。この指定信号に応じて、コマンド発行回路18が読み取りコマンドを記憶装置2に発行することにより読み出し要求を行う(ステップS51)。

【0190】

ステップS51において発行される読み取りコマンドには、基準値145となった値を読み出したときのアドレス値159が指定されているため、当該読み出し要求に対して、正常に読み出しが行われれば、基準値145となっている値と同じ値が記憶装置2から得られるはずである。一方、記憶装置2のレイテンシが低く、ステップS51における読み出し要求に対する読み出しが間に合わなかった場合には、基準値145となった値を正しく読み出すことができず、基準値145と異なる値が受信値148として記憶装置2から得られるはずである。

【0191】

以下、ステップS52ないしS57の各工程は、図10に示す第4の実施の形態におけるステップS33ないしS38の各工程と同様であるため説明を省略する。

【0192】

以上のように、第5の実施の形態における情報処理装置1dのように構成しても、上記実施の形態と同様の効果を得ることができる。

【0193】

また、本実施の形態では、基準値145を取得する際には、制御部10cがプログラムを実行する過程で生じる読み出し要求を検出して、当該読み出し要求における受信値148を基準値145として格納しておくとともに、当該読み出し要求におけるアドレスを認証値を取得する際のアドレスとして格納しておく。これにより、第4の実施の形態における認証方法のように、認証を行うための読み出し要求(ステップS24,S32)を2回行う必要がなくなる。また、認証に用いる値の格納位置を限定する必要もない。

【0194】

<6. 第6の実施の形態>

上記実施の形態では、時間t(認証のための読み取りコマンドを発行してから基準値と認証値との比較を行うまでの時間を決定する際の基準となる時間)は一定であった。しかし、認証を行うたびにこれを変更するように構成してもよい。

【0195】

第6の実施の形態における情報処理装置1は、基準値145と認証値との比較結果と、このときの時間tとを関連付けて認証履歴情報として保存する。そして、認証を行うたびに、認証履歴情報を参照しつつ、時間tを変更する。すなわち、第6の実施の形態における情報処理システム100では、基準値145と認証値とが不一致であっても、直ちに、記憶装置2が記憶装置8であると判定することはない。

【0196】

例えば、時間tの初期値を、時間t<時間Tを満たす値から認証を開始し、認証を行うたびに、順次、所定値Δtだけ時間tの値を増加させる。このように構成すると、記憶装置2のレイテンシ(時間τ)<時間tとなった時点で、基準値145と認証値とが一致するようになる。

【0197】

すなわち、第6の実施の形態における情報処理装置1は、時間tを変更することによって記憶装置2のレイテンシ(時間τ)を検出する機能を有する。そして、τ≒Tであれば、装着されている記憶装置2が正規品の記憶装置7であると判定する。一方、τ≠Tであれば、装着されている記憶装置2が不正規品の記憶装置8であると判定する。

【0198】

上記実施の形態における情報処理装置1では、記憶装置8のレイテンシ(時間TX)をある程度、予測して時間tを決定する必要があった。しかし、第6の実施の形態における情報処理装置1は、不正業者によって製造される記憶装置8のレイテンシが不明であっても、時間tを変更することによって、記憶装置7と記憶装置8との性能差を検出して、これらを見分ける(認証する)ことが可能である。

【0199】

<7. 変形例>

以上、本発明の実施の形態について説明してきたが、本発明は上記実施の形態に限定されるものではなく様々な変形が可能である。

【0200】

例えば、第2の実施の形態における認証部14aは、制御部10とハードウェアが兼用されてもよい。すなわち、プログラム4がマイクロプログラムとしてのプログラム149を含んでおり、CPU15が、RAM17を一時的なワーキングエリアとして使用しつつ、ROM16に格納されたプログラム4(プログラム149)に従って動作することにより、タイミング決定部152、読み取り部153、比較部154および判定部155に相当する機能ブロックが実現されていてもよい。その場合には、さらにハードウェア構成を減らすことができるため、情報処理装置1の製造コストを抑制できる。

【0201】

また、第6の実施の形態における情報処理装置1において、時間tの初期値を、時間T,TX<時間tを満たす値から認証を開始し、認証を行うたびに(比較結果が不一致となるたびに)、順次、所定値Δτだけ時間tの値を減少させてもよい。このように構成した場合、時間t<時間τとなった時点で、基準値145と認証値とが一致しなくなり、記憶装置2のレイテンシを検出することができる。

【0202】

また、上記実施の形態に示した各工程はあくまでも例示であって、これに限定されるものではない。例えば、同様の効果が得られるのであれば、各工程における処理内容や各工程の順序が適宜変更されてもよい。

【図面の簡単な説明】

【0203】

【図1】本発明に係る情報処理システムを示す図である。

【図2】第1の実施の形態における情報処理装置1の構成を示す図である。

【図3】第1の実施の形態における認証部を示す図である。

【図4】第1の実施の形態における認証方法を示す流れ図である。

【図5】第2の実施の形態における情報処理装置の認証部を示す図である。

【図6】第2の実施の形態における認証部が備える機能ブロックをデータの流れとともに示す図である。

【図7】第3の実施の形態における情報処理装置の制御部および認証部を示す図である。

【図8】第3の実施の形態における情報処理装置の制御部および認証部を示す図である。

【図9】第4の実施の形態における認証方法を示す流れ図である。

【図10】第4の実施の形態における認証方法を示す流れ図である。

【図11】第5の実施の形態における情報処理装置の認証部を示す図である。

【図12】第5の実施の形態における認証方法を示す流れ図である。

【図13】第5の実施の形態における認証方法を示す流れ図である。

【符号の説明】

【0204】

1,1a,1b,1c,1d 情報処理装置

10,10b,10c 制御部

100 情報処理システム

11 操作部

12 表示部

13 インターフェース部

14,14a,14b,14c,14d 認証部

15,150 CPU

16,16b,140,140a ROM

17,17b,17c,151 RAM

141,141b,141c,141d タイミングジェネレータ

142,142c 遅延回路

143,153 読み取り部

144,144b 比較回路

145 基準値

18,146 コマンド発行回路

147 受信バッファ

148 受信値

152 タイミング決定部

154 比較部

155 判定部

156 認証値情報

157 比較結果情報

158 バッファ

159 アドレス値

2,7,8 記憶装置

3,4,9 プログラム

【特許請求の範囲】

【請求項1】

記憶装置に格納されたプログラムを実行する情報処理装置であって、

記憶装置が着脱自在に装着されるインターフェース手段と、

前記インターフェース手段に装着された記憶装置に格納されているプログラムを実行する制御手段と、

前記プログラムと独立して動作し、前記インターフェース手段に装着された記憶装置からのデータの読み出し時間に基づいて前記記憶装置の真偽を判定する認証手段と、

を備えることを特徴とする情報処理装置。

【請求項2】

請求項1に記載の情報処理装置であって、

前記認証手段は、

認証用の基準値を格納する記憶部と、

前記インターフェース手段に装着された記憶装置に対して読み出し要求を行い、前記読み出し要求に応じて前記記憶装置から得られた値を格納する読み出し部と、

前記読み出し部に格納されている値を、前記読み出し部による読み出し要求がされてから所定の時間内に認証値として取得し、前記記憶部に記憶されている基準値と前記認証値とを比較する比較手段と、

を備え、

前記認証手段は、前記比較手段の比較結果に応じて前記記憶装置の真偽を判定することを特徴とする情報処理装置。

【請求項3】

請求項1または2に記載の情報処理装置であって、

前記認証手段は、前記インターフェース手段に装着された記憶装置の真偽を判定する論理回路を備えることを特徴とする情報処理装置。

【請求項4】

請求項1または2に記載の情報処理装置であって、

前記認証手段は、前記インターフェース手段に装着された記憶装置の真偽を判定するための認証プログラムを格納するROMを備えることを特徴とする情報処理装置。

【請求項5】

装着された記憶装置に格納されたプログラムを情報処理装置において実行する情報処理システムであって、

前記情報処理装置は、

記憶装置が着脱自在に装着されるインターフェース手段と、

前記インターフェース手段に装着された記憶装置に格納されているプログラムを実行する制御手段と、

前記プログラムと独立して動作し、前記インターフェース手段に装着された記憶装置からのデータの読み出し時間に基づいて前記記憶装置の真偽を判定する認証手段と、

を備えることを特徴とする情報処理システム。

【請求項6】

プログラムを格納した記憶装置が着脱自在に装着される情報処理装置において前記記憶装置を認証する認証方法であって、

(a) 前記情報処理装置が備える記憶部に認証用の基準値を格納する工程と、

(b) 前記プログラムから独立して動作する読み取り部によって前記記憶装置からの値の読み出し要求を行う工程と、

(c) 前記(b)工程において前記記憶装置から読み出された値を受信バッファに格納する工程と、

(d) 前記(b)工程における読み出し要求を行ってから所定の時間内に、前記受信バッファに格納されている値を認証値として取得する工程と、

(e) 前記(a)工程において前記記憶部に格納された基準値と前記(d)工程において取得された認証値とを比較する工程と、

(f) 前記(e)工程における比較結果に基づいて前記記憶装置の真偽を判定する工程と、

を有し、

前記所定の時間は前記記憶装置が真である場合の読み出し時間に応じて決定されることを特徴とする認証方法。

【請求項7】

請求項6に記載の認証方法であって、

(g) 少なくとも前記(b)工程を実行する前に、前記記憶装置の固定位置に固定値を格納する工程をさらに有し、

前記(a)工程において前記記憶部は前記固定値と同じ値を前記基準値として格納し、

前記(b)工程における読み出し要求は前記(g)工程において前記固定値を格納した前記固定位置から値を読み出す要求であることを特徴とする認証方法。

【請求項8】

請求項6に記載の認証方法であって、

前記(a)工程は、

(a-1) 前記記憶装置の所定の位置に格納された値を読み出す工程と、

(a-2) 前記(a-1)工程において読み出された値を基準値として前記記憶部に格納する工程と、

を有し、

前記(b)工程における読み出し部は、前記所定の位置からの読み出し要求を行うことを特徴とする認証方法。

【請求項9】

請求項8に記載の認証方法であって、

前記(a-1)工程における値の読み出しは、前記読み出し部によって実行され、

前記(a-1)工程において読み出された値は、前記読み出し部による読み出し要求を行ってから前記所定の時間内に前記記憶装置から得られた値であることを特徴とする認証方法。

【請求項10】

請求項6に記載の認証方法であって、

(h) 前記記憶装置から値の読み出しが行われたことを検出して、そのとき読み出された値と前記値の前記記憶装置における格納位置とを取得する工程をさらに有し、

前記(a)工程における前記記憶部は、前記(h)工程において取得された値を前記基準値として格納し、

前記(b)工程における前記読み出し部は、前記(h)工程において取得された格納位置からの読み出し要求を行うことを特徴とする認証方法。

【請求項11】

請求項8ないし10のいずれかに記載の認証方法であって、

前記(b)工程は、前記(a)工程が実行された後において、前記記憶装置から読み出される値が格納される受信バッファと前記記憶部とが参照され、前記受信バッファに格納されている値と、前記記憶部に格納されている基準値とが不一致であることが確認されてから実行されることを特徴とする認証方法。

【請求項12】

請求項6ないし11のいずれかに記載の認証方法であって、

(i) 前記所定の時間を変更する工程をさらに有し、

前記(b)工程は、前記(i)工程が実行されるたびに実行されることを特徴とする認証方法。

【請求項1】

記憶装置に格納されたプログラムを実行する情報処理装置であって、

記憶装置が着脱自在に装着されるインターフェース手段と、

前記インターフェース手段に装着された記憶装置に格納されているプログラムを実行する制御手段と、

前記プログラムと独立して動作し、前記インターフェース手段に装着された記憶装置からのデータの読み出し時間に基づいて前記記憶装置の真偽を判定する認証手段と、

を備えることを特徴とする情報処理装置。

【請求項2】

請求項1に記載の情報処理装置であって、

前記認証手段は、

認証用の基準値を格納する記憶部と、

前記インターフェース手段に装着された記憶装置に対して読み出し要求を行い、前記読み出し要求に応じて前記記憶装置から得られた値を格納する読み出し部と、