情報処理装置、情報処理方法、および、プログラム

【課題】全メモリに対するアクセスのインタリーブ数を2の乗数にすることで、メモリ構成に依存しないインタリーブを実施する。

【解決手段】WAY数S10a、S11a、S20a、S21a〜S80a、S81a、および、セグメント数S10b、S11b、S20b、S21b〜S80b、S81b、であるセグメント情報を保持するセグメント情報保持回路S10、S11、S20、S21〜S80、S81と、下限アドレスB10、B11、B20、B21〜B80、B81と、上限アドレスT10、T11、T20、T21〜T80、T81とを有し、メモリ構成上一部のメモリ空間のインタリーブ数が2の乗数を満たさない場合、任意のメモリの下限アドレスを底上げすることで、該当する単位メモリへのアクセスを2の乗数でインタリーブする。

【解決手段】WAY数S10a、S11a、S20a、S21a〜S80a、S81a、および、セグメント数S10b、S11b、S20b、S21b〜S80b、S81b、であるセグメント情報を保持するセグメント情報保持回路S10、S11、S20、S21〜S80、S81と、下限アドレスB10、B11、B20、B21〜B80、B81と、上限アドレスT10、T11、T20、T21〜T80、T81とを有し、メモリ構成上一部のメモリ空間のインタリーブ数が2の乗数を満たさない場合、任意のメモリの下限アドレスを底上げすることで、該当する単位メモリへのアクセスを2の乗数でインタリーブする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、情報処理装置、情報処理方法、および、プログラムに関し、特に、メモリ構成に依存しないインタリーブを実施する情報処理装置、情報処理方法、および、プログラムに関する。

【背景技術】

【0002】

従来、記憶装置のインタリーブ制御において常にインタリーブ数が常に2の乗数であることを実現するため、メモリチャネル配下のメモリの増設およびメモリ縮退に関して、インタリーブ数が2の乗数である条件を満たすメモリ数の単位で増設または縮退しなければならない制約があった。

【0003】

また、2の乗数以外のインタリーブ数(3、5、6、7〜)をハードウエアで実現した場合、複雑なアドレス変換回路の追加が必要である。

【0004】

特許文献1記載の従来技術は、異なるインタリーブグループを設定し、バンクを構成するサブバンク単位のメモリをインタリーブするものである。

【0005】

【特許文献1】特開平10−301842号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

特許文献1記載の技術の問題点は、バンク内のサブバンクの数によっては、インタリーブが実施できないことである。

【0007】

その理由は、特許文献1の図5バンク%4に、インタリーブグループ#1のサブバンクが存在すると、インタリーブグループ#1は、5WAYとなるからである。特許文献1の技術には、この場合の解決策が示されていない。

【0008】

本発明の目的は、全メモリに対するアクセスのインタリーブ数を2の乗数にすることで、メモリチャネル(バンク)配下に実装されるメモリ構成に依存しないインタリーブを実施する情報処理装置、情報処理方法、および、プログラムを提供することである。

【課題を解決するための手段】

【0009】

本発明の第1の情報処理装置は、複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御する情報処理装置であって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施する回路を有する。

【0010】

本発明の第2の情報処理装置は、前記第1の情報処理装置であって、前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブする回路を有する。

【0011】

本発明の第3の情報処理装置は、前記第2の情報処理装置であって、「WAY数Z1、Z2、・・・、Ziのいずれかと、同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリのアドレスからの底上げ分である下限アドレス底上げセグメント数との対」であるセグメント情報を保持するセグメント情報保持回路と、「同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリの上限アドレス+セグメント情報の前記単位メモリの下限アドレス底上げセグメント数=下限アドレス」を保持する下限アドレス回路と、「前記単位メモリの下限アドレス+セグメント情報の前記単位メモリのWAY数=上限アドレス」を保持する上限アドレス回路と、下限アドレス≦アクセスアドレス<上限アドレスであると、ヒット信号を出力し、アクセスアドレスに対しヒット信号の数のWAY数のインタリーブを行うアドレス変換回路と、を有する。

【0012】

本発明の第4の情報処理装置は、前記第3の情報処理装置であって、前記セグメント情報保持回路を備え、アクセスアドレスを出力するデータ処理装置と、アクセスアドレスを入力し、前記下限アドレス回路、前記上限アドレス回路、および、前記アドレス変換回路を備えるメモリコントローラと、を有する。

【0013】

本発明の第5の情報処理装置は、前記第4の情報処理装置であって、前記メモリコントローラに接続され、前記単位メモリを備えるメモリ装置を有する。

【0014】

本発明の第6の情報処理装置は、前記第3の情報処理装置であって、アクセスアドレスを出力するデータ処理装置と、前記下限アドレス回路、前記上限アドレス回路、および、前記アドレス変換回路を備えるメモリコントローラと、を有する。

【0015】

本発明の第7の情報処理装置は、前記第6の情報処理装置であって、前記メモリコントローラに接続され、前記単位メモリを備えるメモリ装置を有する。

【0016】

本発明の第1の情報処理方法は、複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御する情報処理方法であって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施する。

【0017】

本発明の第2の情報処理方法は、前記第1の情報処理方法であって、前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブする。

【0018】

本発明の第3の情報処理方法は、前記第2の情報処理方法であって、「WAY数Z1、Z2、・・・Ziのいずれかと、同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリのアドレスからの底上げ分である下限アドレス底上げセグメント数との対」であるセグメント情報を保持し、「同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリの上限アドレス+セグメント情報の前記単位メモリの下限アドレス底上げセグメント数=下限アドレス」を保持し、「前記単位メモリの下限アドレス+セグメント情報の前記単位メモリのWAY数=上限アドレス」を保持し、下限アドレス≦アクセスアドレス<上限アドレスであると、ヒット信号を出力し、アクセスアドレスに対しヒット信号の数のWAY数のインタリーブを行う。

【0019】

本発明の第1のプログラムは、情報処理装置に、複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御するプログラムであって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施させる。

【0020】

本発明の第2のプログラムは、前記第1のプログラムであって、前記情報処理装置に、前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブする制御を実施させる。

【発明の効果】

【0021】

本発明の効果は、メモリチャネル配下に実装されるメモリ構成に依存せず、全メモリに対するアクセスが簡素に実現できることである。

【0022】

その理由は、メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施するからである。

【発明を実施するための最良の形態】

【0023】

図1は、本発明を実施するための最良の形態の構成を示すブロック図である。

【0024】

図1を参照すると、本発明の情報処理装置は、データ処理装置L1(たとえば、CPU等)と、メモリコントローラL2と、メモリ装置L3とを含む。メモリ装置L3は、メモリチャネルCH1〜CH8を含む。メモリチャネルCH1〜CH8は、それぞれ、《第1単位記憶回路M10、第2単位記憶回路M11》〜《第1単位記憶回路M70、第2単位記憶回路M71》、《第1単位記憶回路M80》(たとえば、メモリ)を含む。

【0025】

単位記憶回路の総数Yは、2の乗数である最大WAY数X(ここでは、8)×2を超えない。総数Yは、図1の数に限定されない。最大WAY数Xは、事前に設定される。

【0026】

Xを超えない最大の2の乗数のWAY数Z1(ここでは、8)を定義し、順次、メモリチャネルCH1〜CH8に単位記憶回路を1つずつ第1単位記憶回路M10〜M80として単位記憶回路を割り当てる。残りの単位記憶回路を、第2単位記憶回路M11〜M71としてメモリチャネルCH1〜CH7に割り当てる。

【0027】

第1単位記憶回路M10〜M80をWAY数Z1(=8)でインタリーブし、残りの単位記憶回路があるので、残りの《Y(=15)−Z1(=8)》=7個の内の4個の第2単位記憶回路M11〜M41を、Xを超えない最大の2の乗数であるWAY数Z2(=4)でインタリーブし、・・・、Zi(最後)で、順次、残りの単位記憶回路を2の乗数でインタリーブする。ここで、第1単位記憶回路M10〜M80は、第2単位記憶回路M11〜M41にとって、《先にインタリーブが決定された》単位記憶回路である。

【0028】

また、メモリチャネルCH1〜CH8の第1単位記憶回路M10〜第2単位記憶回路M81(第1単位記憶回路M80、第2単位記憶回路M81は、ダミー)ごとに、WAY数Z1、Z2、・・・のいずれかと、下限アドレス底上げセグメント数との対を含むセグメント情報を格納するセグメント情報保持回路SG1をメモリチャネルごとにデータ処理装置L1、または、メモリコントローラL2に保持する。

【0029】

ここで、下限アドレス底上げセグメント数は、第2単位記憶回路M11〜M81に対しては、第1単位記憶回路M10〜M80からの底上げ分である。たとえば、WAY数Z1、Z2、Z3、Z4が割り当てられた場合、あるメモリチャネルの第1単位記憶回路が、WAY数Z1で、インタリーブされ、第2単位記憶回路が、WAY数Z2でインタリーブされる場合に、「《先にインタリーブが決定された》インタリーブ数の合計値×単位メモリ容量」を第2単位記憶回路に対する下限アドレス底上げセグメント数とすることが有効である。

【0030】

正確には、メモリチャネルCHkの第n単位メモリの下限アドレス底上げセグメント数は、同一メモリチャネルCHkで、かつ同一第n単位メモリで<先にインタリーブされている>と、残りのメモリチャネルCHkで第n単位メモリの底上げセグメント数=「同一第n単位メモリで先にインタリーブされたWAY数の総和」×単位メモリ容量とすることが有効である。

【0031】

たとえば、X=8であり、単位記憶回路が15個あると、メモリチャネルを《2の2乗=4》とし、メモリチャネルCH1〜メモリチャネルCH8に、まず、8個の単位記憶回路を第1単位記憶回路としてそれぞれ割り当て、次に、残りの15−8=7個の単位記憶回路を第1〜第7メモリに第2単位記憶回路として割り当てる。そして、メモリチャネルCH1〜メモリチャネルCH8の第1単位記憶回路を8WAYでインタリーブする。次に、メモリチャネルCH1〜メモリチャネルCH4の第2単位記憶回路を4WAYでインタリーブする。次に、メモリチャネルCH5〜メモリチャネルCH6の第2単位記憶回路を2WAYでインタリーブする。次に、メモリチャネルCH7の第2単位記憶回路を1WAYとする。

【0032】

また、たとえば、メモリチャネルCH1〜メモリチャネルCH4のセグメント情報は、第1単位記憶回路M10〜M40の《WAY数=8、下限アドレス底上げセグメント数=0》と、第2単位記憶回路M11〜M41の《WAY数=4、下限アドレス底上げセグメント数=0》とである。メモリチャネルCH5〜メモリチャネルCH6のセグメント情報は、第1単位記憶回路M50〜M60の《WAY数=8、下限アドレス底上げセグメント数=0》と、第2単位記憶回路M51〜M61の《WAY数=2、下限アドレス底上げセグメント数=4》とである。ここで、下限アドレス底上げセグメント数4は、「《先にインタリーブが決定された》インタリーブ数の合計値×単位メモリ容量」=4である。メモリチャネルCH7のセグメント情報は、第1単位記憶回路M70の《WAY数=8、下限アドレス底上げセグメント数=0》と、第2単位記憶回路M71の《WAY数=1、下限アドレス底上げセグメント数=6》とである。ここで、下限アドレス底上げセグメント数6は、「《先にインタリーブが決定された》インタリーブ数の合計値×単位メモリ容量」=4+2=6である。メモリチャネルCH8のセグメント情報は、第1単位記憶回路M80の《WAY数=8、下限アドレス底上げセグメント数=0》と、第2単位記憶回路M81の《WAY数=0、下限アドレス底上げセグメント数=0》とである。

【0033】

また、セグメント情報に基づいて、次のように定義する。第1単位記憶回路の下限アドレス=第1単位記憶回路の下限アドレス底上げセグメント数。第1単位記憶回路の上限アドレス=第1単位記憶回路の下限アドレス+第1単位記憶回路のWAY数。第2単位記憶回路の下限アドレス=第1単位記憶回路の上限アドレス+第2単位記憶回路の下限アドレス底上げセグメント数。第2単位記憶回路の上限アドレス=第2単位記憶回路の下限アドレス+第2単位記憶回路のWAY数。ここで、第1単位記憶回路の下限アドレスにベースアドレスを加算することも可能である。

【0034】

メモリをアクセスするメモリアドレスの所定の部分A(最大WAY数×2を表現するビット数以下)に対し、第1単位記憶回路の下限アドレス≦A<第1単位記憶回路の上限アドレス、第2単位記憶回路の下限アドレス≦A<第2単位記憶回路の上限アドレスを計算し、どちらかが成立する場合にヒットすると定義する。全てのメモリチャネルに対してヒットを調べる。ヒットが1つであれば、1WAYと見なす。ヒットが2つであれば、2WAYと見なす。ヒットが4つであれば、4WAYと見なす。ヒットが8つであれば、8WAYと見なす。・・・。次に、メモリアドレスの他の所定の部分Bに基づいて、メモリチャネルを選択し、メモリにアクセスを行う。

【0035】

セグメント情報を格納するセグメント情報保持回路SG1、《第1単位記憶回路の下限アドレス、第1単位記憶回路の上限アドレス、第2単位記憶回路の下限アドレス、および、第2単位記憶回路の上限アドレスを保持する上限下限アドレス回路ULA1は、メモリコントローラL2に設けることが可能である(図1(a))。また、セグメント情報保持回路SG1は、データ処理装置L1に設け、上限下限アドレス回路ULA1は、メモリコントローラL2に設けることが可能である(図1(b))。この場合、データ処理装置L1が、計算を実施し、メモリコントローラL2内の上限下限アドレス回路ULA1に値を設定する。

【0036】

以上は、単位記憶回路の総数Yが、2の乗数である最大WAY数X×2を超えない場合について説明したが、単位記憶回路の総数Y>2の乗数である最大WAY数X×2の場合にも本発明が適用可能である。この場合、Y/Xの商(整数)の個数の単位記憶回路を最大WAY数Xでインタリーブする。残りの、《Y−Y/Xの商(整数)》個の単位記憶回路を、第n単位記憶回路、第n+1単位記憶回路のように構成する。第n単位記憶回路、第n+1単位記憶回路をそれぞれ上述した第1単位記憶回路、第2単位記憶回路とみなしインタリーブする。

【0037】

本発明の第1の効果は、メモリチャネル配下に実装されるメモリ構成に依存せず、全メモリに対するアクセスがインタリーブ数2の乗数で実現でき、簡素で高速なメモリコントローラL2を提供できることである。

【0038】

第2の効果は、メモリコントローラL2配下に実装されるメモリの増設および縮退時のメモリ数に制限がなくなることである。すなわち、任意の数の単位でメモリ増設が可能となり、さらに、最小限のメモリ単位でメモリ縮退可能となる。

【0039】

その理由は、メモリチャネル配下の各メモリに割り付けられたアドレス空間情報、具体的には下限アドレスと上限アドレスの情報を保持する回路を有し、かつ、このアドレス空間が任意に可変設定可能とするためである。

【0040】

次に、本発明の実施例について図面を参照して詳細に説明する。

【0041】

以下、第1単位記憶回路、第2単位記憶回路を、単位メモリと記述する。

【0042】

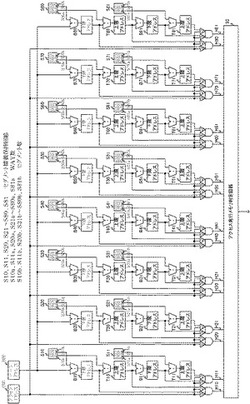

図2は、本発明の第1、第2、第3、第4の実施例のメモリコントローラのアドレス変換回路の構成を示すブロック図である。図3、図4、図5は、図2のアドレス変換回路の動作を示すための説明図である。

【0043】

図6は、本発明の第1の実施例の構成を示すブロック図である。図7、図8、図9は、本発明の第1の実施例の動作を示すための説明図である。

【0044】

図10は、本発明の第2の実施例の構成を示すブロック図である。図11、図12、図13は、本発明の第2の実施例の動作を示すための説明図である。

【0045】

図14は、本発明の第3の実施例の構成を示すブロック図である。図15、図16、図17は、本発明の第3の実施例の動作を示すための説明図である。

【0046】

図18は、本発明の第4の実施例の構成を示すブロック図である。図19、図20、図21は、本発明の第4の実施例の動作を示すための説明図である。

【0047】

第1〜第4の実施例において、差分は、実装される単位メモリ数のみであるため、ここでは、第1の実施例の図6について説明する。

【0048】

図6を参照すると、本発明の第1の実施例は、メモリコントローラ901と、メモリチャネルCH1〜CH8と、メモリチャネルCH1に接続される単位メモリm10、単位メモリm11と、メモリチャネルCH2に接続される単位メモリm20、単位メモリm21と、メモリチャネルCH3に接続される単位メモリm30、単位メモリm31と、メモリチャネルCH4に接続される単位メモリm40、m41と、メモリチャネルCH5に接続される単位メモリm50、単位メモリm51と、メモリチャネルCH6に接続される単位メモリm60、単位メモリm61と、メモリチャネルCH7に接続される単位メモリm70、単位メモリm71と、メモリチャネルCH8に接続される単位メモリm80、単位メモリm81と、メモリコントローラ901に内蔵されるアドレス変換回路91とを含む。

【0049】

メモリコントローラ901はインタフェース900を介してメモリアクセスを受け取りアドレス変換回路91でのアドレス変換結果からアクセス発行対象の単位メモリを単位メモリm10、m11、m20、m21〜m80、m81の中から決定しインタフェース100〜800を介して該当する単位メモリにアクセスを発行する。

【0050】

説明を簡素化するため、単位メモリm10、m11、m20、m21〜m80、m81は、全て8バイト単位アクセス×128ワード構成の容量1KBの単位メモリとする。よって、単位メモリのワードアドレスは、7ビットで構成される。また、各メモリチャネルCH1〜CH8に接続される単位メモリは最大2つまでとする。よって、メモリ最大構成時は、図6の示す通りとなり、メモリ容量は最大1KB×2×8=16KBとする。

【0051】

また、本実施例では、単位メモリの最小構成が1KBであり、この1KBをセグメント単位である。

【0052】

図2を参照すると、セグメント情報保持回路S10、S11、S20、S21〜S80、S81は、それぞれ、図6の単位メモリm10、m11、m20、m21〜m80、m81と対応している。各セグメント情報保持回路S10、S11、S20、S21〜S80、S81は、それぞれ、WAY数S10a、S11a、S20a、S21a〜S80a、S81aと下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bとを格納する。

【0053】

図2のセグメント情報保持回路S10、S11、S20、S21〜S80、S81は、図6の第1の実施例のメモリ最大構成時の設定値を格納する。単位メモリm10、m20、m30〜m80で8WAY制御するため、WAY数S10a、S20a、S30a〜S80aは、8を格納する。また、単位メモリm11、m21、m31〜m81で8WAY制御するため、WAY数S11a、S21a、S31a〜S81aは、8を格納する。下限アドレスの底上げは実施されないため、底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bは、全て0を格納する。

【0054】

図2のB10、B11、B20、B21〜B80、B81は、図6の単位メモリm10、m11、m20、m21〜m80、m81の下限アドレスを保持する回路である(以降、下限アドレスの値を指すこともある)。上限アドレスT10、T11、T20、T21〜T80、T81は、単位メモリm10、m11、m20、m21〜m80、m81の上限アドレスを保持する回路である(以降、上限アドレスの値を指すこともある)。下限アドレス、上限アドレスは、初期設定時に、セグメント情報保持回路S10、S11、S20、S21〜S80、S81に保持されている情報から各々算出され保持される。

【0055】

図2のベースアドレスB00は、メモリコントローラ901配下のメモリ空間のベースアドレスを示す。ベースアドレスB00を基に、単位メモリm10、m11、m20、m21〜m80、m81の下限アドレスB10、B11、B20、B21〜B80、B81と、上限アドレスT10、T11、T20、T21〜T80、T81とが算出される。

【0056】

本実施例では、図4の示すとおりベースアドレスB00は、常時0とする。

【0057】

図2のアクセスアドレスC00は、図6のインタフェース900経由でメモリコントローラ901に発行されたアクセスアドレスを格納する。

【0058】

図3に、アクセスアドレスC00の概要を示す。図3において、本実施例では、メモリ最大構成容量が16KBであるため、アドレスは、A13〜A0までの14ビットとする。また、メモリアクセス単位が8バイトであるため、アドレス変換には、8バイト境界アドレスより下位のA2〜A0以外のA13〜A3を参照する。さらに、本実施例の単位メモリの最小構成容量が1KBであるため、図2の各単位メモリの《下限アドレスB10、B11、B20、B21〜B80、B81、および、上限アドレスT10、T11、T20、T21〜T80、T81》とアクセスアドレスC00との比較は1KB境界より上位のA13〜A10の4ビットで実施する。

【0059】

ここで、単位メモリm10、m11、m20、m21〜m80、m81にそれぞれ対応する下限アドレスB10、B11、B20、B21〜B80、B81、および、上限アドレスT10、T11、T20、T21〜T80、T81の算出方法について説明する。

【0060】

メモリチャネルCH1に関しては、ベースアドレスB00を基に単位メモリm10の下限アドレスB10が算出され、次に、上限アドレスT10が算出され、次に、単位メモリm11の下限アドレスB11が算出され、次に、上限アドレスT11が算出される。

【0061】

メモリチャネルCH1の単位メモリm10の下限アドレスB10と上限アドレスT10とは、下記の式で求められる。計算は、1KB境界より上位の4ビットのみで実施され、結果が保持される。

【0062】

単位メモリm10の下限アドレスB10=ベースアドレスB00+下限アドレス底上げセグメント数S10b。単位メモリm10の上限アドレスT10=単位メモリm10の下限アドレスB10+WAY数S10a。

【0063】

メモリチャネルCH1の単位メモリm11の下限アドレスB11と上限アドレスT11とは、下記の式で求められる。計算は1KB境界より上位の4ビットのみで行われる。

【0064】

単位メモリm11の下限アドレスB11=単位メモリm10の上限アドレスT10+上限アドレス底上げセグメント数S11b。単位メモリm11の上限アドレスT11=単位メモリm11の下限アドレスB11+WAY数S11a。

【0065】

他のチャネルCH2〜CH8についても同様である。

【0066】

図2のヒット信号H10、H11、H20、H21〜H80、H81は、図6の単位メモリm10、m11、m20、m21〜m80、m81と対応している。たとえば、アクセスアドレスC00が、単位メモリm10の下限アドレスB10以上、かつ、上限アドレスT10未満であれば、H10が有効になる。また、メモリチャネルCH1のH10とH11、メモリチャネルCH2のH20とH21、メモリチャネルCH3のH30とH31、メモリチャネルCH4のH40とH41、メモリチャネルCH5のH50とH51、メモリチャネルCH6のH60とH61、メモリチャネルCH7のH70とH71、および、メモリチャネルCH8のH80とH81は、各メモリチャネル内でそれぞれ排他的に有効になる。

【0067】

図2のアクセス発行メモリ判定回路93は、ヒット信号H10、H11、H20、H21〜H80、H81からアクセス発行対象を単位メモリm10、m11、m20、m21〜m80、m81から選択する。

【0068】

アクセス発行メモリ判定回路93は、ヒット信号H10、H11、H20、H21〜H80、H81が1つだけ有効になった場合は、アクセスアドレスを1WAY領域とみなしヒット信号が有効になった該当単位メモリにアクセスを発行する。アクセス発行メモリ判定回路93は、ヒット信号H10、H11、H20、H21〜H80、H81の内2つ有効になった場合は、図5に示されるとおりアクセスアドレスを2WAY領域とみなし、アクセスアドレスC00のA3を参照し、ヒットした2つのメモリチャネルの内1つを選択し該当する単位メモリにアクセスを発行する。アクセス発行メモリ判定回路93は、ヒット信号H10、H11、H20、H21〜H80、H81の内4つ有効になった場合は、図5に示されるとおりアクセスアドレスを4WAY領域とみなし、アクセスアドレスC00のA4〜A3を参照しヒットした4つのメモリチャネルの内1つを選択し該当する単位メモリにアクセスを発行する。アクセス発行メモリ判定回路93は、ヒット信号H10、H11、H20、H21〜H80、H81の内8つ有効になった場合は、アクセスアドレスを図5に示されるとおり8WAY領域とみなし、アクセスアドレスC00のA5〜A3を参照しヒットした8つのメモリチャネルの内1つを選択し該当する単位メモリにアクセスを発行する。

【0069】

次に、本発明の第1の実施例の動作について、図2と図6、図7、図8、図9とを参照して説明する。

【0070】

第1の実施例は、従来からある8WAYインタリーブ(2の乗数)で制御する。

【0071】

図6において、メモリコントローラ901配下のメモリチャネルCH1〜CH8には単位メモリm10、m11、m20、m21〜m80、m81が接続されている、第1の実施例での各単位メモリに対するアドレス割り付けの概要を図8に示す。

【0072】

図8を参照すると、0KB以上〜8KB未満のアドレス領域では、単位メモリm10、m20〜m80の8WAYにてインタリーブ制御が実施される。8KB以上〜16KB未満のアドレス領域では、単位メモリm11、m21〜m81の8WAYにてインタリーブ制御が実施される。

【0073】

図8のアドレス割り付けを基に、セグメント情報保持回路S10、S11、S20、S21〜S80、S81のWAY数S10a、S11a、S20a、S21a〜S80a、S81aと下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bが、図7に示すとおりに決定される。

【0074】

図7を参照すると、第1の実施例では、全領域8WAYインタリーブであるため、WAY数S10a、S11a、S20a、S21a〜S80a、S81aには8が設定される。また、下限アドレスの底上げを実施していないため、下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bには0が設定される。

【0075】

図9に、第1の実施例での各単位メモリに対する詳細なアドレス割り付けを示す。単位メモリへのアクセス単位が8バイトであるため、アドレスの下位3ビットはX(任意)で表記している。

【0076】

次に、第1の実施例におけるアドレス変換回路91の詳細動作を図2を参照して説明する。

【0077】

下限アドレスB10、B11、B20、B21〜B80、B81、および、上限アドレスT10、T11、T20、T21〜T80、T81の値は、図7の設定値から下記のように算出される。メモリチャネルCH1の単位メモリm10の下限アドレスB10、上限アドレスT10は、下記の式で算出される。

【0078】

単位メモリm10の下限アドレスB10=(ベースアドレスB00)0KB+(下限アドレス底上げセグメント数S10b)0KB=0KB。単位メモリm10の上限アドレスT10=(単位メモリm10の下限アドレスB10)0KB+(WAY数S10a)8KB=8KB。

【0079】

よって、単位メモリm10のアドレス領域は、0KB以上〜8KB未満となる。同様に、単位メモリm20、m30〜m80の下限アドレスおよび上限アドレスについても同値となる。

【0080】

メモリチャネルCH1の単位メモリm11の下限アドレスB11、上限アドレスT11は、下記の式で算出される。

【0081】

単位メモリm11の下限アドレスB11=(単位メモリm10の上限アドレスT10)8KB+(下限アドレス底上げセグメント数S11b)0KB=8KB。単位メモリm11の上限アドレスT11=(単位メモリm11の下限アドレスB11)8KB+(WAY数S11a)8KB=16KB。

【0082】

よって、単位メモリm11のアドレス領域は8KB以上〜16KB未満となる。同様に単位メモリm21、m31〜m81の下限アドレスおよび上限アドレスについても同値となる。

【0083】

第1の実施例において、アクセスアドレスC00に0KB以上〜8KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値からヒット信号H10、H20〜H80の8つの信号が有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを8WAY領域とみなし、アクセスアドレスC00のA5〜A3でアクセス先のメモリチャネルを判定し、単位メモリm10、m20〜m80の内のいずれかひとつにアクセスを発行する。同様に、アクセスアドレスC00に8KB以上〜16KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値からヒット信号H11、H21〜H81の8つの信号が有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを8WAY領域とみなし、アクセスアドレスC00のA5〜A3でアクセス先のメモリチャネルを判定し、単位メモリm11、単位メモリm21〜m81の内のいずれかひとつにアクセスを発行する。

【0084】

次に、本発明の第2の実施例について、図2と図10、図11、図12、図13とを参照して説明する。

【0085】

第2の実施例は、従来からある4WAYと2WAYインタリーブ(2の乗数)との混在で制御する。

【0086】

図10を参照すると、メモリコントローラ901配下のメモリチャネルCH1〜CH4には、単位メモリm10、m20、m30、m40、m11、m21が接続されている。メモリチャネルCH5〜CH8は未使用である。第2の実施例での各単位メモリに対するアドレス割り付けの概要を図12に示す。

【0087】

図12を参照すると、0KB以上〜4KB未満のアドレス領域では単位メモリm10、m20、m30、m40の4WAYにてインタリーブ制御が実施される。4KB以上〜6KB未満のアドレス領域では単位メモリm11、m21の2WAYにてインタリーブ制御が実施される。

【0088】

図12のアドレス割り付けを基に、セグメント情報保持回路S10、S11、S20、S21〜S80、S81のWAY数S10a、S11a、S20a、S21a〜S80a、S81aと下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81が、図11に示すとおりに決定される。

【0089】

図11を参照すると、第2の実施例では、WAY数S10a、S20a、S301a、S40aには4が設定され、WAY数S11a、S21aには2が設定され、未使用セグメントについては0が設定される。また、下限アドレスの底上げを実施していないため下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bには0が設定される。

【0090】

図13に第2の実施例での各単位メモリに対する詳細なアドレス割り付けを示す。単位メモリへのアクセス単位が8バイトであるため、アドレスの下位3ビットは、X(任意)で表記している。

【0091】

第2の実施例におけるアドレス変換回路91の詳細動作を図2を参照して説明する。

【0092】

下限アドレスB10、B11、B20、B21〜B80、B81、および、上限アドレスT10、T11、T20、T21〜T80、T81の値は、図11の設定値から下記のように算出される。

【0093】

メモリチャネルCH1の単位メモリm10の下限アドレスB10、および、上限アドレスT10は下記の式で算出される。

単位メモリm10の下限アドレスB10=(ベースアドレスB00)0KB+(下限アドレス底上げセグメント数S10b)0KB=0KB。単位メモリm10の上限アドレスT10=(単位メモリm10の下限アドレスB10)0KB+(WAY数S10a)4KB=4KB。

【0094】

よって、単位メモリm10のアドレス領域は、0KB以上〜4KB未満となる。同様に単位メモリm20、m30、m40の下限アドレス、および、上限アドレスについても同値となる。

【0095】

メモリチャネルCH1の単位メモリm11の下限アドレスB11、上限アドレスT11は、下記の式で算出される。

【0096】

単位メモリm11の下限アドレスB11=(単位メモリm10の上限アドレスT10)4KB+(下限アドレス底上げセグメント数S11b)0KB=4KB。単位メモリm11の上限アドレスT11=(単位メモリm11の下限アドレスB11)4KB+(WAY数S11a)2KB=6KB。

【0097】

よって、単位メモリm11のアドレス領域は、4KB以上〜6KB未満となる。同様に単位メモリm21の下限アドレスおよび上限アドレスについても同値となる。

【0098】

第2の実施例において、アクセスアドレスC00に0KB以上〜4KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値から、ヒット信号H10、H20、H30、H40の4つの信号が有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを4WAY領域とみなし、アクセスアドレスC00のA4〜A3で、アクセス先のメモリチャネルを判定し、単位メモリm10、m20、m30、m40の内のいずれかひとつにアクセスを発行する。同様に、アクセスアドレスC00に4KB以上〜6KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値からヒット信号H11、H21の2つの信号が有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを2WAY領域とみなし、アクセスアドレスC00のA3で、アクセス先のメモリチャネルを判定し、単位メモリm11、m21の内のいずれかひとつにアクセスを発行する。

【0099】

次に、本発明の第3の実施例について、図2と図14、図15、図16、図17とを参照して説明する。

【0100】

第3の実施例は、従来であれば、8WAYと3WAYとのインタリーブ混在で制御するが、アドレス変換回路91により3WAY領域を2WAYと1WAY領域とに置き換えて制御する。

【0101】

図14を参照すると、メモリコントローラ901配下のメモリチャネルCH1〜CH8には、単位メモリm10、m20、m30〜m80、m11、m21、m31が接続されている。

【0102】

第3の実施例での各単位メモリに対するアドレス割り付けの概要を図16に示す。

【0103】

図16を参照すると、第3の実施例は、0KB以上〜8KB未満のアドレス領域では、第1の実施例と同様に、単位メモリm10、m20〜m80の8WAYにてインタリーブ制御を実施する。8KB以上〜11KB未満のアドレス領域では、従来は、単位メモリm11、m21、m31の3WAYにてインタリーブ制御が実施されるが、本発明の第3の実施例では、3WAYを2WAYと1WAYに置き換えることで全アドレス空間にて2の乗数のインタリーブが実現される。具体的には、8KB以上〜10KB未満のアドレス領域では単位メモリm11、m21の2WAYにてインタリーブ制御が実施され、10KB以上〜11KB未満のアドレス領域では、単位メモリm31の1WAYにてインタリーブ制御が実施される。3WAYから2WAYと1WAYへの置き換えは、単位メモリm31の下限アドレスを2KB(2セグメント)底上げすることで実現される。

【0104】

図16のアドレス割り付けを基に、図2のセグメント情報保持回路S10、S11、S20、S21〜S80、S81のWAY数S10a、S11a、S20a、S21a〜S80a、S81aと下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bが図15に示すとおりに決定される。

【0105】

図15について、第3の実施例では、WAY数S10a、S20a、S301a、S40a〜S80aには8が設定され、WAY数S11a、S21aには2が設定され、WAY数S31aには1が設定され、未使用セグメントについては0が設定される。また、単位メモリm31の下限アドレスに2KB(2セグメント)の底上げを実施するため下限アドレス底上げセグメント数S31bに2が設定される。

【0106】

図17に、第3の実施例での各単位メモリに対する詳細なアドレス割り付けを示す。単位メモリへのアクセス単位が8バイトであるためアドレスの下位3ビットはXで表記している。

【0107】

第3の実施例におけるアドレス変換回路91の詳細動作を図2を用いて説明する。

【0108】

図2の下限アドレスB10、B11、B20、B21〜B80、B81、および、上限アドレスT10、T11、T20、T21〜T80、T81の値は図15の設定値から下記のように算出される。メモリチャネルCH1の単位メモリm10の下限アドレスB10、および、上限アドレスT10は下記の式で算出される。

【0109】

単位メモリm10の下限アドレスB10=(ベースアドレスB00)0KB+(下限アドレス底上げセグメント数S10b)0KB=0KB。単位メモリm10の上限アドレスT10=(単位メモリm10の下限アドレスB10)0KB+(WAY数S10a)8KB=8KB。

【0110】

よって、単位メモリm10のアドレス領域は0KB以上〜8KB未満となる。同様に、単位メモリm20、m30〜m80の下限アドレスおよび上限アドレスについても同値となる。

【0111】

メモリチャネルCH1の単位メモリm11の下限アドレスB11、および、上限アドレスT11は下記の式で算出される。

【0112】

単位メモリm11の下限アドレスB11=(単位メモリm10の上限アドレスT10)8KB+(下限アドレス底上げセグメント数S11b)0KB=8KB。単位メモリm11の上限アドレスT11=(単位メモリm11の下限アドレスB11)8KB+(WAY数S11a)2KB=10KB。

【0113】

よって、単位メモリm11のアドレス領域は8KB以上〜10KB未満となる。同様に、単位メモリm21の下限アドレスおよび上限アドレスについても同値となる。

【0114】

底上げを実施するメモリチャネルCH3の単位メモリm31の下限アドレスB31、および、上限アドレスT31は下記の式で算出される。

【0115】

単位メモリm31の下限アドレスB31=(単位メモリm30の上限アドレスT30)8KB+(下限アドレス底上げセグメント数S31b)2KB=10KB。単位メモリm31の上限アドレスT31=(単位メモリm31の下限アドレスB31)10KB+(WAY数S31a)1KB=11KB。

【0116】

よって、単位メモリm31のアドレス領域は10KB以上〜11KB未満となる。

【0117】

第3の実施例において、アクセスアドレスC00に0KB以上〜8KB未満のアドレスが格納された場合は、第1の実施例と同じなので説明を省略する。アクセスアドレスC00に8KB以上〜10KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値から、ヒット信号H11、H21の2つの信号が有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを2WAY領域とみなし、アクセスアドレスC00のA3でアクセス発行先のメモリチャネルを判定し、単位メモリm11、m21の内のいずれかひとつにアクセスを発行する、同様に、アクセスアドレスC00に10KB以上〜11KB未満のアドレスが格納されると、下限アドレスと上限アドレスの設定値からヒット信号H31のみが有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを1WAY領域とみなし単位メモリm31に対してアクセスを発行する。

【0118】

次に、本発明の第4の実施例について、図2と図18、図19、図20、図21とを参照して説明する。

【0119】

第4の実施例は、従来であれば、8WAYと7WAYとのインタリーブ混在で制御するが、アドレス変換回路91により7WAY領域を4WAYと2WAYと1WAY領域とに置き換えて制御する。

【0120】

図18を参照すると、メモリコントローラ901配下のメモリチャネルCH1〜CH8には、単位メモリm10、m20、m30〜m80、m11、m21〜m71が接続されている。第4の実施例での各単位メモリに対するアドレス割り付けの概要を図20に示す。

【0121】

図20を参照すると、0KB以上〜8KB未満のアドレス領域では、第1の実施例と同様に単位メモリm10、m20〜m80の8WAYにてインタリーブ制御が実施される。8KB以上〜15KB未満のアドレス領域では、従来は、単位メモリm11、m21〜m71の7WAYにてインタリーブ制御が実施されていた。本発明の第4の実施例では、7WAYを4WAYと2WAYと1WAYに置き換えることで、全アドレス空間にて2の乗数のインタリーブが実現される。

【0122】

具体的には、8KB以上〜12KB未満のアドレス領域では、単位メモリm11、m21、m31、m41の4WAYにてインタリーブ制御が実施される。12KB以上〜14KB未満のアドレス領域では、単位メモリm51、m61の2WAYにてインタリーブ制御が実施される。14KB以上〜15KB未満のアドレス領域では、単位メモリm71の1WAYにてインタリーブ制御が実施される。7WAYから4WAY、2WAY、および、1WAYへの置き換えは、単位メモリm51、m61の下限アドレスを4KB(4セグメント)底上げすることと、単位メモリm71の下限アドレスを6KB(6セグメント)底上げすることとで実現される。

【0123】

図20のアドレス割り付けを基に、セグメント情報保持回路S10、S11、S20、S21〜S80、S81のWAY数S10a、S11a、S20a、S21a〜S80a、S81a、および、下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bが図19に示すとおりに決定される。

【0124】

図19を参照すると、第4の実施例では、WAY数S10a、S20a、S301a、S40a〜S80aには8が設定される。WAY数S11a、S21a、S31a、S41aには4が設定される。WAY数S51a、S61aには2が設定される。WAY数S71aには1が設定される。その他の未使用単位メモリに対応するセグメントには、0が設定される。また、単位メモリm51、m61の下限アドレスに4KB(4セグメント)の底上げを実施するため、下限アドレス底上げセグメント数S51b、S61bに4が設定される。また、単位メモリm71の下限アドレスに6KB(6セグメント)の底上げを実施するため、下限アドレス底上げセグメント数S71bに6が設定される。

【0125】

図21に、第4の実施例での各単位メモリに対する詳細なアドレス割り付けを示す。単位メモリへのアクセス単位が8バイトであるため、アドレスの下位3ビットは、X(任意)で表記している。

【0126】

第4の実施例におけるアドレス変換回路91の詳細動作を、図2を参照して説明する。

【0127】

図2の下限アドレスB10、B11、B20、B21〜B80、B81と上限アドレスT10、T11、T20、T21〜T80、T81の値は、図19の設定値から下記のように算出される。

【0128】

メモリチャネルCH1の単位メモリm10の下限アドレスB10、および、上限アドレスT10は下記の式で算出される。

【0129】

単位メモリm10の下限アドレスB10=(ベースアドレスB00)0KB+(下限アドレス底上げセグメント数S10b)0KB=0KB。単位メモリm10の上限アドレスT10=(単位メモリm10の下限アドレスB10)0KB+(WAY数S10a)8KB=8KB。

【0130】

よって、単位メモリm10のアドレス領域は、0KB以上〜8KB未満となる。同様に、単位メモリm20、m30〜m80の下限アドレスおよび上限アドレスについても同値となる。

【0131】

メモリチャネルCH1の単位メモリm11の下限アドレスB11、および、上限アドレスT11は下記の式で算出される。

【0132】

単位メモリm11の下限アドレスB11=(単位メモリm10の上限アドレスT10)8KB+(下限アドレス底上げセグメント数S11b)0KB=8KB。単位メモリm11の上限アドレスT11=(単位メモリm11の下限アドレスB11)8KB+(WAY数S11a)4KB=12KB。

【0133】

よって、単位メモリm11のアドレス領域は、8KB以上〜12KB未満となる。同様に、単位メモリm21、単位メモリm31、単位メモリm41の下限アドレスおよび上限アドレスについても同値となる。

【0134】

底上げを実施するメモリチャネルCH5、CH6の単位メモリm51、m61の下限アドレスB51、B61、および、上限アドレスT51、T61は下記の式で算出される。

【0135】

単位メモリm51の下限アドレスB51=(単位メモリm50の上限アドレスT50)8KB+(下限アドレス底上げセグメント数S51b)4KB=12KB。ここで、(下限アドレス底上げセグメント数S51b)4KBは、「《先にインタリーブが決定された》インタリーブ数の合計値×単位メモリ容量」=4×1KBである。単位メモリm51の上限アドレスT51=(単位メモリm51の下限アドレスB51)12KB+(WAY数S51a)2KB=14KB。

【0136】

よって、単位メモリm11のアドレス領域は、12KB以上〜14KB未満となる。同様に、単位メモリm61の下限アドレス、および、上限アドレスについても同値となる。

【0137】

さらに、底上げを実施するメモリチャネルCH7の単位メモリm71の下限アドレスB71と上限アドレスT71は、下記の式で算出される。

【0138】

単位メモリm71の下限アドレスB71=(単位メモリm70の上限アドレスT70)8KB+(下限アドレス底上げセグメント数S71b)6KB=14KB。ここで、(下限アドレス底上げセグメント数S71b)6KBは、「《先にインタリーブが決定された》インタリーブ数の合計値×単位メモリ容量」=(4+2)×1KBである。単位メモリm71の上限アドレスT71=(単位メモリm71の下限アドレスB71)14KB+(WAY数S71a)1KB=15KB。

【0139】

よって、単位メモリm71のアドレス領域は、14KB以上〜15KB未満となる。

【0140】

第4の実施例において、アクセスアドレスC00に0KB以上〜8KB未満のアドレスが格納された場合は、第1の実施例と同じなので説明を省略する。アクセスアドレスC00に8KB以上〜12KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値から、ヒット信号H11、H21、H31、H41の4つの信号が有効になる。アクセス発行メモリ判定回路93は、4WAY領域とみなし、アクセスアドレスC00のA4〜A3でアクセス発行先のメモリチャネルを判定し、単位メモリm11、m21、m31、m41の内のいずれかひとつにアクセスを発行する。同様に、アクセスアドレスC00に、12KB以上〜14KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値からヒット信号H51、H61の2つの信号が有効になる。アクセス発行メモリ判定回路93は、2WAY領域とみなし、アクセスアドレスC00のA3で、アクセス発行先のメモリチャネルを判定し、単位メモリm51、m61の内のいずれかひとつにアクセスを発行する。同様に、アクセスアドレスC00に、14KB以上〜15KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値からヒット信号H71のみが有効になる。アクセス発行メモリ判定回路93は、1WAY領域とみなし単位メモリm71に対してアクセスを発行する。

【0141】

以上説明した制御を、コントロールストアを設け、ファームウェアで実施することが可能である。

【図面の簡単な説明】

【0142】

【図1】本発明を実施するための最良の形態の構成を示すブロック図。

【図2】本発明のアドレス変換回路の構成を示すブロック図。

【図3】アドレス変換回路の動作を示すための説明図。

【図4】アドレス変換回路の動作を示すための説明図。

【図5】アドレス変換回路の動作を示すための説明図。

【図6】本発明の第1の実施例の構成を示すブロック図。

【図7】本発明の第1の実施例の動作を示すための説明図。

【図8】本発明の第1の実施例の動作を示すための説明図。

【図9】本発明の第1の実施例の動作を示すための説明図。

【図10】本発明の第2の実施例の構成を示すブロック図。

【図11】本発明の第2の実施例の動作を示すための説明図。

【図12】本発明の第2の実施例の動作を示すための説明図。

【図13】本発明の第2の実施例の動作を示すための説明図。

【図14】本発明の第3の実施例の構成を示すブロック図。

【図15】本発明の第3の実施例の動作を示すための説明図。

【図16】本発明の第3の実施例の動作を示すための説明図。

【図17】本発明の第3の実施例の動作を示すための説明図。

【図18】本発明の第4の実施例の構成を示すブロック図。

【図19】本発明の第4の実施例の動作を示すための説明図。

【図20】本発明の第4の実施例の動作を示すための説明図。

【図21】本発明の第4の実施例の動作を示すための説明図。

【符号の説明】

【0143】

L1 データ処理装置

L2 メモリコントローラ

L3 メモリ装置

CH1 メモリチャネル

CH2 メモリチャネル

CH3 メモリチャネル

CH4 メモリチャネル

CH5 メモリチャネル

CH6 メモリチャネル

CH7 メモリチャネル

CH8 メモリチャネル

M10〜M80 第1単位記憶回路

M11〜M81 第2単位記憶回路

m10、m11、m20、m21〜m80、m81 単位メモリ

SG1 セグメント情報保持回路

ULA1 上限下限アドレス回路

B00 ベースアドレス

C00 アクセスアドレス

S10、S11、S20、S21〜S80、S81 セグメント情報保持回路

S10a、S11a、S20a、S21a〜S80a、S81a WAY数

S10b、S11b、S20b、S21b〜S80b、S81b セグメント数

B10、B11、B20、B21〜B80、B81 下限アドレス

T10、T11、T20、T21〜T80、T81 上限アドレス

91 アドレス変換回路

93 アクセス発行メモリ判定回路

900 インタフェース

901 メモリコントローラ

100〜800 インタフェース

【技術分野】

【0001】

本発明は、情報処理装置、情報処理方法、および、プログラムに関し、特に、メモリ構成に依存しないインタリーブを実施する情報処理装置、情報処理方法、および、プログラムに関する。

【背景技術】

【0002】

従来、記憶装置のインタリーブ制御において常にインタリーブ数が常に2の乗数であることを実現するため、メモリチャネル配下のメモリの増設およびメモリ縮退に関して、インタリーブ数が2の乗数である条件を満たすメモリ数の単位で増設または縮退しなければならない制約があった。

【0003】

また、2の乗数以外のインタリーブ数(3、5、6、7〜)をハードウエアで実現した場合、複雑なアドレス変換回路の追加が必要である。

【0004】

特許文献1記載の従来技術は、異なるインタリーブグループを設定し、バンクを構成するサブバンク単位のメモリをインタリーブするものである。

【0005】

【特許文献1】特開平10−301842号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

特許文献1記載の技術の問題点は、バンク内のサブバンクの数によっては、インタリーブが実施できないことである。

【0007】

その理由は、特許文献1の図5バンク%4に、インタリーブグループ#1のサブバンクが存在すると、インタリーブグループ#1は、5WAYとなるからである。特許文献1の技術には、この場合の解決策が示されていない。

【0008】

本発明の目的は、全メモリに対するアクセスのインタリーブ数を2の乗数にすることで、メモリチャネル(バンク)配下に実装されるメモリ構成に依存しないインタリーブを実施する情報処理装置、情報処理方法、および、プログラムを提供することである。

【課題を解決するための手段】

【0009】

本発明の第1の情報処理装置は、複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御する情報処理装置であって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施する回路を有する。

【0010】

本発明の第2の情報処理装置は、前記第1の情報処理装置であって、前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブする回路を有する。

【0011】

本発明の第3の情報処理装置は、前記第2の情報処理装置であって、「WAY数Z1、Z2、・・・、Ziのいずれかと、同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリのアドレスからの底上げ分である下限アドレス底上げセグメント数との対」であるセグメント情報を保持するセグメント情報保持回路と、「同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリの上限アドレス+セグメント情報の前記単位メモリの下限アドレス底上げセグメント数=下限アドレス」を保持する下限アドレス回路と、「前記単位メモリの下限アドレス+セグメント情報の前記単位メモリのWAY数=上限アドレス」を保持する上限アドレス回路と、下限アドレス≦アクセスアドレス<上限アドレスであると、ヒット信号を出力し、アクセスアドレスに対しヒット信号の数のWAY数のインタリーブを行うアドレス変換回路と、を有する。

【0012】

本発明の第4の情報処理装置は、前記第3の情報処理装置であって、前記セグメント情報保持回路を備え、アクセスアドレスを出力するデータ処理装置と、アクセスアドレスを入力し、前記下限アドレス回路、前記上限アドレス回路、および、前記アドレス変換回路を備えるメモリコントローラと、を有する。

【0013】

本発明の第5の情報処理装置は、前記第4の情報処理装置であって、前記メモリコントローラに接続され、前記単位メモリを備えるメモリ装置を有する。

【0014】

本発明の第6の情報処理装置は、前記第3の情報処理装置であって、アクセスアドレスを出力するデータ処理装置と、前記下限アドレス回路、前記上限アドレス回路、および、前記アドレス変換回路を備えるメモリコントローラと、を有する。

【0015】

本発明の第7の情報処理装置は、前記第6の情報処理装置であって、前記メモリコントローラに接続され、前記単位メモリを備えるメモリ装置を有する。

【0016】

本発明の第1の情報処理方法は、複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御する情報処理方法であって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施する。

【0017】

本発明の第2の情報処理方法は、前記第1の情報処理方法であって、前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブする。

【0018】

本発明の第3の情報処理方法は、前記第2の情報処理方法であって、「WAY数Z1、Z2、・・・Ziのいずれかと、同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリのアドレスからの底上げ分である下限アドレス底上げセグメント数との対」であるセグメント情報を保持し、「同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリの上限アドレス+セグメント情報の前記単位メモリの下限アドレス底上げセグメント数=下限アドレス」を保持し、「前記単位メモリの下限アドレス+セグメント情報の前記単位メモリのWAY数=上限アドレス」を保持し、下限アドレス≦アクセスアドレス<上限アドレスであると、ヒット信号を出力し、アクセスアドレスに対しヒット信号の数のWAY数のインタリーブを行う。

【0019】

本発明の第1のプログラムは、情報処理装置に、複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御するプログラムであって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施させる。

【0020】

本発明の第2のプログラムは、前記第1のプログラムであって、前記情報処理装置に、前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブする制御を実施させる。

【発明の効果】

【0021】

本発明の効果は、メモリチャネル配下に実装されるメモリ構成に依存せず、全メモリに対するアクセスが簡素に実現できることである。

【0022】

その理由は、メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施するからである。

【発明を実施するための最良の形態】

【0023】

図1は、本発明を実施するための最良の形態の構成を示すブロック図である。

【0024】

図1を参照すると、本発明の情報処理装置は、データ処理装置L1(たとえば、CPU等)と、メモリコントローラL2と、メモリ装置L3とを含む。メモリ装置L3は、メモリチャネルCH1〜CH8を含む。メモリチャネルCH1〜CH8は、それぞれ、《第1単位記憶回路M10、第2単位記憶回路M11》〜《第1単位記憶回路M70、第2単位記憶回路M71》、《第1単位記憶回路M80》(たとえば、メモリ)を含む。

【0025】

単位記憶回路の総数Yは、2の乗数である最大WAY数X(ここでは、8)×2を超えない。総数Yは、図1の数に限定されない。最大WAY数Xは、事前に設定される。

【0026】

Xを超えない最大の2の乗数のWAY数Z1(ここでは、8)を定義し、順次、メモリチャネルCH1〜CH8に単位記憶回路を1つずつ第1単位記憶回路M10〜M80として単位記憶回路を割り当てる。残りの単位記憶回路を、第2単位記憶回路M11〜M71としてメモリチャネルCH1〜CH7に割り当てる。

【0027】

第1単位記憶回路M10〜M80をWAY数Z1(=8)でインタリーブし、残りの単位記憶回路があるので、残りの《Y(=15)−Z1(=8)》=7個の内の4個の第2単位記憶回路M11〜M41を、Xを超えない最大の2の乗数であるWAY数Z2(=4)でインタリーブし、・・・、Zi(最後)で、順次、残りの単位記憶回路を2の乗数でインタリーブする。ここで、第1単位記憶回路M10〜M80は、第2単位記憶回路M11〜M41にとって、《先にインタリーブが決定された》単位記憶回路である。

【0028】

また、メモリチャネルCH1〜CH8の第1単位記憶回路M10〜第2単位記憶回路M81(第1単位記憶回路M80、第2単位記憶回路M81は、ダミー)ごとに、WAY数Z1、Z2、・・・のいずれかと、下限アドレス底上げセグメント数との対を含むセグメント情報を格納するセグメント情報保持回路SG1をメモリチャネルごとにデータ処理装置L1、または、メモリコントローラL2に保持する。

【0029】

ここで、下限アドレス底上げセグメント数は、第2単位記憶回路M11〜M81に対しては、第1単位記憶回路M10〜M80からの底上げ分である。たとえば、WAY数Z1、Z2、Z3、Z4が割り当てられた場合、あるメモリチャネルの第1単位記憶回路が、WAY数Z1で、インタリーブされ、第2単位記憶回路が、WAY数Z2でインタリーブされる場合に、「《先にインタリーブが決定された》インタリーブ数の合計値×単位メモリ容量」を第2単位記憶回路に対する下限アドレス底上げセグメント数とすることが有効である。

【0030】

正確には、メモリチャネルCHkの第n単位メモリの下限アドレス底上げセグメント数は、同一メモリチャネルCHkで、かつ同一第n単位メモリで<先にインタリーブされている>と、残りのメモリチャネルCHkで第n単位メモリの底上げセグメント数=「同一第n単位メモリで先にインタリーブされたWAY数の総和」×単位メモリ容量とすることが有効である。

【0031】

たとえば、X=8であり、単位記憶回路が15個あると、メモリチャネルを《2の2乗=4》とし、メモリチャネルCH1〜メモリチャネルCH8に、まず、8個の単位記憶回路を第1単位記憶回路としてそれぞれ割り当て、次に、残りの15−8=7個の単位記憶回路を第1〜第7メモリに第2単位記憶回路として割り当てる。そして、メモリチャネルCH1〜メモリチャネルCH8の第1単位記憶回路を8WAYでインタリーブする。次に、メモリチャネルCH1〜メモリチャネルCH4の第2単位記憶回路を4WAYでインタリーブする。次に、メモリチャネルCH5〜メモリチャネルCH6の第2単位記憶回路を2WAYでインタリーブする。次に、メモリチャネルCH7の第2単位記憶回路を1WAYとする。

【0032】

また、たとえば、メモリチャネルCH1〜メモリチャネルCH4のセグメント情報は、第1単位記憶回路M10〜M40の《WAY数=8、下限アドレス底上げセグメント数=0》と、第2単位記憶回路M11〜M41の《WAY数=4、下限アドレス底上げセグメント数=0》とである。メモリチャネルCH5〜メモリチャネルCH6のセグメント情報は、第1単位記憶回路M50〜M60の《WAY数=8、下限アドレス底上げセグメント数=0》と、第2単位記憶回路M51〜M61の《WAY数=2、下限アドレス底上げセグメント数=4》とである。ここで、下限アドレス底上げセグメント数4は、「《先にインタリーブが決定された》インタリーブ数の合計値×単位メモリ容量」=4である。メモリチャネルCH7のセグメント情報は、第1単位記憶回路M70の《WAY数=8、下限アドレス底上げセグメント数=0》と、第2単位記憶回路M71の《WAY数=1、下限アドレス底上げセグメント数=6》とである。ここで、下限アドレス底上げセグメント数6は、「《先にインタリーブが決定された》インタリーブ数の合計値×単位メモリ容量」=4+2=6である。メモリチャネルCH8のセグメント情報は、第1単位記憶回路M80の《WAY数=8、下限アドレス底上げセグメント数=0》と、第2単位記憶回路M81の《WAY数=0、下限アドレス底上げセグメント数=0》とである。

【0033】

また、セグメント情報に基づいて、次のように定義する。第1単位記憶回路の下限アドレス=第1単位記憶回路の下限アドレス底上げセグメント数。第1単位記憶回路の上限アドレス=第1単位記憶回路の下限アドレス+第1単位記憶回路のWAY数。第2単位記憶回路の下限アドレス=第1単位記憶回路の上限アドレス+第2単位記憶回路の下限アドレス底上げセグメント数。第2単位記憶回路の上限アドレス=第2単位記憶回路の下限アドレス+第2単位記憶回路のWAY数。ここで、第1単位記憶回路の下限アドレスにベースアドレスを加算することも可能である。

【0034】

メモリをアクセスするメモリアドレスの所定の部分A(最大WAY数×2を表現するビット数以下)に対し、第1単位記憶回路の下限アドレス≦A<第1単位記憶回路の上限アドレス、第2単位記憶回路の下限アドレス≦A<第2単位記憶回路の上限アドレスを計算し、どちらかが成立する場合にヒットすると定義する。全てのメモリチャネルに対してヒットを調べる。ヒットが1つであれば、1WAYと見なす。ヒットが2つであれば、2WAYと見なす。ヒットが4つであれば、4WAYと見なす。ヒットが8つであれば、8WAYと見なす。・・・。次に、メモリアドレスの他の所定の部分Bに基づいて、メモリチャネルを選択し、メモリにアクセスを行う。

【0035】

セグメント情報を格納するセグメント情報保持回路SG1、《第1単位記憶回路の下限アドレス、第1単位記憶回路の上限アドレス、第2単位記憶回路の下限アドレス、および、第2単位記憶回路の上限アドレスを保持する上限下限アドレス回路ULA1は、メモリコントローラL2に設けることが可能である(図1(a))。また、セグメント情報保持回路SG1は、データ処理装置L1に設け、上限下限アドレス回路ULA1は、メモリコントローラL2に設けることが可能である(図1(b))。この場合、データ処理装置L1が、計算を実施し、メモリコントローラL2内の上限下限アドレス回路ULA1に値を設定する。

【0036】

以上は、単位記憶回路の総数Yが、2の乗数である最大WAY数X×2を超えない場合について説明したが、単位記憶回路の総数Y>2の乗数である最大WAY数X×2の場合にも本発明が適用可能である。この場合、Y/Xの商(整数)の個数の単位記憶回路を最大WAY数Xでインタリーブする。残りの、《Y−Y/Xの商(整数)》個の単位記憶回路を、第n単位記憶回路、第n+1単位記憶回路のように構成する。第n単位記憶回路、第n+1単位記憶回路をそれぞれ上述した第1単位記憶回路、第2単位記憶回路とみなしインタリーブする。

【0037】

本発明の第1の効果は、メモリチャネル配下に実装されるメモリ構成に依存せず、全メモリに対するアクセスがインタリーブ数2の乗数で実現でき、簡素で高速なメモリコントローラL2を提供できることである。

【0038】

第2の効果は、メモリコントローラL2配下に実装されるメモリの増設および縮退時のメモリ数に制限がなくなることである。すなわち、任意の数の単位でメモリ増設が可能となり、さらに、最小限のメモリ単位でメモリ縮退可能となる。

【0039】

その理由は、メモリチャネル配下の各メモリに割り付けられたアドレス空間情報、具体的には下限アドレスと上限アドレスの情報を保持する回路を有し、かつ、このアドレス空間が任意に可変設定可能とするためである。

【0040】

次に、本発明の実施例について図面を参照して詳細に説明する。

【0041】

以下、第1単位記憶回路、第2単位記憶回路を、単位メモリと記述する。

【0042】

図2は、本発明の第1、第2、第3、第4の実施例のメモリコントローラのアドレス変換回路の構成を示すブロック図である。図3、図4、図5は、図2のアドレス変換回路の動作を示すための説明図である。

【0043】

図6は、本発明の第1の実施例の構成を示すブロック図である。図7、図8、図9は、本発明の第1の実施例の動作を示すための説明図である。

【0044】

図10は、本発明の第2の実施例の構成を示すブロック図である。図11、図12、図13は、本発明の第2の実施例の動作を示すための説明図である。

【0045】

図14は、本発明の第3の実施例の構成を示すブロック図である。図15、図16、図17は、本発明の第3の実施例の動作を示すための説明図である。

【0046】

図18は、本発明の第4の実施例の構成を示すブロック図である。図19、図20、図21は、本発明の第4の実施例の動作を示すための説明図である。

【0047】

第1〜第4の実施例において、差分は、実装される単位メモリ数のみであるため、ここでは、第1の実施例の図6について説明する。

【0048】

図6を参照すると、本発明の第1の実施例は、メモリコントローラ901と、メモリチャネルCH1〜CH8と、メモリチャネルCH1に接続される単位メモリm10、単位メモリm11と、メモリチャネルCH2に接続される単位メモリm20、単位メモリm21と、メモリチャネルCH3に接続される単位メモリm30、単位メモリm31と、メモリチャネルCH4に接続される単位メモリm40、m41と、メモリチャネルCH5に接続される単位メモリm50、単位メモリm51と、メモリチャネルCH6に接続される単位メモリm60、単位メモリm61と、メモリチャネルCH7に接続される単位メモリm70、単位メモリm71と、メモリチャネルCH8に接続される単位メモリm80、単位メモリm81と、メモリコントローラ901に内蔵されるアドレス変換回路91とを含む。

【0049】

メモリコントローラ901はインタフェース900を介してメモリアクセスを受け取りアドレス変換回路91でのアドレス変換結果からアクセス発行対象の単位メモリを単位メモリm10、m11、m20、m21〜m80、m81の中から決定しインタフェース100〜800を介して該当する単位メモリにアクセスを発行する。

【0050】

説明を簡素化するため、単位メモリm10、m11、m20、m21〜m80、m81は、全て8バイト単位アクセス×128ワード構成の容量1KBの単位メモリとする。よって、単位メモリのワードアドレスは、7ビットで構成される。また、各メモリチャネルCH1〜CH8に接続される単位メモリは最大2つまでとする。よって、メモリ最大構成時は、図6の示す通りとなり、メモリ容量は最大1KB×2×8=16KBとする。

【0051】

また、本実施例では、単位メモリの最小構成が1KBであり、この1KBをセグメント単位である。

【0052】

図2を参照すると、セグメント情報保持回路S10、S11、S20、S21〜S80、S81は、それぞれ、図6の単位メモリm10、m11、m20、m21〜m80、m81と対応している。各セグメント情報保持回路S10、S11、S20、S21〜S80、S81は、それぞれ、WAY数S10a、S11a、S20a、S21a〜S80a、S81aと下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bとを格納する。

【0053】

図2のセグメント情報保持回路S10、S11、S20、S21〜S80、S81は、図6の第1の実施例のメモリ最大構成時の設定値を格納する。単位メモリm10、m20、m30〜m80で8WAY制御するため、WAY数S10a、S20a、S30a〜S80aは、8を格納する。また、単位メモリm11、m21、m31〜m81で8WAY制御するため、WAY数S11a、S21a、S31a〜S81aは、8を格納する。下限アドレスの底上げは実施されないため、底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bは、全て0を格納する。

【0054】

図2のB10、B11、B20、B21〜B80、B81は、図6の単位メモリm10、m11、m20、m21〜m80、m81の下限アドレスを保持する回路である(以降、下限アドレスの値を指すこともある)。上限アドレスT10、T11、T20、T21〜T80、T81は、単位メモリm10、m11、m20、m21〜m80、m81の上限アドレスを保持する回路である(以降、上限アドレスの値を指すこともある)。下限アドレス、上限アドレスは、初期設定時に、セグメント情報保持回路S10、S11、S20、S21〜S80、S81に保持されている情報から各々算出され保持される。

【0055】

図2のベースアドレスB00は、メモリコントローラ901配下のメモリ空間のベースアドレスを示す。ベースアドレスB00を基に、単位メモリm10、m11、m20、m21〜m80、m81の下限アドレスB10、B11、B20、B21〜B80、B81と、上限アドレスT10、T11、T20、T21〜T80、T81とが算出される。

【0056】

本実施例では、図4の示すとおりベースアドレスB00は、常時0とする。

【0057】

図2のアクセスアドレスC00は、図6のインタフェース900経由でメモリコントローラ901に発行されたアクセスアドレスを格納する。

【0058】

図3に、アクセスアドレスC00の概要を示す。図3において、本実施例では、メモリ最大構成容量が16KBであるため、アドレスは、A13〜A0までの14ビットとする。また、メモリアクセス単位が8バイトであるため、アドレス変換には、8バイト境界アドレスより下位のA2〜A0以外のA13〜A3を参照する。さらに、本実施例の単位メモリの最小構成容量が1KBであるため、図2の各単位メモリの《下限アドレスB10、B11、B20、B21〜B80、B81、および、上限アドレスT10、T11、T20、T21〜T80、T81》とアクセスアドレスC00との比較は1KB境界より上位のA13〜A10の4ビットで実施する。

【0059】

ここで、単位メモリm10、m11、m20、m21〜m80、m81にそれぞれ対応する下限アドレスB10、B11、B20、B21〜B80、B81、および、上限アドレスT10、T11、T20、T21〜T80、T81の算出方法について説明する。

【0060】

メモリチャネルCH1に関しては、ベースアドレスB00を基に単位メモリm10の下限アドレスB10が算出され、次に、上限アドレスT10が算出され、次に、単位メモリm11の下限アドレスB11が算出され、次に、上限アドレスT11が算出される。

【0061】

メモリチャネルCH1の単位メモリm10の下限アドレスB10と上限アドレスT10とは、下記の式で求められる。計算は、1KB境界より上位の4ビットのみで実施され、結果が保持される。

【0062】

単位メモリm10の下限アドレスB10=ベースアドレスB00+下限アドレス底上げセグメント数S10b。単位メモリm10の上限アドレスT10=単位メモリm10の下限アドレスB10+WAY数S10a。

【0063】

メモリチャネルCH1の単位メモリm11の下限アドレスB11と上限アドレスT11とは、下記の式で求められる。計算は1KB境界より上位の4ビットのみで行われる。

【0064】

単位メモリm11の下限アドレスB11=単位メモリm10の上限アドレスT10+上限アドレス底上げセグメント数S11b。単位メモリm11の上限アドレスT11=単位メモリm11の下限アドレスB11+WAY数S11a。

【0065】

他のチャネルCH2〜CH8についても同様である。

【0066】

図2のヒット信号H10、H11、H20、H21〜H80、H81は、図6の単位メモリm10、m11、m20、m21〜m80、m81と対応している。たとえば、アクセスアドレスC00が、単位メモリm10の下限アドレスB10以上、かつ、上限アドレスT10未満であれば、H10が有効になる。また、メモリチャネルCH1のH10とH11、メモリチャネルCH2のH20とH21、メモリチャネルCH3のH30とH31、メモリチャネルCH4のH40とH41、メモリチャネルCH5のH50とH51、メモリチャネルCH6のH60とH61、メモリチャネルCH7のH70とH71、および、メモリチャネルCH8のH80とH81は、各メモリチャネル内でそれぞれ排他的に有効になる。

【0067】

図2のアクセス発行メモリ判定回路93は、ヒット信号H10、H11、H20、H21〜H80、H81からアクセス発行対象を単位メモリm10、m11、m20、m21〜m80、m81から選択する。

【0068】

アクセス発行メモリ判定回路93は、ヒット信号H10、H11、H20、H21〜H80、H81が1つだけ有効になった場合は、アクセスアドレスを1WAY領域とみなしヒット信号が有効になった該当単位メモリにアクセスを発行する。アクセス発行メモリ判定回路93は、ヒット信号H10、H11、H20、H21〜H80、H81の内2つ有効になった場合は、図5に示されるとおりアクセスアドレスを2WAY領域とみなし、アクセスアドレスC00のA3を参照し、ヒットした2つのメモリチャネルの内1つを選択し該当する単位メモリにアクセスを発行する。アクセス発行メモリ判定回路93は、ヒット信号H10、H11、H20、H21〜H80、H81の内4つ有効になった場合は、図5に示されるとおりアクセスアドレスを4WAY領域とみなし、アクセスアドレスC00のA4〜A3を参照しヒットした4つのメモリチャネルの内1つを選択し該当する単位メモリにアクセスを発行する。アクセス発行メモリ判定回路93は、ヒット信号H10、H11、H20、H21〜H80、H81の内8つ有効になった場合は、アクセスアドレスを図5に示されるとおり8WAY領域とみなし、アクセスアドレスC00のA5〜A3を参照しヒットした8つのメモリチャネルの内1つを選択し該当する単位メモリにアクセスを発行する。

【0069】

次に、本発明の第1の実施例の動作について、図2と図6、図7、図8、図9とを参照して説明する。

【0070】

第1の実施例は、従来からある8WAYインタリーブ(2の乗数)で制御する。

【0071】

図6において、メモリコントローラ901配下のメモリチャネルCH1〜CH8には単位メモリm10、m11、m20、m21〜m80、m81が接続されている、第1の実施例での各単位メモリに対するアドレス割り付けの概要を図8に示す。

【0072】

図8を参照すると、0KB以上〜8KB未満のアドレス領域では、単位メモリm10、m20〜m80の8WAYにてインタリーブ制御が実施される。8KB以上〜16KB未満のアドレス領域では、単位メモリm11、m21〜m81の8WAYにてインタリーブ制御が実施される。

【0073】

図8のアドレス割り付けを基に、セグメント情報保持回路S10、S11、S20、S21〜S80、S81のWAY数S10a、S11a、S20a、S21a〜S80a、S81aと下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bが、図7に示すとおりに決定される。

【0074】

図7を参照すると、第1の実施例では、全領域8WAYインタリーブであるため、WAY数S10a、S11a、S20a、S21a〜S80a、S81aには8が設定される。また、下限アドレスの底上げを実施していないため、下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bには0が設定される。

【0075】

図9に、第1の実施例での各単位メモリに対する詳細なアドレス割り付けを示す。単位メモリへのアクセス単位が8バイトであるため、アドレスの下位3ビットはX(任意)で表記している。

【0076】

次に、第1の実施例におけるアドレス変換回路91の詳細動作を図2を参照して説明する。

【0077】

下限アドレスB10、B11、B20、B21〜B80、B81、および、上限アドレスT10、T11、T20、T21〜T80、T81の値は、図7の設定値から下記のように算出される。メモリチャネルCH1の単位メモリm10の下限アドレスB10、上限アドレスT10は、下記の式で算出される。

【0078】

単位メモリm10の下限アドレスB10=(ベースアドレスB00)0KB+(下限アドレス底上げセグメント数S10b)0KB=0KB。単位メモリm10の上限アドレスT10=(単位メモリm10の下限アドレスB10)0KB+(WAY数S10a)8KB=8KB。

【0079】

よって、単位メモリm10のアドレス領域は、0KB以上〜8KB未満となる。同様に、単位メモリm20、m30〜m80の下限アドレスおよび上限アドレスについても同値となる。

【0080】

メモリチャネルCH1の単位メモリm11の下限アドレスB11、上限アドレスT11は、下記の式で算出される。

【0081】

単位メモリm11の下限アドレスB11=(単位メモリm10の上限アドレスT10)8KB+(下限アドレス底上げセグメント数S11b)0KB=8KB。単位メモリm11の上限アドレスT11=(単位メモリm11の下限アドレスB11)8KB+(WAY数S11a)8KB=16KB。

【0082】

よって、単位メモリm11のアドレス領域は8KB以上〜16KB未満となる。同様に単位メモリm21、m31〜m81の下限アドレスおよび上限アドレスについても同値となる。

【0083】

第1の実施例において、アクセスアドレスC00に0KB以上〜8KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値からヒット信号H10、H20〜H80の8つの信号が有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを8WAY領域とみなし、アクセスアドレスC00のA5〜A3でアクセス先のメモリチャネルを判定し、単位メモリm10、m20〜m80の内のいずれかひとつにアクセスを発行する。同様に、アクセスアドレスC00に8KB以上〜16KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値からヒット信号H11、H21〜H81の8つの信号が有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを8WAY領域とみなし、アクセスアドレスC00のA5〜A3でアクセス先のメモリチャネルを判定し、単位メモリm11、単位メモリm21〜m81の内のいずれかひとつにアクセスを発行する。

【0084】

次に、本発明の第2の実施例について、図2と図10、図11、図12、図13とを参照して説明する。

【0085】

第2の実施例は、従来からある4WAYと2WAYインタリーブ(2の乗数)との混在で制御する。

【0086】

図10を参照すると、メモリコントローラ901配下のメモリチャネルCH1〜CH4には、単位メモリm10、m20、m30、m40、m11、m21が接続されている。メモリチャネルCH5〜CH8は未使用である。第2の実施例での各単位メモリに対するアドレス割り付けの概要を図12に示す。

【0087】

図12を参照すると、0KB以上〜4KB未満のアドレス領域では単位メモリm10、m20、m30、m40の4WAYにてインタリーブ制御が実施される。4KB以上〜6KB未満のアドレス領域では単位メモリm11、m21の2WAYにてインタリーブ制御が実施される。

【0088】

図12のアドレス割り付けを基に、セグメント情報保持回路S10、S11、S20、S21〜S80、S81のWAY数S10a、S11a、S20a、S21a〜S80a、S81aと下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81が、図11に示すとおりに決定される。

【0089】

図11を参照すると、第2の実施例では、WAY数S10a、S20a、S301a、S40aには4が設定され、WAY数S11a、S21aには2が設定され、未使用セグメントについては0が設定される。また、下限アドレスの底上げを実施していないため下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bには0が設定される。

【0090】

図13に第2の実施例での各単位メモリに対する詳細なアドレス割り付けを示す。単位メモリへのアクセス単位が8バイトであるため、アドレスの下位3ビットは、X(任意)で表記している。

【0091】

第2の実施例におけるアドレス変換回路91の詳細動作を図2を参照して説明する。

【0092】

下限アドレスB10、B11、B20、B21〜B80、B81、および、上限アドレスT10、T11、T20、T21〜T80、T81の値は、図11の設定値から下記のように算出される。

【0093】

メモリチャネルCH1の単位メモリm10の下限アドレスB10、および、上限アドレスT10は下記の式で算出される。

単位メモリm10の下限アドレスB10=(ベースアドレスB00)0KB+(下限アドレス底上げセグメント数S10b)0KB=0KB。単位メモリm10の上限アドレスT10=(単位メモリm10の下限アドレスB10)0KB+(WAY数S10a)4KB=4KB。

【0094】

よって、単位メモリm10のアドレス領域は、0KB以上〜4KB未満となる。同様に単位メモリm20、m30、m40の下限アドレス、および、上限アドレスについても同値となる。

【0095】

メモリチャネルCH1の単位メモリm11の下限アドレスB11、上限アドレスT11は、下記の式で算出される。

【0096】

単位メモリm11の下限アドレスB11=(単位メモリm10の上限アドレスT10)4KB+(下限アドレス底上げセグメント数S11b)0KB=4KB。単位メモリm11の上限アドレスT11=(単位メモリm11の下限アドレスB11)4KB+(WAY数S11a)2KB=6KB。

【0097】

よって、単位メモリm11のアドレス領域は、4KB以上〜6KB未満となる。同様に単位メモリm21の下限アドレスおよび上限アドレスについても同値となる。

【0098】

第2の実施例において、アクセスアドレスC00に0KB以上〜4KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値から、ヒット信号H10、H20、H30、H40の4つの信号が有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを4WAY領域とみなし、アクセスアドレスC00のA4〜A3で、アクセス先のメモリチャネルを判定し、単位メモリm10、m20、m30、m40の内のいずれかひとつにアクセスを発行する。同様に、アクセスアドレスC00に4KB以上〜6KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値からヒット信号H11、H21の2つの信号が有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを2WAY領域とみなし、アクセスアドレスC00のA3で、アクセス先のメモリチャネルを判定し、単位メモリm11、m21の内のいずれかひとつにアクセスを発行する。

【0099】

次に、本発明の第3の実施例について、図2と図14、図15、図16、図17とを参照して説明する。

【0100】

第3の実施例は、従来であれば、8WAYと3WAYとのインタリーブ混在で制御するが、アドレス変換回路91により3WAY領域を2WAYと1WAY領域とに置き換えて制御する。

【0101】

図14を参照すると、メモリコントローラ901配下のメモリチャネルCH1〜CH8には、単位メモリm10、m20、m30〜m80、m11、m21、m31が接続されている。

【0102】

第3の実施例での各単位メモリに対するアドレス割り付けの概要を図16に示す。

【0103】

図16を参照すると、第3の実施例は、0KB以上〜8KB未満のアドレス領域では、第1の実施例と同様に、単位メモリm10、m20〜m80の8WAYにてインタリーブ制御を実施する。8KB以上〜11KB未満のアドレス領域では、従来は、単位メモリm11、m21、m31の3WAYにてインタリーブ制御が実施されるが、本発明の第3の実施例では、3WAYを2WAYと1WAYに置き換えることで全アドレス空間にて2の乗数のインタリーブが実現される。具体的には、8KB以上〜10KB未満のアドレス領域では単位メモリm11、m21の2WAYにてインタリーブ制御が実施され、10KB以上〜11KB未満のアドレス領域では、単位メモリm31の1WAYにてインタリーブ制御が実施される。3WAYから2WAYと1WAYへの置き換えは、単位メモリm31の下限アドレスを2KB(2セグメント)底上げすることで実現される。

【0104】

図16のアドレス割り付けを基に、図2のセグメント情報保持回路S10、S11、S20、S21〜S80、S81のWAY数S10a、S11a、S20a、S21a〜S80a、S81aと下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bが図15に示すとおりに決定される。

【0105】

図15について、第3の実施例では、WAY数S10a、S20a、S301a、S40a〜S80aには8が設定され、WAY数S11a、S21aには2が設定され、WAY数S31aには1が設定され、未使用セグメントについては0が設定される。また、単位メモリm31の下限アドレスに2KB(2セグメント)の底上げを実施するため下限アドレス底上げセグメント数S31bに2が設定される。

【0106】

図17に、第3の実施例での各単位メモリに対する詳細なアドレス割り付けを示す。単位メモリへのアクセス単位が8バイトであるためアドレスの下位3ビットはXで表記している。

【0107】

第3の実施例におけるアドレス変換回路91の詳細動作を図2を用いて説明する。

【0108】

図2の下限アドレスB10、B11、B20、B21〜B80、B81、および、上限アドレスT10、T11、T20、T21〜T80、T81の値は図15の設定値から下記のように算出される。メモリチャネルCH1の単位メモリm10の下限アドレスB10、および、上限アドレスT10は下記の式で算出される。

【0109】

単位メモリm10の下限アドレスB10=(ベースアドレスB00)0KB+(下限アドレス底上げセグメント数S10b)0KB=0KB。単位メモリm10の上限アドレスT10=(単位メモリm10の下限アドレスB10)0KB+(WAY数S10a)8KB=8KB。

【0110】

よって、単位メモリm10のアドレス領域は0KB以上〜8KB未満となる。同様に、単位メモリm20、m30〜m80の下限アドレスおよび上限アドレスについても同値となる。

【0111】

メモリチャネルCH1の単位メモリm11の下限アドレスB11、および、上限アドレスT11は下記の式で算出される。

【0112】

単位メモリm11の下限アドレスB11=(単位メモリm10の上限アドレスT10)8KB+(下限アドレス底上げセグメント数S11b)0KB=8KB。単位メモリm11の上限アドレスT11=(単位メモリm11の下限アドレスB11)8KB+(WAY数S11a)2KB=10KB。

【0113】

よって、単位メモリm11のアドレス領域は8KB以上〜10KB未満となる。同様に、単位メモリm21の下限アドレスおよび上限アドレスについても同値となる。

【0114】

底上げを実施するメモリチャネルCH3の単位メモリm31の下限アドレスB31、および、上限アドレスT31は下記の式で算出される。

【0115】

単位メモリm31の下限アドレスB31=(単位メモリm30の上限アドレスT30)8KB+(下限アドレス底上げセグメント数S31b)2KB=10KB。単位メモリm31の上限アドレスT31=(単位メモリm31の下限アドレスB31)10KB+(WAY数S31a)1KB=11KB。

【0116】

よって、単位メモリm31のアドレス領域は10KB以上〜11KB未満となる。

【0117】

第3の実施例において、アクセスアドレスC00に0KB以上〜8KB未満のアドレスが格納された場合は、第1の実施例と同じなので説明を省略する。アクセスアドレスC00に8KB以上〜10KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値から、ヒット信号H11、H21の2つの信号が有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを2WAY領域とみなし、アクセスアドレスC00のA3でアクセス発行先のメモリチャネルを判定し、単位メモリm11、m21の内のいずれかひとつにアクセスを発行する、同様に、アクセスアドレスC00に10KB以上〜11KB未満のアドレスが格納されると、下限アドレスと上限アドレスの設定値からヒット信号H31のみが有効になる。アクセス発行メモリ判定回路93は、アクセスアドレスを1WAY領域とみなし単位メモリm31に対してアクセスを発行する。

【0118】

次に、本発明の第4の実施例について、図2と図18、図19、図20、図21とを参照して説明する。

【0119】

第4の実施例は、従来であれば、8WAYと7WAYとのインタリーブ混在で制御するが、アドレス変換回路91により7WAY領域を4WAYと2WAYと1WAY領域とに置き換えて制御する。

【0120】

図18を参照すると、メモリコントローラ901配下のメモリチャネルCH1〜CH8には、単位メモリm10、m20、m30〜m80、m11、m21〜m71が接続されている。第4の実施例での各単位メモリに対するアドレス割り付けの概要を図20に示す。

【0121】

図20を参照すると、0KB以上〜8KB未満のアドレス領域では、第1の実施例と同様に単位メモリm10、m20〜m80の8WAYにてインタリーブ制御が実施される。8KB以上〜15KB未満のアドレス領域では、従来は、単位メモリm11、m21〜m71の7WAYにてインタリーブ制御が実施されていた。本発明の第4の実施例では、7WAYを4WAYと2WAYと1WAYに置き換えることで、全アドレス空間にて2の乗数のインタリーブが実現される。

【0122】

具体的には、8KB以上〜12KB未満のアドレス領域では、単位メモリm11、m21、m31、m41の4WAYにてインタリーブ制御が実施される。12KB以上〜14KB未満のアドレス領域では、単位メモリm51、m61の2WAYにてインタリーブ制御が実施される。14KB以上〜15KB未満のアドレス領域では、単位メモリm71の1WAYにてインタリーブ制御が実施される。7WAYから4WAY、2WAY、および、1WAYへの置き換えは、単位メモリm51、m61の下限アドレスを4KB(4セグメント)底上げすることと、単位メモリm71の下限アドレスを6KB(6セグメント)底上げすることとで実現される。

【0123】

図20のアドレス割り付けを基に、セグメント情報保持回路S10、S11、S20、S21〜S80、S81のWAY数S10a、S11a、S20a、S21a〜S80a、S81a、および、下限アドレス底上げセグメント数S10b、S11b、S20b、S21b〜S80b、S81bが図19に示すとおりに決定される。

【0124】

図19を参照すると、第4の実施例では、WAY数S10a、S20a、S301a、S40a〜S80aには8が設定される。WAY数S11a、S21a、S31a、S41aには4が設定される。WAY数S51a、S61aには2が設定される。WAY数S71aには1が設定される。その他の未使用単位メモリに対応するセグメントには、0が設定される。また、単位メモリm51、m61の下限アドレスに4KB(4セグメント)の底上げを実施するため、下限アドレス底上げセグメント数S51b、S61bに4が設定される。また、単位メモリm71の下限アドレスに6KB(6セグメント)の底上げを実施するため、下限アドレス底上げセグメント数S71bに6が設定される。

【0125】

図21に、第4の実施例での各単位メモリに対する詳細なアドレス割り付けを示す。単位メモリへのアクセス単位が8バイトであるため、アドレスの下位3ビットは、X(任意)で表記している。

【0126】

第4の実施例におけるアドレス変換回路91の詳細動作を、図2を参照して説明する。

【0127】

図2の下限アドレスB10、B11、B20、B21〜B80、B81と上限アドレスT10、T11、T20、T21〜T80、T81の値は、図19の設定値から下記のように算出される。

【0128】

メモリチャネルCH1の単位メモリm10の下限アドレスB10、および、上限アドレスT10は下記の式で算出される。

【0129】

単位メモリm10の下限アドレスB10=(ベースアドレスB00)0KB+(下限アドレス底上げセグメント数S10b)0KB=0KB。単位メモリm10の上限アドレスT10=(単位メモリm10の下限アドレスB10)0KB+(WAY数S10a)8KB=8KB。

【0130】

よって、単位メモリm10のアドレス領域は、0KB以上〜8KB未満となる。同様に、単位メモリm20、m30〜m80の下限アドレスおよび上限アドレスについても同値となる。

【0131】

メモリチャネルCH1の単位メモリm11の下限アドレスB11、および、上限アドレスT11は下記の式で算出される。

【0132】

単位メモリm11の下限アドレスB11=(単位メモリm10の上限アドレスT10)8KB+(下限アドレス底上げセグメント数S11b)0KB=8KB。単位メモリm11の上限アドレスT11=(単位メモリm11の下限アドレスB11)8KB+(WAY数S11a)4KB=12KB。

【0133】

よって、単位メモリm11のアドレス領域は、8KB以上〜12KB未満となる。同様に、単位メモリm21、単位メモリm31、単位メモリm41の下限アドレスおよび上限アドレスについても同値となる。

【0134】

底上げを実施するメモリチャネルCH5、CH6の単位メモリm51、m61の下限アドレスB51、B61、および、上限アドレスT51、T61は下記の式で算出される。

【0135】

単位メモリm51の下限アドレスB51=(単位メモリm50の上限アドレスT50)8KB+(下限アドレス底上げセグメント数S51b)4KB=12KB。ここで、(下限アドレス底上げセグメント数S51b)4KBは、「《先にインタリーブが決定された》インタリーブ数の合計値×単位メモリ容量」=4×1KBである。単位メモリm51の上限アドレスT51=(単位メモリm51の下限アドレスB51)12KB+(WAY数S51a)2KB=14KB。

【0136】

よって、単位メモリm11のアドレス領域は、12KB以上〜14KB未満となる。同様に、単位メモリm61の下限アドレス、および、上限アドレスについても同値となる。

【0137】

さらに、底上げを実施するメモリチャネルCH7の単位メモリm71の下限アドレスB71と上限アドレスT71は、下記の式で算出される。

【0138】

単位メモリm71の下限アドレスB71=(単位メモリm70の上限アドレスT70)8KB+(下限アドレス底上げセグメント数S71b)6KB=14KB。ここで、(下限アドレス底上げセグメント数S71b)6KBは、「《先にインタリーブが決定された》インタリーブ数の合計値×単位メモリ容量」=(4+2)×1KBである。単位メモリm71の上限アドレスT71=(単位メモリm71の下限アドレスB71)14KB+(WAY数S71a)1KB=15KB。

【0139】

よって、単位メモリm71のアドレス領域は、14KB以上〜15KB未満となる。

【0140】

第4の実施例において、アクセスアドレスC00に0KB以上〜8KB未満のアドレスが格納された場合は、第1の実施例と同じなので説明を省略する。アクセスアドレスC00に8KB以上〜12KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値から、ヒット信号H11、H21、H31、H41の4つの信号が有効になる。アクセス発行メモリ判定回路93は、4WAY領域とみなし、アクセスアドレスC00のA4〜A3でアクセス発行先のメモリチャネルを判定し、単位メモリm11、m21、m31、m41の内のいずれかひとつにアクセスを発行する。同様に、アクセスアドレスC00に、12KB以上〜14KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値からヒット信号H51、H61の2つの信号が有効になる。アクセス発行メモリ判定回路93は、2WAY領域とみなし、アクセスアドレスC00のA3で、アクセス発行先のメモリチャネルを判定し、単位メモリm51、m61の内のいずれかひとつにアクセスを発行する。同様に、アクセスアドレスC00に、14KB以上〜15KB未満のアドレスが格納されると、下限アドレス、および、上限アドレスの設定値からヒット信号H71のみが有効になる。アクセス発行メモリ判定回路93は、1WAY領域とみなし単位メモリm71に対してアクセスを発行する。

【0141】

以上説明した制御を、コントロールストアを設け、ファームウェアで実施することが可能である。

【図面の簡単な説明】

【0142】

【図1】本発明を実施するための最良の形態の構成を示すブロック図。

【図2】本発明のアドレス変換回路の構成を示すブロック図。

【図3】アドレス変換回路の動作を示すための説明図。

【図4】アドレス変換回路の動作を示すための説明図。

【図5】アドレス変換回路の動作を示すための説明図。

【図6】本発明の第1の実施例の構成を示すブロック図。

【図7】本発明の第1の実施例の動作を示すための説明図。

【図8】本発明の第1の実施例の動作を示すための説明図。

【図9】本発明の第1の実施例の動作を示すための説明図。

【図10】本発明の第2の実施例の構成を示すブロック図。

【図11】本発明の第2の実施例の動作を示すための説明図。

【図12】本発明の第2の実施例の動作を示すための説明図。

【図13】本発明の第2の実施例の動作を示すための説明図。

【図14】本発明の第3の実施例の構成を示すブロック図。

【図15】本発明の第3の実施例の動作を示すための説明図。

【図16】本発明の第3の実施例の動作を示すための説明図。

【図17】本発明の第3の実施例の動作を示すための説明図。

【図18】本発明の第4の実施例の構成を示すブロック図。

【図19】本発明の第4の実施例の動作を示すための説明図。

【図20】本発明の第4の実施例の動作を示すための説明図。

【図21】本発明の第4の実施例の動作を示すための説明図。

【符号の説明】

【0143】

L1 データ処理装置

L2 メモリコントローラ

L3 メモリ装置

CH1 メモリチャネル

CH2 メモリチャネル

CH3 メモリチャネル

CH4 メモリチャネル

CH5 メモリチャネル

CH6 メモリチャネル

CH7 メモリチャネル

CH8 メモリチャネル

M10〜M80 第1単位記憶回路

M11〜M81 第2単位記憶回路

m10、m11、m20、m21〜m80、m81 単位メモリ

SG1 セグメント情報保持回路

ULA1 上限下限アドレス回路

B00 ベースアドレス

C00 アクセスアドレス

S10、S11、S20、S21〜S80、S81 セグメント情報保持回路

S10a、S11a、S20a、S21a〜S80a、S81a WAY数

S10b、S11b、S20b、S21b〜S80b、S81b セグメント数

B10、B11、B20、B21〜B80、B81 下限アドレス

T10、T11、T20、T21〜T80、T81 上限アドレス

91 アドレス変換回路

93 アクセス発行メモリ判定回路

900 インタフェース

901 メモリコントローラ

100〜800 インタフェース

【特許請求の範囲】

【請求項1】

複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御する情報処理装置であって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施する回路を有することを特徴とする情報処理装置。

【請求項2】

前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブする回路を有することを特徴とする請求項1記載の情報処理装置。

【請求項3】

「WAY数Z1、Z2、・・・、Ziのいずれかと、同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリのアドレスからの底上げ分である下限アドレス底上げセグメント数との対」であるセグメント情報を保持するセグメント情報保持回路と、「同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリの上限アドレス+セグメント情報の前記単位メモリの下限アドレス底上げセグメント数=下限アドレス」を保持する下限アドレス回路と、「前記単位メモリの下限アドレス+セグメント情報の前記単位メモリのWAY数=上限アドレス」を保持する上限アドレス回路と、下限アドレス≦アクセスアドレス<上限アドレスであると、ヒット信号を出力し、アクセスアドレスに対しヒット信号の数のWAY数のインタリーブを行うアドレス変換回路と、を有することを特徴とする請求項2記載の情報処理装置。

【請求項4】

前記セグメント情報保持回路を備え、アクセスアドレスを出力するデータ処理装置と、アクセスアドレスを入力し、前記下限アドレス回路、前記上限アドレス回路、および、前記アドレス変換回路を備えるメモリコントローラと、を有することを特徴とする請求項3記載の情報処理装置。

【請求項5】

前記メモリコントローラに接続され、前記単位メモリを備えるメモリ装置を有することを特徴とする請求項4記載の情報処理装置。

【請求項6】

アクセスアドレスを出力するデータ処理装置と、前記下限アドレス回路、前記上限アドレス回路、および、前記アドレス変換回路を備えるメモリコントローラと、を有することを特徴とする請求項3記載の情報処理装置。

【請求項7】

前記メモリコントローラに接続され、前記単位メモリを備えるメモリ装置を有することを特徴とする請求項6記載の情報処理装置。

【請求項8】

複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御する情報処理方法であって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施することを特徴とする情報処理方法。

【請求項9】

前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブすることを特徴とする請求項8記載の情報処理方法。

【請求項10】

「WAY数Z1、Z2、・・・Ziのいずれかと、同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリのアドレスからの底上げ分である下限アドレス底上げセグメント数との対」であるセグメント情報を保持し、

「同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリの上限アドレス+セグメント情報の前記単位メモリの下限アドレス底上げセグメント数=下限アドレス」を保持し、

「前記単位メモリの下限アドレス+セグメント情報の前記単位メモリのWAY数=上限アドレス」を保持し、

下限アドレス≦アクセスアドレス<上限アドレスであると、ヒット信号を出力し、アクセスアドレスに対しヒット信号の数のWAY数のインタリーブを行う、

ことを特徴とする請求項9記載の情報処理方法。

【請求項11】

複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御する情報処理装置におけるプログラムであって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を前記情報処理装置に実施させることを特徴とするプログラム。

【請求項12】

前記情報処理装置に、前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブする制御を実施させることを特徴とする請求項11記載のプログラム。

【請求項1】

複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御する情報処理装置であって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施する回路を有することを特徴とする情報処理装置。

【請求項2】

前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブする回路を有することを特徴とする請求項1記載の情報処理装置。

【請求項3】

「WAY数Z1、Z2、・・・、Ziのいずれかと、同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリのアドレスからの底上げ分である下限アドレス底上げセグメント数との対」であるセグメント情報を保持するセグメント情報保持回路と、「同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリの上限アドレス+セグメント情報の前記単位メモリの下限アドレス底上げセグメント数=下限アドレス」を保持する下限アドレス回路と、「前記単位メモリの下限アドレス+セグメント情報の前記単位メモリのWAY数=上限アドレス」を保持する上限アドレス回路と、下限アドレス≦アクセスアドレス<上限アドレスであると、ヒット信号を出力し、アクセスアドレスに対しヒット信号の数のWAY数のインタリーブを行うアドレス変換回路と、を有することを特徴とする請求項2記載の情報処理装置。

【請求項4】

前記セグメント情報保持回路を備え、アクセスアドレスを出力するデータ処理装置と、アクセスアドレスを入力し、前記下限アドレス回路、前記上限アドレス回路、および、前記アドレス変換回路を備えるメモリコントローラと、を有することを特徴とする請求項3記載の情報処理装置。

【請求項5】

前記メモリコントローラに接続され、前記単位メモリを備えるメモリ装置を有することを特徴とする請求項4記載の情報処理装置。

【請求項6】

アクセスアドレスを出力するデータ処理装置と、前記下限アドレス回路、前記上限アドレス回路、および、前記アドレス変換回路を備えるメモリコントローラと、を有することを特徴とする請求項3記載の情報処理装置。

【請求項7】

前記メモリコントローラに接続され、前記単位メモリを備えるメモリ装置を有することを特徴とする請求項6記載の情報処理装置。

【請求項8】

複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御する情報処理方法であって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を実施することを特徴とする情報処理方法。

【請求項9】

前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブすることを特徴とする請求項8記載の情報処理方法。

【請求項10】

「WAY数Z1、Z2、・・・Ziのいずれかと、同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリのアドレスからの底上げ分である下限アドレス底上げセグメント数との対」であるセグメント情報を保持し、

「同一の前記メモリチャネル内の先にインタリーブが決定された前記単位メモリの上限アドレス+セグメント情報の前記単位メモリの下限アドレス底上げセグメント数=下限アドレス」を保持し、

「前記単位メモリの下限アドレス+セグメント情報の前記単位メモリのWAY数=上限アドレス」を保持し、

下限アドレス≦アクセスアドレス<上限アドレスであると、ヒット信号を出力し、アクセスアドレスに対しヒット信号の数のWAY数のインタリーブを行う、

ことを特徴とする請求項9記載の情報処理方法。

【請求項11】

複数メモリチャネルを備え、前記メモリチャネルに接続される単位メモリをインタリーブ制御する情報処理装置におけるプログラムであって、前記メモリチャネルに接続される単位メモリに対するアクセスに対しインタリーブ数が常に2の乗数になるインタリーブ制御を前記情報処理装置に実施させることを特徴とするプログラム。

【請求項12】

前記情報処理装置に、前記単位メモリの総数がYであると、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z1」個の前記単位メモリをWAY数Z1でインタリーブし、「Y−Z1」個のうち、「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Z2」個の前記単位メモリを、WAY数Z2でインタリーブし、・・・、残りの「2の乗数である最大WAY数Xを超えない最大の2の乗数のWAY数Zi」個の前記単位メモリをWAY数Ziでインタリーブする制御を実施させることを特徴とする請求項11記載のプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2007−172381(P2007−172381A)

【公開日】平成19年7月5日(2007.7.5)

【国際特許分類】

【出願番号】特願2005−370606(P2005−370606)

【出願日】平成17年12月22日(2005.12.22)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成19年7月5日(2007.7.5)

【国際特許分類】

【出願日】平成17年12月22日(2005.12.22)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]