情報処理装置、情報処理装置の識別方法、情報処理装置の識別プログラム及びマザーボード

【課題】必要な処理のみを実行して、消費電力の増加を防止する。

【解決手段】情報処理装置1は、電子装置に対応したインタフェースが設置され、自己を識別する識別情報3aを備える着脱可能なサブボード3が接続されると、識別情報取得部2bが、サブボード3の識別情報3aを取得し、識別部2cが、取得したサブボード3の識別情報3aに基づき、サブボード3の識別情報3aに対応付けられた、サブボード3に設置されたインタフェースに関するインタフェース情報から、接続されたサブボード3に設置されたインタフェースを識別する。

【解決手段】情報処理装置1は、電子装置に対応したインタフェースが設置され、自己を識別する識別情報3aを備える着脱可能なサブボード3が接続されると、識別情報取得部2bが、サブボード3の識別情報3aを取得し、識別部2cが、取得したサブボード3の識別情報3aに基づき、サブボード3の識別情報3aに対応付けられた、サブボード3に設置されたインタフェースに関するインタフェース情報から、接続されたサブボード3に設置されたインタフェースを識別する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、情報処理装置、情報処理装置の識別方法、情報処理装置の識別プログラム及びマザーボードに関する。

【背景技術】

【0002】

コンピュータ等の情報処理装置に対して、ユーザは、例えばプリンタ装置等の電子装置を接続して、情報処理装置を介して当該プリンタ装置を利用することができる(例えば、特許文献1参照)。

【0003】

特に、金融機関では、情報処理装置に対して、通帳用のプリンタ装置もしくはイメージリーダ装置、IC(Integrated Circuit)チップ付キャッシュカードのリーダライタ装置、入出金等の操作を容易に実行できるキーボード等の金融機関特有で多種多様な電子装置が接続されて使用されている。このため、金融機関で利用されている情報処理装置では、各金融機関に個別対応できるように電子装置が接続可能な、コネクタ類が具備された回路基板(サブボード)が用いられている。具体的には、情報処理装置の回路基板(マザーボード)に対してこのようなサブボードを接続して、当該サブボードを介した、多種多様な電子装置を接続することができる。また、情報処理装置のマザーボードをそのままの状態に維持して、当該サブボードを別の種類に交換することで、情報処理装置に接続させたい電子装置の数及び種類を変更することができることから、情報処理装置のマザーボードを共通化することができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平3−15940号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、情報処理装置のマザーボードに対して、サブボードを接続しても、マザーボード側では、当該サブボードに対応されているインタフェースの種類及び数が認識されない。このため、情報処理装置のマザーボードでは、あらゆるインタフェースを動作可能状態に制御できるコントローラ(制御部)を実行するようにしておく必要があり、余計な処理の増加に伴って、消費電力が増加するという問題点があった。

【0006】

本願はこのような点に鑑みてされたものであり、サブボードに対応されたインタフェースを識別できる情報処理装置、情報処理装置の識別方法、情報処理装置の識別プログラム及びマザーボードを提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、電子装置が接続される情報処理装置において、前記電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードと、前記ボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報を記憶するインタフェース情報記憶部と、前記ボードが接続されると、前記ボードの前記識別情報を取得する識別情報取得部と、取得した前記ボードの前記識別情報に基づき、前記インタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別する識別部と、を有する情報処理装置が提供される。

【0008】

また、上記目的を達成するために、上記の情報処理装置と同様の方法及び同様の処理をコンピュータに実行させるプログラムが提供される。

また、上記目的を達成するために、電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報を記憶するインタフェース情報記憶部と、前記ボードが接続されると、前記ボードの前記識別情報を取得する識別情報取得部と、取得した前記ボードの前記識別情報に基づき、前記インタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別する識別部と、を有するマザーボードが提供される。

【発明の効果】

【0009】

上記の情報処理装置、情報処理装置の識別方法、情報処理装置の識別プログラム及びマザーボードによれば、必要な処理のみを実行させて、消費電力の増加を防止することができる。

【図面の簡単な説明】

【0010】

【図1】第1の実施の形態に係る情報処理装置の構成及び機能を示す図である。

【図2】第2の実施の形態に係る情報処理装置のハードウェア構成例を示す図である。

【図3】第2の実施の形態に係る情報処理装置の入出力インタフェースのハードウェア構成例を示す図である。

【図4】第2の実施の形態に係る情報処理装置のサブボードのハードウェア構成例を示す図である。

【図5】第2の実施の形態に係る情報処理装置が備える機能を示すブロック図である。

【図6】第2の実施の形態に係る情報処理装置が備えるテーブルの具体例を示す図である。

【図7】第2の実施の形態に係る情報処理装置で識別を実行するための処理手順を示すフローチャートである。

【発明を実施するための形態】

【0011】

以下、実施の形態を図面を参照して詳細に説明する。

[第1の実施の形態]

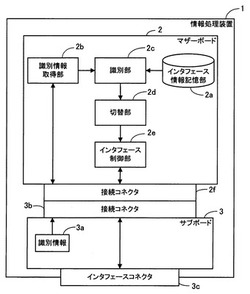

図1は、第1の実施の形態に係る情報処理装置の構成及び機能を示す図である。

【0012】

情報処理装置1は、種々のインタフェースに対応したサブボード3が接続されると、当該サブボード3に対応されたインタフェースを識別することができるものである。

このような情報処理装置1は、図1に示されるように、マザーボード2と、当該マザーボード2に着脱可能に接続されたサブボード3とを備えて、サブボード3は種々のインタフェースに対応されている。

【0013】

マザーボード2は、インタフェース情報記憶部2a、識別情報取得部2b、識別部2c、切替部2d及びインタフェース制御部2eを具備しており、さらに、後述するサブボード3が接続される接続コネクタ2fが設置されている。

【0014】

インタフェース情報記憶部2aは、後述するサブボード3の識別情報3aに対応付けられた、サブボード3に対応されたインタフェースを表すインタフェース情報を記憶する。インタフェース情報は、例えば、USB(Universal Serial Bus)、LAN、パラレル等を表す情報である。

【0015】

識別情報取得部2bは、サブボード3が接続コネクタ2fに接続されるとサブボード3の識別情報3aを取得する。

識別部2cは、取得した識別情報3aに基づき、インタフェース情報記憶部2aが記憶するインタフェース情報から、接続されたサブボード3に対応されたインタフェースを識別する。

【0016】

切替部2dは、識別部2cの識別結果に応じて、後述するインタフェース制御部2eの機能のオン状態/オフ状態を切り替える。

インタフェース制御部2eは、サブボード3に対応されたインタフェースを動作可能状態に制御する。なお、インタフェース制御部2eは、インタフェースの種類に応じて設置されており、前述の切替部2dにより、それぞれのインタフェース制御部2eがオン状態/オフ状態に切り替えられる。

【0017】

接続コネクタ2fは、サブボード3が接続されて、当該接続コネクタ2fを介して、マザーボード2とサブボード3との信号の送受信が実行される。

なお、情報処理装置1は、マザーボード2に配置された、例えば、CPU(Central Processing Unit:中央処理装置)、RAM(Random Access Memory)、HDD(Hard Disk Drive)等の各部(それぞれ図示を省略)が互いにバスで接続されたコンピュータとして実現される。この場合、識別情報取得部2b及び識別部2cの機能は、例えば、CPUにより所定のプログラムで実現される。また、切替部2d及びインタフェース制御部2eは、例えば、CPUが実装されたマザーボード2上の回路として実現される。

【0018】

一方、サブボード3は、自己を識別する識別情報3aを具備しており、さらに、マザーボード2の接続コネクタ2fに接続可能な接続コネクタ3bと、種々のインタフェースに対応することができるインタフェースコネクタ3cとが設置されている。また、サブボード3のインタフェースコネクタ3cに接続された電子装置は、接続コネクタ2fに接続したサブボード3を介して、マザーボード2と信号の送受信が行われる。

【0019】

次に、このような構成及び機能を備える情報処理装置1におけるサブボード3の識別方法の例について説明する。

まず、マザーボード2の接続コネクタ2fに、サブボード3の接続コネクタ3bを接続すると、識別情報取得部2bがサブボード3の識別情報3aを取得する。

【0020】

次いで、識別部2cが、識別情報取得部2bが取得した識別情報3aに基づいて、インタフェース情報記憶部2aのインタフェース情報を参照して、接続されたサブボード3に対応されたインタフェースを識別する。

【0021】

切替部2dは、識別部2cの識別結果に応じて、サブボード3に対応されたインタフェースを動作可能状態に制御するインタフェース制御部2eの機能のみをオン状態にする。

そして、オン状態となったインタフェース制御部2eのみがインタフェースを動作可能状態に制御する。

【0022】

以後、サブボード3のインタフェースに所定の電子装置が接続されると、マザーボード2側で当該電子装置が認識されて、利用されるようになる。

このように、情報処理装置1では、所定のインタフェースが対応されて、識別情報3aを有するサブボード3をマザーボード2に接続した際に、マザーボード2の識別部2cが、当該識別情報に基づいて、インタフェース情報を参照して、接続されたサブボード3に対応されたインタフェースを識別するようにした。

【0023】

これにより、マザーボード2では、サブボード3に対応されたインタフェースを動作可能状態に制御するインタフェース制御部2eの機能のみを利用可能状態にして、サブボード3に対応されていないインタフェースに関するインタフェース制御部2eの機能は利用不可(オフ)状態が維持される。

【0024】

したがって、マザーボード2において、余計な処理の負担と共に、当該処理に応じた消費電力の増加が抑制されるようになる。

また、このような情報処理装置1では、サブボード3に、LANカード等の汎用拡張インタフェースのように、インタフェースに対応した制御装置を搭載させる必要がなく、インタフェースを動作可能状態に制御できる。このため、サブボード3に制御装置の設置等のコストアップを抑制できると共に、サブボード3の小型化に伴って、情報処理装置1を小型化することができる。さらに、情報処理装置1では、マザーボード2により、対応されたインタフェースが動作可能状態に制御される。このため、インタフェースの種類及び数に応じてマザーボード2のBIOS(Basic Input/Output System)を設定するための作業を省略することができる。また、1つのマザーボード2に対して、必要に応じてサブボード3を交換することで様々なインタフェースに対応することができ、インタフェースのバリエーションを増加させることが可能であって、マザーボード2の共通化を実現させることができる。

【0025】

[第2の実施の形態]

次に、上記の情報処理装置について具体的に説明する。

図2は、第2の実施の形態に係る情報処理装置のハードウェア構成例を示す図である。

【0026】

情報処理装置10は、図2に示されるように、マザーボード20と、当該マザーボード20に着脱可能に接続されたサブボード30とを備えて、サブボード30に設置したインタフェースに電子装置を接続することができる。

【0027】

マザーボード20は、CPU20a、RAM20b、HDD20c及び入出力インタフェース20dが設置されている。これらの各部はバス20eで相互に接続されている。

CPU20aは、RAM20b等の記憶媒体に記憶された各種プログラムを実行することにより、この情報処理装置10全体及びサブボード30のインタフェースを統括的に制御する。

【0028】

RAM20bには、CPU20aに実行させるOS(Operating System)やプログラムの少なくとも一部が一時的に格納される。また、RAM20bには、CPU20aによる処理に必要な各種データが格納される。

【0029】

HDD20cには、情報処理装置10上のOSやアプリケーションのプログラムが格納される。また、HDD20cには、CPU20aによる処理に必要な各種データが格納される。

【0030】

入出力インタフェース20dは、接続コネクタ20fを介してサブボード30の接続コネクタ30cに接続され、後述するサブボード30のインタフェースに対して所定の信号の送受信を実行する。また、入出力インタフェース20dは、接続コネクタ20fを介してサブボード30から後述する識別情報31(図5)を受信する。なお、入出力インタフェース20dの構成等の詳細については後述する。

【0031】

一方、サブボード30は、識別回路30a及び電子装置インタフェース30bが配置されている。さらにサブボード30には、マザーボード20の接続コネクタ20fに接続する接続コネクタ30cと、種々のインタフェースに対応されたインタフェースコネクタ30dとが設置されている。

【0032】

識別回路30aは、マザーボード20に電源が投入されると、識別情報31(図5)として所定の応答信号をマザーボード20に対して送信する。

電子装置インタフェース30bは、インタフェースコネクタ30dと接続コネクタ30cとの間の信号の送受信を行う。

【0033】

なお、インタフェースコネクタ30dには、図2では、具体例として、モニタ40、マウス50及びキーボード60が接続されている。これらに対して、マザーボード20のCPU20aは、入出力インタフェース20d及びサブボード30を介して、信号の送受信を実行する。なお、サブボード30の詳細な説明については後述する。

【0034】

次に、入出力インタフェース20dの構成の詳細についてさらに説明する。

図3は、第2の実施の形態に係る情報処理装置の入出力インタフェースのハードウェア構成例を示す図である。

【0035】

入出力インタフェース20dは、図3に示されるように、チップセット20g、切替部20j、オーディオ制御部20k及びネットワーク制御部20lが配置されている。

チップセット20gは、サブボード30からの信号を、接続コネクタ20fを介して、入力すると共に、入力した信号に内部で所定の処理を実行して、所定の信号を出力するGPIO(General Purpose Input/Output:汎用入出力)20iが設置されている。例えば、GPIO20iのGPIOa及びGPIObでは、接続コネクタ20fを介して、サブボード30からの識別情報31を入力する。また、チップセット20gが入力した識別情報31に応じた信号がGPIO1及びGPIO2から出力される。

【0036】

また、チップセット20gには、USB制御部20hが配置されており、USB制御部20hがオン状態であるときに、サブボード30に接続されたUSBを利用することができる。なお、USB制御部20hは、接続コネクタ20fを介して、サブボード30に設けられた複数のUSBコネクタ30d2,130d2(図4(A),(B))ごとに接続されたUSBでの通信を制御することが可能である。

【0037】

切替部20jは、GPIO1及びGPIO2からの信号が入力されて、後述するオーディオ制御部20k及びネットワーク制御部20lの各制御機能をオン状態/オフ状態にそれぞれ切り替える。具体的には、切替部20jには、図3に示されるように、GPIO1及びGPIO2からの信号がそれぞれ入力されるスイッチ素子(トランジスタ素子)が配置されている。当該スイッチ素子が、GPIO1及びGPIO2からの信号に応じて、オーディオ制御部20k及びネットワーク制御部20lの各制御機能をオン状態/オフ状態にそれぞれ切り替える。

【0038】

オーディオ制御部20kは、オン状態の時に、サブボード30に設けられたオーディオコネクタ130d1(図4(B))を有効に利用されるように制御することが可能である。

【0039】

ネットワーク制御部20lは、オン状態の時に、サブボード30に設けられたLANコネクタ30d1(図4(A))を有効に利用されるように制御することが可能である。

なお、これらのオーディオ制御部20k及びネットワーク制御部20lは、サブボード30に接続可能なインタフェースを制御する制御部の例であって、インタフェースに対応して適宜配置することができる。インタフェースに対応した制御部を配置するに伴って、切替部20jにはスイッチ素子も配置される。

【0040】

このような構成を有する入出力インタフェース20dと電気的に接続された接続コネクタ20fに接続されるサブボード30の具体例について以下に説明する。

図4は、第2の実施の形態に係る情報処理装置のサブボードのハードウェア構成例を示す図である。

【0041】

図2に示した情報処理装置10のサブボード30の具体例としてサブボードA,Bを適用することができる。なお、図4(A)にはサブボードAが、図4(B)にはサブボードBがそれぞれ示されている。

【0042】

サブボードAは、図4(A)に示されるように、まず、識別回路30aとして、IDピンa,bを有する。IDピンa,bは、マザーボード20に電源が投入されると、IDピンaから「high(=1)」の応答信号をチップセット20gのGPIOaに、IDピンbから「low(=0)」の応答信号をチップセット20gのGPIObにそれぞれサブボードAの識別情報31として出力する。なお、この時のIDピンa,bから出力される応答信号を(1,0)と表すことにする。

【0043】

また、サブボードAのインタフェースコネクタ30dは、LAN接続されるLANコネクタ30d1と、4つまでのUSBが接続可能なUSBコネクタ30d2とを有する。

一方、サブボードBは、図4(B)に示されるように、識別回路30aとして、IDピンa,bを有するものの、マザーボード20に電源が投入されると、IDピンaから「0」の応答信号をチップセット20gのGPIOaに、IDピンbから「1」の応答信号をチップセット20gのGPIObにそれぞれサブボードBの識別情報31として(0,1)を出力する。

【0044】

また、サブボードBのインタフェースコネクタ30dは、スピーカが接続されるオーディオコネクタ130d1と、2つまでのUSBが接続可能なUSBコネクタ130d2とを有する。

【0045】

なお、図4の場合には、2本のIDピンa,bにより、4パターン((a,b)=(0,0)、(0,1)、(1,0)、(1,1))のサブボード30を識別することができる。また、IDピンの本数は2本に限らず、サブボード30の種類の数に応じて、1本、または、3本以上を設置することができる。

【0046】

次いで、情報処理装置10が備える制御機能について説明する。

図5は、第2の実施の形態に係る情報処理装置が備える機能を示すブロック図である。

情報処理装置10は、種々のインタフェースが対応されたサブボード30が接続されると、当該サブボード30を識別すると共に、サブボード30に対応されたインタフェースを特定し、当該インタフェースを動作可能状態に制御する制御機能のみをオン状態に切り替えることができるものである。

【0047】

このような情報処理装置10のマザーボード20は、インタフェース情報テーブル21、切替処理情報テーブル22及びBIOS23を有し、サブボード30は自己を識別する識別情報31を具備する。

【0048】

インタフェース情報テーブル21は、識別情報31に、サブボード30と共に当該サブボード30に対応されたインタフェースがそれぞれ対応付けられたインタフェース情報を示すものである。

【0049】

また、切替処理情報テーブル22は、サブボード30に対応されたインタフェースを動作可能状態に制御する制御機能のオン状態/オフ状態に切り替えるための切替処理情報を示すものである。

【0050】

ここで、上記のインタフェース情報テーブル21及び切替処理情報テーブル22の詳細について説明する。

図6は、第2の実施の形態に係る情報処理装置が備えるテーブルの具体例を示す図である。

【0051】

なお、図6(A)はインタフェース情報テーブル21を、図6(B)は切替処理情報テーブル22をそれぞれ表している。また、インタフェース情報テーブル21は、サブボードA,Bにそれぞれ対応可能なインタフェース及び当該インタフェースの数を示している。

【0052】

インタフェース情報テーブル21には、図6(A)に示されるように、IDピンa,bに応じてサブボードA,Bが対応付けられている。さらに、サブボードA,Bに対して、対応されたインタフェースとして、「USB」、「LAN」及び「AUDIO」のそれぞれの数が示されている。

【0053】

具体的には、識別情報31としてIDピンa,bが(1,0)の場合には、サブボードAが対応付けられる。

さらに、サブボードAは、図4(A)にも示したように、LANコネクタ30d1及びUSBが4つまで対応可能なUSBコネクタ30d2が対応可能であるために、インタフェース数として、「USB」に4、「LAN」に1が設定されている。一方、サブボードAにはオーディオコネクタは設置されていないために、「AUDIO」には0が設定されている。

【0054】

また、識別情報31としてIDピンa,bが(0,1)の場合には、サブボードBが対応付けられる。

さらに、サブボードBは、図4(B)にも示されるように、オーディオコネクタ130d1及びUSBが2つまで対応可能なUSBコネクタ130d2が接続可能であるために、インタフェース数として、「USB」に2、「AUDIO」に1が設定されている。一方、サブボードBにはLANコネクタは設置されていないために、「LAN」には0が設定されている。

【0055】

一方、切替処理情報テーブル22には、図6(B)に示されるように、「USB1〜4」、「LAN」及び「AUDIO」をそれぞれ有効にする場合には「1」に、無効にする場合には「0」に設定する。

【0056】

後述する切替設定部23cは、インタフェース情報テーブル21のサブボード30に対応されたインタフェースの特定結果に応じて、切替処理情報テーブル22を参照して、インタフェースを動作可能(有効)に制御する制御機能のオン状態/オフ状態が切り替えられる。

【0057】

具体的には、切替処理情報テーブル22から、サブボードAの場合には、「USB1〜4」、「LAN」を「有効(=1)」に、「AUDIO」を「無効(=0)」に設定する。

【0058】

また、サブボードBの場合には、「USB1,2」及び「AUDIO」をそれぞれ「1」に、「USB3,4」及び「LAN」を「0」に設定する。

図5に戻り、BIOS23では、サブボード30の識別情報31からサブボード30に対応されたインタフェースを特定すると共に、当該インタフェースを動作可能に制御する制御機能の状態を切り替えることができる。

【0059】

BIOS23は、このような処理を実行する、識別情報取得部23a、識別部23b及び切替設定部23cを有する。

識別情報取得部23aは、サブボード30から識別情報31を取得する。識別情報取得部23aは、取得の際には、図3で示したように、GPIOa及びGPIObからサブボード30のIDピンa,bからの信号を受信する。

【0060】

識別部23bは、識別情報取得部23aが取得した識別情報31に基づいて、インタフェース情報テーブル21を参照して、接続されているサブボード30を識別するとともに、サブボード30に対応されたインタフェースを特定する。

【0061】

例えば、識別部23bは、識別情報取得部23aが取得した識別情報31のIDピンa,b(0,1)に基づいて、インタフェース情報テーブル21からサブボードBが接続されていることを識別する。さらに、インタフェース情報テーブル21からサブボードBには、USBが2つまで対応可能なUSBコネクタ130d2と、オーディオコネクタ130d1とが設置されていることを特定することができる。

【0062】

切替設定部23cは、識別部23bにより識別されたサブボード30に対応されたインタフェースに基づいて、切替処理情報テーブル22に応じて、サブボード30に対応されたインタフェースを動作可能状態に制御する制御機能のオン状態/オフ状態を決定する。さらに、切替設定部23cは、決定結果に基づいて、USB制御部20hに、USB制御部20hが4つのうちいずれかのUSBを動作可能状態に制御するための切替要求を通知する。また、切替設定部23cは、決定結果に基づいて、切替部20jにオーディオ制御部20kまたはネットワーク制御部20lの切替要求を通知する。

【0063】

次に、情報処理装置10で行われるサブボード30を識別するための処理手順について図5と共に図7を参照して説明する。

図7は、第2の実施の形態に係る情報処理装置で識別を実行するための処理手順を示すフローチャートである。

【0064】

まず初期設定として、予め、インタフェース情報テーブル21にインタフェース情報と、切替処理情報テーブル22に切替処理情報とをそれぞれ記憶させておく。

マザーボード20の電源を切った状態で、マザーボード20の接続コネクタ20fに、サブボード30の接続コネクタ30cを接続する。

【0065】

[ステップS11]

マザーボード20に電源を投入すると、BIOS23が起動して、最低限動作が必要な主コンポーネント(例えば、CPU20a、RAM20b、チップセット20g等)を初期化する。

【0066】

[ステップS12]

初期化終了後、BIOS23の識別情報取得部23aが、サブボード30の識別情報31としてIDピンa,bからの信号を取得する。

【0067】

[ステップS13]

BIOS23の識別部23bは、識別情報取得部23aが取得した識別情報31に基づき、インタフェース情報テーブル21を参照して、マザーボード20に接続されたサブボード30を識別すると共に、当該サブボード30に対応されたインタフェースを特定する。

【0068】

[ステップS14]

BIOS23の切替設定部23cは、ステップS13の特定結果に基づき、切替処理情報テーブル22を参照して、サブボード30に対応されたインタフェースを動作可能状態に制御する制御機能のオン状態/オフ状態の切替を決定する。切替設定部23cは、決定結果に基づいて、USB制御部20hと切替部20jに切替要求を通知する。

【0069】

[ステップS15]

USB制御部20hは、ステップS14の切替要求に基づいて、サブボード30のUSBコネクタを有効に設定する。また、切替部20jは、ステップS14の切替要求に基づいて、オーディオ制御部20kまたはネットワーク制御部20lのうち少なくとも1つを有効に設定する。

【0070】

上記の設定が終了すると、以後通常の初期化処理が実行され、以後、サブボード30のインタフェースにUSB、LANが接続されると、マザーボード20側で当該インタフェースが認識されて、利用されるようになる。

【0071】

次に、情報処理装置10におけるサブボード30の識別処理について具体的に説明する。

まず、情報処理装置10のマザーボード20にサブボードA(図4(A))を接続する場合について説明する。

【0072】

マザーボード20の電源を切った状態で、マザーボード20の接続コネクタ20fに、サブボードAの接続コネクタ30cを接続した後、マザーボード20に電源を投入すると、BIOS23が起動して、最低限動作が必要な主コンポーネントを初期化する(ステップS11)。

【0073】

BIOS23の識別情報取得部23aが、サブボードAのIDピンa,bを参照し、IDピンa,bから識別情報31の(1,0)を取得する(ステップS12)。

BIOS23の識別部23bは、識別情報取得部23aが取得した識別情報31の(1,0)に基づき、インタフェース情報テーブル21(図6(A))を参照して、マザーボード20に接続されたサブボードAを識別する。さらに、当該サブボードAに対応されたインタフェースが4つのUSB、LANであることを特定する(ステップS13)。

【0074】

BIOS23の切替設定部23cは、切替処理情報テーブル22(図6(B))を参照して、サブボードAのUSBコネクタ30d2のUSB1〜4を動作可能状態に制御するUSB制御部20hと、LANコネクタ30d1を動作可能状態に制御するネットワーク制御部20lとの制御機能をオン状態に切り替えることを決定する。さらに、切替設定部23cは、決定結果に基づいて、USB制御部20hと切替部20jに当該切替要求を通知する(ステップS14)。

【0075】

USB制御部20hは、切替要求に基づいて、USBコネクタ30d2のUSB1〜4を「1」に設定して、USB1〜4を動作可能状態に制御する。また、切替部20jは、切替要求に基づいて、ネットワーク制御部20lをオン状態に切り替えて、ネットワーク制御部20lはLANコネクタ30d1を動作可能状態に制御する。

【0076】

このような制御により、オーディオ制御部20kがオン状態に維持されたままで、サブボードAのLANコネクタ30d1及びUSBコネクタ30d2が通常に利用できるようになる。

【0077】

次に、情報処理装置10のマザーボード20にサブボードB(図4(B))を接続する場合について説明する。

上記と同様に、マザーボード20の電源を切った状態で、マザーボード20の接続コネクタ20fに、サブボードBの接続コネクタ30cを接続した後、マザーボード20に電源を投入する(ステップS11)。

【0078】

BIOS23の識別情報取得部23aが、サブボードBのIDピンa,bを参照し、IDピンa,bから識別情報31の(0,1)を取得する(ステップS12)。

BIOS23の識別部23bは、識別情報取得部23aが取得した識別情報31の(0,1)に基づき、インタフェース情報テーブル21(図6(A))を参照して、マザーボード20に接続されたサブボードBを識別する。さらに、当該サブボードBに対応されたインタフェースが2つのUSB、オーディオであることを特定する(ステップS13)。

【0079】

BIOS23の切替設定部23cは、切替処理情報テーブル22(図6(B))を参照して、サブボードBのUSBコネクタ130d2のUSB1,2を動作可能状態に制御するUSB制御部20hと、オーディオコネクタ130d1を動作可能状態に制御するオーディオ制御部20kとの制御機能をオン状態に切り替えることを決定する。さらに、切替設定部23cは、決定結果に基づいて、USB制御部20hと切替部20jに当該切替要求を通知する(ステップS14)。

【0080】

USB制御部20hは、切替要求に基づいて、USBコネクタ130d2のUSB1,2を「1」に設定して、USB1,2を動作可能状態に制御する。また、切替部20jは、切替要求に基づいて、オーディオ制御部20kをオン状態に切り替えて、オーディオ制御部20kはオーディオコネクタ130d1を動作可能状態に制御する。

【0081】

このような制御により、ネットワーク制御部20lがオフ状態に維持されたままで、サブボードBのオーディオコネクタ130d1及びUSBコネクタ130d2が通常に利用できるようになる。

【0082】

このように、情報処理装置10のマザーボード20では、サブボード30に対応されたインタフェースを動作可能状態に制御する制御機能のみを利用可能状態にした。一方、サブボード30に対応されていないインタフェースを動作可能状態に制御する制御機能は利用不可(オフ)状態が維持される。

【0083】

したがって、マザーボード20において、余計な処理の負担と共に、当該処理に応じた消費電力が削減されるようになる。

また、このような情報処理装置10では、サブボード30に、LANカード等の汎用拡張インタフェースのように、インタフェースに対応した制御装置を搭載させる必要がなく、インタフェースを動作可能状態に制御できる。このため、サブボード30に制御装置の設置等のコストアップを抑制できると共に、サブボード30の小型化に伴って、情報処理装置10を小型化することができる。さらに、情報処理装置10では、マザーボード20により、対応されたインタフェースが動作可能状態に制御される。このため、インタフェースの種類及び数に応じてマザーボード20のBIOSを設定するための作業を省略することができる。また、1つのマザーボード20に対して、必要に応じてサブボード30を交換することで様々なインタフェースに対応することができ、インタフェースのバリエーションを増加させることが可能であって、マザーボード20の共通化を実現させることができる。

【0084】

なお、上記で示した処理機能の一部は、コンピュータによって実現することができる。その場合、情報処理装置が有すべき機能の処理内容を記述したプログラムが提供される。そのプログラムをコンピュータで実行することにより、上記処理機能がコンピュータ上で実現される。処理内容を記述したプログラムは、コンピュータで読み取り可能な記録媒体に記録しておくことができる。コンピュータで読み取り可能な記録媒体としては、磁気記憶装置、光ディスク、光磁気記録媒体、半導体メモリ等がある。磁気記憶装置には、ハードディスク装置(HDD)、フレキシブルディスク(FD)、磁気テープ等がある。光ディスクには、DVD、DVD−RAM、CD−ROM/RW等がある。光磁気記録媒体には、MO(Magneto-Optical disk)等がある。

【0085】

プログラムを流通させる場合には、例えば、そのプログラムが記録されたDVD、CD−ROM等の可搬型記録媒体が販売される。また、プログラムをサーバコンピュータの記憶装置に格納しておき、ネットワークを介して、サーバコンピュータから他のコンピュータにそのプログラムを転送することもできる。

【0086】

プログラムを実行するコンピュータは、例えば、可搬型記録媒体に記録されたプログラムもしくはサーバコンピュータから転送されたプログラムを、自己の記憶装置に格納する。そして、コンピュータは、自己の記憶装置からプログラムを読み取り、プログラムに従った処理を実行する。なお、コンピュータは、可搬型記録媒体から直接プログラムを読み取り、そのプログラムに従った処理を実行することもできる。また、コンピュータは、ネットワークを介して接続されたサーバコンピュータからプログラムが転送されるごとに、逐次、受け取ったプログラムに従った処理を実行することもできる。

【0087】

また、上記の処理機能の少なくとも一部を、DSP(Digital Signal Processor)、ASIC(Application Specific Integrated Circuit)、PLD(Programmable Logic Device)等の電子回路で実現することもできる。

【符号の説明】

【0088】

1,10 情報処理装置

2,20 マザーボード

2a インタフェース情報記憶部

2b,23a 識別情報取得部

2c,23b 識別部

2d,20j 切替部

2e インタフェース制御部

2f,3b,20f,30c 接続コネクタ

3,30,A,B サブボード

3a 識別情報

3c,30d インタフェースコネクタ

20a CPU

20b RAM

20c HDD

20d 入出力インタフェース

20e バス

20g チップセット

20h USB制御部

20i GPIO

20k オーディオ制御部

20l ネットワーク制御部

21 インタフェース情報テーブル

22 切替処理情報テーブル

23 BIOS

23c 切替設定部

30a 識別回路

30b 電子装置インタフェース

30d1 LANコネクタ

30d2,130d2 USBコネクタ

31 識別情報

130d1 オーディオコネクタ

40 モニタ

50 マウス

60 キーボード

a,b IDピン

【技術分野】

【0001】

本発明は、情報処理装置、情報処理装置の識別方法、情報処理装置の識別プログラム及びマザーボードに関する。

【背景技術】

【0002】

コンピュータ等の情報処理装置に対して、ユーザは、例えばプリンタ装置等の電子装置を接続して、情報処理装置を介して当該プリンタ装置を利用することができる(例えば、特許文献1参照)。

【0003】

特に、金融機関では、情報処理装置に対して、通帳用のプリンタ装置もしくはイメージリーダ装置、IC(Integrated Circuit)チップ付キャッシュカードのリーダライタ装置、入出金等の操作を容易に実行できるキーボード等の金融機関特有で多種多様な電子装置が接続されて使用されている。このため、金融機関で利用されている情報処理装置では、各金融機関に個別対応できるように電子装置が接続可能な、コネクタ類が具備された回路基板(サブボード)が用いられている。具体的には、情報処理装置の回路基板(マザーボード)に対してこのようなサブボードを接続して、当該サブボードを介した、多種多様な電子装置を接続することができる。また、情報処理装置のマザーボードをそのままの状態に維持して、当該サブボードを別の種類に交換することで、情報処理装置に接続させたい電子装置の数及び種類を変更することができることから、情報処理装置のマザーボードを共通化することができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平3−15940号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、情報処理装置のマザーボードに対して、サブボードを接続しても、マザーボード側では、当該サブボードに対応されているインタフェースの種類及び数が認識されない。このため、情報処理装置のマザーボードでは、あらゆるインタフェースを動作可能状態に制御できるコントローラ(制御部)を実行するようにしておく必要があり、余計な処理の増加に伴って、消費電力が増加するという問題点があった。

【0006】

本願はこのような点に鑑みてされたものであり、サブボードに対応されたインタフェースを識別できる情報処理装置、情報処理装置の識別方法、情報処理装置の識別プログラム及びマザーボードを提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、電子装置が接続される情報処理装置において、前記電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードと、前記ボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報を記憶するインタフェース情報記憶部と、前記ボードが接続されると、前記ボードの前記識別情報を取得する識別情報取得部と、取得した前記ボードの前記識別情報に基づき、前記インタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別する識別部と、を有する情報処理装置が提供される。

【0008】

また、上記目的を達成するために、上記の情報処理装置と同様の方法及び同様の処理をコンピュータに実行させるプログラムが提供される。

また、上記目的を達成するために、電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報を記憶するインタフェース情報記憶部と、前記ボードが接続されると、前記ボードの前記識別情報を取得する識別情報取得部と、取得した前記ボードの前記識別情報に基づき、前記インタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別する識別部と、を有するマザーボードが提供される。

【発明の効果】

【0009】

上記の情報処理装置、情報処理装置の識別方法、情報処理装置の識別プログラム及びマザーボードによれば、必要な処理のみを実行させて、消費電力の増加を防止することができる。

【図面の簡単な説明】

【0010】

【図1】第1の実施の形態に係る情報処理装置の構成及び機能を示す図である。

【図2】第2の実施の形態に係る情報処理装置のハードウェア構成例を示す図である。

【図3】第2の実施の形態に係る情報処理装置の入出力インタフェースのハードウェア構成例を示す図である。

【図4】第2の実施の形態に係る情報処理装置のサブボードのハードウェア構成例を示す図である。

【図5】第2の実施の形態に係る情報処理装置が備える機能を示すブロック図である。

【図6】第2の実施の形態に係る情報処理装置が備えるテーブルの具体例を示す図である。

【図7】第2の実施の形態に係る情報処理装置で識別を実行するための処理手順を示すフローチャートである。

【発明を実施するための形態】

【0011】

以下、実施の形態を図面を参照して詳細に説明する。

[第1の実施の形態]

図1は、第1の実施の形態に係る情報処理装置の構成及び機能を示す図である。

【0012】

情報処理装置1は、種々のインタフェースに対応したサブボード3が接続されると、当該サブボード3に対応されたインタフェースを識別することができるものである。

このような情報処理装置1は、図1に示されるように、マザーボード2と、当該マザーボード2に着脱可能に接続されたサブボード3とを備えて、サブボード3は種々のインタフェースに対応されている。

【0013】

マザーボード2は、インタフェース情報記憶部2a、識別情報取得部2b、識別部2c、切替部2d及びインタフェース制御部2eを具備しており、さらに、後述するサブボード3が接続される接続コネクタ2fが設置されている。

【0014】

インタフェース情報記憶部2aは、後述するサブボード3の識別情報3aに対応付けられた、サブボード3に対応されたインタフェースを表すインタフェース情報を記憶する。インタフェース情報は、例えば、USB(Universal Serial Bus)、LAN、パラレル等を表す情報である。

【0015】

識別情報取得部2bは、サブボード3が接続コネクタ2fに接続されるとサブボード3の識別情報3aを取得する。

識別部2cは、取得した識別情報3aに基づき、インタフェース情報記憶部2aが記憶するインタフェース情報から、接続されたサブボード3に対応されたインタフェースを識別する。

【0016】

切替部2dは、識別部2cの識別結果に応じて、後述するインタフェース制御部2eの機能のオン状態/オフ状態を切り替える。

インタフェース制御部2eは、サブボード3に対応されたインタフェースを動作可能状態に制御する。なお、インタフェース制御部2eは、インタフェースの種類に応じて設置されており、前述の切替部2dにより、それぞれのインタフェース制御部2eがオン状態/オフ状態に切り替えられる。

【0017】

接続コネクタ2fは、サブボード3が接続されて、当該接続コネクタ2fを介して、マザーボード2とサブボード3との信号の送受信が実行される。

なお、情報処理装置1は、マザーボード2に配置された、例えば、CPU(Central Processing Unit:中央処理装置)、RAM(Random Access Memory)、HDD(Hard Disk Drive)等の各部(それぞれ図示を省略)が互いにバスで接続されたコンピュータとして実現される。この場合、識別情報取得部2b及び識別部2cの機能は、例えば、CPUにより所定のプログラムで実現される。また、切替部2d及びインタフェース制御部2eは、例えば、CPUが実装されたマザーボード2上の回路として実現される。

【0018】

一方、サブボード3は、自己を識別する識別情報3aを具備しており、さらに、マザーボード2の接続コネクタ2fに接続可能な接続コネクタ3bと、種々のインタフェースに対応することができるインタフェースコネクタ3cとが設置されている。また、サブボード3のインタフェースコネクタ3cに接続された電子装置は、接続コネクタ2fに接続したサブボード3を介して、マザーボード2と信号の送受信が行われる。

【0019】

次に、このような構成及び機能を備える情報処理装置1におけるサブボード3の識別方法の例について説明する。

まず、マザーボード2の接続コネクタ2fに、サブボード3の接続コネクタ3bを接続すると、識別情報取得部2bがサブボード3の識別情報3aを取得する。

【0020】

次いで、識別部2cが、識別情報取得部2bが取得した識別情報3aに基づいて、インタフェース情報記憶部2aのインタフェース情報を参照して、接続されたサブボード3に対応されたインタフェースを識別する。

【0021】

切替部2dは、識別部2cの識別結果に応じて、サブボード3に対応されたインタフェースを動作可能状態に制御するインタフェース制御部2eの機能のみをオン状態にする。

そして、オン状態となったインタフェース制御部2eのみがインタフェースを動作可能状態に制御する。

【0022】

以後、サブボード3のインタフェースに所定の電子装置が接続されると、マザーボード2側で当該電子装置が認識されて、利用されるようになる。

このように、情報処理装置1では、所定のインタフェースが対応されて、識別情報3aを有するサブボード3をマザーボード2に接続した際に、マザーボード2の識別部2cが、当該識別情報に基づいて、インタフェース情報を参照して、接続されたサブボード3に対応されたインタフェースを識別するようにした。

【0023】

これにより、マザーボード2では、サブボード3に対応されたインタフェースを動作可能状態に制御するインタフェース制御部2eの機能のみを利用可能状態にして、サブボード3に対応されていないインタフェースに関するインタフェース制御部2eの機能は利用不可(オフ)状態が維持される。

【0024】

したがって、マザーボード2において、余計な処理の負担と共に、当該処理に応じた消費電力の増加が抑制されるようになる。

また、このような情報処理装置1では、サブボード3に、LANカード等の汎用拡張インタフェースのように、インタフェースに対応した制御装置を搭載させる必要がなく、インタフェースを動作可能状態に制御できる。このため、サブボード3に制御装置の設置等のコストアップを抑制できると共に、サブボード3の小型化に伴って、情報処理装置1を小型化することができる。さらに、情報処理装置1では、マザーボード2により、対応されたインタフェースが動作可能状態に制御される。このため、インタフェースの種類及び数に応じてマザーボード2のBIOS(Basic Input/Output System)を設定するための作業を省略することができる。また、1つのマザーボード2に対して、必要に応じてサブボード3を交換することで様々なインタフェースに対応することができ、インタフェースのバリエーションを増加させることが可能であって、マザーボード2の共通化を実現させることができる。

【0025】

[第2の実施の形態]

次に、上記の情報処理装置について具体的に説明する。

図2は、第2の実施の形態に係る情報処理装置のハードウェア構成例を示す図である。

【0026】

情報処理装置10は、図2に示されるように、マザーボード20と、当該マザーボード20に着脱可能に接続されたサブボード30とを備えて、サブボード30に設置したインタフェースに電子装置を接続することができる。

【0027】

マザーボード20は、CPU20a、RAM20b、HDD20c及び入出力インタフェース20dが設置されている。これらの各部はバス20eで相互に接続されている。

CPU20aは、RAM20b等の記憶媒体に記憶された各種プログラムを実行することにより、この情報処理装置10全体及びサブボード30のインタフェースを統括的に制御する。

【0028】

RAM20bには、CPU20aに実行させるOS(Operating System)やプログラムの少なくとも一部が一時的に格納される。また、RAM20bには、CPU20aによる処理に必要な各種データが格納される。

【0029】

HDD20cには、情報処理装置10上のOSやアプリケーションのプログラムが格納される。また、HDD20cには、CPU20aによる処理に必要な各種データが格納される。

【0030】

入出力インタフェース20dは、接続コネクタ20fを介してサブボード30の接続コネクタ30cに接続され、後述するサブボード30のインタフェースに対して所定の信号の送受信を実行する。また、入出力インタフェース20dは、接続コネクタ20fを介してサブボード30から後述する識別情報31(図5)を受信する。なお、入出力インタフェース20dの構成等の詳細については後述する。

【0031】

一方、サブボード30は、識別回路30a及び電子装置インタフェース30bが配置されている。さらにサブボード30には、マザーボード20の接続コネクタ20fに接続する接続コネクタ30cと、種々のインタフェースに対応されたインタフェースコネクタ30dとが設置されている。

【0032】

識別回路30aは、マザーボード20に電源が投入されると、識別情報31(図5)として所定の応答信号をマザーボード20に対して送信する。

電子装置インタフェース30bは、インタフェースコネクタ30dと接続コネクタ30cとの間の信号の送受信を行う。

【0033】

なお、インタフェースコネクタ30dには、図2では、具体例として、モニタ40、マウス50及びキーボード60が接続されている。これらに対して、マザーボード20のCPU20aは、入出力インタフェース20d及びサブボード30を介して、信号の送受信を実行する。なお、サブボード30の詳細な説明については後述する。

【0034】

次に、入出力インタフェース20dの構成の詳細についてさらに説明する。

図3は、第2の実施の形態に係る情報処理装置の入出力インタフェースのハードウェア構成例を示す図である。

【0035】

入出力インタフェース20dは、図3に示されるように、チップセット20g、切替部20j、オーディオ制御部20k及びネットワーク制御部20lが配置されている。

チップセット20gは、サブボード30からの信号を、接続コネクタ20fを介して、入力すると共に、入力した信号に内部で所定の処理を実行して、所定の信号を出力するGPIO(General Purpose Input/Output:汎用入出力)20iが設置されている。例えば、GPIO20iのGPIOa及びGPIObでは、接続コネクタ20fを介して、サブボード30からの識別情報31を入力する。また、チップセット20gが入力した識別情報31に応じた信号がGPIO1及びGPIO2から出力される。

【0036】

また、チップセット20gには、USB制御部20hが配置されており、USB制御部20hがオン状態であるときに、サブボード30に接続されたUSBを利用することができる。なお、USB制御部20hは、接続コネクタ20fを介して、サブボード30に設けられた複数のUSBコネクタ30d2,130d2(図4(A),(B))ごとに接続されたUSBでの通信を制御することが可能である。

【0037】

切替部20jは、GPIO1及びGPIO2からの信号が入力されて、後述するオーディオ制御部20k及びネットワーク制御部20lの各制御機能をオン状態/オフ状態にそれぞれ切り替える。具体的には、切替部20jには、図3に示されるように、GPIO1及びGPIO2からの信号がそれぞれ入力されるスイッチ素子(トランジスタ素子)が配置されている。当該スイッチ素子が、GPIO1及びGPIO2からの信号に応じて、オーディオ制御部20k及びネットワーク制御部20lの各制御機能をオン状態/オフ状態にそれぞれ切り替える。

【0038】

オーディオ制御部20kは、オン状態の時に、サブボード30に設けられたオーディオコネクタ130d1(図4(B))を有効に利用されるように制御することが可能である。

【0039】

ネットワーク制御部20lは、オン状態の時に、サブボード30に設けられたLANコネクタ30d1(図4(A))を有効に利用されるように制御することが可能である。

なお、これらのオーディオ制御部20k及びネットワーク制御部20lは、サブボード30に接続可能なインタフェースを制御する制御部の例であって、インタフェースに対応して適宜配置することができる。インタフェースに対応した制御部を配置するに伴って、切替部20jにはスイッチ素子も配置される。

【0040】

このような構成を有する入出力インタフェース20dと電気的に接続された接続コネクタ20fに接続されるサブボード30の具体例について以下に説明する。

図4は、第2の実施の形態に係る情報処理装置のサブボードのハードウェア構成例を示す図である。

【0041】

図2に示した情報処理装置10のサブボード30の具体例としてサブボードA,Bを適用することができる。なお、図4(A)にはサブボードAが、図4(B)にはサブボードBがそれぞれ示されている。

【0042】

サブボードAは、図4(A)に示されるように、まず、識別回路30aとして、IDピンa,bを有する。IDピンa,bは、マザーボード20に電源が投入されると、IDピンaから「high(=1)」の応答信号をチップセット20gのGPIOaに、IDピンbから「low(=0)」の応答信号をチップセット20gのGPIObにそれぞれサブボードAの識別情報31として出力する。なお、この時のIDピンa,bから出力される応答信号を(1,0)と表すことにする。

【0043】

また、サブボードAのインタフェースコネクタ30dは、LAN接続されるLANコネクタ30d1と、4つまでのUSBが接続可能なUSBコネクタ30d2とを有する。

一方、サブボードBは、図4(B)に示されるように、識別回路30aとして、IDピンa,bを有するものの、マザーボード20に電源が投入されると、IDピンaから「0」の応答信号をチップセット20gのGPIOaに、IDピンbから「1」の応答信号をチップセット20gのGPIObにそれぞれサブボードBの識別情報31として(0,1)を出力する。

【0044】

また、サブボードBのインタフェースコネクタ30dは、スピーカが接続されるオーディオコネクタ130d1と、2つまでのUSBが接続可能なUSBコネクタ130d2とを有する。

【0045】

なお、図4の場合には、2本のIDピンa,bにより、4パターン((a,b)=(0,0)、(0,1)、(1,0)、(1,1))のサブボード30を識別することができる。また、IDピンの本数は2本に限らず、サブボード30の種類の数に応じて、1本、または、3本以上を設置することができる。

【0046】

次いで、情報処理装置10が備える制御機能について説明する。

図5は、第2の実施の形態に係る情報処理装置が備える機能を示すブロック図である。

情報処理装置10は、種々のインタフェースが対応されたサブボード30が接続されると、当該サブボード30を識別すると共に、サブボード30に対応されたインタフェースを特定し、当該インタフェースを動作可能状態に制御する制御機能のみをオン状態に切り替えることができるものである。

【0047】

このような情報処理装置10のマザーボード20は、インタフェース情報テーブル21、切替処理情報テーブル22及びBIOS23を有し、サブボード30は自己を識別する識別情報31を具備する。

【0048】

インタフェース情報テーブル21は、識別情報31に、サブボード30と共に当該サブボード30に対応されたインタフェースがそれぞれ対応付けられたインタフェース情報を示すものである。

【0049】

また、切替処理情報テーブル22は、サブボード30に対応されたインタフェースを動作可能状態に制御する制御機能のオン状態/オフ状態に切り替えるための切替処理情報を示すものである。

【0050】

ここで、上記のインタフェース情報テーブル21及び切替処理情報テーブル22の詳細について説明する。

図6は、第2の実施の形態に係る情報処理装置が備えるテーブルの具体例を示す図である。

【0051】

なお、図6(A)はインタフェース情報テーブル21を、図6(B)は切替処理情報テーブル22をそれぞれ表している。また、インタフェース情報テーブル21は、サブボードA,Bにそれぞれ対応可能なインタフェース及び当該インタフェースの数を示している。

【0052】

インタフェース情報テーブル21には、図6(A)に示されるように、IDピンa,bに応じてサブボードA,Bが対応付けられている。さらに、サブボードA,Bに対して、対応されたインタフェースとして、「USB」、「LAN」及び「AUDIO」のそれぞれの数が示されている。

【0053】

具体的には、識別情報31としてIDピンa,bが(1,0)の場合には、サブボードAが対応付けられる。

さらに、サブボードAは、図4(A)にも示したように、LANコネクタ30d1及びUSBが4つまで対応可能なUSBコネクタ30d2が対応可能であるために、インタフェース数として、「USB」に4、「LAN」に1が設定されている。一方、サブボードAにはオーディオコネクタは設置されていないために、「AUDIO」には0が設定されている。

【0054】

また、識別情報31としてIDピンa,bが(0,1)の場合には、サブボードBが対応付けられる。

さらに、サブボードBは、図4(B)にも示されるように、オーディオコネクタ130d1及びUSBが2つまで対応可能なUSBコネクタ130d2が接続可能であるために、インタフェース数として、「USB」に2、「AUDIO」に1が設定されている。一方、サブボードBにはLANコネクタは設置されていないために、「LAN」には0が設定されている。

【0055】

一方、切替処理情報テーブル22には、図6(B)に示されるように、「USB1〜4」、「LAN」及び「AUDIO」をそれぞれ有効にする場合には「1」に、無効にする場合には「0」に設定する。

【0056】

後述する切替設定部23cは、インタフェース情報テーブル21のサブボード30に対応されたインタフェースの特定結果に応じて、切替処理情報テーブル22を参照して、インタフェースを動作可能(有効)に制御する制御機能のオン状態/オフ状態が切り替えられる。

【0057】

具体的には、切替処理情報テーブル22から、サブボードAの場合には、「USB1〜4」、「LAN」を「有効(=1)」に、「AUDIO」を「無効(=0)」に設定する。

【0058】

また、サブボードBの場合には、「USB1,2」及び「AUDIO」をそれぞれ「1」に、「USB3,4」及び「LAN」を「0」に設定する。

図5に戻り、BIOS23では、サブボード30の識別情報31からサブボード30に対応されたインタフェースを特定すると共に、当該インタフェースを動作可能に制御する制御機能の状態を切り替えることができる。

【0059】

BIOS23は、このような処理を実行する、識別情報取得部23a、識別部23b及び切替設定部23cを有する。

識別情報取得部23aは、サブボード30から識別情報31を取得する。識別情報取得部23aは、取得の際には、図3で示したように、GPIOa及びGPIObからサブボード30のIDピンa,bからの信号を受信する。

【0060】

識別部23bは、識別情報取得部23aが取得した識別情報31に基づいて、インタフェース情報テーブル21を参照して、接続されているサブボード30を識別するとともに、サブボード30に対応されたインタフェースを特定する。

【0061】

例えば、識別部23bは、識別情報取得部23aが取得した識別情報31のIDピンa,b(0,1)に基づいて、インタフェース情報テーブル21からサブボードBが接続されていることを識別する。さらに、インタフェース情報テーブル21からサブボードBには、USBが2つまで対応可能なUSBコネクタ130d2と、オーディオコネクタ130d1とが設置されていることを特定することができる。

【0062】

切替設定部23cは、識別部23bにより識別されたサブボード30に対応されたインタフェースに基づいて、切替処理情報テーブル22に応じて、サブボード30に対応されたインタフェースを動作可能状態に制御する制御機能のオン状態/オフ状態を決定する。さらに、切替設定部23cは、決定結果に基づいて、USB制御部20hに、USB制御部20hが4つのうちいずれかのUSBを動作可能状態に制御するための切替要求を通知する。また、切替設定部23cは、決定結果に基づいて、切替部20jにオーディオ制御部20kまたはネットワーク制御部20lの切替要求を通知する。

【0063】

次に、情報処理装置10で行われるサブボード30を識別するための処理手順について図5と共に図7を参照して説明する。

図7は、第2の実施の形態に係る情報処理装置で識別を実行するための処理手順を示すフローチャートである。

【0064】

まず初期設定として、予め、インタフェース情報テーブル21にインタフェース情報と、切替処理情報テーブル22に切替処理情報とをそれぞれ記憶させておく。

マザーボード20の電源を切った状態で、マザーボード20の接続コネクタ20fに、サブボード30の接続コネクタ30cを接続する。

【0065】

[ステップS11]

マザーボード20に電源を投入すると、BIOS23が起動して、最低限動作が必要な主コンポーネント(例えば、CPU20a、RAM20b、チップセット20g等)を初期化する。

【0066】

[ステップS12]

初期化終了後、BIOS23の識別情報取得部23aが、サブボード30の識別情報31としてIDピンa,bからの信号を取得する。

【0067】

[ステップS13]

BIOS23の識別部23bは、識別情報取得部23aが取得した識別情報31に基づき、インタフェース情報テーブル21を参照して、マザーボード20に接続されたサブボード30を識別すると共に、当該サブボード30に対応されたインタフェースを特定する。

【0068】

[ステップS14]

BIOS23の切替設定部23cは、ステップS13の特定結果に基づき、切替処理情報テーブル22を参照して、サブボード30に対応されたインタフェースを動作可能状態に制御する制御機能のオン状態/オフ状態の切替を決定する。切替設定部23cは、決定結果に基づいて、USB制御部20hと切替部20jに切替要求を通知する。

【0069】

[ステップS15]

USB制御部20hは、ステップS14の切替要求に基づいて、サブボード30のUSBコネクタを有効に設定する。また、切替部20jは、ステップS14の切替要求に基づいて、オーディオ制御部20kまたはネットワーク制御部20lのうち少なくとも1つを有効に設定する。

【0070】

上記の設定が終了すると、以後通常の初期化処理が実行され、以後、サブボード30のインタフェースにUSB、LANが接続されると、マザーボード20側で当該インタフェースが認識されて、利用されるようになる。

【0071】

次に、情報処理装置10におけるサブボード30の識別処理について具体的に説明する。

まず、情報処理装置10のマザーボード20にサブボードA(図4(A))を接続する場合について説明する。

【0072】

マザーボード20の電源を切った状態で、マザーボード20の接続コネクタ20fに、サブボードAの接続コネクタ30cを接続した後、マザーボード20に電源を投入すると、BIOS23が起動して、最低限動作が必要な主コンポーネントを初期化する(ステップS11)。

【0073】

BIOS23の識別情報取得部23aが、サブボードAのIDピンa,bを参照し、IDピンa,bから識別情報31の(1,0)を取得する(ステップS12)。

BIOS23の識別部23bは、識別情報取得部23aが取得した識別情報31の(1,0)に基づき、インタフェース情報テーブル21(図6(A))を参照して、マザーボード20に接続されたサブボードAを識別する。さらに、当該サブボードAに対応されたインタフェースが4つのUSB、LANであることを特定する(ステップS13)。

【0074】

BIOS23の切替設定部23cは、切替処理情報テーブル22(図6(B))を参照して、サブボードAのUSBコネクタ30d2のUSB1〜4を動作可能状態に制御するUSB制御部20hと、LANコネクタ30d1を動作可能状態に制御するネットワーク制御部20lとの制御機能をオン状態に切り替えることを決定する。さらに、切替設定部23cは、決定結果に基づいて、USB制御部20hと切替部20jに当該切替要求を通知する(ステップS14)。

【0075】

USB制御部20hは、切替要求に基づいて、USBコネクタ30d2のUSB1〜4を「1」に設定して、USB1〜4を動作可能状態に制御する。また、切替部20jは、切替要求に基づいて、ネットワーク制御部20lをオン状態に切り替えて、ネットワーク制御部20lはLANコネクタ30d1を動作可能状態に制御する。

【0076】

このような制御により、オーディオ制御部20kがオン状態に維持されたままで、サブボードAのLANコネクタ30d1及びUSBコネクタ30d2が通常に利用できるようになる。

【0077】

次に、情報処理装置10のマザーボード20にサブボードB(図4(B))を接続する場合について説明する。

上記と同様に、マザーボード20の電源を切った状態で、マザーボード20の接続コネクタ20fに、サブボードBの接続コネクタ30cを接続した後、マザーボード20に電源を投入する(ステップS11)。

【0078】

BIOS23の識別情報取得部23aが、サブボードBのIDピンa,bを参照し、IDピンa,bから識別情報31の(0,1)を取得する(ステップS12)。

BIOS23の識別部23bは、識別情報取得部23aが取得した識別情報31の(0,1)に基づき、インタフェース情報テーブル21(図6(A))を参照して、マザーボード20に接続されたサブボードBを識別する。さらに、当該サブボードBに対応されたインタフェースが2つのUSB、オーディオであることを特定する(ステップS13)。

【0079】

BIOS23の切替設定部23cは、切替処理情報テーブル22(図6(B))を参照して、サブボードBのUSBコネクタ130d2のUSB1,2を動作可能状態に制御するUSB制御部20hと、オーディオコネクタ130d1を動作可能状態に制御するオーディオ制御部20kとの制御機能をオン状態に切り替えることを決定する。さらに、切替設定部23cは、決定結果に基づいて、USB制御部20hと切替部20jに当該切替要求を通知する(ステップS14)。

【0080】

USB制御部20hは、切替要求に基づいて、USBコネクタ130d2のUSB1,2を「1」に設定して、USB1,2を動作可能状態に制御する。また、切替部20jは、切替要求に基づいて、オーディオ制御部20kをオン状態に切り替えて、オーディオ制御部20kはオーディオコネクタ130d1を動作可能状態に制御する。

【0081】

このような制御により、ネットワーク制御部20lがオフ状態に維持されたままで、サブボードBのオーディオコネクタ130d1及びUSBコネクタ130d2が通常に利用できるようになる。

【0082】

このように、情報処理装置10のマザーボード20では、サブボード30に対応されたインタフェースを動作可能状態に制御する制御機能のみを利用可能状態にした。一方、サブボード30に対応されていないインタフェースを動作可能状態に制御する制御機能は利用不可(オフ)状態が維持される。

【0083】

したがって、マザーボード20において、余計な処理の負担と共に、当該処理に応じた消費電力が削減されるようになる。

また、このような情報処理装置10では、サブボード30に、LANカード等の汎用拡張インタフェースのように、インタフェースに対応した制御装置を搭載させる必要がなく、インタフェースを動作可能状態に制御できる。このため、サブボード30に制御装置の設置等のコストアップを抑制できると共に、サブボード30の小型化に伴って、情報処理装置10を小型化することができる。さらに、情報処理装置10では、マザーボード20により、対応されたインタフェースが動作可能状態に制御される。このため、インタフェースの種類及び数に応じてマザーボード20のBIOSを設定するための作業を省略することができる。また、1つのマザーボード20に対して、必要に応じてサブボード30を交換することで様々なインタフェースに対応することができ、インタフェースのバリエーションを増加させることが可能であって、マザーボード20の共通化を実現させることができる。

【0084】

なお、上記で示した処理機能の一部は、コンピュータによって実現することができる。その場合、情報処理装置が有すべき機能の処理内容を記述したプログラムが提供される。そのプログラムをコンピュータで実行することにより、上記処理機能がコンピュータ上で実現される。処理内容を記述したプログラムは、コンピュータで読み取り可能な記録媒体に記録しておくことができる。コンピュータで読み取り可能な記録媒体としては、磁気記憶装置、光ディスク、光磁気記録媒体、半導体メモリ等がある。磁気記憶装置には、ハードディスク装置(HDD)、フレキシブルディスク(FD)、磁気テープ等がある。光ディスクには、DVD、DVD−RAM、CD−ROM/RW等がある。光磁気記録媒体には、MO(Magneto-Optical disk)等がある。

【0085】

プログラムを流通させる場合には、例えば、そのプログラムが記録されたDVD、CD−ROM等の可搬型記録媒体が販売される。また、プログラムをサーバコンピュータの記憶装置に格納しておき、ネットワークを介して、サーバコンピュータから他のコンピュータにそのプログラムを転送することもできる。

【0086】

プログラムを実行するコンピュータは、例えば、可搬型記録媒体に記録されたプログラムもしくはサーバコンピュータから転送されたプログラムを、自己の記憶装置に格納する。そして、コンピュータは、自己の記憶装置からプログラムを読み取り、プログラムに従った処理を実行する。なお、コンピュータは、可搬型記録媒体から直接プログラムを読み取り、そのプログラムに従った処理を実行することもできる。また、コンピュータは、ネットワークを介して接続されたサーバコンピュータからプログラムが転送されるごとに、逐次、受け取ったプログラムに従った処理を実行することもできる。

【0087】

また、上記の処理機能の少なくとも一部を、DSP(Digital Signal Processor)、ASIC(Application Specific Integrated Circuit)、PLD(Programmable Logic Device)等の電子回路で実現することもできる。

【符号の説明】

【0088】

1,10 情報処理装置

2,20 マザーボード

2a インタフェース情報記憶部

2b,23a 識別情報取得部

2c,23b 識別部

2d,20j 切替部

2e インタフェース制御部

2f,3b,20f,30c 接続コネクタ

3,30,A,B サブボード

3a 識別情報

3c,30d インタフェースコネクタ

20a CPU

20b RAM

20c HDD

20d 入出力インタフェース

20e バス

20g チップセット

20h USB制御部

20i GPIO

20k オーディオ制御部

20l ネットワーク制御部

21 インタフェース情報テーブル

22 切替処理情報テーブル

23 BIOS

23c 切替設定部

30a 識別回路

30b 電子装置インタフェース

30d1 LANコネクタ

30d2,130d2 USBコネクタ

31 識別情報

130d1 オーディオコネクタ

40 モニタ

50 マウス

60 キーボード

a,b IDピン

【特許請求の範囲】

【請求項1】

電子装置が接続される情報処理装置において、

前記電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードと、

前記ボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報を記憶するインタフェース情報記憶部と、

前記ボードが接続されると、前記ボードの前記識別情報を取得する識別情報取得部と、

取得した前記ボードの前記識別情報に基づき、前記インタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別する識別部と、

を有することを特徴とする情報処理装置。

【請求項2】

前記識別情報取得部に対して、前記ボードは前記識別情報に対応する応答信号を出力する識別回路、

を有することを特徴とする請求項1記載の情報処理装置。

【請求項3】

前記ボードに設置された前記インタフェースを動作可能状態に制御するインタフェース制御部と、

前記識別部で識別した前記インタフェースに対応する前記インタフェース制御部を有効状態に切り替える切替部と、

をさらに有することを特徴とする請求項1記載の情報処理装置。

【請求項4】

電子装置が接続される情報処理装置の識別方法において、

前記電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードが接続されると、識別情報取得部が、前記ボードの前記識別情報を取得し、

識別部が前記識別情報取得部が取得した前記ボードの前記識別情報に基づき、前記ボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別する、

ことを特徴とする情報処理装置の識別方法。

【請求項5】

電子装置が接続される情報処理装置の識別プログラムにおいて、

コンピュータに、

前記電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードが接続されると、前記ボードの前記識別情報を取得し、

取得した前記ボードの前記識別情報に基づき、前記ボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別させる、

処理を実行させることを特徴とする情報処理装置の識別プログラム。

【請求項6】

電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報を記憶するインタフェース情報記憶部と、

前記ボードが接続されると、前記ボードの前記識別情報を取得する識別情報取得部と、

取得した前記ボードの前記識別情報に基づき、前記インタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別する識別部と、

を有することを特徴とするマザーボード。

【請求項1】

電子装置が接続される情報処理装置において、

前記電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードと、

前記ボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報を記憶するインタフェース情報記憶部と、

前記ボードが接続されると、前記ボードの前記識別情報を取得する識別情報取得部と、

取得した前記ボードの前記識別情報に基づき、前記インタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別する識別部と、

を有することを特徴とする情報処理装置。

【請求項2】

前記識別情報取得部に対して、前記ボードは前記識別情報に対応する応答信号を出力する識別回路、

を有することを特徴とする請求項1記載の情報処理装置。

【請求項3】

前記ボードに設置された前記インタフェースを動作可能状態に制御するインタフェース制御部と、

前記識別部で識別した前記インタフェースに対応する前記インタフェース制御部を有効状態に切り替える切替部と、

をさらに有することを特徴とする請求項1記載の情報処理装置。

【請求項4】

電子装置が接続される情報処理装置の識別方法において、

前記電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードが接続されると、識別情報取得部が、前記ボードの前記識別情報を取得し、

識別部が前記識別情報取得部が取得した前記ボードの前記識別情報に基づき、前記ボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別する、

ことを特徴とする情報処理装置の識別方法。

【請求項5】

電子装置が接続される情報処理装置の識別プログラムにおいて、

コンピュータに、

前記電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードが接続されると、前記ボードの前記識別情報を取得し、

取得した前記ボードの前記識別情報に基づき、前記ボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別させる、

処理を実行させることを特徴とする情報処理装置の識別プログラム。

【請求項6】

電子装置に対応したインタフェースが設置され、自己を識別する識別情報を備える着脱可能なボードの前記識別情報に対応付けられた、前記ボードに設置された前記インタフェースに関するインタフェース情報を記憶するインタフェース情報記憶部と、

前記ボードが接続されると、前記ボードの前記識別情報を取得する識別情報取得部と、

取得した前記ボードの前記識別情報に基づき、前記インタフェース情報から、接続された前記ボードに設置された前記インタフェースを識別する識別部と、

を有することを特徴とするマザーボード。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−210166(P2011−210166A)

【公開日】平成23年10月20日(2011.10.20)

【国際特許分類】

【出願番号】特願2010−79530(P2010−79530)

【出願日】平成22年3月30日(2010.3.30)

【出願人】(000237639)富士通フロンテック株式会社 (667)

【公開日】平成23年10月20日(2011.10.20)

【国際特許分類】

【出願日】平成22年3月30日(2010.3.30)

【出願人】(000237639)富士通フロンテック株式会社 (667)

[ Back to top ]