情報処理装置、電子回路装置、データ消去方法

【課題】第三者のIC開封によるリバースエンジニアリングに対し高セキュリティを保ちつつ、必要に応じてユーザ自身が十分な解析できる電子回路装置が求められていた。

【解決手段】本発明の電子回路装置は、データを記憶する主記憶手段と、クロック周波数の変化を検出する第1検出手段と、検出された変化を計数する第1計数手段と、外部より設定される所定の値を記憶する第1記憶手段と、第1計数手段で計数された値と第1記憶手段に記憶されている値とに基づいて前記主記憶手段のデータを消去することを指示する消去信号を出力する出力手段と、を備える。本構成によれば、ICパッケージが開封される時に生じる変化をクロック周波数の変化から検出し、また、データ消去に関する基準値をユーザ自身が予め設定できるため、ユーザは使用用途に基づいてデータ消去タイミングの選択することが可能となる。

【解決手段】本発明の電子回路装置は、データを記憶する主記憶手段と、クロック周波数の変化を検出する第1検出手段と、検出された変化を計数する第1計数手段と、外部より設定される所定の値を記憶する第1記憶手段と、第1計数手段で計数された値と第1記憶手段に記憶されている値とに基づいて前記主記憶手段のデータを消去することを指示する消去信号を出力する出力手段と、を備える。本構成によれば、ICパッケージが開封される時に生じる変化をクロック周波数の変化から検出し、また、データ消去に関する基準値をユーザ自身が予め設定できるため、ユーザは使用用途に基づいてデータ消去タイミングの選択することが可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、情報処理装置、当該装置に含まれる電子回路装置及び当該電子回路装置を利用したデータ消去方法に関し、特に高いセキュリティ性を実現するデータ消去方法及び当該方法を実施するために用いられる電子回路装置並びに情報処理装置に関する。

【背景技術】

【0002】

高いセキュリティ性が求められるアプリケーションに関して、その高セキュリティを保つためには、そのアプリケーションを実行する情報処理装置自身(例えば、マイクロコンピュータ)についても、より高いセキュリティ性が求められる。

【0003】

情報処理装置自身が有するセキュリティ機能には、例えば、オンチップデバッグにおいて、セキュリティIDの認証を失敗した時にフラッシュメモリのデータを消去する機能やセキュリティコマンドを設定する機能が挙げられる。

【0004】

しかしながら、第三者がIC開封によるリバースエンジニアリングを行う事により、内蔵フラッシュROMのデータが読み出されてしまうというケースが想定される。このような手法を考慮すると、前述のセキュリティ機能は、十分なセキュリティを確保しているとは言えない。従って、IC開封によるリバースエンジニアリングに対しても、第三者によりフラッシュROMのデータを不正に読み出されて秘密データを悪用されるといった事態を未然に防ぐことができるセキュリティ機能が求められる。

【0005】

そこで、電子データ処理システム用の集積回路チップの保護メモリ内に記憶された秘密データをリバースエンジニアリングにより解析することを防止する手法として、特許文献1に記載の技術が公開されている。

【0006】

特許文献1に記載された集積回路チップは、秘密データを記憶する揮発性メモリと、チップをカプセル封じする材料の不透明層と、カプセル封じ材料によってカプセル封じされ且つ揮発性メモリに結合された保護回路を具備し、当該保護回路は、光にさらされる際に検知可能な変化をする電流特性を持つ光感知素子と、その光感知素子が光にさらされるときに生じる電流の変化を検知するための検知手段と、当該検知手段で電流の変化が検知された場合に揮発性メモリへの電力供給を切断するスイッチ手段と、から構成される。

【0007】

当該構成によれば、カプセル封じ材料がチップから除去された場合、揮発性メモリと電源との結合が解除されて揮発性メモリ内の秘密データが消去される。従って、第三者のIC開封によるリバースエンジニアリングに対しても高いセキュリティ機能を実現することができる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平4−258892号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

製品に不具合が発生した場合には、ユーザは、その不具合の原因を特定するためにICを開封してIC内部の回路の動作を詳しく調査・検証する必要がある。その際には、メモリに格納された情報に関連する調査・検証も行われる。

【0010】

しかしながら、上記の特許文献1に記載の技術を導入していると、ユーザは、メモリの情報が消去されないように、光の照射が全くない環境で、ICの開封作業、及び、不具合の原因を特定するための様々な調査・検証を行わなければならない。

【0011】

すなわち、ユーザが、ユーザ自身の製品を解析する場合にも、解析環境に厳しい条件を課すことになってしまい、解析作業の効率の著しい低下を招くだけでなく、十分な解析すらできないという状況が生じていた。

【課題を解決するための手段】

【0012】

本発明の電子回路装置は、データを記憶する主記憶部と、クロック周波数の変化を検出する第1検出部と、前記検出された変化を計数する第1計数部と、外部より設定される所定の値を記憶する第1記憶部と、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とに基づいて前記主記憶部のデータを消去することを指示する消去信号を出力する出力部と、を具備する。

【0013】

上記構成とすることにより、第三者からのIC開封に対しては高いセキュリティを保ちつつ、ユーザ自身からのIC開封に対しては適切に解析作業を行える環境を提供することができる。

【0014】

また、本発明の情報処理装置は、データを記憶する主記憶部と、演算処理を行う処理部と、第1の周波数を有する第1クロック信号を出力する第1発振部と、第2の周波数を有する第2クロック信号を出力する第2発振部と、前記第1クロック信号及び前記第2クロック信号に基づいて前記第1クロック信号の周波数の変化を検出する検出部と、前記検出された変化を計数する計数部と、外部より設定される所定の値を記憶する記憶部と、前記計数部で計数された値と前記記憶部に記憶されている値とに基づいて消去信号を出力する出力部と、前記消去信号に基づいて前記主記憶部に記憶されているデータを消去する消去部と、を具備する。

【0015】

上記構成とすることにより、第三者からのIC開封に対しては高いセキュリティを保ちつつ、ユーザ自身からのIC開封に対しては適切に解析作業を行える環境を提供することができる。

【0016】

また、本発明のデータ消去方法は、外部より設定される所定の値を記憶部に記憶する記憶ステップと、クロック周波数の変化を検出する検出ステップと、前記検出された変化を計数する計数ステップと、前記計数ステップで計数された値と前記記憶ステップで記憶された値とに基づいて消去信号を出力する出力ステップと、前記消去信号に基づいてデータを消去する消去ステップと、を有する。

【0017】

上記方法によりデータが消去されることで、ユーザ自身からのIC開封に対しては適切に解析作業を行える環境を担保しつつ、第三者からのIC開封に対しては高いセキュリティを保つことが可能となる。

【発明の効果】

【0018】

本発明によれば、第三者のリバースエンジニアリングに対して高いセキュリティ機能を実現しつつ、必要に応じてユーザ自身が適切に解析作業を実施できる装置及び方法を提供することができる。

【図面の簡単な説明】

【0019】

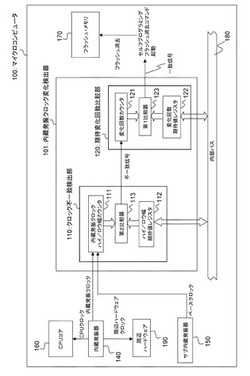

【図1】本発明の実施の形態1に係る情報処理装置の構成例を示すブロック図である。

【図2】本発明の実施の形態1に係る情報処理装置の動作を示すフローチャートである。

【図3】本発明の実施の形態1に係る情報処理装置の動作を示すタイミングチャートである。

【図4】本発明の実施の形態2に係る電子回路装置の構成例を示すブロック図である。

【図5】本発明の実施の形態3に係る電子回路装置の構成例を示すブロック図である。

【図6】本発明の実施の形態3に係る情報処理装置の動作を示すフローチャートである。

【図7】本発明の実施の形態3に係る電子回路装置の別の形態の構成例を示すブロック図である。

【図8】本発明の実施の形態4に係る電子回路装置に含まれる時間計測用タイマの構成例を示すブロック図である。

【発明を実施するための形態】

【0020】

(実施の形態1)

以下、図面を参照して本発明の実施の形態について説明する。

【0021】

図1は、本発明の実施の形態1に係る情報処理装置(マイクロコンピュータ100)のブロック図である。

【0022】

マイクロコンピュータ100は、主に、内蔵発振クロック変化検出器101、内蔵発振器140、サブ内蔵発振器150、CPUコア160、フラッシュメモリ170、内部バス180、及び周辺ハードウェア190から構成される。

【0023】

内蔵発振器140は、基準クロックを生成し、CPUコア160にCPUクロックを、メモリーコントローラ等の周辺ハードウェア190に周辺ハードウェアクロックを、内蔵発振クロック変化検出器101に内蔵発振クロックをそれぞれ供給する第1の発振器である。

【0024】

サブ内蔵発振器150は、内蔵発振クロックとは異なる周波数のクロック信号であるベースクロックを内蔵発振クロック変化検出器101に供給する。

【0025】

CPUコア160は、プログラムに従って演算処理を行う処理部である。

【0026】

フラッシュメモリ170は、マイクロコンピュータ100のメインメモリであり、プログラムやデータを一時記憶する主記憶部である。

【0027】

内部バス180は、マイクロコンピュータ内部の各ブロックを接続する経路である。ユーザは、内部バス180を通じて後述する変化回数期待値レジスタにアクセスし、所定の値を記憶させておくことができる。

【0028】

周辺ハードウェア190は、例えばメモリーコントローラや割り込みコントローラなどであり、内蔵発振器140から出力された周辺ハードウェアクロックに従って動作する。

【0029】

内蔵発振クロック変化検出器101は、さらに、クロック不一致検出部110と、期待変化回数比較部120とから構成される電子回路装置である。

【0030】

クロック不一致検出部110は、IC開封時に生じる内蔵発振クロックの変化を検出する検出部である。期待変化回数比較部120は、クロック不一致検出部110で検出された上記の変化をカウントする変化回数カウンタ121でカウントされた値と変化回数期待値レジスタ122に記憶されている値とに基づいて消去信号を出力する出力部である。以下、各部について詳細に説明する。

【0031】

クロック不一致検出部110は、内蔵発振クロックハイ/ロウ幅カウンタ111と、ハイ/ロウ幅期待値レジスタ112と、第2比較器113と、から構成される。

【0032】

内蔵発振クロックハイ/ロウ幅カウンタ111は、内蔵発振器140から出力される内蔵発振クロックのハイ/ロウレベル期間をカウントする。具体的には、第1の発信器である内蔵発振器140から出力される内蔵発振クロックのハイ/ロウレベル期間を、第2の発振器であるサブ内蔵発振器150から出力されるベースクロックを用いてカウントする。

【0033】

ハイ/ロウ幅期待値レジスタ112は、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされるハイ/ロウレベル期間の期待値を記憶する。

【0034】

第2比較器113は、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされる値と、ハイ/ロウ幅期待値レジスタ112に記憶されている値とを常時比較する。比較の結果、これらの2つの値が不一致となった場合に、第2比較器113は不一致信号を後述する変化回数カウンタ121に出力する。不一致信号は、クロック周波数に変化が生じたことを示す信号である。例えば、ハイ/ロウ幅期待値レジスタ112に期待値として"7"の値を設定している場合であって、内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値が"5"であった場合、両者の値は不一致となるので、クロック周波数が変化したとして不一致信号が出力される。当該不一致信号に基づいて、変化回数カウンタ121がインクリメントされる。なお、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされた値は、第2比較器113における比較処理が行われる毎にクリアされる。

【0035】

ここで、ハイ/ロウ幅期待値レジスタ112は、内部バス180を介してアクセス可能な構成となっており、ユーザは、任意に期待値を設定することができる。なお、マイクロコンピュータ100の動作保証温度範囲内での温度依存による内蔵発振クロック変動を考慮し、設定する期待値に一定のマージンを与えておくことが好ましい。このように設定することで、IC開封によって生じる応力の変化に依存するクロック変動と温度依存によるクロック変動とを区別することができる。例えば、動作保証温度範囲内での温度依存により生じる内蔵発振クロック変動により、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされる値に±1程度の誤差が生じる場合には、ハイ/ロウ幅期待値カウンタに当該誤差を考慮した一定の範囲の値を設定しておくとよい。ハイ/ロウ幅期待値レジスタ112に"6"、"7"、"8"の3つの値を設定しておけば、温度依存による内蔵発振クロック変動が生じても不一致信号は出力されない。

【0036】

期待変化回数比較部120は、変化回数カウンタ121と、変化回数期待値レジスタ122と、第1比較器123と、から構成される。

【0037】

変化回数カウンタ121は、上述した不一致信号を入力し、当該不一致信号に基づいてカウンタの値をインクリメントして記憶する。

【0038】

変化回数期待値レジスタ122は、所定の値を記憶している。また、変化回数期待値レジスタ122は、内部バス18を介してアクセス可能となっており、ユーザは記憶させておく値を任意に設定することができる。変化回数期待値レジスタ122に記憶される所定の値は、第1比較器123で行われる比較処理において比較の基準となる基準値であり、使用目的に応じて外部から設定可能な構成となっている。

【0039】

第1比較器123は、変化回数カウンタ121でカウントされた値と変化回数期待値レジスタ122に記憶されている値とを比較する。第1比較器123は、比較の結果、変化回数カウンタ121にカウントされた値が、変化回数期待値レジスタ122に記憶されている値と一致した場合には、一致信号を生成して出力する。当該一致信号は、フラッシュメモリ170のデータを消去するトリガとなる消去信号である。当該一致信号が出力されることにより、図示せぬ消去部がフラッシュメモリ内のデータを消去する。消去部における消去方法としては、上記一致信号に基づいてフラッシュメモリへの給電を断つスイッチ部を設けることにより消去しても良いし、上記一致信号に基づいてセルフプログラミングフラッシュ消去コマンドを実行する消去コマンド実行部を設けることにより消去してもよい。

【0040】

次に、図1に記載されたマイクロコンピュータ100の動作について説明する。図2は、マイクロコンピュータ100の動作に関するフローチャートである。

【0041】

まず、第2比較器113が、ユーザが任意に設定したハイ/ロウ幅期待値レジスタ112のハイ/ロウ幅期待値と、現在の内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値、すなわち、内蔵発振クロックのハイ/ロウレベル期間をカウントした値と、を比較する(ステップS101)。

【0042】

第2比較器113は、ステップS101における比較の結果2つの値が不一致だった場合は、不一致信号を出力する。変化回数カウンタ121は、当該不一致信号が入力されるとカウンタの値を一回インクリメントしてカウント値を記憶する(ステップS102)。

【0043】

第1比較器123は、ステップS102によってインクリメントされた変化回数カウンタ121のカウント値と、ユーザにより任意に設定された変化回数期待値レジスタ122に格納された値とを比較する(ステップS103)。第1比較器123は、比較の結果、これら2つの値が一致した場合は一致信号を出力する。一方、これら2つの値が一致しなかった場合は、再び上記S101〜S103の処理が繰り返される。

【0044】

上記一致信号に基づいてセルフ消去コマンドが実行され、フラッシュメモリ内のデータが消去される(ステップS104)。

【0045】

次に、クロック不一致検出部110で行われる内蔵発振クロックの変動検出における、内蔵発振クロックのハイ/ロウ幅のカウント方法を図3のタイミングチャートを用いて説明する。

【0046】

CLKは、内蔵発振器140から出力される内蔵発振クロックを示しており、HCLKはそのハイ幅を、LCLKはそのロウ幅をそれぞれ分けて表記している。また、BCLKは、サブ内蔵発振器150から出力されるベースクロックを示している。また、ここでは、図1の内蔵発振クロックハイ/ロウ幅カウンタと不一致信号について、ハイ幅カウンタとロウ幅カウンタ及びハイ幅不一致信号とロウ幅不一致信号というようにハイ・ロウに関して個別に表記している。

【0047】

この例では、CLKのハイ幅及びロウ幅の両方ともBCLKを基準として5カウントされているため、ハイ幅カウンタ及びロウ幅カウンタのカウント値は共に"5"となる。一方、ハイ/ロウ幅期待値レジスタには"7"の値が記憶されているため、第2比較器113に含まれるハイ幅比較器及びロウ幅比較器は、ハイ幅不一致信号とロウ幅不一致信号をそれぞれ生成して変化回数カウンタへ出力する。変化回数期待値レジスタには予め値"M"が記憶されているため、変化回数カウンタの値がMに到達した場合にセルフプログラミング消去コマンド起動トリガとなる一致信号が出力される。

【0048】

なお、クロック不一致検出部110は、内蔵発振クロックのハイ幅とロウ幅の両方を個別にカウントする構成に限るものではない。クロック不一致検出部110は、どちらか片方をカウントして1つの不一致信号を生成しても良いし、ハイ/ロウの組の1周期を単位としてBCLKを用いてカウントして1つの不一致信号を生成する構成であっても良い。

【0049】

なお、内蔵発振クロックとベースクロックとが、加えられる応力や光の照射に対して同様のクロック変動をしてしまうと、内蔵発振クロックのカウントにおいて、常に同じ値をカウントしてしまい、内蔵発振クロックの変動を検出する事ができない。そこで、ベースクロック(BCLK)を出力するサブ内蔵発振器150は、コンデンサ、抵抗等の配置をメインの内蔵発振クロック(CLK)を出力する内蔵発振器140と異なる構成とし、クロックの変化の仕方に相違を持たせる。このように構成することで、ベースクロックもIC開封による応力の変化や光の照射によって変動するが、内蔵発振クロックとは周波数変動特性が異なる為、内蔵発振クロックの変動を検出する事が可能となる。

【0050】

以上説明したように、本実施の形態1に係る情報処理装置は、データを記憶する主記憶部であるフラッシュメモリ、演算処理を行う処理部であるCPUコア、第1の周波数を有する第1クロック信号を出力する第1発振部である内蔵発振器、といった情報処理装置の基本構成に加え、次の構成要素を有している。すなわち、第2の周波数を有する第2クロック信号を出力する第2発振部と、前記第1クロック信号及び前記第2クロック信号に基づいて前記第1クロック信号の周波数の変化を検出する検出部と、前記検出された変化を計数する計数部と、外部より設定される所定の値を記憶する記憶部と、前記計数部で計数された値と前記記憶部に記憶されている値とに基づいて消去信号を出力する出力部と、前記消去信号に基づいて前記主記憶部に記憶されているデータを消去する消去部と、を備えることを特徴としている。

【0051】

また、本実施の形態1に係る情報処理装置に含まれる電子回路装置は、データを記憶する主記憶部と、クロック周波数の変化を検出する第1検出部と、前記検出された変化を計数する第1計数部と、外部より設定される所定の値を記憶する第1記憶部と、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とに基づいて前記主記憶部のデータを消去することを指示する消去信号を出力する出力部と、を備える。

【0052】

このように構成することで、ICパッケージが開封される場合に必然的に生じる応力や外光照射などをクロック周波数の変化で捉え、当該変化量とユーザが予め記憶させた値とが所定の条件を満たした場合に消去信号が出力される。従って、リバースエンジニアリングに対して高いセキュリティを保ちつつ、ユーザ自ら解析を行う場合は、消去信号が出力されないように記憶させる値を設定しておくことができる。

【0053】

例えば、第三者からICを開封された時点で瞬間的に主記憶部に記憶されているデータを消去したい場合は、第1記憶部に記憶させる値を"1"に設定する。このように設定することで、IC開封による応力の変化に起因するクロックの変動が検出された場合、即座に主記憶部に記憶されているデータが消去される。一方、ユーザによる正当な解析作業によりICパッケージを開封する必要がある場合には、開封された瞬間にデータが消去されてしまう事を避けるために、第1記憶部に記憶させる値を非常に大きな値に設定する。このように、ユーザが必要に応じて第1記憶部の値を変更できる構成とすることでユーザの使用用途に応じて、データ消去のタイミングを変更することができる。

【0054】

なお、前記出力部は、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とを比較する第1比較部を備え、前記第1比較部は、比較の結果、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とが一致した場合に消去信号を出力する構成とすることができる。このように構成することで比較的単純な電子回路で発明を実現することができる。

【0055】

また、前記第1計数部は、前記検出部で検出された変化の回数を計数する構成とすることができる。検出されるクロック周波数の変化のうち、その変化の回数を計数する構成とすることで、比較的単純な電子回路で発明を実現することができる。

【0056】

また、前記検出部は、第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数部と、所定の期待値を記憶する第2記憶部と、前記第2計数部で計数された値と前記第2記憶部に記憶されている値とを比較する第2比較部と、を備え、前記第2比較部は、比較の結果、前記第2計数部で計数された値と前記第2記憶部に記憶されている値とが一致しない場合に前記クロック周波数が変化したことを示す信号を前記第1計数部に出力する構成とすることができる。このように周波数の異なる2つのクロック信号を用いることでクロック周波数の変動検出が容易となる。

【0057】

また、前記情報処理装置の前記第1発振部及び前記第2発振部は、光が外部から照射された場合にそれぞれ異なる周波数変動特性を示すことを特徴としても良いし、外部から加えられる応力に対してそれぞれ異なる周波数変動特性を示すことを特徴としても良い。このように第1発振部と第2発振部とが所定の条件下において異なる発振特性を持つことで周波数変動を容易に検出することができる。このような周波数変動特性の差異は、第1発振部と第2発振部における抵抗やキャパシタや光感知素子等の配列や組み合わせに差異を持たせることで実現することができる。

【0058】

また、本実施の形態1に係るデータ消去方法は、外部より設定される所定の値を記憶部に記憶する記憶ステップと、クロック周波数の変化を検出する検出ステップと、前記検出された変化を計数する計数ステップと、前記計数ステップで計数された値と前記記憶ステップで記憶された値とに基づいて消去信号を出力する出力ステップと、前記消去信号に基づいて主記憶部に記憶されているデータを消去する消去ステップと、を有する。このような手順に従ってデータが消去される構成とすることで、使用目的に応じてデータの消去タイミングを変更することができる。

【0059】

なお、上記説明では、変化回数カウンタ121は、クロック周波数の変化回数をカウントする構成を示したがこれに限るものではなく、クロック周波数の変化の量も含めてカウントしても良い。例えば、ハイ/ロウ幅期待値レジスタ112に記録されている値が"9"で、内蔵発振クロックハイ/ロウ幅カウンタ110のカウント値が"5"であった場合、第2比較器113は、これらの値の差異である"4"に対応する情報を不一致信号に含めて変化回数カウンタ121に出力し、変化回数カウンタ121で4回インクリメントされる構成であっても良い。

【0060】

なお、上記説明では変化回数期待値レジスタ122に記憶されている期待値と変化回数カウンタ121のカウント値が同一であった場合に一致信号を送信する場合について説明したが、これに限るものではない。例えば変化回数カウンタ121の値が変化回数期待値レジスタ122に記憶されている期待値を上回った場合に一致信号を出力する構成であっても良い。

【0061】

(実施の形態2)

本実施の形態2に係る発明は、クロック周波数を時系列で比較することでクロック周波数の変化を検出し、第三者のリバースエンジニアリングを防止することを特徴としている。

【0062】

図4は、本実施の形態2に係る電子回路装置である内蔵発振クロック変化検出器201のブロック図である。なお、実施の形態1で説明したブロックと同一のブロックについては一部説明を省略する。

【0063】

本実施の形態2に係るクロック不一致検出部210は、内蔵発振クロックハイ/ロウ幅カウンタ111、タイマ211、ハイ/ロウ幅キャプチャレジスタ212、内蔵発振クロックハイ/ロウ幅現在値レジスタ213、内蔵発振クロックハイ/ロウ幅保持値レジスタ214、第2比較器215、から構成される。

【0064】

タイマ211は、予め設定されている時間経過毎にキャプチャトリガ信号を生成してハイ/ロウ幅キャプチャレジスタ212及び内蔵発振クロックハイ/ロウ幅現在値レジスタ213に出力する。

【0065】

ハイ/ロウ幅キャプチャレジスタ212は、タイマから入力したキャプチャトリガ信号をトリガとして内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値をキャプチャし、キャプチャしたカウント値を内蔵発振クロックハイ/ロウ幅現在値レジスタ213へ出力する。

【0066】

内蔵発振クロックハイ/ロウ幅現在値レジスタ213は、ハイ/ロウ幅キャプチャレジスタから出力されたカウント値を記憶する。また、タイマ211から入力したキャプチャトリガ信号をトリガとして、現在記憶しているカウント値を内蔵発振クロックハイ/ロウ幅保持値レジスタ214に出力し、ハイ/ロウ幅キャプチャレジスタ212から新たに出力されるカウント値を記憶する。

【0067】

内蔵発振クロックハイ/ロウ幅保持値レジスタ214は、内蔵発振クロックハイ/ロウ幅現在値レジスタ213から出力されたカウント値を記憶する。

【0068】

第2比較器215は、内蔵発振クロックハイ/ロウ幅保持値レジスタ214と内蔵発振クロックハイ/ロウ幅現在値レジスタ213にそれぞれ記憶されている値を比較する。比較タイミングは、例えば、タイマ211で計測される所定の時間毎に比較を行う。当該比較の結果、これらの2つの値が異なる場合は、不一致信号を生成し、変化回数カウンタ121へ出力する。その後の動作は実施の形態1と同様であるため説明を省略する。

【0069】

以上の構成によれば、タイマに設定された所定の時間分異なる時刻におけるカウント値を比較できるため、時系列で比較した結果異なるカウント値が生じた場合に不一致信号を生成し、変化回数カウンタ122の値をインクリメントしていく。そして変化回数カウンタ122の値と変化回数期待値レジスタ122に記憶されている値とに基づいて消去信号が出力され、フラッシュメモリのデータを消去することができる。

【0070】

すなわち、本実施の形態2に係る電子回路装置は、クロック周波数の変化を検出する検出部と、前記検出された変化を計数する第1計数部と、外部より設定される所定の値を記憶する第1記憶部と、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とに基づいて消去信号を出力する出力手段と、を備え、前記検出手段は、第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数部と、所定の時間を計測する時間計測部と、前記第2計数部で計数された値を記憶する第2記憶部と、前記第2記憶部で記憶された値と前記時間計測部で計測された所定の時間経過後に前記第2計数部で計数された値とを比較する第2比較部と、から構成され、前記第2比較部は、比較の結果、前記第2記憶部で記憶された値と前記時間計測部で計測された所定の時間経過後に前記第2計数部で計数された値とが一致しない場合に前記クロック周波数が変化したことを示す信号を前記第1計数部に出力することを特徴とする。

【0071】

また、本実施の形態2に係るデータ消去方法は、外部より設定される所定の値を記憶部に記憶する記憶ステップと、クロック信号のハイ幅又はロウ幅を計数する第1計数ステップと、所定の時間の計測を開始する時間計測ステップと、前記時間計測ステップで計測された所定の時間後にクロック信号のハイ幅又はロウ幅を計数する第2計数ステップと、前記第1計数ステップ及び前記第2計数ステップで計数された値を比較する比較ステップと、前記前記第1計数ステップで計数された値と前記第2ステップで計数された値が同一でない回数を計数する第3計数ステップと、前記記憶ステップで記憶した値と前記第3計数ステップで計数された値とに基づいて消去信号を出力する出力ステップと、前記消去信号に基づいてデータを消去する消去ステップと、を有する。

【0072】

IC開封によるリバースエンジニアリングを行うと外光が電子回路装置に照射されるため内蔵発振クロックに変化を生じる。従って、開封前と開封後で内蔵発振クロックハイ/ロウ幅カウンタでカウントされる値が変化する。本実施の形態2の電子回路装置は、異なる時刻で得られたカウント値を比較することによりクロック変化を検出することができるため、応力を装置に与えずにICを開封することができたとしても開封前後で装置に照射される光の変化量に基づいてICが開封されたことを検出し、適切にデータを消去することができる。なお、ユーザ自らが解析のために開封する場合には、変化回数期待値レジスタに大きな値を設定しておけば、ICを開封しても第1比較器123から直ちに消去信号が出力されることがないため、適切に解析作業を行うことができる。

【0073】

なお、第2比較器215は、実施の形態1の場合と同様、動作保証温度範囲内での温度依存を考慮し、内蔵発振クロックハイ/ロウ幅保持値レジスタ214と内蔵発振クロックハイ/ロウ幅現在値レジスタ215にそれぞれ記憶されている値が、所定の誤差以上の差異がある場合に不一致信号を生成するよう構成しても良い。

【0074】

(実施の形態3)

本実施の形態3に係る電子回路装置は、実施の形態1で説明した応力による内蔵発振クロックの変化を検出する第1のクロック不一致検出部と、実施の形態2で説明した内蔵発振クロックの時系列変化を検出する第2のクロック不一致検出部を組み合わせた構成とすることを特徴とする。以下図面を用いて説明する。

【0075】

図5は、本実施の形態3に係る内蔵発振クロック変化検出器301のブロック図である。なお、実施の形態1及び2で説明したブロックと同一のブロックについては一部説明を省略する。

【0076】

本実施の形態3の内蔵発振クロック変化検出器301は、大きく分けて、第1クロック不一致検出部310と、期待変化回数比較部320と、第2クロック不一致検出部330と、から構成される。

【0077】

第1クロック不一致検出部310は、ICが開封された時の応力の変化により生じる内蔵発振クロックの最初の変動を検出する第1の検出部である。第2クロック不一致検出部330は、上記最初の変動が検出された場合、その最初の変動以降にIC開封後の光の照射により発生する内蔵発振クロックの変化を時系列的に検出する第2の検出部である。期待変化回数比較部320は、第1クロック不一致検出部310及び第2クロック不一致検出部330により検出された変動をカウントする。そして、当該カウントした値が予め設定された値と一致した場合に消去信号を出力する出力部である。以下、各ブロックについて詳細に説明する。

【0078】

クロック不一致検出部310は、内蔵発振クロックハイ/ロウ幅カウンタ111と、ハイ/ロウ幅期待値レジスタ112と、第2比較器113と、ハイ/ロウ幅キャプチャレジスタ312と、から構成される。

【0079】

内蔵発振クロックハイ/ロウ幅カウンタ111は、内蔵発振器から出力される内蔵発振クロックのハイ/ロウレベル期間を、サブ内蔵発振器から出力されるベースクロックを用いてカウントする。

【0080】

ハイ/ロウ幅期待値レジスタ112は、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされるハイ/ロウレベル期間の期待値を記憶する。内蔵発振クロックハイ/ロウ幅期待値レジスタ112は、外部より内部バス180を介してアクセス可能な構成となっており、ユーザは、任意に期待値を設定することができる。

【0081】

第2比較器113は、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされる値と、ハイ/ロウ幅期待値レジスタ112に記憶されている値とを常時比較する。比較の結果、これらの2つの値が不一致となった場合に、第2比較器113は第1の不一致信号を後述するハイ/ロウ幅キャプチャレジスタ312、タイマ331及び変化回数カウンタ321に出力する。

【0082】

ハイ/ロウ幅キャプチャレジスタ312は、第2比較器113から出力される第1不一致信号又は後述のタイマ331から出力されるキャプチャトリガ信号をトリガとして内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値をキャプチャする。第1不一致信号に基づいてキャプチャされたカウント値は、後述の内蔵発振クロックハイ/ロウ幅保持値レジスタ334へ、キャプチャトリガ信号に基づいてキャプチャされた値は、後述の内蔵発振クロックハイ/ロウ幅現在値レジスタ333へそれぞれ出力される。

【0083】

第2クロック不一致検出部330は、タイマ331と、内蔵発振クロックハイ/ロウ幅現在値レジスタ333と、内蔵発振クロックハイ/ロウ幅保持値レジスタ334と、第3比較器335と、から構成される。

【0084】

タイマ331は、第2比較器113から出力された第1不一致信号をトリガとして時間計測を開始し、予め設定されている時間経過後にキャプチャトリガ信号を生成してハイ/ロウ幅キャプチャレジスタ312に出力する。

【0085】

内蔵発振クロックハイ/ロウ幅保持値レジスタ334は、ハイ/ロウ幅キャプチャレジスタ312が第1不一致信号をトリガとしてキャプチャした値を入力して記憶する。すなわち、ハイ/ロウ幅キャプチャレジスタ312は、第1不一致信号をトリガとして内蔵発振クロックハイ/ロウ幅カウンタ111からカウント値を取り込み、内蔵発振クロックハイ/ロウ幅保持値レジスタ334へ取り込んだカウント値を出力する。

【0086】

内蔵発振クロックハイ/ロウ幅現在値レジスタ333は、ハイ/ロウ幅キャプチャレジスタ312がキャプチャトリガ信号をトリガとしてキャプチャした値を入力して記憶する。すなわち、ハイ/ロウ幅キャプチャレジスタ312は、キャプチャトリガ信号をトリガとして内蔵発振クロックハイ/ロウ幅カウンタ111からカウント値を取り込み、内蔵発振クロックハイ/ロウ幅現在値レジスタ333へ取り込んだカウント値を出力する。

【0087】

第3比較器335は、内蔵発振クロックハイ/ロウ幅保持値レジスタ334に記憶された値と、内蔵発振クロックハイ/ロウ幅現在値レジスタ333に記憶された値とを比較する。比較の結果、これらの2つの値が不一致となった場合に、第3比較器335は第2の不一致信号を出力する。第3比較器335より出力された第2不一致信号は、変化回数カウンタ321に入力される。

【0088】

期待変化回数比較部320は、変化回数カウンタ321と、変化回数期待値レジスタ122と、第1比較器123と、から構成される。

【0089】

変化回数カウンタ321は、上述した第1不一致信号及び第2不一致信号を入力し、これらの信号が入力される度にカウンタの値をインクリメントして記憶する。

【0090】

変化回数期待値レジスタ122は、外部より設定される所定の値を記憶する。変化回数期待値レジスタ122は、内部バス180を介してアクセス可能となっており、ユーザは記憶させておく値を任意に設定することができる。

【0091】

第1比較器123は、変化回数期待値レジスタ122に記憶されている値と変化回数カウンタ321に記憶されている値を比較する。第1比較器123は、比較の結果、変化回数カウンタ123に記憶されている値が変化回数期待値レジスタ122に記憶されている値と一致した場合は一致信号を生成して出力する。

【0092】

次に、本実施の形態に関する内蔵発振クロック変化検出器301の動作を図6のフローチャートを用いて説明する。なお、ステップS101〜S103は、図3に示すフローチャートのステップステップS101〜S103と同一であるため説明を省略する。

【0093】

S103において、変化回数カウンタ321に記憶されている値と変化回数期待値レジスタ122に記憶されている値とが異なる場合、ハイ/ロウ幅保持値レジスタ334は、ハイ/ロウ幅キャプチャレジスタ312がキャプチャした内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値を格納する(ステップS104)。

【0094】

次に、ハイ/ロウ幅現在値レジスタ333は、タイマ331によって作り出される所定の時間経過後にハイ/ロウ幅キャプチャレジスタ312がキャプチャした内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値を格納する(ステップS105)。

【0095】

次に、第3比較器335は、ハイ/ロウ幅保持値レジスタ334に格納されている過去のカウント値とハイ/ロウ幅現在値レジスタ333に格納されている現在のカウント値とを比較する(ステップS106)。

【0096】

上記比較の結果、上記2つのカウント値が一致する場合は、ステップS101の前段に戻って待機する。一方、比較の結果、上記2つのカウント値が一致しない場合は、第3比較器は、不一致信号を生成して変化回数カウンタ321に出力し、変化回数カウンタ321の値が一つインクリメントされる(ステップS107)。

【0097】

次に、第1比較器123は、変化回数カウンタ321の値と変化回数期待値レジスタ122の値を比較する。これらの値が同一であった場合は一致信号を生成して出力し、同一でない場合はステップS104の前段に戻る(ステップS108)。

【0098】

上記一致信号がトリガとなってセルフプログラミング消去コマンドを起動され、内蔵フラッシュROMのデータが一斉に消去される(ステップS109)。

【0099】

以上の構成によれば、応力が加えられた場合に生じるクロック変動と時系列で現れるクロック変動の両方を用いてフラッシュメモリ内のデータを消去するかどうかを判断することができる。

【0100】

なお、上記説明では、第1クロック不一致検出部と第2クロック不一致検出部が直列的に配置される構成を示したがこれに限るものではなく、第1・第2クロック不一致検出部をパラレルに配置する構成であっても良い。図7は、別の変化形態の内蔵発振クロック変化検出器401のブロック構成を示している。

【0101】

内蔵発振クロック変化検出器401は、第1クロック不一致検出部410と第2クロック検出部430の2つの検出手段及び第1期待変化回数比較部420と第2期待変化回数比較部440の2つの比較手段を備える。内部の各ブロックの機能は上述しているため一部説明を省略する。

【0102】

第1期待変化回数比較部420は、第1クロック不一致検出部410より出力される第1不一致信号を入力し、変化回数期待値レジスタ422の値と変化回数カウンタ421の値が一致した場合に第1一致信号を出力する。また、第2期待変化回数比較部440も、第2クロック不一致検出部430より出力される第2不一致信号を入力し、変化回数期待値レジスタ442の値と変化回数カウンタ441の値が一致した場合に第2一致信号を出力する。

【0103】

消去コマンド実行部450は、第1一致信号と第2一致信号を入力し、この2つの一致信号が入力された場合に消去コマンドを実行してフラッシュメモリのデータを消去する。なお、2つの一致信号の入力タイミングは同一である必要はない。

【0104】

以上説明したように、本実施の形態3に係る電子回路装置は、クロック周波数の変化を検出する第1検出部と、所定の時間を計測する時間計測部と、前記時間計測部で計測された所定の時間分異なる時刻における前記クロック周波数の変化を検出する第2検出部と、前記第1検出部及び前記第2検出部で検出された前記クロック周波数の変化を計数する第1計数部と、外部より設定される所定の値を記憶する第1記憶部と、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とに基づいて消去信号を出力する出力部と、を具備する。

【0105】

また、前記第1検出部は、第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数部と、所定の期待値を記憶する第2記憶部と、前記第2計数部で計数された値と前記第2記憶部に記憶されている値とを比較する第2比較部と、を備え、前記第2比較部は、比較の結果、前記第2計数部で計数された値と前記第2記憶部に記憶されている値とが一致しない場合に前記クロック周波数が変化したことを示す第1不一致信号を前記第1計数部に出力する構成とすることができる。

【0106】

また、前記第2検出部は、前記第2計数部で計数された値を記憶する第3記憶部と、前記第3記憶部で記憶された値と前記時間計測部で計測された所定の時間経過後に前記第2計数部で計数された値とを比較する第3比較部と、を備え、前記第3比較部は、比較の結果、前記第3記憶部で記憶された値と前記時間計測部で計測された所定の時間経過後に前記第2計数部で計数された値とが一致しない場合に前記クロック周波数が変化したことを示す第2不一致信号を前記第1計数部に出力する構成とすることができる。

【0107】

また、前記時間計測部は、前記第1不一致信号を入力することにより前記所定の時間の計測を開始する構成とすることができる。

【0108】

また、所定の値を記憶する第4記憶部を更に備え、前記第1計数部は、前記第1検出部で検出された変化を計数する第1変化計数部と、前記第2検出部で検出された変化を計数する第2変化計数部と、から構成され、前記出力部は、前記第1変化計数部で計数された値と前記第1記憶部に記憶されている値とに基づいて第1の消去信号を出力する第1出力部と、前記第2変化計数部で計数された値と前記第4記憶部に記憶されている値とに基づいて第2の消去信号を出力する第2出力部と、を備える構成とすることができる。

【0109】

上記第1消去信号及び第2消去信号が出力された場合、つまり、2つの検出部でともにクロック周波数の変化が検出された場合に、別途設けられた消去部が、主記憶部に格納されているデータを消去するよう構成しても良い。

【0110】

(実施の形態4)

本実施の形態では、実施の形態3に係る電子回路装置が具備するタイマの計測時間を変更できる構成としたことを特徴とする。

【0111】

図8は、本実施の形態4に係る内蔵発振クロック変化検出器に含まれるタイマ530のブロック図である。

【0112】

タイマ530は、所定の時間を計測する時間計測部であり、図4のタイマ211や図7のタイマ431に対応する。タイマ530は、コンペアレジスタ531と、セレクタ532と、AND回路533と、周波数変化回数タイマカウンタ534と、比較器535と、から構成される。

【0113】

コンペアレジスタ531は、時間計測の基準となる値が記憶されている。

【0114】

セレクタ532は、分周されて複数の周波数をもつベースクロック信号の中から1つの信号を選び出す。ユーザはセレクタ532にアクセス可能であり、どの周波数をもつベースクロック信号を選び出すかを設定できる構成となっている。

【0115】

AND回路533は、タイマ530より出力された不一致信号と、前記セレクタ432から出力された信号とを入力して論理積をとって信号を出力する。

【0116】

周波数変化回数タイマカウンタ534は、AND回路533から出力された信号の周波数変化をカウントする。

【0117】

比較器535は、周波数変化回数タイマカウンタ534でカウントされたカウント値とコンペアレジスタ531に記憶されている基準値とを比較する。比較の結果、上記カウント値と基準値とが一致した場合にキャプチャトリガ信号が出力される。

【0118】

上記構成によれば、ユーザからの設定によりセレクタ536で異なる周波数をもつクロック信号から1つのクロック信号を選び出すことができ、不一致信号との論理積をとって出力信号をカウントできるので、ユーザがタイマ530で計測する時間を設定することができる。

【0119】

なお、タイマで計測する時間の設定方法としては、上記方法に限定されるものではなく、例えばコンペアレジスタにユーザが内部バスを通じてアクセス可能な構成とすることもできる。すなわち、セレクタ536を取り除き、所定の周波数をもつクロック信号と不一致信号との論理積出力を周波数変化回数タイマカウンタがカウントし、コンペアレジスタにユーザが設定した基準値と周波数変化回数タイマカウンタでカウントされたカウント値とを比較するよう構成しても良い。

【0120】

以上、各実施の形態で説明したように、本発明によれば、ユーザがフラッシュメモリの消去タイミングを任意に選択可能となる為、ユーザの使用用途に合わせてセキュリティレベルの設定が可能となる。従って、第三者のリバースエンジニアリングに対して高いセキュリティを保ちつつ、ユーザ自身による十分な解析も可能となる。

【0121】

なお、変化回数レジスタ及びハイ/ロウ幅期待値レジスタは、別途設けられた設定部により格納する値を設定できる。すなわち、設定部は、ユーザからの指示に基づいて変化回数レジスタ又はハイ/ロウ幅期待値レジスタに記憶させる所定の値を設定するよう構成しても良い。

【0122】

また、変化回数レジスタやハイ/ロウ幅期待値レジスタにアクセスをするためには所定の認証や手順を踏んだ場合にアクセスできる構成とすることもできる。この場合、新たにアクセス管理部を別途備え、当該アクセス管理部が、所定の認証処理や設定手順に基づいた上記レジスタへのアクセスが行われたかを判断する判断処理を行う構成であっても良い。当該アクセス管理部で、適切なユーザからのレジスタアクセス要求であることを確認した後に、ユーザが変化回数レジスタ又はハイ/ロウ幅期待値レジスタにアクセスし、これらのレジスタに格納されている基準値を変更できる構成であっても良い。

【0123】

なお、上記説明では消去信号に基づいて主記憶部であるフラッシュメモリのデータを消去する構成について示したがこれに限定するものではなく、別の記憶手段に記憶されている秘密データを消去する構成であっても良い。

【0124】

その他、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0125】

100:マイクロコンピュータ 101:内蔵発振クロック変化検出器

110:クロック不一致検出部 111:内蔵発振クロックハイ/ロウ幅カウンタ

112:ハイ/ロウ幅期待値レジスタ 113:第2比較器

120:期待変化回数比較部 121:変化回数カウンタ

122:変化回数期待値レジスタ 123:第1比較器

140:内蔵発信器 150:サブ内蔵発信器

160:CPUコア 170:フラッシュメモリ

180:内部バス 190:周辺ハードウェア

201:内蔵発振クロック変化検出器 210:クロック不一致検出部

211:タイマ 212:ハイ/ロウ幅キャプチャレジスタ

213:内部発振クロックハイ/ロウ幅現在値レジスタ

214:内部発振クロックハイ/ロウ幅保持値レジスタ

215:第2比較器 301:内部発振クロック変化検出器

310:第1クロック不一致検出部 312:ハイ/ロウ幅キャプチャレジスタ

320:期待変化回数比較部 321:変化回数カウンタ

330:第2クロック不一致検出部 331:タイマ

333:内部発振クロックハイ/ロウ幅現在値レジスタ

334:内部発振クロックハイ/ロウ幅保持値レジスタ

335:第3比較器 401:内部発振クロック変化検出器

410:第1クロック不一致検出部 420:第1期待変化回数比較部

421:変化回数カウンタ 422:変化回数期待値レジスタ

423:第1比較器 430:第2クロック不一致検出部

431:タイマ 440:第2期待変化回数比較部

441:変化回数カウンタ 442:変化回数期待値レジスタ

443:第1比較器 450:消去コマンド生成部

501:内部発振クロック変化検出器 530:タイマ

531:コンペアレジスタ 532:セレクタ

533:AND回路 534:周波数変化回数タイマカウンタ

535:比較器

【技術分野】

【0001】

本発明は、情報処理装置、当該装置に含まれる電子回路装置及び当該電子回路装置を利用したデータ消去方法に関し、特に高いセキュリティ性を実現するデータ消去方法及び当該方法を実施するために用いられる電子回路装置並びに情報処理装置に関する。

【背景技術】

【0002】

高いセキュリティ性が求められるアプリケーションに関して、その高セキュリティを保つためには、そのアプリケーションを実行する情報処理装置自身(例えば、マイクロコンピュータ)についても、より高いセキュリティ性が求められる。

【0003】

情報処理装置自身が有するセキュリティ機能には、例えば、オンチップデバッグにおいて、セキュリティIDの認証を失敗した時にフラッシュメモリのデータを消去する機能やセキュリティコマンドを設定する機能が挙げられる。

【0004】

しかしながら、第三者がIC開封によるリバースエンジニアリングを行う事により、内蔵フラッシュROMのデータが読み出されてしまうというケースが想定される。このような手法を考慮すると、前述のセキュリティ機能は、十分なセキュリティを確保しているとは言えない。従って、IC開封によるリバースエンジニアリングに対しても、第三者によりフラッシュROMのデータを不正に読み出されて秘密データを悪用されるといった事態を未然に防ぐことができるセキュリティ機能が求められる。

【0005】

そこで、電子データ処理システム用の集積回路チップの保護メモリ内に記憶された秘密データをリバースエンジニアリングにより解析することを防止する手法として、特許文献1に記載の技術が公開されている。

【0006】

特許文献1に記載された集積回路チップは、秘密データを記憶する揮発性メモリと、チップをカプセル封じする材料の不透明層と、カプセル封じ材料によってカプセル封じされ且つ揮発性メモリに結合された保護回路を具備し、当該保護回路は、光にさらされる際に検知可能な変化をする電流特性を持つ光感知素子と、その光感知素子が光にさらされるときに生じる電流の変化を検知するための検知手段と、当該検知手段で電流の変化が検知された場合に揮発性メモリへの電力供給を切断するスイッチ手段と、から構成される。

【0007】

当該構成によれば、カプセル封じ材料がチップから除去された場合、揮発性メモリと電源との結合が解除されて揮発性メモリ内の秘密データが消去される。従って、第三者のIC開封によるリバースエンジニアリングに対しても高いセキュリティ機能を実現することができる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平4−258892号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

製品に不具合が発生した場合には、ユーザは、その不具合の原因を特定するためにICを開封してIC内部の回路の動作を詳しく調査・検証する必要がある。その際には、メモリに格納された情報に関連する調査・検証も行われる。

【0010】

しかしながら、上記の特許文献1に記載の技術を導入していると、ユーザは、メモリの情報が消去されないように、光の照射が全くない環境で、ICの開封作業、及び、不具合の原因を特定するための様々な調査・検証を行わなければならない。

【0011】

すなわち、ユーザが、ユーザ自身の製品を解析する場合にも、解析環境に厳しい条件を課すことになってしまい、解析作業の効率の著しい低下を招くだけでなく、十分な解析すらできないという状況が生じていた。

【課題を解決するための手段】

【0012】

本発明の電子回路装置は、データを記憶する主記憶部と、クロック周波数の変化を検出する第1検出部と、前記検出された変化を計数する第1計数部と、外部より設定される所定の値を記憶する第1記憶部と、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とに基づいて前記主記憶部のデータを消去することを指示する消去信号を出力する出力部と、を具備する。

【0013】

上記構成とすることにより、第三者からのIC開封に対しては高いセキュリティを保ちつつ、ユーザ自身からのIC開封に対しては適切に解析作業を行える環境を提供することができる。

【0014】

また、本発明の情報処理装置は、データを記憶する主記憶部と、演算処理を行う処理部と、第1の周波数を有する第1クロック信号を出力する第1発振部と、第2の周波数を有する第2クロック信号を出力する第2発振部と、前記第1クロック信号及び前記第2クロック信号に基づいて前記第1クロック信号の周波数の変化を検出する検出部と、前記検出された変化を計数する計数部と、外部より設定される所定の値を記憶する記憶部と、前記計数部で計数された値と前記記憶部に記憶されている値とに基づいて消去信号を出力する出力部と、前記消去信号に基づいて前記主記憶部に記憶されているデータを消去する消去部と、を具備する。

【0015】

上記構成とすることにより、第三者からのIC開封に対しては高いセキュリティを保ちつつ、ユーザ自身からのIC開封に対しては適切に解析作業を行える環境を提供することができる。

【0016】

また、本発明のデータ消去方法は、外部より設定される所定の値を記憶部に記憶する記憶ステップと、クロック周波数の変化を検出する検出ステップと、前記検出された変化を計数する計数ステップと、前記計数ステップで計数された値と前記記憶ステップで記憶された値とに基づいて消去信号を出力する出力ステップと、前記消去信号に基づいてデータを消去する消去ステップと、を有する。

【0017】

上記方法によりデータが消去されることで、ユーザ自身からのIC開封に対しては適切に解析作業を行える環境を担保しつつ、第三者からのIC開封に対しては高いセキュリティを保つことが可能となる。

【発明の効果】

【0018】

本発明によれば、第三者のリバースエンジニアリングに対して高いセキュリティ機能を実現しつつ、必要に応じてユーザ自身が適切に解析作業を実施できる装置及び方法を提供することができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態1に係る情報処理装置の構成例を示すブロック図である。

【図2】本発明の実施の形態1に係る情報処理装置の動作を示すフローチャートである。

【図3】本発明の実施の形態1に係る情報処理装置の動作を示すタイミングチャートである。

【図4】本発明の実施の形態2に係る電子回路装置の構成例を示すブロック図である。

【図5】本発明の実施の形態3に係る電子回路装置の構成例を示すブロック図である。

【図6】本発明の実施の形態3に係る情報処理装置の動作を示すフローチャートである。

【図7】本発明の実施の形態3に係る電子回路装置の別の形態の構成例を示すブロック図である。

【図8】本発明の実施の形態4に係る電子回路装置に含まれる時間計測用タイマの構成例を示すブロック図である。

【発明を実施するための形態】

【0020】

(実施の形態1)

以下、図面を参照して本発明の実施の形態について説明する。

【0021】

図1は、本発明の実施の形態1に係る情報処理装置(マイクロコンピュータ100)のブロック図である。

【0022】

マイクロコンピュータ100は、主に、内蔵発振クロック変化検出器101、内蔵発振器140、サブ内蔵発振器150、CPUコア160、フラッシュメモリ170、内部バス180、及び周辺ハードウェア190から構成される。

【0023】

内蔵発振器140は、基準クロックを生成し、CPUコア160にCPUクロックを、メモリーコントローラ等の周辺ハードウェア190に周辺ハードウェアクロックを、内蔵発振クロック変化検出器101に内蔵発振クロックをそれぞれ供給する第1の発振器である。

【0024】

サブ内蔵発振器150は、内蔵発振クロックとは異なる周波数のクロック信号であるベースクロックを内蔵発振クロック変化検出器101に供給する。

【0025】

CPUコア160は、プログラムに従って演算処理を行う処理部である。

【0026】

フラッシュメモリ170は、マイクロコンピュータ100のメインメモリであり、プログラムやデータを一時記憶する主記憶部である。

【0027】

内部バス180は、マイクロコンピュータ内部の各ブロックを接続する経路である。ユーザは、内部バス180を通じて後述する変化回数期待値レジスタにアクセスし、所定の値を記憶させておくことができる。

【0028】

周辺ハードウェア190は、例えばメモリーコントローラや割り込みコントローラなどであり、内蔵発振器140から出力された周辺ハードウェアクロックに従って動作する。

【0029】

内蔵発振クロック変化検出器101は、さらに、クロック不一致検出部110と、期待変化回数比較部120とから構成される電子回路装置である。

【0030】

クロック不一致検出部110は、IC開封時に生じる内蔵発振クロックの変化を検出する検出部である。期待変化回数比較部120は、クロック不一致検出部110で検出された上記の変化をカウントする変化回数カウンタ121でカウントされた値と変化回数期待値レジスタ122に記憶されている値とに基づいて消去信号を出力する出力部である。以下、各部について詳細に説明する。

【0031】

クロック不一致検出部110は、内蔵発振クロックハイ/ロウ幅カウンタ111と、ハイ/ロウ幅期待値レジスタ112と、第2比較器113と、から構成される。

【0032】

内蔵発振クロックハイ/ロウ幅カウンタ111は、内蔵発振器140から出力される内蔵発振クロックのハイ/ロウレベル期間をカウントする。具体的には、第1の発信器である内蔵発振器140から出力される内蔵発振クロックのハイ/ロウレベル期間を、第2の発振器であるサブ内蔵発振器150から出力されるベースクロックを用いてカウントする。

【0033】

ハイ/ロウ幅期待値レジスタ112は、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされるハイ/ロウレベル期間の期待値を記憶する。

【0034】

第2比較器113は、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされる値と、ハイ/ロウ幅期待値レジスタ112に記憶されている値とを常時比較する。比較の結果、これらの2つの値が不一致となった場合に、第2比較器113は不一致信号を後述する変化回数カウンタ121に出力する。不一致信号は、クロック周波数に変化が生じたことを示す信号である。例えば、ハイ/ロウ幅期待値レジスタ112に期待値として"7"の値を設定している場合であって、内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値が"5"であった場合、両者の値は不一致となるので、クロック周波数が変化したとして不一致信号が出力される。当該不一致信号に基づいて、変化回数カウンタ121がインクリメントされる。なお、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされた値は、第2比較器113における比較処理が行われる毎にクリアされる。

【0035】

ここで、ハイ/ロウ幅期待値レジスタ112は、内部バス180を介してアクセス可能な構成となっており、ユーザは、任意に期待値を設定することができる。なお、マイクロコンピュータ100の動作保証温度範囲内での温度依存による内蔵発振クロック変動を考慮し、設定する期待値に一定のマージンを与えておくことが好ましい。このように設定することで、IC開封によって生じる応力の変化に依存するクロック変動と温度依存によるクロック変動とを区別することができる。例えば、動作保証温度範囲内での温度依存により生じる内蔵発振クロック変動により、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされる値に±1程度の誤差が生じる場合には、ハイ/ロウ幅期待値カウンタに当該誤差を考慮した一定の範囲の値を設定しておくとよい。ハイ/ロウ幅期待値レジスタ112に"6"、"7"、"8"の3つの値を設定しておけば、温度依存による内蔵発振クロック変動が生じても不一致信号は出力されない。

【0036】

期待変化回数比較部120は、変化回数カウンタ121と、変化回数期待値レジスタ122と、第1比較器123と、から構成される。

【0037】

変化回数カウンタ121は、上述した不一致信号を入力し、当該不一致信号に基づいてカウンタの値をインクリメントして記憶する。

【0038】

変化回数期待値レジスタ122は、所定の値を記憶している。また、変化回数期待値レジスタ122は、内部バス18を介してアクセス可能となっており、ユーザは記憶させておく値を任意に設定することができる。変化回数期待値レジスタ122に記憶される所定の値は、第1比較器123で行われる比較処理において比較の基準となる基準値であり、使用目的に応じて外部から設定可能な構成となっている。

【0039】

第1比較器123は、変化回数カウンタ121でカウントされた値と変化回数期待値レジスタ122に記憶されている値とを比較する。第1比較器123は、比較の結果、変化回数カウンタ121にカウントされた値が、変化回数期待値レジスタ122に記憶されている値と一致した場合には、一致信号を生成して出力する。当該一致信号は、フラッシュメモリ170のデータを消去するトリガとなる消去信号である。当該一致信号が出力されることにより、図示せぬ消去部がフラッシュメモリ内のデータを消去する。消去部における消去方法としては、上記一致信号に基づいてフラッシュメモリへの給電を断つスイッチ部を設けることにより消去しても良いし、上記一致信号に基づいてセルフプログラミングフラッシュ消去コマンドを実行する消去コマンド実行部を設けることにより消去してもよい。

【0040】

次に、図1に記載されたマイクロコンピュータ100の動作について説明する。図2は、マイクロコンピュータ100の動作に関するフローチャートである。

【0041】

まず、第2比較器113が、ユーザが任意に設定したハイ/ロウ幅期待値レジスタ112のハイ/ロウ幅期待値と、現在の内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値、すなわち、内蔵発振クロックのハイ/ロウレベル期間をカウントした値と、を比較する(ステップS101)。

【0042】

第2比較器113は、ステップS101における比較の結果2つの値が不一致だった場合は、不一致信号を出力する。変化回数カウンタ121は、当該不一致信号が入力されるとカウンタの値を一回インクリメントしてカウント値を記憶する(ステップS102)。

【0043】

第1比較器123は、ステップS102によってインクリメントされた変化回数カウンタ121のカウント値と、ユーザにより任意に設定された変化回数期待値レジスタ122に格納された値とを比較する(ステップS103)。第1比較器123は、比較の結果、これら2つの値が一致した場合は一致信号を出力する。一方、これら2つの値が一致しなかった場合は、再び上記S101〜S103の処理が繰り返される。

【0044】

上記一致信号に基づいてセルフ消去コマンドが実行され、フラッシュメモリ内のデータが消去される(ステップS104)。

【0045】

次に、クロック不一致検出部110で行われる内蔵発振クロックの変動検出における、内蔵発振クロックのハイ/ロウ幅のカウント方法を図3のタイミングチャートを用いて説明する。

【0046】

CLKは、内蔵発振器140から出力される内蔵発振クロックを示しており、HCLKはそのハイ幅を、LCLKはそのロウ幅をそれぞれ分けて表記している。また、BCLKは、サブ内蔵発振器150から出力されるベースクロックを示している。また、ここでは、図1の内蔵発振クロックハイ/ロウ幅カウンタと不一致信号について、ハイ幅カウンタとロウ幅カウンタ及びハイ幅不一致信号とロウ幅不一致信号というようにハイ・ロウに関して個別に表記している。

【0047】

この例では、CLKのハイ幅及びロウ幅の両方ともBCLKを基準として5カウントされているため、ハイ幅カウンタ及びロウ幅カウンタのカウント値は共に"5"となる。一方、ハイ/ロウ幅期待値レジスタには"7"の値が記憶されているため、第2比較器113に含まれるハイ幅比較器及びロウ幅比較器は、ハイ幅不一致信号とロウ幅不一致信号をそれぞれ生成して変化回数カウンタへ出力する。変化回数期待値レジスタには予め値"M"が記憶されているため、変化回数カウンタの値がMに到達した場合にセルフプログラミング消去コマンド起動トリガとなる一致信号が出力される。

【0048】

なお、クロック不一致検出部110は、内蔵発振クロックのハイ幅とロウ幅の両方を個別にカウントする構成に限るものではない。クロック不一致検出部110は、どちらか片方をカウントして1つの不一致信号を生成しても良いし、ハイ/ロウの組の1周期を単位としてBCLKを用いてカウントして1つの不一致信号を生成する構成であっても良い。

【0049】

なお、内蔵発振クロックとベースクロックとが、加えられる応力や光の照射に対して同様のクロック変動をしてしまうと、内蔵発振クロックのカウントにおいて、常に同じ値をカウントしてしまい、内蔵発振クロックの変動を検出する事ができない。そこで、ベースクロック(BCLK)を出力するサブ内蔵発振器150は、コンデンサ、抵抗等の配置をメインの内蔵発振クロック(CLK)を出力する内蔵発振器140と異なる構成とし、クロックの変化の仕方に相違を持たせる。このように構成することで、ベースクロックもIC開封による応力の変化や光の照射によって変動するが、内蔵発振クロックとは周波数変動特性が異なる為、内蔵発振クロックの変動を検出する事が可能となる。

【0050】

以上説明したように、本実施の形態1に係る情報処理装置は、データを記憶する主記憶部であるフラッシュメモリ、演算処理を行う処理部であるCPUコア、第1の周波数を有する第1クロック信号を出力する第1発振部である内蔵発振器、といった情報処理装置の基本構成に加え、次の構成要素を有している。すなわち、第2の周波数を有する第2クロック信号を出力する第2発振部と、前記第1クロック信号及び前記第2クロック信号に基づいて前記第1クロック信号の周波数の変化を検出する検出部と、前記検出された変化を計数する計数部と、外部より設定される所定の値を記憶する記憶部と、前記計数部で計数された値と前記記憶部に記憶されている値とに基づいて消去信号を出力する出力部と、前記消去信号に基づいて前記主記憶部に記憶されているデータを消去する消去部と、を備えることを特徴としている。

【0051】

また、本実施の形態1に係る情報処理装置に含まれる電子回路装置は、データを記憶する主記憶部と、クロック周波数の変化を検出する第1検出部と、前記検出された変化を計数する第1計数部と、外部より設定される所定の値を記憶する第1記憶部と、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とに基づいて前記主記憶部のデータを消去することを指示する消去信号を出力する出力部と、を備える。

【0052】

このように構成することで、ICパッケージが開封される場合に必然的に生じる応力や外光照射などをクロック周波数の変化で捉え、当該変化量とユーザが予め記憶させた値とが所定の条件を満たした場合に消去信号が出力される。従って、リバースエンジニアリングに対して高いセキュリティを保ちつつ、ユーザ自ら解析を行う場合は、消去信号が出力されないように記憶させる値を設定しておくことができる。

【0053】

例えば、第三者からICを開封された時点で瞬間的に主記憶部に記憶されているデータを消去したい場合は、第1記憶部に記憶させる値を"1"に設定する。このように設定することで、IC開封による応力の変化に起因するクロックの変動が検出された場合、即座に主記憶部に記憶されているデータが消去される。一方、ユーザによる正当な解析作業によりICパッケージを開封する必要がある場合には、開封された瞬間にデータが消去されてしまう事を避けるために、第1記憶部に記憶させる値を非常に大きな値に設定する。このように、ユーザが必要に応じて第1記憶部の値を変更できる構成とすることでユーザの使用用途に応じて、データ消去のタイミングを変更することができる。

【0054】

なお、前記出力部は、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とを比較する第1比較部を備え、前記第1比較部は、比較の結果、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とが一致した場合に消去信号を出力する構成とすることができる。このように構成することで比較的単純な電子回路で発明を実現することができる。

【0055】

また、前記第1計数部は、前記検出部で検出された変化の回数を計数する構成とすることができる。検出されるクロック周波数の変化のうち、その変化の回数を計数する構成とすることで、比較的単純な電子回路で発明を実現することができる。

【0056】

また、前記検出部は、第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数部と、所定の期待値を記憶する第2記憶部と、前記第2計数部で計数された値と前記第2記憶部に記憶されている値とを比較する第2比較部と、を備え、前記第2比較部は、比較の結果、前記第2計数部で計数された値と前記第2記憶部に記憶されている値とが一致しない場合に前記クロック周波数が変化したことを示す信号を前記第1計数部に出力する構成とすることができる。このように周波数の異なる2つのクロック信号を用いることでクロック周波数の変動検出が容易となる。

【0057】

また、前記情報処理装置の前記第1発振部及び前記第2発振部は、光が外部から照射された場合にそれぞれ異なる周波数変動特性を示すことを特徴としても良いし、外部から加えられる応力に対してそれぞれ異なる周波数変動特性を示すことを特徴としても良い。このように第1発振部と第2発振部とが所定の条件下において異なる発振特性を持つことで周波数変動を容易に検出することができる。このような周波数変動特性の差異は、第1発振部と第2発振部における抵抗やキャパシタや光感知素子等の配列や組み合わせに差異を持たせることで実現することができる。

【0058】

また、本実施の形態1に係るデータ消去方法は、外部より設定される所定の値を記憶部に記憶する記憶ステップと、クロック周波数の変化を検出する検出ステップと、前記検出された変化を計数する計数ステップと、前記計数ステップで計数された値と前記記憶ステップで記憶された値とに基づいて消去信号を出力する出力ステップと、前記消去信号に基づいて主記憶部に記憶されているデータを消去する消去ステップと、を有する。このような手順に従ってデータが消去される構成とすることで、使用目的に応じてデータの消去タイミングを変更することができる。

【0059】

なお、上記説明では、変化回数カウンタ121は、クロック周波数の変化回数をカウントする構成を示したがこれに限るものではなく、クロック周波数の変化の量も含めてカウントしても良い。例えば、ハイ/ロウ幅期待値レジスタ112に記録されている値が"9"で、内蔵発振クロックハイ/ロウ幅カウンタ110のカウント値が"5"であった場合、第2比較器113は、これらの値の差異である"4"に対応する情報を不一致信号に含めて変化回数カウンタ121に出力し、変化回数カウンタ121で4回インクリメントされる構成であっても良い。

【0060】

なお、上記説明では変化回数期待値レジスタ122に記憶されている期待値と変化回数カウンタ121のカウント値が同一であった場合に一致信号を送信する場合について説明したが、これに限るものではない。例えば変化回数カウンタ121の値が変化回数期待値レジスタ122に記憶されている期待値を上回った場合に一致信号を出力する構成であっても良い。

【0061】

(実施の形態2)

本実施の形態2に係る発明は、クロック周波数を時系列で比較することでクロック周波数の変化を検出し、第三者のリバースエンジニアリングを防止することを特徴としている。

【0062】

図4は、本実施の形態2に係る電子回路装置である内蔵発振クロック変化検出器201のブロック図である。なお、実施の形態1で説明したブロックと同一のブロックについては一部説明を省略する。

【0063】

本実施の形態2に係るクロック不一致検出部210は、内蔵発振クロックハイ/ロウ幅カウンタ111、タイマ211、ハイ/ロウ幅キャプチャレジスタ212、内蔵発振クロックハイ/ロウ幅現在値レジスタ213、内蔵発振クロックハイ/ロウ幅保持値レジスタ214、第2比較器215、から構成される。

【0064】

タイマ211は、予め設定されている時間経過毎にキャプチャトリガ信号を生成してハイ/ロウ幅キャプチャレジスタ212及び内蔵発振クロックハイ/ロウ幅現在値レジスタ213に出力する。

【0065】

ハイ/ロウ幅キャプチャレジスタ212は、タイマから入力したキャプチャトリガ信号をトリガとして内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値をキャプチャし、キャプチャしたカウント値を内蔵発振クロックハイ/ロウ幅現在値レジスタ213へ出力する。

【0066】

内蔵発振クロックハイ/ロウ幅現在値レジスタ213は、ハイ/ロウ幅キャプチャレジスタから出力されたカウント値を記憶する。また、タイマ211から入力したキャプチャトリガ信号をトリガとして、現在記憶しているカウント値を内蔵発振クロックハイ/ロウ幅保持値レジスタ214に出力し、ハイ/ロウ幅キャプチャレジスタ212から新たに出力されるカウント値を記憶する。

【0067】

内蔵発振クロックハイ/ロウ幅保持値レジスタ214は、内蔵発振クロックハイ/ロウ幅現在値レジスタ213から出力されたカウント値を記憶する。

【0068】

第2比較器215は、内蔵発振クロックハイ/ロウ幅保持値レジスタ214と内蔵発振クロックハイ/ロウ幅現在値レジスタ213にそれぞれ記憶されている値を比較する。比較タイミングは、例えば、タイマ211で計測される所定の時間毎に比較を行う。当該比較の結果、これらの2つの値が異なる場合は、不一致信号を生成し、変化回数カウンタ121へ出力する。その後の動作は実施の形態1と同様であるため説明を省略する。

【0069】

以上の構成によれば、タイマに設定された所定の時間分異なる時刻におけるカウント値を比較できるため、時系列で比較した結果異なるカウント値が生じた場合に不一致信号を生成し、変化回数カウンタ122の値をインクリメントしていく。そして変化回数カウンタ122の値と変化回数期待値レジスタ122に記憶されている値とに基づいて消去信号が出力され、フラッシュメモリのデータを消去することができる。

【0070】

すなわち、本実施の形態2に係る電子回路装置は、クロック周波数の変化を検出する検出部と、前記検出された変化を計数する第1計数部と、外部より設定される所定の値を記憶する第1記憶部と、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とに基づいて消去信号を出力する出力手段と、を備え、前記検出手段は、第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数部と、所定の時間を計測する時間計測部と、前記第2計数部で計数された値を記憶する第2記憶部と、前記第2記憶部で記憶された値と前記時間計測部で計測された所定の時間経過後に前記第2計数部で計数された値とを比較する第2比較部と、から構成され、前記第2比較部は、比較の結果、前記第2記憶部で記憶された値と前記時間計測部で計測された所定の時間経過後に前記第2計数部で計数された値とが一致しない場合に前記クロック周波数が変化したことを示す信号を前記第1計数部に出力することを特徴とする。

【0071】

また、本実施の形態2に係るデータ消去方法は、外部より設定される所定の値を記憶部に記憶する記憶ステップと、クロック信号のハイ幅又はロウ幅を計数する第1計数ステップと、所定の時間の計測を開始する時間計測ステップと、前記時間計測ステップで計測された所定の時間後にクロック信号のハイ幅又はロウ幅を計数する第2計数ステップと、前記第1計数ステップ及び前記第2計数ステップで計数された値を比較する比較ステップと、前記前記第1計数ステップで計数された値と前記第2ステップで計数された値が同一でない回数を計数する第3計数ステップと、前記記憶ステップで記憶した値と前記第3計数ステップで計数された値とに基づいて消去信号を出力する出力ステップと、前記消去信号に基づいてデータを消去する消去ステップと、を有する。

【0072】

IC開封によるリバースエンジニアリングを行うと外光が電子回路装置に照射されるため内蔵発振クロックに変化を生じる。従って、開封前と開封後で内蔵発振クロックハイ/ロウ幅カウンタでカウントされる値が変化する。本実施の形態2の電子回路装置は、異なる時刻で得られたカウント値を比較することによりクロック変化を検出することができるため、応力を装置に与えずにICを開封することができたとしても開封前後で装置に照射される光の変化量に基づいてICが開封されたことを検出し、適切にデータを消去することができる。なお、ユーザ自らが解析のために開封する場合には、変化回数期待値レジスタに大きな値を設定しておけば、ICを開封しても第1比較器123から直ちに消去信号が出力されることがないため、適切に解析作業を行うことができる。

【0073】

なお、第2比較器215は、実施の形態1の場合と同様、動作保証温度範囲内での温度依存を考慮し、内蔵発振クロックハイ/ロウ幅保持値レジスタ214と内蔵発振クロックハイ/ロウ幅現在値レジスタ215にそれぞれ記憶されている値が、所定の誤差以上の差異がある場合に不一致信号を生成するよう構成しても良い。

【0074】

(実施の形態3)

本実施の形態3に係る電子回路装置は、実施の形態1で説明した応力による内蔵発振クロックの変化を検出する第1のクロック不一致検出部と、実施の形態2で説明した内蔵発振クロックの時系列変化を検出する第2のクロック不一致検出部を組み合わせた構成とすることを特徴とする。以下図面を用いて説明する。

【0075】

図5は、本実施の形態3に係る内蔵発振クロック変化検出器301のブロック図である。なお、実施の形態1及び2で説明したブロックと同一のブロックについては一部説明を省略する。

【0076】

本実施の形態3の内蔵発振クロック変化検出器301は、大きく分けて、第1クロック不一致検出部310と、期待変化回数比較部320と、第2クロック不一致検出部330と、から構成される。

【0077】

第1クロック不一致検出部310は、ICが開封された時の応力の変化により生じる内蔵発振クロックの最初の変動を検出する第1の検出部である。第2クロック不一致検出部330は、上記最初の変動が検出された場合、その最初の変動以降にIC開封後の光の照射により発生する内蔵発振クロックの変化を時系列的に検出する第2の検出部である。期待変化回数比較部320は、第1クロック不一致検出部310及び第2クロック不一致検出部330により検出された変動をカウントする。そして、当該カウントした値が予め設定された値と一致した場合に消去信号を出力する出力部である。以下、各ブロックについて詳細に説明する。

【0078】

クロック不一致検出部310は、内蔵発振クロックハイ/ロウ幅カウンタ111と、ハイ/ロウ幅期待値レジスタ112と、第2比較器113と、ハイ/ロウ幅キャプチャレジスタ312と、から構成される。

【0079】

内蔵発振クロックハイ/ロウ幅カウンタ111は、内蔵発振器から出力される内蔵発振クロックのハイ/ロウレベル期間を、サブ内蔵発振器から出力されるベースクロックを用いてカウントする。

【0080】

ハイ/ロウ幅期待値レジスタ112は、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされるハイ/ロウレベル期間の期待値を記憶する。内蔵発振クロックハイ/ロウ幅期待値レジスタ112は、外部より内部バス180を介してアクセス可能な構成となっており、ユーザは、任意に期待値を設定することができる。

【0081】

第2比較器113は、内蔵発振クロックハイ/ロウ幅カウンタ111でカウントされる値と、ハイ/ロウ幅期待値レジスタ112に記憶されている値とを常時比較する。比較の結果、これらの2つの値が不一致となった場合に、第2比較器113は第1の不一致信号を後述するハイ/ロウ幅キャプチャレジスタ312、タイマ331及び変化回数カウンタ321に出力する。

【0082】

ハイ/ロウ幅キャプチャレジスタ312は、第2比較器113から出力される第1不一致信号又は後述のタイマ331から出力されるキャプチャトリガ信号をトリガとして内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値をキャプチャする。第1不一致信号に基づいてキャプチャされたカウント値は、後述の内蔵発振クロックハイ/ロウ幅保持値レジスタ334へ、キャプチャトリガ信号に基づいてキャプチャされた値は、後述の内蔵発振クロックハイ/ロウ幅現在値レジスタ333へそれぞれ出力される。

【0083】

第2クロック不一致検出部330は、タイマ331と、内蔵発振クロックハイ/ロウ幅現在値レジスタ333と、内蔵発振クロックハイ/ロウ幅保持値レジスタ334と、第3比較器335と、から構成される。

【0084】

タイマ331は、第2比較器113から出力された第1不一致信号をトリガとして時間計測を開始し、予め設定されている時間経過後にキャプチャトリガ信号を生成してハイ/ロウ幅キャプチャレジスタ312に出力する。

【0085】

内蔵発振クロックハイ/ロウ幅保持値レジスタ334は、ハイ/ロウ幅キャプチャレジスタ312が第1不一致信号をトリガとしてキャプチャした値を入力して記憶する。すなわち、ハイ/ロウ幅キャプチャレジスタ312は、第1不一致信号をトリガとして内蔵発振クロックハイ/ロウ幅カウンタ111からカウント値を取り込み、内蔵発振クロックハイ/ロウ幅保持値レジスタ334へ取り込んだカウント値を出力する。

【0086】

内蔵発振クロックハイ/ロウ幅現在値レジスタ333は、ハイ/ロウ幅キャプチャレジスタ312がキャプチャトリガ信号をトリガとしてキャプチャした値を入力して記憶する。すなわち、ハイ/ロウ幅キャプチャレジスタ312は、キャプチャトリガ信号をトリガとして内蔵発振クロックハイ/ロウ幅カウンタ111からカウント値を取り込み、内蔵発振クロックハイ/ロウ幅現在値レジスタ333へ取り込んだカウント値を出力する。

【0087】

第3比較器335は、内蔵発振クロックハイ/ロウ幅保持値レジスタ334に記憶された値と、内蔵発振クロックハイ/ロウ幅現在値レジスタ333に記憶された値とを比較する。比較の結果、これらの2つの値が不一致となった場合に、第3比較器335は第2の不一致信号を出力する。第3比較器335より出力された第2不一致信号は、変化回数カウンタ321に入力される。

【0088】

期待変化回数比較部320は、変化回数カウンタ321と、変化回数期待値レジスタ122と、第1比較器123と、から構成される。

【0089】

変化回数カウンタ321は、上述した第1不一致信号及び第2不一致信号を入力し、これらの信号が入力される度にカウンタの値をインクリメントして記憶する。

【0090】

変化回数期待値レジスタ122は、外部より設定される所定の値を記憶する。変化回数期待値レジスタ122は、内部バス180を介してアクセス可能となっており、ユーザは記憶させておく値を任意に設定することができる。

【0091】

第1比較器123は、変化回数期待値レジスタ122に記憶されている値と変化回数カウンタ321に記憶されている値を比較する。第1比較器123は、比較の結果、変化回数カウンタ123に記憶されている値が変化回数期待値レジスタ122に記憶されている値と一致した場合は一致信号を生成して出力する。

【0092】

次に、本実施の形態に関する内蔵発振クロック変化検出器301の動作を図6のフローチャートを用いて説明する。なお、ステップS101〜S103は、図3に示すフローチャートのステップステップS101〜S103と同一であるため説明を省略する。

【0093】

S103において、変化回数カウンタ321に記憶されている値と変化回数期待値レジスタ122に記憶されている値とが異なる場合、ハイ/ロウ幅保持値レジスタ334は、ハイ/ロウ幅キャプチャレジスタ312がキャプチャした内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値を格納する(ステップS104)。

【0094】

次に、ハイ/ロウ幅現在値レジスタ333は、タイマ331によって作り出される所定の時間経過後にハイ/ロウ幅キャプチャレジスタ312がキャプチャした内蔵発振クロックハイ/ロウ幅カウンタ111のカウント値を格納する(ステップS105)。

【0095】

次に、第3比較器335は、ハイ/ロウ幅保持値レジスタ334に格納されている過去のカウント値とハイ/ロウ幅現在値レジスタ333に格納されている現在のカウント値とを比較する(ステップS106)。

【0096】

上記比較の結果、上記2つのカウント値が一致する場合は、ステップS101の前段に戻って待機する。一方、比較の結果、上記2つのカウント値が一致しない場合は、第3比較器は、不一致信号を生成して変化回数カウンタ321に出力し、変化回数カウンタ321の値が一つインクリメントされる(ステップS107)。

【0097】

次に、第1比較器123は、変化回数カウンタ321の値と変化回数期待値レジスタ122の値を比較する。これらの値が同一であった場合は一致信号を生成して出力し、同一でない場合はステップS104の前段に戻る(ステップS108)。

【0098】

上記一致信号がトリガとなってセルフプログラミング消去コマンドを起動され、内蔵フラッシュROMのデータが一斉に消去される(ステップS109)。

【0099】

以上の構成によれば、応力が加えられた場合に生じるクロック変動と時系列で現れるクロック変動の両方を用いてフラッシュメモリ内のデータを消去するかどうかを判断することができる。

【0100】

なお、上記説明では、第1クロック不一致検出部と第2クロック不一致検出部が直列的に配置される構成を示したがこれに限るものではなく、第1・第2クロック不一致検出部をパラレルに配置する構成であっても良い。図7は、別の変化形態の内蔵発振クロック変化検出器401のブロック構成を示している。

【0101】

内蔵発振クロック変化検出器401は、第1クロック不一致検出部410と第2クロック検出部430の2つの検出手段及び第1期待変化回数比較部420と第2期待変化回数比較部440の2つの比較手段を備える。内部の各ブロックの機能は上述しているため一部説明を省略する。

【0102】

第1期待変化回数比較部420は、第1クロック不一致検出部410より出力される第1不一致信号を入力し、変化回数期待値レジスタ422の値と変化回数カウンタ421の値が一致した場合に第1一致信号を出力する。また、第2期待変化回数比較部440も、第2クロック不一致検出部430より出力される第2不一致信号を入力し、変化回数期待値レジスタ442の値と変化回数カウンタ441の値が一致した場合に第2一致信号を出力する。

【0103】

消去コマンド実行部450は、第1一致信号と第2一致信号を入力し、この2つの一致信号が入力された場合に消去コマンドを実行してフラッシュメモリのデータを消去する。なお、2つの一致信号の入力タイミングは同一である必要はない。

【0104】

以上説明したように、本実施の形態3に係る電子回路装置は、クロック周波数の変化を検出する第1検出部と、所定の時間を計測する時間計測部と、前記時間計測部で計測された所定の時間分異なる時刻における前記クロック周波数の変化を検出する第2検出部と、前記第1検出部及び前記第2検出部で検出された前記クロック周波数の変化を計数する第1計数部と、外部より設定される所定の値を記憶する第1記憶部と、前記第1計数部で計数された値と前記第1記憶部に記憶されている値とに基づいて消去信号を出力する出力部と、を具備する。

【0105】

また、前記第1検出部は、第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数部と、所定の期待値を記憶する第2記憶部と、前記第2計数部で計数された値と前記第2記憶部に記憶されている値とを比較する第2比較部と、を備え、前記第2比較部は、比較の結果、前記第2計数部で計数された値と前記第2記憶部に記憶されている値とが一致しない場合に前記クロック周波数が変化したことを示す第1不一致信号を前記第1計数部に出力する構成とすることができる。

【0106】

また、前記第2検出部は、前記第2計数部で計数された値を記憶する第3記憶部と、前記第3記憶部で記憶された値と前記時間計測部で計測された所定の時間経過後に前記第2計数部で計数された値とを比較する第3比較部と、を備え、前記第3比較部は、比較の結果、前記第3記憶部で記憶された値と前記時間計測部で計測された所定の時間経過後に前記第2計数部で計数された値とが一致しない場合に前記クロック周波数が変化したことを示す第2不一致信号を前記第1計数部に出力する構成とすることができる。

【0107】

また、前記時間計測部は、前記第1不一致信号を入力することにより前記所定の時間の計測を開始する構成とすることができる。

【0108】

また、所定の値を記憶する第4記憶部を更に備え、前記第1計数部は、前記第1検出部で検出された変化を計数する第1変化計数部と、前記第2検出部で検出された変化を計数する第2変化計数部と、から構成され、前記出力部は、前記第1変化計数部で計数された値と前記第1記憶部に記憶されている値とに基づいて第1の消去信号を出力する第1出力部と、前記第2変化計数部で計数された値と前記第4記憶部に記憶されている値とに基づいて第2の消去信号を出力する第2出力部と、を備える構成とすることができる。

【0109】

上記第1消去信号及び第2消去信号が出力された場合、つまり、2つの検出部でともにクロック周波数の変化が検出された場合に、別途設けられた消去部が、主記憶部に格納されているデータを消去するよう構成しても良い。

【0110】

(実施の形態4)

本実施の形態では、実施の形態3に係る電子回路装置が具備するタイマの計測時間を変更できる構成としたことを特徴とする。

【0111】

図8は、本実施の形態4に係る内蔵発振クロック変化検出器に含まれるタイマ530のブロック図である。

【0112】

タイマ530は、所定の時間を計測する時間計測部であり、図4のタイマ211や図7のタイマ431に対応する。タイマ530は、コンペアレジスタ531と、セレクタ532と、AND回路533と、周波数変化回数タイマカウンタ534と、比較器535と、から構成される。

【0113】

コンペアレジスタ531は、時間計測の基準となる値が記憶されている。

【0114】

セレクタ532は、分周されて複数の周波数をもつベースクロック信号の中から1つの信号を選び出す。ユーザはセレクタ532にアクセス可能であり、どの周波数をもつベースクロック信号を選び出すかを設定できる構成となっている。

【0115】

AND回路533は、タイマ530より出力された不一致信号と、前記セレクタ432から出力された信号とを入力して論理積をとって信号を出力する。

【0116】

周波数変化回数タイマカウンタ534は、AND回路533から出力された信号の周波数変化をカウントする。

【0117】

比較器535は、周波数変化回数タイマカウンタ534でカウントされたカウント値とコンペアレジスタ531に記憶されている基準値とを比較する。比較の結果、上記カウント値と基準値とが一致した場合にキャプチャトリガ信号が出力される。

【0118】

上記構成によれば、ユーザからの設定によりセレクタ536で異なる周波数をもつクロック信号から1つのクロック信号を選び出すことができ、不一致信号との論理積をとって出力信号をカウントできるので、ユーザがタイマ530で計測する時間を設定することができる。

【0119】

なお、タイマで計測する時間の設定方法としては、上記方法に限定されるものではなく、例えばコンペアレジスタにユーザが内部バスを通じてアクセス可能な構成とすることもできる。すなわち、セレクタ536を取り除き、所定の周波数をもつクロック信号と不一致信号との論理積出力を周波数変化回数タイマカウンタがカウントし、コンペアレジスタにユーザが設定した基準値と周波数変化回数タイマカウンタでカウントされたカウント値とを比較するよう構成しても良い。

【0120】

以上、各実施の形態で説明したように、本発明によれば、ユーザがフラッシュメモリの消去タイミングを任意に選択可能となる為、ユーザの使用用途に合わせてセキュリティレベルの設定が可能となる。従って、第三者のリバースエンジニアリングに対して高いセキュリティを保ちつつ、ユーザ自身による十分な解析も可能となる。

【0121】

なお、変化回数レジスタ及びハイ/ロウ幅期待値レジスタは、別途設けられた設定部により格納する値を設定できる。すなわち、設定部は、ユーザからの指示に基づいて変化回数レジスタ又はハイ/ロウ幅期待値レジスタに記憶させる所定の値を設定するよう構成しても良い。

【0122】

また、変化回数レジスタやハイ/ロウ幅期待値レジスタにアクセスをするためには所定の認証や手順を踏んだ場合にアクセスできる構成とすることもできる。この場合、新たにアクセス管理部を別途備え、当該アクセス管理部が、所定の認証処理や設定手順に基づいた上記レジスタへのアクセスが行われたかを判断する判断処理を行う構成であっても良い。当該アクセス管理部で、適切なユーザからのレジスタアクセス要求であることを確認した後に、ユーザが変化回数レジスタ又はハイ/ロウ幅期待値レジスタにアクセスし、これらのレジスタに格納されている基準値を変更できる構成であっても良い。

【0123】

なお、上記説明では消去信号に基づいて主記憶部であるフラッシュメモリのデータを消去する構成について示したがこれに限定するものではなく、別の記憶手段に記憶されている秘密データを消去する構成であっても良い。

【0124】

その他、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0125】

100:マイクロコンピュータ 101:内蔵発振クロック変化検出器

110:クロック不一致検出部 111:内蔵発振クロックハイ/ロウ幅カウンタ

112:ハイ/ロウ幅期待値レジスタ 113:第2比較器

120:期待変化回数比較部 121:変化回数カウンタ

122:変化回数期待値レジスタ 123:第1比較器

140:内蔵発信器 150:サブ内蔵発信器

160:CPUコア 170:フラッシュメモリ

180:内部バス 190:周辺ハードウェア

201:内蔵発振クロック変化検出器 210:クロック不一致検出部

211:タイマ 212:ハイ/ロウ幅キャプチャレジスタ

213:内部発振クロックハイ/ロウ幅現在値レジスタ

214:内部発振クロックハイ/ロウ幅保持値レジスタ

215:第2比較器 301:内部発振クロック変化検出器

310:第1クロック不一致検出部 312:ハイ/ロウ幅キャプチャレジスタ

320:期待変化回数比較部 321:変化回数カウンタ

330:第2クロック不一致検出部 331:タイマ

333:内部発振クロックハイ/ロウ幅現在値レジスタ

334:内部発振クロックハイ/ロウ幅保持値レジスタ

335:第3比較器 401:内部発振クロック変化検出器

410:第1クロック不一致検出部 420:第1期待変化回数比較部

421:変化回数カウンタ 422:変化回数期待値レジスタ

423:第1比較器 430:第2クロック不一致検出部

431:タイマ 440:第2期待変化回数比較部

441:変化回数カウンタ 442:変化回数期待値レジスタ

443:第1比較器 450:消去コマンド生成部

501:内部発振クロック変化検出器 530:タイマ

531:コンペアレジスタ 532:セレクタ

533:AND回路 534:周波数変化回数タイマカウンタ

535:比較器

【特許請求の範囲】

【請求項1】

データを記憶する主記憶手段と、

クロック周波数の変化を検出する第1検出手段と、

前記検出された変化を計数する第1計数手段と、

外部より設定される所定の値を記憶する第1記憶手段と、

前記第1計数手段で計数された値と前記第1記憶手段に記憶されている値とに基づいて前記主記憶手段のデータを消去することを指示する消去信号を出力する出力手段と、

を具備する電子回路装置。

【請求項2】

前記出力手段は、前記第1計数手段で計数された値と前記第1記憶手段に記憶されている値とを比較する第1比較手段を備え、

前記第1比較手段は、比較の結果、前記第1計数手段で計数された値と前記第1記憶手段に記憶されている値とが一致した場合に前記消去信号を出力する、

請求項1に記載の電子回路装置。

【請求項3】

前記第1計数手段は、前記第1検出手段で検出された変化の回数を計数する、

請求項1に記載の電子回路装置。

【請求項4】

前記第1検出手段は、

第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数手段と、

所定の期待値を記憶する第2記憶手段と、

前記第2計数手段で計数された値と前記第2記憶手段に記憶されている値とを比較する第2比較手段と、

を備え、

前記第2比較手段は、比較の結果、前記第2計数手段で計数された値と前記第2記憶手段に記憶されている値とが一致しない場合に前記クロック周波数が変化したことを示す信号を前記第1計数手段に出力する、

請求項1から請求項3のいずれかに記載の電子回路装置。

【請求項5】

前記第1検出手段は、

第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数手段と、

所定の時間を計測する時間計測手段と、

前記第2計数手段で計数された値を記憶する第2記憶手段と、

前記第2記憶手段に記憶された値と前記時間計測手段で計測された所定の時間経過後に前記第2計数手段で計数された値とを比較する第2比較手段と、

を備え、

前記第2比較手段は、比較の結果、前記第2記憶手段で記憶された値と前記時間計測手段で計測された所定の時間経過後に前記第2計数手段で計数された値とが一致しない場合に前記クロック周波数が変化したことを示す信号を前記第1計数手段に出力する、

請求項1から請求項3のいずれかに記載の電子回路装置。

【請求項6】

所定の時間を計測する時間計測手段と、

前記時間計測手段で計測された所定の時間分異なる時刻におけるクロック周波数の変化を検出する第2検出手段と、

を更に具備し、

前記第1計数手段は、前記第1検出手段及び前記第2検出手段で検出された前記クロック周波数の変化を計数する、

請求項1から請求項3のいずれかに記載の電子回路装置。

【請求項7】

外部より設定される所定の値を記憶する第2記憶手段を更に具備し、

前記第1計数手段は、

前記第1検出手段で検出された変化を計数する第1変化計数手段と、

前記第2検出手段で検出された変化を計数する第2変化計数手段と、

を備え、

前記出力手段は、

前記第1変化計数手段で計数された値と前記第1記憶手段に記憶されている値とに基づいて第1の消去信号を出力する第1出力手段と、

前記第2変化計数手段で計数された値と前記第2記憶手段に記憶されている値とに基づいて第2の消去信号を出力する第2出力手段と、

を備える、

請求項6に記載の電子回路装置。

【請求項8】

前記第1検出手段は、

第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数手段と、

所定の期待値を記憶する第2記憶手段と、

前記第2計数手段で計数された値と前記第2記憶手段に記憶されている値とを比較する第2比較手段と、

を備え、

前記第2比較手段は、比較の結果、前記第2計数手段で計数された値と前記第2記憶手段に記憶されている値とが一致しない場合に前記クロック周波数が変化したことを示す第1不一致信号を前記第1計数手段に出力する、

請求項6に記載の電子回路装置。

【請求項9】

前記第2検出手段は、

前記第2計数手段で計数された値を記憶する第3記憶手段と、

前記第3記憶手段で記憶された値と前記時間計測手段で計測された所定の時間経過後に前記第2計数手段で計数された値とを比較する第3比較手段と、

を備え、

前記第3比較手段は、比較の結果、前記第3記憶手段で記憶された値と前記計測手段で計測された所定の時間経過後に前記第2計数手段で計数された値とが一致しない場合に前記クロック周波数が変化したことを示す第2不一致信号を前記第1計数手段に出力する、

請求項8に記載の電子回路装置。

【請求項10】

前記時間計測手段は、前記第1不一致信号を入力することにより前記所定の時間の計測を開始する、

請求項9に記載の電子回路装置。

【請求項11】

データを記憶する主記憶手段と

演算処理を行う処理手段と、

第1の周波数を有する第1クロック信号を出力する第1発振手段と、

第2の周波数を有する第2クロック信号を出力する第2発振手段と、

前記第1クロック信号及び前記第2クロック信号に基づいて前記第1クロック信号の周波数の変化を検出する検出手段と、

前記検出された変化を計数する計数手段と、

外部より設定される所定の値を記憶する記憶手段と、

前記計数手段で計数された値と前記記憶手段に記憶されている値とに基づいて消去信号を出力する出力手段と、

前記消去信号に基づいて前記主記憶手段に記憶されているデータを消去する消去手段と、

を具備する情報処理装置。

【請求項12】

前記第1発振手段及び前記第2発振手段は、外部から加えられる応力に対してそれぞれ異なる周波数変動特性を示すことを特徴とする、

請求項11に記載の情報処理装置。

【請求項13】

前記第1発振手段及び前記第2発振手段は、光が外部から照射された場合にそれぞれ異なる周波数変動特性を示すことを特徴とする、

請求項11に記載の情報処理装置。

【請求項14】

外部より設定される所定の値を記録部に記憶する記憶ステップと、

クロック周波数の変化を検出する第1検出ステップと、

前記検出された変化を計数する計数ステップと、

前記計数ステップで計数された値と前記記憶ステップで記憶された値とに基づいて消去信号を出力する出力ステップと、

前記消去信号に基づいて主記憶部に記憶されているデータを消去する消去ステップと、

を有するデータ消去方法。

【請求項15】

前記第1検出ステップにおける検出結果に基づいて所定の時間の計測を開始する時間計測ステップと、

前記時間計測ステップで計測された所定の時間分異なる時刻における前記クロック周波数の変化を検出する第2検出ステップと、

を更に有し、

前記計数ステップは、第1検出ステップ及び前記第2検出ステップで検出された変化を計数する、

請求項14に記載のデータ消去方法。

【請求項1】

データを記憶する主記憶手段と、

クロック周波数の変化を検出する第1検出手段と、

前記検出された変化を計数する第1計数手段と、

外部より設定される所定の値を記憶する第1記憶手段と、

前記第1計数手段で計数された値と前記第1記憶手段に記憶されている値とに基づいて前記主記憶手段のデータを消去することを指示する消去信号を出力する出力手段と、

を具備する電子回路装置。

【請求項2】

前記出力手段は、前記第1計数手段で計数された値と前記第1記憶手段に記憶されている値とを比較する第1比較手段を備え、

前記第1比較手段は、比較の結果、前記第1計数手段で計数された値と前記第1記憶手段に記憶されている値とが一致した場合に前記消去信号を出力する、

請求項1に記載の電子回路装置。

【請求項3】

前記第1計数手段は、前記第1検出手段で検出された変化の回数を計数する、

請求項1に記載の電子回路装置。

【請求項4】

前記第1検出手段は、

第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数手段と、

所定の期待値を記憶する第2記憶手段と、

前記第2計数手段で計数された値と前記第2記憶手段に記憶されている値とを比較する第2比較手段と、

を備え、

前記第2比較手段は、比較の結果、前記第2計数手段で計数された値と前記第2記憶手段に記憶されている値とが一致しない場合に前記クロック周波数が変化したことを示す信号を前記第1計数手段に出力する、

請求項1から請求項3のいずれかに記載の電子回路装置。

【請求項5】

前記第1検出手段は、

第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数手段と、

所定の時間を計測する時間計測手段と、

前記第2計数手段で計数された値を記憶する第2記憶手段と、

前記第2記憶手段に記憶された値と前記時間計測手段で計測された所定の時間経過後に前記第2計数手段で計数された値とを比較する第2比較手段と、

を備え、

前記第2比較手段は、比較の結果、前記第2記憶手段で記憶された値と前記時間計測手段で計測された所定の時間経過後に前記第2計数手段で計数された値とが一致しない場合に前記クロック周波数が変化したことを示す信号を前記第1計数手段に出力する、

請求項1から請求項3のいずれかに記載の電子回路装置。

【請求項6】

所定の時間を計測する時間計測手段と、

前記時間計測手段で計測された所定の時間分異なる時刻におけるクロック周波数の変化を検出する第2検出手段と、

を更に具備し、

前記第1計数手段は、前記第1検出手段及び前記第2検出手段で検出された前記クロック周波数の変化を計数する、

請求項1から請求項3のいずれかに記載の電子回路装置。

【請求項7】

外部より設定される所定の値を記憶する第2記憶手段を更に具備し、

前記第1計数手段は、

前記第1検出手段で検出された変化を計数する第1変化計数手段と、

前記第2検出手段で検出された変化を計数する第2変化計数手段と、

を備え、

前記出力手段は、

前記第1変化計数手段で計数された値と前記第1記憶手段に記憶されている値とに基づいて第1の消去信号を出力する第1出力手段と、

前記第2変化計数手段で計数された値と前記第2記憶手段に記憶されている値とに基づいて第2の消去信号を出力する第2出力手段と、

を備える、

請求項6に記載の電子回路装置。

【請求項8】

前記第1検出手段は、

第1の周波数を有するクロック信号のハイ幅又はロウ幅を第2の周波数を有するクロック信号を用いて計数する第2計数手段と、

所定の期待値を記憶する第2記憶手段と、

前記第2計数手段で計数された値と前記第2記憶手段に記憶されている値とを比較する第2比較手段と、

を備え、

前記第2比較手段は、比較の結果、前記第2計数手段で計数された値と前記第2記憶手段に記憶されている値とが一致しない場合に前記クロック周波数が変化したことを示す第1不一致信号を前記第1計数手段に出力する、

請求項6に記載の電子回路装置。

【請求項9】

前記第2検出手段は、

前記第2計数手段で計数された値を記憶する第3記憶手段と、

前記第3記憶手段で記憶された値と前記時間計測手段で計測された所定の時間経過後に前記第2計数手段で計数された値とを比較する第3比較手段と、

を備え、

前記第3比較手段は、比較の結果、前記第3記憶手段で記憶された値と前記計測手段で計測された所定の時間経過後に前記第2計数手段で計数された値とが一致しない場合に前記クロック周波数が変化したことを示す第2不一致信号を前記第1計数手段に出力する、

請求項8に記載の電子回路装置。

【請求項10】

前記時間計測手段は、前記第1不一致信号を入力することにより前記所定の時間の計測を開始する、

請求項9に記載の電子回路装置。

【請求項11】

データを記憶する主記憶手段と

演算処理を行う処理手段と、

第1の周波数を有する第1クロック信号を出力する第1発振手段と、

第2の周波数を有する第2クロック信号を出力する第2発振手段と、

前記第1クロック信号及び前記第2クロック信号に基づいて前記第1クロック信号の周波数の変化を検出する検出手段と、

前記検出された変化を計数する計数手段と、

外部より設定される所定の値を記憶する記憶手段と、

前記計数手段で計数された値と前記記憶手段に記憶されている値とに基づいて消去信号を出力する出力手段と、

前記消去信号に基づいて前記主記憶手段に記憶されているデータを消去する消去手段と、

を具備する情報処理装置。

【請求項12】

前記第1発振手段及び前記第2発振手段は、外部から加えられる応力に対してそれぞれ異なる周波数変動特性を示すことを特徴とする、

請求項11に記載の情報処理装置。

【請求項13】

前記第1発振手段及び前記第2発振手段は、光が外部から照射された場合にそれぞれ異なる周波数変動特性を示すことを特徴とする、

請求項11に記載の情報処理装置。

【請求項14】

外部より設定される所定の値を記録部に記憶する記憶ステップと、

クロック周波数の変化を検出する第1検出ステップと、

前記検出された変化を計数する計数ステップと、

前記計数ステップで計数された値と前記記憶ステップで記憶された値とに基づいて消去信号を出力する出力ステップと、

前記消去信号に基づいて主記憶部に記憶されているデータを消去する消去ステップと、

を有するデータ消去方法。

【請求項15】

前記第1検出ステップにおける検出結果に基づいて所定の時間の計測を開始する時間計測ステップと、

前記時間計測ステップで計測された所定の時間分異なる時刻における前記クロック周波数の変化を検出する第2検出ステップと、

を更に有し、

前記計数ステップは、第1検出ステップ及び前記第2検出ステップで検出された変化を計数する、

請求項14に記載のデータ消去方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−3731(P2013−3731A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2011−132525(P2011−132525)

【出願日】平成23年6月14日(2011.6.14)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成23年6月14日(2011.6.14)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]