情報処理装置および情報処理装置の制御方法

【課題】通信時に発生するノイズを抑制しつつ、高速な通信を可能とする情報処理装置を提供する。

【解決手段】情報処理装置1には、2本1組の信号線7a,7bで構成される信号線対7と信号線対7に対して入力された2進数の複数ビットのデータに応じた電圧レベルに設定するためのドライバ2と、信号線対7の他端側に接続され、信号線対7の電圧レベルに応じて2進数の複数ビットのデータに変換するためのレシーバ3とが設けられる。ドライバ2は、信号線対7に電圧を印加するための定電圧源4と、2進数の複数ビットのデータに応じて信号線対の入出力インピーダンスを調整するスイッチSW6a,6bと、2進数の複数ビットのデータに応じて信号線対のそれぞれの信号線に流す電流の向きを切り替えるスイッチSW9a,SW9b,SW10a,SW10bとを含む。

【解決手段】情報処理装置1には、2本1組の信号線7a,7bで構成される信号線対7と信号線対7に対して入力された2進数の複数ビットのデータに応じた電圧レベルに設定するためのドライバ2と、信号線対7の他端側に接続され、信号線対7の電圧レベルに応じて2進数の複数ビットのデータに変換するためのレシーバ3とが設けられる。ドライバ2は、信号線対7に電圧を印加するための定電圧源4と、2進数の複数ビットのデータに応じて信号線対の入出力インピーダンスを調整するスイッチSW6a,6bと、2進数の複数ビットのデータに応じて信号線対のそれぞれの信号線に流す電流の向きを切り替えるスイッチSW9a,SW9b,SW10a,SW10bとを含む。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、通信用の配線数が限られる小型の情報処理装置および情報処理装置の制御方法に関する。

【背景技術】

【0002】

従来からデ−タの通信方式として、大きく分けてシリアル通信とパラレル通信とが用いられてきた。パラレル通信は一度に複数のデ−タを通信できるので、シリアル通信に比べて通信に使用するクロック信号の周波数を低く設定できる点等の利点を有している。しかし、パラレル通信には複数の信号線が必要になるため、小型化が必要な機器、特に回転ヒンジなどを通して通信する機器に用いようとした場合に、使用する複数の信号線を接続(配線)できない場合もある。また、接続(配線)する信号線の本数が増えればそれだけコストもかかる。

【0003】

このため、小型化が必要な機器、特に回転ヒンジなどを通して通信する機器に用いる通信方式としては、一般的にシリアル通信が用いられている。シリアル通信すなわちシリアル通信を用いた種々の伝送方式が提案されている(例えば、特許文献1および2)。

【0004】

上記シリアル通信の主なものとしては、1本の信号線のみしか用いないシングルエンド方式に対して、上記シングルエンド方式の問題点をもとに改良された、通常2本1組の信号線を用いるLVDS(小振幅差動信号方式:Low-Voltage Differential Signaling)等の差動シリアル通信方式がある。

【0005】

上記差動シリアル通信方式の上記シングルエンド方式に比較した場合のメリットは、外来ノイズが発生した場合に2本の信号線のそれぞれが外来ノイズの影響を同様にうけることによって、2本の信号線間の電位差自体の変化を抑え、外来ノイズへの耐性を向上させる点にある。

【0006】

また、他のメリットは、2本の信号線をお互い間近に配置、配線することによって、並行して配置された差動シリアル通信方式に用いられる信号線のそれぞれは向きが反対でありながら、流れる電流は同じである平衡な差動線路とすることである。つまり、大きさが等しく反対向きの信号が並行した信号線のそれぞれに流れるため、同心円状の磁力線は打ち消される方向に働き、また同心円状の電気力線は結合するように働き、その結果、外に伝播する電磁界エネルギ−(すなわちノイズ)を非常に小さく抑えられることになる。

【0007】

2本1組の信号線からなる差動シリアル通信では、通信回路が1組のクロックラインと複数組のデ−タラインとで構成され、2本の信号線はそれぞれ「+」、「−」を表し、差動シリアルの入力バッファ(レシーバ)に接続されている。そして、「+」の信号線の電圧レベルが「−」の信号線よりも高い電圧レベルであれば「1」、逆であれば「0」であるとして受信する。すなわち、2本1組のデ−タラインの情報量は1ビットとなる。

【0008】

つまり、デ−タライン1組に対して1ビットのデ−タ量しか表すことができないため、高速にデ−タ通信を行うためには、信号線を速く動作させるか、複数組のデ−タラインを使用する必要がある。

【0009】

信号線を速く動作させるのは、IC自身のプロセスの問題、又は負荷容量等の外部要因などの問題によって困難であり、複数組のデ−タラインを使用するとした場合でも、クロックラインに同期させる必要がある問題、又は信号線の接続本数が増えてしまうためのコストの増加等の問題が生じる。

【0010】

このため、特許文献3では、信号線の電位の高さによって1本の信号線を3通りの状態、つまり3進デ−タ(3進法で表されるデ−タ)で表すデ−タ伝送装置を提案している。

【0011】

すなわち、例えば、2進デ−タ(2進法で表されるデ−タ)を3本の信号線によって送信する場合には信号線3本分の2進デ−タを3進デ−タに変換して2本の信号線によって送信し、受信側は信号線2本分の3進デ−タを信号線3本分の2進デ−タの状態に戻すことによって、物理的に2本の信号線で3本分の情報量を送信する。その結果、一度に送信する情報量を増やすことを可能にしている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開平4−234249号公報

【特許文献2】特開2010−166403号公報

【特許文献3】特開平11−177639号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、上記特許文献3に開示されているデ−タ伝送装置では、信号線の電位が異なる複数の信号線を用いることになる。そのため、流れる電流が同じであり、かつ、反対向きの信号をそれぞれの信号線に生じさせることができない。したがって、シングルエンド方式を用いた通信方式と同様に、信号線自身から発生するノイズが大きくなってしまうという問題がある。

【0014】

本発明は、上記のよううな問題を解決するためのものであって、通信時に発生するノイズを抑制しつつ、高速な通信を可能とする情報処理装置および情報処理装置の制御方法を提供することを目的とする。

【課題を解決するための手段】

【0015】

本発明のある局面に従う情報処理装置は、2本1組の信号線で構成される信号線対と、信号線対の一端側に接続され、信号線対に対して入力された2進数の複数ビットのデータに応じた電圧レベルに設定するためのドライバと、信号線対の他端側に接続され、信号線対の電圧レベルに応じて2進数の複数ビットのデータに変換するためのレシーバとを備える。ドライバは、信号線対に電圧を印加するための定電圧源と、2進数の複数ビットのデータに応じて信号線対の入出力インピーダンスを調整するインピーダンス調整部と、2進数の複数ビットのデータに応じて信号線対のそれぞれの信号線に流す電流の向きを切り替える切替部とを含む。

【0016】

好ましくは、インピーダンス調整部は、定電圧源と信号線対の一方と接続される第1の内部ノードとの間に設けられた第1の抵抗素子と、定電圧源と第1の内部ノードとの間に設けられ、第1の抵抗素子と並列に設けられた第1のスイッチ素子と、固定電圧と信号線対の他方と接続される第2の内部ノードとの間に設けられた第2の抵抗素子と、固定電圧と第2の内部ノードとの間に設けられ、第2の抵抗素子と並列に設けられた第2のスイッチ素子とを有する。第1および第2のスイッチ素子は、2進数の複数ビットのデータに応じて相補的にオン・オフする。

【0017】

特に、切替部は、2進数の複数ビットのデータに応じて、第1および第2の内部ノードと信号線対の一方および他方とそれぞれ接続するための第3および第4のスイッチ素子と、2進数の複数ビットのデータに応じて、第3および第4のスイッチ素子と相補的に動作し、第1および第2の内部ノードと信号線対の他方および一方とそれぞれ接続するための第5および第6のスイッチ素子とを含む。

【0018】

好ましくは、複数ビットは、2ビットである。

好ましくは、レシーバは、信号線対の信号線間の電位差に応じて2進数の複数ビットのうちの一部ビットのデータに変換する電位差識別部と、信号線対の信号線間の中間電圧レベルに従って2進数の複数ビットのうちの残りのビットのデータに変換するコモン信号識別部とを含む。

【0019】

本発明のある局面に従う情報処理装置の制御方法は、2本1組の信号線で構成される信号線対に対して2進数の複数ビットのデータを伝送する情報処理装置の制御方法であって、信号線対に電圧を印加するステップと、2進数の複数ビットのデータに応じて信号線対の入出力インピーダンスを調整するステップと、2進数の複数ビットのデータに応じて信号線対のそれぞれの信号線に流す電流の向きを切り替えるステップと、信号線対の電圧レベルに応じて2進数の複数ビットのデータに変換するステップとを備える。

【発明の効果】

【0020】

本発明に従う情報処理装置には、2本1組の信号線で構成される信号線対と、ドライバと、レシーバとが設けられ、ドライバは、信号線対に電圧を印加するための定電圧源と、2進数の複数ビットのデータに応じて信号線対の入出力インピーダンスを調整するインピーダンス調整部と、2進数の複数ビットのデータに応じて信号線対のそれぞれの信号線に流す電流の向きを切り替える切替部とを含む。したがって、2本1組の信号線対を用いて複数ビットのデータ通信が可能であるとともに、信号線に流れる電流の向きが互いに逆である差動線路を構成するため通信時に発生するノイズを抑制することが可能となる。

【図面の簡単な説明】

【0021】

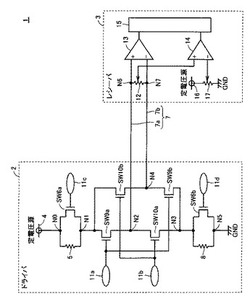

【図1】本発明の実施の形態に従う情報処理装置1の構成について説明する図である。

【図2】本発明の実施の形態に従う信号線7a,7bの電位とコモン電圧ならびに2ビットの情報との関係を説明する図である。

【図3】本発明の実施の形態に従う信号線7a,7bの電位とコモン電圧ならびに2ビットの情報との関係を説明する別の図である。

【発明を実施するための形態】

【0022】

以下、本発明の実施の形態について、図面を参照して説明する。以下の説明では、同一の部品には同一の符号を附してある。それらの名称および機能も同じである。したがって、それらについての詳細な説明は繰返さない。

【0023】

図1は、本発明の実施の形態に従う情報処理装置1の構成について説明する図である。

図1を参照して、本発明の実施の形態に従う情報処理装置1は、信号を送信する側のドライバ2と信号を受信する側のレシーバ(受信装置)3とが設けられた構成である。当該ドライバ2とレシーバ3との間には、2本の信号線を1組とした信号線対7が接続された構成となっている。ここで、2本1組の信号線対7のそれぞれの信号線を信号線7a,7bとする。

【0024】

ドライバ2は、定電圧源4と、上位電位側および下位電位側の抵抗素子(インピ−ダンス成分)5,8と、スイッチSW6a,SW6b,SW9a,SW9b,SW10a,SW10bとを含む。

【0025】

定電圧源4は、ノードN0と電気的に結合される。本例において、定電圧源4は、一例として400mVの電圧を供給する。

【0026】

抵抗素子5は、ノードN0とノード(内部ノード)N1との間に接続される。スイッチSW6aは、抵抗素子5と並列にノードN0とノードN1との間に接続され、抵抗素子5に電流が流れないようにバイパスさせるために設けられる。

【0027】

固定電圧GNDは、ノードN5と電気的に結合される。

抵抗素子8は、ノードN5とノード(内部ノード)N3との間に接続される。スイッチSW6bは、抵抗素子8と並列にノードN5とノードN3との間に接続され、抵抗素子8に電流が流れないようにバイパスさせるために設けられる。

【0028】

本例においては、スイッチSW6a,SW6bとは相補的に動作する。

スイッチSW9aは、ノードN1とノードN2との間に接続され、ゲートに論理回路11aの入力を受ける。

【0029】

スイッチSW10aは、ノードN2とノードN3との間に接続され、ゲートに論理回路11bの入力を受ける。

【0030】

スイッチSW10bは、ノードN1とノードN4との間に接続され、ゲートに論理回路11bの入力を受ける。

【0031】

スイッチSW9bは、ノードN4とノードN3との間に接続され、ゲートに論理回路11aの入力を受ける。

【0032】

ノードN2は、信号線7aと接続される接続ノードである。ノードN4は、信号線7bと接続される接続ノードである。

【0033】

スイッチSW9aとスイッチSW9bとは論理回路11aの入力を受けて動作し、論理回路11aの入力が「H」レベルである場合に、ノードN1とノードN2とを接続する。また、ノードN3とノードN4とを接続する。すなわち、信号線7a,7bとノードN1,N3とをそれぞれ電気的に結合させる。

【0034】

スイッチSW10aとスイッチSW10bとは論理回路11bの入力を受けて動作し、論理回路11bの入力が「H」レベルである場合に、ノードN1とノードN4とを接続する。また、ノードN2とノードN3とを接続する。すなわち、信号線7a,7bとノードN3,N1とをそれぞれ電気的に結合させる。

【0035】

本例においては、スイッチSW9a,SW9bと、スイッチSW10a,10bとは、相補的に動作し、信号線7a,7bに電流を供給する流れを切り替える切替回路として機能する。

【0036】

具体的には、論理回路11aの入力が「H」レベルである場合には、ノードN2が高電位、ノードN4が低電位となって、信号線7aから信号線7bに対して電流が供給される。

【0037】

一方、論理回路11bの入力が「H」レベルである場合には、ノードN2が低電位、ノードN4が高電位となって、信号線7bから信号線7aに対して電流が供給される。

【0038】

論理回路11cによって制御されるスイッチSW6aは、定電圧源4によって印加されるノードN1の電圧レベルを調整するスイッチである。

【0039】

具体的には、スイッチSW6aがONしている場合には、スイッチSW6aがバイパス経路として機能し、ノード(内部ノード)N1は、スイッチSW6a自体のインピーダンス成分(例えば0.1Ω以下)に従って電圧降下した値に設定される。

【0040】

一方、スイッチSW6aをOFFした場合には、抵抗素子5を介してノードN1に電圧が印加されることになる。すなわち、定電圧源4の出力電流は抵抗素子5を通ってノードN1に流れることになる。本例においては、一例として抵抗素子5のインピーダンスは、300Ωとする。そのため、ノード(内部ノード)N1は、抵抗素子5のインピーダンス成分(300Ω)に従って電圧降下した値に設定される。

【0041】

また、同様に、論理回路11dによって制御されるスイッチSW6bは、固定電圧(GND)との電気的な結合を制御してノード(内部ノード)N3の電圧レベルを調整するスイッチである。

【0042】

具体的には、スイッチSW6bがONしている場合には、スイッチSW6bがバイパス経路として機能する。すなわち、スイッチSW6b側に電流が流れる。したがって、ノード(内部ノード)N3は、スイッチSW6b自体のインピーダンス成分(例えば0.1Ω以下)に従う電圧降下分、固定電圧(GND)よりも高い電圧レベルに設定される。

【0043】

一方、スイッチSW6bがOFFしている場合には、抵抗素子8を通って固定電圧(GND)に電流が流れることになる。本例においては、一例として抵抗素子8のインピーダンスは、300Ωとする。そのため、ノード(内部ノード)N3は、抵抗素子8のインピーダンス成分(300Ω)に従う電圧降下分、固定電圧(GND)よりも高い電圧レベルに設定される。

【0044】

次に、レシーバ3の構成について説明する。

レシーバ3は、抵抗素子12と、差動アンプ13,14と、デコーダ15と、定電圧源16と、抵抗素子17とを含む。

【0045】

抵抗素子12は、信号線7aと信号線7bとの間に設けられる。従って、抵抗素子12のインピーダンスに従う電位差が信号線7aと7bとの間に生じる。本例においては、抵抗素子12のインピーダンスは100Ωとする。

【0046】

差動アンプ13は、信号線7a,7bとそれぞれ接続される。具体的には、「+」側の入力端子と信号線7aとが接続され、「−」側の入力端子と信号線7bとが接続され、信号線7a,7bの電位差に応じた信号を出力する。一例として信号線7aが信号線7bよりも電位が高ければ「H」レベルの信号を出力する。一方、信号線7bが信号線7aよりも電位が高ければ「L」レベルの信号を出力する。

【0047】

定電圧源16は、抵抗素子17を介して固定電圧(GND)と接続される。したがって、抵抗素子17には定電流が流れる。抵抗素子17の所定位置と差動アンプ14の「−」側端子とが電気的に接続され、所定位置の調整が可能であるものとする。本例においては、差動アンプ14に入力される電圧レベルをコモン電圧閾値として調節するものとする。本例においては、一例として抵抗素子17のインピーダンスは、400Ωとする。また、定電圧源16は、一例として400mVの電圧を供給する。本例においては、差動アンプ14の「−」側端子と抵抗素子17の中間位置とが接続され、コモン電圧閾値V4は200mVに設定される。

【0048】

差動アンプ14は、抵抗素子12の中間位置と、抵抗素子17の所定位置とそれぞれ接続される。具体的には、「+」側の入力端子と抵抗素子12の中間位置とが接続され、「−」側の入力端子と抵抗素子17の所定位置とが接続され、当該接続位置における電位差に応じた信号を出力する。一例として、「+」側の入力端子が「−」側の入力端子よりも電位が高ければ「H」レベルの信号を出力する。一方、「+」側の入力端子が「−」側の入力端子よりも電位が低ければ「L」レベルの信号を出力する。

【0049】

デコーダ15は、差動アンプ13,14から出力されたそれぞれの信号に基づいて2進数の複数ビット(本例においては2ビット)のデータに変換して出力する。

【0050】

以下、上記の情報処理装置1の通信方式について説明する。

次に、本発明の実施の形態に従う情報処理装置1での通信プロトコルについて説明する。

【0051】

本発明の実施の形態においては、2本1組の信号線対7の電位および電位差を組み合わせた情報を2ビットの値で表現する。

【0052】

一例として、例えば、2本の信号線の電位の中間レベルをコモン電圧とすると、コモン電圧がある一定の電圧レベル(コモン電圧閾値V4)よりも高い電位を示す状態を「1」、低い電位を示す状態を「0」と規定する。本例においては、2ビットのうちの上位ビットの値が対応する。

【0053】

さらに、信号線7aが信号線7bよりも高い電位を示す状態を「1」、低い電位を示す状態を「0」と規定する。本例においては、2ビットのうちの下位ビットの値が対応する。

【0054】

図2は、本発明の実施の形態に従う信号線7a,7bの電位とコモン電圧ならびに2ビットの情報との関係を説明する図である。

【0055】

図2を参照して、本例においては、所定時間毎(例えばt1〜t2)に情報を伝達する場合について説明する。

【0056】

本例においては、一例として、時刻t1〜t9までの期間においてそれぞれ情報を伝達する場合が示されている。

【0057】

時刻t1からの所定時間内において、信号線7aが電圧V1レベルであり、かつ信号線7bが電圧V3レベルである状態は「11」であると規定する。

【0058】

信号線7aと信号線7bとの間の中間電圧であるコモン電圧V2はコモン電圧閾値V4より高い電圧レベルである。したがってコモン電圧V2とコモン閾値電圧V4との間のコモン電位差で表される1ビット情報を「1」とする。

【0059】

また、信号線7aの電圧V1レベルの方が信号線7bの電圧V3レベルよりも高い。したがって2信号線電位差で表される1ビット情報を「1」とする。

【0060】

すなわち、所定時間毎に2ビットの情報を伝達することが可能である。

時刻t2からの所定時間内において、信号線7aが電圧V3レベルであり、かつ、信号線7bが電圧V1レベルである状態は「10」であると規定する。

【0061】

信号線7aと信号線7bとの間の中間電圧であるコモン電圧V2はコモン電圧閾値V4より高い電圧レベルである。したがって、コモン電圧V2とコモン閾値電圧V4との間のコモン電位差であらわされる1ビット情報を「1」とする。

【0062】

また、信号線7bの電圧V1レベルの方が信号線7aの電圧V3レベルよりも高い。したがって2信号線電位差で表される1ビット情報を「0」とする。

【0063】

時刻t3からの所定時間内において、信号線7aが電圧V5レベルであり、かつ、信号線7bが電圧V7レベルである状態は「01」であると規定する。

【0064】

信号線7aと信号線7bとの間の中間電圧であるコモン電圧V6はコモン電圧閾値V4より低い電圧レベルである。したがって、コモン電圧V6とコモン閾値電圧V4との間のコモン電位差で表される1ビット情報を「0」とする。

【0065】

また、信号線7aの電圧V5レベルの方が信号線7bの電圧V7レベルよりも高い。したがって2信号線電位差で表される1ビット情報を「1」とする。

【0066】

時刻t4からの所定時間内において、信号線7aが電圧V7レベルであり、かつ、信号線7bが電圧V5レベルである状態は「00」であると規定する。

【0067】

信号線7aと信号線7bとの間の中間電圧であるコモン電圧V6はコモン電圧閾値V4より低い電圧レベルである。したがって、コモン電圧V6とコモン閾値電圧V4との間のコモン電位差で表される1ビット情報を「0」とする。

【0068】

また、信号線7bの電圧V5レベルの方が信号線7aの電圧V7レベルよりも高い。したがって2信号線電位差で表される1ビット情報を「0」とする。

【0069】

時刻t5,t6,t7,t8からの所定時間内については、それぞれ時刻t1,t2,t3,t4と同様であるのでその詳細な説明は繰り返さない。

【0070】

本例においては一例として、電圧V1は400mV、電圧V2は350mV、電圧V3は300mV、電圧V4は200mV、電圧V5は100mV、電圧V6は50mV、電圧V7は0Vとする。

【0071】

レシーバ3は、当該信号線7a,7bの電位レベルおよび電位差に従って2進数の2ビットの情報にデコードして出力する。

【0072】

本例においては、時刻t1〜t9までの期間において2ビット×8=16ビットの情報を伝達することが可能である。

【0073】

以下、2進数の2ビットの情報に従うドライバ2の動作について説明する。

ドライバ2は、入力される2進数の2ビットの情報が「11」の場合には、信号線7a,7bを電圧V1,V3にそれぞれ設定する。この場合、論理回路11aは、「H」レベルの信号を出力し、論理回路11bは、「L」レベルの信号を出力する。また、論理回路11cは、「H」レベルの信号を出力し、論理回路11dは、「L」レベルの信号を出力する。

【0074】

ドライバ2において、論理回路11cの「H」レベルの信号の入力に応答してスイッチSW6aがオンする。そして、論理回路11aの「H」レベルの信号の入力に応答してスイッチSW9a,SW9bがオンする。一方、スイッチSW6b、スイッチSW10a,SW10bはオフである。

【0075】

当該状態において、定電圧源4から固定電圧GNDまでの電流経路は、定電圧源4〜スイッチSW6a〜スイッチSW9a〜信号線7a〜抵抗素子12〜信号線7b〜スイッチSW9b〜抵抗素子8〜固定電圧GNDとなる。総インピーダンスは、抵抗素子12と抵抗素子8とを加算した400Ωとなる。なお、スイッチSW6a等のインピーダンス成分については値が小さいため省略している。

【0076】

定電圧源4の電圧レベルが400mVであるとすると、流れる電流は1mAである。そして、ノードN2の電圧レベルは400mV、ノードN4の電圧レベルは300mVに設定される。ノードN2とノードN4との間のコモン電圧は350mVに設定される。

【0077】

ドライバ2は、入力される2進数の2ビットの情報が「10」の場合には、信号線7a,7bを電圧V3,V1にそれぞれ設定する。この場合、論理回路11aは、「L」レベルの信号を出力し、論理回路11bは、「H」レベルの信号を出力する。また、論理回路11cは、「H」レベルの信号を出力し、論理回路11dは、「L」レベルの信号を出力する。

【0078】

ドライバ2において、論理回路11cの「H」レベルの信号の入力に応答してスイッチSW6aがオンする。そして、論理回路11bの「H」レベルの信号の入力に応答してスイッチSW10a,SW10bがオンする。一方、スイッチSW6b、スイッチSW9a,SW9bはオフである。

【0079】

当該状態において、定電圧源4から固定電圧GNDまでの電流経路は、定電圧源4〜スイッチSW6a〜スイッチSW10b〜信号線7b〜抵抗素子12〜信号線7a〜スイッチSW10a〜抵抗素子8〜固定電圧GNDとなる。総インピーダンスは、抵抗素子12と抵抗素子8とを加算した400Ωとなる。なお、スイッチSW6a等のインピーダンス成分については値が小さいため省略している。

【0080】

定電圧源4の電圧レベルが400mVであるとすると、流れる電流は1mAである。そして、ノードN4の電圧レベルは400mV、ノードN2の電圧レベルは300mVに設定される。ノードN2とノードN4との間のコモン電圧は350mVに設定される。すなわち、上記の2ビットの情報が「11」の場合と、信号線7a,7bに流れる電流の向きが逆になる。

【0081】

ドライバ2は、入力される2進数の2ビットの情報が「01」の場合には、信号線7a,7bを電圧V5,V7にそれぞれ設定する。この場合、論理回路11aは、「H」レベルの信号を出力し、論理回路11bは、「L」レベルの信号を出力する。また、論理回路11cは、「L」レベルの信号を出力し、論理回路11dは、「H」レベルの信号を出力する。

【0082】

ドライバ2において、論理回路11dの「H」レベルの信号の入力に応答してスイッチSW6bがオンする。そして、論理回路11aの「H」レベルの信号の入力に応答してスイッチSW9a,SW9bがオンする。一方、スイッチSW6a、スイッチSW10a,SW10bはオフである。

【0083】

当該状態において、定電圧源4から固定電圧GNDまでの電流経路は、定電圧源4〜抵抗素子5〜スイッチSW9a〜信号線7a〜抵抗素子12〜信号線7b〜スイッチSW9b〜スイッチSW6b〜固定電圧GNDとなる。総インピーダンスは、抵抗素子12と抵抗素子5とを加算した400Ωとなる。なお、スイッチSW6b等のインピーダンス成分については値が小さいため省略している。

【0084】

定電圧源4の電圧レベルが400mVであるとすると、流れる電流は1mAである。そして、ノードN2の電圧レベルは100mV、ノードN4の電圧レベルは0Vに設定される。ノードN2とノードN4との間のコモン電圧は50mVに設定される。

【0085】

ドライバ2は、入力される2進数の2ビットの情報が「00」の場合には、信号線7a,7bを電圧V7,V5にそれぞれ設定する。この場合、論理回路11aは、「L」レベルの信号を出力し、論理回路11bは、「H」レベルの信号を出力する。また、論理回路11cは、「L」レベルの信号を出力し、論理回路11dは、「H」レベルの信号を出力する。

【0086】

ドライバ2において、論理回路11dの「H」レベルの信号の入力に応答してスイッチSW6bがオンする。そして、論理回路11bの「H」レベルの信号の入力に応答してスイッチSW10a,SW10bがオンする。一方、スイッチSW6a、スイッチSW9a,SW9bはオフである。

【0087】

当該状態において、定電圧源4から固定電圧GNDまでの電流経路は、定電圧源4〜抵抗素子5〜スイッチSW10b〜信号線7b〜抵抗素子12〜信号線7a〜スイッチSW10a〜スイッチSW6b〜固定電圧GNDとなる。総インピーダンスは、抵抗素子12と抵抗素子8とを加算した400Ωとなる。なお、スイッチSW6b等のインピーダンス成分については値が小さいため省略している。

【0088】

定電圧源4の電圧レベルが400mVであるとすると、流れる電流は1mAである。そして、ノードN4の電圧レベルは100mV、ノードN2の電圧レベルは0Vに設定される。ノードN2とノードN4との間のコモン電圧は50mVに設定される。すなわち、上記の2ビットの情報が「01」の場合と、信号線7a,7bに流れる電流の向きが逆になる。

【0089】

レシーバ3は、上述した方式に従って信号線7a,7bの電位差およびコモン電圧に従ってデコードして、2進数の2ビットのデータ(情報)を出力する。

【0090】

具体的には、信号線7a,7bがそれぞれ電圧V1,V3である場合には、信号線7aの電圧V1レベルの方が信号線7bの電圧V3レベルよりも高いため差動アンプ13は「H」レベルを出力する。また、信号線7a,7bの電圧レベルの中間電圧であるコモン電圧V2はコモン電圧閾値V4より高い電圧レベルであるため、差動アンプ14は「H」レベルを出力する。デコーダ15は、差動アンプ13,14からともに「H」レベルの信号を受けて、信号線7aが電圧V1レベルであり、かつ信号線7bが電圧V3レベルである状態であると判定して、情報「11」を出力する。

【0091】

また、信号線7a,7bがそれぞれ電圧V3,V1である場合には、信号線7bの電圧V1レベルの方が信号線7aの電圧V3レベルよりも高いため差動アンプ13は「L」レベルを出力する。また、信号線7a,7bの電圧レベルの中間電圧であるコモン電圧V2はコモン電圧閾値V4より高い電圧レベルであるため、差動アンプ14は「H」レベルを出力する。デコーダ15は、差動アンプ13から「L」レベルの信号、差動アンプ14から「H」レベルの信号を受けて、信号線7aが電圧V3レベルであり、かつ信号線7bが電圧V1レベルである状態であると判定して、情報「10」を出力する。

【0092】

また、信号線7a,7bがそれぞれ電圧V5,V7である場合には、信号線7aの電圧V5レベルの方が信号線7bの電圧V7レベルよりも高いため差動アンプ13は「H」レベルを出力する。また、信号線7a,7bの電圧レベルの中間電圧であるコモン電圧V6はコモン電圧閾値V4より低い電圧レベルであるため、差動アンプ14は「L」レベルを出力する。デコーダ15は、差動アンプ13から「H」レベルの信号を受け、差動アンプ14から「L」レベルの信号を受けて、信号線7aが電圧V5レベルであり、かつ信号線7bが電圧V7レベルである状態であると判定して、情報「01」を出力する。

【0093】

また、信号線7a,7bがそれぞれ電圧V7,V5である場合には、信号線7bの電圧V5レベルの方が信号線7aの電圧V7レベルよりも高いため差動アンプ13は「L」レベルを出力する。また、信号線7a,7bの電圧レベルの中間電圧であるコモン電圧V6はコモン電圧閾値V4より低い電圧レベルであるため、差動アンプ14は「L」レベルを出力する。デコーダ15は、差動アンプ13,14からともに「L」レベルの信号を受けて、信号線7aが電圧V7レベルであり、かつ信号線7bが電圧V5レベルである状態であると判定して、情報「00」を出力する。

【0094】

上述のような回路構成を用いることによって、2進数の複数ビットの情報を2本1組の信号線対を用いて伝送することが可能となる。

【0095】

2本1組の信号線で構成される信号線対7に対して2進数の複数ビットのデータを伝送するための方法としては、ドライバ2において、信号線対7に定電圧源4に従う電圧を印加する。そして、2進数の複数ビットのデータに応じて信号線対7の入出力インピーダンスをスイッチを用いて調整する。また、2進数の複数ビットのデータに応じて信号線対7のそれぞれの信号線に流す電流の向きをスイッチを用いて切り替える。レシーバ3においては、信号線対7の電圧レベルに応じて2進数の複数ビットのデータに変換して出力する。

【0096】

なお、本発明の実施の形態においては、レシーバ3において、上述のような差動アンプを用いて情報を識別する構成を採用しているが、ADコンバ−タを用いて電圧レベルに従って情報を判定して出力するようにしても良い。

【0097】

また、本発明の実施の形態においては、定電圧源を用いた回路構成について説明していいるが、必ずしもこれに限定されず、例えば定電流源を用いた回路構成としてもよい。

【0098】

また、本実施の形態においては、差動アンプ14の+側の入力端子について、抵抗素子12のインピ−ダンス成分の中間付近と接続する構成について説明しているが、必ずしもこれに限定されず、例えば、ノードN2あるいはノードN4と接続する構成としても良い。

【0099】

なお、本例においては、信号線7a,7bの4状態の電位と2進数の2ビットの情報とをそれぞれ関連付けてデータを伝送する方式について説明しており、それぞれの電位状態と情報との組み合わせについては任意の組み合わせに設定することが可能である。

【0100】

本実施の形態においては、レシーバにおいて、2本1組の信号線対を用いて複数ビットの情報を受信することができるため高速な通信を可能としている。また、上述したように差動シリアル通信方式であり、外来ノイズの影響に強く、ノイズ耐性に強い。さらに、2本1組の信号線対について、互いに信号線に流れる電流の向きは反対でありながら、流れる電流は同じである平衡な差動線路とすることが可能である。つまり、大きさが等しく反対向きの信号が並行した信号線のそれぞれに流れるため、同心円状の磁力線は打ち消される方向に働き、また同心円状の電気力線は結合するように働き、その結果、外に伝播する電磁界エネルギー(すなわちノイズ)を非常に小さく抑えられることが可能である。したがって、通信時に発生するノイズ量を抑えながらも、通信経路における信号線の配線数を増やすことなく通信の高速化を実現し得る情報処理装置を実現することが可能である。

【0101】

なお、本例においては、1つの信号線対を用いて2ビットの情報を伝送する方式について説明したがさらに複数本の信号線対を用いてさらに複数ビットの情報を伝送するようにすることも可能である。

【0102】

また、本発明の実施の形態に従う情報処理装置では、2本1組の信号線対のそれぞれの信号線に流す電流の向きを切り替えることによりビット値を表現できる。したがって、電流の量のみによってビット値を表現する場合に比較して2倍のビットの値を表現できるようになる。すなわち、電流の量を半分にしても同じ量のビットの値を表現することが可能となる。よって、電流値を小さくできるので、情報処理装置の消費電力を低減できる。また、電流の量を切り替えてビット値を表現する構成よりも電流の向きを切り替える構成の方が安価な回路で実現できるため情報処理装置のコストを低下させることができる。

【0103】

なお、図2においては、スイッチに対する論理回路11a,11bからの入力信号と、論理回路11c,11dからの入力信号とが同じタイミングで入力される場合について説明した。

【0104】

一方で、当該入力タイミングは同じでなくても良い。すなわち、コモン電圧が変化するスイッチSW6aとスイッチSW6bとの切り替えタイミングと、2本1組の信号線の電位差(電流の向き)が切り替わるスイッチSW9a,SW9bと、スイッチSW10a,SW10bとの切り替えタイミングとが同時でなくても良い。

【0105】

図3は、本発明の実施の形態に従う信号線7a,7bの電位とコモン電圧ならびに2ビットの情報との関係を説明する別の図である。

【0106】

図3を参照して、ここでは、図2と比較して、コモン電圧の切り替え時間と、電流経路の切り替え時間とが異なる場合の例が示されている。

【0107】

具体的には、コモン電圧の切り替えは電流経路の切り替え時間よりも周期が長い場合が示されている。本例においては、時刻t1,t3,t5,t7に切り替えられる場合が示されている。

【0108】

一方で電流経路の切り替えは、所定時間毎(例えばt1〜t2)である。

本例においては、一例として、時刻t1〜t9までの期間においてそれぞれ情報を伝達する場合が示されている。

【0109】

具体的には、時刻t1からの所定時間内において、信号線7aは電圧V1レベルであり、かつ信号線7bは電圧V3レベルである。したがって、2信号線電位差で表される1ビット情報は「1」である。

【0110】

次に、時刻t2からの所定時間内において、信号線7aは電圧V3レベルであり、かつ、信号線7bは電圧V1レベルである。したがって、2信号線電位差で表される1ビット情報は「0」である。

【0111】

また、時刻t1〜t3の期間において、信号線7aと信号線7bとの間の中間電圧であるコモン電圧V2はコモン電圧閾値V4より高い電圧レベルである。したがってコモン電圧V2とコモン閾値電圧V4との間のコモン電位差で表される1ビット情報は「1」である。

【0112】

したがって、時刻t1〜t3の期間において、3ビットの情報を伝達することが可能である。

【0113】

同様に、時刻t3からの所定時間内において、信号線7aは電圧V5レベルであり、かつ、信号線7bは電圧V7レベルである。したがって、2信号線電位差で表される1ビット情報は「1」である。

【0114】

ここで、信号線7bは、電圧V1から電圧V7への遷移となるため当該電圧の遷移時間にある程度の時間が必要となる場合が示されているが、時刻t3と時刻t4との間の時刻t34から時刻t4の期間においては情報に応じた電位差が生じるため当該期間に信号を取り込むことにより情報をデコードして出力することが可能である。

【0115】

また、次に、時刻t4からの所定時間内において、信号線7aは電圧V7レベルであり、かつ、信号線7bは電圧V5レベルである。したがって、2信号線電位差で表される1ビット情報は「0」である。

【0116】

また、時刻t3〜t5の期間において、信号線7aと信号線7bとの間の中間電圧であるコモン電圧V6はコモン電圧閾値V4より低い電圧レベルである。したがって、コモン電圧V6とコモン閾値電圧V4との間のコモン電位差で表される1ビット情報は「0」である。

【0117】

したがって、時刻t3〜t5の期間において、3ビットの情報を伝達することが可能である。

【0118】

時刻t5以降の情報の伝達についても同様の方式により実行される。

本例においては、コモン電圧とコモン閾値電圧との比較に基づく情報の伝達期間を長く設定している。信号線の電圧レベルを例えば電圧V1から電圧V7まで遷移させて安定状態とするまでには時間がかかる可能性がある。すなわち、コモン電圧が安定するまでに時間がかかる可能性がある。所定時間毎に情報を伝達させる場合に当該所定時間の期間が短い場合には、高速に電圧レベルを設定する必要があるが、遷移期間が長いとコモン閾値電圧との比較による情報である正しいデコード結果を得ることができない。

【0119】

したがって、本例においては、コモン電圧の切り替えに従って情報を伝達する場合において安定して情報を伝達するために所定期間の2倍の期間を確保して、情報を伝達する方式としている。

【0120】

本例においては、時刻t1〜t9までの期間において3ビット×4=12ビットの情報を伝達することが可能である。

【0121】

本例では、コモン電圧の切り替え期間が、2本1組の信号線の電位差の切り替え期間よりも長くなっているため、より安定しノイズの少ない差動シリアル通信環境となる。

【0122】

以上のように、本発明の情報処理装置は、通信時に発生するノイズ量を抑えながらも、通信経路における信号線の配線数を増やすことなく通信の高速化を実現し得る情報処理装置を提供する。したがって、本発明は、シリアル通信インタ−フェ−スを用いる携帯機器等に関連した産業分野に好適に用いることができる。

【0123】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0124】

1 情報処理装置、2 ドライバ、3 レシーバ、4 定電圧源、5,8,12,17 抵抗素子、7 信号線対、7a,7b 信号線、11a,11b,11c,11d 論理回路、13,14 差動アンプ、15 デコーダ。

【技術分野】

【0001】

この発明は、通信用の配線数が限られる小型の情報処理装置および情報処理装置の制御方法に関する。

【背景技術】

【0002】

従来からデ−タの通信方式として、大きく分けてシリアル通信とパラレル通信とが用いられてきた。パラレル通信は一度に複数のデ−タを通信できるので、シリアル通信に比べて通信に使用するクロック信号の周波数を低く設定できる点等の利点を有している。しかし、パラレル通信には複数の信号線が必要になるため、小型化が必要な機器、特に回転ヒンジなどを通して通信する機器に用いようとした場合に、使用する複数の信号線を接続(配線)できない場合もある。また、接続(配線)する信号線の本数が増えればそれだけコストもかかる。

【0003】

このため、小型化が必要な機器、特に回転ヒンジなどを通して通信する機器に用いる通信方式としては、一般的にシリアル通信が用いられている。シリアル通信すなわちシリアル通信を用いた種々の伝送方式が提案されている(例えば、特許文献1および2)。

【0004】

上記シリアル通信の主なものとしては、1本の信号線のみしか用いないシングルエンド方式に対して、上記シングルエンド方式の問題点をもとに改良された、通常2本1組の信号線を用いるLVDS(小振幅差動信号方式:Low-Voltage Differential Signaling)等の差動シリアル通信方式がある。

【0005】

上記差動シリアル通信方式の上記シングルエンド方式に比較した場合のメリットは、外来ノイズが発生した場合に2本の信号線のそれぞれが外来ノイズの影響を同様にうけることによって、2本の信号線間の電位差自体の変化を抑え、外来ノイズへの耐性を向上させる点にある。

【0006】

また、他のメリットは、2本の信号線をお互い間近に配置、配線することによって、並行して配置された差動シリアル通信方式に用いられる信号線のそれぞれは向きが反対でありながら、流れる電流は同じである平衡な差動線路とすることである。つまり、大きさが等しく反対向きの信号が並行した信号線のそれぞれに流れるため、同心円状の磁力線は打ち消される方向に働き、また同心円状の電気力線は結合するように働き、その結果、外に伝播する電磁界エネルギ−(すなわちノイズ)を非常に小さく抑えられることになる。

【0007】

2本1組の信号線からなる差動シリアル通信では、通信回路が1組のクロックラインと複数組のデ−タラインとで構成され、2本の信号線はそれぞれ「+」、「−」を表し、差動シリアルの入力バッファ(レシーバ)に接続されている。そして、「+」の信号線の電圧レベルが「−」の信号線よりも高い電圧レベルであれば「1」、逆であれば「0」であるとして受信する。すなわち、2本1組のデ−タラインの情報量は1ビットとなる。

【0008】

つまり、デ−タライン1組に対して1ビットのデ−タ量しか表すことができないため、高速にデ−タ通信を行うためには、信号線を速く動作させるか、複数組のデ−タラインを使用する必要がある。

【0009】

信号線を速く動作させるのは、IC自身のプロセスの問題、又は負荷容量等の外部要因などの問題によって困難であり、複数組のデ−タラインを使用するとした場合でも、クロックラインに同期させる必要がある問題、又は信号線の接続本数が増えてしまうためのコストの増加等の問題が生じる。

【0010】

このため、特許文献3では、信号線の電位の高さによって1本の信号線を3通りの状態、つまり3進デ−タ(3進法で表されるデ−タ)で表すデ−タ伝送装置を提案している。

【0011】

すなわち、例えば、2進デ−タ(2進法で表されるデ−タ)を3本の信号線によって送信する場合には信号線3本分の2進デ−タを3進デ−タに変換して2本の信号線によって送信し、受信側は信号線2本分の3進デ−タを信号線3本分の2進デ−タの状態に戻すことによって、物理的に2本の信号線で3本分の情報量を送信する。その結果、一度に送信する情報量を増やすことを可能にしている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開平4−234249号公報

【特許文献2】特開2010−166403号公報

【特許文献3】特開平11−177639号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、上記特許文献3に開示されているデ−タ伝送装置では、信号線の電位が異なる複数の信号線を用いることになる。そのため、流れる電流が同じであり、かつ、反対向きの信号をそれぞれの信号線に生じさせることができない。したがって、シングルエンド方式を用いた通信方式と同様に、信号線自身から発生するノイズが大きくなってしまうという問題がある。

【0014】

本発明は、上記のよううな問題を解決するためのものであって、通信時に発生するノイズを抑制しつつ、高速な通信を可能とする情報処理装置および情報処理装置の制御方法を提供することを目的とする。

【課題を解決するための手段】

【0015】

本発明のある局面に従う情報処理装置は、2本1組の信号線で構成される信号線対と、信号線対の一端側に接続され、信号線対に対して入力された2進数の複数ビットのデータに応じた電圧レベルに設定するためのドライバと、信号線対の他端側に接続され、信号線対の電圧レベルに応じて2進数の複数ビットのデータに変換するためのレシーバとを備える。ドライバは、信号線対に電圧を印加するための定電圧源と、2進数の複数ビットのデータに応じて信号線対の入出力インピーダンスを調整するインピーダンス調整部と、2進数の複数ビットのデータに応じて信号線対のそれぞれの信号線に流す電流の向きを切り替える切替部とを含む。

【0016】

好ましくは、インピーダンス調整部は、定電圧源と信号線対の一方と接続される第1の内部ノードとの間に設けられた第1の抵抗素子と、定電圧源と第1の内部ノードとの間に設けられ、第1の抵抗素子と並列に設けられた第1のスイッチ素子と、固定電圧と信号線対の他方と接続される第2の内部ノードとの間に設けられた第2の抵抗素子と、固定電圧と第2の内部ノードとの間に設けられ、第2の抵抗素子と並列に設けられた第2のスイッチ素子とを有する。第1および第2のスイッチ素子は、2進数の複数ビットのデータに応じて相補的にオン・オフする。

【0017】

特に、切替部は、2進数の複数ビットのデータに応じて、第1および第2の内部ノードと信号線対の一方および他方とそれぞれ接続するための第3および第4のスイッチ素子と、2進数の複数ビットのデータに応じて、第3および第4のスイッチ素子と相補的に動作し、第1および第2の内部ノードと信号線対の他方および一方とそれぞれ接続するための第5および第6のスイッチ素子とを含む。

【0018】

好ましくは、複数ビットは、2ビットである。

好ましくは、レシーバは、信号線対の信号線間の電位差に応じて2進数の複数ビットのうちの一部ビットのデータに変換する電位差識別部と、信号線対の信号線間の中間電圧レベルに従って2進数の複数ビットのうちの残りのビットのデータに変換するコモン信号識別部とを含む。

【0019】

本発明のある局面に従う情報処理装置の制御方法は、2本1組の信号線で構成される信号線対に対して2進数の複数ビットのデータを伝送する情報処理装置の制御方法であって、信号線対に電圧を印加するステップと、2進数の複数ビットのデータに応じて信号線対の入出力インピーダンスを調整するステップと、2進数の複数ビットのデータに応じて信号線対のそれぞれの信号線に流す電流の向きを切り替えるステップと、信号線対の電圧レベルに応じて2進数の複数ビットのデータに変換するステップとを備える。

【発明の効果】

【0020】

本発明に従う情報処理装置には、2本1組の信号線で構成される信号線対と、ドライバと、レシーバとが設けられ、ドライバは、信号線対に電圧を印加するための定電圧源と、2進数の複数ビットのデータに応じて信号線対の入出力インピーダンスを調整するインピーダンス調整部と、2進数の複数ビットのデータに応じて信号線対のそれぞれの信号線に流す電流の向きを切り替える切替部とを含む。したがって、2本1組の信号線対を用いて複数ビットのデータ通信が可能であるとともに、信号線に流れる電流の向きが互いに逆である差動線路を構成するため通信時に発生するノイズを抑制することが可能となる。

【図面の簡単な説明】

【0021】

【図1】本発明の実施の形態に従う情報処理装置1の構成について説明する図である。

【図2】本発明の実施の形態に従う信号線7a,7bの電位とコモン電圧ならびに2ビットの情報との関係を説明する図である。

【図3】本発明の実施の形態に従う信号線7a,7bの電位とコモン電圧ならびに2ビットの情報との関係を説明する別の図である。

【発明を実施するための形態】

【0022】

以下、本発明の実施の形態について、図面を参照して説明する。以下の説明では、同一の部品には同一の符号を附してある。それらの名称および機能も同じである。したがって、それらについての詳細な説明は繰返さない。

【0023】

図1は、本発明の実施の形態に従う情報処理装置1の構成について説明する図である。

図1を参照して、本発明の実施の形態に従う情報処理装置1は、信号を送信する側のドライバ2と信号を受信する側のレシーバ(受信装置)3とが設けられた構成である。当該ドライバ2とレシーバ3との間には、2本の信号線を1組とした信号線対7が接続された構成となっている。ここで、2本1組の信号線対7のそれぞれの信号線を信号線7a,7bとする。

【0024】

ドライバ2は、定電圧源4と、上位電位側および下位電位側の抵抗素子(インピ−ダンス成分)5,8と、スイッチSW6a,SW6b,SW9a,SW9b,SW10a,SW10bとを含む。

【0025】

定電圧源4は、ノードN0と電気的に結合される。本例において、定電圧源4は、一例として400mVの電圧を供給する。

【0026】

抵抗素子5は、ノードN0とノード(内部ノード)N1との間に接続される。スイッチSW6aは、抵抗素子5と並列にノードN0とノードN1との間に接続され、抵抗素子5に電流が流れないようにバイパスさせるために設けられる。

【0027】

固定電圧GNDは、ノードN5と電気的に結合される。

抵抗素子8は、ノードN5とノード(内部ノード)N3との間に接続される。スイッチSW6bは、抵抗素子8と並列にノードN5とノードN3との間に接続され、抵抗素子8に電流が流れないようにバイパスさせるために設けられる。

【0028】

本例においては、スイッチSW6a,SW6bとは相補的に動作する。

スイッチSW9aは、ノードN1とノードN2との間に接続され、ゲートに論理回路11aの入力を受ける。

【0029】

スイッチSW10aは、ノードN2とノードN3との間に接続され、ゲートに論理回路11bの入力を受ける。

【0030】

スイッチSW10bは、ノードN1とノードN4との間に接続され、ゲートに論理回路11bの入力を受ける。

【0031】

スイッチSW9bは、ノードN4とノードN3との間に接続され、ゲートに論理回路11aの入力を受ける。

【0032】

ノードN2は、信号線7aと接続される接続ノードである。ノードN4は、信号線7bと接続される接続ノードである。

【0033】

スイッチSW9aとスイッチSW9bとは論理回路11aの入力を受けて動作し、論理回路11aの入力が「H」レベルである場合に、ノードN1とノードN2とを接続する。また、ノードN3とノードN4とを接続する。すなわち、信号線7a,7bとノードN1,N3とをそれぞれ電気的に結合させる。

【0034】

スイッチSW10aとスイッチSW10bとは論理回路11bの入力を受けて動作し、論理回路11bの入力が「H」レベルである場合に、ノードN1とノードN4とを接続する。また、ノードN2とノードN3とを接続する。すなわち、信号線7a,7bとノードN3,N1とをそれぞれ電気的に結合させる。

【0035】

本例においては、スイッチSW9a,SW9bと、スイッチSW10a,10bとは、相補的に動作し、信号線7a,7bに電流を供給する流れを切り替える切替回路として機能する。

【0036】

具体的には、論理回路11aの入力が「H」レベルである場合には、ノードN2が高電位、ノードN4が低電位となって、信号線7aから信号線7bに対して電流が供給される。

【0037】

一方、論理回路11bの入力が「H」レベルである場合には、ノードN2が低電位、ノードN4が高電位となって、信号線7bから信号線7aに対して電流が供給される。

【0038】

論理回路11cによって制御されるスイッチSW6aは、定電圧源4によって印加されるノードN1の電圧レベルを調整するスイッチである。

【0039】

具体的には、スイッチSW6aがONしている場合には、スイッチSW6aがバイパス経路として機能し、ノード(内部ノード)N1は、スイッチSW6a自体のインピーダンス成分(例えば0.1Ω以下)に従って電圧降下した値に設定される。

【0040】

一方、スイッチSW6aをOFFした場合には、抵抗素子5を介してノードN1に電圧が印加されることになる。すなわち、定電圧源4の出力電流は抵抗素子5を通ってノードN1に流れることになる。本例においては、一例として抵抗素子5のインピーダンスは、300Ωとする。そのため、ノード(内部ノード)N1は、抵抗素子5のインピーダンス成分(300Ω)に従って電圧降下した値に設定される。

【0041】

また、同様に、論理回路11dによって制御されるスイッチSW6bは、固定電圧(GND)との電気的な結合を制御してノード(内部ノード)N3の電圧レベルを調整するスイッチである。

【0042】

具体的には、スイッチSW6bがONしている場合には、スイッチSW6bがバイパス経路として機能する。すなわち、スイッチSW6b側に電流が流れる。したがって、ノード(内部ノード)N3は、スイッチSW6b自体のインピーダンス成分(例えば0.1Ω以下)に従う電圧降下分、固定電圧(GND)よりも高い電圧レベルに設定される。

【0043】

一方、スイッチSW6bがOFFしている場合には、抵抗素子8を通って固定電圧(GND)に電流が流れることになる。本例においては、一例として抵抗素子8のインピーダンスは、300Ωとする。そのため、ノード(内部ノード)N3は、抵抗素子8のインピーダンス成分(300Ω)に従う電圧降下分、固定電圧(GND)よりも高い電圧レベルに設定される。

【0044】

次に、レシーバ3の構成について説明する。

レシーバ3は、抵抗素子12と、差動アンプ13,14と、デコーダ15と、定電圧源16と、抵抗素子17とを含む。

【0045】

抵抗素子12は、信号線7aと信号線7bとの間に設けられる。従って、抵抗素子12のインピーダンスに従う電位差が信号線7aと7bとの間に生じる。本例においては、抵抗素子12のインピーダンスは100Ωとする。

【0046】

差動アンプ13は、信号線7a,7bとそれぞれ接続される。具体的には、「+」側の入力端子と信号線7aとが接続され、「−」側の入力端子と信号線7bとが接続され、信号線7a,7bの電位差に応じた信号を出力する。一例として信号線7aが信号線7bよりも電位が高ければ「H」レベルの信号を出力する。一方、信号線7bが信号線7aよりも電位が高ければ「L」レベルの信号を出力する。

【0047】

定電圧源16は、抵抗素子17を介して固定電圧(GND)と接続される。したがって、抵抗素子17には定電流が流れる。抵抗素子17の所定位置と差動アンプ14の「−」側端子とが電気的に接続され、所定位置の調整が可能であるものとする。本例においては、差動アンプ14に入力される電圧レベルをコモン電圧閾値として調節するものとする。本例においては、一例として抵抗素子17のインピーダンスは、400Ωとする。また、定電圧源16は、一例として400mVの電圧を供給する。本例においては、差動アンプ14の「−」側端子と抵抗素子17の中間位置とが接続され、コモン電圧閾値V4は200mVに設定される。

【0048】

差動アンプ14は、抵抗素子12の中間位置と、抵抗素子17の所定位置とそれぞれ接続される。具体的には、「+」側の入力端子と抵抗素子12の中間位置とが接続され、「−」側の入力端子と抵抗素子17の所定位置とが接続され、当該接続位置における電位差に応じた信号を出力する。一例として、「+」側の入力端子が「−」側の入力端子よりも電位が高ければ「H」レベルの信号を出力する。一方、「+」側の入力端子が「−」側の入力端子よりも電位が低ければ「L」レベルの信号を出力する。

【0049】

デコーダ15は、差動アンプ13,14から出力されたそれぞれの信号に基づいて2進数の複数ビット(本例においては2ビット)のデータに変換して出力する。

【0050】

以下、上記の情報処理装置1の通信方式について説明する。

次に、本発明の実施の形態に従う情報処理装置1での通信プロトコルについて説明する。

【0051】

本発明の実施の形態においては、2本1組の信号線対7の電位および電位差を組み合わせた情報を2ビットの値で表現する。

【0052】

一例として、例えば、2本の信号線の電位の中間レベルをコモン電圧とすると、コモン電圧がある一定の電圧レベル(コモン電圧閾値V4)よりも高い電位を示す状態を「1」、低い電位を示す状態を「0」と規定する。本例においては、2ビットのうちの上位ビットの値が対応する。

【0053】

さらに、信号線7aが信号線7bよりも高い電位を示す状態を「1」、低い電位を示す状態を「0」と規定する。本例においては、2ビットのうちの下位ビットの値が対応する。

【0054】

図2は、本発明の実施の形態に従う信号線7a,7bの電位とコモン電圧ならびに2ビットの情報との関係を説明する図である。

【0055】

図2を参照して、本例においては、所定時間毎(例えばt1〜t2)に情報を伝達する場合について説明する。

【0056】

本例においては、一例として、時刻t1〜t9までの期間においてそれぞれ情報を伝達する場合が示されている。

【0057】

時刻t1からの所定時間内において、信号線7aが電圧V1レベルであり、かつ信号線7bが電圧V3レベルである状態は「11」であると規定する。

【0058】

信号線7aと信号線7bとの間の中間電圧であるコモン電圧V2はコモン電圧閾値V4より高い電圧レベルである。したがってコモン電圧V2とコモン閾値電圧V4との間のコモン電位差で表される1ビット情報を「1」とする。

【0059】

また、信号線7aの電圧V1レベルの方が信号線7bの電圧V3レベルよりも高い。したがって2信号線電位差で表される1ビット情報を「1」とする。

【0060】

すなわち、所定時間毎に2ビットの情報を伝達することが可能である。

時刻t2からの所定時間内において、信号線7aが電圧V3レベルであり、かつ、信号線7bが電圧V1レベルである状態は「10」であると規定する。

【0061】

信号線7aと信号線7bとの間の中間電圧であるコモン電圧V2はコモン電圧閾値V4より高い電圧レベルである。したがって、コモン電圧V2とコモン閾値電圧V4との間のコモン電位差であらわされる1ビット情報を「1」とする。

【0062】

また、信号線7bの電圧V1レベルの方が信号線7aの電圧V3レベルよりも高い。したがって2信号線電位差で表される1ビット情報を「0」とする。

【0063】

時刻t3からの所定時間内において、信号線7aが電圧V5レベルであり、かつ、信号線7bが電圧V7レベルである状態は「01」であると規定する。

【0064】

信号線7aと信号線7bとの間の中間電圧であるコモン電圧V6はコモン電圧閾値V4より低い電圧レベルである。したがって、コモン電圧V6とコモン閾値電圧V4との間のコモン電位差で表される1ビット情報を「0」とする。

【0065】

また、信号線7aの電圧V5レベルの方が信号線7bの電圧V7レベルよりも高い。したがって2信号線電位差で表される1ビット情報を「1」とする。

【0066】

時刻t4からの所定時間内において、信号線7aが電圧V7レベルであり、かつ、信号線7bが電圧V5レベルである状態は「00」であると規定する。

【0067】

信号線7aと信号線7bとの間の中間電圧であるコモン電圧V6はコモン電圧閾値V4より低い電圧レベルである。したがって、コモン電圧V6とコモン閾値電圧V4との間のコモン電位差で表される1ビット情報を「0」とする。

【0068】

また、信号線7bの電圧V5レベルの方が信号線7aの電圧V7レベルよりも高い。したがって2信号線電位差で表される1ビット情報を「0」とする。

【0069】

時刻t5,t6,t7,t8からの所定時間内については、それぞれ時刻t1,t2,t3,t4と同様であるのでその詳細な説明は繰り返さない。

【0070】

本例においては一例として、電圧V1は400mV、電圧V2は350mV、電圧V3は300mV、電圧V4は200mV、電圧V5は100mV、電圧V6は50mV、電圧V7は0Vとする。

【0071】

レシーバ3は、当該信号線7a,7bの電位レベルおよび電位差に従って2進数の2ビットの情報にデコードして出力する。

【0072】

本例においては、時刻t1〜t9までの期間において2ビット×8=16ビットの情報を伝達することが可能である。

【0073】

以下、2進数の2ビットの情報に従うドライバ2の動作について説明する。

ドライバ2は、入力される2進数の2ビットの情報が「11」の場合には、信号線7a,7bを電圧V1,V3にそれぞれ設定する。この場合、論理回路11aは、「H」レベルの信号を出力し、論理回路11bは、「L」レベルの信号を出力する。また、論理回路11cは、「H」レベルの信号を出力し、論理回路11dは、「L」レベルの信号を出力する。

【0074】

ドライバ2において、論理回路11cの「H」レベルの信号の入力に応答してスイッチSW6aがオンする。そして、論理回路11aの「H」レベルの信号の入力に応答してスイッチSW9a,SW9bがオンする。一方、スイッチSW6b、スイッチSW10a,SW10bはオフである。

【0075】

当該状態において、定電圧源4から固定電圧GNDまでの電流経路は、定電圧源4〜スイッチSW6a〜スイッチSW9a〜信号線7a〜抵抗素子12〜信号線7b〜スイッチSW9b〜抵抗素子8〜固定電圧GNDとなる。総インピーダンスは、抵抗素子12と抵抗素子8とを加算した400Ωとなる。なお、スイッチSW6a等のインピーダンス成分については値が小さいため省略している。

【0076】

定電圧源4の電圧レベルが400mVであるとすると、流れる電流は1mAである。そして、ノードN2の電圧レベルは400mV、ノードN4の電圧レベルは300mVに設定される。ノードN2とノードN4との間のコモン電圧は350mVに設定される。

【0077】

ドライバ2は、入力される2進数の2ビットの情報が「10」の場合には、信号線7a,7bを電圧V3,V1にそれぞれ設定する。この場合、論理回路11aは、「L」レベルの信号を出力し、論理回路11bは、「H」レベルの信号を出力する。また、論理回路11cは、「H」レベルの信号を出力し、論理回路11dは、「L」レベルの信号を出力する。

【0078】

ドライバ2において、論理回路11cの「H」レベルの信号の入力に応答してスイッチSW6aがオンする。そして、論理回路11bの「H」レベルの信号の入力に応答してスイッチSW10a,SW10bがオンする。一方、スイッチSW6b、スイッチSW9a,SW9bはオフである。

【0079】

当該状態において、定電圧源4から固定電圧GNDまでの電流経路は、定電圧源4〜スイッチSW6a〜スイッチSW10b〜信号線7b〜抵抗素子12〜信号線7a〜スイッチSW10a〜抵抗素子8〜固定電圧GNDとなる。総インピーダンスは、抵抗素子12と抵抗素子8とを加算した400Ωとなる。なお、スイッチSW6a等のインピーダンス成分については値が小さいため省略している。

【0080】

定電圧源4の電圧レベルが400mVであるとすると、流れる電流は1mAである。そして、ノードN4の電圧レベルは400mV、ノードN2の電圧レベルは300mVに設定される。ノードN2とノードN4との間のコモン電圧は350mVに設定される。すなわち、上記の2ビットの情報が「11」の場合と、信号線7a,7bに流れる電流の向きが逆になる。

【0081】

ドライバ2は、入力される2進数の2ビットの情報が「01」の場合には、信号線7a,7bを電圧V5,V7にそれぞれ設定する。この場合、論理回路11aは、「H」レベルの信号を出力し、論理回路11bは、「L」レベルの信号を出力する。また、論理回路11cは、「L」レベルの信号を出力し、論理回路11dは、「H」レベルの信号を出力する。

【0082】

ドライバ2において、論理回路11dの「H」レベルの信号の入力に応答してスイッチSW6bがオンする。そして、論理回路11aの「H」レベルの信号の入力に応答してスイッチSW9a,SW9bがオンする。一方、スイッチSW6a、スイッチSW10a,SW10bはオフである。

【0083】

当該状態において、定電圧源4から固定電圧GNDまでの電流経路は、定電圧源4〜抵抗素子5〜スイッチSW9a〜信号線7a〜抵抗素子12〜信号線7b〜スイッチSW9b〜スイッチSW6b〜固定電圧GNDとなる。総インピーダンスは、抵抗素子12と抵抗素子5とを加算した400Ωとなる。なお、スイッチSW6b等のインピーダンス成分については値が小さいため省略している。

【0084】

定電圧源4の電圧レベルが400mVであるとすると、流れる電流は1mAである。そして、ノードN2の電圧レベルは100mV、ノードN4の電圧レベルは0Vに設定される。ノードN2とノードN4との間のコモン電圧は50mVに設定される。

【0085】

ドライバ2は、入力される2進数の2ビットの情報が「00」の場合には、信号線7a,7bを電圧V7,V5にそれぞれ設定する。この場合、論理回路11aは、「L」レベルの信号を出力し、論理回路11bは、「H」レベルの信号を出力する。また、論理回路11cは、「L」レベルの信号を出力し、論理回路11dは、「H」レベルの信号を出力する。

【0086】

ドライバ2において、論理回路11dの「H」レベルの信号の入力に応答してスイッチSW6bがオンする。そして、論理回路11bの「H」レベルの信号の入力に応答してスイッチSW10a,SW10bがオンする。一方、スイッチSW6a、スイッチSW9a,SW9bはオフである。

【0087】

当該状態において、定電圧源4から固定電圧GNDまでの電流経路は、定電圧源4〜抵抗素子5〜スイッチSW10b〜信号線7b〜抵抗素子12〜信号線7a〜スイッチSW10a〜スイッチSW6b〜固定電圧GNDとなる。総インピーダンスは、抵抗素子12と抵抗素子8とを加算した400Ωとなる。なお、スイッチSW6b等のインピーダンス成分については値が小さいため省略している。

【0088】

定電圧源4の電圧レベルが400mVであるとすると、流れる電流は1mAである。そして、ノードN4の電圧レベルは100mV、ノードN2の電圧レベルは0Vに設定される。ノードN2とノードN4との間のコモン電圧は50mVに設定される。すなわち、上記の2ビットの情報が「01」の場合と、信号線7a,7bに流れる電流の向きが逆になる。

【0089】

レシーバ3は、上述した方式に従って信号線7a,7bの電位差およびコモン電圧に従ってデコードして、2進数の2ビットのデータ(情報)を出力する。

【0090】

具体的には、信号線7a,7bがそれぞれ電圧V1,V3である場合には、信号線7aの電圧V1レベルの方が信号線7bの電圧V3レベルよりも高いため差動アンプ13は「H」レベルを出力する。また、信号線7a,7bの電圧レベルの中間電圧であるコモン電圧V2はコモン電圧閾値V4より高い電圧レベルであるため、差動アンプ14は「H」レベルを出力する。デコーダ15は、差動アンプ13,14からともに「H」レベルの信号を受けて、信号線7aが電圧V1レベルであり、かつ信号線7bが電圧V3レベルである状態であると判定して、情報「11」を出力する。

【0091】

また、信号線7a,7bがそれぞれ電圧V3,V1である場合には、信号線7bの電圧V1レベルの方が信号線7aの電圧V3レベルよりも高いため差動アンプ13は「L」レベルを出力する。また、信号線7a,7bの電圧レベルの中間電圧であるコモン電圧V2はコモン電圧閾値V4より高い電圧レベルであるため、差動アンプ14は「H」レベルを出力する。デコーダ15は、差動アンプ13から「L」レベルの信号、差動アンプ14から「H」レベルの信号を受けて、信号線7aが電圧V3レベルであり、かつ信号線7bが電圧V1レベルである状態であると判定して、情報「10」を出力する。

【0092】

また、信号線7a,7bがそれぞれ電圧V5,V7である場合には、信号線7aの電圧V5レベルの方が信号線7bの電圧V7レベルよりも高いため差動アンプ13は「H」レベルを出力する。また、信号線7a,7bの電圧レベルの中間電圧であるコモン電圧V6はコモン電圧閾値V4より低い電圧レベルであるため、差動アンプ14は「L」レベルを出力する。デコーダ15は、差動アンプ13から「H」レベルの信号を受け、差動アンプ14から「L」レベルの信号を受けて、信号線7aが電圧V5レベルであり、かつ信号線7bが電圧V7レベルである状態であると判定して、情報「01」を出力する。

【0093】

また、信号線7a,7bがそれぞれ電圧V7,V5である場合には、信号線7bの電圧V5レベルの方が信号線7aの電圧V7レベルよりも高いため差動アンプ13は「L」レベルを出力する。また、信号線7a,7bの電圧レベルの中間電圧であるコモン電圧V6はコモン電圧閾値V4より低い電圧レベルであるため、差動アンプ14は「L」レベルを出力する。デコーダ15は、差動アンプ13,14からともに「L」レベルの信号を受けて、信号線7aが電圧V7レベルであり、かつ信号線7bが電圧V5レベルである状態であると判定して、情報「00」を出力する。

【0094】

上述のような回路構成を用いることによって、2進数の複数ビットの情報を2本1組の信号線対を用いて伝送することが可能となる。

【0095】

2本1組の信号線で構成される信号線対7に対して2進数の複数ビットのデータを伝送するための方法としては、ドライバ2において、信号線対7に定電圧源4に従う電圧を印加する。そして、2進数の複数ビットのデータに応じて信号線対7の入出力インピーダンスをスイッチを用いて調整する。また、2進数の複数ビットのデータに応じて信号線対7のそれぞれの信号線に流す電流の向きをスイッチを用いて切り替える。レシーバ3においては、信号線対7の電圧レベルに応じて2進数の複数ビットのデータに変換して出力する。

【0096】

なお、本発明の実施の形態においては、レシーバ3において、上述のような差動アンプを用いて情報を識別する構成を採用しているが、ADコンバ−タを用いて電圧レベルに従って情報を判定して出力するようにしても良い。

【0097】

また、本発明の実施の形態においては、定電圧源を用いた回路構成について説明していいるが、必ずしもこれに限定されず、例えば定電流源を用いた回路構成としてもよい。

【0098】

また、本実施の形態においては、差動アンプ14の+側の入力端子について、抵抗素子12のインピ−ダンス成分の中間付近と接続する構成について説明しているが、必ずしもこれに限定されず、例えば、ノードN2あるいはノードN4と接続する構成としても良い。

【0099】

なお、本例においては、信号線7a,7bの4状態の電位と2進数の2ビットの情報とをそれぞれ関連付けてデータを伝送する方式について説明しており、それぞれの電位状態と情報との組み合わせについては任意の組み合わせに設定することが可能である。

【0100】

本実施の形態においては、レシーバにおいて、2本1組の信号線対を用いて複数ビットの情報を受信することができるため高速な通信を可能としている。また、上述したように差動シリアル通信方式であり、外来ノイズの影響に強く、ノイズ耐性に強い。さらに、2本1組の信号線対について、互いに信号線に流れる電流の向きは反対でありながら、流れる電流は同じである平衡な差動線路とすることが可能である。つまり、大きさが等しく反対向きの信号が並行した信号線のそれぞれに流れるため、同心円状の磁力線は打ち消される方向に働き、また同心円状の電気力線は結合するように働き、その結果、外に伝播する電磁界エネルギー(すなわちノイズ)を非常に小さく抑えられることが可能である。したがって、通信時に発生するノイズ量を抑えながらも、通信経路における信号線の配線数を増やすことなく通信の高速化を実現し得る情報処理装置を実現することが可能である。

【0101】

なお、本例においては、1つの信号線対を用いて2ビットの情報を伝送する方式について説明したがさらに複数本の信号線対を用いてさらに複数ビットの情報を伝送するようにすることも可能である。

【0102】

また、本発明の実施の形態に従う情報処理装置では、2本1組の信号線対のそれぞれの信号線に流す電流の向きを切り替えることによりビット値を表現できる。したがって、電流の量のみによってビット値を表現する場合に比較して2倍のビットの値を表現できるようになる。すなわち、電流の量を半分にしても同じ量のビットの値を表現することが可能となる。よって、電流値を小さくできるので、情報処理装置の消費電力を低減できる。また、電流の量を切り替えてビット値を表現する構成よりも電流の向きを切り替える構成の方が安価な回路で実現できるため情報処理装置のコストを低下させることができる。

【0103】

なお、図2においては、スイッチに対する論理回路11a,11bからの入力信号と、論理回路11c,11dからの入力信号とが同じタイミングで入力される場合について説明した。

【0104】

一方で、当該入力タイミングは同じでなくても良い。すなわち、コモン電圧が変化するスイッチSW6aとスイッチSW6bとの切り替えタイミングと、2本1組の信号線の電位差(電流の向き)が切り替わるスイッチSW9a,SW9bと、スイッチSW10a,SW10bとの切り替えタイミングとが同時でなくても良い。

【0105】

図3は、本発明の実施の形態に従う信号線7a,7bの電位とコモン電圧ならびに2ビットの情報との関係を説明する別の図である。

【0106】

図3を参照して、ここでは、図2と比較して、コモン電圧の切り替え時間と、電流経路の切り替え時間とが異なる場合の例が示されている。

【0107】

具体的には、コモン電圧の切り替えは電流経路の切り替え時間よりも周期が長い場合が示されている。本例においては、時刻t1,t3,t5,t7に切り替えられる場合が示されている。

【0108】

一方で電流経路の切り替えは、所定時間毎(例えばt1〜t2)である。

本例においては、一例として、時刻t1〜t9までの期間においてそれぞれ情報を伝達する場合が示されている。

【0109】

具体的には、時刻t1からの所定時間内において、信号線7aは電圧V1レベルであり、かつ信号線7bは電圧V3レベルである。したがって、2信号線電位差で表される1ビット情報は「1」である。

【0110】

次に、時刻t2からの所定時間内において、信号線7aは電圧V3レベルであり、かつ、信号線7bは電圧V1レベルである。したがって、2信号線電位差で表される1ビット情報は「0」である。

【0111】

また、時刻t1〜t3の期間において、信号線7aと信号線7bとの間の中間電圧であるコモン電圧V2はコモン電圧閾値V4より高い電圧レベルである。したがってコモン電圧V2とコモン閾値電圧V4との間のコモン電位差で表される1ビット情報は「1」である。

【0112】

したがって、時刻t1〜t3の期間において、3ビットの情報を伝達することが可能である。

【0113】

同様に、時刻t3からの所定時間内において、信号線7aは電圧V5レベルであり、かつ、信号線7bは電圧V7レベルである。したがって、2信号線電位差で表される1ビット情報は「1」である。

【0114】

ここで、信号線7bは、電圧V1から電圧V7への遷移となるため当該電圧の遷移時間にある程度の時間が必要となる場合が示されているが、時刻t3と時刻t4との間の時刻t34から時刻t4の期間においては情報に応じた電位差が生じるため当該期間に信号を取り込むことにより情報をデコードして出力することが可能である。

【0115】

また、次に、時刻t4からの所定時間内において、信号線7aは電圧V7レベルであり、かつ、信号線7bは電圧V5レベルである。したがって、2信号線電位差で表される1ビット情報は「0」である。

【0116】

また、時刻t3〜t5の期間において、信号線7aと信号線7bとの間の中間電圧であるコモン電圧V6はコモン電圧閾値V4より低い電圧レベルである。したがって、コモン電圧V6とコモン閾値電圧V4との間のコモン電位差で表される1ビット情報は「0」である。

【0117】

したがって、時刻t3〜t5の期間において、3ビットの情報を伝達することが可能である。

【0118】

時刻t5以降の情報の伝達についても同様の方式により実行される。

本例においては、コモン電圧とコモン閾値電圧との比較に基づく情報の伝達期間を長く設定している。信号線の電圧レベルを例えば電圧V1から電圧V7まで遷移させて安定状態とするまでには時間がかかる可能性がある。すなわち、コモン電圧が安定するまでに時間がかかる可能性がある。所定時間毎に情報を伝達させる場合に当該所定時間の期間が短い場合には、高速に電圧レベルを設定する必要があるが、遷移期間が長いとコモン閾値電圧との比較による情報である正しいデコード結果を得ることができない。

【0119】

したがって、本例においては、コモン電圧の切り替えに従って情報を伝達する場合において安定して情報を伝達するために所定期間の2倍の期間を確保して、情報を伝達する方式としている。

【0120】

本例においては、時刻t1〜t9までの期間において3ビット×4=12ビットの情報を伝達することが可能である。

【0121】

本例では、コモン電圧の切り替え期間が、2本1組の信号線の電位差の切り替え期間よりも長くなっているため、より安定しノイズの少ない差動シリアル通信環境となる。

【0122】

以上のように、本発明の情報処理装置は、通信時に発生するノイズ量を抑えながらも、通信経路における信号線の配線数を増やすことなく通信の高速化を実現し得る情報処理装置を提供する。したがって、本発明は、シリアル通信インタ−フェ−スを用いる携帯機器等に関連した産業分野に好適に用いることができる。

【0123】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0124】

1 情報処理装置、2 ドライバ、3 レシーバ、4 定電圧源、5,8,12,17 抵抗素子、7 信号線対、7a,7b 信号線、11a,11b,11c,11d 論理回路、13,14 差動アンプ、15 デコーダ。

【特許請求の範囲】

【請求項1】

2本1組の信号線で構成される信号線対と、

前記信号線対の一端側に接続され、前記信号線対に対して入力された2進数の複数ビットのデータに応じた電圧レベルに設定するためのドライバと、

前記信号線対の他端側に接続され、前記信号線対の電圧レベルに応じて前記2進数の複数ビットのデータに変換するためのレシーバとを備え、

前記ドライバは、

前記信号線対に電圧を印加するための定電圧源と、

前記2進数の複数ビットのデータに応じて前記信号線対の入出力インピーダンスを調整するインピーダンス調整部と、

前記2進数の複数ビットのデータに応じて前記信号線対のそれぞれの信号線に流す電流の向きを切り替える切替部とを含む、情報処理装置。

【請求項2】

前記インピーダンス調整部は、

前記定電圧源と前記信号線対の一方と接続される第1の内部ノードとの間に設けられた第1の抵抗素子と、

前記定電圧源と前記第1の内部ノードとの間に設けられ、前記第1の抵抗素子と並列に設けられた第1のスイッチ素子と、

固定電圧と前記信号線対の他方と接続される第2の内部ノードとの間に設けられた第2の抵抗素子と、

前記固定電圧と前記第2の内部ノードとの間に設けられ、前記第2の抵抗素子と並列に設けられた第2のスイッチ素子とを有し、

前記第1および第2のスイッチ素子は、前記2進数の複数ビットのデータに応じて相補的にオン・オフする、請求項1記載の情報処理装置。

【請求項3】

切替部は、

前記2進数の複数ビットのデータに応じて、前記第1および第2の内部ノードと前記信号線対の一方および他方とそれぞれ接続するための第3および第4のスイッチ素子と、

前記2進数の複数ビットのデータに応じて、前記第3および第4のスイッチ素子と相補的に動作し、前記第1および第2の内部ノードと前記信号線対の他方および一方とそれぞれ接続するための第5および第6のスイッチ素子とを含む、請求項2記載の情報処理装置。

【請求項4】

前記複数ビットは、2ビットである、請求項1〜3のいずれかに記載の情報処理装置。

【請求項5】

前記レシーバは、

前記信号線対の信号線間の電位差に応じて前記2進数の複数ビットのうちの一部ビットのデータに変換する電位差識別部と、

前記信号線対の信号線間の中間電圧レベルに従って前記2進数の複数ビットのうちの残りのビットのデータに変換するコモン信号識別部とを含む、請求項1〜4のいずれかに記載の情報処理装置。

【請求項6】

2本1組の信号線で構成される信号線対に対して2進数の複数ビットのデータを伝送する情報処理装置の制御方法であって、

前記信号線対に電圧を印加するステップと、

前記2進数の複数ビットのデータに応じて前記信号線対の入出力インピーダンスを調整するステップと、

前記2進数の複数ビットのデータに応じて前記信号線対のそれぞれの信号線に流す電流の向きを切り替えるステップと、

前記信号線対の電圧レベルに応じて前記2進数の複数ビットのデータに変換するステップとを備える、情報処理装置の制御方法。

【請求項1】

2本1組の信号線で構成される信号線対と、

前記信号線対の一端側に接続され、前記信号線対に対して入力された2進数の複数ビットのデータに応じた電圧レベルに設定するためのドライバと、

前記信号線対の他端側に接続され、前記信号線対の電圧レベルに応じて前記2進数の複数ビットのデータに変換するためのレシーバとを備え、

前記ドライバは、

前記信号線対に電圧を印加するための定電圧源と、

前記2進数の複数ビットのデータに応じて前記信号線対の入出力インピーダンスを調整するインピーダンス調整部と、

前記2進数の複数ビットのデータに応じて前記信号線対のそれぞれの信号線に流す電流の向きを切り替える切替部とを含む、情報処理装置。

【請求項2】

前記インピーダンス調整部は、

前記定電圧源と前記信号線対の一方と接続される第1の内部ノードとの間に設けられた第1の抵抗素子と、

前記定電圧源と前記第1の内部ノードとの間に設けられ、前記第1の抵抗素子と並列に設けられた第1のスイッチ素子と、

固定電圧と前記信号線対の他方と接続される第2の内部ノードとの間に設けられた第2の抵抗素子と、

前記固定電圧と前記第2の内部ノードとの間に設けられ、前記第2の抵抗素子と並列に設けられた第2のスイッチ素子とを有し、

前記第1および第2のスイッチ素子は、前記2進数の複数ビットのデータに応じて相補的にオン・オフする、請求項1記載の情報処理装置。

【請求項3】

切替部は、

前記2進数の複数ビットのデータに応じて、前記第1および第2の内部ノードと前記信号線対の一方および他方とそれぞれ接続するための第3および第4のスイッチ素子と、

前記2進数の複数ビットのデータに応じて、前記第3および第4のスイッチ素子と相補的に動作し、前記第1および第2の内部ノードと前記信号線対の他方および一方とそれぞれ接続するための第5および第6のスイッチ素子とを含む、請求項2記載の情報処理装置。

【請求項4】

前記複数ビットは、2ビットである、請求項1〜3のいずれかに記載の情報処理装置。

【請求項5】

前記レシーバは、

前記信号線対の信号線間の電位差に応じて前記2進数の複数ビットのうちの一部ビットのデータに変換する電位差識別部と、

前記信号線対の信号線間の中間電圧レベルに従って前記2進数の複数ビットのうちの残りのビットのデータに変換するコモン信号識別部とを含む、請求項1〜4のいずれかに記載の情報処理装置。

【請求項6】

2本1組の信号線で構成される信号線対に対して2進数の複数ビットのデータを伝送する情報処理装置の制御方法であって、

前記信号線対に電圧を印加するステップと、

前記2進数の複数ビットのデータに応じて前記信号線対の入出力インピーダンスを調整するステップと、

前記2進数の複数ビットのデータに応じて前記信号線対のそれぞれの信号線に流す電流の向きを切り替えるステップと、

前記信号線対の電圧レベルに応じて前記2進数の複数ビットのデータに変換するステップとを備える、情報処理装置の制御方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−9157(P2013−9157A)

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願番号】特願2011−140533(P2011−140533)

【出願日】平成23年6月24日(2011.6.24)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願日】平成23年6月24日(2011.6.24)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]