情報処理装置及び情報処理方法

【課題】レイテンシを増加させることなくデータの信頼性を確保する。

【解決手段】この情報処理装置は、誤り訂正情報付加手段と、誤り訂正情報付加手段から誤り訂正情報付データを入力し、誤り訂正手段と、誤り訂正手段から訂正後データを入力する第1データ経路と、入力データを主記憶手段及び誤り訂正手段を介さずに直接入力する第2データ経路が接続された緩衝用バッファと、緩衝用バッファに第1データ経路を介して訂正後データを入力する第1動作、及び第2データ経路を介して入力データを入力する第2動作の実行及び停止を制御する緩衝用バッファ制御手段と、を備える。

【解決手段】この情報処理装置は、誤り訂正情報付加手段と、誤り訂正情報付加手段から誤り訂正情報付データを入力し、誤り訂正手段と、誤り訂正手段から訂正後データを入力する第1データ経路と、入力データを主記憶手段及び誤り訂正手段を介さずに直接入力する第2データ経路が接続された緩衝用バッファと、緩衝用バッファに第1データ経路を介して訂正後データを入力する第1動作、及び第2データ経路を介して入力データを入力する第2動作の実行及び停止を制御する緩衝用バッファ制御手段と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、情報処理装置及び情報処理方法に関し、特に、内蔵RAMに格納されるデータの誤り訂正を行なう機能を備えた情報処理装置及び情報処理方法に関する。

【背景技術】

【0002】

一般的に、情報処理装置の論理回路は、データ信号を、例えば1ビットの誤り訂正可能なECC(Error Detection and Correction)で保護し、持ち回る。また、制御系の信号については、誤り検出のみを目的としたパリティで保護することが多い。ここで、制御系のデータをバッファ等に格納するにあたって、ファーストインファーストアウトのようなバッファを使用する場合、レジスタではなく遅延や面積に有利な内蔵RAM(Random Access Memory)が使用される。しかしながら、FIT数(故障率)が悪いRAMを使用すると、パリティ等の誤り検出用の回路では誤りの訂正ができず、1ビットの誤りでシステムダウンする可能性がある。

【0003】

そのため、RAMのデータを保護する対策の1つとして、RAMに格納するときにECCを追加して、読み出すときにECCチェックを行い、誤り訂正を行う方法が知られている(例えば、特許文献1)。しかしながら、読み出しデータは、ECCチェック後の訂正後のデータを使用しなければならず、遅延が悪化することとなる。そのため、内蔵RAMのFIT数の救済策としては、レジスタを1個追加して遅延性能低下を許容するか、コストの高い高速テクノロジを使用するか選択を迫られることが多い。一方、テクノロジの微細化が進むにつれて、紫外線等によるエラーの可能性が高くなる中、高信頼性や高性能性に加え、低価格化が求められており、全ての条件満たす情報処理装置が要求されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−103005号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

情報処理装置の論理回路でRAMを使用する際、故障率の高いRAMであれば、ビット誤りが発生する確立が高くなる。よって、高い信頼性が求められる場合にRAMを使用するときは、ECC等の誤り訂正符号を付加する。ECCにより誤り訂正を行う場合は、1ビットのビット誤りが発生しても訂正可能になるため、システムダウンの危険性を回避することができる。しかしながら、RAMの読み出し遅延に加えて、誤り訂正回路による遅延が追加されるため、出力データをそのまま直接論理に使用できないことがあり、その場合はレジスタを挟んで使用せざるをえず1タイミング分、レイテンシが遅くなる。

【0006】

この問題点を具体的に説明する。情報処理装置に、図2に示す構成のRAMが設けられているとする。また、図2に示すRAMは、図3に示すように、T3でリードアドレス(RAMリードアドレス12)を入力するとT4でデータ(出力データ15)が出力されるような仕様であるとする。この場合、図2のRAM22に、ECCを追加することで、図7に示すような情報処理装置を構成する場合には、RAM22に格納する前に、ECC生成部21によりECC生成を行い、RAM22の読み出し後に、ECC誤り訂正部23によりECC誤り訂正を行う。

【0007】

しかし、図7のRAM22読み出しから信号線34、ECC誤り訂正部23、信号線35までの遅延が大きく、出力データをこのまま使用することができない場合は、レジスタ27を追加せざるを得ない。しかしながら、レジスタ27を追加すると、図8で示すようにT3でリードアドレス(RAMリードアドレス12)を入力してもT5にならないと読み出しデータ(出力データ15)を使用できない。このように、レイテンシが増加すると、制御機能によっては性能悪化につながる恐れがあり、信頼性と性能のどちらを優先するのか判断が難しい場合があった。

【0008】

本発明は、このような問題点に対してなされたものであり、レイテンシを増加することなくRAMのデータを保護できる情報処理装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明に係る情報処理装置は、外部から入力される入力データに、誤り訂正情報を付加して誤り訂正情報付データを生成する誤り訂正情報付加手段と、前記誤り訂正情報付加手段から誤り訂正情報付データを入力し、前記誤り訂正情報付データを出力する主記憶手段と、前記主記憶手段から前記誤り訂正情報付データを入力し、前記誤り訂正情報付データに含まれる前記訂正情報に基づいて誤り訂正を行い、前記入力データに相当する誤り訂正後データを生成する誤り訂正手段と、前記誤り訂正手段から前記誤り訂正後データを入力する第1データ経路と、前記入力データを前記主記憶手段及び前記誤り訂正手段を介さずに入力する第2データ経路が接続された緩衝用バッファと、前記第1データ経路を介して前記緩衝用バッファに前記誤り訂正後データを入力する第1動作と、前記第2データ経路を介して前記緩衝用バッファに前記入力データを入力する第2動作の開始及び停止を制御すると共に、外部から入力されるリードアドレスに従って、前記緩衝用バッファに格納された前記誤り訂正後データ及び前記入力データを出力データとして出力するよう前記緩衝用バッファを制御する緩衝用バッファ制御手段と、を備えたことを特徴とする。

ことを特徴とする。

【0010】

また、本発明に係る情報処理方法は、外部から入力される入力データに、誤り訂正情報を付加して誤り訂正情報付データを生成し、前記誤り訂正情報付データを主記憶手段に入力し、前記主記憶手段から前記誤り訂正情報付データを入力し、前記誤り訂正情報付データに含まれる前記訂正情報に基づいて誤り訂正を行って、前記入力データに相当する誤り訂正後データを生成し、前記誤り訂正後データを入力する第1データ経路と、前記入力データを前記主記憶手段を介さずに入力する第2データ経路が接続された緩衝用バッファに対し、前記第1データ経路を介して前記緩衝用バッファに前記誤り訂正後データを入力する第1動作と、前記第2データ経路を介して前記緩衝用バッファに前記入力データを入力する第2動作の開始及び停止を制御し、外部から入力されるリードアドレスに従って、前記緩衝用バッファに格納された前記誤り訂正後データ及び前記入力データを出力データとして出力する、ことを特徴とする。

【発明の効果】

【0011】

本発明に係る情報処理装置及び情報処理方法によれば、RAM読み出しデータのECC誤り訂正回路の遅延を隠蔽することより、レイテンシを増加することなくRAMのデータを保護できるようになり、システムダウンの減少が図れるため、性能低下を伴わずに信頼性を向上させることができる。

【図面の簡単な説明】

【0012】

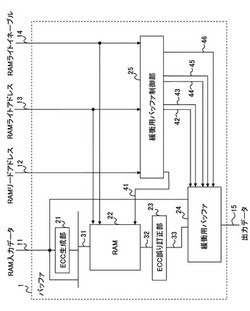

【図1】本発明の実施の形態にかかる情報処理装置の全体構成を示す図である。

【図2】本発明の実施の形態にかかる情報処理装置に含まれる、RAMの構成例を示す図である。

【図3】図2に示すRAMの動作を示すタイミングチャートである。

【図4】本発明の実施の形態に係る情報処理装置の動作を示すタイミングチャートである。

【図5】本発明の実施の形態に係る情報処理装置の動作を示すタイミングチャートである。

【図6】本発明の実施の形態に係る情報処理装置の動作を示すタイミングチャートである。

【図7】従来の情報処理装置の全体構成を示す図である。

【図8】従来の情報処理装置の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0013】

実施の形態.

以下、添付した図面を参照し、本発明の最良な実施の形態について説明する。図1は、本発明の実施の形態に係る情報処理装置の全体構成を示す図であり、図2は、その情報処理装置に含まれるRAMの一例を示す図である。まず、本実施形態の構成の説明にあたり、情報処理装置に内蔵されるRAM22の一例について図2を用いて説明する。RAM22に入力される入力信号は、RAM22への書き込みデータであるRAM入力データ11、RAM22の読み出しアドレスであるRAMリードアドレス12、RAM22の書き込みアドレスであるRAMライトアドレス13、RAM22への書き込みを指示するRAMライトイネーブル14である。RAM22への書き込みは、RAMライトイネーブル14が有効なときにRAMライトアドレス13が示すRAM22のワードに、RAM入力データ11を書き込む。

【0014】

RAM22からの読み出しは、RAMリードアドレス12によって指定されるワードのデータが読み出される。この読み出されたデータは、出力データ15として出力される。RAM22は、FIFOファーストインファーストアウト構成を対象としている。そのため、RAMライトアドレス13は、書き込み指示(RAMライトイネーブル14)が有効になる度に1加算されて、最大ワード数に達すると0に戻り、以降も同様の動作を繰り返す。

【0015】

また、RAMリードアドレス12についても同様に、読み出す度に1加算され、最大ワード数になると0に戻る動作を繰り返す。なお、本説明では、RAM22の入力信号から出力信号(出力データ15)の間の部分を、バッファ1と規定する。

【0016】

次に、本発明の実施の全体構成について図1を用いて説明する。図1中のRAM22は、図2に記載されたものであるとする。図1の情報処理装置では、図2のバッファ1の入出力信号やタイミングはそのままとし、ECC機能を追加しながらもRAM読み出し後のECC訂正回路の遅延を、出力データ15に見せないようにする機能を持つFIFOバッファである。

【0017】

バッファ1は、入力信号として、RAM入力データ11、RAMリードアドレス12、RAMライトアドレス13、RAMライトイネーブル14を入力し、出力信号として出力データ15を出力する。バッファ1は、RAM22、ECC生成部21、ECC誤り訂正部23、緩衝用バッファ24、及び緩衝用バッファ制御部25を有している。

【0018】

ECC生成部21は、RAM入力データ11を入力し、RAM入力データ11に、ECCを付加してECC付きデータ31を生成する。

【0019】

RAM22は、ECC生成部21によって生成された、ECC付きデータ31が格納可能なビット幅を有している。RAM22への書き込みは、RAMライトイネーブル14が有効なときに、RAMライトアドレス13が示すワードに、ECC付きデータ31が格納される。RAM22からの読み出しは、バッファ1に入力されるRAMリードアドレス12ではなく、後述する緩衝用バッファ制御部25で生成されたバッファ内RAMリードアドレス41によって指定されるワードのデータが読み出される。

【0020】

RAMリードアドレス12をRAM22の読み出しアドレスとして使用しないのは、以下の理由による。すなわち、本実施の形態では、緩衝用バッファ24の出力を、出力データ15としているが、緩衝用バッファ24には、RAM22、ECC誤り訂正部23及びを経由してRAM入力データ11に相当する誤り訂正後データ33を入力する第1のデータ経路と、RAM22及びECC誤り訂正部23を介さずにRAM入力データ11を直接緩衝用バッファ24に入力する第2のデータ経路が接続されている。そして、出力データ15として出力されるべきタイミングに対し、第1のデータ経路を介した出力データが遅れる場合には、遅延の小さい第2のデータ経路を介した出力データを、出力データ15として採用する。そのため、この制御を実現するために、RAMリードアドレス12をRAM22の読み出しアドレスとして使用せず、緩衝用バッファ制御部25によってバッファ内RAMリードアドレス41を生成し、RAM22の読み出しアドレスとして用いている。

【0021】

ECC誤り訂正部23は、RAM22から読み出したRAM出力データ32をECCチェックする。ECC誤り訂正部23は、誤りがない場合は読み出したデータをそのまま使用し、1ビット誤りなど訂正可能な範囲のビット誤りがある場合は誤りを訂正する。ECC誤り訂正部23は、このデータをECC誤り訂正後データ33として緩衝用バッファ24に送出する。なお、ECC誤り訂正部23は、ECC部分は送出せず、RAM入力データ11に相当するデータのみをECC誤り訂正後データ33として出力する。

【0022】

緩衝用バッファ24は、ECC誤り訂正部23の遅延を出力データ15に見せないために設けられている。前述したように、緩衝用バッファ24には、RAM22及びECC誤り訂正部23(第1のデータ経路)を介して、RAM入力データ11に相当するデータが入力されると共に、RAM22及びECC誤り訂正部23を介さずに(第2のデータ経路を介して)直接RAM入力データ11が入力される。緩衝用バッファ24は、RAM入力データ11と同じビット幅をもち、数ワードからなるレジスタ構成をとる。緩衝用バッファ24は、レジスタ構成であるため、故障率は低いのでECC保護は行わない。緩衝用バッファ24には、RAM22書き込みデータであるRAM入力データ11またはRAM22読み出し後のECC誤り訂正後データ33が書き込まれ、緩衝用バッファ24の読み出しデータはバッファ1としての出力データ15になる。

【0023】

緩衝用バッファ24に必要な最小ワード数は、緩衝用バッファ24によるレイテンシを隠蔽できる数が必要である。具体的には、緩衝用バッファ24に必要な最小ワード数は、RAMライトイネーブル14が有効になってRAM入力データ11がRAM22に書き込まれてから、書き込まれた同一ワードをRAM22から読み出せるまでにかかるクロック数と、緩衝用バッファ24に入力されたデータが、緩衝用バッファ24から読み出されるまでにかかるクロック数を足した数である。緩衝用バッファ24の読み出しワードは、FIFOとしてのバッファ1の読み出し順と一致するように、初期値0から始まり、読み出し毎に1加算して最大ワードになったところで初期値に戻り繰り返す。

【0024】

書き込みワードに関しては読み出し順と書き込み順が一致しない場合もあるため、読み出し順のワードに対応するように書き込むワードを決定する。ここで、緩衝用バッファ24の書き込み制御には二種類ある。1つめは、RAM22にRAM入力データ11を書き込む際に、RAM22に書き込まれるRAM入力データ11を、RAM22への書き込みに並行して緩衝用バッファ24に格納する制御である。2つめは、RAM読み出し時に、RAM22及びECC誤り訂正部23を経由したRAM入力データ11に相当するECC訂正後データ33を、緩衝用バッファ24に書き込む制御である。

【0025】

そこで、RAM書き込み時に緩衝用バッファ24に並行して緩衝用バッファ24に書き込む場合の緩衝用バッファ24のライトイネーブルを、バッファライトイネーブル(RAMライト)44、そのときの書き込みワードを示すアドレスをバッファライトアドレス(RAMライト)42と呼ぶ。また、RAM22の読み出し後のECC誤り訂正後データ33を緩衝用バッファ24に書き込む場合の緩衝用バッファ24のライトイネーブルを、バッファライトイネーブル(RAMリード)45、そのときの書き込みワードを示すアドレスをRAMリード時のバッファライトアドレス(RAMリード)43と呼ぶこととする。

【0026】

すなわち、本実施の形態の構成では、バッファライトイネーブル(RAMライト)44が有効なときは、バッファライトアドレス(RAMライト)42が示すワードにRAM入力データ11を書き込む。また、バッファライトイネーブル(RAMリード)45が有効なときはバッファライトアドレス(RAMリード)43が示すワードにRAM読み出し後のECC誤り訂正後データ33を書き込む。この二つの書き込み制御は、RAM本来の読み出しタイミングを守るために同時に起こることがある。

【0027】

緩衝用バッファ24からの読み出しについては、バッファリードアドレス46が示すワードのデータを選択して出力する。この緩衝用バッファ24の読み出しデータがバッファ1の出力データ15になるため、出力データ15の遅延は緩衝用バッファ24の読み出し遅延だけになる。

【0028】

緩衝用バッファ制御部25は、RAM22の読み出しワードを示すバッファ内RAMリードアドレス41、緩衝用バッファ24の書き込みワードを示すバッファライトアドレス(RAMライト)42、バッファライトアドレス(RAMリード)43と、書き込み指示であるバッファライトイネーブル(RAMライト)44、バッファライトイネーブル(RAMリード)45、読み出しワードを示すバッファリードアドレス46を生成する機能を持つ。

【0029】

バッファ内RAMリードアドレス41は、RAM22に有効データが格納されているときに、緩衝用バッファ24にまだ書き込まれていない有効データの先頭のワードに向けておくことで、緩衝用バッファ24に空きができたときにすぐに書き込めるようにしておく。ここで、有効データとは、RAM22に格納されたECC付きデータ31のうち、いまだRAM22から緩衝用バッファ24に読み出されておらず、かつ、緩衝用バッファ24に先読みされた(直接入力された)RAM入力データ11に相当するECC付きデータ31を除くデータのことを示すものとする。

【0030】

ここで、バッファライトイネーブル(RAMライト)44が有効になる、すなわち、緩衝用バッファ24に直接入力されるRAM入力データ11が出力データ15として採用されるのは、条件(1)〜(3)を全て満たす場合である。

条件(1)RAMライトイネーブル14が有効であり、

条件(2)次のクロックにおいて緩衝用バッファ24に空きがあることが判明し、

条件(3)RAM22に格納されている有効データの数(ワード数)が、緩衝用バッファ24の空きワード数より少ないか、もしくは空の場合である。

【0031】

また、バッファライトイネーブル(RAMリード)45が有効になる、すなわち、RAM22及びECC誤り訂正部23を経由したECC誤り訂正後データ33が出力データ15として採用されるのは、条件(4)乃至(6)をいずれも満たす場合である。

条件(4)RAM22に格納されている有効データのワード数があるとき、

条件(5)次のクロックにおいて緩衝用バッファ24に空きが生じると判明したとき、

条件(6)RAM22の読み出しデータが有効なときである。

【0032】

なお、前述したように、同時書き込みが行なわれる、すなわち、バッファライトイネーブル(RAMライト)44及びバッファライトイネーブル(RAMリード)45が同時に有効になるのは、条件(1)乃至(3)と条件(4)乃至(6)がそれぞれ同時に成り立つときである。

【0033】

バッファライトアドレス42、43については、バッファ構造によっては必ずしも緩衝用バッファ24の読み出し順通りに緩衝用バッファ24に書き込めるとは限らないため、FIFOのバッファの読み出し順序に追随しているバッファリードアドレス46に適合したワードを探して指定する。バッファリードアドレス46については、RAMリードアドレス12の変化点で1加算していき、最大ワード値に到達したら初期値に戻り、これを繰り返すことでRAMのFIFOバッファの読み出し順を守る。

【0034】

以上の機能により、RAMの読み出し後にECC誤り訂正回路を追加しても、その回路遅延がその後の出力データに見えることなくRAMのFIT数救済につなげることができる。

【0035】

次に、このように構成された情報処理装置の動作について説明する。まず、情報処理装置に含まれるRAM22(図2)の読み出しにかかるクロック数、つまりレイテンシについては、一例として図3に示す場合を対象とする。図3に示すように、RAM22は、RAM22への書き込みタイミング(T2)の次のタイミング(T3)から書き込みデータが有効になり、読み出しアドレスを受け取ったタイミング(T3)の次のタイミング(T4)で読み出しデータを出力できる仕様であるとする。

【0036】

さらに具体的に説明すると、RAM22への書き込みは、T2のタイミングでRAMライトイネーブル14が有効になると、T2のRAMライトアドレス13が示すワード0にT2のRAM入力データ11を書き込む制御を行い、次のタイミングのT3からデータが有効になる。RAM22の読み出しは、T3でワード0を示すRAMリードアドレス12が入力されると、読み出しデータはT4で出力データ15として送出される。ここで、T2でRAMリードアドレス12がワード0を指していても、T3の出力データ15が期待通りではないのは、T2ではワード0にまだ最新のデータが書き込まれていないからである。よって、書き込み指示後に書き込んだデータを読み出せるのは、RAMライトイネーブル14が有効になったタイミングから2クロック後になる。

【0037】

以降では、図3のタイミングを持つRAM22に、本実施の形態に係る機能を追加して情報処理装置を構成した場合の情報処理装置の動作を説明する。なお、図3に示す、RAM22の読み出しタイミングを守りながらECC誤り訂正回路による遅延影響を出力に見せないようにするために最低限必要な緩衝用バッファ24のワード数は、前述したように、RAMライトイネーブル14が有効になってから(RAM入力データ11が書き込まれてから)、書き込まれた同一ワードを読み出せるまでにかかるクロック数と、緩衝用バッファ24に入力されたデータが読み出されるまでにかかるクロック数の和となる。具体的には、図3の仕様のRAM22では、緩衝用バッファ24として最低限必要なワード数は、RAMライトイネーブル14が有効になってから、書き込まれた同一ワードを読み出せるまでにかかる2タイミング分に、緩衝用バッファ24に入力されたデータが読み出されるまでにかかるクロック数1を足した3タイミング分、つまり3ワード分となる。

【0038】

[RAMへの書き込み動作]

はじめに、RAM22への書き込みまでの動作について図4を使って説明する。RAM22への書き込みは、RAM22及びECC誤り訂正部23を経由したECC誤り訂正後データ33が出力データ15として採用されるか否かに関わらず、RAMライトイネーブル14が有効なときに、RAMライトアドレス13が示すワードに、RAM入力データ11にECCを付加したECC付きデータ31を書き込む。具体的には、図4に示すように、T2のタイミングでRAMライトイネーブル14が有効であるため、T2のRAMライトアドレス13が示すワード0に、T2のRAM入力データ11(a)とECC生成部21で生成したT2のRAM入力データ11(a)のECCをあわせたECC付きデータ31(a+)をRAM22に書き込む。

【0039】

[緩衝用バッファへの書き込み動作]

次に、緩衝用バッファ24への書き込み動作について説明する。緩衝用バッファ24への書き込み動作には、(動作1)RAM22及び誤り訂正部23を介さずにRAM入力データ11だけを直接書き込む動作と、(動作2)RAM22から読み出された後のECC誤り訂正後データ33を書き込む動作と、(動作3)RAM入力データ11とECC誤り訂正後データ33の両方を同時に書き込む場合がある。

【0040】

(動作1)RAM22及びECC誤り訂正部23を介さずにRAM入力データ11だけを直接書き込む場合を、図4を用いて説明する。図4のT2のタイミングでは、RAMライトイネーブル14が有効であり(条件1)、RAM22と緩衝用バッファ24は共に空であるので(条件2、3)、条件(1)〜(3)を全て満たすため、バッファライトイネーブル(RAMライト)44が有効になる。そのため、バッファライトアドレス(RAMライト)42が示す緩衝用バッファ24のワード0に、RAM入力データ11を書き込む。また、これと同時に、RAM入力データ11にECCデータを付加したECC付きデータ31を、RAM22にも書き込む。

【0041】

T3、T4でも同様に、RAMライトイネーブル14が有効であり(条件1)、緩衝用バッファ24に空きがあり(条件2)、RAM22の有効ワード数も緩衝用バッファ24のワード数以下であるため(条件3)、T2と同様の動作を行う。

【0042】

T5についても、RAMライトイネーブル14が有効であり(条件1)、前のタイミングのT4で緩衝用バッファ24のワード0が読み出されているため空きができており(条件2)、かつ、RAM22内に格納されているデータは、相当するRAM入力データ11が全てRAM22を介さずに直接緩衝用バッファ24に格納されていているため、有効データのワード数は0であり、緩衝用バッファ24のワード数よりも少ない(条件3)。よって、条件(1)〜(3)を全て満たすため、バッファライトイネーブル(RAMライト)44が有効になり、RAM入力データ11が、緩衝用バッファ24に直接格納される。

【0043】

(動作2)RAM読み出し後のECC誤り訂正後データ33だけを書き込む場合について図5を用いて説明する。図5のT5では、緩衝用バッファ24は全て使われていて、T5以降もRAM22への書き込みが続いているが、緩衝用バッファ24の読み出しがなく空きができないため、(条件2)を満たさない。そのため、T5からT7では緩衝用バッファ24にRAM入力データ11は書き込めず、バッファライトイネーブル(RAMライト)44は無効となる。

【0044】

ここで、バッファライトイネーブル(RAMライト)44が無効となる間でも(T5〜T7)、RAMライトイネーブル14はT5〜T7で有効となっているので、RAM22には継続して、ECC付きデータ(d+)、(e+)、(f+)を書き込む。よって、T8のタイミングでは緩衝用バッファ24に書き込まれていないRAM22の有効データ(d+)、(e+)、(f+)が3ワード分存在している。すなわち、T7〜T10までのRAM22の有効データの数は3であり、緩衝用バッファ24の持つワード数3と同じである(条件4)。なお、有効データのワード数は、RAMライトアドレス、RAMリードアドレスを元に求められるRAMの格納ワード数から、緩衝用バッファ24に直接格納したワード数を引くことにより求めることができる。

【0045】

このとき、バッファ内RAMリードアドレス41は、緩衝用バッファ24に書き込まれていないワードの中で先頭アドレスであるワード3にあらかじめ向けておき、先読みできるようにしておく。その後、T10で、RAMリードアドレス12が次のアドレスに移行することにより、ワード0から出力データ(a)が出力されるため、緩衝用バッファ24のワード0が次のタイミング(T11)で空きができることが判明する(条件5)。そのため、T10で(条件4)及び(条件5)が満たされるので、FIFOで次のワードとなるRAM22の読み出しデータを格納するために、バッファライトイネーブル(RAMリード)45が有効になる。

【0046】

T10において、バッファライトアドレス(RAMリード)43が示す緩衝用バッファ24のワード0に、RAM22のワード3(d+)を読み出し、ECC誤り訂正したECC誤り訂正後データ33(d)を書き込む。これにより、次のタイミングT11において、緩衝用バッファ24のワード0にECC誤り訂正後データ33(d)が格納される。また、T10では、RAM22の次のワードを読み出すため、バッファ内RAMリードアドレス41を1加算してワード4に変更する。T11、T12についても同様である。

【0047】

(動作3)RAM入力データ11とRAM読み出し後のECC誤り訂正後データ33を両方同時に書き込む制御について図6を用いて説明する。T6では、RAMライトアドレス13として入力されたアドレス数は4であり、緩衝用バッファ24に直接格納されたRAM入力データ11のワード数は3であるため、RAM22内に格納されている有効データ数は1(=4−3)である。よって、RAM22内に格納されている有効データ数は、緩衝用バッファ24の有するワード数よりも少ないこととなる(条件4)。また、RAMリードアドレス12がインクリメントされるため、次のタイミングで緩衝用バッファ24のワード0に空きがでることが判明する(条件5)。従って、(条件4)及び(条件5)を満たすため、バッファリードイネーブル(RAMリード)45が有効になり、RAM22及びECC誤り訂正部23を介した誤り訂正後データ33の緩衝用バッファ24への書き込みが可能になる。

【0048】

ここで、T7において、バッファリードイネーブル(RAMリード)45を有効にしてRAM22のワード3から読み出してECC誤り訂正したECC誤り訂正後データ33(d)を緩衝用バッファ24に書き込むと共に、RAMライト時のバッファライトイネーブル46を有効にしてRAM入力データ11(e)についても直接緩衝用バッファ24に書き込む。

【0049】

すなわち、T7において、バッファライトイネーブル(RAMリード)45とバッファライトイネーブル(RAMライト)44の両方がそれぞれ同時に有効になり、RAMのFIFO順序を損なわないようにバッファライトアドレス(RAMリード)43はワード0に、バッファライトアドレス(RAMライト)42はワード1に向け、ワード0にはECC誤り訂正後データ33(d)をワード1にはECC付きデータ31(e)をそれぞれ書き込む。

【0050】

ここで、もし、この二種類の同時書き込みを許さないとすると、T7でRAMライトアドレス13がワード4を示すRAM書き込みデータ(e)については一旦RAM22に格納してから読み出さないとならないため、最短でも緩衝用バッファ24に書き込み指示が出来るのはT9になる。その場合、T9でRAMライトアドレス13がワード5を示すRAM書き込みデータについても同様に最短で緩衝用バッファ24に書き込み指示ができるのがT11になる。そのため、T10でRAMリードアドレス12が示すワード5(データf)の読み出しに間に合わなくなる。よって、このような場合では、二種類の同時書き込みが必要となる。

【0051】

[RAMから緩衝用バッファへの読み出し動作]

RAM22から緩衝用バッファ24への読み出し動作を、図5を用いて説明する。T9のタイミングで読み出したいRAM22のワード、ここではワード3をバッファ内RAMリードアドレス41で示すと、T10でRAM22からデータが読みだされる。T10でRAM22から読み出されたワード3のRAM出力データ32(d+)をECC誤り訂正部23でECCチェックし、誤りがない場合はそのままで、誤りがある場合は訂正して、ECC誤り訂正後データ33(d)として緩衝用バッファ24に送出する。

【0052】

[緩衝用バッファから出力データを読み出す動作]

緩衝用バッファ24の読み出し動作は、図4を用いて説明する。T3のタイミングではRAMリードアドレス12とバッファリードアドレス46は、ともに初期状態のワード0を示しているため、T4では緩衝用バッファ24のワード0のデータが選択されバッファ1の出力データ15となる。次に、T4でRAMリードアドレス12が0から1に変化するため、T5ではバッファリードアドレス46が1加算されてワード1に変わる。よって、T5ではバッファ1の出力データ15は緩衝用バッファ24のワード1のデータになる。T6も同様であり、ワード2まで到達すると次はワード0に戻り、以降繰り返される。

【0053】

次に、このように構成された情報処理装置の効果について説明する。本実施の形態では、RAM22及びECC誤り訂正部23を介してECC誤り訂正後データ33を入力する第1のデータ経路と、RAM22及びECC誤り生成部23を介さず直接RAM入力データ11を入力する第2のデータ経路を、緩衝用バッファ24に接続し、緩衝用バッファ24の出力を、バッファ1の出力データ15として構成する。これにより、第1のデータ経路を介した出力データ15が外部から入力されるRAMリードアドレス12に対して遅れる場合には、遅延の小さい第2のデータ経路を介して直接RAM入力データ11を緩衝用バッファ24に格納する。これにより、出力データ15のECC誤り訂正回路の遅延を隠蔽することができる。

【0054】

また、RAM周りに緩衝用のレジスタ構成のバッファを付加して、RAM読み出しデータのECC誤り訂正回路の遅延を隠蔽することより、レイテンシを増加することなくRAMのデータを保護できるようになり、システムダウンの減少が図れるため、性能低下を伴わずに信頼性を向上させることができる。

【0055】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0056】

1 バッファ

11 RAM入力データ

12 RAMリードアドレス

13 RAMライトアドレス

14 RAMライトイネーブル

15 出力データ

21 ECC生成部

23 ECC誤り訂正部

24 緩衝用バッファ

25 緩衝用バッファ制御部

31 ECC付きデータ

32 RAM出力データ

33 ECC誤り訂正後データ

34、35 信号線

41 リードアドレス

42、43 バッファライトアドレス

44、45 バッファライトイネーブル

46 バッファリードアドレス

【技術分野】

【0001】

本発明は、情報処理装置及び情報処理方法に関し、特に、内蔵RAMに格納されるデータの誤り訂正を行なう機能を備えた情報処理装置及び情報処理方法に関する。

【背景技術】

【0002】

一般的に、情報処理装置の論理回路は、データ信号を、例えば1ビットの誤り訂正可能なECC(Error Detection and Correction)で保護し、持ち回る。また、制御系の信号については、誤り検出のみを目的としたパリティで保護することが多い。ここで、制御系のデータをバッファ等に格納するにあたって、ファーストインファーストアウトのようなバッファを使用する場合、レジスタではなく遅延や面積に有利な内蔵RAM(Random Access Memory)が使用される。しかしながら、FIT数(故障率)が悪いRAMを使用すると、パリティ等の誤り検出用の回路では誤りの訂正ができず、1ビットの誤りでシステムダウンする可能性がある。

【0003】

そのため、RAMのデータを保護する対策の1つとして、RAMに格納するときにECCを追加して、読み出すときにECCチェックを行い、誤り訂正を行う方法が知られている(例えば、特許文献1)。しかしながら、読み出しデータは、ECCチェック後の訂正後のデータを使用しなければならず、遅延が悪化することとなる。そのため、内蔵RAMのFIT数の救済策としては、レジスタを1個追加して遅延性能低下を許容するか、コストの高い高速テクノロジを使用するか選択を迫られることが多い。一方、テクノロジの微細化が進むにつれて、紫外線等によるエラーの可能性が高くなる中、高信頼性や高性能性に加え、低価格化が求められており、全ての条件満たす情報処理装置が要求されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−103005号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

情報処理装置の論理回路でRAMを使用する際、故障率の高いRAMであれば、ビット誤りが発生する確立が高くなる。よって、高い信頼性が求められる場合にRAMを使用するときは、ECC等の誤り訂正符号を付加する。ECCにより誤り訂正を行う場合は、1ビットのビット誤りが発生しても訂正可能になるため、システムダウンの危険性を回避することができる。しかしながら、RAMの読み出し遅延に加えて、誤り訂正回路による遅延が追加されるため、出力データをそのまま直接論理に使用できないことがあり、その場合はレジスタを挟んで使用せざるをえず1タイミング分、レイテンシが遅くなる。

【0006】

この問題点を具体的に説明する。情報処理装置に、図2に示す構成のRAMが設けられているとする。また、図2に示すRAMは、図3に示すように、T3でリードアドレス(RAMリードアドレス12)を入力するとT4でデータ(出力データ15)が出力されるような仕様であるとする。この場合、図2のRAM22に、ECCを追加することで、図7に示すような情報処理装置を構成する場合には、RAM22に格納する前に、ECC生成部21によりECC生成を行い、RAM22の読み出し後に、ECC誤り訂正部23によりECC誤り訂正を行う。

【0007】

しかし、図7のRAM22読み出しから信号線34、ECC誤り訂正部23、信号線35までの遅延が大きく、出力データをこのまま使用することができない場合は、レジスタ27を追加せざるを得ない。しかしながら、レジスタ27を追加すると、図8で示すようにT3でリードアドレス(RAMリードアドレス12)を入力してもT5にならないと読み出しデータ(出力データ15)を使用できない。このように、レイテンシが増加すると、制御機能によっては性能悪化につながる恐れがあり、信頼性と性能のどちらを優先するのか判断が難しい場合があった。

【0008】

本発明は、このような問題点に対してなされたものであり、レイテンシを増加することなくRAMのデータを保護できる情報処理装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明に係る情報処理装置は、外部から入力される入力データに、誤り訂正情報を付加して誤り訂正情報付データを生成する誤り訂正情報付加手段と、前記誤り訂正情報付加手段から誤り訂正情報付データを入力し、前記誤り訂正情報付データを出力する主記憶手段と、前記主記憶手段から前記誤り訂正情報付データを入力し、前記誤り訂正情報付データに含まれる前記訂正情報に基づいて誤り訂正を行い、前記入力データに相当する誤り訂正後データを生成する誤り訂正手段と、前記誤り訂正手段から前記誤り訂正後データを入力する第1データ経路と、前記入力データを前記主記憶手段及び前記誤り訂正手段を介さずに入力する第2データ経路が接続された緩衝用バッファと、前記第1データ経路を介して前記緩衝用バッファに前記誤り訂正後データを入力する第1動作と、前記第2データ経路を介して前記緩衝用バッファに前記入力データを入力する第2動作の開始及び停止を制御すると共に、外部から入力されるリードアドレスに従って、前記緩衝用バッファに格納された前記誤り訂正後データ及び前記入力データを出力データとして出力するよう前記緩衝用バッファを制御する緩衝用バッファ制御手段と、を備えたことを特徴とする。

ことを特徴とする。

【0010】

また、本発明に係る情報処理方法は、外部から入力される入力データに、誤り訂正情報を付加して誤り訂正情報付データを生成し、前記誤り訂正情報付データを主記憶手段に入力し、前記主記憶手段から前記誤り訂正情報付データを入力し、前記誤り訂正情報付データに含まれる前記訂正情報に基づいて誤り訂正を行って、前記入力データに相当する誤り訂正後データを生成し、前記誤り訂正後データを入力する第1データ経路と、前記入力データを前記主記憶手段を介さずに入力する第2データ経路が接続された緩衝用バッファに対し、前記第1データ経路を介して前記緩衝用バッファに前記誤り訂正後データを入力する第1動作と、前記第2データ経路を介して前記緩衝用バッファに前記入力データを入力する第2動作の開始及び停止を制御し、外部から入力されるリードアドレスに従って、前記緩衝用バッファに格納された前記誤り訂正後データ及び前記入力データを出力データとして出力する、ことを特徴とする。

【発明の効果】

【0011】

本発明に係る情報処理装置及び情報処理方法によれば、RAM読み出しデータのECC誤り訂正回路の遅延を隠蔽することより、レイテンシを増加することなくRAMのデータを保護できるようになり、システムダウンの減少が図れるため、性能低下を伴わずに信頼性を向上させることができる。

【図面の簡単な説明】

【0012】

【図1】本発明の実施の形態にかかる情報処理装置の全体構成を示す図である。

【図2】本発明の実施の形態にかかる情報処理装置に含まれる、RAMの構成例を示す図である。

【図3】図2に示すRAMの動作を示すタイミングチャートである。

【図4】本発明の実施の形態に係る情報処理装置の動作を示すタイミングチャートである。

【図5】本発明の実施の形態に係る情報処理装置の動作を示すタイミングチャートである。

【図6】本発明の実施の形態に係る情報処理装置の動作を示すタイミングチャートである。

【図7】従来の情報処理装置の全体構成を示す図である。

【図8】従来の情報処理装置の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0013】

実施の形態.

以下、添付した図面を参照し、本発明の最良な実施の形態について説明する。図1は、本発明の実施の形態に係る情報処理装置の全体構成を示す図であり、図2は、その情報処理装置に含まれるRAMの一例を示す図である。まず、本実施形態の構成の説明にあたり、情報処理装置に内蔵されるRAM22の一例について図2を用いて説明する。RAM22に入力される入力信号は、RAM22への書き込みデータであるRAM入力データ11、RAM22の読み出しアドレスであるRAMリードアドレス12、RAM22の書き込みアドレスであるRAMライトアドレス13、RAM22への書き込みを指示するRAMライトイネーブル14である。RAM22への書き込みは、RAMライトイネーブル14が有効なときにRAMライトアドレス13が示すRAM22のワードに、RAM入力データ11を書き込む。

【0014】

RAM22からの読み出しは、RAMリードアドレス12によって指定されるワードのデータが読み出される。この読み出されたデータは、出力データ15として出力される。RAM22は、FIFOファーストインファーストアウト構成を対象としている。そのため、RAMライトアドレス13は、書き込み指示(RAMライトイネーブル14)が有効になる度に1加算されて、最大ワード数に達すると0に戻り、以降も同様の動作を繰り返す。

【0015】

また、RAMリードアドレス12についても同様に、読み出す度に1加算され、最大ワード数になると0に戻る動作を繰り返す。なお、本説明では、RAM22の入力信号から出力信号(出力データ15)の間の部分を、バッファ1と規定する。

【0016】

次に、本発明の実施の全体構成について図1を用いて説明する。図1中のRAM22は、図2に記載されたものであるとする。図1の情報処理装置では、図2のバッファ1の入出力信号やタイミングはそのままとし、ECC機能を追加しながらもRAM読み出し後のECC訂正回路の遅延を、出力データ15に見せないようにする機能を持つFIFOバッファである。

【0017】

バッファ1は、入力信号として、RAM入力データ11、RAMリードアドレス12、RAMライトアドレス13、RAMライトイネーブル14を入力し、出力信号として出力データ15を出力する。バッファ1は、RAM22、ECC生成部21、ECC誤り訂正部23、緩衝用バッファ24、及び緩衝用バッファ制御部25を有している。

【0018】

ECC生成部21は、RAM入力データ11を入力し、RAM入力データ11に、ECCを付加してECC付きデータ31を生成する。

【0019】

RAM22は、ECC生成部21によって生成された、ECC付きデータ31が格納可能なビット幅を有している。RAM22への書き込みは、RAMライトイネーブル14が有効なときに、RAMライトアドレス13が示すワードに、ECC付きデータ31が格納される。RAM22からの読み出しは、バッファ1に入力されるRAMリードアドレス12ではなく、後述する緩衝用バッファ制御部25で生成されたバッファ内RAMリードアドレス41によって指定されるワードのデータが読み出される。

【0020】

RAMリードアドレス12をRAM22の読み出しアドレスとして使用しないのは、以下の理由による。すなわち、本実施の形態では、緩衝用バッファ24の出力を、出力データ15としているが、緩衝用バッファ24には、RAM22、ECC誤り訂正部23及びを経由してRAM入力データ11に相当する誤り訂正後データ33を入力する第1のデータ経路と、RAM22及びECC誤り訂正部23を介さずにRAM入力データ11を直接緩衝用バッファ24に入力する第2のデータ経路が接続されている。そして、出力データ15として出力されるべきタイミングに対し、第1のデータ経路を介した出力データが遅れる場合には、遅延の小さい第2のデータ経路を介した出力データを、出力データ15として採用する。そのため、この制御を実現するために、RAMリードアドレス12をRAM22の読み出しアドレスとして使用せず、緩衝用バッファ制御部25によってバッファ内RAMリードアドレス41を生成し、RAM22の読み出しアドレスとして用いている。

【0021】

ECC誤り訂正部23は、RAM22から読み出したRAM出力データ32をECCチェックする。ECC誤り訂正部23は、誤りがない場合は読み出したデータをそのまま使用し、1ビット誤りなど訂正可能な範囲のビット誤りがある場合は誤りを訂正する。ECC誤り訂正部23は、このデータをECC誤り訂正後データ33として緩衝用バッファ24に送出する。なお、ECC誤り訂正部23は、ECC部分は送出せず、RAM入力データ11に相当するデータのみをECC誤り訂正後データ33として出力する。

【0022】

緩衝用バッファ24は、ECC誤り訂正部23の遅延を出力データ15に見せないために設けられている。前述したように、緩衝用バッファ24には、RAM22及びECC誤り訂正部23(第1のデータ経路)を介して、RAM入力データ11に相当するデータが入力されると共に、RAM22及びECC誤り訂正部23を介さずに(第2のデータ経路を介して)直接RAM入力データ11が入力される。緩衝用バッファ24は、RAM入力データ11と同じビット幅をもち、数ワードからなるレジスタ構成をとる。緩衝用バッファ24は、レジスタ構成であるため、故障率は低いのでECC保護は行わない。緩衝用バッファ24には、RAM22書き込みデータであるRAM入力データ11またはRAM22読み出し後のECC誤り訂正後データ33が書き込まれ、緩衝用バッファ24の読み出しデータはバッファ1としての出力データ15になる。

【0023】

緩衝用バッファ24に必要な最小ワード数は、緩衝用バッファ24によるレイテンシを隠蔽できる数が必要である。具体的には、緩衝用バッファ24に必要な最小ワード数は、RAMライトイネーブル14が有効になってRAM入力データ11がRAM22に書き込まれてから、書き込まれた同一ワードをRAM22から読み出せるまでにかかるクロック数と、緩衝用バッファ24に入力されたデータが、緩衝用バッファ24から読み出されるまでにかかるクロック数を足した数である。緩衝用バッファ24の読み出しワードは、FIFOとしてのバッファ1の読み出し順と一致するように、初期値0から始まり、読み出し毎に1加算して最大ワードになったところで初期値に戻り繰り返す。

【0024】

書き込みワードに関しては読み出し順と書き込み順が一致しない場合もあるため、読み出し順のワードに対応するように書き込むワードを決定する。ここで、緩衝用バッファ24の書き込み制御には二種類ある。1つめは、RAM22にRAM入力データ11を書き込む際に、RAM22に書き込まれるRAM入力データ11を、RAM22への書き込みに並行して緩衝用バッファ24に格納する制御である。2つめは、RAM読み出し時に、RAM22及びECC誤り訂正部23を経由したRAM入力データ11に相当するECC訂正後データ33を、緩衝用バッファ24に書き込む制御である。

【0025】

そこで、RAM書き込み時に緩衝用バッファ24に並行して緩衝用バッファ24に書き込む場合の緩衝用バッファ24のライトイネーブルを、バッファライトイネーブル(RAMライト)44、そのときの書き込みワードを示すアドレスをバッファライトアドレス(RAMライト)42と呼ぶ。また、RAM22の読み出し後のECC誤り訂正後データ33を緩衝用バッファ24に書き込む場合の緩衝用バッファ24のライトイネーブルを、バッファライトイネーブル(RAMリード)45、そのときの書き込みワードを示すアドレスをRAMリード時のバッファライトアドレス(RAMリード)43と呼ぶこととする。

【0026】

すなわち、本実施の形態の構成では、バッファライトイネーブル(RAMライト)44が有効なときは、バッファライトアドレス(RAMライト)42が示すワードにRAM入力データ11を書き込む。また、バッファライトイネーブル(RAMリード)45が有効なときはバッファライトアドレス(RAMリード)43が示すワードにRAM読み出し後のECC誤り訂正後データ33を書き込む。この二つの書き込み制御は、RAM本来の読み出しタイミングを守るために同時に起こることがある。

【0027】

緩衝用バッファ24からの読み出しについては、バッファリードアドレス46が示すワードのデータを選択して出力する。この緩衝用バッファ24の読み出しデータがバッファ1の出力データ15になるため、出力データ15の遅延は緩衝用バッファ24の読み出し遅延だけになる。

【0028】

緩衝用バッファ制御部25は、RAM22の読み出しワードを示すバッファ内RAMリードアドレス41、緩衝用バッファ24の書き込みワードを示すバッファライトアドレス(RAMライト)42、バッファライトアドレス(RAMリード)43と、書き込み指示であるバッファライトイネーブル(RAMライト)44、バッファライトイネーブル(RAMリード)45、読み出しワードを示すバッファリードアドレス46を生成する機能を持つ。

【0029】

バッファ内RAMリードアドレス41は、RAM22に有効データが格納されているときに、緩衝用バッファ24にまだ書き込まれていない有効データの先頭のワードに向けておくことで、緩衝用バッファ24に空きができたときにすぐに書き込めるようにしておく。ここで、有効データとは、RAM22に格納されたECC付きデータ31のうち、いまだRAM22から緩衝用バッファ24に読み出されておらず、かつ、緩衝用バッファ24に先読みされた(直接入力された)RAM入力データ11に相当するECC付きデータ31を除くデータのことを示すものとする。

【0030】

ここで、バッファライトイネーブル(RAMライト)44が有効になる、すなわち、緩衝用バッファ24に直接入力されるRAM入力データ11が出力データ15として採用されるのは、条件(1)〜(3)を全て満たす場合である。

条件(1)RAMライトイネーブル14が有効であり、

条件(2)次のクロックにおいて緩衝用バッファ24に空きがあることが判明し、

条件(3)RAM22に格納されている有効データの数(ワード数)が、緩衝用バッファ24の空きワード数より少ないか、もしくは空の場合である。

【0031】

また、バッファライトイネーブル(RAMリード)45が有効になる、すなわち、RAM22及びECC誤り訂正部23を経由したECC誤り訂正後データ33が出力データ15として採用されるのは、条件(4)乃至(6)をいずれも満たす場合である。

条件(4)RAM22に格納されている有効データのワード数があるとき、

条件(5)次のクロックにおいて緩衝用バッファ24に空きが生じると判明したとき、

条件(6)RAM22の読み出しデータが有効なときである。

【0032】

なお、前述したように、同時書き込みが行なわれる、すなわち、バッファライトイネーブル(RAMライト)44及びバッファライトイネーブル(RAMリード)45が同時に有効になるのは、条件(1)乃至(3)と条件(4)乃至(6)がそれぞれ同時に成り立つときである。

【0033】

バッファライトアドレス42、43については、バッファ構造によっては必ずしも緩衝用バッファ24の読み出し順通りに緩衝用バッファ24に書き込めるとは限らないため、FIFOのバッファの読み出し順序に追随しているバッファリードアドレス46に適合したワードを探して指定する。バッファリードアドレス46については、RAMリードアドレス12の変化点で1加算していき、最大ワード値に到達したら初期値に戻り、これを繰り返すことでRAMのFIFOバッファの読み出し順を守る。

【0034】

以上の機能により、RAMの読み出し後にECC誤り訂正回路を追加しても、その回路遅延がその後の出力データに見えることなくRAMのFIT数救済につなげることができる。

【0035】

次に、このように構成された情報処理装置の動作について説明する。まず、情報処理装置に含まれるRAM22(図2)の読み出しにかかるクロック数、つまりレイテンシについては、一例として図3に示す場合を対象とする。図3に示すように、RAM22は、RAM22への書き込みタイミング(T2)の次のタイミング(T3)から書き込みデータが有効になり、読み出しアドレスを受け取ったタイミング(T3)の次のタイミング(T4)で読み出しデータを出力できる仕様であるとする。

【0036】

さらに具体的に説明すると、RAM22への書き込みは、T2のタイミングでRAMライトイネーブル14が有効になると、T2のRAMライトアドレス13が示すワード0にT2のRAM入力データ11を書き込む制御を行い、次のタイミングのT3からデータが有効になる。RAM22の読み出しは、T3でワード0を示すRAMリードアドレス12が入力されると、読み出しデータはT4で出力データ15として送出される。ここで、T2でRAMリードアドレス12がワード0を指していても、T3の出力データ15が期待通りではないのは、T2ではワード0にまだ最新のデータが書き込まれていないからである。よって、書き込み指示後に書き込んだデータを読み出せるのは、RAMライトイネーブル14が有効になったタイミングから2クロック後になる。

【0037】

以降では、図3のタイミングを持つRAM22に、本実施の形態に係る機能を追加して情報処理装置を構成した場合の情報処理装置の動作を説明する。なお、図3に示す、RAM22の読み出しタイミングを守りながらECC誤り訂正回路による遅延影響を出力に見せないようにするために最低限必要な緩衝用バッファ24のワード数は、前述したように、RAMライトイネーブル14が有効になってから(RAM入力データ11が書き込まれてから)、書き込まれた同一ワードを読み出せるまでにかかるクロック数と、緩衝用バッファ24に入力されたデータが読み出されるまでにかかるクロック数の和となる。具体的には、図3の仕様のRAM22では、緩衝用バッファ24として最低限必要なワード数は、RAMライトイネーブル14が有効になってから、書き込まれた同一ワードを読み出せるまでにかかる2タイミング分に、緩衝用バッファ24に入力されたデータが読み出されるまでにかかるクロック数1を足した3タイミング分、つまり3ワード分となる。

【0038】

[RAMへの書き込み動作]

はじめに、RAM22への書き込みまでの動作について図4を使って説明する。RAM22への書き込みは、RAM22及びECC誤り訂正部23を経由したECC誤り訂正後データ33が出力データ15として採用されるか否かに関わらず、RAMライトイネーブル14が有効なときに、RAMライトアドレス13が示すワードに、RAM入力データ11にECCを付加したECC付きデータ31を書き込む。具体的には、図4に示すように、T2のタイミングでRAMライトイネーブル14が有効であるため、T2のRAMライトアドレス13が示すワード0に、T2のRAM入力データ11(a)とECC生成部21で生成したT2のRAM入力データ11(a)のECCをあわせたECC付きデータ31(a+)をRAM22に書き込む。

【0039】

[緩衝用バッファへの書き込み動作]

次に、緩衝用バッファ24への書き込み動作について説明する。緩衝用バッファ24への書き込み動作には、(動作1)RAM22及び誤り訂正部23を介さずにRAM入力データ11だけを直接書き込む動作と、(動作2)RAM22から読み出された後のECC誤り訂正後データ33を書き込む動作と、(動作3)RAM入力データ11とECC誤り訂正後データ33の両方を同時に書き込む場合がある。

【0040】

(動作1)RAM22及びECC誤り訂正部23を介さずにRAM入力データ11だけを直接書き込む場合を、図4を用いて説明する。図4のT2のタイミングでは、RAMライトイネーブル14が有効であり(条件1)、RAM22と緩衝用バッファ24は共に空であるので(条件2、3)、条件(1)〜(3)を全て満たすため、バッファライトイネーブル(RAMライト)44が有効になる。そのため、バッファライトアドレス(RAMライト)42が示す緩衝用バッファ24のワード0に、RAM入力データ11を書き込む。また、これと同時に、RAM入力データ11にECCデータを付加したECC付きデータ31を、RAM22にも書き込む。

【0041】

T3、T4でも同様に、RAMライトイネーブル14が有効であり(条件1)、緩衝用バッファ24に空きがあり(条件2)、RAM22の有効ワード数も緩衝用バッファ24のワード数以下であるため(条件3)、T2と同様の動作を行う。

【0042】

T5についても、RAMライトイネーブル14が有効であり(条件1)、前のタイミングのT4で緩衝用バッファ24のワード0が読み出されているため空きができており(条件2)、かつ、RAM22内に格納されているデータは、相当するRAM入力データ11が全てRAM22を介さずに直接緩衝用バッファ24に格納されていているため、有効データのワード数は0であり、緩衝用バッファ24のワード数よりも少ない(条件3)。よって、条件(1)〜(3)を全て満たすため、バッファライトイネーブル(RAMライト)44が有効になり、RAM入力データ11が、緩衝用バッファ24に直接格納される。

【0043】

(動作2)RAM読み出し後のECC誤り訂正後データ33だけを書き込む場合について図5を用いて説明する。図5のT5では、緩衝用バッファ24は全て使われていて、T5以降もRAM22への書き込みが続いているが、緩衝用バッファ24の読み出しがなく空きができないため、(条件2)を満たさない。そのため、T5からT7では緩衝用バッファ24にRAM入力データ11は書き込めず、バッファライトイネーブル(RAMライト)44は無効となる。

【0044】

ここで、バッファライトイネーブル(RAMライト)44が無効となる間でも(T5〜T7)、RAMライトイネーブル14はT5〜T7で有効となっているので、RAM22には継続して、ECC付きデータ(d+)、(e+)、(f+)を書き込む。よって、T8のタイミングでは緩衝用バッファ24に書き込まれていないRAM22の有効データ(d+)、(e+)、(f+)が3ワード分存在している。すなわち、T7〜T10までのRAM22の有効データの数は3であり、緩衝用バッファ24の持つワード数3と同じである(条件4)。なお、有効データのワード数は、RAMライトアドレス、RAMリードアドレスを元に求められるRAMの格納ワード数から、緩衝用バッファ24に直接格納したワード数を引くことにより求めることができる。

【0045】

このとき、バッファ内RAMリードアドレス41は、緩衝用バッファ24に書き込まれていないワードの中で先頭アドレスであるワード3にあらかじめ向けておき、先読みできるようにしておく。その後、T10で、RAMリードアドレス12が次のアドレスに移行することにより、ワード0から出力データ(a)が出力されるため、緩衝用バッファ24のワード0が次のタイミング(T11)で空きができることが判明する(条件5)。そのため、T10で(条件4)及び(条件5)が満たされるので、FIFOで次のワードとなるRAM22の読み出しデータを格納するために、バッファライトイネーブル(RAMリード)45が有効になる。

【0046】

T10において、バッファライトアドレス(RAMリード)43が示す緩衝用バッファ24のワード0に、RAM22のワード3(d+)を読み出し、ECC誤り訂正したECC誤り訂正後データ33(d)を書き込む。これにより、次のタイミングT11において、緩衝用バッファ24のワード0にECC誤り訂正後データ33(d)が格納される。また、T10では、RAM22の次のワードを読み出すため、バッファ内RAMリードアドレス41を1加算してワード4に変更する。T11、T12についても同様である。

【0047】

(動作3)RAM入力データ11とRAM読み出し後のECC誤り訂正後データ33を両方同時に書き込む制御について図6を用いて説明する。T6では、RAMライトアドレス13として入力されたアドレス数は4であり、緩衝用バッファ24に直接格納されたRAM入力データ11のワード数は3であるため、RAM22内に格納されている有効データ数は1(=4−3)である。よって、RAM22内に格納されている有効データ数は、緩衝用バッファ24の有するワード数よりも少ないこととなる(条件4)。また、RAMリードアドレス12がインクリメントされるため、次のタイミングで緩衝用バッファ24のワード0に空きがでることが判明する(条件5)。従って、(条件4)及び(条件5)を満たすため、バッファリードイネーブル(RAMリード)45が有効になり、RAM22及びECC誤り訂正部23を介した誤り訂正後データ33の緩衝用バッファ24への書き込みが可能になる。

【0048】

ここで、T7において、バッファリードイネーブル(RAMリード)45を有効にしてRAM22のワード3から読み出してECC誤り訂正したECC誤り訂正後データ33(d)を緩衝用バッファ24に書き込むと共に、RAMライト時のバッファライトイネーブル46を有効にしてRAM入力データ11(e)についても直接緩衝用バッファ24に書き込む。

【0049】

すなわち、T7において、バッファライトイネーブル(RAMリード)45とバッファライトイネーブル(RAMライト)44の両方がそれぞれ同時に有効になり、RAMのFIFO順序を損なわないようにバッファライトアドレス(RAMリード)43はワード0に、バッファライトアドレス(RAMライト)42はワード1に向け、ワード0にはECC誤り訂正後データ33(d)をワード1にはECC付きデータ31(e)をそれぞれ書き込む。

【0050】

ここで、もし、この二種類の同時書き込みを許さないとすると、T7でRAMライトアドレス13がワード4を示すRAM書き込みデータ(e)については一旦RAM22に格納してから読み出さないとならないため、最短でも緩衝用バッファ24に書き込み指示が出来るのはT9になる。その場合、T9でRAMライトアドレス13がワード5を示すRAM書き込みデータについても同様に最短で緩衝用バッファ24に書き込み指示ができるのがT11になる。そのため、T10でRAMリードアドレス12が示すワード5(データf)の読み出しに間に合わなくなる。よって、このような場合では、二種類の同時書き込みが必要となる。

【0051】

[RAMから緩衝用バッファへの読み出し動作]

RAM22から緩衝用バッファ24への読み出し動作を、図5を用いて説明する。T9のタイミングで読み出したいRAM22のワード、ここではワード3をバッファ内RAMリードアドレス41で示すと、T10でRAM22からデータが読みだされる。T10でRAM22から読み出されたワード3のRAM出力データ32(d+)をECC誤り訂正部23でECCチェックし、誤りがない場合はそのままで、誤りがある場合は訂正して、ECC誤り訂正後データ33(d)として緩衝用バッファ24に送出する。

【0052】

[緩衝用バッファから出力データを読み出す動作]

緩衝用バッファ24の読み出し動作は、図4を用いて説明する。T3のタイミングではRAMリードアドレス12とバッファリードアドレス46は、ともに初期状態のワード0を示しているため、T4では緩衝用バッファ24のワード0のデータが選択されバッファ1の出力データ15となる。次に、T4でRAMリードアドレス12が0から1に変化するため、T5ではバッファリードアドレス46が1加算されてワード1に変わる。よって、T5ではバッファ1の出力データ15は緩衝用バッファ24のワード1のデータになる。T6も同様であり、ワード2まで到達すると次はワード0に戻り、以降繰り返される。

【0053】

次に、このように構成された情報処理装置の効果について説明する。本実施の形態では、RAM22及びECC誤り訂正部23を介してECC誤り訂正後データ33を入力する第1のデータ経路と、RAM22及びECC誤り生成部23を介さず直接RAM入力データ11を入力する第2のデータ経路を、緩衝用バッファ24に接続し、緩衝用バッファ24の出力を、バッファ1の出力データ15として構成する。これにより、第1のデータ経路を介した出力データ15が外部から入力されるRAMリードアドレス12に対して遅れる場合には、遅延の小さい第2のデータ経路を介して直接RAM入力データ11を緩衝用バッファ24に格納する。これにより、出力データ15のECC誤り訂正回路の遅延を隠蔽することができる。

【0054】

また、RAM周りに緩衝用のレジスタ構成のバッファを付加して、RAM読み出しデータのECC誤り訂正回路の遅延を隠蔽することより、レイテンシを増加することなくRAMのデータを保護できるようになり、システムダウンの減少が図れるため、性能低下を伴わずに信頼性を向上させることができる。

【0055】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0056】

1 バッファ

11 RAM入力データ

12 RAMリードアドレス

13 RAMライトアドレス

14 RAMライトイネーブル

15 出力データ

21 ECC生成部

23 ECC誤り訂正部

24 緩衝用バッファ

25 緩衝用バッファ制御部

31 ECC付きデータ

32 RAM出力データ

33 ECC誤り訂正後データ

34、35 信号線

41 リードアドレス

42、43 バッファライトアドレス

44、45 バッファライトイネーブル

46 バッファリードアドレス

【特許請求の範囲】

【請求項1】

外部から入力される入力データに、誤り訂正情報を付加して誤り訂正情報付データを生成する誤り訂正情報付加手段と、

前記誤り訂正情報付加手段から誤り訂正情報付データを入力し、前記誤り訂正情報付データを出力する主記憶手段と、

前記主記憶手段から前記誤り訂正情報付データを入力し、前記誤り訂正情報付データに含まれる前記訂正情報に基づいて誤り訂正を行い、前記入力データに相当する誤り訂正後データを生成する誤り訂正手段と、

前記誤り訂正手段から前記誤り訂正後データを入力する第1データ経路と、前記入力データを前記主記憶手段及び前記誤り訂正手段を介さずに入力する第2データ経路が接続された緩衝用バッファと、

前記第1データ経路を介して前記緩衝用バッファに前記誤り訂正後データを入力する第1動作と、前記第2データ経路を介して前記緩衝用バッファに前記入力データを入力する第2動作の開始及び停止を制御すると共に、外部から入力されるリードアドレスに従って、前記緩衝用バッファに格納された前記誤り訂正後データ及び前記入力データを出力データとして出力するよう前記緩衝用バッファを制御する緩衝用バッファ制御手段と、を備えた情報処理装置。

【請求項2】

前記緩衝用バッファ制御手段は、前記第1動作によって前記緩衝用バッファに入力された前記誤り訂正後データが、外部から入力される前記リードアドレスのタイミングによって前記出力データとして読み出せない場合には、前記第2動作によって前記緩衝用バッファに入力された前記入力データを、前記出力データとして前記緩衝用バッファから出力するよう前記緩衝用バッファの前記第1動作及び前記第2動作の開始及び停止を制御する、請求項1に記載の情報処理装置。

【請求項3】

前記緩衝用バッファに格納することができるデータ単位数は、前記主記憶手段へ前記入力データが書き込まれてから、その入力データを前記主記憶手段から前記緩衝用バッファに読み出すまでにかかるクロック数と、前記誤り訂正後データ又は前記入力データが前記緩衝用バッファに入力されてから読み出されるまでにかかるクロック数の和以上である、請求項1又は2に記載の情報処理装置。

【請求項4】

前記緩衝用バッファ制御手段は、外部から入力されたライトアドレス数から、前記第1動作によって直接前記緩衝用バッファに入力された前記入力データのデータ単位数を減じた値に基づいて、前記緩衝用バッファの前記第1動作及び前記第2動作の開始及び停止を制御する、請求項1乃至3のうちいずれか1項に記載の情報処理装置。

【請求項5】

前記緩衝用バッファ制御手段は、前記主記憶手段から読み出す誤り訂正情報付データを指定する主記憶手段リードアドレスを生成する、請求項1乃至4のうちいずれか1項に記載の情報処理装置。

【請求項6】

外部から入力される入力データに、誤り訂正情報を付加して誤り訂正情報付データを生成し、

前記誤り訂正情報付データを主記憶手段に入力し、

前記主記憶手段から前記誤り訂正情報付データを入力し、前記誤り訂正情報付データに含まれる前記訂正情報に基づいて誤り訂正を行って、前記入力データに相当する誤り訂正後データを生成し、

前記誤り訂正後データを入力する第1データ経路と、前記入力データを前記主記憶手段を介さずに入力する第2データ経路が接続された緩衝用バッファに対し、前記第1データ経路を介して前記緩衝用バッファに前記誤り訂正後データを入力する第1動作と、前記第2データ経路を介して前記緩衝用バッファに前記入力データを入力する第2動作の開始及び停止を制御し、

外部から入力されるリードアドレスに従って、前記緩衝用バッファに格納された前記誤り訂正後データ及び前記入力データを出力データとして出力する、情報処理方法。

【請求項7】

前記第1動作によって前記緩衝用バッファに入力された前記誤り訂正後データが、外部から入力される前記リードアドレスのタイミングによって前記出力データとして読み出せない場合には、前記第2動作によって前記緩衝用バッファに入力された前記入力データを、前記出力データとして前記緩衝用バッファから出力するよう前記緩衝用バッファの前記第1動作及び前記第2動作の開始及び停止を制御する、請求項6に記載の情報処理方法。

【請求項8】

前記緩衝用バッファに格納することができるデータ単位数は、前記主記憶手段へ前記入力データが書き込まれてから、その入力データを前記主記憶手段から前記緩衝用バッファに読み出すまでにかかるクロック数と、前記誤り訂正後データ又は前記入力データが前記緩衝用バッファに入力されてから読み出されるまでにかかるクロック数の和以上である、請求項6又は7に記載の情報処理方法。

【請求項9】

前記緩衝用バッファ制御手段は、外部から入力されたライトアドレス数から、前記第1動作によって直接前記緩衝用バッファに入力された前記入力データのデータ単位数を減じた値に基づいて、前記緩衝用バッファの前記第1動作及び前記第2動作の開始及び停止を制御する、請求項6乃至8のうちいずれか1項に記載の情報処理方法。

【請求項10】

前記主記憶手段から読み出される誤り訂正情報付データを指定する主記憶手段リードアドレスを生成する、請求項6乃至9のうちいずれか1項に記載の情報処理方法。

【請求項1】

外部から入力される入力データに、誤り訂正情報を付加して誤り訂正情報付データを生成する誤り訂正情報付加手段と、

前記誤り訂正情報付加手段から誤り訂正情報付データを入力し、前記誤り訂正情報付データを出力する主記憶手段と、

前記主記憶手段から前記誤り訂正情報付データを入力し、前記誤り訂正情報付データに含まれる前記訂正情報に基づいて誤り訂正を行い、前記入力データに相当する誤り訂正後データを生成する誤り訂正手段と、

前記誤り訂正手段から前記誤り訂正後データを入力する第1データ経路と、前記入力データを前記主記憶手段及び前記誤り訂正手段を介さずに入力する第2データ経路が接続された緩衝用バッファと、

前記第1データ経路を介して前記緩衝用バッファに前記誤り訂正後データを入力する第1動作と、前記第2データ経路を介して前記緩衝用バッファに前記入力データを入力する第2動作の開始及び停止を制御すると共に、外部から入力されるリードアドレスに従って、前記緩衝用バッファに格納された前記誤り訂正後データ及び前記入力データを出力データとして出力するよう前記緩衝用バッファを制御する緩衝用バッファ制御手段と、を備えた情報処理装置。

【請求項2】

前記緩衝用バッファ制御手段は、前記第1動作によって前記緩衝用バッファに入力された前記誤り訂正後データが、外部から入力される前記リードアドレスのタイミングによって前記出力データとして読み出せない場合には、前記第2動作によって前記緩衝用バッファに入力された前記入力データを、前記出力データとして前記緩衝用バッファから出力するよう前記緩衝用バッファの前記第1動作及び前記第2動作の開始及び停止を制御する、請求項1に記載の情報処理装置。

【請求項3】

前記緩衝用バッファに格納することができるデータ単位数は、前記主記憶手段へ前記入力データが書き込まれてから、その入力データを前記主記憶手段から前記緩衝用バッファに読み出すまでにかかるクロック数と、前記誤り訂正後データ又は前記入力データが前記緩衝用バッファに入力されてから読み出されるまでにかかるクロック数の和以上である、請求項1又は2に記載の情報処理装置。

【請求項4】

前記緩衝用バッファ制御手段は、外部から入力されたライトアドレス数から、前記第1動作によって直接前記緩衝用バッファに入力された前記入力データのデータ単位数を減じた値に基づいて、前記緩衝用バッファの前記第1動作及び前記第2動作の開始及び停止を制御する、請求項1乃至3のうちいずれか1項に記載の情報処理装置。

【請求項5】

前記緩衝用バッファ制御手段は、前記主記憶手段から読み出す誤り訂正情報付データを指定する主記憶手段リードアドレスを生成する、請求項1乃至4のうちいずれか1項に記載の情報処理装置。

【請求項6】

外部から入力される入力データに、誤り訂正情報を付加して誤り訂正情報付データを生成し、

前記誤り訂正情報付データを主記憶手段に入力し、

前記主記憶手段から前記誤り訂正情報付データを入力し、前記誤り訂正情報付データに含まれる前記訂正情報に基づいて誤り訂正を行って、前記入力データに相当する誤り訂正後データを生成し、

前記誤り訂正後データを入力する第1データ経路と、前記入力データを前記主記憶手段を介さずに入力する第2データ経路が接続された緩衝用バッファに対し、前記第1データ経路を介して前記緩衝用バッファに前記誤り訂正後データを入力する第1動作と、前記第2データ経路を介して前記緩衝用バッファに前記入力データを入力する第2動作の開始及び停止を制御し、

外部から入力されるリードアドレスに従って、前記緩衝用バッファに格納された前記誤り訂正後データ及び前記入力データを出力データとして出力する、情報処理方法。

【請求項7】

前記第1動作によって前記緩衝用バッファに入力された前記誤り訂正後データが、外部から入力される前記リードアドレスのタイミングによって前記出力データとして読み出せない場合には、前記第2動作によって前記緩衝用バッファに入力された前記入力データを、前記出力データとして前記緩衝用バッファから出力するよう前記緩衝用バッファの前記第1動作及び前記第2動作の開始及び停止を制御する、請求項6に記載の情報処理方法。

【請求項8】

前記緩衝用バッファに格納することができるデータ単位数は、前記主記憶手段へ前記入力データが書き込まれてから、その入力データを前記主記憶手段から前記緩衝用バッファに読み出すまでにかかるクロック数と、前記誤り訂正後データ又は前記入力データが前記緩衝用バッファに入力されてから読み出されるまでにかかるクロック数の和以上である、請求項6又は7に記載の情報処理方法。

【請求項9】

前記緩衝用バッファ制御手段は、外部から入力されたライトアドレス数から、前記第1動作によって直接前記緩衝用バッファに入力された前記入力データのデータ単位数を減じた値に基づいて、前記緩衝用バッファの前記第1動作及び前記第2動作の開始及び停止を制御する、請求項6乃至8のうちいずれか1項に記載の情報処理方法。

【請求項10】

前記主記憶手段から読み出される誤り訂正情報付データを指定する主記憶手段リードアドレスを生成する、請求項6乃至9のうちいずれか1項に記載の情報処理方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−128470(P2012−128470A)

【公開日】平成24年7月5日(2012.7.5)

【国際特許分類】

【出願番号】特願2010−276598(P2010−276598)

【出願日】平成22年12月13日(2010.12.13)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成24年7月5日(2012.7.5)

【国際特許分類】

【出願日】平成22年12月13日(2010.12.13)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]