情報処理装置及び画像形成装置

【課題】一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにする。

【解決手段】監視部37は、第1の送信バッファ25に蓄積されているデータ量が、所定のしきい値を超えていれば、第1のチップ11と第2のチップ13との間でデータの転送遅延が発生するとみなす。しきい値を超えれば、第2にチップ13に配置された複数の第2の機能ブロックのうち予め定められた第2の機能ブロックについては、第2のチップ13において、第2の送信バッファを経由させずに第2の追越用ラインを経由させ、第1のチップ11において、第1の受信バッファ35を経由させずに第1の追越用ライン39を経由させて、宛先となる第1の機能ブロック19へ転送させる。

【解決手段】監視部37は、第1の送信バッファ25に蓄積されているデータ量が、所定のしきい値を超えていれば、第1のチップ11と第2のチップ13との間でデータの転送遅延が発生するとみなす。しきい値を超えれば、第2にチップ13に配置された複数の第2の機能ブロックのうち予め定められた第2の機能ブロックについては、第2のチップ13において、第2の送信バッファを経由させずに第2の追越用ラインを経由させ、第1のチップ11において、第1の受信バッファ35を経由させずに第1の追越用ライン39を経由させて、宛先となる第1の機能ブロック19へ転送させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マスターやスレーブの機能を有する複数の機能ブロックが形成された複数のチップを含む情報処理装置、及び、それを備える画像形成装置に関する。

【背景技術】

【0002】

マスターやスレーブの機能を有する複数の機能ブロックが一つのチップに形成されており、このようなチップ間でデータの転送をする場合、一方のチップの複数の機能ブロックから他方のチップへデータを転送するアクセスが競合すれば、一方のチップ上で調停がなされる。マスターとは制御する側のデバイスであり、CPU(Central Processing Unit)、DMA(Direct Memory Access)コントローラ等を指している。スレーブとは制御される側のデバイスであり、メモリ、I/O(Input/Output)デバイス等を指している。

【0003】

チップ間のインターフェイスとして、例えばPCIエキスプレス(Peripheral Component Interconnect Express)がある。PCIエキスプレスはシリアル転送インターフェイスであり、PCIのようなパラレルインターフェイスの欠点を改良し、高速データ転送を可能とする。PCIエキスプレスではトランザクション層でパケットのやり取りをする。

【0004】

PCIエキスプレスを用いた調停の一例として、トランザクション層のパケットをモニタし、その結果をフィードバック制御してアビトレーションテーブルに反映することにより、実際に伝送されたパケットの量に応じてパケット伝送の優先度を割り当てる技術が提案されている(例えば、特許文献1参照)。

【0005】

また、PCIエキスプレスを用いた調停の他の例として、画像出力部のメモリーリードトランザクションのトラフィククラスの優先度を、画像入力部のメモリーライトトランザクションのトラフィククラスの優先度より高くし、かつ、メモリーリードトランザクションが発行されてからメモリーライトトランザクションが発行されるように、ストリクトプライオリティを設定することで、ライン同期転送のタイミング制約があっても、高速で画像データの出力が可能となり、メモリーリードトランザクションをライン有効期限内に受信でき、複数の画像データの転送を同時に行うことができる技術が提案されている(例えば、特許文献2参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−249816号公報(要約)

【特許文献2】特開2005−354658号公報(要約)

【発明の概要】

【発明が解決しようとする課題】

【0007】

一方のチップから他方チップへ転送されるデータは、一方のチップの送信バッファ(例えば、FIFO(First-In First-Out))を経由して、他方のチップへ転送される。このため、一方のチップの複数の機能ブロックから他方のチップへデータを転送するアクセスが競合することにより、これらの機能ブロック間で調停がされても、送信バッファに既に蓄積されているデータ量が多ければ、調停によって先に他方のチップへ転送するとされたデータであっても、他方のチップへの転送が遅れてしまう。特に、リアルタイム性が有するデータ(例えば、用紙を送りながら、画像データで表される画像を用紙に形成する動作におけるその画像データ)は、転送遅延が生じてはならない。

【0008】

本発明は、マスター及びスレーブの少なくとも一方の機能を有する複数の機能ブロックを含むチップ間において、一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにすることが可能な情報処理装置及びそれを備えた画像形成装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成する本発明の一の局面に係る情報処理装置は、転送するデータを一時格納する第1の送信バッファ及び転送されてきたデータを一時格納する第1の受信バッファを有する第1のインターフェイスと、それぞれがマスター及びスレーブの少なくとも一方の機能を有する複数の第1の機能ブロックと、前記第1のインターフェイスと前記複数の第1の機能ブロックとを接続する第1のバスと、を含む第1のチップと、転送するデータを一時格納する第2の送信バッファ及び転送されてきたデータを一時格納する第2の受信バッファを有し、前記第1のインターフェイスと互いにデータの転送を実行する第2のインターフェイスと、それぞれがマスター及びスレーブの少なくとも一方の機能を有する複数の第2の機能ブロックと、前記第2のインターフェイスと前記複数の第2の機能ブロックとを接続する第2のバスと、を含む第2のチップと、を備え、前記第1のチップは、前記第1の送信バッファ及び前記第1の受信バッファの少なくとも一方に蓄積されているデータ量が、所定のしきい値を超えているか監視する監視部と、前記第2のチップから転送されてきたデータを、前記第1の受信バッファを経由しないで前記第1のバスへ転送する第1の追越用ラインと、前記第2のチップから転送されてきたデータが、(1)前記複数の第2の機能ブロックのうち予め定められた第2の機能ブロックからのデータの場合、前記しきい値を超えていれば、前記第1の追越用ラインを経由して前記第1のバスへ転送する選択をし、前記しきい値を超えていなければ、前記第1の受信バッファを経由して前記第1のバスへ転送する選択をし、(2)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロック以外からのデータの場合、前記しきい値を超えているか否かにかかわらず前記第1の受信バッファを経由して前記第1のバスへ転送する選択をする第1の追越制御部と、を含み、前記第2のチップは、前記第1のチップへ転送するデータを前記第2の送信バッファを経由しないで前記第1のチップへ転送する第2の追越用ラインと、前記第1のチップへ転送するデータが、(3)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロックからのデータの場合、前記しきい値を超えていれば、前記第2の追越用ラインを経由して前記第1のチップへ転送する選択をし、前記しきい値を超えていなければ、前記第2の送信バッファを経由して前記第1のチップへ転送する選択をし、(4)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロック以外からのデータの場合、前記しきい値を超えているか否かにかかわらず前記第2の送信バッファを経由して前記第1のチップへ転送する選択をする第2の追越制御部と、を含む。

【0010】

第1のチップと第2のチップとの間でデータを転送(言い換えれば、送受信)する場合に、第1の送信バッファ、第1の受信バッファ、第2の送信バッファ及び第2の受信バッファの少なくとも一つに、所定量を超えるデータが蓄積すれば(例えば、満杯になれば)、これらのバッファには、所定量を超えてデータが蓄積されている可能性が高い。このため、チップ間でデータの転送遅延が発生する又は発生するおそれがある。本発明の一の局面に係る情報処理装置では、第1の送信バッファ及び第1の受信バッファの少なくとも一方に蓄積されているデータ量が、所定のしきい値を超えていれば、第1のチップと第2のチップとの間でデータの転送遅延が発生するとみなしている。そして、上記しきい値を超えれば、複数の第2の機能ブロックのうち予め定められた第2の機能ブロックについては、第2のチップで第2の送信バッファを経由させずに第2の追越用ラインを経由させ、第1のチップで第1の受信バッファを経由させずに第1の追越用ラインを経由させて、宛先となる第1の機能ブロックへ転送させている。従って、マスター及びスレーブの少なくとも一方の機能を有する複数の機能ブロックを含むチップ間において、一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにすることが可能となる。

【0011】

上記構成において、前記予め定められた第2の機能ブロックは、前記複数の第1の機能ブロックのいずれかにデータの書き込みを要求する第2の機能ブロックである。

【0012】

本発明では、上述したように、第1のチップと第2のチップとの間で、データの転送遅延が発生するとみなした場合、予め定められた第2の機能ブロックからのデータについては、第2の追越用ライン及び第1の追越用ラインを利用して、第2のチップから第1のチップへデータを転送する。第2の機能ブロックが第1の機能ブロックにデータの読み出しをする場合、第1の機能ブロックで読み出されたデータを第2のチップへ転送する動作がされる。この転送では、第2の追越用ライン及び第1の追越用ラインを利用できないので、データの転送遅延が発生する可能性がある。これに対して、第2の機能ブロックが第1の機能ブロックにデータの書き込みをする場合、データの読み出しをする場合と異なり、第1の機能ブロックで読み出されたデータを第2のチップへ転送する動作がされない。従って、予め定められた第2の機能ブロックが、第1の機能ブロックにデータの書き込みを要求する場合、予め定められた第2の機能ブロックが、第1の機能ブロックにデータの読み出しを要求する場合に比べて、データの転送遅延をより確実に防止することが可能となる。

【0013】

上記構成において、前記第2のチップは、前記複数の第2の機能ブロックの少なくとも二つの間で、前記第2のバスの使用権が競合すれば、前記複数の第2の機能ブロックのそれぞれに予め与えられた優先度に従って、前記第2のバスの使用権を調停する調停部を含み、前記予め定められた第2の機能ブロックは、前記優先度が一番高く設定されている第2の機能ブロックを含む。

【0014】

この構成によれば、優先度が一番高く設定されている第2の機能ブロックからのデータについては、転送遅延が生じないようにすることが可能となる。

【0015】

上記構成において、前記第1及び第2の追越制御部は、前記予め定められた第2の機能ブロックを、前記複数の第2の機能ブロックの中から変更することができる。

【0016】

この構成によれば、情報処理装置の動作状況に応じて、予め定められた第2の機能ブロックを変えることが可能となる。

【0017】

上記構成において、前記第1のチップと前記第2のチップとは、シリアルバスによって接続されており、前記第1及び第2のインターフェイスは、シリアル転送インターフェイスである。

【0018】

第1のチップと第2のチップとの間で、データをシリアル転送する場合、データをパラレルからシリアルに、シリアルからパラレルに変換する必要があるので、第1の送信バッファ、第1の受信バッファ、第2の送信バッファ及び第2の受信バッファにデータが蓄積しやすい。従って、第1のチップと第2のチップとの間で、データをシリアル転送する構成において、本発明は特に有効である。

【0019】

上記構成において、前記第1及び第2のインターフェイスは、PCIエキスプレスである。PCIエキスプレスは、シリアル転送インターフェイスの一例である。

【0020】

本発明の他の局面に係る画像形成装置は、上述した情報処理装置と、画像データで表される画像を用紙に形成する画像形成部と、を備える。

【0021】

本発明の他の局面に係る画像形成装置によれば、本発明の一の局面に係る情報処理装置を備えるので、上述した本発明の一の局面に係る情報処理装置と同様の作用及び効果を有する。

【0022】

上記構成において、前記第1及び第2の追越制御部は、前記画像形成部による画像形成時に、前記(1)〜(4)の制御を実行する。また、上記構成において、原稿を読み取って前記画像データを生成する原稿読取部を備え、前記第1及び第2の追越制御部は、前記原稿読取部による原稿読取時に、前記(1)〜(4)の制御を実行する。

【0023】

画像形成部で画像を形成する動作がされているとき、及び原稿読取部で原稿を読み取る動作がされているときは、データ転送にリアルタイム性が要求される。この構成によれば、第1のチップと第2のチップとの間で、データの転送遅延が発生するとみなした場合、複数の第2の機能ブロックのうち、リアルタイム性が要求される第2の機能ブロックからのデータを、第2の追越用ライン及び第1の追越用ラインを利用して宛先となる第1の機能ブロックに転送することができる。従って、リアルタイム性を要求されるデータの転送遅延を防止することが可能となる。

【0024】

上記構成において、前記予め定められた第2の機能ブロックは、前記複数の第1の機能ブロックのいずれかに、前記画像データの書き込みを要求する第2の機能ブロックである。

【0025】

この構成の作用及び効果は、上述した予め定められた第2の機能ブロックが、複数の第1の機能ブロックのいずれかにデータの書き込みを要求している構成と同様である。

【発明の効果】

【0026】

本発明によれば、マスター及びスレーブの少なくとも一方の機能を有する複数の機能ブロックを含むチップ間において、一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにすることが可能となる。

【図面の簡単な説明】

【0027】

【図1】本実施形態に係る画像形成装置の内部構造の概略を示す図である。

【図2】図1に示す画像形成装置の構成を示すブロック図である。

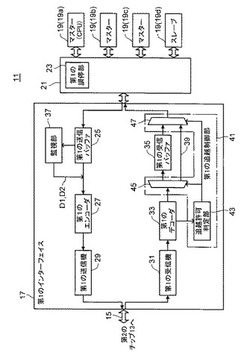

【図3】本実施形態に係る情報処理装置に備えられる第1のチップの構成を示すブロック図である。

【図4】本実施形態に係る情報処理装置に備えられる第2のチップの構成を示すブロック図である。

【図5】本実施形態に係る情報処理装置の動作を説明するフローチャートである。

【発明を実施するための形態】

【0028】

以下、図面に基づいて本発明の実施形態を詳細に説明する。図1は本発明の一実施形態に係る画像形成装置1の内部構造の概略を示す図である。画像形成装置1は例えば、コピー、プリンタ、スキャナ及びファクシミリの機能を有するデジタル複合機に適用することができる。画像形成装置1は装置本体100、装置本体100の上に配置された原稿読取部200、原稿読取部200の上に配置された原稿給送部300及び装置本体100の上部前面に配置された操作部400を備える。

【0029】

原稿給送部300は自動原稿送り装置として機能し、原稿載置部301に置かれた複数枚の原稿を連続的に原稿読取部200に送ることができる。

【0030】

原稿読取部200は露光ランプ等を搭載したキャリッジ201、ガラス等の透明部材により構成された原稿台203、不図示のCCD(Charge Coupled Device)センサー及び原稿読取スリット205を備える。原稿台203に載置された原稿を読み取る場合、キャリッジ201を原稿台203の長手方向に移動させながらCCDセンサーにより原稿を読み取る。これに対して、原稿給送部300から給送された原稿を読み取る場合、キャリッジ201を原稿読取スリット205と対向する位置に移動させて、原稿給送部300から送られてきた原稿を、原稿読取スリット205を通してCCDセンサーにより読み取る。CCDセンサーは読み取った原稿を画像データとして出力する。

【0031】

装置本体100は用紙貯留部101、画像形成部103及び定着部105を備える。用紙貯留部101は装置本体100の最下部に配置されており、用紙の束を貯留することができる用紙トレイ107を備える。用紙トレイ107に貯留された用紙の束において、最上位の用紙がピックアップローラ109の駆動により、用紙搬送路111へ向けて送出される。用紙は用紙搬送路111を通って、画像形成部103へ搬送される。

【0032】

画像形成部103は搬送されてきた用紙にトナー画像を形成する。画像形成部103は感光体ドラム113、露光部115、現像部117及び転写部119を備える。露光部115は画像データ(原稿読取部200から出力された画像データ、パソコンから送信された画像データ、ファクシミリ受信の画像データ等)に対応して変調された光を生成し、一様に帯電された感光体ドラム113の周面に照射する。これにより、感光体ドラム113の周面には画像データに対応する静電潜像が形成される。この状態で感光体ドラム113の周面に現像部117からトナーを供給することにより、周面には画像データに対応するトナー画像が形成される。このトナー画像は転写部119によって先ほど説明した用紙貯留部101から搬送されてきた用紙に転写される。

【0033】

トナー画像が転写された用紙は、定着部105に送られる。定着部105において、トナー画像と用紙に熱と圧力が加えられて、トナー画像は用紙に定着される。用紙はスタックトレイ121又は排紙トレイ123に排紙される。

【0034】

操作部400は操作キー部401と表示部403を備える。表示部403はタッチパネル機能を有しており、ソフトキーを含む画面が表示される。ユーザーは画面を見ながらソフトキーを操作することによって、コピー等の機能の実行に必要な設定等をする。

【0035】

操作キー部401にはハードキーからなる操作キーが設けられている。具体的にはスタートキー405、テンキー407、ストップキー409、リセットキー411、コピー、プリンタ、スキャナ及びファクシミリを切り換えるための機能切換キー413等が設けられている。

【0036】

スタートキー405はコピー、ファクシミリ送信等の動作を開始させるキーである。テンキー407はコピー部数、ファクシミリ番号等の数字を入力するキーである。ストップキー409はコピー動作等を途中で中止させるキーである。リセットキー411は設定された内容を初期設定状態に戻すキーである。

【0037】

機能切換キー413はコピーキー及び送信キー等を備えており、コピー機能、送信機能等を相互に切り替えるキーである。コピーキーを操作すれば、コピーの初期画面が表示部403に表示される。送信キーを操作すれば、ファクシミリ送信及びメール送信の初期画面が表示部403に表示される。

【0038】

図2は図1に示す画像形成装置1の構成を示すブロック図である。画像形成装置1は装置本体100、原稿読取部200、原稿給送部300、操作部400、制御部500及び通信部600がバスによって相互に接続された構成を有する。装置本体100、原稿読取部200、原稿給送部300及び操作部400に関しては既に説明したので、説明を省略する。

【0039】

通信部600はファクシミリ通信部601及びネットワークI/F部603を備える。ファクシミリ通信部601は相手先ファクシミリとの電話回線の接続を制御するNCU(Network Control Unit)及びファクシミリ通信用の信号を変復調する変復調回路を備える。ファクシミリ通信部601は電話回線605に接続される。

【0040】

ネットワークI/F部603はLAN(Local Area Network)607に接続される。ネットワークI/F部603はLAN607に接続されたパソコン等の端末装置との間で通信を実行するための通信インターフェイス回路である。

【0041】

制御部500はCPU(Central Processing Unit)、ROM(Read Only Memory)、RAM(Random Access Memory)及び画像メモリ等を備える。CPUは画像形成装置1を動作させるために必要な制御を、装置本体100等の画像形成装置1の上記構成要素に対して実行する。ROMは画像形成装置1の動作の制御に必要なソフトウェアを記憶している。RAMはソフトウェアの実行時に発生するデータの一時的な記憶及びアプリケーションソフトの記憶等に利用される。画像メモリは画像データ(原稿読取部200から出力された画像データ、パソコンから送信された画像データ、ファクシミリ受信の画像データ等)を一時的に記憶する。

【0042】

制御部500は情報処理装置501の機能を有する。情報処理装置501は第1のチップ11及び第2のチップ13を備える。

【0043】

図3は本実施形態に係る情報処理装置501に備えられる第1のチップ11の構成を示すブロック図であり、図4は第2のチップ13の構成を示すブロック図である。図3に示すように、第1のチップ11は、第1のインターフェイス17、四つの第1の機能ブロック19a,19b,19c,19d、第1のバス21及び第1の調停部23を備える。

【0044】

第1のインターフェイス17は、図4に示す第2のインターフェイス51とシリアルバス15により接続されている。第1のインターフェイス17及び第2のインターフェイス51は、例えば、PCIエキスプレスである。

【0045】

第1の機能ブロック19aはマスター(CPU)として機能する。第1の機能ブロック19b,19cはマスター(DMA)として機能する。第1の機能ブロック19dはスレーブ(例えば、DRAM)として機能する。これらの第1の機能ブロック19a,19b,19c,19dを区別する必要がなければ、第1の機能ブロック19と記載する。複数の第1の機能ブロック19の数は、四つに限定されない。複数の第1の機能ブロック19の構成は、マスターが三つ、スレーブが一つの例で説明しているが、これに限定されない。

【0046】

四つの第1の機能ブロック19のそれぞれ、及び第1のインターフェイス17は、第1のバス21に接続されている。第1のバス21はパラレルバスである。第1のバス21には、第1の調停部23が備えられている。

【0047】

第1の調停部23は、四つの第1の機能ブロック19の少なくとも二つの間で、第1のバス21の使用権が競合すれば、調停をする。例えば、第1の機能ブロック19bから第2のチップ13へデータ(このときはリクエストデータ)を転送する要求、第1の機能ブロック19dから第2のチップ13へデータ(このときはコンプリーションデータ)を転送する要求、第2のチップ13から転送されてきたデータ(このときはリクエスト又はコンプリーションデータ)を第1の機能ブロック19のいずれかに転送する要求が同時に発生したとする。この場合、第1の調停部23は、第1の機能ブロック19のそれぞれに、予め与えられた優先度に従って、第1のバス21の使用権を調停する。

【0048】

第1のインターフェイス17は、第1の送信バッファ25、第1のエンコーダ27、第1の送信機29、第1の受信機31、第1のデコーダ33及び第1の受信バッファ35を備える。

【0049】

第1の送信バッファ25は、FIFOバッファであり、第1の機能ブロック19から第2のチップ13へ転送するデータを一時格納することができる。第1のエンコーダ27は、第1の送信バッファ25を経由して送られてきたデータを、エンコードする。エンコードされたデータは、図示しない変換部でパラレルからシリアルに変換されて、第1の送信機29はそのシリアル化されたデータを、シリアルバス15を用いて、第2のチップ13へ転送する。

【0050】

第1の受信機31は、シリアルバス15を使用して第2のチップ13から転送されてきたデータを受信する。このデータは、図示しない変換部でシリアルからパラレルに変換されて、第1のデコーダ33によりデコードされる。デコードされたデータは、FIFOバッファである第1の受信バッファ35で一時格納されて、第1のバス21を経由して、宛先となる第1の機能ブロック19へ転送される。

【0051】

第1のインターフェイス17は、さらに、監視部37、第1の追越用ライン39及び第1の追越制御部41を備える。監視部37は、第1の送信バッファ25に蓄積されたデータ量が、所定のしきい値を超えているか監視する。本実施形態では、第1の送信バッファ25に蓄積されているデータ量が、所定のしきい値を超えていれば、第1のチップ11と第2のチップ13との間でデータの転送遅延が発生している又は発生するおそれがあるとみなしている。しきい値はこの観点から定められ、例えば、第1の送信バッファ25にデータが満杯に蓄積されていることを示す値である。しきい値は予め定めることができる。

【0052】

監視部37は、第1の送信バッファ25に蓄積されたデータ量が、しきい値以下の状態からしきい値を超えた状態に変化したと判定すれば、追越許可の属性を示すパケットデータD1を第1のエンコーダ27へ送る。一方、監視部37は、第1の送信バッファ25に蓄積されたデータ量が、しきい値を超えている状態からしきい値以下の状態に変化したと判定すれば、追越許可取消の属性を示すパケットデータD2を、第1のエンコーダ27へ送る。パケットデータD1,D2は、シリアルバス15を使用して、第1の送信機29によって第2のチップ13へ転送される。

【0053】

第1の追越用ライン39は、第1の受信バッファ35と並行に配置されている。第2のチップ13から転送されてきたデータは、第1の追越用ライン39によって、第1の受信バッファ35を経由しないで第1のバス21へ転送することができる。

【0054】

第1の追越制御部41は、追越許可判定部43、第1の分配回路45及び第1の選択回路47を備える。第1の分配回路45は、第1のデコーダ33から出力されたデータを、第1の受信バッファ35又は第1の追越用ライン39のいずれに転送するかを切り換える。第1の選択回路47は、第1のバス21へ転送するデータを、第1の受信バッファ35を経由したデータ又は第1の追越用ライン39を経由したデータのいずれにするかを切り換える。

【0055】

追越許可判定部43は、第2のチップ13から転送されてきたデータが、追越許可の属性を備えていると判定すれば、第1の分配回路45及び第1の選択回路47を操作して、第1の追越用ライン39を経由してそのデータを第1のバス21へ転送させる。一方、追越許可判定部43は、第2のチップ13から転送されてきたデータが、追越許可の属性を備えていないと判定すれば、第1の分配回路45及び第1の選択回路47を操作して、第1の受信バッファ35を経由してそのデータを第1のバス21へ転送させる。追越許可の属性については、後で説明する。

【0056】

次に、第2のチップ13について説明する。図4に示すように、第2のチップ13は、第2のインターフェイス51、四つの第2の機能ブロック53a,53b,53c,53d、第2のバス55及び第2の調停部57を備える。

【0057】

第2のインターフェイス51は、図3に示す第1のインターフェイス17とシリアルバス15により接続されている。

【0058】

第2の機能ブロック53aはマスター(CPU)として機能する。第2の機能ブロック53b,53cはマスター(DMA)として機能する。第2の機能ブロック53dはスレーブ(例えば、DRAM)として機能する。これらの第2の機能ブロック53a,53b,53c,53dを区別する必要がなければ、第2の機能ブロック53と記載する。複数の第2の機能ブロック53の数は、四つに限定されない。複数の第2の機能ブロック53の構成は、マスターが三つ、スレーブが一つの例で説明しているが、これに限定されない。

【0059】

四つの第2の機能ブロック53は、第2の調停部57を通して第2のバス55に接続されている。第2のバス55には第2のインターフェイス51が接続されている。第2のバス55はパラレルバスである。

【0060】

四つの第2の機能ブロック53のそれぞれ、及び第2のインターフェイス51は、第2のバス55に接続されている。第2のバス55はパラレルバスである。第2のバス55には、第2の調停部57が備えられている。

【0061】

第2の調停部57は、四つの第2の機能ブロック53の少なくとも二つの間で、第2のバス55の使用権が競合すれば、調停をする。例えば、第2の機能ブロック53bから第1のチップ11へデータ(このときはリクエストデータ)を転送する要求、第2の機能ブロック53dから第1のチップ11へデータ(このときはコンプリーションデータ)を転送する要求、第1のチップ11から転送されてきたデータ(このときはリクエスト又はコンプリーションデータ)を第2の機能ブロック53のいずれかに転送する要求が同時に発生したとする。この場合、第2の調停部57は、第2の機能ブロック53のそれぞれに、予め与えられた優先度に従って、第2のバス55の使用権を調停する。

【0062】

第2のインターフェイス51は、第2の受信機59、第2のデコーダ61、第2の受信バッファ63、第2の送信バッファ65、第2のエンコーダ67及び第2の送信機69を備える。

【0063】

第2の受信機59は、シリアルバス15を使用して第1のチップ11から転送されてきたデータを受信する。このデータは、図示しない変換部でシリアルからパラレルに変換されて、第2のデコーダ61によりデコードされる。デコードされたデータは、FIFOバッファである第2の受信バッファ63で一時格納されて、第2のバス55を経由して、宛先となる第2の機能ブロック53へ転送される。

【0064】

第2の送信バッファ65は、FIFOバッファであり、第2の機能ブロック53から第1のチップ11へ転送するデータを一時格納することができる。第2のエンコーダ67は、第2の送信バッファ65を経由して送られてきたデータを、エンコードする。エンコードされたデータは、図示しない変換部でパラレルからシリアルに変換されて、第2の送信機69はそのシリアル化されたデータを、シリアルバス15を用いて、第1のチップ11へ転送する。

【0065】

第2のインターフェイス51は、さらに、第2の追越用ライン71及び第2の追越制御部73を備える。第2の追越用ライン71は、第2の送信バッファ65と並行に配置されている。第1のチップ11へ転送するデータは、第2の追越用ライン71によって、第2の送信バッファ65を経由しないで第1のチップ11へ転送することができる。

【0066】

第2の追越制御部73は、四つの第2の機能ブロック53のうち予め定められた第2の機能ブロック53が、データを第1のチップ11へ転送する場合、第2の送信バッファ65を経由させたり、第2の追越用ライン71を経由させたりする制御をする。一方、第2の追越制御部73は、予め定められた第2の機能ブロック以外の第2の機能ブロック53が、データを第1のチップ11へ転送する場合、第2の送信バッファ65を経由させる。以下、予め定められた第2の機能ブロック53が、第2の機能ブロック53bを例に説明する。

【0067】

第2の追越制御部73は、追越許可属性付加部75、第2の分配回路77及び第2の選択回路79を備える。第2の分配回路77は、第2のバス55から転送されてきたデータを、第2の送信バッファ65又は第2の追越用ライン71のいずれに転送するかを切り換える。第2の選択回路79は、第2のエンコーダ67へ転送するデータを、第2の送信バッファ65を経由したデータ又は第2の追越用ライン71を経由したデータのいずれにするかを切り換える。

【0068】

第1のチップ11から転送されてきた追越許可の属性を示すパケットデータD1及び追越許可取消の属性を示すパケットデータD2は、第2のデコーダ61でデコードされ、追越許可信号S1及び追越許可取消信号S2として、第2の追越制御部73へ送られる。

【0069】

追越許可信号S1が第2の追越制御部73に送られると、第2の機能ブロック53b(予め定められた第2の機能ブロック)が、データを第1のチップ11へ転送する場合、追越許可属性付加部75は、そのデータのパケットに追越許可の属性を付加する。そして、追越許可属性付加部75は、第2の機能ブロック53bからのデータが、第2のバス55から転送されてくると、第2の分配回路77及び第2の選択回路79を操作して、第2の追越用ライン71を経由してそのデータを第2のエンコーダ67へ転送する。これに対して、追越許可属性付加部75は、第2の機能ブロック53b以外の第2の機能ブロック53からのデータが、第2のバス55から転送されてきた場合、第2の分配回路77及び第2の選択回路79を操作して、第2の送信バッファ65を経由してそのデータを第2のエンコーダ67へ転送する。

【0070】

追越許可取消信号S2が第2の追越制御部73に送られると、追越許可属性付加部75は、第2の機能ブロック53bが、データを第1のチップ11へ転送する場合、そのデータのパケットに追越許可の属性を付加する処理をしない。そして、追越許可属性付加部75は、第2の機能ブロック53bからのデータが、第2のバス55から転送されてくると、第2の機能ブロック53b以外の第2の機能ブロック53からのデータが、第2のバス55から転送されてきた場合と同様に、第2の分配回路77及び第2の選択回路79を操作して、第2の送信バッファ65を経由してそのデータを第2のエンコーダ67へ転送させる。

【0071】

上述したように、図3に示す第1の追越制御部41は、第2のチップ13から転送されてきたデータが、追越許可の属性を備えていると判定すれば、第1の追越用ライン39を経由してそのデータを第1のバス21へ転送させる。一方、第1の追越制御部41は、第2のチップ13から転送されてきたデータが、追越許可の属性を備えていないと判定すれば、第1の受信バッファ35を経由してそのデータを第1のバス21へ転送させる。

【0072】

第1の追越制御部41で実行される制御をまとめると次の通りである。第2のチップ13から転送されてきたデータが、四つの第2の機能ブロック53のうち予め定められた第2の機能ブロック53bからのデータの場合、しきい値を超えていれば、第1の追越用ライン39を経由して第1のバス21へ転送する選択をし、しきい値を超えていなければ、第1の受信バッファ35を経由して第1のバス21へ転送する選択をする。第2のチップ13から転送されてきたデータが、四つ第2の機能ブロック53のうち予め定められた第2の機能ブロック以外からのデータの場合、しきい値を超えているか否かにかかわらず第1の受信バッファ35を経由して第1のバス21へ転送する選択をする。

【0073】

第2の追越制御部73で実行される制御をまとめると次の通りである。第1のチップ11へ転送するデータが、四つの第2の機能ブロック53のうち予め定められた第2の機能ブロック53bからのデータの場合、しきい値を超えていれば、第2の追越用ライン71を経由して第1のチップ11へ転送する選択をし、しきい値を超えていなければ、第2の送信バッファ65を経由して第1のチップ11へ転送する選択をする。第1のチップ11へ転送するデータが、四つの第2の機能ブロック53のうち予め定められた第2の機能ブロック以外からのデータの場合、しきい値を超えているか否かにかかわらず第2の送信バッファ65を経由して第1のチップ11へ転送する選択をする。

【0074】

次に、本実施形態に係る情報処理装置501の動作を説明する。図5は、その動作を説明するフローチャートである。図3に示す監視部37は、第1の送信バッファ25に蓄積されているデータ量が所定のしきい値を超えたか判断する(ステップS1)。データ量がしきい値を超えていなければ、第1のチップ11と第2のチップ13との間で、データの転送遅延が発生しないとみなす。このため、監視部37が、第1の送信バッファ25に蓄積されているデータ量がしきい値を超えたと判断しなければ(ステップS1でNo)、第2の追越制御部73は、四つの第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしているか判断する(ステップS3)。第2の追越制御部73が、第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしていると判断しない場合(ステップS3でNo)、ステップS3の処理が繰り返される。

【0075】

第2の追越制御部73が、第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしていると判断した場合(ステップS3でYes)、第1及び第2の追越制御部41,73は、四つの第2の機能ブロック53のいずれのデータについても、第2の送信バッファ65及び第1の受信バッファ35を経由させる(ステップS5)。従って、四つの第2の機能ブロック53のいずれのデータについても、第2の送信バッファ65及び第1の受信バッファ35を経由して、宛先となる第1の機能ブロック19へ転送される(ステップS7)。

【0076】

監視部37が、第1の送信バッファ25に蓄積されているデータ量がしきい値を超えたと判断すれば(ステップS1でYes)、監視部37は、追越許可の属性を示すパケットデータD1を生成する(ステップS9)。パケットデータD1は、第1のチップ11から第2のチップ13へ転送され、第2のデコーダ61でデコードされて、追越許可信号S1が生成される(ステップS11)。追越許可信号S1は第2の追越制御部73に送られる。

【0077】

第2の追越制御部73は、四つの第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしているか判断する(ステップS13)。第2の追越制御部73が、第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしていると判断しない場合(ステップS13でNo)、ステップS13の処理が繰り返される。

【0078】

第2の追越制御部73が、第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしていると判断した場合(ステップS13でYes)、この第2の機能ブロック53が、第2の機能ブロック53b(予め定められた第2の機能ブロック)か否か判断する(ステップS15)。第2の追越制御部73が、第2の機能ブロック53bと判断しなければ(ステップS15でNo)、ステップS5へ進む。つまり、第2の機能ブロック53b以外の第2の機能ブロック53のデータは、第2の送信バッファ65及び第1の受信バッファ35を経由して、宛先となる第1の機能ブロック19へ転送される。

【0079】

第2の追越制御部73が、第2の機能ブロック53bと判断すれば(ステップS15でYes)、第2の機能ブロック53bのデータに、追越許可の属性を付加する処理をする(ステップS17)。

【0080】

第2の追越制御部73は、第2の機能ブロック53bからのデータを、第2の送信バッファ65を経由させずに、第2の追越用ライン71を経由させて転送する(ステップS19)。そのデータは第2の送信機69によって、第1のチップ11へ転送される。

【0081】

第1の追越制御部41は、データに含まれる追越許可の属性を確認し、第1の受信バッファ35を経由させずに、第1の追越用ライン39を経由させて、データを転送する(ステップS21)。データは第1のバス21を経由して宛先となる第1の機能ブロック19へ転送される(ステップS23)。

【0082】

監視部37は、第1の送信バッファ25に蓄積されているデータ量がしきい値以下になったか判断する(ステップS25)。監視部37は、第1の送信バッファ25に蓄積されているデータ量がしきい値以下になったと判断しない場合(ステップS25でNo)、すなわち、しきい値を超えた状態の場合、ステップS13へ進む。

【0083】

監視部37は、第1の送信バッファ25に蓄積されているデータ量がしきい値以下になったと判断した場合(ステップS25でYes)、監視部37は、追越許可取消の属性を示すパケットデータD2を生成する(ステップS27)。パケットデータD2は、第1のチップ11から第2のチップ13へ転送され、第2のデコーダ61でデコードされて、追越許可取消信号S2が生成される(ステップS29)。追越許可取消信号S2は第2の追越制御部73に送られる。そしてステップS3へ進む。

【0084】

本実施形態の主な効果を説明する。第1のチップ11と第2のチップ13との間でデータを転送(言い換えれば、送受信)する場合に、第1の送信バッファ25、第1の受信バッファ35、第2の送信バッファ65及び第2の受信バッファ63の少なくとも一つに、所定量を超えるデータが蓄積すれば(例えば、満杯になれば)、これらのバッファには、所定量を超えてデータが蓄積されている可能性が高い。このため、チップ11,13間でデータの転送遅延が発生する又は発生するおそれがある。本実施形態に係る情報処理装置501では、第1の送信バッファ25に蓄積されているデータ量が、所定のしきい値を超えていれば、第1のチップ11と第2のチップ13との間でデータの転送遅延が発生しているとみなしている。

【0085】

そして、上記しきい値を超えれば、四つの第2の機能ブロック53のうち予め定められた第2の機能ブロック53については、第2のチップ13で第2の送信バッファ65を経由させずに第2の追越用ライン71を経由させ、第1のチップ11で第1の受信バッファ35を経由させずに第1の追越用ライン39を経由させて、宛先となる第1の機能ブロック19へ転送させている。従って、マスター及びスレーブの少なくとも一方の機能を有する複数の機能ブロックを含むチップ間において、一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにすることが可能となる。

【0086】

以上のことから、本実施形態によれば、第1の送信バッファ25に蓄積されたデータ量が満杯になっても、第1のチップ11及び第2のチップ13の単価を上げたり、これらのチップでのソフトウェアの処理を煩雑にしたりすることなく、予め定められた第2の機能ブロック53のデータについては、待たせることなく、第1のチップ11で受信することができる。

【0087】

また、本実施形態では、上述したように、第1のチップ11と第2のチップ13との間で、データの転送遅延が発生しているとみなした場合、予め定められた第2の機能ブロック53からのデータについては、第2の追越用ライン71及び第1の追越用ライン39を利用して、第2のチップ13から第1のチップ11へデータを転送する。第2の機能ブロック53が第1の機能ブロック19にデータの読み出しをする場合、第1の機能ブロック19で読み出されたデータを第2のチップ13へ転送する動作がされる。この転送では、第2の追越用ライン71及び第1の追越用ライン39を利用できないので、データの転送遅延が発生する可能性がある。これに対して、第2の機能ブロック53が第1の機能ブロック19にデータの書き込みをする場合、データの読み出しをする場合と異なり、第1の機能ブロック19で読み出されたデータを第2のチップ13へ転送する動作がされない。従って、予め定められた第2の機能ブロック53が、第1の機能ブロック19にデータの書き込みを要求する場合、予め定められた第2の機能ブロック53が、第1の機能ブロック19にデータの読み出しを要求する場合に比べて、データの転送遅延をより確実に防止することが可能となる。

【0088】

本実施形態では、第1のインターフェイス17及び第2のインターフェイス51が、シリアル転送インターフェイスである。第1のチップ11と第2のチップ13との間で、データをシリアル転送する場合、データをパラレルからシリアルに、シリアルからパラレルに変換する必要があるので、第1の送信バッファ25、第1の受信バッファ35、第2の送信バッファ65及び第2の受信バッファ63にデータが蓄積しやすい。しかしながら本実施形態によれば、上述したように、第2の機能ブロック53から第1の機能ブロック19へデータを転送する場合に、予め定められた第2の機能ブロック53からのデータについては、転送遅延が生じないようにすることが可能となる。

【0089】

本実施形態によれば、画像形成部103による画像形成時及び原稿読取部200による原稿読取時に、図5で説明した制御を実行させることができる。画像形成部103で画像を形成する動作がされているとき、及び、原稿読取部200で原稿を読み取る動作がされているときは、データの転送にリアルタイム性が要求される。本実施形態によれば、第1のチップ11と第2のチップ13との間で、データの転送遅延が発生するとみなした場合、四つ第2の機能ブロック53のうち、リアルタイム性が要求される第2の機能ブロック53からのデータ(例えば、画像データ)を、第2の追越用ライン71及び第1の追越用ライン39を利用して宛先となる第1の機能ブロック19に転送することができる。従って、リアルタイム性を要求されるデータの転送遅延を防止することが可能となる。

【0090】

本実施形態の変形例を説明する。第1の変形例は以下の通りである。第2の調停部57は、四つ第2の機能ブロック53の少なくとも二つの間で、第2のバス55の使用権が競合すれば、四つ第2の機能ブロック53のそれぞれに予め与えられた優先度に従って、第2のバス55の使用権を調停する。第1の変形例では、予め定められた第2の機能ブロック53が、優先度が一番高く設定されている第2の機能ブロック53を含む。第1の変形例によれば、優先度が一番高く設定されている第2の機能ブロック53からのデータについては、転送遅延が生じないようにすることが可能となる。

【0091】

第2の変形例は次の通りである。第1の追越制御部41及び第2の追越制御部73は、予め定められた第2の機能ブロック53を、四つ第2の機能ブロック53の中から変更することができる。第2の変形例によれば、情報処理装置501の動作状況に応じて、予め定められた第2の機能ブロック53を変えることが可能となる。

【0092】

第3の変形例は次の通りである。本実施形態では、第1の送信バッファ25に蓄積されているデータが所定量を超えれば、第2の追越用ライン71及び第1の追越用ライン39を利用して、第2のチップ13から第1のチップ11へデータを転送できることを説明した。第3の変形例は、第1の受信バッファ35に蓄積されているデータが所定量を超えれば、第2の追越用ライン71及び第1の追越用ライン39を利用して、第2のチップ13から第1のチップ11へデータを転送させる。

【0093】

第4の変形例は次の通りである。本実施形態では、第2のチップ13から第1のチップ11へデータを転送するときに、第2の追越用ライン71及び第1の追越用ライン39を用いてデータを転送できることを説明した。第4の変形例では、それに加えて、第1のチップ11から第2のチップ13へデータを転送するときに、追越用ラインを用いてデータを転送できるようにする。この場合、第1のチップ11に、第1の送信バッファ25に並行して追越用ラインを配置し、第2の追加制御部73と同様の追加制御部を配置する。第2のチップ13に、第2の受信バッファ63に並行して追越用ラインを配置し、第1の追加制御部41と同様の追加制御部を配置し、第2の送信バッファ65に蓄積されているデータを監視するために、監視部37と同様のものを配置する。

【符号の説明】

【0094】

1 画像形成装置

11 第1のチップ

13 第2のチップ

17 第1のインターフェイス

19,19a〜19d 第1の機能ブロック

21 第1のバス

25 第1の送信バッファ

35 第1の受信バッファ

39 第1の追越用ライン

41 第1の追越制御部

51 第2のインターフェイス

53,53a〜53d 第2の機能ブロック

55 第2のバス

63 第2の受信バッファ

65 第2の送信バッファ

71 第2の追越用ライン

73 第2の追越制御部

501 情報処理装置

【技術分野】

【0001】

本発明は、マスターやスレーブの機能を有する複数の機能ブロックが形成された複数のチップを含む情報処理装置、及び、それを備える画像形成装置に関する。

【背景技術】

【0002】

マスターやスレーブの機能を有する複数の機能ブロックが一つのチップに形成されており、このようなチップ間でデータの転送をする場合、一方のチップの複数の機能ブロックから他方のチップへデータを転送するアクセスが競合すれば、一方のチップ上で調停がなされる。マスターとは制御する側のデバイスであり、CPU(Central Processing Unit)、DMA(Direct Memory Access)コントローラ等を指している。スレーブとは制御される側のデバイスであり、メモリ、I/O(Input/Output)デバイス等を指している。

【0003】

チップ間のインターフェイスとして、例えばPCIエキスプレス(Peripheral Component Interconnect Express)がある。PCIエキスプレスはシリアル転送インターフェイスであり、PCIのようなパラレルインターフェイスの欠点を改良し、高速データ転送を可能とする。PCIエキスプレスではトランザクション層でパケットのやり取りをする。

【0004】

PCIエキスプレスを用いた調停の一例として、トランザクション層のパケットをモニタし、その結果をフィードバック制御してアビトレーションテーブルに反映することにより、実際に伝送されたパケットの量に応じてパケット伝送の優先度を割り当てる技術が提案されている(例えば、特許文献1参照)。

【0005】

また、PCIエキスプレスを用いた調停の他の例として、画像出力部のメモリーリードトランザクションのトラフィククラスの優先度を、画像入力部のメモリーライトトランザクションのトラフィククラスの優先度より高くし、かつ、メモリーリードトランザクションが発行されてからメモリーライトトランザクションが発行されるように、ストリクトプライオリティを設定することで、ライン同期転送のタイミング制約があっても、高速で画像データの出力が可能となり、メモリーリードトランザクションをライン有効期限内に受信でき、複数の画像データの転送を同時に行うことができる技術が提案されている(例えば、特許文献2参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−249816号公報(要約)

【特許文献2】特開2005−354658号公報(要約)

【発明の概要】

【発明が解決しようとする課題】

【0007】

一方のチップから他方チップへ転送されるデータは、一方のチップの送信バッファ(例えば、FIFO(First-In First-Out))を経由して、他方のチップへ転送される。このため、一方のチップの複数の機能ブロックから他方のチップへデータを転送するアクセスが競合することにより、これらの機能ブロック間で調停がされても、送信バッファに既に蓄積されているデータ量が多ければ、調停によって先に他方のチップへ転送するとされたデータであっても、他方のチップへの転送が遅れてしまう。特に、リアルタイム性が有するデータ(例えば、用紙を送りながら、画像データで表される画像を用紙に形成する動作におけるその画像データ)は、転送遅延が生じてはならない。

【0008】

本発明は、マスター及びスレーブの少なくとも一方の機能を有する複数の機能ブロックを含むチップ間において、一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにすることが可能な情報処理装置及びそれを備えた画像形成装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成する本発明の一の局面に係る情報処理装置は、転送するデータを一時格納する第1の送信バッファ及び転送されてきたデータを一時格納する第1の受信バッファを有する第1のインターフェイスと、それぞれがマスター及びスレーブの少なくとも一方の機能を有する複数の第1の機能ブロックと、前記第1のインターフェイスと前記複数の第1の機能ブロックとを接続する第1のバスと、を含む第1のチップと、転送するデータを一時格納する第2の送信バッファ及び転送されてきたデータを一時格納する第2の受信バッファを有し、前記第1のインターフェイスと互いにデータの転送を実行する第2のインターフェイスと、それぞれがマスター及びスレーブの少なくとも一方の機能を有する複数の第2の機能ブロックと、前記第2のインターフェイスと前記複数の第2の機能ブロックとを接続する第2のバスと、を含む第2のチップと、を備え、前記第1のチップは、前記第1の送信バッファ及び前記第1の受信バッファの少なくとも一方に蓄積されているデータ量が、所定のしきい値を超えているか監視する監視部と、前記第2のチップから転送されてきたデータを、前記第1の受信バッファを経由しないで前記第1のバスへ転送する第1の追越用ラインと、前記第2のチップから転送されてきたデータが、(1)前記複数の第2の機能ブロックのうち予め定められた第2の機能ブロックからのデータの場合、前記しきい値を超えていれば、前記第1の追越用ラインを経由して前記第1のバスへ転送する選択をし、前記しきい値を超えていなければ、前記第1の受信バッファを経由して前記第1のバスへ転送する選択をし、(2)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロック以外からのデータの場合、前記しきい値を超えているか否かにかかわらず前記第1の受信バッファを経由して前記第1のバスへ転送する選択をする第1の追越制御部と、を含み、前記第2のチップは、前記第1のチップへ転送するデータを前記第2の送信バッファを経由しないで前記第1のチップへ転送する第2の追越用ラインと、前記第1のチップへ転送するデータが、(3)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロックからのデータの場合、前記しきい値を超えていれば、前記第2の追越用ラインを経由して前記第1のチップへ転送する選択をし、前記しきい値を超えていなければ、前記第2の送信バッファを経由して前記第1のチップへ転送する選択をし、(4)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロック以外からのデータの場合、前記しきい値を超えているか否かにかかわらず前記第2の送信バッファを経由して前記第1のチップへ転送する選択をする第2の追越制御部と、を含む。

【0010】

第1のチップと第2のチップとの間でデータを転送(言い換えれば、送受信)する場合に、第1の送信バッファ、第1の受信バッファ、第2の送信バッファ及び第2の受信バッファの少なくとも一つに、所定量を超えるデータが蓄積すれば(例えば、満杯になれば)、これらのバッファには、所定量を超えてデータが蓄積されている可能性が高い。このため、チップ間でデータの転送遅延が発生する又は発生するおそれがある。本発明の一の局面に係る情報処理装置では、第1の送信バッファ及び第1の受信バッファの少なくとも一方に蓄積されているデータ量が、所定のしきい値を超えていれば、第1のチップと第2のチップとの間でデータの転送遅延が発生するとみなしている。そして、上記しきい値を超えれば、複数の第2の機能ブロックのうち予め定められた第2の機能ブロックについては、第2のチップで第2の送信バッファを経由させずに第2の追越用ラインを経由させ、第1のチップで第1の受信バッファを経由させずに第1の追越用ラインを経由させて、宛先となる第1の機能ブロックへ転送させている。従って、マスター及びスレーブの少なくとも一方の機能を有する複数の機能ブロックを含むチップ間において、一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにすることが可能となる。

【0011】

上記構成において、前記予め定められた第2の機能ブロックは、前記複数の第1の機能ブロックのいずれかにデータの書き込みを要求する第2の機能ブロックである。

【0012】

本発明では、上述したように、第1のチップと第2のチップとの間で、データの転送遅延が発生するとみなした場合、予め定められた第2の機能ブロックからのデータについては、第2の追越用ライン及び第1の追越用ラインを利用して、第2のチップから第1のチップへデータを転送する。第2の機能ブロックが第1の機能ブロックにデータの読み出しをする場合、第1の機能ブロックで読み出されたデータを第2のチップへ転送する動作がされる。この転送では、第2の追越用ライン及び第1の追越用ラインを利用できないので、データの転送遅延が発生する可能性がある。これに対して、第2の機能ブロックが第1の機能ブロックにデータの書き込みをする場合、データの読み出しをする場合と異なり、第1の機能ブロックで読み出されたデータを第2のチップへ転送する動作がされない。従って、予め定められた第2の機能ブロックが、第1の機能ブロックにデータの書き込みを要求する場合、予め定められた第2の機能ブロックが、第1の機能ブロックにデータの読み出しを要求する場合に比べて、データの転送遅延をより確実に防止することが可能となる。

【0013】

上記構成において、前記第2のチップは、前記複数の第2の機能ブロックの少なくとも二つの間で、前記第2のバスの使用権が競合すれば、前記複数の第2の機能ブロックのそれぞれに予め与えられた優先度に従って、前記第2のバスの使用権を調停する調停部を含み、前記予め定められた第2の機能ブロックは、前記優先度が一番高く設定されている第2の機能ブロックを含む。

【0014】

この構成によれば、優先度が一番高く設定されている第2の機能ブロックからのデータについては、転送遅延が生じないようにすることが可能となる。

【0015】

上記構成において、前記第1及び第2の追越制御部は、前記予め定められた第2の機能ブロックを、前記複数の第2の機能ブロックの中から変更することができる。

【0016】

この構成によれば、情報処理装置の動作状況に応じて、予め定められた第2の機能ブロックを変えることが可能となる。

【0017】

上記構成において、前記第1のチップと前記第2のチップとは、シリアルバスによって接続されており、前記第1及び第2のインターフェイスは、シリアル転送インターフェイスである。

【0018】

第1のチップと第2のチップとの間で、データをシリアル転送する場合、データをパラレルからシリアルに、シリアルからパラレルに変換する必要があるので、第1の送信バッファ、第1の受信バッファ、第2の送信バッファ及び第2の受信バッファにデータが蓄積しやすい。従って、第1のチップと第2のチップとの間で、データをシリアル転送する構成において、本発明は特に有効である。

【0019】

上記構成において、前記第1及び第2のインターフェイスは、PCIエキスプレスである。PCIエキスプレスは、シリアル転送インターフェイスの一例である。

【0020】

本発明の他の局面に係る画像形成装置は、上述した情報処理装置と、画像データで表される画像を用紙に形成する画像形成部と、を備える。

【0021】

本発明の他の局面に係る画像形成装置によれば、本発明の一の局面に係る情報処理装置を備えるので、上述した本発明の一の局面に係る情報処理装置と同様の作用及び効果を有する。

【0022】

上記構成において、前記第1及び第2の追越制御部は、前記画像形成部による画像形成時に、前記(1)〜(4)の制御を実行する。また、上記構成において、原稿を読み取って前記画像データを生成する原稿読取部を備え、前記第1及び第2の追越制御部は、前記原稿読取部による原稿読取時に、前記(1)〜(4)の制御を実行する。

【0023】

画像形成部で画像を形成する動作がされているとき、及び原稿読取部で原稿を読み取る動作がされているときは、データ転送にリアルタイム性が要求される。この構成によれば、第1のチップと第2のチップとの間で、データの転送遅延が発生するとみなした場合、複数の第2の機能ブロックのうち、リアルタイム性が要求される第2の機能ブロックからのデータを、第2の追越用ライン及び第1の追越用ラインを利用して宛先となる第1の機能ブロックに転送することができる。従って、リアルタイム性を要求されるデータの転送遅延を防止することが可能となる。

【0024】

上記構成において、前記予め定められた第2の機能ブロックは、前記複数の第1の機能ブロックのいずれかに、前記画像データの書き込みを要求する第2の機能ブロックである。

【0025】

この構成の作用及び効果は、上述した予め定められた第2の機能ブロックが、複数の第1の機能ブロックのいずれかにデータの書き込みを要求している構成と同様である。

【発明の効果】

【0026】

本発明によれば、マスター及びスレーブの少なくとも一方の機能を有する複数の機能ブロックを含むチップ間において、一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにすることが可能となる。

【図面の簡単な説明】

【0027】

【図1】本実施形態に係る画像形成装置の内部構造の概略を示す図である。

【図2】図1に示す画像形成装置の構成を示すブロック図である。

【図3】本実施形態に係る情報処理装置に備えられる第1のチップの構成を示すブロック図である。

【図4】本実施形態に係る情報処理装置に備えられる第2のチップの構成を示すブロック図である。

【図5】本実施形態に係る情報処理装置の動作を説明するフローチャートである。

【発明を実施するための形態】

【0028】

以下、図面に基づいて本発明の実施形態を詳細に説明する。図1は本発明の一実施形態に係る画像形成装置1の内部構造の概略を示す図である。画像形成装置1は例えば、コピー、プリンタ、スキャナ及びファクシミリの機能を有するデジタル複合機に適用することができる。画像形成装置1は装置本体100、装置本体100の上に配置された原稿読取部200、原稿読取部200の上に配置された原稿給送部300及び装置本体100の上部前面に配置された操作部400を備える。

【0029】

原稿給送部300は自動原稿送り装置として機能し、原稿載置部301に置かれた複数枚の原稿を連続的に原稿読取部200に送ることができる。

【0030】

原稿読取部200は露光ランプ等を搭載したキャリッジ201、ガラス等の透明部材により構成された原稿台203、不図示のCCD(Charge Coupled Device)センサー及び原稿読取スリット205を備える。原稿台203に載置された原稿を読み取る場合、キャリッジ201を原稿台203の長手方向に移動させながらCCDセンサーにより原稿を読み取る。これに対して、原稿給送部300から給送された原稿を読み取る場合、キャリッジ201を原稿読取スリット205と対向する位置に移動させて、原稿給送部300から送られてきた原稿を、原稿読取スリット205を通してCCDセンサーにより読み取る。CCDセンサーは読み取った原稿を画像データとして出力する。

【0031】

装置本体100は用紙貯留部101、画像形成部103及び定着部105を備える。用紙貯留部101は装置本体100の最下部に配置されており、用紙の束を貯留することができる用紙トレイ107を備える。用紙トレイ107に貯留された用紙の束において、最上位の用紙がピックアップローラ109の駆動により、用紙搬送路111へ向けて送出される。用紙は用紙搬送路111を通って、画像形成部103へ搬送される。

【0032】

画像形成部103は搬送されてきた用紙にトナー画像を形成する。画像形成部103は感光体ドラム113、露光部115、現像部117及び転写部119を備える。露光部115は画像データ(原稿読取部200から出力された画像データ、パソコンから送信された画像データ、ファクシミリ受信の画像データ等)に対応して変調された光を生成し、一様に帯電された感光体ドラム113の周面に照射する。これにより、感光体ドラム113の周面には画像データに対応する静電潜像が形成される。この状態で感光体ドラム113の周面に現像部117からトナーを供給することにより、周面には画像データに対応するトナー画像が形成される。このトナー画像は転写部119によって先ほど説明した用紙貯留部101から搬送されてきた用紙に転写される。

【0033】

トナー画像が転写された用紙は、定着部105に送られる。定着部105において、トナー画像と用紙に熱と圧力が加えられて、トナー画像は用紙に定着される。用紙はスタックトレイ121又は排紙トレイ123に排紙される。

【0034】

操作部400は操作キー部401と表示部403を備える。表示部403はタッチパネル機能を有しており、ソフトキーを含む画面が表示される。ユーザーは画面を見ながらソフトキーを操作することによって、コピー等の機能の実行に必要な設定等をする。

【0035】

操作キー部401にはハードキーからなる操作キーが設けられている。具体的にはスタートキー405、テンキー407、ストップキー409、リセットキー411、コピー、プリンタ、スキャナ及びファクシミリを切り換えるための機能切換キー413等が設けられている。

【0036】

スタートキー405はコピー、ファクシミリ送信等の動作を開始させるキーである。テンキー407はコピー部数、ファクシミリ番号等の数字を入力するキーである。ストップキー409はコピー動作等を途中で中止させるキーである。リセットキー411は設定された内容を初期設定状態に戻すキーである。

【0037】

機能切換キー413はコピーキー及び送信キー等を備えており、コピー機能、送信機能等を相互に切り替えるキーである。コピーキーを操作すれば、コピーの初期画面が表示部403に表示される。送信キーを操作すれば、ファクシミリ送信及びメール送信の初期画面が表示部403に表示される。

【0038】

図2は図1に示す画像形成装置1の構成を示すブロック図である。画像形成装置1は装置本体100、原稿読取部200、原稿給送部300、操作部400、制御部500及び通信部600がバスによって相互に接続された構成を有する。装置本体100、原稿読取部200、原稿給送部300及び操作部400に関しては既に説明したので、説明を省略する。

【0039】

通信部600はファクシミリ通信部601及びネットワークI/F部603を備える。ファクシミリ通信部601は相手先ファクシミリとの電話回線の接続を制御するNCU(Network Control Unit)及びファクシミリ通信用の信号を変復調する変復調回路を備える。ファクシミリ通信部601は電話回線605に接続される。

【0040】

ネットワークI/F部603はLAN(Local Area Network)607に接続される。ネットワークI/F部603はLAN607に接続されたパソコン等の端末装置との間で通信を実行するための通信インターフェイス回路である。

【0041】

制御部500はCPU(Central Processing Unit)、ROM(Read Only Memory)、RAM(Random Access Memory)及び画像メモリ等を備える。CPUは画像形成装置1を動作させるために必要な制御を、装置本体100等の画像形成装置1の上記構成要素に対して実行する。ROMは画像形成装置1の動作の制御に必要なソフトウェアを記憶している。RAMはソフトウェアの実行時に発生するデータの一時的な記憶及びアプリケーションソフトの記憶等に利用される。画像メモリは画像データ(原稿読取部200から出力された画像データ、パソコンから送信された画像データ、ファクシミリ受信の画像データ等)を一時的に記憶する。

【0042】

制御部500は情報処理装置501の機能を有する。情報処理装置501は第1のチップ11及び第2のチップ13を備える。

【0043】

図3は本実施形態に係る情報処理装置501に備えられる第1のチップ11の構成を示すブロック図であり、図4は第2のチップ13の構成を示すブロック図である。図3に示すように、第1のチップ11は、第1のインターフェイス17、四つの第1の機能ブロック19a,19b,19c,19d、第1のバス21及び第1の調停部23を備える。

【0044】

第1のインターフェイス17は、図4に示す第2のインターフェイス51とシリアルバス15により接続されている。第1のインターフェイス17及び第2のインターフェイス51は、例えば、PCIエキスプレスである。

【0045】

第1の機能ブロック19aはマスター(CPU)として機能する。第1の機能ブロック19b,19cはマスター(DMA)として機能する。第1の機能ブロック19dはスレーブ(例えば、DRAM)として機能する。これらの第1の機能ブロック19a,19b,19c,19dを区別する必要がなければ、第1の機能ブロック19と記載する。複数の第1の機能ブロック19の数は、四つに限定されない。複数の第1の機能ブロック19の構成は、マスターが三つ、スレーブが一つの例で説明しているが、これに限定されない。

【0046】

四つの第1の機能ブロック19のそれぞれ、及び第1のインターフェイス17は、第1のバス21に接続されている。第1のバス21はパラレルバスである。第1のバス21には、第1の調停部23が備えられている。

【0047】

第1の調停部23は、四つの第1の機能ブロック19の少なくとも二つの間で、第1のバス21の使用権が競合すれば、調停をする。例えば、第1の機能ブロック19bから第2のチップ13へデータ(このときはリクエストデータ)を転送する要求、第1の機能ブロック19dから第2のチップ13へデータ(このときはコンプリーションデータ)を転送する要求、第2のチップ13から転送されてきたデータ(このときはリクエスト又はコンプリーションデータ)を第1の機能ブロック19のいずれかに転送する要求が同時に発生したとする。この場合、第1の調停部23は、第1の機能ブロック19のそれぞれに、予め与えられた優先度に従って、第1のバス21の使用権を調停する。

【0048】

第1のインターフェイス17は、第1の送信バッファ25、第1のエンコーダ27、第1の送信機29、第1の受信機31、第1のデコーダ33及び第1の受信バッファ35を備える。

【0049】

第1の送信バッファ25は、FIFOバッファであり、第1の機能ブロック19から第2のチップ13へ転送するデータを一時格納することができる。第1のエンコーダ27は、第1の送信バッファ25を経由して送られてきたデータを、エンコードする。エンコードされたデータは、図示しない変換部でパラレルからシリアルに変換されて、第1の送信機29はそのシリアル化されたデータを、シリアルバス15を用いて、第2のチップ13へ転送する。

【0050】

第1の受信機31は、シリアルバス15を使用して第2のチップ13から転送されてきたデータを受信する。このデータは、図示しない変換部でシリアルからパラレルに変換されて、第1のデコーダ33によりデコードされる。デコードされたデータは、FIFOバッファである第1の受信バッファ35で一時格納されて、第1のバス21を経由して、宛先となる第1の機能ブロック19へ転送される。

【0051】

第1のインターフェイス17は、さらに、監視部37、第1の追越用ライン39及び第1の追越制御部41を備える。監視部37は、第1の送信バッファ25に蓄積されたデータ量が、所定のしきい値を超えているか監視する。本実施形態では、第1の送信バッファ25に蓄積されているデータ量が、所定のしきい値を超えていれば、第1のチップ11と第2のチップ13との間でデータの転送遅延が発生している又は発生するおそれがあるとみなしている。しきい値はこの観点から定められ、例えば、第1の送信バッファ25にデータが満杯に蓄積されていることを示す値である。しきい値は予め定めることができる。

【0052】

監視部37は、第1の送信バッファ25に蓄積されたデータ量が、しきい値以下の状態からしきい値を超えた状態に変化したと判定すれば、追越許可の属性を示すパケットデータD1を第1のエンコーダ27へ送る。一方、監視部37は、第1の送信バッファ25に蓄積されたデータ量が、しきい値を超えている状態からしきい値以下の状態に変化したと判定すれば、追越許可取消の属性を示すパケットデータD2を、第1のエンコーダ27へ送る。パケットデータD1,D2は、シリアルバス15を使用して、第1の送信機29によって第2のチップ13へ転送される。

【0053】

第1の追越用ライン39は、第1の受信バッファ35と並行に配置されている。第2のチップ13から転送されてきたデータは、第1の追越用ライン39によって、第1の受信バッファ35を経由しないで第1のバス21へ転送することができる。

【0054】

第1の追越制御部41は、追越許可判定部43、第1の分配回路45及び第1の選択回路47を備える。第1の分配回路45は、第1のデコーダ33から出力されたデータを、第1の受信バッファ35又は第1の追越用ライン39のいずれに転送するかを切り換える。第1の選択回路47は、第1のバス21へ転送するデータを、第1の受信バッファ35を経由したデータ又は第1の追越用ライン39を経由したデータのいずれにするかを切り換える。

【0055】

追越許可判定部43は、第2のチップ13から転送されてきたデータが、追越許可の属性を備えていると判定すれば、第1の分配回路45及び第1の選択回路47を操作して、第1の追越用ライン39を経由してそのデータを第1のバス21へ転送させる。一方、追越許可判定部43は、第2のチップ13から転送されてきたデータが、追越許可の属性を備えていないと判定すれば、第1の分配回路45及び第1の選択回路47を操作して、第1の受信バッファ35を経由してそのデータを第1のバス21へ転送させる。追越許可の属性については、後で説明する。

【0056】

次に、第2のチップ13について説明する。図4に示すように、第2のチップ13は、第2のインターフェイス51、四つの第2の機能ブロック53a,53b,53c,53d、第2のバス55及び第2の調停部57を備える。

【0057】

第2のインターフェイス51は、図3に示す第1のインターフェイス17とシリアルバス15により接続されている。

【0058】

第2の機能ブロック53aはマスター(CPU)として機能する。第2の機能ブロック53b,53cはマスター(DMA)として機能する。第2の機能ブロック53dはスレーブ(例えば、DRAM)として機能する。これらの第2の機能ブロック53a,53b,53c,53dを区別する必要がなければ、第2の機能ブロック53と記載する。複数の第2の機能ブロック53の数は、四つに限定されない。複数の第2の機能ブロック53の構成は、マスターが三つ、スレーブが一つの例で説明しているが、これに限定されない。

【0059】

四つの第2の機能ブロック53は、第2の調停部57を通して第2のバス55に接続されている。第2のバス55には第2のインターフェイス51が接続されている。第2のバス55はパラレルバスである。

【0060】

四つの第2の機能ブロック53のそれぞれ、及び第2のインターフェイス51は、第2のバス55に接続されている。第2のバス55はパラレルバスである。第2のバス55には、第2の調停部57が備えられている。

【0061】

第2の調停部57は、四つの第2の機能ブロック53の少なくとも二つの間で、第2のバス55の使用権が競合すれば、調停をする。例えば、第2の機能ブロック53bから第1のチップ11へデータ(このときはリクエストデータ)を転送する要求、第2の機能ブロック53dから第1のチップ11へデータ(このときはコンプリーションデータ)を転送する要求、第1のチップ11から転送されてきたデータ(このときはリクエスト又はコンプリーションデータ)を第2の機能ブロック53のいずれかに転送する要求が同時に発生したとする。この場合、第2の調停部57は、第2の機能ブロック53のそれぞれに、予め与えられた優先度に従って、第2のバス55の使用権を調停する。

【0062】

第2のインターフェイス51は、第2の受信機59、第2のデコーダ61、第2の受信バッファ63、第2の送信バッファ65、第2のエンコーダ67及び第2の送信機69を備える。

【0063】

第2の受信機59は、シリアルバス15を使用して第1のチップ11から転送されてきたデータを受信する。このデータは、図示しない変換部でシリアルからパラレルに変換されて、第2のデコーダ61によりデコードされる。デコードされたデータは、FIFOバッファである第2の受信バッファ63で一時格納されて、第2のバス55を経由して、宛先となる第2の機能ブロック53へ転送される。

【0064】

第2の送信バッファ65は、FIFOバッファであり、第2の機能ブロック53から第1のチップ11へ転送するデータを一時格納することができる。第2のエンコーダ67は、第2の送信バッファ65を経由して送られてきたデータを、エンコードする。エンコードされたデータは、図示しない変換部でパラレルからシリアルに変換されて、第2の送信機69はそのシリアル化されたデータを、シリアルバス15を用いて、第1のチップ11へ転送する。

【0065】

第2のインターフェイス51は、さらに、第2の追越用ライン71及び第2の追越制御部73を備える。第2の追越用ライン71は、第2の送信バッファ65と並行に配置されている。第1のチップ11へ転送するデータは、第2の追越用ライン71によって、第2の送信バッファ65を経由しないで第1のチップ11へ転送することができる。

【0066】

第2の追越制御部73は、四つの第2の機能ブロック53のうち予め定められた第2の機能ブロック53が、データを第1のチップ11へ転送する場合、第2の送信バッファ65を経由させたり、第2の追越用ライン71を経由させたりする制御をする。一方、第2の追越制御部73は、予め定められた第2の機能ブロック以外の第2の機能ブロック53が、データを第1のチップ11へ転送する場合、第2の送信バッファ65を経由させる。以下、予め定められた第2の機能ブロック53が、第2の機能ブロック53bを例に説明する。

【0067】

第2の追越制御部73は、追越許可属性付加部75、第2の分配回路77及び第2の選択回路79を備える。第2の分配回路77は、第2のバス55から転送されてきたデータを、第2の送信バッファ65又は第2の追越用ライン71のいずれに転送するかを切り換える。第2の選択回路79は、第2のエンコーダ67へ転送するデータを、第2の送信バッファ65を経由したデータ又は第2の追越用ライン71を経由したデータのいずれにするかを切り換える。

【0068】

第1のチップ11から転送されてきた追越許可の属性を示すパケットデータD1及び追越許可取消の属性を示すパケットデータD2は、第2のデコーダ61でデコードされ、追越許可信号S1及び追越許可取消信号S2として、第2の追越制御部73へ送られる。

【0069】

追越許可信号S1が第2の追越制御部73に送られると、第2の機能ブロック53b(予め定められた第2の機能ブロック)が、データを第1のチップ11へ転送する場合、追越許可属性付加部75は、そのデータのパケットに追越許可の属性を付加する。そして、追越許可属性付加部75は、第2の機能ブロック53bからのデータが、第2のバス55から転送されてくると、第2の分配回路77及び第2の選択回路79を操作して、第2の追越用ライン71を経由してそのデータを第2のエンコーダ67へ転送する。これに対して、追越許可属性付加部75は、第2の機能ブロック53b以外の第2の機能ブロック53からのデータが、第2のバス55から転送されてきた場合、第2の分配回路77及び第2の選択回路79を操作して、第2の送信バッファ65を経由してそのデータを第2のエンコーダ67へ転送する。

【0070】

追越許可取消信号S2が第2の追越制御部73に送られると、追越許可属性付加部75は、第2の機能ブロック53bが、データを第1のチップ11へ転送する場合、そのデータのパケットに追越許可の属性を付加する処理をしない。そして、追越許可属性付加部75は、第2の機能ブロック53bからのデータが、第2のバス55から転送されてくると、第2の機能ブロック53b以外の第2の機能ブロック53からのデータが、第2のバス55から転送されてきた場合と同様に、第2の分配回路77及び第2の選択回路79を操作して、第2の送信バッファ65を経由してそのデータを第2のエンコーダ67へ転送させる。

【0071】

上述したように、図3に示す第1の追越制御部41は、第2のチップ13から転送されてきたデータが、追越許可の属性を備えていると判定すれば、第1の追越用ライン39を経由してそのデータを第1のバス21へ転送させる。一方、第1の追越制御部41は、第2のチップ13から転送されてきたデータが、追越許可の属性を備えていないと判定すれば、第1の受信バッファ35を経由してそのデータを第1のバス21へ転送させる。

【0072】

第1の追越制御部41で実行される制御をまとめると次の通りである。第2のチップ13から転送されてきたデータが、四つの第2の機能ブロック53のうち予め定められた第2の機能ブロック53bからのデータの場合、しきい値を超えていれば、第1の追越用ライン39を経由して第1のバス21へ転送する選択をし、しきい値を超えていなければ、第1の受信バッファ35を経由して第1のバス21へ転送する選択をする。第2のチップ13から転送されてきたデータが、四つ第2の機能ブロック53のうち予め定められた第2の機能ブロック以外からのデータの場合、しきい値を超えているか否かにかかわらず第1の受信バッファ35を経由して第1のバス21へ転送する選択をする。

【0073】

第2の追越制御部73で実行される制御をまとめると次の通りである。第1のチップ11へ転送するデータが、四つの第2の機能ブロック53のうち予め定められた第2の機能ブロック53bからのデータの場合、しきい値を超えていれば、第2の追越用ライン71を経由して第1のチップ11へ転送する選択をし、しきい値を超えていなければ、第2の送信バッファ65を経由して第1のチップ11へ転送する選択をする。第1のチップ11へ転送するデータが、四つの第2の機能ブロック53のうち予め定められた第2の機能ブロック以外からのデータの場合、しきい値を超えているか否かにかかわらず第2の送信バッファ65を経由して第1のチップ11へ転送する選択をする。

【0074】

次に、本実施形態に係る情報処理装置501の動作を説明する。図5は、その動作を説明するフローチャートである。図3に示す監視部37は、第1の送信バッファ25に蓄積されているデータ量が所定のしきい値を超えたか判断する(ステップS1)。データ量がしきい値を超えていなければ、第1のチップ11と第2のチップ13との間で、データの転送遅延が発生しないとみなす。このため、監視部37が、第1の送信バッファ25に蓄積されているデータ量がしきい値を超えたと判断しなければ(ステップS1でNo)、第2の追越制御部73は、四つの第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしているか判断する(ステップS3)。第2の追越制御部73が、第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしていると判断しない場合(ステップS3でNo)、ステップS3の処理が繰り返される。

【0075】

第2の追越制御部73が、第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしていると判断した場合(ステップS3でYes)、第1及び第2の追越制御部41,73は、四つの第2の機能ブロック53のいずれのデータについても、第2の送信バッファ65及び第1の受信バッファ35を経由させる(ステップS5)。従って、四つの第2の機能ブロック53のいずれのデータについても、第2の送信バッファ65及び第1の受信バッファ35を経由して、宛先となる第1の機能ブロック19へ転送される(ステップS7)。

【0076】

監視部37が、第1の送信バッファ25に蓄積されているデータ量がしきい値を超えたと判断すれば(ステップS1でYes)、監視部37は、追越許可の属性を示すパケットデータD1を生成する(ステップS9)。パケットデータD1は、第1のチップ11から第2のチップ13へ転送され、第2のデコーダ61でデコードされて、追越許可信号S1が生成される(ステップS11)。追越許可信号S1は第2の追越制御部73に送られる。

【0077】

第2の追越制御部73は、四つの第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしているか判断する(ステップS13)。第2の追越制御部73が、第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしていると判断しない場合(ステップS13でNo)、ステップS13の処理が繰り返される。

【0078】

第2の追越制御部73が、第2の機能ブロック53のいずれかが、第1の機能ブロック19のいずれかにデータを転送する要求をしていると判断した場合(ステップS13でYes)、この第2の機能ブロック53が、第2の機能ブロック53b(予め定められた第2の機能ブロック)か否か判断する(ステップS15)。第2の追越制御部73が、第2の機能ブロック53bと判断しなければ(ステップS15でNo)、ステップS5へ進む。つまり、第2の機能ブロック53b以外の第2の機能ブロック53のデータは、第2の送信バッファ65及び第1の受信バッファ35を経由して、宛先となる第1の機能ブロック19へ転送される。

【0079】

第2の追越制御部73が、第2の機能ブロック53bと判断すれば(ステップS15でYes)、第2の機能ブロック53bのデータに、追越許可の属性を付加する処理をする(ステップS17)。

【0080】

第2の追越制御部73は、第2の機能ブロック53bからのデータを、第2の送信バッファ65を経由させずに、第2の追越用ライン71を経由させて転送する(ステップS19)。そのデータは第2の送信機69によって、第1のチップ11へ転送される。

【0081】

第1の追越制御部41は、データに含まれる追越許可の属性を確認し、第1の受信バッファ35を経由させずに、第1の追越用ライン39を経由させて、データを転送する(ステップS21)。データは第1のバス21を経由して宛先となる第1の機能ブロック19へ転送される(ステップS23)。

【0082】

監視部37は、第1の送信バッファ25に蓄積されているデータ量がしきい値以下になったか判断する(ステップS25)。監視部37は、第1の送信バッファ25に蓄積されているデータ量がしきい値以下になったと判断しない場合(ステップS25でNo)、すなわち、しきい値を超えた状態の場合、ステップS13へ進む。

【0083】

監視部37は、第1の送信バッファ25に蓄積されているデータ量がしきい値以下になったと判断した場合(ステップS25でYes)、監視部37は、追越許可取消の属性を示すパケットデータD2を生成する(ステップS27)。パケットデータD2は、第1のチップ11から第2のチップ13へ転送され、第2のデコーダ61でデコードされて、追越許可取消信号S2が生成される(ステップS29)。追越許可取消信号S2は第2の追越制御部73に送られる。そしてステップS3へ進む。

【0084】

本実施形態の主な効果を説明する。第1のチップ11と第2のチップ13との間でデータを転送(言い換えれば、送受信)する場合に、第1の送信バッファ25、第1の受信バッファ35、第2の送信バッファ65及び第2の受信バッファ63の少なくとも一つに、所定量を超えるデータが蓄積すれば(例えば、満杯になれば)、これらのバッファには、所定量を超えてデータが蓄積されている可能性が高い。このため、チップ11,13間でデータの転送遅延が発生する又は発生するおそれがある。本実施形態に係る情報処理装置501では、第1の送信バッファ25に蓄積されているデータ量が、所定のしきい値を超えていれば、第1のチップ11と第2のチップ13との間でデータの転送遅延が発生しているとみなしている。

【0085】

そして、上記しきい値を超えれば、四つの第2の機能ブロック53のうち予め定められた第2の機能ブロック53については、第2のチップ13で第2の送信バッファ65を経由させずに第2の追越用ライン71を経由させ、第1のチップ11で第1の受信バッファ35を経由させずに第1の追越用ライン39を経由させて、宛先となる第1の機能ブロック19へ転送させている。従って、マスター及びスレーブの少なくとも一方の機能を有する複数の機能ブロックを含むチップ間において、一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにすることが可能となる。

【0086】

以上のことから、本実施形態によれば、第1の送信バッファ25に蓄積されたデータ量が満杯になっても、第1のチップ11及び第2のチップ13の単価を上げたり、これらのチップでのソフトウェアの処理を煩雑にしたりすることなく、予め定められた第2の機能ブロック53のデータについては、待たせることなく、第1のチップ11で受信することができる。

【0087】

また、本実施形態では、上述したように、第1のチップ11と第2のチップ13との間で、データの転送遅延が発生しているとみなした場合、予め定められた第2の機能ブロック53からのデータについては、第2の追越用ライン71及び第1の追越用ライン39を利用して、第2のチップ13から第1のチップ11へデータを転送する。第2の機能ブロック53が第1の機能ブロック19にデータの読み出しをする場合、第1の機能ブロック19で読み出されたデータを第2のチップ13へ転送する動作がされる。この転送では、第2の追越用ライン71及び第1の追越用ライン39を利用できないので、データの転送遅延が発生する可能性がある。これに対して、第2の機能ブロック53が第1の機能ブロック19にデータの書き込みをする場合、データの読み出しをする場合と異なり、第1の機能ブロック19で読み出されたデータを第2のチップ13へ転送する動作がされない。従って、予め定められた第2の機能ブロック53が、第1の機能ブロック19にデータの書き込みを要求する場合、予め定められた第2の機能ブロック53が、第1の機能ブロック19にデータの読み出しを要求する場合に比べて、データの転送遅延をより確実に防止することが可能となる。

【0088】

本実施形態では、第1のインターフェイス17及び第2のインターフェイス51が、シリアル転送インターフェイスである。第1のチップ11と第2のチップ13との間で、データをシリアル転送する場合、データをパラレルからシリアルに、シリアルからパラレルに変換する必要があるので、第1の送信バッファ25、第1の受信バッファ35、第2の送信バッファ65及び第2の受信バッファ63にデータが蓄積しやすい。しかしながら本実施形態によれば、上述したように、第2の機能ブロック53から第1の機能ブロック19へデータを転送する場合に、予め定められた第2の機能ブロック53からのデータについては、転送遅延が生じないようにすることが可能となる。

【0089】

本実施形態によれば、画像形成部103による画像形成時及び原稿読取部200による原稿読取時に、図5で説明した制御を実行させることができる。画像形成部103で画像を形成する動作がされているとき、及び、原稿読取部200で原稿を読み取る動作がされているときは、データの転送にリアルタイム性が要求される。本実施形態によれば、第1のチップ11と第2のチップ13との間で、データの転送遅延が発生するとみなした場合、四つ第2の機能ブロック53のうち、リアルタイム性が要求される第2の機能ブロック53からのデータ(例えば、画像データ)を、第2の追越用ライン71及び第1の追越用ライン39を利用して宛先となる第1の機能ブロック19に転送することができる。従って、リアルタイム性を要求されるデータの転送遅延を防止することが可能となる。

【0090】

本実施形態の変形例を説明する。第1の変形例は以下の通りである。第2の調停部57は、四つ第2の機能ブロック53の少なくとも二つの間で、第2のバス55の使用権が競合すれば、四つ第2の機能ブロック53のそれぞれに予め与えられた優先度に従って、第2のバス55の使用権を調停する。第1の変形例では、予め定められた第2の機能ブロック53が、優先度が一番高く設定されている第2の機能ブロック53を含む。第1の変形例によれば、優先度が一番高く設定されている第2の機能ブロック53からのデータについては、転送遅延が生じないようにすることが可能となる。

【0091】

第2の変形例は次の通りである。第1の追越制御部41及び第2の追越制御部73は、予め定められた第2の機能ブロック53を、四つ第2の機能ブロック53の中から変更することができる。第2の変形例によれば、情報処理装置501の動作状況に応じて、予め定められた第2の機能ブロック53を変えることが可能となる。

【0092】

第3の変形例は次の通りである。本実施形態では、第1の送信バッファ25に蓄積されているデータが所定量を超えれば、第2の追越用ライン71及び第1の追越用ライン39を利用して、第2のチップ13から第1のチップ11へデータを転送できることを説明した。第3の変形例は、第1の受信バッファ35に蓄積されているデータが所定量を超えれば、第2の追越用ライン71及び第1の追越用ライン39を利用して、第2のチップ13から第1のチップ11へデータを転送させる。

【0093】

第4の変形例は次の通りである。本実施形態では、第2のチップ13から第1のチップ11へデータを転送するときに、第2の追越用ライン71及び第1の追越用ライン39を用いてデータを転送できることを説明した。第4の変形例では、それに加えて、第1のチップ11から第2のチップ13へデータを転送するときに、追越用ラインを用いてデータを転送できるようにする。この場合、第1のチップ11に、第1の送信バッファ25に並行して追越用ラインを配置し、第2の追加制御部73と同様の追加制御部を配置する。第2のチップ13に、第2の受信バッファ63に並行して追越用ラインを配置し、第1の追加制御部41と同様の追加制御部を配置し、第2の送信バッファ65に蓄積されているデータを監視するために、監視部37と同様のものを配置する。

【符号の説明】

【0094】

1 画像形成装置

11 第1のチップ

13 第2のチップ

17 第1のインターフェイス

19,19a〜19d 第1の機能ブロック

21 第1のバス

25 第1の送信バッファ

35 第1の受信バッファ

39 第1の追越用ライン

41 第1の追越制御部

51 第2のインターフェイス

53,53a〜53d 第2の機能ブロック

55 第2のバス

63 第2の受信バッファ

65 第2の送信バッファ

71 第2の追越用ライン

73 第2の追越制御部

501 情報処理装置

【特許請求の範囲】

【請求項1】

転送するデータを一時格納する第1の送信バッファ及び転送されてきたデータを一時格納する第1の受信バッファを有する第1のインターフェイスと、それぞれがマスター及びスレーブの少なくとも一方の機能を有する複数の第1の機能ブロックと、前記第1のインターフェイスと前記複数の第1の機能ブロックとを接続する第1のバスと、を含む第1のチップと、

転送するデータを一時格納する第2の送信バッファ及び転送されてきたデータを一時格納する第2の受信バッファを有し、前記第1のインターフェイスと互いにデータの転送を実行する第2のインターフェイスと、それぞれがマスター及びスレーブの少なくとも一方の機能を有する複数の第2の機能ブロックと、前記第2のインターフェイスと前記複数の第2の機能ブロックとを接続する第2のバスと、を含む第2のチップと、を備え、

前記第1のチップは、

前記第1の送信バッファ及び前記第1の受信バッファの少なくとも一方に蓄積されているデータ量が、所定のしきい値を超えているか監視する監視部と、

前記第2のチップから転送されてきたデータを、前記第1の受信バッファを経由しないで前記第1のバスへ転送する第1の追越用ラインと、

前記第2のチップから転送されてきたデータが、(1)前記複数の第2の機能ブロックのうち予め定められた第2の機能ブロックからのデータの場合、前記しきい値を超えていれば、前記第1の追越用ラインを経由して前記第1のバスへ転送する選択をし、前記しきい値を超えていなければ、前記第1の受信バッファを経由して前記第1のバスへ転送する選択をし、(2)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロック以外からのデータの場合、前記しきい値を超えているか否かにかかわらず前記第1の受信バッファを経由して前記第1のバスへ転送する選択をする第1の追越制御部と、を含み、

前記第2のチップは、

前記第1のチップへ転送するデータを前記第2の送信バッファを経由しないで前記第1のチップへ転送する第2の追越用ラインと、

前記第1のチップへ転送するデータが、(3)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロックからのデータの場合、前記しきい値を超えていれば、前記第2の追越用ラインを経由して前記第1のチップへ転送する選択をし、前記しきい値を超えていなければ、前記第2の送信バッファを経由して前記第1のチップへ転送する選択をし、(4)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロック以外からのデータの場合、前記しきい値を超えているか否かにかかわらず前記第2の送信バッファを経由して前記第1のチップへ転送する選択をする第2の追越制御部と、を含む情報処理装置。

【請求項2】

前記予め定められた第2の機能ブロックは、前記複数の第1の機能ブロックのいずれかにデータの書き込みを要求する第2の機能ブロックである請求項1に記載の情報処理装置。

【請求項3】

前記第2のチップは、前記複数の第2の機能ブロックの少なくとも二つの間で、前記第2のバスの使用権が競合すれば、前記複数の第2の機能ブロックのそれぞれに予め与えられた優先度に従って、前記第2のバスの使用権を調停する調停部を含み、

前記予め定められた第2の機能ブロックは、前記優先度が一番高く設定されている第2の機能ブロックを含む請求項1又は2に記載の情報処理装置。

【請求項4】

前記第1及び第2の追越制御部は、前記予め定められた第2の機能ブロックを、前記複数の第2の機能ブロックの中から変更することができる請求項1〜3のいずれか一項に記載の情報処理装置。

【請求項5】

前記第1のチップと前記第2のチップとは、シリアルバスによって接続されており、

前記第1及び第2のインターフェイスは、シリアル転送インターフェイスである請求項1〜4のいずれか一項に記載の情報処理装置。

【請求項6】

前記第1及び第2のインターフェイスは、PCIエキスプレスである請求項5に記載の情報処理装置。

【請求項7】

請求項1〜6のいずれか一項に記載の情報処理装置と、

画像データで表される画像を用紙に形成する画像形成部と、を備える画像形成装置。

【請求項8】

前記第1及び第2の追越制御部は、前記画像形成部による画像形成時に、前記(1)〜(4)の制御を実行する請求項7に記載の画像形成装置。

【請求項9】

原稿を読み取って前記画像データを生成する原稿読取部を備え、

前記第1及び第2の追越制御部は、前記原稿読取部による原稿読取時に、前記(1)〜(4)の制御を実行する請求項7又は8に記載の画像形成装置。

【請求項10】

前記予め定められた第2の機能ブロックは、前記複数の第1の機能ブロックのいずれかに、前記画像データの書き込みを要求する第2の機能ブロックである請求項7〜9のいずれか一項に記載の画像形成装置。

【請求項1】

転送するデータを一時格納する第1の送信バッファ及び転送されてきたデータを一時格納する第1の受信バッファを有する第1のインターフェイスと、それぞれがマスター及びスレーブの少なくとも一方の機能を有する複数の第1の機能ブロックと、前記第1のインターフェイスと前記複数の第1の機能ブロックとを接続する第1のバスと、を含む第1のチップと、

転送するデータを一時格納する第2の送信バッファ及び転送されてきたデータを一時格納する第2の受信バッファを有し、前記第1のインターフェイスと互いにデータの転送を実行する第2のインターフェイスと、それぞれがマスター及びスレーブの少なくとも一方の機能を有する複数の第2の機能ブロックと、前記第2のインターフェイスと前記複数の第2の機能ブロックとを接続する第2のバスと、を含む第2のチップと、を備え、

前記第1のチップは、

前記第1の送信バッファ及び前記第1の受信バッファの少なくとも一方に蓄積されているデータ量が、所定のしきい値を超えているか監視する監視部と、

前記第2のチップから転送されてきたデータを、前記第1の受信バッファを経由しないで前記第1のバスへ転送する第1の追越用ラインと、

前記第2のチップから転送されてきたデータが、(1)前記複数の第2の機能ブロックのうち予め定められた第2の機能ブロックからのデータの場合、前記しきい値を超えていれば、前記第1の追越用ラインを経由して前記第1のバスへ転送する選択をし、前記しきい値を超えていなければ、前記第1の受信バッファを経由して前記第1のバスへ転送する選択をし、(2)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロック以外からのデータの場合、前記しきい値を超えているか否かにかかわらず前記第1の受信バッファを経由して前記第1のバスへ転送する選択をする第1の追越制御部と、を含み、

前記第2のチップは、

前記第1のチップへ転送するデータを前記第2の送信バッファを経由しないで前記第1のチップへ転送する第2の追越用ラインと、

前記第1のチップへ転送するデータが、(3)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロックからのデータの場合、前記しきい値を超えていれば、前記第2の追越用ラインを経由して前記第1のチップへ転送する選択をし、前記しきい値を超えていなければ、前記第2の送信バッファを経由して前記第1のチップへ転送する選択をし、(4)前記複数の第2の機能ブロックのうち前記予め定められた第2の機能ブロック以外からのデータの場合、前記しきい値を超えているか否かにかかわらず前記第2の送信バッファを経由して前記第1のチップへ転送する選択をする第2の追越制御部と、を含む情報処理装置。

【請求項2】

前記予め定められた第2の機能ブロックは、前記複数の第1の機能ブロックのいずれかにデータの書き込みを要求する第2の機能ブロックである請求項1に記載の情報処理装置。

【請求項3】

前記第2のチップは、前記複数の第2の機能ブロックの少なくとも二つの間で、前記第2のバスの使用権が競合すれば、前記複数の第2の機能ブロックのそれぞれに予め与えられた優先度に従って、前記第2のバスの使用権を調停する調停部を含み、

前記予め定められた第2の機能ブロックは、前記優先度が一番高く設定されている第2の機能ブロックを含む請求項1又は2に記載の情報処理装置。

【請求項4】

前記第1及び第2の追越制御部は、前記予め定められた第2の機能ブロックを、前記複数の第2の機能ブロックの中から変更することができる請求項1〜3のいずれか一項に記載の情報処理装置。

【請求項5】

前記第1のチップと前記第2のチップとは、シリアルバスによって接続されており、

前記第1及び第2のインターフェイスは、シリアル転送インターフェイスである請求項1〜4のいずれか一項に記載の情報処理装置。

【請求項6】

前記第1及び第2のインターフェイスは、PCIエキスプレスである請求項5に記載の情報処理装置。

【請求項7】

請求項1〜6のいずれか一項に記載の情報処理装置と、

画像データで表される画像を用紙に形成する画像形成部と、を備える画像形成装置。

【請求項8】

前記第1及び第2の追越制御部は、前記画像形成部による画像形成時に、前記(1)〜(4)の制御を実行する請求項7に記載の画像形成装置。

【請求項9】

原稿を読み取って前記画像データを生成する原稿読取部を備え、

前記第1及び第2の追越制御部は、前記原稿読取部による原稿読取時に、前記(1)〜(4)の制御を実行する請求項7又は8に記載の画像形成装置。

【請求項10】

前記予め定められた第2の機能ブロックは、前記複数の第1の機能ブロックのいずれかに、前記画像データの書き込みを要求する第2の機能ブロックである請求項7〜9のいずれか一項に記載の画像形成装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−25674(P2013−25674A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2011−161893(P2011−161893)

【出願日】平成23年7月25日(2011.7.25)

【出願人】(000006150)京セラドキュメントソリューションズ株式会社 (13,173)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願日】平成23年7月25日(2011.7.25)

【出願人】(000006150)京セラドキュメントソリューションズ株式会社 (13,173)

【Fターム(参考)】

[ Back to top ]