成膜方法および半導体装置

【課題】スパッタ法により、酸化物半導体膜上に薄膜を成膜する際に、酸化物半導体膜のプラズマダメージを膜面内均一性良く抑制して成膜する。

【解決手段】基板B上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜1上に、基板BとターゲットTとを対向させて、プラズマを用いるスパッタ法によりターゲットTの構成元素を含む薄膜2を形成する成膜方法において、薄膜2の成膜時のプラズマ中のプラズマ電位Vs(V)と、基板Bの基板電位Vsub(V)との電位差を0V超20V以下とする。

【解決手段】基板B上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜1上に、基板BとターゲットTとを対向させて、プラズマを用いるスパッタ法によりターゲットTの構成元素を含む薄膜2を形成する成膜方法において、薄膜2の成膜時のプラズマ中のプラズマ電位Vs(V)と、基板Bの基板電位Vsub(V)との電位差を0V超20V以下とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スパッタ法により、IGZO等の酸化物半導体膜下地上に薄膜を成膜する成膜方法および該方法を用いて得られた半導体装置に関するものである。

【背景技術】

【0002】

近年、液晶ディスプレイや有機エレクトロルミネッセンス(有機EL)ディスプレイ等の駆動素子として、薄膜トランジスタ(TFT)等の半導体装置が広く使用されている。薄膜トランジスタにおける半導体膜としては、アモルファスシリコンや低温ポリシリコン等が一般的に用いられているが、これらの半導体膜の成膜には高温プロセスが不可欠であり、樹脂基板等耐熱性の低いフレキシブル基板上への成膜は困難である。

【0003】

そこで、低温成膜が可能な半導体膜としてIGZO等の酸化物半導体膜が注目されている。酸化物半導体膜は、樹脂基板の耐熱温度以下の温度でも成膜できるため、フレキシブルELディスプレイ等に用いる薄膜トランジスタや薄膜センサ等の半導体膜として期待されている。

【0004】

この酸化物半導体膜上に絶縁膜等の薄膜を成形する際に、高温処理を用いずに薄膜形成可能なスパッタ法(スパッタリング法)が主に用いられる。スパッタ法は、高真空中でプラズマ放電により生成されるArイオン等のプラズマイオンをターゲットに衝突させて、これによりたたき出されたターゲットの構成原子或いは粒子(以下、スパッタ粒子という。)を成膜基板の表面に堆積させることにより成膜する方法である。

【0005】

スパッタ法により酸化物半導体膜上に薄膜を形成する際に、プラズマイオンは、ターゲットだけではなく、基板上に成膜された酸化物半導体膜にも衝突し、酸化物半導体膜にプラズマダメージを与えることが問題となっている。非特許文献1のFig.2には(図8)、IGZO膜へのArプラズマ照射時間に対する、IGZO膜の電気抵抗への影響が示されている。非特許文献1のFig.2には、Arイオンを照射する時間が長い程、IGZO膜の電気抵抗率が減少し、キャリア密度が高くなることが示されている。

【0006】

特許文献1の段落[0022]には、通常、酸化物半導体の電気伝導度や電子キャリア密度は成膜時の酸素分圧により制御され、主として薄膜中の酸素欠損量を制御することにより電子キャリア密度を制御することが記載されている。特許文献1には、上記酸素欠損を抑制するために、スパッタ法による薄膜成膜時に酸素を流入する方法が開示されている。

【0007】

また、非特許文献1には、IGZO膜上にSiO2保護膜を成膜する際の酸素条件によって、得られる薄膜トランジスタの閾値電圧をシフトさせ、電気特性に影響を及ぼすことが記載されている(非特許文献1、Fig.5)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2008−218495号公報

【非特許文献】

【0009】

【非特許文献1】“Improvements in the device characteristics of amorphous indium gallium zinc oxide thin-film transistors by Ar plasma treatment”, Sumsung SDI Co. Ltd., Applied Physics Letters 90, 262106 2007.

【非特許文献2】“World’s Largest(15-inch) XGA AMLCD Panel Using IGZO Oxide TFT”, Sumsung Electronics Co. Ltd., SID08 DIGEST, p.625-628

【発明の開示】

【発明が解決しようとする課題】

【0010】

しかしながら、特許文献1の、成膜ガス中の酸素流量により調整する方法では、酸素のフローむらより、酸化物半導体膜表面の位置によって成膜ガス中の酸素量が異なり、酸素導入による効果を均一に得ることが難しく、このため、膜面内において均一なキャリア密度を有する信頼性の高い膜を得ることが難しい。半導体膜の信頼性は、それを用いた薄膜素子の素子特性に大きく影響を与え、例えば、薄膜トランジスタでは、キャリア密度の信頼性の低い半導体膜を用いると、Vg−Id特性において、ドレイン電流が立ち上がるゲート印加電圧および閾値電圧が負側にシフトし、薄膜トランジスタ特性上好ましくない性質を示すことが、特許文献1にも記載されている。

【0011】

非特許文献1には、酸素条件の制御方法については一切記載されていないため、具体的な成膜条件が不明である。

【0012】

本発明は上記問題に鑑みてなされたものであり、スパッタ法により酸化物半導体膜上へ薄膜を成膜する際に、下地となるIGZO等の酸化物半導体膜のキャリア密度を膜面内において均一性高く維持することが可能な成膜方法を提供することを目的とするものである。

【0013】

また、本発明は、上記成膜方法を用いて得られた、素子特性及び信頼性の良好な半導体装置を提供することを目的とするものである。

【課題を解決するための手段】

【0014】

本発明の成膜方法は、基板上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜上に、前記基板とターゲットとを対向させて、プラズマを用いるスパッタ法により前記ターゲットの構成元素を含む薄膜を形成する成膜方法において、

該薄膜の成膜時のプラズマ中のプラズマ電位Vs(V)と、前記基板の基板電位Vsub(V)との電位差|Vs−Vsub|が下記式(1)を満足するように前記電位差を制御して前記薄膜を成膜することを特徴とするものである。本発明の成膜方法において、下記式(2)を満足するように前記電位差を制御して前記薄膜を成膜することが好ましい。

0<|Vs−Vsub|(V)≦20 ・・・(1)、

0<|Vs−Vsub|(V)≦16 ・・・(2)

【0015】

ここで、プラズマ電位とは、成膜ガスがスパッタ装置内において電離したプラズマイオンの電位の絶対値の最大値を意味する。例えば、成膜ガスとしてArガスを用いる場合は、Ar+イオン電位の最大値を意味するものとする。

【0016】

本明細書において、「電位」は、ラングミュアプローブを用いてシングルプローブ法あるいはトリプルプローブ法により測定するものとする。原理的に測定可能であれば他の手法でも構わない。

【0017】

また、成膜時の電位差|Vs−Vsub|を20(V)以下となるように制御する期間は、酸化物半導体膜上に薄膜を形成する工程の中の全期間である必要はなく、薄膜の膜厚が下地の酸化物半導体膜表面へのスパッタによる影響が無視できる範囲となるまで制御すればよい。

【0018】

また、電位差|Vs−Vsub|は、プラズマ電位Vsと基板電位Vsubの差を相対的に変化させればよいが、成膜速度に大きく影響を与えずに変化させることができることから、基板電位Vsubにバイアス印加して変化させることが好ましい。成膜速度に大きく影響を与えない範囲内であれば、プラズマ電位Vsと基板電位Vsubのどちらか、又は両方を変化させてもよい。プラズマイオンが正イオンでありプラズマ電位Vsが0Vより大きく50V以下である場合は、前記基板に正電圧をバイアス印加して電位差|Vs−Vsub|を制御することが好ましい。また、本発明の成膜方法は、前記酸化物半導体膜が、下記一般式(P1)で表される1種または複数種の酸化物からなる(不可避不純物を含んでもよい)場合に好適に適用することができる。

(In2−xGax)O3・(ZnO)m・・・(P1)

(式中0<x<2かつmは自然数)

【0019】

本発明の成膜方法において、前記成膜時の基板温度Tsが300℃以下であり、前記基板と前記ターゲットとの距離Dが40mm以上150mm以下であり、成膜圧力Pが0.1Pa以上5Pa以下であることが好ましく、成膜圧力Pは0.1Pa以上1.0Pa以下であることがより好ましい。

【0020】

また、本発明の成膜方法において、前記薄膜が絶縁体膜である場合に好適に適用することができる。

【0021】

本発明の薄膜素子は、基板上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜と、上記本発明の成膜方法により成膜された薄膜とを備えたことを特徴とするものである。かかる薄膜素子としては、前記酸化物半導体膜からなる活性層と、前記薄膜からなるゲート絶縁膜とを備えた薄膜トランジスタ等の半導体装置が挙げられる。

【0022】

上記本発明の薄膜素子は、基板を用意し、該基板上にInと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜を成膜する工程と、

該酸化物半導体膜上に、上記本発明の成膜方法により絶縁膜を形成する工程と、

前記酸化物半導体膜に電圧を印加する、又は、該酸化物半導体膜から電流を取り出す電極を形成する工程とを有する薄膜素子の製造方法により製造することができる。

【0023】

また、本発明の薄膜素子の製造方法において、前記電極を、上記本発明の成膜方法を用いて形成することが好ましい。

【発明の効果】

【0024】

本発明の成膜方法は、基板上に成膜されたIGZO等の酸化物半導体膜上に、プラズマを用いるスパッタ法により、薄膜を形成する際に、成膜時のプラズマ中のプラズマ電位Vs(V)と基板電位Vsub(V)との電位差|Vs−Vsub|を20(V)以下となるように制御して成膜している。かかる構成によれば、酸化物半導体膜のプラズマダメージによる酸素欠損を、膜面内において均一性高く抑制することができる。従って、本発明によれば、下地となるIGZO等の酸化物半導体膜のキャリア密度を膜面内において均一性高く維持することができる。

【0025】

また、プラズマ電位Vsが正であり、基板に正電圧をバイアス印加して電位差を制御する構成では、成膜レートを大きく低下させることなく電位差|Vs−Vsub|を制御することができる。

【図面の簡単な説明】

【0026】

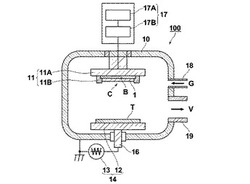

【図1A】本発明の成膜方法好適なRFスパッタ成膜装置の概略断面図

【図1B】スパッタ成膜中の様子を模式的に示す図

【図2】RFスパッタ装置内のAr+プラズマ空間中における基板―ターゲット間の電位の分布の様子を示す模式図

【図3A】本発明に係る一実施形態の半導体装置(薄膜素子)の製造工程を示す断面図(その1)

【図3B】本発明に係る一実施形態の半導体装置の製造工程を示す断面図(その2)

【図3C】本発明に係る一実施形態の半導体装置の製造工程を示す断面図(その3)

【図3D】本発明に係る一実施形態の半導体装置の製造工程を示す断面図(その4)

【図4A】実施例1の薄膜素子サンプルの上面図

【図4B】図4AのA−A’断面図

【図5】電位差|Vs−Vsub|と酸化物半導体膜のキャリア密度の関係を示す図

【図6】ターゲット投入電力と基板電位の関係を示す図

【図7】圧力と基板電位の関係を示す図

【図8】非特許文献1のFig.2

【発明を実施するための形態】

【0027】

「薄膜の成膜方法」

図面を参照して、本発明に係る一実施形態の成膜方法について説明する。本発明の成膜方法は、基板上に成膜された、InGaZnO4(IGZO)等の酸化物半導体膜上に、プラズマを用いるスパッタ法により薄膜を成膜するものである。

【0028】

プラズマを用いるスパッタ法としては、特に制限されないが、2極スパッタリング法、3極スパッタリング法、直流スパッタリング法、高周波スパッタリング法(RFスパッタ法)、ECRスパッタリング法、マグネトロンスパッタリング法、対向ターゲットスパッタリング法、及びパルススパッタ法等が挙げられる。

【0029】

本実施形態では、RFスパッタ法を例に説明をする。図1Aは装置の全体構成を示す断面図であり、図1Bは成膜中の様子を模式的に示す図である。視認しやすくするために各部の縮尺は適宜変更してある。本実施形態では高周波スパッタリング装置(RFスパッタリング装置)を例として説明する。

【0030】

図1Aに示す成膜装置100は、内部に、基板Bが装着可能であり、装着された基板Bを所定温度に加熱することが可能な基板ホルダ11と、ターゲットTが装着可能なターゲットホルダ12とが備えられた真空容器10から概略構成されている。本実施形態の装置では、真空容器10内が成膜室となっている。真空容器10内において、基板ホルダ11とターゲットホルダ12とは互いに対向するように離間配置されている。真空容器10はステンレス等の導電体からなり、接地されている。

【0031】

基板Bは特に制限されず、Si基板、酸化物基板、ガラス基板、及び各種フレキシブル基板など、用途に応じて適宜選択することができる。基板Bはかかる基板に電極等の膜が形成されたものでもよい。ターゲットTの組成は、成膜する膜の組成に応じて選定される。

【0032】

成膜装置100においては、プラズマ電極(本実施形態ではターゲットホルダ12がプラズマ電極として機能する。)の放電により真空容器10内に導入されたガスGがプラズマ化され、Arイオン等のプラスイオンが生成する。生成したプラスイオンはターゲットTをスパッタする。プラスイオンにスパッタされたターゲットTの構成元素は、ターゲットから放出され中性あるいはイオン化された状態で基板Bに成膜される。図中、符号Pがプラズマ空間を模式的に示している。

【0033】

成膜装置100には、真空容器10内にプラズマ化させるガスGを導入するガス導入手段が設けられている。ガス導入手段は、プラズマ化させるガスGの供給源(図示略)と、供給源から供給されたガスGを真空容器10内に導入するガス導入管18とから構成されている。

【0034】

成膜装置100には、真空ポンプ等の排気手段(図示略)に接続され、真空容器10内のガスの排気Vを行うガス排出管19が備えられている。真空容器10に対するこれらガス導入管18とガス排出管19との接続箇所は適宜設計でき、これらガス導入管18とガス排出管19は真空容器10内のガス濃度がなるべく均一になるように設けられることが好ましい。ガスGとしては特に制限なく、Ar、又はAr/O2混合ガス等が使用される。

【0035】

図1Bに模式的に示すように、プラズマ電極12の放電により真空容器10内に導入された成膜ガスGがプラズマ化され、Arイオン等のプラスイオンIpが生成する。生成したプラスイオンIpはターゲットTをスパッタする。プラスイオンIpにスパッタされたターゲットTの構成原子或いは粒子(スパッタ粒子)Tpは、ターゲットから放出され中性あるいはイオン化された状態で成膜基板B(あるいは成膜基板B上に既に成膜されている薄膜表面)に蒸着される。図中、符号Pがプラズマ空間を示している。

【0036】

プラズマ空間Pの電位は、成膜時のプラズマ中のプラズマ電位Vs(V)となる。成膜基板Bの電位は基板電位Vsub(V)となる。このプラズマ空間Pの電位と成膜基板Bの電位との電位差|Vs−Vsub|の加速電圧により、ターゲットTと成膜基板Bとの間にあるスパッタ粒子Tpは、運動エネルギーを得て成膜基板B上に成膜された酸化物半導体膜1上に薄膜として堆積する。なお、酸化物半導体膜1と成膜基板Bはほぼ同じ電位と考えられる。

【0037】

基板ホルダ11は、基板Bが載置される板状のホルダ本体11Aと、ホルダ本体11Aに取り付けられ、基板Bの端部を固定する固定部材11Bとから概略構成されている。基板ホルダ11は、真空容器10の内底面に取り付けられた保持部材15により保持されている。

【0038】

ホルダ本体11A、固定部材11B、及び保持部材15はいずれもステンレス等の導電体からなり、保持部材15と真空容器10とは絶縁材を介して互いに絶縁されている(絶縁材については図示略)。基板ホルダ11は真空容器10の外部に配置された直流電流印加ユニット(電位調整手段)17に電気的に接続されており、基板ホルダ11に電位が印加可能であると共に、その電位が調整可能に構成されている。直流電流印加ユニット17は、直流電源17Aと整合回路17Bとから概略構成されている。整合回路17Bは必要に応じて設けられるものであり、直流電源17Aと基板ホルダ11との間に整合回路17Bを介在させることで、基板ホルダ11の電位調整が容易となり、好ましい。

【0039】

本実施形態では、ホルダ本体11A、固定部材11B、及び保持部材15が同電位となっている。基板ホルダ11に直流バイアス電流を印加する本実施形態では、基板自体が導電体である、あるいは基板は絶縁体であっても基板表面に電極等の導電体膜が形成されていることが好ましい。かかる構成では、基板Bと基板ホルダ11とを効果的に同電位にすることができ、好ましい。圧電体膜等の成膜では、通常下地に下部電極が形成されているので、基板電位と基板ホルダ11とを同電位にすることができる。

【0040】

本実施形態では、基板ホルダ11のホルダ本体11Aのサイズが、基板Bの外周から基板Bの側方に10mm以上大きく設計されていることが好ましい。

【0041】

ターゲットホルダ12はターゲットTが載置される板状のホルダ本体からなり、真空容器10に取り付けられた保持部材16により保持されている。保持部材16と真空容器10とは絶縁材を介して互いに絶縁されている。保持部材16は真空容器10の外部に配置された高周波電源(RF電源)13に接続されており、ターゲットホルダ12がプラズマを発生させるためのプラズマ電極(カソード電極)となっている。高周波電源13のターゲットホルダ接続側と反対側は接地されている。

【0042】

本実施形態では、真空容器10内にプラズマを発生させるプラズマ発生手段14として、高周波電源13及びプラズマ電極(カソード電極)として機能するターゲットホルダ12が備えられている。

【0043】

背景技術において述べたように、プラズマを用いるスパッタ法により、IGZO等の酸化物半導体膜1上に薄膜2を成膜する際に、プラズマダメージにより酸化物半導体膜1のキャリア密度が高くなり、電気特性を低下させること、そして、通常、キャリア密度は、膜中の酸素欠損量により制御されることを述べた。

【0044】

特許文献1及び非特許文献1、2より、スパッタ法におけるプラズマダメージによるキャリア密度の増大は、酸化物半導体膜1へのプラズマイオンの衝突により酸化物半導体膜中1の酸素がスパッタされて膜中から抜ける、酸素欠損によるものと考えられる。

【0045】

膜中の酸素量によりキャリア密度が変化することは本発明者も確認している。本発明者は、IGZO膜のスパッタ成膜時の成膜ガス中の酸素量を変化させて、膜中の酸素量とキャリア密度との関係を調べた。その結果、酸素量が多くなるほどキャリア密度が低くなること、そして、成膜ガス中の酸素の体積分率を約0.8%とすることにより、薄膜トランジスタの半導体膜として用いる場合に、0V近辺で立ち上がる良好な特性を有するキャリア密度(1×1014〜1×1015(個/cm3))が得られることを確認している。

【0046】

酸素欠損を補う方法としては、特許文献1では酸素を真空容器中に流入させて積極的に酸素元素を膜中に注入する方法が開示されているが、既に述べたようにフローむらにより、酸素欠損抑制効果が膜面内にて均一に得られないことから、膜質が不均一となり、酸化物半導体膜としての信頼性が低いものとなってしまう。更に、酸素を真空容器中に流入させると成膜速度に大きく影響を及ぼし良好な生産性を維持することが難しい。

【0047】

本発明者は、下地となる酸化物半導体膜のキャリア密度の面内均一性を保って酸素欠損を補う方法について鋭意検討を行った。

【0048】

上記のように、酸化物半導体膜1への酸素欠損(プラズマダメージ)は、酸化物半導体膜1がスパッタされることにより生じる現象である。プラズマイオンは、自分自身の電位と、スパッタするターゲットあるいは基板との電位差によりエネルギーを得てターゲットあるいは基板をスパッタする。

【0049】

図2は、RFスパッタ装置内のAr+プラズマ空間中において基板を接地した場合の、基板―ターゲット間の電位の分布の様子を示す模式図である。図2に示されるように、ArガスはプラズマによりAr+と電子に電離しており、ターゲット側はAr+と電子のRFの反応速度の違いによる自己バイアスにより負電位(−100〜−150V程度)となっている。プラズマ電位は、基板―ターゲット間のプラズマ空間においてAr+の電位(最大電位)となり、接地されている基板では0Vとなっている。

【0050】

Ar+プラズマイオンは陽イオンであるため、負電位のターゲット側に加速してターゲットに衝突するが、ターゲットの構成元素のスパッタ閾値以上のエネルギーを有している場合にその元素は叩き出され(スパッタされ)、対向配置されている基板側に成膜される。プラズマのエネルギーは、プラズマイオンとスパッタされる側の電位差が大きいほど大きくなる。

【0051】

一方、図示されるように、基板電位Vsubとプラズマ電位Vsとにも電位差があるため、その電位差に応じたエネルギーで基板側の表面はスパッタされ、これがプラズマダメージの要因となると考えられる。従って、酸化物半導体膜のプラズマダメージを抑制するためには、酸化物半導体膜の電位、つまり、基板電位Vsubと、プラズマ電位Vsとの電位差|Vs―Vsub|(V)を小さくすることにより、酸化物半導体膜表面に衝突するプラズマエネルギーが小さくなり、酸素のスパッタを抑制することができると考えられる。かかる方法では、膜面内において均一性高く、酸化物半導体膜のプラズマダメージによる酸素欠損を抑制することができる。なお、|Vs―Vsub|(V)はそのまま電子温度(eV)に変換することができる。電子温度1eV=11600K(Kは絶対温度)に相当する。

【0052】

本発明者は、酸化物半導体膜のプラズマダメージによる酸素欠損を、膜面において均一性高く抑制することができる電位差|Vs−Vsub|について好適な範囲を見出した。

【0053】

すなわち、本発明の成膜方法は、基板B上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜1上に、基板BとターゲットTとを対向させて、プラズマを用いるスパッタ法によりターゲットTの構成元素を含む薄膜2を形成する成膜方法であって、成膜時のプラズマ中のプラズマ電位Vs(V)と、基板Bの基板電位Vsub(V)との電位差|Vs−Vsub|が下記式(1)を満足するようにこの電位差を制御して薄膜2を成膜することを特徴とするものである。

0<|Vs−Vsub|(V)≦20 ・・・(1)

【0054】

後記実施例の図5に、本発明者が見いだした|Vs−Vsub|と、酸化物半導体膜のキャリア密度との関係を示してある。一般に、半導体膜のキャリア密度は、キャリア密度が約1X1014〜1X1015(個/cm3)が好適であるとされている。図5には、スパッタ法によって酸化物半導体膜1上に成膜する際、電位差|Vs−Vsub|が上記式(1)を満足する範囲内であれば、酸化物半導体膜1のキャリア密度を半導体装置等に用いる半導体膜として好適な範囲に維持し、酸化膜半導体膜上に薄膜2を成膜することができることが示されている。

【0055】

さらに、下記式(2)を満足する場合には、薄膜2形成後の酸化物半導体膜1のキャリア密度は、薄膜2形成前の10倍以内に抑えられており、酸化物半導体膜1のキャリア密度の変化をさらに良好に抑制でき、好ましい。|Vs−Vsub|の値は、求められる半導体膜のキャリア密度により設定すればよい。すなわち、|Vs−Vsub|は、求められる半導体膜のキャリア密度が得られる閾値以下に設定すればよい。

【0056】

0<|Vs−Vsub|(V)≦16 ・・・(2)

本実施形態の酸化物半導体膜1上に薄膜2を成膜する方法によれば、酸化物半導体膜1上に薄膜2を成膜する際に電位差|Vs−Vsub|を好適化することによりプラズマダメージを抑制するため、特許文献1に示される成膜ガス中に酸素を混合する方法に比して、酸化物半導体膜1で得られる酸素欠乏抑制効果の膜面内均一性が高く、その結果、酸化物半導体のキャリア密度を均一且つ良好に維持して、薄膜2を成膜することができる。

【0057】

電位差|Vs−Vsub|は、プラズマ電位Vsと基板電位Vsubの差を相対的に変化させればよく、例えば、プラズマ電位Vsと基板電位Vsubのどちらかを変化させてもよく、両方を変化させてもよい。

【0058】

本実施形態の成膜装置100では、基板ホルダ11に直流電流印加ユニット(電位調整手段)17が電気的に接続されており、基板ホルダ11に電位が印加可能であると共に、その電位が調整可能に構成されている。かかる構成では、基板Bに電圧を印加して基板電位Vsubを制御することにより、電位差|Vs−Vsub|を制御することが好ましい。プラズマ電位Vsが正電位である場合は、Vsubとして基板Bに正電圧をバイアス印加して電位差|Vs−Vsub|を制御する。

【0059】

基板Bにバイアス印加することにより、電位差|Vs−Vsub|を制御する構成では、成膜速度や、膜質等に影響を及ぼすプラズマ電位を変化させない上、成膜ガスに酸素を等の反応速度を低下させるガスを混合しないため成膜速度の低下を抑制し、生産効率よく成膜を実施することができる。

【0060】

また、既に述べたように、上記式(1)を満足するように|Vs−Vsub|の制御する期間は、酸化物半導体膜上に薄膜を形成する工程の中の全期間であってもよいし、薄膜の膜厚が下地の酸化物半導体膜表面へのスパッタによる影響が無視できる範囲となるまでの一部の期間としてもよい。例えば、酸化物半導体膜1上に薄膜2を成膜する期間のうち、膜2が所定の厚み、例えば数nm程度になるまで、電位差|Vs−Vsub|を20(V)以下に制御し、その後電位差|Vs−Vsub|を20(V)以上の値(従来の成膜条件による電位差)に戻して薄膜2の成膜を行ってもよい。

【0061】

また、式(1)を満足する範囲内に制御する期間中において、電位差|Vs−Vsub|は一定値に維持してもよく、電位差|Vs−Vsub|を複数の値に連続的に、あるいは断続的に変化させてもよい。なお、電位差|Vs−Vsub|を成膜途中に変更することにより、薄膜2の種類によっては、膜特性に影響を及ぼす可能性がある。従って、電位差|Vs−Vsub|を途中変更する構成は、膜特性への影響を無視できる範囲で行うことが好ましい。

【0062】

電位差|Vs−Vsub|の制御は、上記基板電位をバイアス印加により変化させる方法に限らず、電位差|Vs−Vsub|の制御が行える方法であれば種々の方法を適用できる。

【0063】

例えば、後記実施例2に示されるように、ターゲット投入電力、成膜圧力により制御することも可能である。しかしながら、後記実施例2の図6、図7に示されるように、成膜圧力及びターゲット投入電力を変化させることにより、プラズマ電位Vsを変化させることは可能であるが、図示されるように変化率が小さく、例えば、Arイオンを用いる場合には、ターゲット投入電力により|Vs−Vsub|を20V以下とするのは難しく、また、成膜圧力により|Vs−Vsub|を20V以下とするには、10Pa以上の圧力が必要となり、成膜速度が非常に遅くなるため生産性の点で好ましくない。

【0064】

一般に、スパッタ法においては、ターゲット投入電力は4W以上、成膜圧力は0.1Pa以上5Pa以下、より好ましくは1Pa以下で成膜を実施しなければ生産性上現実的ではない。成膜圧力は、元素の種類によってその値は異なるが、大きすぎるとターゲットTからたたき出された粒子が散乱等の影響により基板Bに到達する割合が少なくなり成膜が難しくなる。また、小さすぎても安定したプラズマ空間を得ることができない。

【0065】

従って、成膜圧力及びターゲット投入電力による制御は、生産性を良好に保つことができるプラズマイオン種を用いている構成、基板のバイアス印加と組み合わせる構成、あるいは、薄膜の膜厚が下地の酸化物半導体膜1表面へのスパッタによる影響が無視できる範囲となるまでの最短期間の制御とする構成が好適であると考えられる)。

薄膜2の|Vs−Vsub|以外の成膜条件としては、成膜装置内のプラズマが安定して発生可能であれば特に制限されないが、良好な生産性で成膜が実施できる条件であることが好ましい。上記酸化物半導体膜1が、フレキシブルデバイスとして好適であることから、使用する基板の耐熱温度以下の温度にて、好適に成膜可能な条件とすることが好ましい。一般に、樹脂基板の耐熱温度は、ポリイミド等の耐熱性の高いもので300℃程度であることから、成膜温度Tsは300℃以下であることが好ましい。

【0066】

基板−ターゲット間距離Dは、長いほど成膜速度が遅くなるが、成膜される膜の均一性等は良好になる。また、短すぎるとプラズマの安定性を損なうことから、基板−ターゲット間距離Dは40mm以上150mm以下であることが好ましい。

以下に、上記本発明の成膜方法を適用するに好適な材料構成について説明する。

【0067】

本実施形態において、基板Bは特に制限されず、Si基板、ガラス基板、各種フレキシブル基板等、用途に応じて選択すればよい。本発明では、樹脂基板の耐熱温度以下の温度で成膜が可能な酸化物半導体膜を備えた構成としている。従って、成膜基板Bは、樹脂基板等のフレキシブル基板を使用することができる。

【0068】

フレキシブル基板としては、ポリビニルアルコール系樹脂,ポリカーボネート誘導体(帝人(株):WRF),セルロース誘導体(セルローストリアセテート,セルロースジアセテート),ポリオレフィン系樹脂(日本ゼオン(株):ゼオノア、ゼオネックス),ポリサルホン系樹脂(ポリエーテルサルホン,ポリサルホン),ノルボルネン系樹脂(JSR(株): アートン),ポリエステル系樹脂(PET,PEN,架橋フマル酸ジエステル)ポリイミド系樹脂,ポリアミド系樹脂,ポリアミドイミド系樹脂,ポリアリレート系樹脂,アクリル系樹脂,エポキシ系樹脂,エピスルフィド系樹脂,フッ素系樹脂,シリコーン系樹脂フィルム,ポリベンズアゾ-ル系樹脂,シアネート系樹脂,芳香族エーテル系樹脂(ポリエーテルケトン),マレイミド−オレフィン系樹脂等の樹脂基板、液晶ポリマー基板、

また、これら樹脂基板中に酸化ケイ素粒子,金属ナノ粒子,無機酸化物ナノ粒子,無機窒化物ナノ粒子, 金属系・無機系のナノファイバー又はマイクロファイバー,カーボン繊維,カーボンナノチューブ,ガラスフェレーク,ガラスファイバー,ガラスビーズ,粘土鉱物、雲母派生結晶構造を含んだ複合樹脂基板、

薄いガラスと上記単独有機材料との間に少なくとも1回の接合界面を有する積層プラスチック材料、無機層(ex.SiO2, Al2O3, SiOxNy)と有機層(上記)を交互に積層することで少なくとも1回以上の接合界面を有するバリア性能を有する複合材料、

ステンレス基板、あるいはステンレスと異種金属を積層した金属多層基板、アルミニウム基板、あるいは、表面に酸化処理(例えば、陽極酸化処理)を施すことで、表面の絶縁性を向上してある酸化被膜付きのアルミニウム基板等を挙げることができる。

【0069】

酸化物半導体膜1としては、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体からなる(不可避不純物を含んでもよい)ものであれば特に制限されないが、下記一般式(P1)で表されるInGaZnO4(IGZO)等のホモロガス化合物が一例として挙げられる。

(In2−xGax)O3・(ZnO)m・・・(P1)

(式中0<x<2かつm>0)

【0070】

酸化物半導体膜1の成膜方法は特に制限されず、気相法、液相法など、用いる基板や酸化物半導体の種類に応じて好適な成膜方法を用いてよい。

【0071】

酸化物半導体膜1上に成膜する薄膜2としては特に制限されず、導電体膜、半導体膜、絶縁体膜、及び誘電体膜等の任意の組成の膜の成膜に適用することができる。薄膜トランジスタの半導体層として酸化物半導体膜1を用いる場合には、保護膜やゲート絶縁膜、層間絶縁膜等の絶縁膜、及びソース/ドレイン電極等が挙げられる。

【0072】

薄膜トランジスタのこれらの絶縁膜としては、Ga2O3、SiO2、Al2O3、SiON、SiN、HfO2、Y2O3、Ta2O5、MgO等の酸化物からなる(不可避不純物を含んでもよい。)絶縁膜が挙げられる。

【0073】

また、ソース/ドレイン電極としては、Pt,Au,Pd,Cr,Ni,Mo,Ag,W,Cu,Ti,In,Sn等の金属又はこれらの合金、錫酸化物、酸化インジウム、インジウム錫酸化物(ITO)等が挙げられる。

【0074】

Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体においては、構成元素のスパッタされやすさ(スパッタ率)は酸素が格段に高い(スパッタ閾値が格段に低いことと同意)。従って、上記酸化物半導体膜においては、その上に成膜する膜のスパッタ成膜時に、膜表面から抜けて欠損を生じる元素は酸素の割合が格段に大きく、酸素欠損はキャリア密度へ大きく影響を及ぼす要因となる。上記Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeのスパッタ率は、Znが大きいが、今回、酸化物半導体膜上に成膜する各種膜(保護膜、絶縁膜、電極等)の成膜条件下においては、これらの元素についてはほぼ同様と考えてよく、酸素欠損による影響を考慮すればよい。ここで、「スパッタ率」とは、入射イオンの数とそれによってスパッタされた原子数との比で定義されるものであり、その単位は(atoms/ion)である。例えば、「真空ハンドブック」((株)アルバック編、オーム社発行)の表8.1.7には、Arイオン300eVの条件におけるスパッタ率が記載されている。

【0075】

本発明の成膜方法は、基板B上に成膜されたIGZO等の酸化物半導体膜1上に、プラズマを用いるスパッタ法により、薄膜2を形成する際に、成膜時のプラズマ中のプラズマ電位Vs(V)と基板電位Vsub(V)との電位差|Vs−Vsub|を、20(V)以下となるように制御して成膜している。かかる構成によれば、酸化物半導体膜1のプラズマダメージによる酸素欠損を、膜面内において均一性高く抑制することができる。従って、本発明によれば、下地となるIGZO等の酸化物半導体膜1のキャリア密度を膜面内において均一性高く維持して薄膜2を成膜することができる。

【0076】

また、プラズマ電位Vsが正であり、基板Bに正電圧をバイアス印加して電位差|Vs−Vsub|を制御する構成では、成膜速度を大きく低下させることなく電位差を制御することができ、好ましい。

【0077】

「半導体装置(薄膜素子)」

図3Aから図3Dを参照して、上記実施形態の酸化物半導体膜1及び薄膜2を用いた半導体装置(薄膜素子)3及びその製造方法について説明する。本実施形態では、ボトムゲート型を例として説明する。図3Aから図3Dは、薄膜トランジスタ(TFT)の製造工程図(基板の厚み方向の断面図)である。視認しやすくするため、構成要素の縮尺は実際のものとは適宜異ならせてある。

【0078】

本実施形態の半導体装置(薄膜トランジスタ:TFT)3は、基板B上に、上記実施形態の酸化物半導体膜1を用いて得られた活性層32と、上記実施形態の成膜方法により成膜された保護膜(絶縁膜)2と、電極とを備えたものである。

【0079】

まず、図3Aに示すように、基板Bを用意し、n+Si等からなるゲート電極30及びゲート絶縁膜31を形成する。ゲート絶縁膜31としては、先述の絶縁体材料等があげられる。基板Bは、上記実施形態で説明したのと同様の基板が使用できる。

【0080】

次いで、図3Bに示すように、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜1(活性層32)を形成する。成膜方法については、上記成膜方法の実施形態において記載したとおりである。

【0081】

さらに、図3Cに示すように、活性層32上にソース電極33及びドレイン電極34を形成する。ソース電極33及びドレイン電極34は、スパッタ法、蒸着法等の気相成膜とフォトリソグラフィ法によるパターニングを組み合わせた製造方法やインクジェット法等により形成することができる。

【0082】

最後に、図3Dに示すように、活性層32、ソース電極33及びドレイン電極34上に上記実施形態の成膜方法により、保護膜(絶縁膜)2を形成する。

以上の工程により、本実施形態の半導体装置(TFT)3が製造される。

【0083】

本実施形態の半導体装置(TFT)3は、酸化物半導体膜1を用いて得られた活性層32上に、上記本発明の成膜方法により成膜された保護膜2を備えたものであるので、上記本発明の成膜方法と同様の効果を奏する。本実施形態の半導体装置3は、信頼性の高いキャリア密度の安定した酸化物半導体膜1を備えているので、ON−OFF特性が良好かつ安定性の高いものとなる。

【0084】

また、本実施形態において半導体装置の製造方法では、全工程の成膜を300℃以下の成膜温度にて実施することができるため、耐熱性の低いフレキシブル基板等上にも良好な半導体特性を示す半導体装置3を得ることができる。従って、本発明の半導体装置の製造方法によれば、フレキシブルな大画面有機ELディスプレイ等の様々な電気製品に好適に用いることができる、高品質な半導体装置を提供可能である。

【0085】

本実施形態のようなボトムゲート型の場合、ソース電極33及びドレイン電極34を生産性の高いスパッタ法により成膜する場合は、上記本発明のスパッタ法による成膜方法により成膜する構成とすることが好ましい。ソース電極33及びドレイン電極34をスパッタ法により成膜する際に受けるプラズマダメージは、オーミックコンタクトの観点からは良い方向に働くが、酸化物半導体膜のキャリア密度が高くなると、ソースードレイン間の抵抗が下がり、半導体装置のON−OFF特性が低下してしまう。従って、ソース電極33及びドレイン電極34を上記本発明の成膜方法により成膜することにより、ON−OFF特性のより良好な半導体装置を製造することができる。

【0086】

「設計変更」

上記実施形態において、スパッタ成膜装置としてRFスパッタ成膜装置を用いたが、上記の成膜条件となるようにプラズマ空間電位を調整できればスパッタリング装置は特に制限されない。

【0087】

なお、本実施例は、プラズマ電位Vsが基板電位Vsubより高い場合の例であるが、基板電位Vsubがプラズマ電位Vsより高い場合も、電位差|Vs−Vsub|が上述の値以下になるよう制御すれば、同様の効果を得ることができる。

【0088】

また、酸化物半導体膜1を備えた半導体装置について説明したが、半導体装置以外の、センサやアクチュエータなどの半導体デバイスにも適用可能である。

【実施例】

【0089】

本発明に係る実施例及び比較例について説明する。

(実施例1)

約1cm2の正方形の市販の合成石英基板(1mm厚,入江株式会社製T−4040合成石英基板)上に、IGZO半導体膜、電極、及び、上記本発明の成膜方法により成膜された絶縁膜(保護膜)を備えた薄膜素子サンプルを下記のようにして複数用意した。図4Aは、薄膜素子サンプルの上面図、図4Bは図4AのA−A’断面図である。図4Aにおいて、基板の縦辺および横辺のサイズはW1=10(mm)、IGZO膜の縦辺および横辺のサイズはW2=8(mm)、電極間の距離はW3=6(mm)である。

【0090】

まず、パスカル社製マルチスパッタ装置を用いて、基板上に膜厚50nmのIGZO膜を成膜した。成膜条件は、基板温度Ts=常温、到達真空度6.0X10−6Pa、Ar/O2混合雰囲気(O2体積分率0.8%)、成膜圧力0.8Pa、ターゲットInGaZnO4及びZnO(共に、4Nターゲット)、基板―ターゲット間距離150mm、ターゲット投入電力DC50W(IGZO)、DC10W(ZnO)、成膜時間30分であった。

【0091】

次いで、上記IGZO膜上の4つの角領域に、Ti/Au電極(厚み50nm/200nm)を真空蒸着法により成膜した。

【0092】

成膜されたIGZO膜のキャリア密度を、東陽テクニカ製ACホール測定システム(RESITEST8300)を用いて測定したところ、キャリア密度は約2X1014(個/cm3)であった。

【0093】

複数の各薄膜素子サンプルに対し、IGZO成膜時と同じスパッタ装置を用いて、それぞれ異なる電位差|Vs―Vsub|となるように基板に接地電位(0V)〜26Vの範囲でバイアス印加して、絶縁膜であるGa2O3を、電極表面が一部露出するようにメタルマスクを使用して成膜した。なお、日本高周波製トリプルプローブモニタ(TPM−2000)を用いて、図1Aに示す基板位置近傍Cのプラズマ電位を測定したところ、プラズマ電位Vsは26(V)であった。

【0094】

成膜条件は、基板温度Ts=常温、到達真空度7.0X10−6Pa、Ar雰囲気、成膜圧力0.4Pa、ターゲットGa2O3(4Nターゲット)、基板―ターゲット間距離150mm、ターゲット投入電力RF50W、成膜時間30分であった。

【0095】

絶縁膜成膜後の薄膜素子のキャリア密度を、上記と同様にして測定した結果を表1及び図5に示す。表1及び図5には、基板電位を接地電位(0V)とした場合(|Vs―Vsub|≒26V)には、キャリア密度が約1X1017(個/cm3)に増大していること、そして、基板へのバイアス印加により、|Vs―Vsub|を20V以下とすれば、キャリア密度の増大を1桁以内に抑制できること、更に、16V以下とすることにより、良好な半導体特性を有する範囲内のキャリア密度(1×1014〜1×1015(個/cm3)に維持できることが示されている。

【0096】

以上により、成膜時のプラズマ中のプラズマ電位Vs(V)と基板電位Vsub(V)との電位差|Vs−Vsub|を20(V)以下、好ましくは16V以下に制御することで、プラズマイオンによる酸化物半導体膜への衝突による酸素欠損を抑え、酸化物半導体膜中のキャリア密度の増大を抑制して、酸化物半導体膜上に薄膜を成膜することが可能であることが実証された。

【表1】

【0097】

(実施例2)

基板へのバイアス印加以外の方法で|Vs―Vsub|を20V以下に制御可能な成膜条件について検討を行った。成膜条件として、成膜圧力(デポ圧)及びターゲット投入電力を選定し、基板電位を接地電位として、これらの成膜条件を変化させた時の図1Aに示す基板位置近傍Cのプラズマ電位の変化の様子を、実施例1と同様に日本高周波製トリプルプローブモニタ(TPM−2000)を用いて調べた。変化させた成膜条件以外の成膜条件は実施例1と同様とした。

【0098】

図6及び図7に得られた結果を示す。図6は、ターゲット投入電力と基板電位の関係を示した図であり、図7は、成膜圧力と基板電位の関係を示した図である。

【0099】

図6に示されるように、ターゲット投入電力を25W〜100Wの間で変化させると、プラズマ電位Vs22V〜30Vに、つまり、電位差|Vs−Vsub|を22V〜30Vに制御できることが確認された。

【0100】

また、図7に示されるように、成膜圧力を、0.4Pa〜20Paまで変化させると、プラズマ電位Vs18V〜26Vに、つまり、電位差|Vs−Vsub|を18V〜26Vに制御できることが確認された。

【産業上の利用可能性】

【0101】

本発明は、プラズマを用いるスパッタ法による任意の組成を有する成膜に適用することができる。本発明は、液晶ディスプレイや有機ELディスプレイに搭載される薄膜トランジスタや、X線センサ、アクチュエータの製造に好ましく適用することができる。

【符号の説明】

【0102】

1 酸化物半導体膜

2 薄膜(絶縁膜,保護膜)

3 半導体装置(薄膜素子,薄膜トランジスタ)

10 真空容器

11 基板ホルダ

12 プラズマ電極(ターゲットホルダ)

13 高周波電源

14 プラズマ発生手段

17 直流電流印加ユニット(電位調整手段)

18 ガス導入管

19 ガス排出管

21,22,30,33,34 電極

100 スパッタ成膜装置

B 成膜基板

G 成膜ガス

Ip プラスイオン

P プラズマ空間

T ターゲット

Tp スパッタ粒子

Vsub 基板電位

Vs プラズマ電位

【技術分野】

【0001】

本発明は、スパッタ法により、IGZO等の酸化物半導体膜下地上に薄膜を成膜する成膜方法および該方法を用いて得られた半導体装置に関するものである。

【背景技術】

【0002】

近年、液晶ディスプレイや有機エレクトロルミネッセンス(有機EL)ディスプレイ等の駆動素子として、薄膜トランジスタ(TFT)等の半導体装置が広く使用されている。薄膜トランジスタにおける半導体膜としては、アモルファスシリコンや低温ポリシリコン等が一般的に用いられているが、これらの半導体膜の成膜には高温プロセスが不可欠であり、樹脂基板等耐熱性の低いフレキシブル基板上への成膜は困難である。

【0003】

そこで、低温成膜が可能な半導体膜としてIGZO等の酸化物半導体膜が注目されている。酸化物半導体膜は、樹脂基板の耐熱温度以下の温度でも成膜できるため、フレキシブルELディスプレイ等に用いる薄膜トランジスタや薄膜センサ等の半導体膜として期待されている。

【0004】

この酸化物半導体膜上に絶縁膜等の薄膜を成形する際に、高温処理を用いずに薄膜形成可能なスパッタ法(スパッタリング法)が主に用いられる。スパッタ法は、高真空中でプラズマ放電により生成されるArイオン等のプラズマイオンをターゲットに衝突させて、これによりたたき出されたターゲットの構成原子或いは粒子(以下、スパッタ粒子という。)を成膜基板の表面に堆積させることにより成膜する方法である。

【0005】

スパッタ法により酸化物半導体膜上に薄膜を形成する際に、プラズマイオンは、ターゲットだけではなく、基板上に成膜された酸化物半導体膜にも衝突し、酸化物半導体膜にプラズマダメージを与えることが問題となっている。非特許文献1のFig.2には(図8)、IGZO膜へのArプラズマ照射時間に対する、IGZO膜の電気抵抗への影響が示されている。非特許文献1のFig.2には、Arイオンを照射する時間が長い程、IGZO膜の電気抵抗率が減少し、キャリア密度が高くなることが示されている。

【0006】

特許文献1の段落[0022]には、通常、酸化物半導体の電気伝導度や電子キャリア密度は成膜時の酸素分圧により制御され、主として薄膜中の酸素欠損量を制御することにより電子キャリア密度を制御することが記載されている。特許文献1には、上記酸素欠損を抑制するために、スパッタ法による薄膜成膜時に酸素を流入する方法が開示されている。

【0007】

また、非特許文献1には、IGZO膜上にSiO2保護膜を成膜する際の酸素条件によって、得られる薄膜トランジスタの閾値電圧をシフトさせ、電気特性に影響を及ぼすことが記載されている(非特許文献1、Fig.5)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2008−218495号公報

【非特許文献】

【0009】

【非特許文献1】“Improvements in the device characteristics of amorphous indium gallium zinc oxide thin-film transistors by Ar plasma treatment”, Sumsung SDI Co. Ltd., Applied Physics Letters 90, 262106 2007.

【非特許文献2】“World’s Largest(15-inch) XGA AMLCD Panel Using IGZO Oxide TFT”, Sumsung Electronics Co. Ltd., SID08 DIGEST, p.625-628

【発明の開示】

【発明が解決しようとする課題】

【0010】

しかしながら、特許文献1の、成膜ガス中の酸素流量により調整する方法では、酸素のフローむらより、酸化物半導体膜表面の位置によって成膜ガス中の酸素量が異なり、酸素導入による効果を均一に得ることが難しく、このため、膜面内において均一なキャリア密度を有する信頼性の高い膜を得ることが難しい。半導体膜の信頼性は、それを用いた薄膜素子の素子特性に大きく影響を与え、例えば、薄膜トランジスタでは、キャリア密度の信頼性の低い半導体膜を用いると、Vg−Id特性において、ドレイン電流が立ち上がるゲート印加電圧および閾値電圧が負側にシフトし、薄膜トランジスタ特性上好ましくない性質を示すことが、特許文献1にも記載されている。

【0011】

非特許文献1には、酸素条件の制御方法については一切記載されていないため、具体的な成膜条件が不明である。

【0012】

本発明は上記問題に鑑みてなされたものであり、スパッタ法により酸化物半導体膜上へ薄膜を成膜する際に、下地となるIGZO等の酸化物半導体膜のキャリア密度を膜面内において均一性高く維持することが可能な成膜方法を提供することを目的とするものである。

【0013】

また、本発明は、上記成膜方法を用いて得られた、素子特性及び信頼性の良好な半導体装置を提供することを目的とするものである。

【課題を解決するための手段】

【0014】

本発明の成膜方法は、基板上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜上に、前記基板とターゲットとを対向させて、プラズマを用いるスパッタ法により前記ターゲットの構成元素を含む薄膜を形成する成膜方法において、

該薄膜の成膜時のプラズマ中のプラズマ電位Vs(V)と、前記基板の基板電位Vsub(V)との電位差|Vs−Vsub|が下記式(1)を満足するように前記電位差を制御して前記薄膜を成膜することを特徴とするものである。本発明の成膜方法において、下記式(2)を満足するように前記電位差を制御して前記薄膜を成膜することが好ましい。

0<|Vs−Vsub|(V)≦20 ・・・(1)、

0<|Vs−Vsub|(V)≦16 ・・・(2)

【0015】

ここで、プラズマ電位とは、成膜ガスがスパッタ装置内において電離したプラズマイオンの電位の絶対値の最大値を意味する。例えば、成膜ガスとしてArガスを用いる場合は、Ar+イオン電位の最大値を意味するものとする。

【0016】

本明細書において、「電位」は、ラングミュアプローブを用いてシングルプローブ法あるいはトリプルプローブ法により測定するものとする。原理的に測定可能であれば他の手法でも構わない。

【0017】

また、成膜時の電位差|Vs−Vsub|を20(V)以下となるように制御する期間は、酸化物半導体膜上に薄膜を形成する工程の中の全期間である必要はなく、薄膜の膜厚が下地の酸化物半導体膜表面へのスパッタによる影響が無視できる範囲となるまで制御すればよい。

【0018】

また、電位差|Vs−Vsub|は、プラズマ電位Vsと基板電位Vsubの差を相対的に変化させればよいが、成膜速度に大きく影響を与えずに変化させることができることから、基板電位Vsubにバイアス印加して変化させることが好ましい。成膜速度に大きく影響を与えない範囲内であれば、プラズマ電位Vsと基板電位Vsubのどちらか、又は両方を変化させてもよい。プラズマイオンが正イオンでありプラズマ電位Vsが0Vより大きく50V以下である場合は、前記基板に正電圧をバイアス印加して電位差|Vs−Vsub|を制御することが好ましい。また、本発明の成膜方法は、前記酸化物半導体膜が、下記一般式(P1)で表される1種または複数種の酸化物からなる(不可避不純物を含んでもよい)場合に好適に適用することができる。

(In2−xGax)O3・(ZnO)m・・・(P1)

(式中0<x<2かつmは自然数)

【0019】

本発明の成膜方法において、前記成膜時の基板温度Tsが300℃以下であり、前記基板と前記ターゲットとの距離Dが40mm以上150mm以下であり、成膜圧力Pが0.1Pa以上5Pa以下であることが好ましく、成膜圧力Pは0.1Pa以上1.0Pa以下であることがより好ましい。

【0020】

また、本発明の成膜方法において、前記薄膜が絶縁体膜である場合に好適に適用することができる。

【0021】

本発明の薄膜素子は、基板上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜と、上記本発明の成膜方法により成膜された薄膜とを備えたことを特徴とするものである。かかる薄膜素子としては、前記酸化物半導体膜からなる活性層と、前記薄膜からなるゲート絶縁膜とを備えた薄膜トランジスタ等の半導体装置が挙げられる。

【0022】

上記本発明の薄膜素子は、基板を用意し、該基板上にInと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜を成膜する工程と、

該酸化物半導体膜上に、上記本発明の成膜方法により絶縁膜を形成する工程と、

前記酸化物半導体膜に電圧を印加する、又は、該酸化物半導体膜から電流を取り出す電極を形成する工程とを有する薄膜素子の製造方法により製造することができる。

【0023】

また、本発明の薄膜素子の製造方法において、前記電極を、上記本発明の成膜方法を用いて形成することが好ましい。

【発明の効果】

【0024】

本発明の成膜方法は、基板上に成膜されたIGZO等の酸化物半導体膜上に、プラズマを用いるスパッタ法により、薄膜を形成する際に、成膜時のプラズマ中のプラズマ電位Vs(V)と基板電位Vsub(V)との電位差|Vs−Vsub|を20(V)以下となるように制御して成膜している。かかる構成によれば、酸化物半導体膜のプラズマダメージによる酸素欠損を、膜面内において均一性高く抑制することができる。従って、本発明によれば、下地となるIGZO等の酸化物半導体膜のキャリア密度を膜面内において均一性高く維持することができる。

【0025】

また、プラズマ電位Vsが正であり、基板に正電圧をバイアス印加して電位差を制御する構成では、成膜レートを大きく低下させることなく電位差|Vs−Vsub|を制御することができる。

【図面の簡単な説明】

【0026】

【図1A】本発明の成膜方法好適なRFスパッタ成膜装置の概略断面図

【図1B】スパッタ成膜中の様子を模式的に示す図

【図2】RFスパッタ装置内のAr+プラズマ空間中における基板―ターゲット間の電位の分布の様子を示す模式図

【図3A】本発明に係る一実施形態の半導体装置(薄膜素子)の製造工程を示す断面図(その1)

【図3B】本発明に係る一実施形態の半導体装置の製造工程を示す断面図(その2)

【図3C】本発明に係る一実施形態の半導体装置の製造工程を示す断面図(その3)

【図3D】本発明に係る一実施形態の半導体装置の製造工程を示す断面図(その4)

【図4A】実施例1の薄膜素子サンプルの上面図

【図4B】図4AのA−A’断面図

【図5】電位差|Vs−Vsub|と酸化物半導体膜のキャリア密度の関係を示す図

【図6】ターゲット投入電力と基板電位の関係を示す図

【図7】圧力と基板電位の関係を示す図

【図8】非特許文献1のFig.2

【発明を実施するための形態】

【0027】

「薄膜の成膜方法」

図面を参照して、本発明に係る一実施形態の成膜方法について説明する。本発明の成膜方法は、基板上に成膜された、InGaZnO4(IGZO)等の酸化物半導体膜上に、プラズマを用いるスパッタ法により薄膜を成膜するものである。

【0028】

プラズマを用いるスパッタ法としては、特に制限されないが、2極スパッタリング法、3極スパッタリング法、直流スパッタリング法、高周波スパッタリング法(RFスパッタ法)、ECRスパッタリング法、マグネトロンスパッタリング法、対向ターゲットスパッタリング法、及びパルススパッタ法等が挙げられる。

【0029】

本実施形態では、RFスパッタ法を例に説明をする。図1Aは装置の全体構成を示す断面図であり、図1Bは成膜中の様子を模式的に示す図である。視認しやすくするために各部の縮尺は適宜変更してある。本実施形態では高周波スパッタリング装置(RFスパッタリング装置)を例として説明する。

【0030】

図1Aに示す成膜装置100は、内部に、基板Bが装着可能であり、装着された基板Bを所定温度に加熱することが可能な基板ホルダ11と、ターゲットTが装着可能なターゲットホルダ12とが備えられた真空容器10から概略構成されている。本実施形態の装置では、真空容器10内が成膜室となっている。真空容器10内において、基板ホルダ11とターゲットホルダ12とは互いに対向するように離間配置されている。真空容器10はステンレス等の導電体からなり、接地されている。

【0031】

基板Bは特に制限されず、Si基板、酸化物基板、ガラス基板、及び各種フレキシブル基板など、用途に応じて適宜選択することができる。基板Bはかかる基板に電極等の膜が形成されたものでもよい。ターゲットTの組成は、成膜する膜の組成に応じて選定される。

【0032】

成膜装置100においては、プラズマ電極(本実施形態ではターゲットホルダ12がプラズマ電極として機能する。)の放電により真空容器10内に導入されたガスGがプラズマ化され、Arイオン等のプラスイオンが生成する。生成したプラスイオンはターゲットTをスパッタする。プラスイオンにスパッタされたターゲットTの構成元素は、ターゲットから放出され中性あるいはイオン化された状態で基板Bに成膜される。図中、符号Pがプラズマ空間を模式的に示している。

【0033】

成膜装置100には、真空容器10内にプラズマ化させるガスGを導入するガス導入手段が設けられている。ガス導入手段は、プラズマ化させるガスGの供給源(図示略)と、供給源から供給されたガスGを真空容器10内に導入するガス導入管18とから構成されている。

【0034】

成膜装置100には、真空ポンプ等の排気手段(図示略)に接続され、真空容器10内のガスの排気Vを行うガス排出管19が備えられている。真空容器10に対するこれらガス導入管18とガス排出管19との接続箇所は適宜設計でき、これらガス導入管18とガス排出管19は真空容器10内のガス濃度がなるべく均一になるように設けられることが好ましい。ガスGとしては特に制限なく、Ar、又はAr/O2混合ガス等が使用される。

【0035】

図1Bに模式的に示すように、プラズマ電極12の放電により真空容器10内に導入された成膜ガスGがプラズマ化され、Arイオン等のプラスイオンIpが生成する。生成したプラスイオンIpはターゲットTをスパッタする。プラスイオンIpにスパッタされたターゲットTの構成原子或いは粒子(スパッタ粒子)Tpは、ターゲットから放出され中性あるいはイオン化された状態で成膜基板B(あるいは成膜基板B上に既に成膜されている薄膜表面)に蒸着される。図中、符号Pがプラズマ空間を示している。

【0036】

プラズマ空間Pの電位は、成膜時のプラズマ中のプラズマ電位Vs(V)となる。成膜基板Bの電位は基板電位Vsub(V)となる。このプラズマ空間Pの電位と成膜基板Bの電位との電位差|Vs−Vsub|の加速電圧により、ターゲットTと成膜基板Bとの間にあるスパッタ粒子Tpは、運動エネルギーを得て成膜基板B上に成膜された酸化物半導体膜1上に薄膜として堆積する。なお、酸化物半導体膜1と成膜基板Bはほぼ同じ電位と考えられる。

【0037】

基板ホルダ11は、基板Bが載置される板状のホルダ本体11Aと、ホルダ本体11Aに取り付けられ、基板Bの端部を固定する固定部材11Bとから概略構成されている。基板ホルダ11は、真空容器10の内底面に取り付けられた保持部材15により保持されている。

【0038】

ホルダ本体11A、固定部材11B、及び保持部材15はいずれもステンレス等の導電体からなり、保持部材15と真空容器10とは絶縁材を介して互いに絶縁されている(絶縁材については図示略)。基板ホルダ11は真空容器10の外部に配置された直流電流印加ユニット(電位調整手段)17に電気的に接続されており、基板ホルダ11に電位が印加可能であると共に、その電位が調整可能に構成されている。直流電流印加ユニット17は、直流電源17Aと整合回路17Bとから概略構成されている。整合回路17Bは必要に応じて設けられるものであり、直流電源17Aと基板ホルダ11との間に整合回路17Bを介在させることで、基板ホルダ11の電位調整が容易となり、好ましい。

【0039】

本実施形態では、ホルダ本体11A、固定部材11B、及び保持部材15が同電位となっている。基板ホルダ11に直流バイアス電流を印加する本実施形態では、基板自体が導電体である、あるいは基板は絶縁体であっても基板表面に電極等の導電体膜が形成されていることが好ましい。かかる構成では、基板Bと基板ホルダ11とを効果的に同電位にすることができ、好ましい。圧電体膜等の成膜では、通常下地に下部電極が形成されているので、基板電位と基板ホルダ11とを同電位にすることができる。

【0040】

本実施形態では、基板ホルダ11のホルダ本体11Aのサイズが、基板Bの外周から基板Bの側方に10mm以上大きく設計されていることが好ましい。

【0041】

ターゲットホルダ12はターゲットTが載置される板状のホルダ本体からなり、真空容器10に取り付けられた保持部材16により保持されている。保持部材16と真空容器10とは絶縁材を介して互いに絶縁されている。保持部材16は真空容器10の外部に配置された高周波電源(RF電源)13に接続されており、ターゲットホルダ12がプラズマを発生させるためのプラズマ電極(カソード電極)となっている。高周波電源13のターゲットホルダ接続側と反対側は接地されている。

【0042】

本実施形態では、真空容器10内にプラズマを発生させるプラズマ発生手段14として、高周波電源13及びプラズマ電極(カソード電極)として機能するターゲットホルダ12が備えられている。

【0043】

背景技術において述べたように、プラズマを用いるスパッタ法により、IGZO等の酸化物半導体膜1上に薄膜2を成膜する際に、プラズマダメージにより酸化物半導体膜1のキャリア密度が高くなり、電気特性を低下させること、そして、通常、キャリア密度は、膜中の酸素欠損量により制御されることを述べた。

【0044】

特許文献1及び非特許文献1、2より、スパッタ法におけるプラズマダメージによるキャリア密度の増大は、酸化物半導体膜1へのプラズマイオンの衝突により酸化物半導体膜中1の酸素がスパッタされて膜中から抜ける、酸素欠損によるものと考えられる。

【0045】

膜中の酸素量によりキャリア密度が変化することは本発明者も確認している。本発明者は、IGZO膜のスパッタ成膜時の成膜ガス中の酸素量を変化させて、膜中の酸素量とキャリア密度との関係を調べた。その結果、酸素量が多くなるほどキャリア密度が低くなること、そして、成膜ガス中の酸素の体積分率を約0.8%とすることにより、薄膜トランジスタの半導体膜として用いる場合に、0V近辺で立ち上がる良好な特性を有するキャリア密度(1×1014〜1×1015(個/cm3))が得られることを確認している。

【0046】

酸素欠損を補う方法としては、特許文献1では酸素を真空容器中に流入させて積極的に酸素元素を膜中に注入する方法が開示されているが、既に述べたようにフローむらにより、酸素欠損抑制効果が膜面内にて均一に得られないことから、膜質が不均一となり、酸化物半導体膜としての信頼性が低いものとなってしまう。更に、酸素を真空容器中に流入させると成膜速度に大きく影響を及ぼし良好な生産性を維持することが難しい。

【0047】

本発明者は、下地となる酸化物半導体膜のキャリア密度の面内均一性を保って酸素欠損を補う方法について鋭意検討を行った。

【0048】

上記のように、酸化物半導体膜1への酸素欠損(プラズマダメージ)は、酸化物半導体膜1がスパッタされることにより生じる現象である。プラズマイオンは、自分自身の電位と、スパッタするターゲットあるいは基板との電位差によりエネルギーを得てターゲットあるいは基板をスパッタする。

【0049】

図2は、RFスパッタ装置内のAr+プラズマ空間中において基板を接地した場合の、基板―ターゲット間の電位の分布の様子を示す模式図である。図2に示されるように、ArガスはプラズマによりAr+と電子に電離しており、ターゲット側はAr+と電子のRFの反応速度の違いによる自己バイアスにより負電位(−100〜−150V程度)となっている。プラズマ電位は、基板―ターゲット間のプラズマ空間においてAr+の電位(最大電位)となり、接地されている基板では0Vとなっている。

【0050】

Ar+プラズマイオンは陽イオンであるため、負電位のターゲット側に加速してターゲットに衝突するが、ターゲットの構成元素のスパッタ閾値以上のエネルギーを有している場合にその元素は叩き出され(スパッタされ)、対向配置されている基板側に成膜される。プラズマのエネルギーは、プラズマイオンとスパッタされる側の電位差が大きいほど大きくなる。

【0051】

一方、図示されるように、基板電位Vsubとプラズマ電位Vsとにも電位差があるため、その電位差に応じたエネルギーで基板側の表面はスパッタされ、これがプラズマダメージの要因となると考えられる。従って、酸化物半導体膜のプラズマダメージを抑制するためには、酸化物半導体膜の電位、つまり、基板電位Vsubと、プラズマ電位Vsとの電位差|Vs―Vsub|(V)を小さくすることにより、酸化物半導体膜表面に衝突するプラズマエネルギーが小さくなり、酸素のスパッタを抑制することができると考えられる。かかる方法では、膜面内において均一性高く、酸化物半導体膜のプラズマダメージによる酸素欠損を抑制することができる。なお、|Vs―Vsub|(V)はそのまま電子温度(eV)に変換することができる。電子温度1eV=11600K(Kは絶対温度)に相当する。

【0052】

本発明者は、酸化物半導体膜のプラズマダメージによる酸素欠損を、膜面において均一性高く抑制することができる電位差|Vs−Vsub|について好適な範囲を見出した。

【0053】

すなわち、本発明の成膜方法は、基板B上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜1上に、基板BとターゲットTとを対向させて、プラズマを用いるスパッタ法によりターゲットTの構成元素を含む薄膜2を形成する成膜方法であって、成膜時のプラズマ中のプラズマ電位Vs(V)と、基板Bの基板電位Vsub(V)との電位差|Vs−Vsub|が下記式(1)を満足するようにこの電位差を制御して薄膜2を成膜することを特徴とするものである。

0<|Vs−Vsub|(V)≦20 ・・・(1)

【0054】

後記実施例の図5に、本発明者が見いだした|Vs−Vsub|と、酸化物半導体膜のキャリア密度との関係を示してある。一般に、半導体膜のキャリア密度は、キャリア密度が約1X1014〜1X1015(個/cm3)が好適であるとされている。図5には、スパッタ法によって酸化物半導体膜1上に成膜する際、電位差|Vs−Vsub|が上記式(1)を満足する範囲内であれば、酸化物半導体膜1のキャリア密度を半導体装置等に用いる半導体膜として好適な範囲に維持し、酸化膜半導体膜上に薄膜2を成膜することができることが示されている。

【0055】

さらに、下記式(2)を満足する場合には、薄膜2形成後の酸化物半導体膜1のキャリア密度は、薄膜2形成前の10倍以内に抑えられており、酸化物半導体膜1のキャリア密度の変化をさらに良好に抑制でき、好ましい。|Vs−Vsub|の値は、求められる半導体膜のキャリア密度により設定すればよい。すなわち、|Vs−Vsub|は、求められる半導体膜のキャリア密度が得られる閾値以下に設定すればよい。

【0056】

0<|Vs−Vsub|(V)≦16 ・・・(2)

本実施形態の酸化物半導体膜1上に薄膜2を成膜する方法によれば、酸化物半導体膜1上に薄膜2を成膜する際に電位差|Vs−Vsub|を好適化することによりプラズマダメージを抑制するため、特許文献1に示される成膜ガス中に酸素を混合する方法に比して、酸化物半導体膜1で得られる酸素欠乏抑制効果の膜面内均一性が高く、その結果、酸化物半導体のキャリア密度を均一且つ良好に維持して、薄膜2を成膜することができる。

【0057】

電位差|Vs−Vsub|は、プラズマ電位Vsと基板電位Vsubの差を相対的に変化させればよく、例えば、プラズマ電位Vsと基板電位Vsubのどちらかを変化させてもよく、両方を変化させてもよい。

【0058】

本実施形態の成膜装置100では、基板ホルダ11に直流電流印加ユニット(電位調整手段)17が電気的に接続されており、基板ホルダ11に電位が印加可能であると共に、その電位が調整可能に構成されている。かかる構成では、基板Bに電圧を印加して基板電位Vsubを制御することにより、電位差|Vs−Vsub|を制御することが好ましい。プラズマ電位Vsが正電位である場合は、Vsubとして基板Bに正電圧をバイアス印加して電位差|Vs−Vsub|を制御する。

【0059】

基板Bにバイアス印加することにより、電位差|Vs−Vsub|を制御する構成では、成膜速度や、膜質等に影響を及ぼすプラズマ電位を変化させない上、成膜ガスに酸素を等の反応速度を低下させるガスを混合しないため成膜速度の低下を抑制し、生産効率よく成膜を実施することができる。

【0060】

また、既に述べたように、上記式(1)を満足するように|Vs−Vsub|の制御する期間は、酸化物半導体膜上に薄膜を形成する工程の中の全期間であってもよいし、薄膜の膜厚が下地の酸化物半導体膜表面へのスパッタによる影響が無視できる範囲となるまでの一部の期間としてもよい。例えば、酸化物半導体膜1上に薄膜2を成膜する期間のうち、膜2が所定の厚み、例えば数nm程度になるまで、電位差|Vs−Vsub|を20(V)以下に制御し、その後電位差|Vs−Vsub|を20(V)以上の値(従来の成膜条件による電位差)に戻して薄膜2の成膜を行ってもよい。

【0061】

また、式(1)を満足する範囲内に制御する期間中において、電位差|Vs−Vsub|は一定値に維持してもよく、電位差|Vs−Vsub|を複数の値に連続的に、あるいは断続的に変化させてもよい。なお、電位差|Vs−Vsub|を成膜途中に変更することにより、薄膜2の種類によっては、膜特性に影響を及ぼす可能性がある。従って、電位差|Vs−Vsub|を途中変更する構成は、膜特性への影響を無視できる範囲で行うことが好ましい。

【0062】

電位差|Vs−Vsub|の制御は、上記基板電位をバイアス印加により変化させる方法に限らず、電位差|Vs−Vsub|の制御が行える方法であれば種々の方法を適用できる。

【0063】

例えば、後記実施例2に示されるように、ターゲット投入電力、成膜圧力により制御することも可能である。しかしながら、後記実施例2の図6、図7に示されるように、成膜圧力及びターゲット投入電力を変化させることにより、プラズマ電位Vsを変化させることは可能であるが、図示されるように変化率が小さく、例えば、Arイオンを用いる場合には、ターゲット投入電力により|Vs−Vsub|を20V以下とするのは難しく、また、成膜圧力により|Vs−Vsub|を20V以下とするには、10Pa以上の圧力が必要となり、成膜速度が非常に遅くなるため生産性の点で好ましくない。

【0064】

一般に、スパッタ法においては、ターゲット投入電力は4W以上、成膜圧力は0.1Pa以上5Pa以下、より好ましくは1Pa以下で成膜を実施しなければ生産性上現実的ではない。成膜圧力は、元素の種類によってその値は異なるが、大きすぎるとターゲットTからたたき出された粒子が散乱等の影響により基板Bに到達する割合が少なくなり成膜が難しくなる。また、小さすぎても安定したプラズマ空間を得ることができない。

【0065】

従って、成膜圧力及びターゲット投入電力による制御は、生産性を良好に保つことができるプラズマイオン種を用いている構成、基板のバイアス印加と組み合わせる構成、あるいは、薄膜の膜厚が下地の酸化物半導体膜1表面へのスパッタによる影響が無視できる範囲となるまでの最短期間の制御とする構成が好適であると考えられる)。

薄膜2の|Vs−Vsub|以外の成膜条件としては、成膜装置内のプラズマが安定して発生可能であれば特に制限されないが、良好な生産性で成膜が実施できる条件であることが好ましい。上記酸化物半導体膜1が、フレキシブルデバイスとして好適であることから、使用する基板の耐熱温度以下の温度にて、好適に成膜可能な条件とすることが好ましい。一般に、樹脂基板の耐熱温度は、ポリイミド等の耐熱性の高いもので300℃程度であることから、成膜温度Tsは300℃以下であることが好ましい。

【0066】

基板−ターゲット間距離Dは、長いほど成膜速度が遅くなるが、成膜される膜の均一性等は良好になる。また、短すぎるとプラズマの安定性を損なうことから、基板−ターゲット間距離Dは40mm以上150mm以下であることが好ましい。

以下に、上記本発明の成膜方法を適用するに好適な材料構成について説明する。

【0067】

本実施形態において、基板Bは特に制限されず、Si基板、ガラス基板、各種フレキシブル基板等、用途に応じて選択すればよい。本発明では、樹脂基板の耐熱温度以下の温度で成膜が可能な酸化物半導体膜を備えた構成としている。従って、成膜基板Bは、樹脂基板等のフレキシブル基板を使用することができる。

【0068】

フレキシブル基板としては、ポリビニルアルコール系樹脂,ポリカーボネート誘導体(帝人(株):WRF),セルロース誘導体(セルローストリアセテート,セルロースジアセテート),ポリオレフィン系樹脂(日本ゼオン(株):ゼオノア、ゼオネックス),ポリサルホン系樹脂(ポリエーテルサルホン,ポリサルホン),ノルボルネン系樹脂(JSR(株): アートン),ポリエステル系樹脂(PET,PEN,架橋フマル酸ジエステル)ポリイミド系樹脂,ポリアミド系樹脂,ポリアミドイミド系樹脂,ポリアリレート系樹脂,アクリル系樹脂,エポキシ系樹脂,エピスルフィド系樹脂,フッ素系樹脂,シリコーン系樹脂フィルム,ポリベンズアゾ-ル系樹脂,シアネート系樹脂,芳香族エーテル系樹脂(ポリエーテルケトン),マレイミド−オレフィン系樹脂等の樹脂基板、液晶ポリマー基板、

また、これら樹脂基板中に酸化ケイ素粒子,金属ナノ粒子,無機酸化物ナノ粒子,無機窒化物ナノ粒子, 金属系・無機系のナノファイバー又はマイクロファイバー,カーボン繊維,カーボンナノチューブ,ガラスフェレーク,ガラスファイバー,ガラスビーズ,粘土鉱物、雲母派生結晶構造を含んだ複合樹脂基板、

薄いガラスと上記単独有機材料との間に少なくとも1回の接合界面を有する積層プラスチック材料、無機層(ex.SiO2, Al2O3, SiOxNy)と有機層(上記)を交互に積層することで少なくとも1回以上の接合界面を有するバリア性能を有する複合材料、

ステンレス基板、あるいはステンレスと異種金属を積層した金属多層基板、アルミニウム基板、あるいは、表面に酸化処理(例えば、陽極酸化処理)を施すことで、表面の絶縁性を向上してある酸化被膜付きのアルミニウム基板等を挙げることができる。

【0069】

酸化物半導体膜1としては、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体からなる(不可避不純物を含んでもよい)ものであれば特に制限されないが、下記一般式(P1)で表されるInGaZnO4(IGZO)等のホモロガス化合物が一例として挙げられる。

(In2−xGax)O3・(ZnO)m・・・(P1)

(式中0<x<2かつm>0)

【0070】

酸化物半導体膜1の成膜方法は特に制限されず、気相法、液相法など、用いる基板や酸化物半導体の種類に応じて好適な成膜方法を用いてよい。

【0071】

酸化物半導体膜1上に成膜する薄膜2としては特に制限されず、導電体膜、半導体膜、絶縁体膜、及び誘電体膜等の任意の組成の膜の成膜に適用することができる。薄膜トランジスタの半導体層として酸化物半導体膜1を用いる場合には、保護膜やゲート絶縁膜、層間絶縁膜等の絶縁膜、及びソース/ドレイン電極等が挙げられる。

【0072】

薄膜トランジスタのこれらの絶縁膜としては、Ga2O3、SiO2、Al2O3、SiON、SiN、HfO2、Y2O3、Ta2O5、MgO等の酸化物からなる(不可避不純物を含んでもよい。)絶縁膜が挙げられる。

【0073】

また、ソース/ドレイン電極としては、Pt,Au,Pd,Cr,Ni,Mo,Ag,W,Cu,Ti,In,Sn等の金属又はこれらの合金、錫酸化物、酸化インジウム、インジウム錫酸化物(ITO)等が挙げられる。

【0074】

Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体においては、構成元素のスパッタされやすさ(スパッタ率)は酸素が格段に高い(スパッタ閾値が格段に低いことと同意)。従って、上記酸化物半導体膜においては、その上に成膜する膜のスパッタ成膜時に、膜表面から抜けて欠損を生じる元素は酸素の割合が格段に大きく、酸素欠損はキャリア密度へ大きく影響を及ぼす要因となる。上記Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeのスパッタ率は、Znが大きいが、今回、酸化物半導体膜上に成膜する各種膜(保護膜、絶縁膜、電極等)の成膜条件下においては、これらの元素についてはほぼ同様と考えてよく、酸素欠損による影響を考慮すればよい。ここで、「スパッタ率」とは、入射イオンの数とそれによってスパッタされた原子数との比で定義されるものであり、その単位は(atoms/ion)である。例えば、「真空ハンドブック」((株)アルバック編、オーム社発行)の表8.1.7には、Arイオン300eVの条件におけるスパッタ率が記載されている。

【0075】

本発明の成膜方法は、基板B上に成膜されたIGZO等の酸化物半導体膜1上に、プラズマを用いるスパッタ法により、薄膜2を形成する際に、成膜時のプラズマ中のプラズマ電位Vs(V)と基板電位Vsub(V)との電位差|Vs−Vsub|を、20(V)以下となるように制御して成膜している。かかる構成によれば、酸化物半導体膜1のプラズマダメージによる酸素欠損を、膜面内において均一性高く抑制することができる。従って、本発明によれば、下地となるIGZO等の酸化物半導体膜1のキャリア密度を膜面内において均一性高く維持して薄膜2を成膜することができる。

【0076】

また、プラズマ電位Vsが正であり、基板Bに正電圧をバイアス印加して電位差|Vs−Vsub|を制御する構成では、成膜速度を大きく低下させることなく電位差を制御することができ、好ましい。

【0077】

「半導体装置(薄膜素子)」

図3Aから図3Dを参照して、上記実施形態の酸化物半導体膜1及び薄膜2を用いた半導体装置(薄膜素子)3及びその製造方法について説明する。本実施形態では、ボトムゲート型を例として説明する。図3Aから図3Dは、薄膜トランジスタ(TFT)の製造工程図(基板の厚み方向の断面図)である。視認しやすくするため、構成要素の縮尺は実際のものとは適宜異ならせてある。

【0078】

本実施形態の半導体装置(薄膜トランジスタ:TFT)3は、基板B上に、上記実施形態の酸化物半導体膜1を用いて得られた活性層32と、上記実施形態の成膜方法により成膜された保護膜(絶縁膜)2と、電極とを備えたものである。

【0079】

まず、図3Aに示すように、基板Bを用意し、n+Si等からなるゲート電極30及びゲート絶縁膜31を形成する。ゲート絶縁膜31としては、先述の絶縁体材料等があげられる。基板Bは、上記実施形態で説明したのと同様の基板が使用できる。

【0080】

次いで、図3Bに示すように、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜1(活性層32)を形成する。成膜方法については、上記成膜方法の実施形態において記載したとおりである。

【0081】

さらに、図3Cに示すように、活性層32上にソース電極33及びドレイン電極34を形成する。ソース電極33及びドレイン電極34は、スパッタ法、蒸着法等の気相成膜とフォトリソグラフィ法によるパターニングを組み合わせた製造方法やインクジェット法等により形成することができる。

【0082】

最後に、図3Dに示すように、活性層32、ソース電極33及びドレイン電極34上に上記実施形態の成膜方法により、保護膜(絶縁膜)2を形成する。

以上の工程により、本実施形態の半導体装置(TFT)3が製造される。

【0083】

本実施形態の半導体装置(TFT)3は、酸化物半導体膜1を用いて得られた活性層32上に、上記本発明の成膜方法により成膜された保護膜2を備えたものであるので、上記本発明の成膜方法と同様の効果を奏する。本実施形態の半導体装置3は、信頼性の高いキャリア密度の安定した酸化物半導体膜1を備えているので、ON−OFF特性が良好かつ安定性の高いものとなる。

【0084】

また、本実施形態において半導体装置の製造方法では、全工程の成膜を300℃以下の成膜温度にて実施することができるため、耐熱性の低いフレキシブル基板等上にも良好な半導体特性を示す半導体装置3を得ることができる。従って、本発明の半導体装置の製造方法によれば、フレキシブルな大画面有機ELディスプレイ等の様々な電気製品に好適に用いることができる、高品質な半導体装置を提供可能である。

【0085】

本実施形態のようなボトムゲート型の場合、ソース電極33及びドレイン電極34を生産性の高いスパッタ法により成膜する場合は、上記本発明のスパッタ法による成膜方法により成膜する構成とすることが好ましい。ソース電極33及びドレイン電極34をスパッタ法により成膜する際に受けるプラズマダメージは、オーミックコンタクトの観点からは良い方向に働くが、酸化物半導体膜のキャリア密度が高くなると、ソースードレイン間の抵抗が下がり、半導体装置のON−OFF特性が低下してしまう。従って、ソース電極33及びドレイン電極34を上記本発明の成膜方法により成膜することにより、ON−OFF特性のより良好な半導体装置を製造することができる。

【0086】

「設計変更」

上記実施形態において、スパッタ成膜装置としてRFスパッタ成膜装置を用いたが、上記の成膜条件となるようにプラズマ空間電位を調整できればスパッタリング装置は特に制限されない。

【0087】

なお、本実施例は、プラズマ電位Vsが基板電位Vsubより高い場合の例であるが、基板電位Vsubがプラズマ電位Vsより高い場合も、電位差|Vs−Vsub|が上述の値以下になるよう制御すれば、同様の効果を得ることができる。

【0088】

また、酸化物半導体膜1を備えた半導体装置について説明したが、半導体装置以外の、センサやアクチュエータなどの半導体デバイスにも適用可能である。

【実施例】

【0089】

本発明に係る実施例及び比較例について説明する。

(実施例1)

約1cm2の正方形の市販の合成石英基板(1mm厚,入江株式会社製T−4040合成石英基板)上に、IGZO半導体膜、電極、及び、上記本発明の成膜方法により成膜された絶縁膜(保護膜)を備えた薄膜素子サンプルを下記のようにして複数用意した。図4Aは、薄膜素子サンプルの上面図、図4Bは図4AのA−A’断面図である。図4Aにおいて、基板の縦辺および横辺のサイズはW1=10(mm)、IGZO膜の縦辺および横辺のサイズはW2=8(mm)、電極間の距離はW3=6(mm)である。

【0090】

まず、パスカル社製マルチスパッタ装置を用いて、基板上に膜厚50nmのIGZO膜を成膜した。成膜条件は、基板温度Ts=常温、到達真空度6.0X10−6Pa、Ar/O2混合雰囲気(O2体積分率0.8%)、成膜圧力0.8Pa、ターゲットInGaZnO4及びZnO(共に、4Nターゲット)、基板―ターゲット間距離150mm、ターゲット投入電力DC50W(IGZO)、DC10W(ZnO)、成膜時間30分であった。

【0091】

次いで、上記IGZO膜上の4つの角領域に、Ti/Au電極(厚み50nm/200nm)を真空蒸着法により成膜した。

【0092】

成膜されたIGZO膜のキャリア密度を、東陽テクニカ製ACホール測定システム(RESITEST8300)を用いて測定したところ、キャリア密度は約2X1014(個/cm3)であった。

【0093】

複数の各薄膜素子サンプルに対し、IGZO成膜時と同じスパッタ装置を用いて、それぞれ異なる電位差|Vs―Vsub|となるように基板に接地電位(0V)〜26Vの範囲でバイアス印加して、絶縁膜であるGa2O3を、電極表面が一部露出するようにメタルマスクを使用して成膜した。なお、日本高周波製トリプルプローブモニタ(TPM−2000)を用いて、図1Aに示す基板位置近傍Cのプラズマ電位を測定したところ、プラズマ電位Vsは26(V)であった。

【0094】

成膜条件は、基板温度Ts=常温、到達真空度7.0X10−6Pa、Ar雰囲気、成膜圧力0.4Pa、ターゲットGa2O3(4Nターゲット)、基板―ターゲット間距離150mm、ターゲット投入電力RF50W、成膜時間30分であった。

【0095】

絶縁膜成膜後の薄膜素子のキャリア密度を、上記と同様にして測定した結果を表1及び図5に示す。表1及び図5には、基板電位を接地電位(0V)とした場合(|Vs―Vsub|≒26V)には、キャリア密度が約1X1017(個/cm3)に増大していること、そして、基板へのバイアス印加により、|Vs―Vsub|を20V以下とすれば、キャリア密度の増大を1桁以内に抑制できること、更に、16V以下とすることにより、良好な半導体特性を有する範囲内のキャリア密度(1×1014〜1×1015(個/cm3)に維持できることが示されている。

【0096】

以上により、成膜時のプラズマ中のプラズマ電位Vs(V)と基板電位Vsub(V)との電位差|Vs−Vsub|を20(V)以下、好ましくは16V以下に制御することで、プラズマイオンによる酸化物半導体膜への衝突による酸素欠損を抑え、酸化物半導体膜中のキャリア密度の増大を抑制して、酸化物半導体膜上に薄膜を成膜することが可能であることが実証された。

【表1】

【0097】

(実施例2)

基板へのバイアス印加以外の方法で|Vs―Vsub|を20V以下に制御可能な成膜条件について検討を行った。成膜条件として、成膜圧力(デポ圧)及びターゲット投入電力を選定し、基板電位を接地電位として、これらの成膜条件を変化させた時の図1Aに示す基板位置近傍Cのプラズマ電位の変化の様子を、実施例1と同様に日本高周波製トリプルプローブモニタ(TPM−2000)を用いて調べた。変化させた成膜条件以外の成膜条件は実施例1と同様とした。

【0098】

図6及び図7に得られた結果を示す。図6は、ターゲット投入電力と基板電位の関係を示した図であり、図7は、成膜圧力と基板電位の関係を示した図である。

【0099】

図6に示されるように、ターゲット投入電力を25W〜100Wの間で変化させると、プラズマ電位Vs22V〜30Vに、つまり、電位差|Vs−Vsub|を22V〜30Vに制御できることが確認された。

【0100】

また、図7に示されるように、成膜圧力を、0.4Pa〜20Paまで変化させると、プラズマ電位Vs18V〜26Vに、つまり、電位差|Vs−Vsub|を18V〜26Vに制御できることが確認された。

【産業上の利用可能性】

【0101】

本発明は、プラズマを用いるスパッタ法による任意の組成を有する成膜に適用することができる。本発明は、液晶ディスプレイや有機ELディスプレイに搭載される薄膜トランジスタや、X線センサ、アクチュエータの製造に好ましく適用することができる。

【符号の説明】

【0102】

1 酸化物半導体膜

2 薄膜(絶縁膜,保護膜)

3 半導体装置(薄膜素子,薄膜トランジスタ)

10 真空容器

11 基板ホルダ

12 プラズマ電極(ターゲットホルダ)

13 高周波電源

14 プラズマ発生手段

17 直流電流印加ユニット(電位調整手段)

18 ガス導入管

19 ガス排出管

21,22,30,33,34 電極

100 スパッタ成膜装置

B 成膜基板

G 成膜ガス

Ip プラスイオン

P プラズマ空間

T ターゲット

Tp スパッタ粒子

Vsub 基板電位

Vs プラズマ電位

【特許請求の範囲】

【請求項1】

基板上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜上に、前記基板とターゲットとを対向させて、プラズマを用いるスパッタ法により前記ターゲットの構成元素を含む薄膜を形成する成膜方法において、

該薄膜の成膜時のプラズマ中のプラズマ電位Vs(V)と、前記基板の基板電位Vsub(V)との電位差|Vs−Vsub|が下記式(1)を満足するように前記電位差を制御して前記薄膜を成膜することを特徴とする成膜方法。

0<|Vs−Vsub|(V)≦20 ・・・(1)

【請求項2】

下記式(2)を満足するように前記電位差を制御して前記薄膜を成膜することを特徴とする請求項1に記載の成膜方法。

0<|Vs−Vsub|(V)≦16 ・・・(2)

【請求項3】

前記プラズマ電位Vsが0Vより大きく50V以下であり、前記基板に正電圧をバイアス印加して前記電位差を制御することを特徴とする請求項1又は2に記載の成膜方法。

【請求項4】

前記酸化物半導体膜が、下記一般式(P1)で表される1種または複数種の酸化物からなる(不可避不純物を含んでもよい。)ことを特徴とする請求項1〜3のいずれかに記載の成膜方法。

(In2−xGax)O3・(ZnO)m・・・(P1)

(式中0<x<2かつm>0)

【請求項5】

前記成膜時の基板温度Tsが300℃以下であり、前記基板と前記ターゲットとの距離Dが40mm以上150mm以下であり、成膜圧力Pが0.1Pa以上5Pa以下であることを特徴とする請求項1〜4のいずれかに記載の成膜方法。

【請求項6】

成膜圧力Pが0.1Pa以上1Pa以下であることを特徴とする請求項5に記載の成膜方法。

【請求項7】

前記薄膜が、絶縁体膜であることを特徴とする請求項1〜6のいずれかに記載の成膜方法。

【請求項8】

基板を用意し、該基板上にInと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜を成膜する工程と、

該酸化物半導体膜上に、請求項1〜7のいずれかに記載の成膜方法により絶縁膜を形成する工程と、

前記酸化物半導体膜に電圧を印加する、又は、該酸化物半導体膜から電流を取り出す電極を形成する工程とを有することを特徴とする薄膜素子の製造方法。

【請求項9】

前記電極を、請求項1〜7のいずれかに記載の成膜方法を用いて形成することを特徴とする請求項8に記載の薄膜素子の製造方法。

【請求項10】

前記薄膜素子が、半導体装置であることを特徴とする請求項9に記載の薄膜素子の製造方法。

【請求項1】

基板上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜上に、前記基板とターゲットとを対向させて、プラズマを用いるスパッタ法により前記ターゲットの構成元素を含む薄膜を形成する成膜方法において、

該薄膜の成膜時のプラズマ中のプラズマ電位Vs(V)と、前記基板の基板電位Vsub(V)との電位差|Vs−Vsub|が下記式(1)を満足するように前記電位差を制御して前記薄膜を成膜することを特徴とする成膜方法。

0<|Vs−Vsub|(V)≦20 ・・・(1)

【請求項2】

下記式(2)を満足するように前記電位差を制御して前記薄膜を成膜することを特徴とする請求項1に記載の成膜方法。

0<|Vs−Vsub|(V)≦16 ・・・(2)

【請求項3】

前記プラズマ電位Vsが0Vより大きく50V以下であり、前記基板に正電圧をバイアス印加して前記電位差を制御することを特徴とする請求項1又は2に記載の成膜方法。

【請求項4】

前記酸化物半導体膜が、下記一般式(P1)で表される1種または複数種の酸化物からなる(不可避不純物を含んでもよい。)ことを特徴とする請求項1〜3のいずれかに記載の成膜方法。

(In2−xGax)O3・(ZnO)m・・・(P1)

(式中0<x<2かつm>0)

【請求項5】

前記成膜時の基板温度Tsが300℃以下であり、前記基板と前記ターゲットとの距離Dが40mm以上150mm以下であり、成膜圧力Pが0.1Pa以上5Pa以下であることを特徴とする請求項1〜4のいずれかに記載の成膜方法。

【請求項6】

成膜圧力Pが0.1Pa以上1Pa以下であることを特徴とする請求項5に記載の成膜方法。

【請求項7】

前記薄膜が、絶縁体膜であることを特徴とする請求項1〜6のいずれかに記載の成膜方法。

【請求項8】

基板を用意し、該基板上にInと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜を成膜する工程と、

該酸化物半導体膜上に、請求項1〜7のいずれかに記載の成膜方法により絶縁膜を形成する工程と、

前記酸化物半導体膜に電圧を印加する、又は、該酸化物半導体膜から電流を取り出す電極を形成する工程とを有することを特徴とする薄膜素子の製造方法。

【請求項9】

前記電極を、請求項1〜7のいずれかに記載の成膜方法を用いて形成することを特徴とする請求項8に記載の薄膜素子の製造方法。

【請求項10】

前記薄膜素子が、半導体装置であることを特徴とする請求項9に記載の薄膜素子の製造方法。

【図1A】

【図1B】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図4A】

【図4B】

【図5】

【図6】

【図7】

【図8】

【図1B】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図4A】

【図4B】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−142174(P2011−142174A)

【公開日】平成23年7月21日(2011.7.21)

【国際特許分類】

【出願番号】特願2010−1336(P2010−1336)

【出願日】平成22年1月6日(2010.1.6)

【出願人】(306037311)富士フイルム株式会社 (25,513)

【復代理人】

【識別番号】100160679

【弁理士】

【氏名又は名称】中島 弘子

【Fターム(参考)】

【公開日】平成23年7月21日(2011.7.21)

【国際特許分類】

【出願日】平成22年1月6日(2010.1.6)

【出願人】(306037311)富士フイルム株式会社 (25,513)

【復代理人】

【識別番号】100160679

【弁理士】

【氏名又は名称】中島 弘子

【Fターム(参考)】

[ Back to top ]