抵抗体チップ及びその実装方法

【課題】薄膜抵抗体を高密度に積層した抵抗体チップを提供する。

【解決手段】シリコン基板1上には、上下に離隔して複数層の薄膜抵抗体群が積層されている。各層の薄膜抵抗体群は、同一平面に平行に配列された複数の帯状の薄膜抵抗体7−1a・・・により構成されている。各層毎の複数の薄膜抵抗体7−1a・・・は、各層の層間絶縁膜4−1・・・によりそれぞれ被覆されている。複数のプラグ6は、各層の複数の薄膜抵抗体7−1a・・・にそれぞれ接続され、複数層の層間絶縁膜4−1・・・を上下に貫通して最上層の層間絶縁膜4−4の表面に引き出されている。複数のプラグ6の上端には、パッド7−1a・・・がそれぞれ接合され、この複数のパッド7−1a・・・が、最上層の層間絶縁膜4−4上において離隔して配置されている。最上層の層間絶縁膜4−4は、パッドパッド7−1a・・・を除いてパッシベーション膜8により被覆されている。

【解決手段】シリコン基板1上には、上下に離隔して複数層の薄膜抵抗体群が積層されている。各層の薄膜抵抗体群は、同一平面に平行に配列された複数の帯状の薄膜抵抗体7−1a・・・により構成されている。各層毎の複数の薄膜抵抗体7−1a・・・は、各層の層間絶縁膜4−1・・・によりそれぞれ被覆されている。複数のプラグ6は、各層の複数の薄膜抵抗体7−1a・・・にそれぞれ接続され、複数層の層間絶縁膜4−1・・・を上下に貫通して最上層の層間絶縁膜4−4の表面に引き出されている。複数のプラグ6の上端には、パッド7−1a・・・がそれぞれ接合され、この複数のパッド7−1a・・・が、最上層の層間絶縁膜4−4上において離隔して配置されている。最上層の層間絶縁膜4−4は、パッドパッド7−1a・・・を除いてパッシベーション膜8により被覆されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄型受動部品の1つである薄型抵抗体部品、特に、薄膜抵抗体を高密度に積層した抵抗体チップとその実装方法に関するものである。

【背景技術】

【0002】

従来、薄型受動部品を積層する技術としては、例えば、次のような文献に記載されるものがあった。

【0003】

【非特許文献1】荻野等「集積受動素子の開発」、第17回エレクトロニクス実装学術講演大会集、2003年3月、13B−16、p.177−178

【非特許文献2】益・岡田「シリコン上の高周波受動素子技術」、応用物理、2004年9月、第73巻、第9号、p.1172−1178

【0004】

非特許文献1に示されているように、近年の電子機器の小型化は、急激であり、特に、携帯電話に代表されるモバイル機器は小型・軽量化の要求が高く、かつ、高機能化の要求も高まっている。携帯電話等の高周波(RF)送受信回路回路を含むデバイスは、コンデンサ、抵抗、インダクタ等の受動部品を多く搭載する。現在での実装面積におけるこの受動部品の割合は60%程度を占めており、小型化の大きな障害となっている。

【0005】

又、非特許文献2に示されているように、シリコン上に高周波用受動部品を搭載する開発も進んでいる。

【発明の開示】

【発明が解決しようとする課題】

【0006】

従来の受動部品は部品単体で、ある程度の大きさと厚みがあるために、表面実装する以外に実装方法がなく、従って実装面積を削減するためには部品の大きさを小さくするしか方法がなく、その方向で小型化が進められてきた。しかし、その小型化も限界に近くなってきており、物性的にも限界に近づいている。更に、部品の小型化に伴い、部品を実装するマウンタ(搭載機)が対応できなくなってきている。

【0007】

即ち、受動部品では1つの部品がある程度の大きさと厚みを有しているために、平面的に表面実装しなければならないので、今後の小型軽量、高機能化のための実装面積の減少と実装部品点数の増加に対応できない。部品の小型化は限界に達してきており、この限界を超えて小型化できても、小さすぎて実際にマウンタでハンドリング(把持)することが不可能になる。

【0008】

本発明は、上記のような限界をなくし、狭い実装面積に、多くの抵抗体を実装する薄型の抵抗体チップとその実装方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明の抵抗体チップは、基板と、同一平面に平行に配列された複数の帯状の薄膜抵抗体が、前記基板上において上下に離隔して複数層積層された薄膜抵抗体群と、前記各層毎の複数の薄膜抵抗体をそれぞれ被覆する複数層の層間絶縁膜と、横方向に離隔して配置されて前記各層の複数の薄膜抵抗体にそれぞれ接続された複数のプラグであって、前記複数層の層間絶縁膜を上下に貫通して前記最上層の層間絶縁膜の表面に引き出された前記複数のプラグと、前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極とを備えている。

【0010】

本発明の抵抗体チップにおいて、前記最上層の層間絶縁膜は、前記複数の電極を露出させた状態でパッシベーション膜により被覆してもよい。前記各層の複数の薄膜抵抗体における下面に、ストッパ絶縁膜をそれぞれ形成してもよい。前記各電極上には、導電性ポストを立設してもよい。又、前記複数の電極に接続され、前記パッシベーション膜上に配置された再配線層と、前記再配線層に接続され、所定の平面位置に配置された複数のパッドと、前記複数のパッドを露出させた状態で前記再配線層を被覆する絶縁膜とを設けてもよい。

【0011】

本発明の抵抗体チップの実装方法では、前記抵抗体チップを用い、前記半田ボールが形成された面に対して反対の面に、他のチップを搭載している。前記抵抗体チップを用い、前記素子搭載領域に、他のチップを搭載してもよい。又、前記抵抗体チップを用い、前記基板をバックグラインド(底面研磨)により薄膜化し、プリント基板を含む他の基板に埋め込んでもよい。

【発明の効果】

【0012】

請求項1、2、11、12に係る発明によれば、それぞれの層にそれぞれの抵抗値を有する抵抗体が複数存在するので、1つの抵抗体チップで複数の抵抗体を複数個得ることができる。更に、基板をバックグラインドにより薄型化すれば、抵抗体チップの全体の厚さを例えば数十μmという薄型に容易にできる。このような薄型の抵抗体チップを使用する場合、複数の抵抗体を一度に実装できるので、実装面積を削減でき、実装コストも削減できる。

【0013】

請求項3に係る発明によれば、各層の抵抗体の下に、各ストッパ絶縁膜が形成されているので、プラグを設けるためのコンタクトホールの形成時に、オーバエッチングを防止できる。

【0014】

請求項4に係る発明によれば、電極上にポストを設けたので、基板の中に抵抗体チップを埋め込んでそのポストにより電極の引き出しが行え、他の部品の表面実装の面積を増加できる。

【0015】

請求項5、6に係る発明によれば、再配線層によりパッドを再配置したので、パッドがチップ周辺部に偏在している状態から、均一な状態に再配置でき、パッド間の隣接距離が広くなる。これにより、はんだボール等を用いた実装が可能になる。

【0016】

請求項7に係る発明によれば、他の小型のチップ等をパッドの無い素子搭載領域に載せることができ、実装面積を削減できる。

【0017】

請求項8に係る発明によれば、例えば、抵抗体の長さを同一にすることにより、同一の抵抗値の抵抗体を多く集積できる。しかも、各層とも抵抗体の設計が同一であり、配置位置が異なるだけなので、設計が容易になる。

【0018】

請求項9、10に係る発明によれば、各層のポリシリコンへのイオンのドーピング量を調節することにより、異なった抵抗値に調節することができる。又、どの抵抗値の抵抗体を、どれくらいの数用意するかの設計の自由度も高くなる。

【0019】

請求項13に係る発明によれば、半田ボールにより、抵抗体チップを基板等に強固に接続できるので、その抵抗体チップ上に他のチップを実装でき、実装面積を有効に利用できる。

【0020】

請求項14に係る発明によれば、素子搭載領域に他のチップを搭載することにより、実装面積を有効に利用できる。

【0021】

請求項15に係る発明によれば、基板の薄膜化により抵抗体チップ全体を薄くでき、積層構造の薄型の部品内蔵プリント基板を容易に製造できる。

【発明を実施するための最良の形態】

【0022】

本発明を実施するための最良の形態の抵抗体チップでは、基板を有し、この基板上において、上下に離隔して複数層の薄膜抵抗体群が積層されている。各層の薄膜抵抗体群は、同一平面に平行に配列された複数の帯状の薄膜抵抗体により構成されている。各層毎の複数の薄膜抵抗体は、各層の層間絶縁膜によりそれぞれ被覆されている。横方向に離隔して配置された複数のプラグは、各層の複数の薄膜抵抗体にそれぞれ接続され、複数層の層間絶縁膜を上下に貫通して最上層の層間絶縁膜の表面に引き出されている。複数のプラグの上端には、電極がそれぞれ接合され、この複数の電極が、最上層の層間絶縁膜上において離隔して配置されている。最上層の層間絶縁膜は、複数の電極を露出させた状態でパッシベーション膜により被覆されている。

【実施例1】

【0023】

(構成)

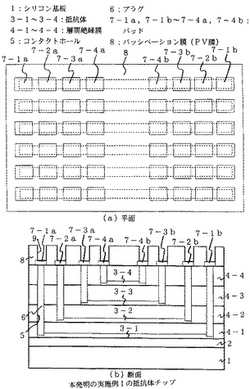

図1(a)、(b)は本発明の実施例1を示す抵抗体チップの概略の構成図であり、同図(a)は表面から見た平面図、及び同図(b)はその縦断面図である。

【0024】

この抵抗体チップは、全体の厚さが例えば100μm以下、好ましくは50μm以下の積層構造をしており、底面がバックグラインドにより薄膜化(例えば、100μm以下、好ましくは50μm以下に薄膜化)されるシリコン基板1を有している。シリコン基板1上には酸化膜(SiO2)からなる保護用のプロテクト絶縁膜2が被着され、このプロテクト絶縁膜2上に、複数層(例えば、4層)の薄膜抵抗体群が、酸化膜からなる層間絶縁膜4−1〜4−4を介して積層されている。

【0025】

各層の薄膜抵抗体群は、ボロン又は砒素等のイオンを注入したポリシリコン膜によりそれぞれ形成されている。ポリシリコン膜は、例えば、ボロンの注入によりp型になり、砒素の注入によりn型になる。1層目の薄膜抵抗体群は、複数の同一長さL1の帯状薄膜抵抗体3−1が同一平面上に平行に配列されて構成されている。同様に、2層目の薄膜抵抗体群は複数の同一長さL2の帯状薄膜抵抗体3−2により、3層目の薄膜抵抗体群は複数の同一長さL3の帯状薄膜抵抗体3−3により、4層目の薄膜抵抗体群は複数の同一長さL4の帯状薄膜抵抗体4−2により、それぞれ構成されている。各層の抵抗体3−1〜3−4の長さL1,L2,L3,L4は異なっており、例えば、L1>L2>L3>L4に設定されている。

【0026】

各層の抵抗体3−1〜3−4の一端と他端とに位置する垂直方向には、離隔して配置された複数のコンタクトホール5が形成され、これらのコンタクトホール5中にタングステン(W)等が埋設されて複数のプラグ6が形成されている。複数のプラグ6の上端面は、4層目の層間絶縁膜4−1の表面と同一面に位置しており、それらのプラグ6の上端面上に、アルミニュウムからなる複数の電極(例えば、パッド)7−1a,7−1b〜7−4a,7−4bが形成されている。

【0027】

パッド7−1aはプラグ6を介して1層目の抵抗体3−1の一端に接続され、それと離間したパッド7−1bはプラグ6を介して1層目の抵抗体3−1の他端に接続されている。同様に、パッド7−2aと7−2bは各プラグ6を介して2層目の抵抗体3−2の一端と他端に接続され、パッド7−3aと7−3bは各プラグ6を介して3層目の抵抗体3−3の一端と他端に接続され、パッド7−4aと7−4bは各プラグ6を介して4層目の抵抗体3−4の一端と他端に接続されている。4層目の層間絶縁膜4−4は、窒化膜(SiN)等の不活性化膜であるパッシベーション膜(以下「PV膜」という。)8により覆われ、このPV膜8における各パッド7−1a,7−1b〜7−4a,7−4b箇所のみに開口部9が形成されてその各パッド7−1a,7−1b〜7−4a,7−4bが露出している。

【0028】

(製造方法)

図1の抵抗体チップは、例えば、次のような工程により製造される。

先ず、シリコン基板1上に水蒸気を流しながら加熱し、酸化膜からなるプロテクト絶縁膜2を形成する。その上に、1層目のポリシリコン膜を形成し、ボロン又は砒素等のイオンを注入する。このときのイオンのドーズ量(注入量)は目標とする抵抗値により調節する。ポリシリコン膜上に、レジストをスピンコート(回転塗布)し、キュア(熱処理)した後に、ポリシリコン膜をフォトリソグラフィ技術により、レジストのパターニング後にエッチングし、直線の帯状からなる複数の薄膜抵抗体3−1を形成する。次に、複数の薄膜抵抗体3−1上に、例えば、プラズマTEOSを用いてCVD法(化学的気相成長法)により、酸化膜からなる1層目の層間絶縁膜4−1を形成する。その後、アニール(熱処理)を行う。

【0029】

1層目の層間絶縁膜4−1の上に、前記と同様2層目のにポリシリコン膜を形成し、ボロン等のイオンを注入し、フォトリソグラフィ技術を利用してパターニングし、2層目の複数の薄膜抵抗体3−2を形成する。1層目と異なっているのは、薄膜抵抗体3−2のパターンが短いことのみである。その後、前記と同様に、酸化膜からなる2層目の層間絶縁膜4−2を形成する。

【0030】

層間絶縁膜4−2の上に、前記と同様に、3層目の複数の薄膜抵抗体3−3を形成する。この場合も、2層目より抵抗体3−3の長さが短い以外は、全く同様の処理である。更にその上に、酸化膜からなる3層目の層間絶縁膜4−3を形成する。

【0031】

層間絶縁膜4−3の上に、前記と同様に、4層目の複数の薄膜抵抗体3−4を形成する。この場合も、3層目より抵抗体3−4の長さが短い以外は、全く同様の処理である。更にその上に、酸化膜からなる4層目の層間絶縁膜4−4を形成する。

【0032】

層間絶縁膜4−4の上にレジストを塗布し、キュアした後に、フォトリソグラフィ技術で、各層の抵抗体3−1〜3−4の両端の位置のみ、レジストを除去する。各層の抵抗体3−1〜3−4の両端に位置する層間絶縁膜4−1〜4−4箇所に、コンタクトホール5を酸化膜エッチャ(除去器)で開ける。コンタクトホール5内に、チタン等のバリア膜を形成し、CVD法により例えばタングステンのプラグ6を埋め込む。次に、CMP装置(化学的機械的研磨装置)により、層間絶縁膜4−4上のタングステンがなくなるまで研磨する。

【0033】

研磨した層間絶縁膜4−4の上に、スパッタリング法によりアルミニュウム膜を形成する。フォトリソグラフィ技術を用い、プラグ6上以外のアルミニュウム膜をエッチングし、パッド7−1a,7−1b〜7−4a,7−4bを形成する。このパッド7−1a,7−1b〜7−4a,7−4bの上に、窒化膜等のPV膜8を形成する。PV膜8上にレジストを塗布し、フォトリソグラフィ技術を用いて、パッド7−1a,7−1b〜7−4a,7−4b上のPV膜8をエッチングにより除去する。以上の工程により、図1の構造を有する抵抗アレイが形成される。

【0034】

このような抵抗体アレイにおいて、多層に形成した抵抗体3−1〜3−4により、複数の抵抗値を有するが抵抗体チップが複数個得られる。この抵抗体チップをバックグラインドして薄膜化し、ダイシング(切断)により個片化する。その後、実装時において、例えば、プリント基板等の上にダイスボンディング(固着)し、このダイスボンドされた抵抗体チップのそれぞれのパッド7−1a,7−1b〜7−4a,7−4bを必要な他の部品とワイヤボンディング(ワイヤ接続)等で結線することにより、所望の回路動作を行わせることができる。

【0035】

(効果)

本実施例1では、次の(a)、(b)のような効果がある

(a) それぞれの層にそれぞれの抵抗値を有する抵抗体3−1〜3−4が複数存在するので、1つの抵抗体チップで複数の抵抗体3−1〜3−4を複数個得ることができる。

【0036】

(b) 基板1をバックグラインドにより薄型化するので、抵抗体チップの全体の厚さを例えば数十μmという薄型に容易にできる。このような薄型の抵抗体チップを使用する場合、複数の抵抗体3−1〜3−4を一度に実装できるので、実装面積を削減でき、実装コストも削減できる。

【実施例2】

【0037】

(構成・製造方法)

図2は、本発明の実施例2を示す抵抗体チップの概略の縦断面図であり、実施例1を示す図1中の要素と共通の要素には共通の符号が付されている。

【0038】

本実施例2では、実施例1における各層の薄膜抵抗体用のポリシリコン膜を形成する前に、これらの下の各層間絶縁膜4−1〜4−4をCMPにより平坦化し、この上に、CVD法により窒化膜等の各ストッパ絶縁膜10−1〜10−4を形成した後に、各層の薄膜抵抗体用のポリシリコン膜を形成して各層の薄膜抵抗体群を形成するようにしている点のみが実施例1と異なる。その他の構成や製造方法は、実施例1とほぼ同様である。

【0039】

(効果)

本実施例2では、実施例1の効果の他に、次の(c)、(d)のような効果もある。

(c) 各層のポリシリコンの抵抗体3−1〜3−4の下が、CMPにより平坦化されているので、抵抗体3−1〜3−4の加工精度が向上する。

【0040】

(d) 各層のポリシリコンの抵抗体3−1〜3−4の下に、各ストッパ絶縁膜10−1〜10−4が形成されているので、コンタクトホール5の形成時にオーバエッチングが生じても、下層の絶縁膜2,4−1〜4−3がエッチングされるおそれがない。つまり、ストッパ絶縁膜10−1〜10−4により、オーバエッチングを防止できる。

【実施例3】

【0041】

(構成・製造方法)

図3は、本発明の実施例3を示す抵抗体チップの概略の縦断面図であり、実施例2を示す図2中の要素と共通の要素には共通の符号が付されている。

【0042】

本実施例3では、実施例2におけるアルミニュウムのパッド7−1a,7−1b〜7−4a,7−4bの上に、ニッケル・リン(NiP)膜11と銅(Cu)膜12を鍍金法により形成し、その後、シリコン基板1をバックグラインド法により50μm程度に薄膜化したものである。その他の構成や製造方法は、実施例2とほぼ同様である。

【0043】

(実装例)

図4は、図3の抵抗体チップ20の基板への埋め込み実装例を示す概略の縦断面図である。

【0044】

例えば、図3の抵抗体チップ20をプリント基板等の基板21へ埋め込む場合、基板21上に抵抗体チップ20を固着した後、この全面を樹脂絶縁膜22で覆う。炭酸ガスレーザ等により、パッド7−1a,7−1b〜7−4a,7−4b上の樹脂絶縁膜22にビアホール23を形成し、銅ポスト24を鍍金により形成する。パッド7−1a,7−1b〜7−4a,7−4bの上面に銅膜12が形成されているので、鍍金が容易で、銅ポスト24との導通が取れる。

【0045】

(効果)

本実施例3では、実施例1及び2の効果の他に、次の(e)のような効果もある。

(e) 基板21の中に抵抗体チップ20が埋め込まれているので、他の部品の表面実装の面積が増加する。なお、図4の実装例では、基板21上に抵抗体チップ20を搭載しているが、これに代えて、基板21に収納凹部を設け、この収納凹部内に抵抗体チップ20を埋設してもよい。これにより、全体の厚みを薄くすることができる。

【実施例4】

【0046】

(構成・製造方法)

5(a)、(b)は本発明の実施例4を示す抵抗体チップの概略の構成図であり、同図(a)は表面から見た平面図、及び同図(b)はその縦断面図である。この図5において、実施例1を示す図1中の要素と共通の要素には共通の符号が付されている。

【0047】

図1の実施例1では、各層毎に異なる長さのポリシリコンの薄膜抵抗体3−1〜3−4が設けられているが、本実施例4では、各層のポリシリコンの薄膜抵抗体3A−1〜3A−4の長さを同一にしている。その他の構成や製造方法は、実施例1とほぼ同様である。

【0048】

(効果)

本実施例4では、実施例1〜3の効果の他に、次の(f)、(g)のような効果もある。

(f) 各層のポリシリコンの薄膜抵抗体3A−1〜3A−4の長さが同一なので、同一の抵抗値の抵抗体3A−1〜3A−4を多く集積できる。又、各層のポリシリコンへのイオンのドーピング量を調節することにより、異なった抵抗値に調節することができる。

【0049】

(g) 各層とも抵抗体3A−1〜3A−4の設計が同一であり、配置位置が異なるだけなので、設計が容易になる。又、イオン打ち込み(インプラ)により抵抗値を調節するので、どの抵抗値の抵抗体を、どれくらいの数用意するかの設計の自由度が高くなる。

【実施例5】

【0050】

本実施例5では、実施例1、2又は4の抵抗体チップ20をパッケージングしたWCSP(ウエハレベル・チップ・サイズ・パッケージ)について説明する。

【0051】

WCSPは、アップしたウエハ上に、銅での再配線を行うものである。通常のICチップ(集積回路チップ)は、パッドがチップの周辺部に配設されている。これに対し、WCSPでは、再配線により、パッドを自由な位置に置けるので、実装の形態を選択する自由度が増える。

【0052】

図6(1)、(2−1)〜(2−3)、(3−1)〜(3−4)、(4−1)〜(4−6)は、本実施例5に用いるWCSPの種類を示す図である。

【0053】

図6(1)は、実施例1、2又は4で製造された抵抗体チップ20を含む処理済ウエハ30の概略の断面図である。この処理済ウエハ30は、抵抗体チップ20が多数形成されたウエハ本体30Aを有し、このウエハ本体30AがPV膜8により被覆され、多数のアルミニュウムのパッド7が露出している。

【0054】

図6(2−1)〜(2−3)は、処理済ウエハ30を用いたタイプ1のWCSP40−1を示す概略の製造工程図である。このWCSP40−1では、(2−1)の工程において、PV膜8上に銅の再配線41を形成し、その上を(2−2)の工程において、絶縁膜42−1で覆う。再配線41上における所定箇所の絶縁膜42−1を、エッチングにより除去して開口部を形成し、その開口部に(2−3)の工程において、半田ボール43を形成すれば、タイプ1のWCSP40−1が製造できる。

【0055】

図6(3−1)〜(3−4)は、処理済ウエハ30を用いたタイプ2のWCSP40−2を示す概略の製造工程図である。このWCSP40−2では、(3−1)の工程において、PV膜8上に絶縁膜42−1を形成した後、この絶縁膜42−1におけるパッド7箇所及び半田ボール形成予定箇所を、エッチングにより除去する。(3−2)の工程において、絶縁膜42−1上に銅の再配線41を形成する。(3−3)の工程において、再配線41を絶縁膜42−2で覆った後、この絶縁膜42−2におけるハンドボール形成予定箇所をエッチングにより除去して開口部を形成する。(3−4)の工程において、その開口部に半田ボール43を形成すれば、タイプ2のWCSP40−2が製造できる。

【0056】

図6(4−1)〜(4−6)は、処理済ウエハ30を用いたタイプ3のWCSP40−3を示す概略の製造工程図である。このWCSP40−3では、(4−1)の工程において、PV膜8上に絶縁膜42−1を形成した後、この絶縁膜42−1におけるパッド7箇所をエッチングにより除去する。(4−2)の工程において、絶縁膜42−1上に銅の再配線41を形成し、(4−3)の工程において、再配線41の所定箇所にメタルのパッド44を形成する。(4−4)の工程において、全面を絶縁膜42−2で覆った後、(4−5)の工程において、パッド44が露出するまで絶縁膜42−2をエッチングする。その後、(4−6)の工程において、露出したパッド44上に半田ボール43を形成すれば、タイプ3のWCSP40−3が製造できる。

【0057】

図7(1)〜(9)は、図6のWCSPの製造方法例を示す製造工程図である。

製造に先立ち、図6のタイプ1〜3のWCSP40−1〜40−3の中から、密着性、パッド数、チップ面積等を考慮して、製造すべきWCSP40−1〜40−3を選択する。以下、WCSP40−3の製造工程例を説明する。

【0058】

(1)の工程で用意したウエハプロセス(WP)済の処理済ウエハ30を用い、(2)の工程において、全面に絶縁膜42−1を形成する。(3)の工程において、絶縁膜42−1上に銅鍍金による再配線41を形成し、(4)の工程において、再配線41上の所定箇所に銅のパッド44を形成する。(5)の工程において、全面に樹脂の絶縁膜42−2により封止し、(6)の工程において、絶縁膜42−2をグラインド(研磨)してパッド44の上面を露出させる。(7)の工程において、パッド44上に半田印刷等で半田ボール43を形成する。(8)の工程において、電気的テスト等を行い、更に、ウエハ裏面をバックグラインドして薄膜化し、ダイシングにより個片化した後、(9)の工程において、製造されたWCSP40−3の外観検査を行い製造工程を終了する。

【0059】

図8は、図6のWCSP40−3によるパッド44の再配置の例を示す平面図である。

このWCSP40−3では、多数のパッド44を均一に配置することにより、1つのパッド44当たりの面積が増加する。そのため、パッド数が多い抵抗体チップ20でも、基板上に形成された配線等に、半田ボール43等による接続(実装)が可能になる。

【0060】

図9は、図8のWCSP40−3を基板に実装した例を示す図である。

この実装例では、基板45の表面に予め形成されている銅の配線46に、図8のWCSP40−3を載せ、半田ボール43により接続している。パッド数が多いWCSP40−3を半田ボール43により接続するので、強固に接続できる。そのため、WCSP40−3の上に、たのチップ等を搭載することが可能である。

【0061】

図10は、図9のWCSP40−3上への他のチップの積層例を示す図である。

この積層例では、基板45上に搭載されたWCSP40−3における半田ボール43とは反対の面に、他のチップ50を固着し、このチップ50のワイヤ51をワイヤボンディングにより他のチップ等と接続している。これにより、実装密度を向上できる。

【0062】

(効果)

本実施例5のWCSPでは、次の(A)、(B)のような効果がある。

(A) 図8に示すWCSP40−1により、図1等のパッド7−1a,7−1b〜7−4a,7−4bがチップ周辺部に偏在している状態から、WCSP上に均一な状態に再配置できるので、パッド44間の隣接距離が広くなる。それにより、半田ボール43等を用いた実装が可能になる。

【0063】

(B) 図9に示す半田ボール43により、WCSP40−3を基板45に強固に接続できるので、そのWCSP40−3の上に図10のような他のチップ50を実装できるので、実装面積を有効に利用できる。

【実施例6】

【0064】

(構成・製造方法)

図11は、本発明の実施例6を示すWCSP40−3によるパッド44の他の再配置例の図であり、実施例5を示す図8中の要素と共通の要素には共通の符号が付されている。

【0065】

抵抗体チップ20をWCSP40−3により再配線する場合、WCSP表面の中央に設けられた素子搭載領域の周辺部に多数のパッド44を偏在させる。更に、再配線後のパッド44の上面に金等を形成する。このようにすれば、パッド44のない中央の素子搭載領域に、他の小型のチップを搭載することが可能になる。

【0066】

図12は、図11のWCSP40−3上への他のチップの積層例を示す図である。

図11のWCSP40−3と同様の方法により、一回り小型のチップ51を作製すれば、このチップ51をWCSP40−3の素子搭載領域にダイスボンディングすることができる。上のチップ51から、下のWCSP40−3のパッド44が露出しているので、上のチップ51のパッド52と下のWCSP40−3のパッド44から、ワイヤボンディングにより必要なチップ等との接続が行える。本実施例6では、パッド44,52の上面に金等が形成されているので、良好なボンディング特性を得ることができる。

【0067】

(効果)

本実施例6では、WCSP40−3により、図1等の抵抗体チップ20のパッド7−1a,7−1b〜7−4a,7−4bを再配置したパッド44を、WCSP周辺部に集中したために、他の小型のチップ51をパッド44の無い素子搭載領域に載せることができる。このように、チップ51を積層することにより、実装面積の削減を行うことができる。

【実施例7】

【0068】

図13は、本発明の実施例7を示す抵抗体チップ20を用いた部品内蔵プリント基板の概略の断面図である。

【0069】

この図13では、実施例1〜4の薄型の抵抗体チップ20をプリント基板に内蔵させた部品内蔵プリント基板の実装例が示されている。この部品内蔵プリント基板の製造では、例えば、薄型の抵抗体チップ20の他に、予め薄型のインダクタチップ53、コンデンサチップ54、及びICチップ55等の薄型部品を製造しておく。そして、プリント基板本体60上に、例えば、コンデンサチップ54及びICチップ55等を固着し、アルミニュウム箔、銅箔等の1層目配線層61−1により結線し、これらを樹脂絶縁膜62により被覆して1層目を形成する。更に、1層目の上に、抵抗体ちっぷ20及びインダクタチップ53等を固着し、1層目配線層61−1にビアホール63を介して接続された2層目配線層61−2によって結線し、これらを樹脂絶縁膜62により被覆して2層目を形成する等すれば、図13のような積層構造の薄型の部品内蔵プリント基板を容易に製造できる。

【0070】

抵抗体チップ20等の他の実装例としては、例えば、プリント基板本体60内に図示しない収納凹部を形成し、この収納凹部内に抵抗体チップ20等を搭載して樹脂絶縁膜62等により被覆する等、種々の実装形態が可能である。

【実施例8】

【0071】

本発明は、上記実施例に限定されず、種々の変形や利用形態が可能である。この利用形態である実施例8としては、例えば、次の(1)、(2)のようなものがある。

【0072】

(1) 抵抗体チップ20では、シリコン基板1を用いたが、ガラス基板やアルミナ基板等を用いてもよい。

【0073】

(2) 薄膜抵抗体3−1〜3−4,3A−1〜3A−4は、直線の帯状で構成したが、曲線や角形等の他の帯状で構成してもよい。又、薄膜抵抗体3−1〜3−4,3A−1〜3A−4として、ボロンや砒素等のイオンを注入したポリシリコン膜を用いたが、酸化ルテニウムや、或いは、ニッケル(Ni)、コバルト(Co)、クロム(Cr)等の遷移元素とその合金等を用いてもよい。

【図面の簡単な説明】

【0074】

【図1】本発明の実施例1を示す抵抗体チップの概略の構成図である。

【図2】本発明の実施例2を示す抵抗体チップの概略の縦断面図である。

【図3】本発明の実施例3を示す抵抗体チップの概略の縦断面図である。

【図4】図3の抵抗体チップ20の基板への埋め込み実装例を示す概略の縦断面図である。

【図5】本発明の実施例4を示す抵抗体チップの概略の構成図である。

【図6】本発明の本実施例5に用いるWCSPの種類を示す図である。

【図7】図6のWCSPの製造方法例を示す製造工程図である。

【図8】図6のWCSP40−3によるパッド44の再配置の例を示す平面図である。

【図9】図8のWCSP40−3を基板に実装した例を示す図である。

【図10】図9のWCSP40−3上への他のチップの積層例を示す図である。

【図11】本発明の実施例6を示すWCSP40−3によるパッド44の他の再配置例の図である。

【図12】図11のWCSP40−3上への他のチップの積層例を示す図である。

【図13】本発明の実施例7を示す抵抗体チップ20を用いた部品内蔵プリント基板の概略の断面図である。

【符号の説明】

【0075】

1 シリコン基板

3−1〜3−4,3A−1〜3A−4 抵抗体

4−1〜4−4 層間絶縁膜

5 コンタクトホール

6 プラグ

7,7−1a,7−1b〜7−4a,7−4b,44,52 パッド

8 パッシベーション膜(PV膜)

10−1〜10−4 ストッパ絶縁膜

20 抵抗体チップ

21,45 基板

22,62 樹脂絶縁膜

24 ポスト

30 処理済ウエハ

30A ウエハ本体

40−1〜40−3 WCSP

41 再配線

42−1,42−2 絶縁膜

43 半田ボール

50,51 チップ

53 インダクタチップ

54 コンデンサチップ

55 ICチップ

60 プリント基板本体

【技術分野】

【0001】

本発明は、薄型受動部品の1つである薄型抵抗体部品、特に、薄膜抵抗体を高密度に積層した抵抗体チップとその実装方法に関するものである。

【背景技術】

【0002】

従来、薄型受動部品を積層する技術としては、例えば、次のような文献に記載されるものがあった。

【0003】

【非特許文献1】荻野等「集積受動素子の開発」、第17回エレクトロニクス実装学術講演大会集、2003年3月、13B−16、p.177−178

【非特許文献2】益・岡田「シリコン上の高周波受動素子技術」、応用物理、2004年9月、第73巻、第9号、p.1172−1178

【0004】

非特許文献1に示されているように、近年の電子機器の小型化は、急激であり、特に、携帯電話に代表されるモバイル機器は小型・軽量化の要求が高く、かつ、高機能化の要求も高まっている。携帯電話等の高周波(RF)送受信回路回路を含むデバイスは、コンデンサ、抵抗、インダクタ等の受動部品を多く搭載する。現在での実装面積におけるこの受動部品の割合は60%程度を占めており、小型化の大きな障害となっている。

【0005】

又、非特許文献2に示されているように、シリコン上に高周波用受動部品を搭載する開発も進んでいる。

【発明の開示】

【発明が解決しようとする課題】

【0006】

従来の受動部品は部品単体で、ある程度の大きさと厚みがあるために、表面実装する以外に実装方法がなく、従って実装面積を削減するためには部品の大きさを小さくするしか方法がなく、その方向で小型化が進められてきた。しかし、その小型化も限界に近くなってきており、物性的にも限界に近づいている。更に、部品の小型化に伴い、部品を実装するマウンタ(搭載機)が対応できなくなってきている。

【0007】

即ち、受動部品では1つの部品がある程度の大きさと厚みを有しているために、平面的に表面実装しなければならないので、今後の小型軽量、高機能化のための実装面積の減少と実装部品点数の増加に対応できない。部品の小型化は限界に達してきており、この限界を超えて小型化できても、小さすぎて実際にマウンタでハンドリング(把持)することが不可能になる。

【0008】

本発明は、上記のような限界をなくし、狭い実装面積に、多くの抵抗体を実装する薄型の抵抗体チップとその実装方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明の抵抗体チップは、基板と、同一平面に平行に配列された複数の帯状の薄膜抵抗体が、前記基板上において上下に離隔して複数層積層された薄膜抵抗体群と、前記各層毎の複数の薄膜抵抗体をそれぞれ被覆する複数層の層間絶縁膜と、横方向に離隔して配置されて前記各層の複数の薄膜抵抗体にそれぞれ接続された複数のプラグであって、前記複数層の層間絶縁膜を上下に貫通して前記最上層の層間絶縁膜の表面に引き出された前記複数のプラグと、前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極とを備えている。

【0010】

本発明の抵抗体チップにおいて、前記最上層の層間絶縁膜は、前記複数の電極を露出させた状態でパッシベーション膜により被覆してもよい。前記各層の複数の薄膜抵抗体における下面に、ストッパ絶縁膜をそれぞれ形成してもよい。前記各電極上には、導電性ポストを立設してもよい。又、前記複数の電極に接続され、前記パッシベーション膜上に配置された再配線層と、前記再配線層に接続され、所定の平面位置に配置された複数のパッドと、前記複数のパッドを露出させた状態で前記再配線層を被覆する絶縁膜とを設けてもよい。

【0011】

本発明の抵抗体チップの実装方法では、前記抵抗体チップを用い、前記半田ボールが形成された面に対して反対の面に、他のチップを搭載している。前記抵抗体チップを用い、前記素子搭載領域に、他のチップを搭載してもよい。又、前記抵抗体チップを用い、前記基板をバックグラインド(底面研磨)により薄膜化し、プリント基板を含む他の基板に埋め込んでもよい。

【発明の効果】

【0012】

請求項1、2、11、12に係る発明によれば、それぞれの層にそれぞれの抵抗値を有する抵抗体が複数存在するので、1つの抵抗体チップで複数の抵抗体を複数個得ることができる。更に、基板をバックグラインドにより薄型化すれば、抵抗体チップの全体の厚さを例えば数十μmという薄型に容易にできる。このような薄型の抵抗体チップを使用する場合、複数の抵抗体を一度に実装できるので、実装面積を削減でき、実装コストも削減できる。

【0013】

請求項3に係る発明によれば、各層の抵抗体の下に、各ストッパ絶縁膜が形成されているので、プラグを設けるためのコンタクトホールの形成時に、オーバエッチングを防止できる。

【0014】

請求項4に係る発明によれば、電極上にポストを設けたので、基板の中に抵抗体チップを埋め込んでそのポストにより電極の引き出しが行え、他の部品の表面実装の面積を増加できる。

【0015】

請求項5、6に係る発明によれば、再配線層によりパッドを再配置したので、パッドがチップ周辺部に偏在している状態から、均一な状態に再配置でき、パッド間の隣接距離が広くなる。これにより、はんだボール等を用いた実装が可能になる。

【0016】

請求項7に係る発明によれば、他の小型のチップ等をパッドの無い素子搭載領域に載せることができ、実装面積を削減できる。

【0017】

請求項8に係る発明によれば、例えば、抵抗体の長さを同一にすることにより、同一の抵抗値の抵抗体を多く集積できる。しかも、各層とも抵抗体の設計が同一であり、配置位置が異なるだけなので、設計が容易になる。

【0018】

請求項9、10に係る発明によれば、各層のポリシリコンへのイオンのドーピング量を調節することにより、異なった抵抗値に調節することができる。又、どの抵抗値の抵抗体を、どれくらいの数用意するかの設計の自由度も高くなる。

【0019】

請求項13に係る発明によれば、半田ボールにより、抵抗体チップを基板等に強固に接続できるので、その抵抗体チップ上に他のチップを実装でき、実装面積を有効に利用できる。

【0020】

請求項14に係る発明によれば、素子搭載領域に他のチップを搭載することにより、実装面積を有効に利用できる。

【0021】

請求項15に係る発明によれば、基板の薄膜化により抵抗体チップ全体を薄くでき、積層構造の薄型の部品内蔵プリント基板を容易に製造できる。

【発明を実施するための最良の形態】

【0022】

本発明を実施するための最良の形態の抵抗体チップでは、基板を有し、この基板上において、上下に離隔して複数層の薄膜抵抗体群が積層されている。各層の薄膜抵抗体群は、同一平面に平行に配列された複数の帯状の薄膜抵抗体により構成されている。各層毎の複数の薄膜抵抗体は、各層の層間絶縁膜によりそれぞれ被覆されている。横方向に離隔して配置された複数のプラグは、各層の複数の薄膜抵抗体にそれぞれ接続され、複数層の層間絶縁膜を上下に貫通して最上層の層間絶縁膜の表面に引き出されている。複数のプラグの上端には、電極がそれぞれ接合され、この複数の電極が、最上層の層間絶縁膜上において離隔して配置されている。最上層の層間絶縁膜は、複数の電極を露出させた状態でパッシベーション膜により被覆されている。

【実施例1】

【0023】

(構成)

図1(a)、(b)は本発明の実施例1を示す抵抗体チップの概略の構成図であり、同図(a)は表面から見た平面図、及び同図(b)はその縦断面図である。

【0024】

この抵抗体チップは、全体の厚さが例えば100μm以下、好ましくは50μm以下の積層構造をしており、底面がバックグラインドにより薄膜化(例えば、100μm以下、好ましくは50μm以下に薄膜化)されるシリコン基板1を有している。シリコン基板1上には酸化膜(SiO2)からなる保護用のプロテクト絶縁膜2が被着され、このプロテクト絶縁膜2上に、複数層(例えば、4層)の薄膜抵抗体群が、酸化膜からなる層間絶縁膜4−1〜4−4を介して積層されている。

【0025】

各層の薄膜抵抗体群は、ボロン又は砒素等のイオンを注入したポリシリコン膜によりそれぞれ形成されている。ポリシリコン膜は、例えば、ボロンの注入によりp型になり、砒素の注入によりn型になる。1層目の薄膜抵抗体群は、複数の同一長さL1の帯状薄膜抵抗体3−1が同一平面上に平行に配列されて構成されている。同様に、2層目の薄膜抵抗体群は複数の同一長さL2の帯状薄膜抵抗体3−2により、3層目の薄膜抵抗体群は複数の同一長さL3の帯状薄膜抵抗体3−3により、4層目の薄膜抵抗体群は複数の同一長さL4の帯状薄膜抵抗体4−2により、それぞれ構成されている。各層の抵抗体3−1〜3−4の長さL1,L2,L3,L4は異なっており、例えば、L1>L2>L3>L4に設定されている。

【0026】

各層の抵抗体3−1〜3−4の一端と他端とに位置する垂直方向には、離隔して配置された複数のコンタクトホール5が形成され、これらのコンタクトホール5中にタングステン(W)等が埋設されて複数のプラグ6が形成されている。複数のプラグ6の上端面は、4層目の層間絶縁膜4−1の表面と同一面に位置しており、それらのプラグ6の上端面上に、アルミニュウムからなる複数の電極(例えば、パッド)7−1a,7−1b〜7−4a,7−4bが形成されている。

【0027】

パッド7−1aはプラグ6を介して1層目の抵抗体3−1の一端に接続され、それと離間したパッド7−1bはプラグ6を介して1層目の抵抗体3−1の他端に接続されている。同様に、パッド7−2aと7−2bは各プラグ6を介して2層目の抵抗体3−2の一端と他端に接続され、パッド7−3aと7−3bは各プラグ6を介して3層目の抵抗体3−3の一端と他端に接続され、パッド7−4aと7−4bは各プラグ6を介して4層目の抵抗体3−4の一端と他端に接続されている。4層目の層間絶縁膜4−4は、窒化膜(SiN)等の不活性化膜であるパッシベーション膜(以下「PV膜」という。)8により覆われ、このPV膜8における各パッド7−1a,7−1b〜7−4a,7−4b箇所のみに開口部9が形成されてその各パッド7−1a,7−1b〜7−4a,7−4bが露出している。

【0028】

(製造方法)

図1の抵抗体チップは、例えば、次のような工程により製造される。

先ず、シリコン基板1上に水蒸気を流しながら加熱し、酸化膜からなるプロテクト絶縁膜2を形成する。その上に、1層目のポリシリコン膜を形成し、ボロン又は砒素等のイオンを注入する。このときのイオンのドーズ量(注入量)は目標とする抵抗値により調節する。ポリシリコン膜上に、レジストをスピンコート(回転塗布)し、キュア(熱処理)した後に、ポリシリコン膜をフォトリソグラフィ技術により、レジストのパターニング後にエッチングし、直線の帯状からなる複数の薄膜抵抗体3−1を形成する。次に、複数の薄膜抵抗体3−1上に、例えば、プラズマTEOSを用いてCVD法(化学的気相成長法)により、酸化膜からなる1層目の層間絶縁膜4−1を形成する。その後、アニール(熱処理)を行う。

【0029】

1層目の層間絶縁膜4−1の上に、前記と同様2層目のにポリシリコン膜を形成し、ボロン等のイオンを注入し、フォトリソグラフィ技術を利用してパターニングし、2層目の複数の薄膜抵抗体3−2を形成する。1層目と異なっているのは、薄膜抵抗体3−2のパターンが短いことのみである。その後、前記と同様に、酸化膜からなる2層目の層間絶縁膜4−2を形成する。

【0030】

層間絶縁膜4−2の上に、前記と同様に、3層目の複数の薄膜抵抗体3−3を形成する。この場合も、2層目より抵抗体3−3の長さが短い以外は、全く同様の処理である。更にその上に、酸化膜からなる3層目の層間絶縁膜4−3を形成する。

【0031】

層間絶縁膜4−3の上に、前記と同様に、4層目の複数の薄膜抵抗体3−4を形成する。この場合も、3層目より抵抗体3−4の長さが短い以外は、全く同様の処理である。更にその上に、酸化膜からなる4層目の層間絶縁膜4−4を形成する。

【0032】

層間絶縁膜4−4の上にレジストを塗布し、キュアした後に、フォトリソグラフィ技術で、各層の抵抗体3−1〜3−4の両端の位置のみ、レジストを除去する。各層の抵抗体3−1〜3−4の両端に位置する層間絶縁膜4−1〜4−4箇所に、コンタクトホール5を酸化膜エッチャ(除去器)で開ける。コンタクトホール5内に、チタン等のバリア膜を形成し、CVD法により例えばタングステンのプラグ6を埋め込む。次に、CMP装置(化学的機械的研磨装置)により、層間絶縁膜4−4上のタングステンがなくなるまで研磨する。

【0033】

研磨した層間絶縁膜4−4の上に、スパッタリング法によりアルミニュウム膜を形成する。フォトリソグラフィ技術を用い、プラグ6上以外のアルミニュウム膜をエッチングし、パッド7−1a,7−1b〜7−4a,7−4bを形成する。このパッド7−1a,7−1b〜7−4a,7−4bの上に、窒化膜等のPV膜8を形成する。PV膜8上にレジストを塗布し、フォトリソグラフィ技術を用いて、パッド7−1a,7−1b〜7−4a,7−4b上のPV膜8をエッチングにより除去する。以上の工程により、図1の構造を有する抵抗アレイが形成される。

【0034】

このような抵抗体アレイにおいて、多層に形成した抵抗体3−1〜3−4により、複数の抵抗値を有するが抵抗体チップが複数個得られる。この抵抗体チップをバックグラインドして薄膜化し、ダイシング(切断)により個片化する。その後、実装時において、例えば、プリント基板等の上にダイスボンディング(固着)し、このダイスボンドされた抵抗体チップのそれぞれのパッド7−1a,7−1b〜7−4a,7−4bを必要な他の部品とワイヤボンディング(ワイヤ接続)等で結線することにより、所望の回路動作を行わせることができる。

【0035】

(効果)

本実施例1では、次の(a)、(b)のような効果がある

(a) それぞれの層にそれぞれの抵抗値を有する抵抗体3−1〜3−4が複数存在するので、1つの抵抗体チップで複数の抵抗体3−1〜3−4を複数個得ることができる。

【0036】

(b) 基板1をバックグラインドにより薄型化するので、抵抗体チップの全体の厚さを例えば数十μmという薄型に容易にできる。このような薄型の抵抗体チップを使用する場合、複数の抵抗体3−1〜3−4を一度に実装できるので、実装面積を削減でき、実装コストも削減できる。

【実施例2】

【0037】

(構成・製造方法)

図2は、本発明の実施例2を示す抵抗体チップの概略の縦断面図であり、実施例1を示す図1中の要素と共通の要素には共通の符号が付されている。

【0038】

本実施例2では、実施例1における各層の薄膜抵抗体用のポリシリコン膜を形成する前に、これらの下の各層間絶縁膜4−1〜4−4をCMPにより平坦化し、この上に、CVD法により窒化膜等の各ストッパ絶縁膜10−1〜10−4を形成した後に、各層の薄膜抵抗体用のポリシリコン膜を形成して各層の薄膜抵抗体群を形成するようにしている点のみが実施例1と異なる。その他の構成や製造方法は、実施例1とほぼ同様である。

【0039】

(効果)

本実施例2では、実施例1の効果の他に、次の(c)、(d)のような効果もある。

(c) 各層のポリシリコンの抵抗体3−1〜3−4の下が、CMPにより平坦化されているので、抵抗体3−1〜3−4の加工精度が向上する。

【0040】

(d) 各層のポリシリコンの抵抗体3−1〜3−4の下に、各ストッパ絶縁膜10−1〜10−4が形成されているので、コンタクトホール5の形成時にオーバエッチングが生じても、下層の絶縁膜2,4−1〜4−3がエッチングされるおそれがない。つまり、ストッパ絶縁膜10−1〜10−4により、オーバエッチングを防止できる。

【実施例3】

【0041】

(構成・製造方法)

図3は、本発明の実施例3を示す抵抗体チップの概略の縦断面図であり、実施例2を示す図2中の要素と共通の要素には共通の符号が付されている。

【0042】

本実施例3では、実施例2におけるアルミニュウムのパッド7−1a,7−1b〜7−4a,7−4bの上に、ニッケル・リン(NiP)膜11と銅(Cu)膜12を鍍金法により形成し、その後、シリコン基板1をバックグラインド法により50μm程度に薄膜化したものである。その他の構成や製造方法は、実施例2とほぼ同様である。

【0043】

(実装例)

図4は、図3の抵抗体チップ20の基板への埋め込み実装例を示す概略の縦断面図である。

【0044】

例えば、図3の抵抗体チップ20をプリント基板等の基板21へ埋め込む場合、基板21上に抵抗体チップ20を固着した後、この全面を樹脂絶縁膜22で覆う。炭酸ガスレーザ等により、パッド7−1a,7−1b〜7−4a,7−4b上の樹脂絶縁膜22にビアホール23を形成し、銅ポスト24を鍍金により形成する。パッド7−1a,7−1b〜7−4a,7−4bの上面に銅膜12が形成されているので、鍍金が容易で、銅ポスト24との導通が取れる。

【0045】

(効果)

本実施例3では、実施例1及び2の効果の他に、次の(e)のような効果もある。

(e) 基板21の中に抵抗体チップ20が埋め込まれているので、他の部品の表面実装の面積が増加する。なお、図4の実装例では、基板21上に抵抗体チップ20を搭載しているが、これに代えて、基板21に収納凹部を設け、この収納凹部内に抵抗体チップ20を埋設してもよい。これにより、全体の厚みを薄くすることができる。

【実施例4】

【0046】

(構成・製造方法)

5(a)、(b)は本発明の実施例4を示す抵抗体チップの概略の構成図であり、同図(a)は表面から見た平面図、及び同図(b)はその縦断面図である。この図5において、実施例1を示す図1中の要素と共通の要素には共通の符号が付されている。

【0047】

図1の実施例1では、各層毎に異なる長さのポリシリコンの薄膜抵抗体3−1〜3−4が設けられているが、本実施例4では、各層のポリシリコンの薄膜抵抗体3A−1〜3A−4の長さを同一にしている。その他の構成や製造方法は、実施例1とほぼ同様である。

【0048】

(効果)

本実施例4では、実施例1〜3の効果の他に、次の(f)、(g)のような効果もある。

(f) 各層のポリシリコンの薄膜抵抗体3A−1〜3A−4の長さが同一なので、同一の抵抗値の抵抗体3A−1〜3A−4を多く集積できる。又、各層のポリシリコンへのイオンのドーピング量を調節することにより、異なった抵抗値に調節することができる。

【0049】

(g) 各層とも抵抗体3A−1〜3A−4の設計が同一であり、配置位置が異なるだけなので、設計が容易になる。又、イオン打ち込み(インプラ)により抵抗値を調節するので、どの抵抗値の抵抗体を、どれくらいの数用意するかの設計の自由度が高くなる。

【実施例5】

【0050】

本実施例5では、実施例1、2又は4の抵抗体チップ20をパッケージングしたWCSP(ウエハレベル・チップ・サイズ・パッケージ)について説明する。

【0051】

WCSPは、アップしたウエハ上に、銅での再配線を行うものである。通常のICチップ(集積回路チップ)は、パッドがチップの周辺部に配設されている。これに対し、WCSPでは、再配線により、パッドを自由な位置に置けるので、実装の形態を選択する自由度が増える。

【0052】

図6(1)、(2−1)〜(2−3)、(3−1)〜(3−4)、(4−1)〜(4−6)は、本実施例5に用いるWCSPの種類を示す図である。

【0053】

図6(1)は、実施例1、2又は4で製造された抵抗体チップ20を含む処理済ウエハ30の概略の断面図である。この処理済ウエハ30は、抵抗体チップ20が多数形成されたウエハ本体30Aを有し、このウエハ本体30AがPV膜8により被覆され、多数のアルミニュウムのパッド7が露出している。

【0054】

図6(2−1)〜(2−3)は、処理済ウエハ30を用いたタイプ1のWCSP40−1を示す概略の製造工程図である。このWCSP40−1では、(2−1)の工程において、PV膜8上に銅の再配線41を形成し、その上を(2−2)の工程において、絶縁膜42−1で覆う。再配線41上における所定箇所の絶縁膜42−1を、エッチングにより除去して開口部を形成し、その開口部に(2−3)の工程において、半田ボール43を形成すれば、タイプ1のWCSP40−1が製造できる。

【0055】

図6(3−1)〜(3−4)は、処理済ウエハ30を用いたタイプ2のWCSP40−2を示す概略の製造工程図である。このWCSP40−2では、(3−1)の工程において、PV膜8上に絶縁膜42−1を形成した後、この絶縁膜42−1におけるパッド7箇所及び半田ボール形成予定箇所を、エッチングにより除去する。(3−2)の工程において、絶縁膜42−1上に銅の再配線41を形成する。(3−3)の工程において、再配線41を絶縁膜42−2で覆った後、この絶縁膜42−2におけるハンドボール形成予定箇所をエッチングにより除去して開口部を形成する。(3−4)の工程において、その開口部に半田ボール43を形成すれば、タイプ2のWCSP40−2が製造できる。

【0056】

図6(4−1)〜(4−6)は、処理済ウエハ30を用いたタイプ3のWCSP40−3を示す概略の製造工程図である。このWCSP40−3では、(4−1)の工程において、PV膜8上に絶縁膜42−1を形成した後、この絶縁膜42−1におけるパッド7箇所をエッチングにより除去する。(4−2)の工程において、絶縁膜42−1上に銅の再配線41を形成し、(4−3)の工程において、再配線41の所定箇所にメタルのパッド44を形成する。(4−4)の工程において、全面を絶縁膜42−2で覆った後、(4−5)の工程において、パッド44が露出するまで絶縁膜42−2をエッチングする。その後、(4−6)の工程において、露出したパッド44上に半田ボール43を形成すれば、タイプ3のWCSP40−3が製造できる。

【0057】

図7(1)〜(9)は、図6のWCSPの製造方法例を示す製造工程図である。

製造に先立ち、図6のタイプ1〜3のWCSP40−1〜40−3の中から、密着性、パッド数、チップ面積等を考慮して、製造すべきWCSP40−1〜40−3を選択する。以下、WCSP40−3の製造工程例を説明する。

【0058】

(1)の工程で用意したウエハプロセス(WP)済の処理済ウエハ30を用い、(2)の工程において、全面に絶縁膜42−1を形成する。(3)の工程において、絶縁膜42−1上に銅鍍金による再配線41を形成し、(4)の工程において、再配線41上の所定箇所に銅のパッド44を形成する。(5)の工程において、全面に樹脂の絶縁膜42−2により封止し、(6)の工程において、絶縁膜42−2をグラインド(研磨)してパッド44の上面を露出させる。(7)の工程において、パッド44上に半田印刷等で半田ボール43を形成する。(8)の工程において、電気的テスト等を行い、更に、ウエハ裏面をバックグラインドして薄膜化し、ダイシングにより個片化した後、(9)の工程において、製造されたWCSP40−3の外観検査を行い製造工程を終了する。

【0059】

図8は、図6のWCSP40−3によるパッド44の再配置の例を示す平面図である。

このWCSP40−3では、多数のパッド44を均一に配置することにより、1つのパッド44当たりの面積が増加する。そのため、パッド数が多い抵抗体チップ20でも、基板上に形成された配線等に、半田ボール43等による接続(実装)が可能になる。

【0060】

図9は、図8のWCSP40−3を基板に実装した例を示す図である。

この実装例では、基板45の表面に予め形成されている銅の配線46に、図8のWCSP40−3を載せ、半田ボール43により接続している。パッド数が多いWCSP40−3を半田ボール43により接続するので、強固に接続できる。そのため、WCSP40−3の上に、たのチップ等を搭載することが可能である。

【0061】

図10は、図9のWCSP40−3上への他のチップの積層例を示す図である。

この積層例では、基板45上に搭載されたWCSP40−3における半田ボール43とは反対の面に、他のチップ50を固着し、このチップ50のワイヤ51をワイヤボンディングにより他のチップ等と接続している。これにより、実装密度を向上できる。

【0062】

(効果)

本実施例5のWCSPでは、次の(A)、(B)のような効果がある。

(A) 図8に示すWCSP40−1により、図1等のパッド7−1a,7−1b〜7−4a,7−4bがチップ周辺部に偏在している状態から、WCSP上に均一な状態に再配置できるので、パッド44間の隣接距離が広くなる。それにより、半田ボール43等を用いた実装が可能になる。

【0063】

(B) 図9に示す半田ボール43により、WCSP40−3を基板45に強固に接続できるので、そのWCSP40−3の上に図10のような他のチップ50を実装できるので、実装面積を有効に利用できる。

【実施例6】

【0064】

(構成・製造方法)

図11は、本発明の実施例6を示すWCSP40−3によるパッド44の他の再配置例の図であり、実施例5を示す図8中の要素と共通の要素には共通の符号が付されている。

【0065】

抵抗体チップ20をWCSP40−3により再配線する場合、WCSP表面の中央に設けられた素子搭載領域の周辺部に多数のパッド44を偏在させる。更に、再配線後のパッド44の上面に金等を形成する。このようにすれば、パッド44のない中央の素子搭載領域に、他の小型のチップを搭載することが可能になる。

【0066】

図12は、図11のWCSP40−3上への他のチップの積層例を示す図である。

図11のWCSP40−3と同様の方法により、一回り小型のチップ51を作製すれば、このチップ51をWCSP40−3の素子搭載領域にダイスボンディングすることができる。上のチップ51から、下のWCSP40−3のパッド44が露出しているので、上のチップ51のパッド52と下のWCSP40−3のパッド44から、ワイヤボンディングにより必要なチップ等との接続が行える。本実施例6では、パッド44,52の上面に金等が形成されているので、良好なボンディング特性を得ることができる。

【0067】

(効果)

本実施例6では、WCSP40−3により、図1等の抵抗体チップ20のパッド7−1a,7−1b〜7−4a,7−4bを再配置したパッド44を、WCSP周辺部に集中したために、他の小型のチップ51をパッド44の無い素子搭載領域に載せることができる。このように、チップ51を積層することにより、実装面積の削減を行うことができる。

【実施例7】

【0068】

図13は、本発明の実施例7を示す抵抗体チップ20を用いた部品内蔵プリント基板の概略の断面図である。

【0069】

この図13では、実施例1〜4の薄型の抵抗体チップ20をプリント基板に内蔵させた部品内蔵プリント基板の実装例が示されている。この部品内蔵プリント基板の製造では、例えば、薄型の抵抗体チップ20の他に、予め薄型のインダクタチップ53、コンデンサチップ54、及びICチップ55等の薄型部品を製造しておく。そして、プリント基板本体60上に、例えば、コンデンサチップ54及びICチップ55等を固着し、アルミニュウム箔、銅箔等の1層目配線層61−1により結線し、これらを樹脂絶縁膜62により被覆して1層目を形成する。更に、1層目の上に、抵抗体ちっぷ20及びインダクタチップ53等を固着し、1層目配線層61−1にビアホール63を介して接続された2層目配線層61−2によって結線し、これらを樹脂絶縁膜62により被覆して2層目を形成する等すれば、図13のような積層構造の薄型の部品内蔵プリント基板を容易に製造できる。

【0070】

抵抗体チップ20等の他の実装例としては、例えば、プリント基板本体60内に図示しない収納凹部を形成し、この収納凹部内に抵抗体チップ20等を搭載して樹脂絶縁膜62等により被覆する等、種々の実装形態が可能である。

【実施例8】

【0071】

本発明は、上記実施例に限定されず、種々の変形や利用形態が可能である。この利用形態である実施例8としては、例えば、次の(1)、(2)のようなものがある。

【0072】

(1) 抵抗体チップ20では、シリコン基板1を用いたが、ガラス基板やアルミナ基板等を用いてもよい。

【0073】

(2) 薄膜抵抗体3−1〜3−4,3A−1〜3A−4は、直線の帯状で構成したが、曲線や角形等の他の帯状で構成してもよい。又、薄膜抵抗体3−1〜3−4,3A−1〜3A−4として、ボロンや砒素等のイオンを注入したポリシリコン膜を用いたが、酸化ルテニウムや、或いは、ニッケル(Ni)、コバルト(Co)、クロム(Cr)等の遷移元素とその合金等を用いてもよい。

【図面の簡単な説明】

【0074】

【図1】本発明の実施例1を示す抵抗体チップの概略の構成図である。

【図2】本発明の実施例2を示す抵抗体チップの概略の縦断面図である。

【図3】本発明の実施例3を示す抵抗体チップの概略の縦断面図である。

【図4】図3の抵抗体チップ20の基板への埋め込み実装例を示す概略の縦断面図である。

【図5】本発明の実施例4を示す抵抗体チップの概略の構成図である。

【図6】本発明の本実施例5に用いるWCSPの種類を示す図である。

【図7】図6のWCSPの製造方法例を示す製造工程図である。

【図8】図6のWCSP40−3によるパッド44の再配置の例を示す平面図である。

【図9】図8のWCSP40−3を基板に実装した例を示す図である。

【図10】図9のWCSP40−3上への他のチップの積層例を示す図である。

【図11】本発明の実施例6を示すWCSP40−3によるパッド44の他の再配置例の図である。

【図12】図11のWCSP40−3上への他のチップの積層例を示す図である。

【図13】本発明の実施例7を示す抵抗体チップ20を用いた部品内蔵プリント基板の概略の断面図である。

【符号の説明】

【0075】

1 シリコン基板

3−1〜3−4,3A−1〜3A−4 抵抗体

4−1〜4−4 層間絶縁膜

5 コンタクトホール

6 プラグ

7,7−1a,7−1b〜7−4a,7−4b,44,52 パッド

8 パッシベーション膜(PV膜)

10−1〜10−4 ストッパ絶縁膜

20 抵抗体チップ

21,45 基板

22,62 樹脂絶縁膜

24 ポスト

30 処理済ウエハ

30A ウエハ本体

40−1〜40−3 WCSP

41 再配線

42−1,42−2 絶縁膜

43 半田ボール

50,51 チップ

53 インダクタチップ

54 コンデンサチップ

55 ICチップ

60 プリント基板本体

【特許請求の範囲】

【請求項1】

基板と、

同一平面に平行に配列された複数の帯状の薄膜抵抗体が、前記基板上において上下に離隔して複数層積層された薄膜抵抗体群と、

前記各層毎の複数の薄膜抵抗体をそれぞれ被覆する複数層の層間絶縁膜と、

横方向に離隔して配置されて前記各層の複数の薄膜抵抗体にそれぞれ接続された複数のプラグであって、前記複数層の層間絶縁膜を上下に貫通して前記最上層の層間絶縁膜の表面に引き出された前記複数のプラグと、

前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極と、

を備えたことを特徴とする抵抗体チップ。

【請求項2】

請求項1記載の抵抗体チップにおいて、

前記最上層の層間絶縁膜は、前記複数の電極を露出させた状態でパッシベーション膜により被覆されていることを特徴とする抵抗体チップ。

【請求項3】

請求項2記載の抵抗体チップにおいて、

前記各層の複数の薄膜抵抗体における下面に、ストッパ絶縁膜がそれぞれ形成されていることを特徴とする抵抗体チップ。

【請求項4】

請求項2又は3記載の抵抗体チップにおいて、

前記各電極上には、導電性ポストが立設されていることを特徴とする抵抗体チップ。

【請求項5】

請求項2又は3記載の抵抗体チップにおいて、

前記複数の電極に接続され、前記パッシベーション膜上に配置された再配線層と、

前記再配線層に接続され、所定の平面位置に配置された複数のパッドと、

前記複数のパッドを露出させた状態で前記再配線層を被覆する絶縁膜と、

を有することを特徴とする抵抗体チップ。

【請求項6】

請求項5記載の抵抗体チップにおいて、

前記複数のパッドは、前記複数の電極の配置間隔よりも大きな間隔で配置され、前記各パッド上に半田ボールが形成されていることを特徴とする抵抗体チップ。

【請求項7】

請求項5記載の抵抗体チップにおいて、

前記複数のパッドは、表面に設けられた素子搭載領域の周辺部に配置されていることを特徴とする抵抗体チップ。

【請求項8】

請求項1〜7のいずれか1項に記載の抵抗体チップにおいて、

前記薄膜抵抗体は、長さにより抵抗値が調節されていることを特徴とする抵抗体チップ。

【請求項9】

請求項1〜7のいずれか1項に記載の抵抗体チップにおいて、

前記薄膜抵抗体は、イオンが注入されたポリシリコンにより形成されていることを特徴とする抵抗体チップ。

【請求項10】

請求項9記載の抵抗体チップにおいて、

前記薄膜抵抗体は、前記イオンの注入量により抵抗値が調節されていることを特徴とする抵抗体チップ。

【請求項11】

請求項1〜7のいずれか1項に記載の抵抗体チップにおいて、

前記薄膜抵抗体は、酸化ルテニウムと、ニッケル、コバルト又はクロムを含む遷移元素とその合金と、のいずれか1つにより形成されていることを特徴とする抵抗体チップ。

【請求項12】

請求項1〜11のいずれか1項に記載の抵抗体チップにおいて、

前記基板は、シリコン基板、ガラス基板、又は、アルミナ基板のいずれか1つにより構成されていることを特徴とする抵抗体チップ。

【請求項13】

請求項6記載の抵抗体チップを用い、前記半田ボールが形成された面に対して反対の面に、他のチップを搭載することを特徴とする抵抗体チップの実装方法。

【請求項14】

請求項7記載の抵抗体チップを用い、前記素子搭載領域に、他のチップを搭載することを特徴とする抵抗体チップの実装方法。

【請求項15】

請求項1〜14のいずれか1項に記載の抵抗体チップを用い、

前記基板をバックグラインドにより薄膜化し、プリント基板を含む他の基板に埋め込むことを特徴とする抵抗体チップの実装方法。

【請求項1】

基板と、

同一平面に平行に配列された複数の帯状の薄膜抵抗体が、前記基板上において上下に離隔して複数層積層された薄膜抵抗体群と、

前記各層毎の複数の薄膜抵抗体をそれぞれ被覆する複数層の層間絶縁膜と、

横方向に離隔して配置されて前記各層の複数の薄膜抵抗体にそれぞれ接続された複数のプラグであって、前記複数層の層間絶縁膜を上下に貫通して前記最上層の層間絶縁膜の表面に引き出された前記複数のプラグと、

前記複数のプラグの上端にそれぞれ接合され、前記最上層の層間絶縁膜上において離隔して配置された複数の電極と、

を備えたことを特徴とする抵抗体チップ。

【請求項2】

請求項1記載の抵抗体チップにおいて、

前記最上層の層間絶縁膜は、前記複数の電極を露出させた状態でパッシベーション膜により被覆されていることを特徴とする抵抗体チップ。

【請求項3】

請求項2記載の抵抗体チップにおいて、

前記各層の複数の薄膜抵抗体における下面に、ストッパ絶縁膜がそれぞれ形成されていることを特徴とする抵抗体チップ。

【請求項4】

請求項2又は3記載の抵抗体チップにおいて、

前記各電極上には、導電性ポストが立設されていることを特徴とする抵抗体チップ。

【請求項5】

請求項2又は3記載の抵抗体チップにおいて、

前記複数の電極に接続され、前記パッシベーション膜上に配置された再配線層と、

前記再配線層に接続され、所定の平面位置に配置された複数のパッドと、

前記複数のパッドを露出させた状態で前記再配線層を被覆する絶縁膜と、

を有することを特徴とする抵抗体チップ。

【請求項6】

請求項5記載の抵抗体チップにおいて、

前記複数のパッドは、前記複数の電極の配置間隔よりも大きな間隔で配置され、前記各パッド上に半田ボールが形成されていることを特徴とする抵抗体チップ。

【請求項7】

請求項5記載の抵抗体チップにおいて、

前記複数のパッドは、表面に設けられた素子搭載領域の周辺部に配置されていることを特徴とする抵抗体チップ。

【請求項8】

請求項1〜7のいずれか1項に記載の抵抗体チップにおいて、

前記薄膜抵抗体は、長さにより抵抗値が調節されていることを特徴とする抵抗体チップ。

【請求項9】

請求項1〜7のいずれか1項に記載の抵抗体チップにおいて、

前記薄膜抵抗体は、イオンが注入されたポリシリコンにより形成されていることを特徴とする抵抗体チップ。

【請求項10】

請求項9記載の抵抗体チップにおいて、

前記薄膜抵抗体は、前記イオンの注入量により抵抗値が調節されていることを特徴とする抵抗体チップ。

【請求項11】

請求項1〜7のいずれか1項に記載の抵抗体チップにおいて、

前記薄膜抵抗体は、酸化ルテニウムと、ニッケル、コバルト又はクロムを含む遷移元素とその合金と、のいずれか1つにより形成されていることを特徴とする抵抗体チップ。

【請求項12】

請求項1〜11のいずれか1項に記載の抵抗体チップにおいて、

前記基板は、シリコン基板、ガラス基板、又は、アルミナ基板のいずれか1つにより構成されていることを特徴とする抵抗体チップ。

【請求項13】

請求項6記載の抵抗体チップを用い、前記半田ボールが形成された面に対して反対の面に、他のチップを搭載することを特徴とする抵抗体チップの実装方法。

【請求項14】

請求項7記載の抵抗体チップを用い、前記素子搭載領域に、他のチップを搭載することを特徴とする抵抗体チップの実装方法。

【請求項15】

請求項1〜14のいずれか1項に記載の抵抗体チップを用い、

前記基板をバックグラインドにより薄膜化し、プリント基板を含む他の基板に埋め込むことを特徴とする抵抗体チップの実装方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2006−186038(P2006−186038A)

【公開日】平成18年7月13日(2006.7.13)

【国際特許分類】

【出願番号】特願2004−376661(P2004−376661)

【出願日】平成16年12月27日(2004.12.27)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【出願人】(596091004)株式会社マルチ (18)

【出願人】(899000068)学校法人早稲田大学 (602)

【出願人】(502273096)株式会社関東学院大学表面工学研究所 (52)

【Fターム(参考)】

【公開日】平成18年7月13日(2006.7.13)

【国際特許分類】

【出願日】平成16年12月27日(2004.12.27)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【出願人】(596091004)株式会社マルチ (18)

【出願人】(899000068)学校法人早稲田大学 (602)

【出願人】(502273096)株式会社関東学院大学表面工学研究所 (52)

【Fターム(参考)】

[ Back to top ]