抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の製造方法

【課題】安定したスイッチング動作を低コストで実行する抵抗変化型不揮発性記憶装置を提供する。

【解決手段】抵抗変化型不揮発性記憶装置は、第1配線3と、第1配線3上に形成された層間絶縁層53と、層間絶縁膜53上に形成された第2配線6と、第1配線3と第2配線6との間に形成された抵抗変化型素子11とを具備する。層間絶縁層53は、第1配線3と第2配線6とに挟まれるように形成され、第1配線3の幅以下の幅を有するホール9を備える。抵抗変化型素子11は、第1配線3と接して、ホール9の底部に形成された下部電極13と、下部電極13上に形成された抵抗変化層12と、抵抗変化層12上に形成された上部電極11とを備える。下部電極13、抵抗変化層12及び上部電極11は、ホール9の内部に形成される。第1配線3は銅を含み、下部電極13、13aはルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

【解決手段】抵抗変化型不揮発性記憶装置は、第1配線3と、第1配線3上に形成された層間絶縁層53と、層間絶縁膜53上に形成された第2配線6と、第1配線3と第2配線6との間に形成された抵抗変化型素子11とを具備する。層間絶縁層53は、第1配線3と第2配線6とに挟まれるように形成され、第1配線3の幅以下の幅を有するホール9を備える。抵抗変化型素子11は、第1配線3と接して、ホール9の底部に形成された下部電極13と、下部電極13上に形成された抵抗変化層12と、抵抗変化層12上に形成された上部電極11とを備える。下部電極13、抵抗変化層12及び上部電極11は、ホール9の内部に形成される。第1配線3は銅を含み、下部電極13、13aはルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の製造方法に関する。

【背景技術】

【0002】

不揮発性メモリの分野においては、フラッシュメモリ、強誘電体メモリ(Ferroelectric Random Access Memory;FeRAM)、磁気メモリ(Magnetic Random Access Memory;MRAM)、OUM(Ovonic Unified Memory)等の研究が盛んである。しかし、最近、これらの従来の不揮発性メモリと異なる不揮発性メモリとして、抵抗変化型メモリ(Resistance Random Access Memory;ReRAM)が提案されている。例えば、非特許文献1の抵抗変化型メモリは、電圧パルスの印加でメモリセルの抵抗変化層の抵抗値を設定することにより情報を書き込むことができる。加えて、抵抗値を非破壊で測定することにより情報を読み出すことができる。この抵抗変化型メモリは、メモリセルの面積が小さく、多値化が可能である。そのため、既存の不揮発性メモリをしのぐ可能性を有している。非特許文献1では、抵抗変化層としてPCMO(Pr0.7Ca0.3MnO3)及びYBCO(YBa2Cu3Oy)が用いられている。抵抗変化型メモリに関しては他の提案もなされている。例えば、非特許文献2の抵抗変化型メモリでは、抵抗変化層として約50nmの多結晶NiOx(x=1〜1.5)が用いられている。上部電極に正の電圧を印加することで、低抵抗状態もしくは高抵抗状態に変化する。また、例えば、非特許文献3の抵抗変化型メモリでは、抵抗変化層として80nmの微結晶TiO2が用いられている。

【0003】

一般的に、抵抗変化型メモリの1つのメモリセルは、1つの制御用トランジスタと1つの抵抗変化素子を備えている。そのようなメモリセルを有する抵抗変化型メモリは、1T1R型ともいわれている。図1は、従来の1T1R型の抵抗変化型メモリの構成を示す平面図である。1T1R型の抵抗変化型メモリ190は、複数のワード線(又はゲート)122と、複数のビット線(又は第2配線)106と、複数の共通線108と、複数のメモリセルMCとを具備している。複数のワード線(又はゲート)122は、Y方向に延在している。ビット線(又は第2配線)106は、X方向に延在している。共通線108は、Y方向に延在しいている。複数のメモリセルMCは、複数のワード線122と複数のビット線106との交点の各々に対応して設けられている。

【0004】

図2は、図1におけるa−a’断面の構成を示す断面図である。メモリセルMCの1個分の構成を示している。メモリセルMCは、制御トランジスタ102と、抵抗変化素子101とを備えている。半導体基板170上に素子分離領域171及び制御トランジスタ102が形成されている。制御トランジスタ102は、ゲート絶縁膜123、ゲート122(ワード線)、ドレイン121、ソース124、サイドウォール125を備えている。ドレイン121、ソース124にはコンタクト104が接続されている。制御トランジスタ102及びコンタクト104は第1層間絶縁膜151及び第1キャップ絶縁膜161に覆われている。ドレイン121側のコンタクト104は、第1キャップ絶縁膜161の開口部を介して、バリアメタル132と銅(Cu)131からなる第1配線103に接続されている。第1配線103は、第2層間絶縁膜152及び第2キャップ絶縁膜162に覆われている。抵抗変化型メモリの抵抗変化素子101は、第2キャップ絶縁膜162の開口部を介して、第1配線103に接続されている。抵抗変化素子101は、第1配線103と接続される下部電極113、下部電極113上の抵抗変化層112及び抵抗変化層112上の上部電極111からなるMIM(Metal/Insulator/Metal)構造を有している。上部電極111は、バリアメタル135と銅(Cu)134からなる第1ビア105及び第2配線106(ビット線)に接続されている。ソース124側のコンタクト104は、第1キャップ絶縁膜161の開口部を介して、共通線108に接続されている。抵抗変化素子101は、第3層間絶縁膜153及び第3キャップ絶縁膜163に覆われている。第2配線106は第3キャップ絶縁膜163上に設けられている。図2に示すように、従来構造では、抵抗変化素子101が、配線層の間(ここでは第1配線103の配線層と第2配線106の配線層との間)に形成されている。この場合、抵抗変化素子101は、隣接するメモリセルMCの抵抗変化素子101とは孤立したMIMキャパシタ構造を有している。そのため、抵抗変化素子101は(寄生)容量を有していると見ることもできる。

【0005】

従来構造の動作方法について説明する。まず、初期化については、以下のようにして行う。第2配線106を介して上部電極111に正の電圧を印加し、抵抗変化層112を低抵抗化(Forming)する。このとき、ゲート122に印加する電圧を調整して、制御トランジスタ102の飽和電流値によって電流制限がかかるようにする。それにより、抵抗変化層112は所望の抵抗値になる。なお、Formingは、上部電極111の替わりに下部電極113に正の電圧を印加して行っても良い。

【0006】

次に、書き込みについては、以下のようにして行う。低抵抗状態から高抵抗状態へのスイッチングには、ソース124及びゲート122に正の電圧を印加する。高抵抗状態から低抵抗状態へのスイッチングには、上部電極111及びゲート122に正の電圧を印加する。このとき、共通線108には高抵抗状態へのスイッチングのときよりも高い電圧を印加する。また、ゲート122に印加する電圧を調整して、制御トランジスタ102の飽和電流値による電流制限がかかるようにする。それにより、抵抗変化層112は所望の抵抗値になる。なお、高抵抗状態から低抵抗状態へのスイッチング及び低抵抗状態から高抵抗状態のスイッチングにおいて、ソース124の替わりに上部電極111に正の電圧を印加してもスイッチング動作を行うことができる。

【0007】

関連する技術として、特開2009−117668号公報に不揮発性メモリ用可変抵抗およびその製造方法並びに不揮発性メモリが開示されている。この不揮発性メモリ用可変抵抗は、層間絶縁膜と、下部電極と、可変抵抗層と、上部電極と、第2配線層とを具備する。層間絶縁膜は、第1配線層上に設けられ、第1配線層に接続する貫通孔を有する。下部電極は、貫通孔内に設けられ第1配線層に接続する。可変抵抗層は、貫通孔内に設けられ下部電極上に設けられている。上部電極は、貫通孔内に設けられ可変抵抗層上に設けられている。第2配線層は、層間絶縁膜上に設けられ、上部電極と接続する。また、不揮発性メモリ用可変抵抗は、可変抵抗層と、層間絶縁膜と、プラグ金属を具備する。可変抵抗層は、第1配線層表面に設けられている。層間絶縁膜は、第1配線層上に設けられている。プラグ金属は、層間絶縁膜内に設けられ可変抵抗層に接続する。

【0008】

また、特開2010−027753号公報に不揮発性記憶素子およびその製造方法が開示されている。この不揮発性記憶素子は、第1の電極と、層間絶縁膜と、開口部と、抵抗変化膜と、第2の電極とを備えている。第1の電極は、基板上に形成されている。層間絶縁膜は、第1の電極上に形成されている。開口部は、層間絶縁膜を貫通するように形成されている。抵抗変化膜は、開口部の少なくとも底部に形成されかつ第1の電極と接続されている。第2の電極は、抵抗変化膜に隣接して形成されかつ開口部の内部に充填されている。第1の電極と第2の電極とに挟まれた抵抗変化膜が、電気的パルスの印加により抵抗値を増加または減少する特性を有する記憶部を構成する。抵抗値の変化により情報を記憶または読み出しを行う。すなわち、第1の電極は第1の配線でもある。第1の電極上には開口部が形成されている。その開口部の底部及び内壁には抵抗変化層が形成されている。抵抗変化層の内側に第2の電極が埋め込まれている。

【0009】

また、特開2009−295842号公報に半導体メモリ装置及びその製造方法が開示されている。この半導体メモリ装置は、層間絶縁膜と、導電パターンと、下部電極と、遷移金属酸化物膜と、上部電極とを備えている。層間絶縁膜は、基板上方に形成され、溝を有する。導電パターンは、溝に囲まれた層間絶縁膜に埋め込まれている。下部電極は、導電パターン上及び溝の側壁の少なくとも一部に形成されている。遷移金属酸化物膜は、下部電極の上に形成されている。上部電極は、導電パターン上及び溝の側壁の少なくとも一部において遷移金属酸化物膜の上に形成されている。

【0010】

また、特開2006−128680号公報に、集積回路内での金属層の選択的形成が開示されている。この集積回路中に導電層を選択的に形成するための方法は、銅から成る第1表面、及び第2表面を与える工程と、第1表面及び第2表面を貴金属の気相化合物と接触させる工程であって、それによって貴金属から成る導電層を第2表面と比較して第1表面上に選択的に形成するところの工程とから成る。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2009−117668号公報

【特許文献2】特開2010−027753号公報

【特許文献3】特開2009−295842号公報

【特許文献4】特開2006−128680号公報

【非特許文献】

【0012】

【非特許文献1】W.W.Zhuang et al.,“Novell Colossal Magnetoresistive Thin Film Nonvolatile Resistance Random Access Memory(RRAM)”,IEDM,論文番号7.5,pp.193−196,2002.

【非特許文献2】G.−S.Park et al.,“Observation of electric−field induced Ni filament channels in polycrystalline NiOx film”,APL,Vol.91,pp.222103,2007.

【非特許文献3】C.Yoshida et al.,“High speed resistive switching in Pt/TiO2/TiN film for nonvolatile memory application”,APL,Vol.91,pp.223510,2007.

【非特許文献4】J.F.Gibbons et al.,“Switching properties of thin NiO Films”,Solid State Electronics,vol.7,pp.785,1964.

【非特許文献5】K.Kinoshita et al.,“Bias polarity dependent data retention of resistive random access memory consisting of binary transition metal oxide”,APL,vol.89,pp.103509,2006.

【発明の概要】

【発明が解決しようとする課題】

【0013】

従来構造の抵抗変化型メモリの抵抗変化素子は、MIM構造の加工時に側壁部に加わるダメージにより、以下のような課題がある。

【0014】

図3A〜図3Bは、抵抗変化型メモリのスイッチンッグ原理を説明したものである(非特許文献4、非特許文献5)。図3Aに示すように、抵抗変化型メモリの抵抗変化素子は、上部電極111(例示:金属)、抵抗変化層112(例示:遷移金属酸化物)及び下部電極113(例示:金属)を備えている。ここで、図3Bに示すように、抵抗変化素子は、上部電極111に電圧を印加されて低抵抗化(Forming)された状態では、抵抗変化層112中に電流パス114が形成されている。この電流パス114が形成されている状態で、上部電極111と下部電極113との間に電圧を印加することによって、電流パス114内で酸化還元反応が起きる。その結果、電流パス114の抵抗値が変化する。

【0015】

図4は、抵抗変化型メモリの問題点を示す図である。抵抗変化素子の電流パス114の抵抗値の変化は、この電流パス114の上下電極界面付近における酸化還元によっておこると考えられている。しかし、図4に示すように、実際に形成される電流パスは1抵抗変化素子あたり1本だけでなく、不完全な電流パス116も含めて抵抗変化層112中の様々な場所で形成される。特に、エッチングダメージの入っている側部117で電流パス115が形成されやすい。抵抗化(Forming)後のスイッチング動作において、これらの不完全な電流パス116やダメージの入った側部117付近の電流パス115が導通した場合、抵抗値が急激にさがり、誤動作の原因となる。特に、ダメージの入った側部117付近の電流パス115のスイッチング特性は、ダメージの入っていない電極中心付近の電流パス114のスイッチング特性と異なる。そのため、抵抗変化素子性能のバラツキや信頼性が大幅に劣化する。

【0016】

このように、抵抗変化層の膜質や抵抗変化層の有効領域と抵抗変化層の端部との位置関係によって、抵抗変化素子性能のバラツキや信頼性が大幅に劣化する。

【0017】

また、図1及び図2に示されるように、1つのビット線106に対して複数のメモリセルMCが接続されている。そのため、高速化のためには、メモリセルMCの面積を縮小して寄生容量を低減する必要がある。しかし、メモリセルMCは孤立したMIM構造を有しているので、その縮小パターニングは非常に困難である。第2キャップ絶縁膜162の開口部との目ずれ許容度を考慮しても、抵抗変化素子101の素子面積の縮小による容量低減は困難である。

【0018】

また、従来構造では、配線層間(ここでは第1配線103及び第2配線106)に、MIM構造の抵抗変化素子101と、上部電極111と第2配線106とをつなぐビア105が形成されており、配線層間の厚さがスケーリングによって小さくなった場合、抵抗変化素子101の形成が困難である。更に、従来構造ではロジックLSIに混載しようとした場合、最低でも2回のPR工程(第2キャップ絶縁膜162の開口及びMIM構造のパターニング)の追加が必要であり、製造コストの低減が困難である。

【0019】

特開2009−117668号公報(特許文献1)では、貫通孔の内部において、下方に下部電極が形成され、下部電極の表面に抵抗変化層が形成され、抵抗変化層の表面に上部電極が形成されている。抵抗変化層は、例えば下部電極の表面を酸化して形成されている(特許文献1の図10〜図12、図14〜図15)。この方法を用いた実施例では、貫通孔の断面と抵抗変化層、上部電極及び下部電極の断面とが同じになる。すなわち、基板に平行な断面において、抵抗変化層の端部まで、抵抗変化素子の有効領域となっている。そのため、その端部に起因した特性ばらつきが懸念される(上述の図4で指摘された問題点)。更に、下部電極の金属成分と抵抗変化層の金属成分とが同じになるという制約がある。また、抵抗変化層は、例えば下部電極の表面に別の膜を成膜して形成されている(特許文献1の図13)。この方法を用いた実施例では、抵抗変化層における基板に平行な断面の端部は、抵抗変化素子の有効領域から離れている。従って、その端部に起因した特性ばらつきは小さい。しかし、第2配線層と層間絶縁層との間に抵抗変化層が入るため、配線層の厚さがスケーリングによって小さくなった場合、第2配線層の形成が困難となる問題がある。また、抵抗変化層は、例えば下部電極及びバリア層の表面に別の膜を成膜して形成されている(特許文献1の図16)。この方法を用いた実施例では、抵抗変化層の端部は、抵抗変化素子の有効領域から離れている。従って、その端部に起因した特性ばらつきは小さい。しかし、上部電極と抵抗変化層とバリア層とが寄生容量を形成することが問題となる。

【0020】

また、特開2010−027753号公報(特許文献2)では、開口部内に設けられているのは抵抗変化層及び第2の電極(上部電極)だけで、第1の電極(下部電極)は開口部の外側に設けられている。第1の電極は、第1の配線でもある。そのため、第1の電極(=第1の配線)の材料には制約がある。また、第1の配線(=第1の電極)の材料として、抵抗変化素子に最適な特性を有する材料を用いた場合、配線形成のプロセスが従来のプロセスから変更されることになり、製造プロセスを再検討する必要が有り、製造コストの上昇が懸念される。

【0021】

また、特開2009−295842号公報(特許文献3)では、貫通孔又は開口部のビアや配線とは別にMIM構造を形成している。そのため、MIM構造分の高さを下げることはできない。したがって、配線層間の厚さがスケーリングによって小さくなった場合、MIM構造の形成が困難である。また、ダミーの溝を必要とする点からも、スケーリングが困難である。

【課題を解決するための手段】

【0022】

以下に、発明を実施するための形態で使用される番号・符号を用いて、課題を解決するための手段を説明する。これらの番号・符号は、特許請求の範囲の記載と発明を実施するための形態との対応関係を明らかにするために括弧付きで付加されたものである。ただし、それらの番号・符号を、特許請求の範囲に記載されている発明の技術的範囲の解釈に用いてはならない。

【0023】

本発明の抵抗変化型不揮発性記憶装置は、第1配線(3)と、層間絶縁層(53)と、第2配線(6)と、抵抗変化型素子(1、1a)とを具備している。層間絶縁層(53)は、第1配線(3)上に形成されている。第2配線(6)は、層間絶縁膜(53)上に形成されている。抵抗変化型素子(1、1a)は、第1配線(3)と第2配線(6)との間に形成されている。層間絶縁層(53)は、第1配線(3)と第2配線(6)とに挟まれるように形成され、第1配線(3)の幅以下の幅を有するホール(9)を備えている。抵抗変化型素子(1、1a)は、下部電極(13、13a)と、抵抗変化層(12、12a)と、上部電極(11、11a)とを備えている。下部電極(13、13a)は、第1配線(3)と接して、ホール(9)の底部に形成されている。抵抗変化層(12、12a)は、下部電極(13、13a)上に形成されている。上部電極(11、11a)は、抵抗変化層(12、12a)上に形成されている。下部電極(13、13a)、抵抗変化層(12、12a)及び上部電極(11、11a)は、ホール(9)の内部に形成されている。第1配線(3)は銅を含み、下部電極(13、13a)はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

【0024】

本発明の抵抗変化型不揮発性記憶装置は、第1配線(3)と、層間絶縁層(53)と、第2配線(6)と、抵抗変化型素子(1、1a)とを具備している。層間絶縁層(53)は、第1配線(3)上に形成されている。第2配線(6)は、層間絶縁膜(53)上に形成されている。抵抗変化型素子(1、1a)は、第1配線(3)と第2配線(6)との間に形成されている。層間絶縁層(53)は、第1配線(3)と第2配線(6)とに挟まれるように形成され、第1配線(3)の幅以下の幅を有するホール(9)を備えている。抵抗変化型素子(1、1a)は、下部電極(13、13a)と、抵抗変化層(12、12a)と、上部電極(11、11a)とを備えている。下部電極(13、13a)は、第1配線(3)と接して、ホール(9)の底部に形成されている。抵抗変化層(12、12a)は、下部電極(13、13a)上に形成されている。上部電極(11、11a)は、抵抗変化層(12、12a)上に形成されている。下部電極(13、13a)、抵抗変化層(12、12a)及び上部電極(11、11a)は、ホール(9)の内部に形成されている。抵抗変化層(12、12a)及び上部電極(13、13a)の端部は、第2配線(6)の底面と接している。

【0025】

本発明の半導体装置は、複数の抵抗変化型不揮発性記憶装置(90/90a)と、複数の抵抗変化型不揮発性記憶装置(90/90a)を用いる論理回路(91)とを具備している。ただし複数の抵抗変化型不揮発性記憶装置(90/90a)は上記各段落に記載されている。

【0026】

本発明の抵抗変化型不揮発性記憶装置の製造方法は、第1配線(3)上に形成された層間絶縁層(53)中に、第1配線(3)の幅以下の幅を有するホール(9)を形成する工程と、ホール(9)の内部に抵抗変化型素子(1、1a)を形成する工程と、抵抗変化型素子(1、1a)と接するように抵抗変化型素子(1、1a)上に第2配線(6)を形成する工程とを具備している。抵抗変化型素子(1、1a)を形成する工程は、第1配線(3)と接して、ホール(9)の底部に下部電極(13、13a)を形成する工程と、下部電極(13、13a)上に抵抗変化層(12、12a)用の第1膜を形成する工程と、第1膜上に上部電極(11、11a)用の第2膜を形成する工程と、層間絶縁層(53)上の第1膜及び第2膜を除去する工程とを備えている。第1配線(3)は銅を含み、下部電極(13、13a)はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

【0027】

本発明の抵抗変化型不揮発性記憶装置の製造方法は、第1配線(3)上に形成された層間絶縁層(53)中に、第1配線(3)の幅以下の幅を有するホール(9)を形成する工程と、ホール(9)の内部に抵抗変化型素子(1、1a)を形成する工程と、抵抗変化型素子(1、1a)と接するように抵抗変化型素子(1、1a)上に第2配線(6)を形成する工程とを具備している。抵抗変化型素子(1、1a)を形成する工程は、第1配線(3)と接して、ホール(9)の底部に下部電極(13、13a)を形成する工程と、下部電極(13、13a)上に抵抗変化層(12、12a)用の第1膜を形成する工程と、第1膜上に上部電極(11、11a)用の第2膜を形成する工程と、層間絶縁層(53)上の第1膜及び第2膜を除去する工程とを備えている。抵抗変化層(12、12a)及び上部電極(11、11a)の端部は、第2配線(6)の底面と接する。

【発明の効果】

【0028】

本発明により、安定したスイッチング動作を低コストで実行することができる。また、本発明により、動作速度を向上させることができる。また、本発明により、デバイススケーリングの問題を回避可能である。また、ロジックLSI等との混載が可能であり、製造コストも下げられる。

【図面の簡単な説明】

【0029】

【図1】図1は、従来の1T1R型の抵抗変化型メモリの構成を示す平面図である。

【図2】図2は、図1におけるa−a’断面の構成を示す断面図である。

【図3A】図3Aは、抵抗変化型メモリのスイッチンッグ原理を説明したものである。

【図3B】図3Bは、抵抗変化型メモリのスイッチンッグ原理を説明したものである。

【図4】図4は、抵抗変化型メモリの問題点を示す図である。

【図5】図5は、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の主要部の構成を示す断面図である。

【図6】図6は、低抵抗化(Forming)後の抵抗変化素子の構成を示す断面図である。

【図7A】図7Aは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7B】図7Bは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7C】図7Cは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7D】図7Dは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7E】図7Eは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7F】図7Fは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7G】図7Gは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7H】図7Hは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7I】図7Iは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図8】図8は、本発明の第2の実施の形態に係る半導体装置の構成を示す平面図である。

【図9A】図9Aは、本発明の第2の実施の形態に係る半導体装置における抵抗変化型不揮発記憶装置の領域の構成を示す断面図である。

【図9B】図9Bは、本発明の第2の実施の形態に係る半導体装置におけるロジックLSIの領域の構成を示す断面図である。

【図10A】図10Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図10B】図10Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図11A】図11Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図11B】図11Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図12A】図12Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図12B】図12Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図13A】図13Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図13B】図13Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図14A】図14Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図14B】図14Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図15A】図15Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図15B】図15Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図16】図16は、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の主要部の構成を示す断面図である。

【図17A】図17Aは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図17B】図17Bは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図17C】図17Cは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図17D】図17Dは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図17E】図17Eは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図17F】図17Fは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【発明を実施するための形態】

【0030】

以下、本発明の抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の製造方法の実施の形態に関して、添付図面を参照して説明する。

【0031】

(第1の実施の形態)

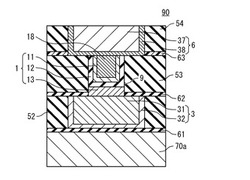

本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の構成について、添付図面を参照して説明する。図5は、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の主要部の構成を示す断面図である。抵抗変化型不揮発記憶装置90は、基板70aと、第1キャップ絶縁膜61と、第1配線3と、第2層間絶縁膜52と、第2キャップ絶縁膜62と、抵抗変化型素子1と、第3層間絶縁膜53と、第3キャップ絶縁膜63と、第2配線6と、第4層間絶縁膜54とを具備している。

【0032】

第1配線3は、基板70a上に設けられている。第1配線3は、例えば第1メタル配線31とそれを側方及び底面において覆うバリアメタル層32とを備えている。ただし、基板70aは、表面領域に素子を形成された半導体基板と、その半導体基板を覆う第1層間絶縁膜や第1キャップ絶縁膜61を備えている。第1層間絶縁膜及び第1キャップ絶縁膜61は第1層間絶縁層ということもできる。従って、第1配線3は、第1層間絶縁層上に設けられている。第1配線3は、第2層間絶縁膜52に埋設され、第2キャップ絶縁膜62に覆われている。第2層間絶縁膜52及び第2キャップ絶縁膜62は第2層間絶縁層ということもできる。従って、第1配線3は、第2層間絶縁層に埋設されている。

【0033】

第3層間絶縁膜53は、第2層間絶縁層上に設けられている。第3層間絶縁膜53は、ホール9を備えている。ホール9は、第1配線3と第2配線6とに挟まれるように、第3層間絶縁層53を貫通するように設けられている。ホール9の底面は、第1配線3の上面に接していて、その上面からはみ出していない。ホール9の横断面(基板70aの表面に平行な面)が円形の場合、その断面の直径は第1配線3の配線幅以下である。ただし、ホール9の底面が第1配線3の上面からはみ出さなければ、ホール9の横断面は他の形を有していても良い。その場合、ホール9の幅(基板70aの表面に平行な方向)は第1配線3の配線幅以下である。第3キャップ絶縁膜63は、第3層間絶縁膜53上に設けられている。第3層間絶縁膜53及び第3キャップ絶縁膜63は第3層間絶縁層ということもできる。

【0034】

抵抗変化型素子1は、抵抗値の変化で情報を記憶する。第1配線3と第2配線6との間に形成されたホール9内に設けられている。抵抗変化型素子1は、下部電極13と、抵抗変化層12と、上部電極11とを備えている。

【0035】

下部電極13は、ホール9の底部のみに形成されている。その端部は、ホール9の底部近傍の側壁に接している。下部電極13は、金属の導体で形成されている。下部電極13は、第2層間絶縁層の開口部の第1配線3(第1メタル配線31)上に選択成長で形成されていることが好ましい。追加プロセスを要せずに、下部電極13をホール9内のみに形成できるからである。その形成方法については後述される。

【0036】

抵抗変化層12は、下部電極13上及びホール9の側壁上に形成されている。その端部は、ホール9の上部に達している。その端部は、第2配線6の底面に接していることが好ましい。それにより、抵抗変化層12の端部と下部電極13の端部とを大きく隔てることができる。その結果、後述されるように、抵抗変化素子1は、抵抗変化層12の端部の影響を受け難くなる。抵抗変化層12は、下部電極13とは異なる金属材料を用いた酸化物を含むことができる。

【0037】

上部電極11は、抵抗変化層12上を内側から覆うように形成されている。その端部は、ホール9の上部に達している。その端部は、第2配線6の底面に接していることが好ましい。抵抗変化素子1と第2配線6とを接続するためのビアやコンタクトを別途製造する必要が無いからである。上部電極11は、金属の導体で形成されている。上部電極11は、その更に内側の領域を埋める埋め込み層(金属)18を備えていても良い。

【0038】

第2配線6は、第3層間絶縁膜53上に設けられている。第2配線6は、例えば第2メタル配線37とそれを側面及び底面において覆うバリアメタル層38とを備えている。第2配線層6は、第3層間絶縁層上に設けられていてもよい。第2配線6は、第4層間絶縁膜54に埋設されている。

【0039】

第1メタル配線31は、基板表面に垂直な方向において(111)方位へ配向した結晶粒を主成分として含む多結晶膜であることが好ましい。すなわち、第1メタル配線31は、(111)配向性を有する膜であることが好ましい。後述されるように下部電極13を選択成長させ易いからである。例えば、第1メタル配線31として(111)配向性を有する銅(Cu)配線を用いた場合、下部電極13としては例えば(002)配向性を有するルテニウム(Ru)膜を選択成長させることができる。ただし、主成分は、最も多い成分である。

【0040】

第1メタル配線31は、銅(Cu)、アルミニウム(Al)、シリコン(Si)が考えられる。第1メタル配線31として銅(Cu)及びアルミニウム(Al)を用いる場合、第1メタル配線31及びホール9はそれぞれ通常の配線及びビアホールが想定される。第1メタル配線31としてシリコンを用いる場合、第1メタル配線31及びホール9はそれぞれソース/ドレイン及びコンタクトホールが想定される。後述される製造方法の例では、(111)配向の銅(Cu)を用いている。

【0041】

下部電極13は、第1メタル配線31が銅(Cu)の場合、主成分としてルテニウム(Ru)、タングステン(W)、コバルト(Co)、白金(Pt)、金(Au)、ロジウム(Rh)、イリジウム(Ir)及びパラジウム(Pd)からなる群から選択された少なくとも1種の金属を含有することが好ましい。下部電極13を選択成長させやすいからである。このうち、ルテニウム(Ru)、タングステン(W)、コバルト(Co)、白金(Pt)は、抵抗変化素子1の下部電極13の材料として特に好ましい。後述される製造方法の例では、(111)配向の銅(Cu)の第1メタル配線31との結晶整合性に優れているものとして、(002)配向のルテニウム(Ru)の下部電極13を用いている。

【0042】

また、下部電極13は、第1メタル配線31がアルミニウム(Al)の場合、主成分としてタングステン(W)、タンタル(Ta)及びチタニウム(Ti)からなる群から選択される少なくとも1種の金属を含有することが好ましい。下部電極13を選択成長させやすいからである。

【0043】

また、下部電極13は、第1メタル配線31がシリコン(Si)の場合、主成分としてタングステン(W)、タンタル(Ta)及びチタニウム(Ti)からなる群から選択される少なくとも1種の金属を含有することが好ましい。下部電極13を選択成長させやすいからである。

【0044】

上部電極は、例えば、チタニウム(Ti)、窒化チタニウム(TiN)、アルミニウム(Al)、ニッケル(Ni)、銅(Cu)、銅アルミニウム(CuAl)、タンタル(Ta)、窒化タンタル(TaN)、ジルコニウム(Zr)、ハフニウム(Hf)、モリブデン(Mo)、ルテニウム(Ru)、白金(Pt)などによって形成できる。また、これらの材料の積層体であっても良い。後述される製造方法の例では、窒化チタニウム(TiN)を用いている。

【0045】

抵抗変化層12は酸化チタニウム(TiO2)、酸化鉄(FeO)、酸化ニッケル(NiO)、酸化ジルコニウム(ZrO2)、酸化銅(CuO)、酸化ハフニウム(HfO2)、酸化タンタル(Ta2O5)、酸化タングステン(WO)、及びこれらの窒化物やシリケートを少なくとも含む単層膜若しくは積層膜が好ましい。後述される製造方法の例では、酸化ニッケル(NiO)を用いている。

【0046】

第1〜第4層間絶縁膜51〜54の材料としては、酸化シリコン(SiO2)が例示される。第1〜第3キャップ絶縁膜61〜63の材料としては、窒化シリコンSiNxが例示される。

【0047】

図6は、低抵抗化(Forming)後の抵抗変化素子の構成を示す断面図である。抵抗変化素子1を拡大して示している。抵抗変化素子1では、下部電極13と上部電極11とに挟まれた(下部電極13と上部電極11とが重なった)領域が、抵抗変化層12における有効領域Aである。有効領域Aは、電流パス14が生成される可能性のある領域である。この図6の場合、上部電極11と下部電極13とは、その一部しか重なっていない。すなわち、上部電極11の一部分11pと下部電極13の一部分13pとが重なっているだけである。この重なった領域が、抵抗変化層12における有効領域A(α1からα2まで)である。図に示されるように、この有効領域Aは、ホール9(ビアホール又はコンタクトホール)の底部における周辺を除いた領域にしかない。すなわち、その有効領域Aの境界α1、α2は、ホール9の側壁や、下部電極13の端部や、抵抗変化層12の端部や、上部電極11の端部から離れている。そのため、電流パスはホール9の底部における周辺を除いた領域にしかできなくなる。したがって、電流パスはホール9の側壁や、下部電極13の端部や、抵抗変化層12の端部や、上部電極11の端部の影響を受けることはない。言い換えると、抵抗変化層12の端部は第3層間絶縁膜53の上側表面と概ね同じ面にあり、上部電極11と下部電極13と挟まれていない。そのため、ダメージの入っている抵抗変化層12の端部17に電流パスが形成されることはない。したがって、抵抗変化型メモリのバラツキ及び信頼性が向上する。

【0048】

また、本実施の形態では、既述のように上部電極11と下部電極13とは、一部しか重なっていない(有効領域A)。そのため、MIM構造を有する抵抗変化素子1の容量を、従来構造と比較して小さくすることができる。その結果、ビット線の寄生容量が減少するので、書き換え動作及び読み出し動作の高速化が可能となる。

【0049】

また、本実施の形態では、図4に示されるように、ホール9内に抵抗変化素子1が埋め込まれ、上部電極11の上端の位置が第2配線6の下面の位置と概ね同じである。そのため、新たに上部電極11と接続するためのビアやコンタクトを新たに形成する必要がない。更に、図4に示すような本実施の形態の抵抗変化型メモリを用いることでMIM構造の高さに起因したスケーリングの問題を回避することができる。

【0050】

次に、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の動作方法について、図5を参照して説明する。

まず、低抵抗化(Forming)を行うため、上部電極11に正の電圧を印加し、抵抗変化層12を低抵抗化する。なお、低抵抗化(Forming)は、上部電極11の代わりに下部電極13に正の電圧を印加しても良い。次に、低抵抗状態から高抵抗状態へのスイッチングのときには、上部電極11に正の電圧を印加する。この場合、低抵抗化(Forming)の場合よりも電流が流れるように、負荷抵抗の抵抗を下げておくことが好ましい。一方、高抵抗状態から低抵抗状態へのスイッチングのときには、上部電極11に正の電圧を印加する。この場合、上部電極11には高抵抗状態へのスイッチングの場合よりも高い電圧を印加する。また、低抵抗化(Forming)の場合と同様に抵抗変化素子1に負荷抵抗をつけておき、低抵抗化後に電流が流れすぎないようにしておくのが好ましい。なお、高抵抗状態から低抵抗状態へのスイッチングのときにも、上部電極11の代わりに下部電極13に正の電圧を印加しても良い。

【0051】

次に、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法について説明する。図7A〜図7Iは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【0052】

まず、図7Aに示すように、基板70aが準備される。基板70aは、半導体基板の表面領域に形成された素子と、それを覆う第1層間絶縁膜及び第1キャップ絶縁膜61とを備えている。次に、基板70a上に第2層間絶縁膜52を形成する。第1キャップ絶縁膜61としては、ここではシリコン窒化膜(SiNx)を用いる。第1層間絶縁膜及び第2層間絶縁膜52としては、ここではシリコン酸化膜(SiO2)を用いる。それぞれ、プラズマCVD(Chemical Vapor Deposition)法を用いて堆積する。

【0053】

次に、図7Bに示すように、PR(Photoresist)工程とドライエッチング工程により、第2層間絶縁膜52に溝を形成する。その後、バリアメタル層32用の膜及び第1メタル配線31用の膜を形成する。バリアメタル層32用の膜としては、ここではタンタル窒化膜(TaN)を用いる。第1メタル配線31用の膜としては、ここでは銅(Cu)を用いる。タンタル窒化膜(TaN)はスパッタ法を用いて堆積する。銅(Cu)はスパッタ法及びメッキ法を用いて堆積する。その後、CMP(Chemical Mechanical Polishing)工程を用いて、表面の平坦化を行い、第1配線3としての銅(Cu)配線を形成する。

【0054】

続いて、図7Cに示すように、表面に第2キャップ絶縁膜62及び第3層間絶縁膜53を形成する。第2キャップ絶縁膜62としては、ここではシリコン窒化膜(SiNx)を用いる。第3層間絶縁膜53としては、ここではシリコン酸化膜(SiO2)を用いる。それぞれ、プラズマCVD(Chemical Vapor Deposition)法を用いて堆積する。

【0055】

その後、図7Dに示すように、PR工程とドライエッチング工程を用いて、第3層間絶縁膜53及び第2キャップ絶縁膜62にホール(開口部)9を設ける。それにより、第1配線3(Cu配線)の表面が露出する。すなわち、第1配線3の銅(Cu)が露出する。

【0056】

次に、図7Eに示すように、ホール9の銅(Cu)の露出した部分にルテニウム(Ru)を所定の膜厚で選択CVD法により形成する。すなわち、ホール9の底部に、第1配線3と接してルテニウム(Ru)を選択成長させる。具体的には、例えば、ルテニウムの有機金属化合物(例示:Ru3(CO)12)を用いた熱CVD法(例示:プロセスガスはCOガス)により形成することができる。そのルテニウム(Ru)は下部電極13となる。この下部電極13は、ホール9の底部にのみ存在しており、その端部はホール9の内側の側壁に接している。

【0057】

なお、下部電極13として、他の金属、例えば、タングステン(W)、コバルト(Co)、白金(Pt)、金(Au)、ロジウム(Rh)、イリジウム(Ir)及びパラジウム(Pd)からなる群から選択された少なくとも1種の金属を用いる場合にも、同様に、その金属を含む有機金属化合物を用いた熱CVD法により形成することが可能である。

【0058】

なお、第1配線3としてアルミニウム(Al)配線(若しくはチタニウム窒化膜(TiN)/アルミニウム(Al)積層配線)、又は、シリコン(Si)基板(例示:ソース/ドレイン)を用い、下部電極13としてタングステン(W)、タンタル(Ta)及びチタニウム(Ti)のうちのいずれかを用いる場合には、例えば以下の方法を用いることができる。すなわち、それぞれ原料ガスとして六フッ化タングステン、四塩化チタン及び五フッ化タンタルを用いた熱CVD法により下部電極13を形成する。

【0059】

続いて、図7Fに示すように、第3層間絶縁膜53の表面、ホール9の内部の側壁及び下部電極13の表面を覆うように、抵抗変化層12用の膜、上部電極11用の膜及び埋め込み層18用の膜を形成する。抵抗変化層12用の膜としては、ここではニッケル酸化膜(NiO)を用いる。上部電極13用の膜としては、ここではチタニウム窒化膜(TiN)を用いる。埋め込み層18用の膜としては、ここではタングステン(W)を用いる。これらは、はスパッタ法で成膜される。なお、埋め込み層18は上部電極11と同じ材料でもよいし、また上部電極11用の膜を厚く形成するなどして、埋め込み層18を無くしてもかまわない。

【0060】

その後、図7Gに示すように、表面をCMP工程で平坦化する。それにより、抵抗変化素子1の全てはホール9(開口部)に埋め込まれる。そのとき、下部電極13は、ホール9の底部のみに形成されている。抵抗変化層12は、下部電極13上及びホール9の側壁上に形成されている。その端部は、ホール9の上部に達している。上部電極11は、抵抗変化層12上を内側から覆うように形成されている。その端部は、ホール9の上部に達している。

【0061】

次に、図7Hに示すように、表面に第3キャップ絶縁膜63及び第4層間絶縁膜54を形成する。第3キャップ絶縁膜63としては、ここではシリコン窒化膜(SiNx)を用いる。第4層間絶縁膜54としては、ここではシリコン酸化膜(SiO2)を用いる。それぞれ、プラズマCVD法を用いて堆積する。

【0062】

続いて、図7Iに示すように、PR工程とドライエッチング工程を用いて、第4層間絶縁膜54及び第3キャップ絶縁膜63に溝を形成する。それにより、上部電極11及び埋め込み層18が露出する。更に、バリアメタル層38用の膜及び第2メタル配線37用の膜を形成する。バリアメタル層38用の膜としては、ここではタンタル窒化膜(TaN)を用いる。第2メタル配線37用の膜としては、ここでは銅(Cu)を用いる。タンタル窒化膜(TaN)はスパッタ法を用いて堆積する。銅(Cu)はスパッタ法及びメッキ法を用いて堆積する。その後、CMP工程を用いて、表面の平坦化を行い、第2配線6としての銅(Cu)配線を形成する。

【0063】

以上により、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置90が製造される。

【0064】

本実施の形態では、抵抗変化層12の有効領域は、下部電極13と面したホール9の底部(周辺部を除く)の部分だけである。抵抗変化層12の端部は、ホール9の上端部へ延在してホール9の底部から離れている。そのため、抵抗変化層12の端部のダメージに起因した、抵抗変化素子1のばらつきを低減することができる。また、ホール9径で抵抗変化素子1の容量が決まるため、ホール9の径を小さくすることで、寄生容量を小さくすることができる。それにより、抵抗変化型メモリの高速動作が可能となる。更に、従来のMIM構造+ビア構造ではなく、ビアホールに相当するホール9内に抵抗変化素子1が埋め込まれているため、MIM構造の高さに起因したスケーリングの問題が回避できる。更に、1回のPR工程の追加で抵抗変化型不揮発素子をロジックLSI(後述)に混載可能であり、製造コストを低減することができる。

【0065】

(第2の実施の形態)

本発明の第2の実施の形態に係る抵抗変化型不揮発記憶装置の構成について、添付図面を参照して説明する。第2の実施の形態は、第1の実施の形態に係る抵抗変化型不揮発記憶装置90を1T1R(1トランジスタ1抵抗)型の抵抗変化型メモリ(ReRAM)に適用し、ロジックLSI(large−scale integration)91と混載した半導体装置に関する。以下、詳細に説明する。

【0066】

図8は、本発明の第2の実施の形態に係る半導体装置の構成を示す平面図である。ただし、この図では、半導体装置のうち抵抗変化型不揮発記憶装置90(1T1R型の抵抗変化型メモリ)の領域を示している。抵抗変化型不揮発記憶装置90は、複数のワード線(又はゲート)22と、複数のビット線(又は第2配線)6と、複数の共通線8と、複数のメモリセルMCとを具備している。複数のワード線(又はゲート)22は、Y方向に延在している。複数のビット線(又は第2配線)6は、X方向に延在している。複数の共通線8は、Y方向に延在しいている。複数のメモリセルMCは、複数のワード線22と複数のビット線6との交点の各々に対応して行列状に設けられている。

【0067】

図9Aは、本発明の第2の実施の形態に係る半導体装置における抵抗変化型不揮発記憶装置の領域の構成を示す断面図である。この図では、図8におけるb−b’断面の構成を示している。すなわち、メモリセルMCの1個分の構成を示している。抵抗変化型不揮発記憶装置90のメモリセルMCは、制御トランジスタ2と、抵抗変化素子1とを備えている。素子分離領域71で囲まれた領域において、半導体基板70上に及び制御トランジスタ2が形成されている。制御トランジスタ2は、ゲート絶縁膜23、ゲート22(ワード線)、ドレイン21、ソース24、サイドウォール25を備えている。ドレイン21、ソース24にはコンタクト4が接続されている。制御トランジスタ2及びコンタクト4は第1層間絶縁膜51及び第1キャップ絶縁膜61に覆われている。ドレイン21側のコンタクト4は、第1キャップ絶縁膜61の開口部を介して、バリアメタル層32と第1メタル配線31からなる第1配線3に接続されている。第1配線3は、第2層間絶縁膜52及び第2キャップ絶縁膜62に側面及び上面を覆われている。抵抗変化型メモリの抵抗変化素子1は、第2キャップ絶縁膜62の開口部を介して、第1配線3に接続されている。抵抗変化素子1は、第1配線3と接続される下部電極13、下部電極13上の抵抗変化層12及び抵抗変化層12上の上部電極11からなるMIM(Metal/Insulator/Metal)構造を有している。上部電極11内部には埋め込み層18が設けられていてもよい。上部電極11(及び埋め込み層18)は、バリアメタル層38と第2メタル配線37からなる第2配線6(ビット線)に接続されている。ソース24側のコンタクト4は、第1キャップ絶縁膜61の開口部を介して、共通線8に接続されている。抵抗変化素子1は、第3層間絶縁膜53及び第3キャップ絶縁膜63に側面を覆われている。第2配線6は第3層間絶縁膜53上に設けられている。第2配線6は、第4層間絶縁膜54に側面を覆われている。図9Aに示すように、本実施の形態では、抵抗変化素子1が、配線層の間(ここでは第1配線3の配線層と第2配線6の配線層との間)に設けられたホール9内に形成されている。抵抗変化素子1は、隣接するメモリセルMCの抵抗変化素子1とは孤立したMIMキャパシタ構造を有している。

【0068】

一方、半導体装置のうちロジックLSI91の領域は以下に示すとおりである。図9Bは、本発明の第2の実施の形態に係る半導体装置におけるロジックLSIの領域の構成を示す断面図である。この図では、ロジックLSI91における一つのトランジスタを含む領域を示している。素子分離領域71aで囲まれた領域において、半導体基板70上に制御トランジスタ2aが形成されている。制御トランジスタ2aは、ゲート絶縁膜23a、ゲート22a、ドレイン21a、ソース24a、サイドウォール25aを備えている。ドレイン21a、ソース24aにはコンタクト4aが接続されている。制御トランジスタ2a及びコンタクト4aは第1層間絶縁膜51及び第1キャップ絶縁膜61に覆われている。ドレイン21a側のコンタクト4aは、第1キャップ絶縁膜61の開口部を介して、バリアメタル層32aと第1メタル配線31aからなる第1配線3aに接続されている。第1配線3aは、第2層間絶縁膜52及び第2キャップ絶縁膜62に側面及び上面を覆われている。第1配線3aは、第2キャップ絶縁膜62の開口部を介して、バリアメタル層35aとビアメタル34aからなるビア5aに接続されている。ビア5aは、第3層間絶縁膜53及び第3キャップ絶縁膜63に側面を覆われている。ビア5aは、第3キャップ絶縁膜63の開口部を介して、バリアメタル層38aと第2メタル配線37aからなる第2配線6aに接続されている。第2配線6aは第3キャップ絶縁膜63上に設けられている。第2配線6aは、第4層間絶縁膜54に側面を覆われている。ソース24a側も同様である。図9A及び図9Bに示すように、基板70の表面領域及び各層の役割は、抵抗変化型メモリの領域と、ロジックLSIの領域とで同様である。

【0069】

図9Aの場合では、抵抗変化素子1を、第1配線3の配線層(第1配線層)と第2配線6の配線層(第2配線層)との間に形成している。しかし、抵抗変化素子1を、他の連続した二つの配線層の間に形成しても良い。更に、抵抗変化素子1を、連続しない二つの配線層の間(例示:第1配線層と第3配線層との間)に形成しても良い。更に、抵抗変化素子1を、コンタクト4内に形成してもよい。

【0070】

本実施の形態における第1配線3、抵抗変化素子1及び第2配線6のその他の構成や機能については、第1の実施の形態の場合と同様である。

【0071】

本実施の形態では、ロジックLSI領域でのビアホールに対応するホール9内に抵抗変化素子1が埋め込まれている。加えて、上部電極11の最上部の位置が第2配線6の下面の位置と同じである。そのため、上部電極11と第2配線6とを接続するためのビアを新たに形成する必要がない。更に、図9Aに示すような本実施の形態の抵抗変化型メモリを用いることでMIM構造の高さに起因したスケーリングの問題を回避することができる。また、本実施の形態の抵抗変化型メモリの構造はロジックLSIの領域の構造に影響を与えない。そのため、ロジックデバイスとの混載に有効である。

【0072】

更に、第1の実施の形態の図6に示されるように、下部電極13と上部電極11とに挟まれた領域が、抵抗変化層12における有効領域Aとなる。上部電極11と下部電極13とは、その一部しか重なっていない。そのため、従来構造と比較して、抵抗変化素子1の容量を小さくすることができる。その結果、ビット線(第2配線6)の寄生容量が減少し、書き換え・読み出し動作の高速化が可能となる。

【0073】

また、有効領域Aの境界はホール9の側壁や、下部電極13の端部や、上部電極11の端部に達していない。そのため、電流パスはホール9の底部における周辺を除いた領域にしかできなくなる。したがって、電流パスはホール9の側壁や、下部電極13の端部や、上部電極11の端部の影響を受けることはない。言い換えると、ダメージの入っている抵抗変化層12の端部17に不完全な電流パスが形成されることはない。したがって、抵抗変化型メモリのバラツキ及び信頼性が向上する。

【0074】

次に、本発明の第2の実施の形態に係る半導体装置の抵抗変化型不揮発記憶装置の動作方法について、は、第1の実施の形態と同様である。

【0075】

次に、本発明の第2の実施の形態に係る半導体装置の製造方法について説明する。図10A及び図10B〜図15A及び図15Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。ただし、図nA(n=10〜15の整数)は抵抗変化型不揮発記憶装置90の領域(以下「メモリ部」ともいう)であり、図nBはロジックLSI91の領域(以下「ロジック部」ともいう)である。

【0076】

まず、図10A及び図10Bに示すように、メモリ部及びロジック部において、半導体基板70上に、通常のMOSFET工程を用いて、素子分離層71、71a、ゲート22、22a、ゲート絶縁膜23、23a、ソース24、24a、ドレイン21、21a及びサイドウォール25、25aを形成する。ここでは、半導体基板70としてp−シリコン(Si)、ゲート絶縁膜23、23aとしてシリコン酸化膜(SiOx)、ゲート22、22aとしてポリシリコン膜(poly−Si)、ソース24、24a、ドレイン21、21aとしてn+シリコン(n+Si)、サイドウォール25、25aとしてシリコン窒化膜(SiNx)をそれぞれ用いる。

【0077】

次に、図11A及び図11Bに示すように、メモリ部及びロジック部において、全面に第1層間絶縁膜51用の膜を堆積し、CMP工程によって平坦化して、第1層間絶縁膜51を形成する。第1層間絶縁膜53としては、ここではシリコン酸化膜(SiOx)を用い、プラズマCVD法を用いて堆積する。更に、PR工程とドライエッチング工程を用いて、第1層間絶縁膜51に開口部を設ける。次に、その開口部にコンタクト4、4aを埋め込み、それぞれソース24、24a、ドレイン21、21aと接続する。コンタクト4、4aとして、ここではタングステン(W)を用い、スパッタ法を用いて成膜した。

【0078】

次に、図12A及び図12Bに示すように、メモリ部及びロジック部において、全面に第1キャップ絶縁膜61及び第2層間絶縁膜52を堆積する。第1キャップ絶得膜61としては、ここではシリコン窒化膜(SiNx)を用い、第2層間絶縁膜52としては、ここではシリコン酸化膜(SiOx)を用いる。更に、PR工程とドライエッチング工程により、第2層間絶縁膜52及び第1キャップ絶縁膜61に溝を形成する。その後、バリアメタル層32、32a用の膜及び第1メタル配線31、31a用の膜を堆積する。バリアメタル層32、32a用の膜としては、ここではタンタル窒化膜(TaN)を用い、スパッタ法を用いて成膜する。第1メタル配線31、31a用の膜としては、ここでは銅(Cu)を用い、スパッタ法及びメッキ法を用いて成膜する。更に、CMP工程を用いて、表面の平坦化を行い、第1配線3(32+31)、第1配線3a(32a+31a)を形成する。

【0079】

次に、図13A及び図13Bに示すように、メモリ部及びロジック部において、全面に第2キャップ絶縁膜62及び第3層間絶縁膜53を堆積する。第2キャップ絶縁膜62としてはここでは、シリコン窒化膜(SiNx)を用い、第3層間絶縁膜53としては、ここではシリコン酸化膜(SiOx)を用いる。それぞれ、プラズマCVD法を用いて堆積する。更に、メモリ部において、PR工程とドライエッチング工程を用いて、所定の領域のみ第3層間絶縁膜53及び第2キャップ絶縁膜62にホール9(開口部)を設ける。これにより、第1配線3の表面の銅(Cu)が露出する。更に、ホール9の銅(Cu)の露出部分に、ルテニウム(Ru)を選択CVD成長させる。このルテニウム(Ru)膜は、下部電極13となる。次に、全面に、抵抗変化層12用の膜、上部電極11用の膜及び埋め込み層18用の膜を堆積する。抵抗変化層12用の膜として、ここではTiO2とTa2O5の積層膜を用い、上部電極11用の膜として、ここではチタニウム窒化膜(TiN)を用い、埋め込み層18として、ここではタングステン(W)を用いる。なお、埋め込み層18用の膜は、上部電極11用の膜と同じ材料でもよく、また、埋め込み層を無くしてもかまわない。次に、表面をCMP工程で平坦化する。それにより、メモリ部において、抵抗変化素子1(下部電極13、抵抗変化層12及び上部電極11)がホール9に埋め込まれた構成が形成される。

【0080】

次に、図14A及び図14Bに示すように、メモリ部とロジック部において、全面に第3キャップ絶縁膜63及び第4層間絶縁膜54を堆積する。第3キャップ絶縁層63としては、ここではシリコン窒化膜(SiNx)を用い、第4層間絶縁膜54としては、ここではシリコン酸化膜(SiOx)を用いる。それぞれ、プラズマCVD法を用いて堆積する。

【0081】

次に、図15A及び図15Bに示すように、PR工程とドライエッチング工程を用いて、メモリ部において、第4層間絶縁膜54及び第3キャップ絶縁膜63に溝を形成し、ロジック部において、第4層間絶縁膜54に溝を形成し、第3キャップ絶縁膜63、第3層間絶縁膜53及び第2キャップ絶縁膜62にビアホールを形成する。それにより、メモリ部において上部電極11(及び埋め込み層18)が露出し、ロジック部において他の第1配線3aが露出する。その後、全面にバリアメタル層38、35a、38a用の膜、ビアメタル34a及び第2メタル配線37、37a用の膜を堆積する。バリアメタル層38、35a、38a用の膜としては、ここではタンタル窒化膜(TaN)を用い、スパッタ法を用いて成膜する。ビアメタル34a及び第2メタル配線37、37a用の膜としては、ここでは銅(Cu)を用い、スパッタ法及びメッキ法を用いて成膜する。更に、CMP工程を用いて、表面の平坦化を行い、第2配線6(38+37)、ビア5a(34a+35a)、第2配線6a(38a+37a)を形成する。

【0082】

以上により、本発明の第2の実施の形態に係る半導体装置が製造される。

【0083】

本実施の形態についても、第1の実施の形態と同様の効果を得ることができる。

加えて、本実施の形態に係る抵抗変化型不揮発記憶装置は1回のPR工程の追加でロジックLSIに混載可能であり、製造コストの大幅な削減が可能となる。更に、ロジックLSIのデバイスパラメータを変えることなく抵抗変化型不揮発記憶装置を混載することができる。

【0084】

(第3の実施の形態)

本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の構成について、添付図面を参照して説明する。第3の実施の形態では、抵抗変化素子1aの下部電極13aがホール9の底部だけでなく、底部から側壁の途中まで形成されている点で、第1の実施の形態と異なる。以下詳細に説明する。

【0085】

図16は、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の主要部の構成を示す断面図である。抵抗変化型不揮発記憶装置90aは、基板70aと、第1キャップ絶縁膜61と、第1配線3と、第2層間絶縁膜52と、第2キャップ絶縁膜62と、抵抗変化型素子1aと、第3層間絶縁膜53と、第3キャップ絶縁膜63と、第2配線6と、第4層間絶縁膜54とを具備している。

【0086】

抵抗変化型素子1aは、抵抗値の変化で情報を記憶する。第1配線3と第2配線6との間に形成されたホール9内に設けられている。抵抗変化型素子1aは、下部電極13aと、抵抗変化層12aと、上部電極11aとを備えている。

【0087】

下部電極13aは、ホール9の底部及び底部から側壁の途中まで連続的に形成されている。ただし、その端部は、ホール9の側壁の途中に在り、ホール9の上部に達していない。下部電極13aは、金属の導体で形成されている。下部電極13aは、選択成長でなく通常の成膜法で形成されている。その形成方法については後述される。

【0088】

抵抗変化層12aは、下部電極13a上及びホール9の側壁上に形成されている。その端部は、ホール9の上部に達している。その端部は、第2配線6の底面に接していることが好ましい。それにより、抵抗変化層12aの端部と下部電極13aの端部とを大きく隔てることができる。その結果、抵抗変化素子1aは、抵抗変化層12aの端部の影響を受け難くなる。抵抗変化層12aは、下部電極13aとは異なる金属材料を用いた酸化物を含むことができる。

【0089】

上部電極11aは、抵抗変化層12a上を内側から覆うように形成されている。その端部は、ホール9の上部に達している。その端部は、第2配線6の底面に接していることが好ましい。抵抗変化素子1aと第2配線6とを接続するためのビアやコンタクトを別途製造する必要が無いからである。上部電極11aは、金属の導体で形成されている。上部電極11aは、その更に内側の領域を埋める埋め込み層(金属)18を備えていても良い。

【0090】

抵抗変化型素子1aのその他の特徴、及び、抵抗変化型不揮発記憶装置のその他の構成については、第1の実施の形態と同様である。

【0091】

この場合においても、第1の実施の形態で説明された効果と同様の効果を得ることができる。

【0092】

次に、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の動作方法については、第1の実施の形態と同様である。

【0093】

次に、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法について説明する。図17A〜図17Fは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【0094】

まず、第1の実施の形態における図7A及び図7Bの工程を実施する。

次に、図17Aに示すように、表面に第2キャップ絶縁膜62、第3層間絶縁膜53及び第3キャップ絶縁膜63を形成する。第2キャップ絶縁膜62及び第3キャップ絶縁膜63としては、ここではシリコン窒化膜(SiNx)を用いる。第3層間絶縁膜53としては、ここではシリコン酸化膜(SiO2)を用いる。それぞれ、プラズマCVD法を用いて堆積する。

【0095】

続いて、図17Bに示すように、PR工程とドライエッチング工程を用いて、第3キャップ絶縁膜63、第3層間絶縁膜53及び第2キャップ絶縁膜62にホール(開口部)9を設ける。それにより、第1配線3の表面が露出する。すなわち、第1配線3の銅(Cu)が露出する。

【0096】

その後、図17Cに示すように、全面に下部電極13a用の膜を形成する。下部電極13a用の膜としては、ここではルテニウム(Ru)を用いる。ルテニウム(Ru)はスパッタ法で成膜される。それにより、下部電極13a用の膜が、第3キャップ絶縁膜63の表面及びホール9の内部の表面(ホール9の底部を含む)を覆う。その後、全面にレジスト42を塗布し、所定の条件下でアッシングを行う。それにより、レジスト42は、ホール9の底部及び側壁の途中まで下部電極13a用の膜を覆う。

【0097】

次に、図17Dに示すように、下部電極13a用の膜をエッチバックする。その後、レジスト42をアッシングにより除去する。それにより、下部電極13aが、ホール9の底部及び底部から側壁の途中まで連続的に形成される。

【0098】

続いて、図17Eに示すように、第3ストッパ絶縁膜63の表面、ホール9の内部の上部側壁及び下部電極13の表面を覆うように、抵抗変化層12a用の膜、上部電極11a用の膜及び埋め込み層18用の膜を形成する。抵抗変化層12a用の膜としては、ここではニッケル酸化膜(NiO)を用いる。上部電極13a用の膜としては、ここではチタニウム窒化膜(TiN)を用いる。埋め込み層18用の膜としては、ここではタングステン(W)を用いる。これらは、はスパッタ法で成膜される。なお、埋め込み層18は上部電極11aと同じ材料でもよいし、また上部電極11a用の膜を厚く形成するなどして、埋め込み層18を無くしてもかまわない。

【0099】

次に、図17Fに示すように、表面をCMP工程で平坦化する。それにより、抵抗変化素子1aの全てはホール9(開口部)に埋め込まれる。そのとき、下部電極13aは、ホール9の底部及び底部から側壁の途中まで連続的に形成されている。ただし、その端部は、ホール9の側壁の途中に在り、ホール9の上部に達していない。抵抗変化層12aは、下部電極13a上及びホール9の側壁上に形成されている。その端部は、ホール9の上部に達している。上部電極11aは、抵抗変化層12a上を内側から覆うように形成されている。その端部は、ホール9の上部に達している。

【0100】

その後、第1の実施の形態における図7H(ただし、第3ストッパ絶縁膜63の形成を除く)及び図7Iの工程を実施する。

【0101】

以上により、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置が製造される。

【0102】

なお、下部電極13a、抵抗変化層12a及び上部電極11aの材料に関しては、第1の実施の形態に記載のとおりである。

【0103】

本実施の形態により、第1の実施の形態と同様の効果を得ることができる。

また、選択CVD成長を行わず、通常の成膜方法を用いることができる。それにより、製造コストを削減することができる。また、本実施の形態も、第2の実施の形態のような半導体装置へ適用が可能である。

【0104】

本発明は上記各実施の形態に限定されず、本発明の技術思想の範囲内において、各実施の形態は適宜変形又は変更され得ることは明らかである。

【符号の説明】

【0105】

1、1a 抵抗変化型素子

2、2a 制御トランジスタ

3、3a 第1配線

4、4a コンタクト

5a ビア

6、6a 第2配線

8 共通線

9 ホール

11、11a 上部電極

11p 上部電極1

12、12a 抵抗変化層

13、13a 下部電極

13p 下部電極13の一部分

18 埋め込み層(金属)

21、21a ドレイン

22、22a ゲート

23、23a ゲート絶縁膜

24、24a ソース

25、25a サイドウォール

31、31a 第1メタル配線

32、32a バリアメタル層

34a ビア

35a バリアメタル層

37、37a 第2メタル配線

38、38a バリアメタル層

51 第1層間絶縁膜

52 第2層間絶縁膜

53 第3層間絶縁膜

54 第4層間絶縁膜

61 第1キャップ絶縁膜

62 第2キャップ絶縁膜

63 第3キャップ絶縁膜

70、70a 基板

71 素子分離層

90、90a 抵抗変化型不揮発記憶装置(抵抗変化型メモリ)

91 ロジックLSI

100 抵抗変化素子

101 抵抗変化素子

102 制御トランジスタ

103 第1配線

104 コンタクト

105 第1ビア

106 ビット線(又は第2配線)

108 共通線

111 上部電極

112 抵抗変化層

113 下部電極

114 電流パス

115 電流パス

116 電流パス

117 側部

121 ドレイン

122 ワード線(又はゲート)

123 ゲート絶縁膜

124 ソース

125 サイドウォール

131 銅(Cu)

132 バリアメタル

134 銅(Cu)

135 バリアメタル

151 第1層間絶縁膜

152 第2層間絶縁膜

153 第3層間絶縁膜

161 第1キャップ絶縁膜

162 第2キャップ絶縁膜

163 第3キャップ絶縁膜

170 半導体基板

171 素子分離領域

190 抵抗変化型メモリ

MC メモリセル

【技術分野】

【0001】

本発明は、抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の製造方法に関する。

【背景技術】

【0002】

不揮発性メモリの分野においては、フラッシュメモリ、強誘電体メモリ(Ferroelectric Random Access Memory;FeRAM)、磁気メモリ(Magnetic Random Access Memory;MRAM)、OUM(Ovonic Unified Memory)等の研究が盛んである。しかし、最近、これらの従来の不揮発性メモリと異なる不揮発性メモリとして、抵抗変化型メモリ(Resistance Random Access Memory;ReRAM)が提案されている。例えば、非特許文献1の抵抗変化型メモリは、電圧パルスの印加でメモリセルの抵抗変化層の抵抗値を設定することにより情報を書き込むことができる。加えて、抵抗値を非破壊で測定することにより情報を読み出すことができる。この抵抗変化型メモリは、メモリセルの面積が小さく、多値化が可能である。そのため、既存の不揮発性メモリをしのぐ可能性を有している。非特許文献1では、抵抗変化層としてPCMO(Pr0.7Ca0.3MnO3)及びYBCO(YBa2Cu3Oy)が用いられている。抵抗変化型メモリに関しては他の提案もなされている。例えば、非特許文献2の抵抗変化型メモリでは、抵抗変化層として約50nmの多結晶NiOx(x=1〜1.5)が用いられている。上部電極に正の電圧を印加することで、低抵抗状態もしくは高抵抗状態に変化する。また、例えば、非特許文献3の抵抗変化型メモリでは、抵抗変化層として80nmの微結晶TiO2が用いられている。

【0003】

一般的に、抵抗変化型メモリの1つのメモリセルは、1つの制御用トランジスタと1つの抵抗変化素子を備えている。そのようなメモリセルを有する抵抗変化型メモリは、1T1R型ともいわれている。図1は、従来の1T1R型の抵抗変化型メモリの構成を示す平面図である。1T1R型の抵抗変化型メモリ190は、複数のワード線(又はゲート)122と、複数のビット線(又は第2配線)106と、複数の共通線108と、複数のメモリセルMCとを具備している。複数のワード線(又はゲート)122は、Y方向に延在している。ビット線(又は第2配線)106は、X方向に延在している。共通線108は、Y方向に延在しいている。複数のメモリセルMCは、複数のワード線122と複数のビット線106との交点の各々に対応して設けられている。

【0004】

図2は、図1におけるa−a’断面の構成を示す断面図である。メモリセルMCの1個分の構成を示している。メモリセルMCは、制御トランジスタ102と、抵抗変化素子101とを備えている。半導体基板170上に素子分離領域171及び制御トランジスタ102が形成されている。制御トランジスタ102は、ゲート絶縁膜123、ゲート122(ワード線)、ドレイン121、ソース124、サイドウォール125を備えている。ドレイン121、ソース124にはコンタクト104が接続されている。制御トランジスタ102及びコンタクト104は第1層間絶縁膜151及び第1キャップ絶縁膜161に覆われている。ドレイン121側のコンタクト104は、第1キャップ絶縁膜161の開口部を介して、バリアメタル132と銅(Cu)131からなる第1配線103に接続されている。第1配線103は、第2層間絶縁膜152及び第2キャップ絶縁膜162に覆われている。抵抗変化型メモリの抵抗変化素子101は、第2キャップ絶縁膜162の開口部を介して、第1配線103に接続されている。抵抗変化素子101は、第1配線103と接続される下部電極113、下部電極113上の抵抗変化層112及び抵抗変化層112上の上部電極111からなるMIM(Metal/Insulator/Metal)構造を有している。上部電極111は、バリアメタル135と銅(Cu)134からなる第1ビア105及び第2配線106(ビット線)に接続されている。ソース124側のコンタクト104は、第1キャップ絶縁膜161の開口部を介して、共通線108に接続されている。抵抗変化素子101は、第3層間絶縁膜153及び第3キャップ絶縁膜163に覆われている。第2配線106は第3キャップ絶縁膜163上に設けられている。図2に示すように、従来構造では、抵抗変化素子101が、配線層の間(ここでは第1配線103の配線層と第2配線106の配線層との間)に形成されている。この場合、抵抗変化素子101は、隣接するメモリセルMCの抵抗変化素子101とは孤立したMIMキャパシタ構造を有している。そのため、抵抗変化素子101は(寄生)容量を有していると見ることもできる。

【0005】

従来構造の動作方法について説明する。まず、初期化については、以下のようにして行う。第2配線106を介して上部電極111に正の電圧を印加し、抵抗変化層112を低抵抗化(Forming)する。このとき、ゲート122に印加する電圧を調整して、制御トランジスタ102の飽和電流値によって電流制限がかかるようにする。それにより、抵抗変化層112は所望の抵抗値になる。なお、Formingは、上部電極111の替わりに下部電極113に正の電圧を印加して行っても良い。

【0006】

次に、書き込みについては、以下のようにして行う。低抵抗状態から高抵抗状態へのスイッチングには、ソース124及びゲート122に正の電圧を印加する。高抵抗状態から低抵抗状態へのスイッチングには、上部電極111及びゲート122に正の電圧を印加する。このとき、共通線108には高抵抗状態へのスイッチングのときよりも高い電圧を印加する。また、ゲート122に印加する電圧を調整して、制御トランジスタ102の飽和電流値による電流制限がかかるようにする。それにより、抵抗変化層112は所望の抵抗値になる。なお、高抵抗状態から低抵抗状態へのスイッチング及び低抵抗状態から高抵抗状態のスイッチングにおいて、ソース124の替わりに上部電極111に正の電圧を印加してもスイッチング動作を行うことができる。

【0007】

関連する技術として、特開2009−117668号公報に不揮発性メモリ用可変抵抗およびその製造方法並びに不揮発性メモリが開示されている。この不揮発性メモリ用可変抵抗は、層間絶縁膜と、下部電極と、可変抵抗層と、上部電極と、第2配線層とを具備する。層間絶縁膜は、第1配線層上に設けられ、第1配線層に接続する貫通孔を有する。下部電極は、貫通孔内に設けられ第1配線層に接続する。可変抵抗層は、貫通孔内に設けられ下部電極上に設けられている。上部電極は、貫通孔内に設けられ可変抵抗層上に設けられている。第2配線層は、層間絶縁膜上に設けられ、上部電極と接続する。また、不揮発性メモリ用可変抵抗は、可変抵抗層と、層間絶縁膜と、プラグ金属を具備する。可変抵抗層は、第1配線層表面に設けられている。層間絶縁膜は、第1配線層上に設けられている。プラグ金属は、層間絶縁膜内に設けられ可変抵抗層に接続する。

【0008】

また、特開2010−027753号公報に不揮発性記憶素子およびその製造方法が開示されている。この不揮発性記憶素子は、第1の電極と、層間絶縁膜と、開口部と、抵抗変化膜と、第2の電極とを備えている。第1の電極は、基板上に形成されている。層間絶縁膜は、第1の電極上に形成されている。開口部は、層間絶縁膜を貫通するように形成されている。抵抗変化膜は、開口部の少なくとも底部に形成されかつ第1の電極と接続されている。第2の電極は、抵抗変化膜に隣接して形成されかつ開口部の内部に充填されている。第1の電極と第2の電極とに挟まれた抵抗変化膜が、電気的パルスの印加により抵抗値を増加または減少する特性を有する記憶部を構成する。抵抗値の変化により情報を記憶または読み出しを行う。すなわち、第1の電極は第1の配線でもある。第1の電極上には開口部が形成されている。その開口部の底部及び内壁には抵抗変化層が形成されている。抵抗変化層の内側に第2の電極が埋め込まれている。

【0009】

また、特開2009−295842号公報に半導体メモリ装置及びその製造方法が開示されている。この半導体メモリ装置は、層間絶縁膜と、導電パターンと、下部電極と、遷移金属酸化物膜と、上部電極とを備えている。層間絶縁膜は、基板上方に形成され、溝を有する。導電パターンは、溝に囲まれた層間絶縁膜に埋め込まれている。下部電極は、導電パターン上及び溝の側壁の少なくとも一部に形成されている。遷移金属酸化物膜は、下部電極の上に形成されている。上部電極は、導電パターン上及び溝の側壁の少なくとも一部において遷移金属酸化物膜の上に形成されている。

【0010】

また、特開2006−128680号公報に、集積回路内での金属層の選択的形成が開示されている。この集積回路中に導電層を選択的に形成するための方法は、銅から成る第1表面、及び第2表面を与える工程と、第1表面及び第2表面を貴金属の気相化合物と接触させる工程であって、それによって貴金属から成る導電層を第2表面と比較して第1表面上に選択的に形成するところの工程とから成る。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2009−117668号公報

【特許文献2】特開2010−027753号公報

【特許文献3】特開2009−295842号公報

【特許文献4】特開2006−128680号公報

【非特許文献】

【0012】

【非特許文献1】W.W.Zhuang et al.,“Novell Colossal Magnetoresistive Thin Film Nonvolatile Resistance Random Access Memory(RRAM)”,IEDM,論文番号7.5,pp.193−196,2002.

【非特許文献2】G.−S.Park et al.,“Observation of electric−field induced Ni filament channels in polycrystalline NiOx film”,APL,Vol.91,pp.222103,2007.

【非特許文献3】C.Yoshida et al.,“High speed resistive switching in Pt/TiO2/TiN film for nonvolatile memory application”,APL,Vol.91,pp.223510,2007.

【非特許文献4】J.F.Gibbons et al.,“Switching properties of thin NiO Films”,Solid State Electronics,vol.7,pp.785,1964.

【非特許文献5】K.Kinoshita et al.,“Bias polarity dependent data retention of resistive random access memory consisting of binary transition metal oxide”,APL,vol.89,pp.103509,2006.

【発明の概要】

【発明が解決しようとする課題】

【0013】

従来構造の抵抗変化型メモリの抵抗変化素子は、MIM構造の加工時に側壁部に加わるダメージにより、以下のような課題がある。

【0014】

図3A〜図3Bは、抵抗変化型メモリのスイッチンッグ原理を説明したものである(非特許文献4、非特許文献5)。図3Aに示すように、抵抗変化型メモリの抵抗変化素子は、上部電極111(例示:金属)、抵抗変化層112(例示:遷移金属酸化物)及び下部電極113(例示:金属)を備えている。ここで、図3Bに示すように、抵抗変化素子は、上部電極111に電圧を印加されて低抵抗化(Forming)された状態では、抵抗変化層112中に電流パス114が形成されている。この電流パス114が形成されている状態で、上部電極111と下部電極113との間に電圧を印加することによって、電流パス114内で酸化還元反応が起きる。その結果、電流パス114の抵抗値が変化する。

【0015】

図4は、抵抗変化型メモリの問題点を示す図である。抵抗変化素子の電流パス114の抵抗値の変化は、この電流パス114の上下電極界面付近における酸化還元によっておこると考えられている。しかし、図4に示すように、実際に形成される電流パスは1抵抗変化素子あたり1本だけでなく、不完全な電流パス116も含めて抵抗変化層112中の様々な場所で形成される。特に、エッチングダメージの入っている側部117で電流パス115が形成されやすい。抵抗化(Forming)後のスイッチング動作において、これらの不完全な電流パス116やダメージの入った側部117付近の電流パス115が導通した場合、抵抗値が急激にさがり、誤動作の原因となる。特に、ダメージの入った側部117付近の電流パス115のスイッチング特性は、ダメージの入っていない電極中心付近の電流パス114のスイッチング特性と異なる。そのため、抵抗変化素子性能のバラツキや信頼性が大幅に劣化する。

【0016】

このように、抵抗変化層の膜質や抵抗変化層の有効領域と抵抗変化層の端部との位置関係によって、抵抗変化素子性能のバラツキや信頼性が大幅に劣化する。

【0017】

また、図1及び図2に示されるように、1つのビット線106に対して複数のメモリセルMCが接続されている。そのため、高速化のためには、メモリセルMCの面積を縮小して寄生容量を低減する必要がある。しかし、メモリセルMCは孤立したMIM構造を有しているので、その縮小パターニングは非常に困難である。第2キャップ絶縁膜162の開口部との目ずれ許容度を考慮しても、抵抗変化素子101の素子面積の縮小による容量低減は困難である。

【0018】

また、従来構造では、配線層間(ここでは第1配線103及び第2配線106)に、MIM構造の抵抗変化素子101と、上部電極111と第2配線106とをつなぐビア105が形成されており、配線層間の厚さがスケーリングによって小さくなった場合、抵抗変化素子101の形成が困難である。更に、従来構造ではロジックLSIに混載しようとした場合、最低でも2回のPR工程(第2キャップ絶縁膜162の開口及びMIM構造のパターニング)の追加が必要であり、製造コストの低減が困難である。

【0019】

特開2009−117668号公報(特許文献1)では、貫通孔の内部において、下方に下部電極が形成され、下部電極の表面に抵抗変化層が形成され、抵抗変化層の表面に上部電極が形成されている。抵抗変化層は、例えば下部電極の表面を酸化して形成されている(特許文献1の図10〜図12、図14〜図15)。この方法を用いた実施例では、貫通孔の断面と抵抗変化層、上部電極及び下部電極の断面とが同じになる。すなわち、基板に平行な断面において、抵抗変化層の端部まで、抵抗変化素子の有効領域となっている。そのため、その端部に起因した特性ばらつきが懸念される(上述の図4で指摘された問題点)。更に、下部電極の金属成分と抵抗変化層の金属成分とが同じになるという制約がある。また、抵抗変化層は、例えば下部電極の表面に別の膜を成膜して形成されている(特許文献1の図13)。この方法を用いた実施例では、抵抗変化層における基板に平行な断面の端部は、抵抗変化素子の有効領域から離れている。従って、その端部に起因した特性ばらつきは小さい。しかし、第2配線層と層間絶縁層との間に抵抗変化層が入るため、配線層の厚さがスケーリングによって小さくなった場合、第2配線層の形成が困難となる問題がある。また、抵抗変化層は、例えば下部電極及びバリア層の表面に別の膜を成膜して形成されている(特許文献1の図16)。この方法を用いた実施例では、抵抗変化層の端部は、抵抗変化素子の有効領域から離れている。従って、その端部に起因した特性ばらつきは小さい。しかし、上部電極と抵抗変化層とバリア層とが寄生容量を形成することが問題となる。

【0020】

また、特開2010−027753号公報(特許文献2)では、開口部内に設けられているのは抵抗変化層及び第2の電極(上部電極)だけで、第1の電極(下部電極)は開口部の外側に設けられている。第1の電極は、第1の配線でもある。そのため、第1の電極(=第1の配線)の材料には制約がある。また、第1の配線(=第1の電極)の材料として、抵抗変化素子に最適な特性を有する材料を用いた場合、配線形成のプロセスが従来のプロセスから変更されることになり、製造プロセスを再検討する必要が有り、製造コストの上昇が懸念される。

【0021】

また、特開2009−295842号公報(特許文献3)では、貫通孔又は開口部のビアや配線とは別にMIM構造を形成している。そのため、MIM構造分の高さを下げることはできない。したがって、配線層間の厚さがスケーリングによって小さくなった場合、MIM構造の形成が困難である。また、ダミーの溝を必要とする点からも、スケーリングが困難である。

【課題を解決するための手段】

【0022】

以下に、発明を実施するための形態で使用される番号・符号を用いて、課題を解決するための手段を説明する。これらの番号・符号は、特許請求の範囲の記載と発明を実施するための形態との対応関係を明らかにするために括弧付きで付加されたものである。ただし、それらの番号・符号を、特許請求の範囲に記載されている発明の技術的範囲の解釈に用いてはならない。

【0023】

本発明の抵抗変化型不揮発性記憶装置は、第1配線(3)と、層間絶縁層(53)と、第2配線(6)と、抵抗変化型素子(1、1a)とを具備している。層間絶縁層(53)は、第1配線(3)上に形成されている。第2配線(6)は、層間絶縁膜(53)上に形成されている。抵抗変化型素子(1、1a)は、第1配線(3)と第2配線(6)との間に形成されている。層間絶縁層(53)は、第1配線(3)と第2配線(6)とに挟まれるように形成され、第1配線(3)の幅以下の幅を有するホール(9)を備えている。抵抗変化型素子(1、1a)は、下部電極(13、13a)と、抵抗変化層(12、12a)と、上部電極(11、11a)とを備えている。下部電極(13、13a)は、第1配線(3)と接して、ホール(9)の底部に形成されている。抵抗変化層(12、12a)は、下部電極(13、13a)上に形成されている。上部電極(11、11a)は、抵抗変化層(12、12a)上に形成されている。下部電極(13、13a)、抵抗変化層(12、12a)及び上部電極(11、11a)は、ホール(9)の内部に形成されている。第1配線(3)は銅を含み、下部電極(13、13a)はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

【0024】

本発明の抵抗変化型不揮発性記憶装置は、第1配線(3)と、層間絶縁層(53)と、第2配線(6)と、抵抗変化型素子(1、1a)とを具備している。層間絶縁層(53)は、第1配線(3)上に形成されている。第2配線(6)は、層間絶縁膜(53)上に形成されている。抵抗変化型素子(1、1a)は、第1配線(3)と第2配線(6)との間に形成されている。層間絶縁層(53)は、第1配線(3)と第2配線(6)とに挟まれるように形成され、第1配線(3)の幅以下の幅を有するホール(9)を備えている。抵抗変化型素子(1、1a)は、下部電極(13、13a)と、抵抗変化層(12、12a)と、上部電極(11、11a)とを備えている。下部電極(13、13a)は、第1配線(3)と接して、ホール(9)の底部に形成されている。抵抗変化層(12、12a)は、下部電極(13、13a)上に形成されている。上部電極(11、11a)は、抵抗変化層(12、12a)上に形成されている。下部電極(13、13a)、抵抗変化層(12、12a)及び上部電極(11、11a)は、ホール(9)の内部に形成されている。抵抗変化層(12、12a)及び上部電極(13、13a)の端部は、第2配線(6)の底面と接している。

【0025】

本発明の半導体装置は、複数の抵抗変化型不揮発性記憶装置(90/90a)と、複数の抵抗変化型不揮発性記憶装置(90/90a)を用いる論理回路(91)とを具備している。ただし複数の抵抗変化型不揮発性記憶装置(90/90a)は上記各段落に記載されている。

【0026】

本発明の抵抗変化型不揮発性記憶装置の製造方法は、第1配線(3)上に形成された層間絶縁層(53)中に、第1配線(3)の幅以下の幅を有するホール(9)を形成する工程と、ホール(9)の内部に抵抗変化型素子(1、1a)を形成する工程と、抵抗変化型素子(1、1a)と接するように抵抗変化型素子(1、1a)上に第2配線(6)を形成する工程とを具備している。抵抗変化型素子(1、1a)を形成する工程は、第1配線(3)と接して、ホール(9)の底部に下部電極(13、13a)を形成する工程と、下部電極(13、13a)上に抵抗変化層(12、12a)用の第1膜を形成する工程と、第1膜上に上部電極(11、11a)用の第2膜を形成する工程と、層間絶縁層(53)上の第1膜及び第2膜を除去する工程とを備えている。第1配線(3)は銅を含み、下部電極(13、13a)はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含んでいる。

【0027】

本発明の抵抗変化型不揮発性記憶装置の製造方法は、第1配線(3)上に形成された層間絶縁層(53)中に、第1配線(3)の幅以下の幅を有するホール(9)を形成する工程と、ホール(9)の内部に抵抗変化型素子(1、1a)を形成する工程と、抵抗変化型素子(1、1a)と接するように抵抗変化型素子(1、1a)上に第2配線(6)を形成する工程とを具備している。抵抗変化型素子(1、1a)を形成する工程は、第1配線(3)と接して、ホール(9)の底部に下部電極(13、13a)を形成する工程と、下部電極(13、13a)上に抵抗変化層(12、12a)用の第1膜を形成する工程と、第1膜上に上部電極(11、11a)用の第2膜を形成する工程と、層間絶縁層(53)上の第1膜及び第2膜を除去する工程とを備えている。抵抗変化層(12、12a)及び上部電極(11、11a)の端部は、第2配線(6)の底面と接する。

【発明の効果】

【0028】

本発明により、安定したスイッチング動作を低コストで実行することができる。また、本発明により、動作速度を向上させることができる。また、本発明により、デバイススケーリングの問題を回避可能である。また、ロジックLSI等との混載が可能であり、製造コストも下げられる。

【図面の簡単な説明】

【0029】

【図1】図1は、従来の1T1R型の抵抗変化型メモリの構成を示す平面図である。

【図2】図2は、図1におけるa−a’断面の構成を示す断面図である。

【図3A】図3Aは、抵抗変化型メモリのスイッチンッグ原理を説明したものである。

【図3B】図3Bは、抵抗変化型メモリのスイッチンッグ原理を説明したものである。

【図4】図4は、抵抗変化型メモリの問題点を示す図である。

【図5】図5は、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の主要部の構成を示す断面図である。

【図6】図6は、低抵抗化(Forming)後の抵抗変化素子の構成を示す断面図である。

【図7A】図7Aは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7B】図7Bは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7C】図7Cは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7D】図7Dは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7E】図7Eは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7F】図7Fは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7G】図7Gは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7H】図7Hは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図7I】図7Iは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図8】図8は、本発明の第2の実施の形態に係る半導体装置の構成を示す平面図である。

【図9A】図9Aは、本発明の第2の実施の形態に係る半導体装置における抵抗変化型不揮発記憶装置の領域の構成を示す断面図である。

【図9B】図9Bは、本発明の第2の実施の形態に係る半導体装置におけるロジックLSIの領域の構成を示す断面図である。

【図10A】図10Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図10B】図10Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図11A】図11Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図11B】図11Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図12A】図12Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図12B】図12Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図13A】図13Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図13B】図13Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図14A】図14Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図14B】図14Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図15A】図15Aは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図15B】図15Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。

【図16】図16は、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の主要部の構成を示す断面図である。

【図17A】図17Aは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図17B】図17Bは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図17C】図17Cは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図17D】図17Dは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図17E】図17Eは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【図17F】図17Fは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【発明を実施するための形態】

【0030】

以下、本発明の抵抗変化型不揮発記憶装置、半導体装置及び抵抗変化型不揮発記憶装置の製造方法の実施の形態に関して、添付図面を参照して説明する。

【0031】

(第1の実施の形態)

本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の構成について、添付図面を参照して説明する。図5は、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の主要部の構成を示す断面図である。抵抗変化型不揮発記憶装置90は、基板70aと、第1キャップ絶縁膜61と、第1配線3と、第2層間絶縁膜52と、第2キャップ絶縁膜62と、抵抗変化型素子1と、第3層間絶縁膜53と、第3キャップ絶縁膜63と、第2配線6と、第4層間絶縁膜54とを具備している。

【0032】

第1配線3は、基板70a上に設けられている。第1配線3は、例えば第1メタル配線31とそれを側方及び底面において覆うバリアメタル層32とを備えている。ただし、基板70aは、表面領域に素子を形成された半導体基板と、その半導体基板を覆う第1層間絶縁膜や第1キャップ絶縁膜61を備えている。第1層間絶縁膜及び第1キャップ絶縁膜61は第1層間絶縁層ということもできる。従って、第1配線3は、第1層間絶縁層上に設けられている。第1配線3は、第2層間絶縁膜52に埋設され、第2キャップ絶縁膜62に覆われている。第2層間絶縁膜52及び第2キャップ絶縁膜62は第2層間絶縁層ということもできる。従って、第1配線3は、第2層間絶縁層に埋設されている。

【0033】

第3層間絶縁膜53は、第2層間絶縁層上に設けられている。第3層間絶縁膜53は、ホール9を備えている。ホール9は、第1配線3と第2配線6とに挟まれるように、第3層間絶縁層53を貫通するように設けられている。ホール9の底面は、第1配線3の上面に接していて、その上面からはみ出していない。ホール9の横断面(基板70aの表面に平行な面)が円形の場合、その断面の直径は第1配線3の配線幅以下である。ただし、ホール9の底面が第1配線3の上面からはみ出さなければ、ホール9の横断面は他の形を有していても良い。その場合、ホール9の幅(基板70aの表面に平行な方向)は第1配線3の配線幅以下である。第3キャップ絶縁膜63は、第3層間絶縁膜53上に設けられている。第3層間絶縁膜53及び第3キャップ絶縁膜63は第3層間絶縁層ということもできる。

【0034】

抵抗変化型素子1は、抵抗値の変化で情報を記憶する。第1配線3と第2配線6との間に形成されたホール9内に設けられている。抵抗変化型素子1は、下部電極13と、抵抗変化層12と、上部電極11とを備えている。

【0035】

下部電極13は、ホール9の底部のみに形成されている。その端部は、ホール9の底部近傍の側壁に接している。下部電極13は、金属の導体で形成されている。下部電極13は、第2層間絶縁層の開口部の第1配線3(第1メタル配線31)上に選択成長で形成されていることが好ましい。追加プロセスを要せずに、下部電極13をホール9内のみに形成できるからである。その形成方法については後述される。

【0036】

抵抗変化層12は、下部電極13上及びホール9の側壁上に形成されている。その端部は、ホール9の上部に達している。その端部は、第2配線6の底面に接していることが好ましい。それにより、抵抗変化層12の端部と下部電極13の端部とを大きく隔てることができる。その結果、後述されるように、抵抗変化素子1は、抵抗変化層12の端部の影響を受け難くなる。抵抗変化層12は、下部電極13とは異なる金属材料を用いた酸化物を含むことができる。

【0037】

上部電極11は、抵抗変化層12上を内側から覆うように形成されている。その端部は、ホール9の上部に達している。その端部は、第2配線6の底面に接していることが好ましい。抵抗変化素子1と第2配線6とを接続するためのビアやコンタクトを別途製造する必要が無いからである。上部電極11は、金属の導体で形成されている。上部電極11は、その更に内側の領域を埋める埋め込み層(金属)18を備えていても良い。

【0038】

第2配線6は、第3層間絶縁膜53上に設けられている。第2配線6は、例えば第2メタル配線37とそれを側面及び底面において覆うバリアメタル層38とを備えている。第2配線層6は、第3層間絶縁層上に設けられていてもよい。第2配線6は、第4層間絶縁膜54に埋設されている。

【0039】

第1メタル配線31は、基板表面に垂直な方向において(111)方位へ配向した結晶粒を主成分として含む多結晶膜であることが好ましい。すなわち、第1メタル配線31は、(111)配向性を有する膜であることが好ましい。後述されるように下部電極13を選択成長させ易いからである。例えば、第1メタル配線31として(111)配向性を有する銅(Cu)配線を用いた場合、下部電極13としては例えば(002)配向性を有するルテニウム(Ru)膜を選択成長させることができる。ただし、主成分は、最も多い成分である。

【0040】

第1メタル配線31は、銅(Cu)、アルミニウム(Al)、シリコン(Si)が考えられる。第1メタル配線31として銅(Cu)及びアルミニウム(Al)を用いる場合、第1メタル配線31及びホール9はそれぞれ通常の配線及びビアホールが想定される。第1メタル配線31としてシリコンを用いる場合、第1メタル配線31及びホール9はそれぞれソース/ドレイン及びコンタクトホールが想定される。後述される製造方法の例では、(111)配向の銅(Cu)を用いている。

【0041】

下部電極13は、第1メタル配線31が銅(Cu)の場合、主成分としてルテニウム(Ru)、タングステン(W)、コバルト(Co)、白金(Pt)、金(Au)、ロジウム(Rh)、イリジウム(Ir)及びパラジウム(Pd)からなる群から選択された少なくとも1種の金属を含有することが好ましい。下部電極13を選択成長させやすいからである。このうち、ルテニウム(Ru)、タングステン(W)、コバルト(Co)、白金(Pt)は、抵抗変化素子1の下部電極13の材料として特に好ましい。後述される製造方法の例では、(111)配向の銅(Cu)の第1メタル配線31との結晶整合性に優れているものとして、(002)配向のルテニウム(Ru)の下部電極13を用いている。

【0042】

また、下部電極13は、第1メタル配線31がアルミニウム(Al)の場合、主成分としてタングステン(W)、タンタル(Ta)及びチタニウム(Ti)からなる群から選択される少なくとも1種の金属を含有することが好ましい。下部電極13を選択成長させやすいからである。

【0043】

また、下部電極13は、第1メタル配線31がシリコン(Si)の場合、主成分としてタングステン(W)、タンタル(Ta)及びチタニウム(Ti)からなる群から選択される少なくとも1種の金属を含有することが好ましい。下部電極13を選択成長させやすいからである。

【0044】

上部電極は、例えば、チタニウム(Ti)、窒化チタニウム(TiN)、アルミニウム(Al)、ニッケル(Ni)、銅(Cu)、銅アルミニウム(CuAl)、タンタル(Ta)、窒化タンタル(TaN)、ジルコニウム(Zr)、ハフニウム(Hf)、モリブデン(Mo)、ルテニウム(Ru)、白金(Pt)などによって形成できる。また、これらの材料の積層体であっても良い。後述される製造方法の例では、窒化チタニウム(TiN)を用いている。

【0045】

抵抗変化層12は酸化チタニウム(TiO2)、酸化鉄(FeO)、酸化ニッケル(NiO)、酸化ジルコニウム(ZrO2)、酸化銅(CuO)、酸化ハフニウム(HfO2)、酸化タンタル(Ta2O5)、酸化タングステン(WO)、及びこれらの窒化物やシリケートを少なくとも含む単層膜若しくは積層膜が好ましい。後述される製造方法の例では、酸化ニッケル(NiO)を用いている。

【0046】

第1〜第4層間絶縁膜51〜54の材料としては、酸化シリコン(SiO2)が例示される。第1〜第3キャップ絶縁膜61〜63の材料としては、窒化シリコンSiNxが例示される。

【0047】

図6は、低抵抗化(Forming)後の抵抗変化素子の構成を示す断面図である。抵抗変化素子1を拡大して示している。抵抗変化素子1では、下部電極13と上部電極11とに挟まれた(下部電極13と上部電極11とが重なった)領域が、抵抗変化層12における有効領域Aである。有効領域Aは、電流パス14が生成される可能性のある領域である。この図6の場合、上部電極11と下部電極13とは、その一部しか重なっていない。すなわち、上部電極11の一部分11pと下部電極13の一部分13pとが重なっているだけである。この重なった領域が、抵抗変化層12における有効領域A(α1からα2まで)である。図に示されるように、この有効領域Aは、ホール9(ビアホール又はコンタクトホール)の底部における周辺を除いた領域にしかない。すなわち、その有効領域Aの境界α1、α2は、ホール9の側壁や、下部電極13の端部や、抵抗変化層12の端部や、上部電極11の端部から離れている。そのため、電流パスはホール9の底部における周辺を除いた領域にしかできなくなる。したがって、電流パスはホール9の側壁や、下部電極13の端部や、抵抗変化層12の端部や、上部電極11の端部の影響を受けることはない。言い換えると、抵抗変化層12の端部は第3層間絶縁膜53の上側表面と概ね同じ面にあり、上部電極11と下部電極13と挟まれていない。そのため、ダメージの入っている抵抗変化層12の端部17に電流パスが形成されることはない。したがって、抵抗変化型メモリのバラツキ及び信頼性が向上する。

【0048】

また、本実施の形態では、既述のように上部電極11と下部電極13とは、一部しか重なっていない(有効領域A)。そのため、MIM構造を有する抵抗変化素子1の容量を、従来構造と比較して小さくすることができる。その結果、ビット線の寄生容量が減少するので、書き換え動作及び読み出し動作の高速化が可能となる。

【0049】

また、本実施の形態では、図4に示されるように、ホール9内に抵抗変化素子1が埋め込まれ、上部電極11の上端の位置が第2配線6の下面の位置と概ね同じである。そのため、新たに上部電極11と接続するためのビアやコンタクトを新たに形成する必要がない。更に、図4に示すような本実施の形態の抵抗変化型メモリを用いることでMIM構造の高さに起因したスケーリングの問題を回避することができる。

【0050】

次に、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の動作方法について、図5を参照して説明する。

まず、低抵抗化(Forming)を行うため、上部電極11に正の電圧を印加し、抵抗変化層12を低抵抗化する。なお、低抵抗化(Forming)は、上部電極11の代わりに下部電極13に正の電圧を印加しても良い。次に、低抵抗状態から高抵抗状態へのスイッチングのときには、上部電極11に正の電圧を印加する。この場合、低抵抗化(Forming)の場合よりも電流が流れるように、負荷抵抗の抵抗を下げておくことが好ましい。一方、高抵抗状態から低抵抗状態へのスイッチングのときには、上部電極11に正の電圧を印加する。この場合、上部電極11には高抵抗状態へのスイッチングの場合よりも高い電圧を印加する。また、低抵抗化(Forming)の場合と同様に抵抗変化素子1に負荷抵抗をつけておき、低抵抗化後に電流が流れすぎないようにしておくのが好ましい。なお、高抵抗状態から低抵抗状態へのスイッチングのときにも、上部電極11の代わりに下部電極13に正の電圧を印加しても良い。

【0051】

次に、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法について説明する。図7A〜図7Iは、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【0052】

まず、図7Aに示すように、基板70aが準備される。基板70aは、半導体基板の表面領域に形成された素子と、それを覆う第1層間絶縁膜及び第1キャップ絶縁膜61とを備えている。次に、基板70a上に第2層間絶縁膜52を形成する。第1キャップ絶縁膜61としては、ここではシリコン窒化膜(SiNx)を用いる。第1層間絶縁膜及び第2層間絶縁膜52としては、ここではシリコン酸化膜(SiO2)を用いる。それぞれ、プラズマCVD(Chemical Vapor Deposition)法を用いて堆積する。

【0053】

次に、図7Bに示すように、PR(Photoresist)工程とドライエッチング工程により、第2層間絶縁膜52に溝を形成する。その後、バリアメタル層32用の膜及び第1メタル配線31用の膜を形成する。バリアメタル層32用の膜としては、ここではタンタル窒化膜(TaN)を用いる。第1メタル配線31用の膜としては、ここでは銅(Cu)を用いる。タンタル窒化膜(TaN)はスパッタ法を用いて堆積する。銅(Cu)はスパッタ法及びメッキ法を用いて堆積する。その後、CMP(Chemical Mechanical Polishing)工程を用いて、表面の平坦化を行い、第1配線3としての銅(Cu)配線を形成する。

【0054】

続いて、図7Cに示すように、表面に第2キャップ絶縁膜62及び第3層間絶縁膜53を形成する。第2キャップ絶縁膜62としては、ここではシリコン窒化膜(SiNx)を用いる。第3層間絶縁膜53としては、ここではシリコン酸化膜(SiO2)を用いる。それぞれ、プラズマCVD(Chemical Vapor Deposition)法を用いて堆積する。

【0055】

その後、図7Dに示すように、PR工程とドライエッチング工程を用いて、第3層間絶縁膜53及び第2キャップ絶縁膜62にホール(開口部)9を設ける。それにより、第1配線3(Cu配線)の表面が露出する。すなわち、第1配線3の銅(Cu)が露出する。

【0056】

次に、図7Eに示すように、ホール9の銅(Cu)の露出した部分にルテニウム(Ru)を所定の膜厚で選択CVD法により形成する。すなわち、ホール9の底部に、第1配線3と接してルテニウム(Ru)を選択成長させる。具体的には、例えば、ルテニウムの有機金属化合物(例示:Ru3(CO)12)を用いた熱CVD法(例示:プロセスガスはCOガス)により形成することができる。そのルテニウム(Ru)は下部電極13となる。この下部電極13は、ホール9の底部にのみ存在しており、その端部はホール9の内側の側壁に接している。

【0057】

なお、下部電極13として、他の金属、例えば、タングステン(W)、コバルト(Co)、白金(Pt)、金(Au)、ロジウム(Rh)、イリジウム(Ir)及びパラジウム(Pd)からなる群から選択された少なくとも1種の金属を用いる場合にも、同様に、その金属を含む有機金属化合物を用いた熱CVD法により形成することが可能である。

【0058】

なお、第1配線3としてアルミニウム(Al)配線(若しくはチタニウム窒化膜(TiN)/アルミニウム(Al)積層配線)、又は、シリコン(Si)基板(例示:ソース/ドレイン)を用い、下部電極13としてタングステン(W)、タンタル(Ta)及びチタニウム(Ti)のうちのいずれかを用いる場合には、例えば以下の方法を用いることができる。すなわち、それぞれ原料ガスとして六フッ化タングステン、四塩化チタン及び五フッ化タンタルを用いた熱CVD法により下部電極13を形成する。

【0059】

続いて、図7Fに示すように、第3層間絶縁膜53の表面、ホール9の内部の側壁及び下部電極13の表面を覆うように、抵抗変化層12用の膜、上部電極11用の膜及び埋め込み層18用の膜を形成する。抵抗変化層12用の膜としては、ここではニッケル酸化膜(NiO)を用いる。上部電極13用の膜としては、ここではチタニウム窒化膜(TiN)を用いる。埋め込み層18用の膜としては、ここではタングステン(W)を用いる。これらは、はスパッタ法で成膜される。なお、埋め込み層18は上部電極11と同じ材料でもよいし、また上部電極11用の膜を厚く形成するなどして、埋め込み層18を無くしてもかまわない。

【0060】

その後、図7Gに示すように、表面をCMP工程で平坦化する。それにより、抵抗変化素子1の全てはホール9(開口部)に埋め込まれる。そのとき、下部電極13は、ホール9の底部のみに形成されている。抵抗変化層12は、下部電極13上及びホール9の側壁上に形成されている。その端部は、ホール9の上部に達している。上部電極11は、抵抗変化層12上を内側から覆うように形成されている。その端部は、ホール9の上部に達している。

【0061】

次に、図7Hに示すように、表面に第3キャップ絶縁膜63及び第4層間絶縁膜54を形成する。第3キャップ絶縁膜63としては、ここではシリコン窒化膜(SiNx)を用いる。第4層間絶縁膜54としては、ここではシリコン酸化膜(SiO2)を用いる。それぞれ、プラズマCVD法を用いて堆積する。

【0062】

続いて、図7Iに示すように、PR工程とドライエッチング工程を用いて、第4層間絶縁膜54及び第3キャップ絶縁膜63に溝を形成する。それにより、上部電極11及び埋め込み層18が露出する。更に、バリアメタル層38用の膜及び第2メタル配線37用の膜を形成する。バリアメタル層38用の膜としては、ここではタンタル窒化膜(TaN)を用いる。第2メタル配線37用の膜としては、ここでは銅(Cu)を用いる。タンタル窒化膜(TaN)はスパッタ法を用いて堆積する。銅(Cu)はスパッタ法及びメッキ法を用いて堆積する。その後、CMP工程を用いて、表面の平坦化を行い、第2配線6としての銅(Cu)配線を形成する。

【0063】

以上により、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置90が製造される。

【0064】

本実施の形態では、抵抗変化層12の有効領域は、下部電極13と面したホール9の底部(周辺部を除く)の部分だけである。抵抗変化層12の端部は、ホール9の上端部へ延在してホール9の底部から離れている。そのため、抵抗変化層12の端部のダメージに起因した、抵抗変化素子1のばらつきを低減することができる。また、ホール9径で抵抗変化素子1の容量が決まるため、ホール9の径を小さくすることで、寄生容量を小さくすることができる。それにより、抵抗変化型メモリの高速動作が可能となる。更に、従来のMIM構造+ビア構造ではなく、ビアホールに相当するホール9内に抵抗変化素子1が埋め込まれているため、MIM構造の高さに起因したスケーリングの問題が回避できる。更に、1回のPR工程の追加で抵抗変化型不揮発素子をロジックLSI(後述)に混載可能であり、製造コストを低減することができる。

【0065】

(第2の実施の形態)

本発明の第2の実施の形態に係る抵抗変化型不揮発記憶装置の構成について、添付図面を参照して説明する。第2の実施の形態は、第1の実施の形態に係る抵抗変化型不揮発記憶装置90を1T1R(1トランジスタ1抵抗)型の抵抗変化型メモリ(ReRAM)に適用し、ロジックLSI(large−scale integration)91と混載した半導体装置に関する。以下、詳細に説明する。

【0066】

図8は、本発明の第2の実施の形態に係る半導体装置の構成を示す平面図である。ただし、この図では、半導体装置のうち抵抗変化型不揮発記憶装置90(1T1R型の抵抗変化型メモリ)の領域を示している。抵抗変化型不揮発記憶装置90は、複数のワード線(又はゲート)22と、複数のビット線(又は第2配線)6と、複数の共通線8と、複数のメモリセルMCとを具備している。複数のワード線(又はゲート)22は、Y方向に延在している。複数のビット線(又は第2配線)6は、X方向に延在している。複数の共通線8は、Y方向に延在しいている。複数のメモリセルMCは、複数のワード線22と複数のビット線6との交点の各々に対応して行列状に設けられている。

【0067】

図9Aは、本発明の第2の実施の形態に係る半導体装置における抵抗変化型不揮発記憶装置の領域の構成を示す断面図である。この図では、図8におけるb−b’断面の構成を示している。すなわち、メモリセルMCの1個分の構成を示している。抵抗変化型不揮発記憶装置90のメモリセルMCは、制御トランジスタ2と、抵抗変化素子1とを備えている。素子分離領域71で囲まれた領域において、半導体基板70上に及び制御トランジスタ2が形成されている。制御トランジスタ2は、ゲート絶縁膜23、ゲート22(ワード線)、ドレイン21、ソース24、サイドウォール25を備えている。ドレイン21、ソース24にはコンタクト4が接続されている。制御トランジスタ2及びコンタクト4は第1層間絶縁膜51及び第1キャップ絶縁膜61に覆われている。ドレイン21側のコンタクト4は、第1キャップ絶縁膜61の開口部を介して、バリアメタル層32と第1メタル配線31からなる第1配線3に接続されている。第1配線3は、第2層間絶縁膜52及び第2キャップ絶縁膜62に側面及び上面を覆われている。抵抗変化型メモリの抵抗変化素子1は、第2キャップ絶縁膜62の開口部を介して、第1配線3に接続されている。抵抗変化素子1は、第1配線3と接続される下部電極13、下部電極13上の抵抗変化層12及び抵抗変化層12上の上部電極11からなるMIM(Metal/Insulator/Metal)構造を有している。上部電極11内部には埋め込み層18が設けられていてもよい。上部電極11(及び埋め込み層18)は、バリアメタル層38と第2メタル配線37からなる第2配線6(ビット線)に接続されている。ソース24側のコンタクト4は、第1キャップ絶縁膜61の開口部を介して、共通線8に接続されている。抵抗変化素子1は、第3層間絶縁膜53及び第3キャップ絶縁膜63に側面を覆われている。第2配線6は第3層間絶縁膜53上に設けられている。第2配線6は、第4層間絶縁膜54に側面を覆われている。図9Aに示すように、本実施の形態では、抵抗変化素子1が、配線層の間(ここでは第1配線3の配線層と第2配線6の配線層との間)に設けられたホール9内に形成されている。抵抗変化素子1は、隣接するメモリセルMCの抵抗変化素子1とは孤立したMIMキャパシタ構造を有している。

【0068】

一方、半導体装置のうちロジックLSI91の領域は以下に示すとおりである。図9Bは、本発明の第2の実施の形態に係る半導体装置におけるロジックLSIの領域の構成を示す断面図である。この図では、ロジックLSI91における一つのトランジスタを含む領域を示している。素子分離領域71aで囲まれた領域において、半導体基板70上に制御トランジスタ2aが形成されている。制御トランジスタ2aは、ゲート絶縁膜23a、ゲート22a、ドレイン21a、ソース24a、サイドウォール25aを備えている。ドレイン21a、ソース24aにはコンタクト4aが接続されている。制御トランジスタ2a及びコンタクト4aは第1層間絶縁膜51及び第1キャップ絶縁膜61に覆われている。ドレイン21a側のコンタクト4aは、第1キャップ絶縁膜61の開口部を介して、バリアメタル層32aと第1メタル配線31aからなる第1配線3aに接続されている。第1配線3aは、第2層間絶縁膜52及び第2キャップ絶縁膜62に側面及び上面を覆われている。第1配線3aは、第2キャップ絶縁膜62の開口部を介して、バリアメタル層35aとビアメタル34aからなるビア5aに接続されている。ビア5aは、第3層間絶縁膜53及び第3キャップ絶縁膜63に側面を覆われている。ビア5aは、第3キャップ絶縁膜63の開口部を介して、バリアメタル層38aと第2メタル配線37aからなる第2配線6aに接続されている。第2配線6aは第3キャップ絶縁膜63上に設けられている。第2配線6aは、第4層間絶縁膜54に側面を覆われている。ソース24a側も同様である。図9A及び図9Bに示すように、基板70の表面領域及び各層の役割は、抵抗変化型メモリの領域と、ロジックLSIの領域とで同様である。

【0069】

図9Aの場合では、抵抗変化素子1を、第1配線3の配線層(第1配線層)と第2配線6の配線層(第2配線層)との間に形成している。しかし、抵抗変化素子1を、他の連続した二つの配線層の間に形成しても良い。更に、抵抗変化素子1を、連続しない二つの配線層の間(例示:第1配線層と第3配線層との間)に形成しても良い。更に、抵抗変化素子1を、コンタクト4内に形成してもよい。

【0070】

本実施の形態における第1配線3、抵抗変化素子1及び第2配線6のその他の構成や機能については、第1の実施の形態の場合と同様である。

【0071】

本実施の形態では、ロジックLSI領域でのビアホールに対応するホール9内に抵抗変化素子1が埋め込まれている。加えて、上部電極11の最上部の位置が第2配線6の下面の位置と同じである。そのため、上部電極11と第2配線6とを接続するためのビアを新たに形成する必要がない。更に、図9Aに示すような本実施の形態の抵抗変化型メモリを用いることでMIM構造の高さに起因したスケーリングの問題を回避することができる。また、本実施の形態の抵抗変化型メモリの構造はロジックLSIの領域の構造に影響を与えない。そのため、ロジックデバイスとの混載に有効である。

【0072】

更に、第1の実施の形態の図6に示されるように、下部電極13と上部電極11とに挟まれた領域が、抵抗変化層12における有効領域Aとなる。上部電極11と下部電極13とは、その一部しか重なっていない。そのため、従来構造と比較して、抵抗変化素子1の容量を小さくすることができる。その結果、ビット線(第2配線6)の寄生容量が減少し、書き換え・読み出し動作の高速化が可能となる。

【0073】

また、有効領域Aの境界はホール9の側壁や、下部電極13の端部や、上部電極11の端部に達していない。そのため、電流パスはホール9の底部における周辺を除いた領域にしかできなくなる。したがって、電流パスはホール9の側壁や、下部電極13の端部や、上部電極11の端部の影響を受けることはない。言い換えると、ダメージの入っている抵抗変化層12の端部17に不完全な電流パスが形成されることはない。したがって、抵抗変化型メモリのバラツキ及び信頼性が向上する。

【0074】

次に、本発明の第2の実施の形態に係る半導体装置の抵抗変化型不揮発記憶装置の動作方法について、は、第1の実施の形態と同様である。

【0075】

次に、本発明の第2の実施の形態に係る半導体装置の製造方法について説明する。図10A及び図10B〜図15A及び図15Bは、本発明の第2の実施の形態に係る半導体装置の製造方法を示す断面図である。ただし、図nA(n=10〜15の整数)は抵抗変化型不揮発記憶装置90の領域(以下「メモリ部」ともいう)であり、図nBはロジックLSI91の領域(以下「ロジック部」ともいう)である。

【0076】

まず、図10A及び図10Bに示すように、メモリ部及びロジック部において、半導体基板70上に、通常のMOSFET工程を用いて、素子分離層71、71a、ゲート22、22a、ゲート絶縁膜23、23a、ソース24、24a、ドレイン21、21a及びサイドウォール25、25aを形成する。ここでは、半導体基板70としてp−シリコン(Si)、ゲート絶縁膜23、23aとしてシリコン酸化膜(SiOx)、ゲート22、22aとしてポリシリコン膜(poly−Si)、ソース24、24a、ドレイン21、21aとしてn+シリコン(n+Si)、サイドウォール25、25aとしてシリコン窒化膜(SiNx)をそれぞれ用いる。

【0077】

次に、図11A及び図11Bに示すように、メモリ部及びロジック部において、全面に第1層間絶縁膜51用の膜を堆積し、CMP工程によって平坦化して、第1層間絶縁膜51を形成する。第1層間絶縁膜53としては、ここではシリコン酸化膜(SiOx)を用い、プラズマCVD法を用いて堆積する。更に、PR工程とドライエッチング工程を用いて、第1層間絶縁膜51に開口部を設ける。次に、その開口部にコンタクト4、4aを埋め込み、それぞれソース24、24a、ドレイン21、21aと接続する。コンタクト4、4aとして、ここではタングステン(W)を用い、スパッタ法を用いて成膜した。

【0078】

次に、図12A及び図12Bに示すように、メモリ部及びロジック部において、全面に第1キャップ絶縁膜61及び第2層間絶縁膜52を堆積する。第1キャップ絶得膜61としては、ここではシリコン窒化膜(SiNx)を用い、第2層間絶縁膜52としては、ここではシリコン酸化膜(SiOx)を用いる。更に、PR工程とドライエッチング工程により、第2層間絶縁膜52及び第1キャップ絶縁膜61に溝を形成する。その後、バリアメタル層32、32a用の膜及び第1メタル配線31、31a用の膜を堆積する。バリアメタル層32、32a用の膜としては、ここではタンタル窒化膜(TaN)を用い、スパッタ法を用いて成膜する。第1メタル配線31、31a用の膜としては、ここでは銅(Cu)を用い、スパッタ法及びメッキ法を用いて成膜する。更に、CMP工程を用いて、表面の平坦化を行い、第1配線3(32+31)、第1配線3a(32a+31a)を形成する。

【0079】

次に、図13A及び図13Bに示すように、メモリ部及びロジック部において、全面に第2キャップ絶縁膜62及び第3層間絶縁膜53を堆積する。第2キャップ絶縁膜62としてはここでは、シリコン窒化膜(SiNx)を用い、第3層間絶縁膜53としては、ここではシリコン酸化膜(SiOx)を用いる。それぞれ、プラズマCVD法を用いて堆積する。更に、メモリ部において、PR工程とドライエッチング工程を用いて、所定の領域のみ第3層間絶縁膜53及び第2キャップ絶縁膜62にホール9(開口部)を設ける。これにより、第1配線3の表面の銅(Cu)が露出する。更に、ホール9の銅(Cu)の露出部分に、ルテニウム(Ru)を選択CVD成長させる。このルテニウム(Ru)膜は、下部電極13となる。次に、全面に、抵抗変化層12用の膜、上部電極11用の膜及び埋め込み層18用の膜を堆積する。抵抗変化層12用の膜として、ここではTiO2とTa2O5の積層膜を用い、上部電極11用の膜として、ここではチタニウム窒化膜(TiN)を用い、埋め込み層18として、ここではタングステン(W)を用いる。なお、埋め込み層18用の膜は、上部電極11用の膜と同じ材料でもよく、また、埋め込み層を無くしてもかまわない。次に、表面をCMP工程で平坦化する。それにより、メモリ部において、抵抗変化素子1(下部電極13、抵抗変化層12及び上部電極11)がホール9に埋め込まれた構成が形成される。

【0080】

次に、図14A及び図14Bに示すように、メモリ部とロジック部において、全面に第3キャップ絶縁膜63及び第4層間絶縁膜54を堆積する。第3キャップ絶縁層63としては、ここではシリコン窒化膜(SiNx)を用い、第4層間絶縁膜54としては、ここではシリコン酸化膜(SiOx)を用いる。それぞれ、プラズマCVD法を用いて堆積する。

【0081】

次に、図15A及び図15Bに示すように、PR工程とドライエッチング工程を用いて、メモリ部において、第4層間絶縁膜54及び第3キャップ絶縁膜63に溝を形成し、ロジック部において、第4層間絶縁膜54に溝を形成し、第3キャップ絶縁膜63、第3層間絶縁膜53及び第2キャップ絶縁膜62にビアホールを形成する。それにより、メモリ部において上部電極11(及び埋め込み層18)が露出し、ロジック部において他の第1配線3aが露出する。その後、全面にバリアメタル層38、35a、38a用の膜、ビアメタル34a及び第2メタル配線37、37a用の膜を堆積する。バリアメタル層38、35a、38a用の膜としては、ここではタンタル窒化膜(TaN)を用い、スパッタ法を用いて成膜する。ビアメタル34a及び第2メタル配線37、37a用の膜としては、ここでは銅(Cu)を用い、スパッタ法及びメッキ法を用いて成膜する。更に、CMP工程を用いて、表面の平坦化を行い、第2配線6(38+37)、ビア5a(34a+35a)、第2配線6a(38a+37a)を形成する。

【0082】

以上により、本発明の第2の実施の形態に係る半導体装置が製造される。

【0083】

本実施の形態についても、第1の実施の形態と同様の効果を得ることができる。

加えて、本実施の形態に係る抵抗変化型不揮発記憶装置は1回のPR工程の追加でロジックLSIに混載可能であり、製造コストの大幅な削減が可能となる。更に、ロジックLSIのデバイスパラメータを変えることなく抵抗変化型不揮発記憶装置を混載することができる。

【0084】

(第3の実施の形態)

本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の構成について、添付図面を参照して説明する。第3の実施の形態では、抵抗変化素子1aの下部電極13aがホール9の底部だけでなく、底部から側壁の途中まで形成されている点で、第1の実施の形態と異なる。以下詳細に説明する。

【0085】

図16は、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の主要部の構成を示す断面図である。抵抗変化型不揮発記憶装置90aは、基板70aと、第1キャップ絶縁膜61と、第1配線3と、第2層間絶縁膜52と、第2キャップ絶縁膜62と、抵抗変化型素子1aと、第3層間絶縁膜53と、第3キャップ絶縁膜63と、第2配線6と、第4層間絶縁膜54とを具備している。

【0086】

抵抗変化型素子1aは、抵抗値の変化で情報を記憶する。第1配線3と第2配線6との間に形成されたホール9内に設けられている。抵抗変化型素子1aは、下部電極13aと、抵抗変化層12aと、上部電極11aとを備えている。

【0087】

下部電極13aは、ホール9の底部及び底部から側壁の途中まで連続的に形成されている。ただし、その端部は、ホール9の側壁の途中に在り、ホール9の上部に達していない。下部電極13aは、金属の導体で形成されている。下部電極13aは、選択成長でなく通常の成膜法で形成されている。その形成方法については後述される。

【0088】

抵抗変化層12aは、下部電極13a上及びホール9の側壁上に形成されている。その端部は、ホール9の上部に達している。その端部は、第2配線6の底面に接していることが好ましい。それにより、抵抗変化層12aの端部と下部電極13aの端部とを大きく隔てることができる。その結果、抵抗変化素子1aは、抵抗変化層12aの端部の影響を受け難くなる。抵抗変化層12aは、下部電極13aとは異なる金属材料を用いた酸化物を含むことができる。

【0089】

上部電極11aは、抵抗変化層12a上を内側から覆うように形成されている。その端部は、ホール9の上部に達している。その端部は、第2配線6の底面に接していることが好ましい。抵抗変化素子1aと第2配線6とを接続するためのビアやコンタクトを別途製造する必要が無いからである。上部電極11aは、金属の導体で形成されている。上部電極11aは、その更に内側の領域を埋める埋め込み層(金属)18を備えていても良い。

【0090】

抵抗変化型素子1aのその他の特徴、及び、抵抗変化型不揮発記憶装置のその他の構成については、第1の実施の形態と同様である。

【0091】

この場合においても、第1の実施の形態で説明された効果と同様の効果を得ることができる。

【0092】

次に、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の動作方法については、第1の実施の形態と同様である。

【0093】

次に、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法について説明する。図17A〜図17Fは、本発明の第3の実施の形態に係る抵抗変化型不揮発記憶装置の製造方法を示す断面図である。

【0094】

まず、第1の実施の形態における図7A及び図7Bの工程を実施する。

次に、図17Aに示すように、表面に第2キャップ絶縁膜62、第3層間絶縁膜53及び第3キャップ絶縁膜63を形成する。第2キャップ絶縁膜62及び第3キャップ絶縁膜63としては、ここではシリコン窒化膜(SiNx)を用いる。第3層間絶縁膜53としては、ここではシリコン酸化膜(SiO2)を用いる。それぞれ、プラズマCVD法を用いて堆積する。

【0095】

続いて、図17Bに示すように、PR工程とドライエッチング工程を用いて、第3キャップ絶縁膜63、第3層間絶縁膜53及び第2キャップ絶縁膜62にホール(開口部)9を設ける。それにより、第1配線3の表面が露出する。すなわち、第1配線3の銅(Cu)が露出する。

【0096】

その後、図17Cに示すように、全面に下部電極13a用の膜を形成する。下部電極13a用の膜としては、ここではルテニウム(Ru)を用いる。ルテニウム(Ru)はスパッタ法で成膜される。それにより、下部電極13a用の膜が、第3キャップ絶縁膜63の表面及びホール9の内部の表面(ホール9の底部を含む)を覆う。その後、全面にレジスト42を塗布し、所定の条件下でアッシングを行う。それにより、レジスト42は、ホール9の底部及び側壁の途中まで下部電極13a用の膜を覆う。

【0097】

次に、図17Dに示すように、下部電極13a用の膜をエッチバックする。その後、レジスト42をアッシングにより除去する。それにより、下部電極13aが、ホール9の底部及び底部から側壁の途中まで連続的に形成される。

【0098】

続いて、図17Eに示すように、第3ストッパ絶縁膜63の表面、ホール9の内部の上部側壁及び下部電極13の表面を覆うように、抵抗変化層12a用の膜、上部電極11a用の膜及び埋め込み層18用の膜を形成する。抵抗変化層12a用の膜としては、ここではニッケル酸化膜(NiO)を用いる。上部電極13a用の膜としては、ここではチタニウム窒化膜(TiN)を用いる。埋め込み層18用の膜としては、ここではタングステン(W)を用いる。これらは、はスパッタ法で成膜される。なお、埋め込み層18は上部電極11aと同じ材料でもよいし、また上部電極11a用の膜を厚く形成するなどして、埋め込み層18を無くしてもかまわない。

【0099】

次に、図17Fに示すように、表面をCMP工程で平坦化する。それにより、抵抗変化素子1aの全てはホール9(開口部)に埋め込まれる。そのとき、下部電極13aは、ホール9の底部及び底部から側壁の途中まで連続的に形成されている。ただし、その端部は、ホール9の側壁の途中に在り、ホール9の上部に達していない。抵抗変化層12aは、下部電極13a上及びホール9の側壁上に形成されている。その端部は、ホール9の上部に達している。上部電極11aは、抵抗変化層12a上を内側から覆うように形成されている。その端部は、ホール9の上部に達している。

【0100】

その後、第1の実施の形態における図7H(ただし、第3ストッパ絶縁膜63の形成を除く)及び図7Iの工程を実施する。

【0101】

以上により、本発明の第1の実施の形態に係る抵抗変化型不揮発記憶装置が製造される。

【0102】

なお、下部電極13a、抵抗変化層12a及び上部電極11aの材料に関しては、第1の実施の形態に記載のとおりである。

【0103】

本実施の形態により、第1の実施の形態と同様の効果を得ることができる。

また、選択CVD成長を行わず、通常の成膜方法を用いることができる。それにより、製造コストを削減することができる。また、本実施の形態も、第2の実施の形態のような半導体装置へ適用が可能である。

【0104】

本発明は上記各実施の形態に限定されず、本発明の技術思想の範囲内において、各実施の形態は適宜変形又は変更され得ることは明らかである。

【符号の説明】

【0105】

1、1a 抵抗変化型素子

2、2a 制御トランジスタ

3、3a 第1配線

4、4a コンタクト

5a ビア

6、6a 第2配線

8 共通線

9 ホール

11、11a 上部電極

11p 上部電極1

12、12a 抵抗変化層

13、13a 下部電極

13p 下部電極13の一部分

18 埋め込み層(金属)

21、21a ドレイン

22、22a ゲート

23、23a ゲート絶縁膜

24、24a ソース

25、25a サイドウォール

31、31a 第1メタル配線

32、32a バリアメタル層

34a ビア

35a バリアメタル層

37、37a 第2メタル配線

38、38a バリアメタル層

51 第1層間絶縁膜

52 第2層間絶縁膜

53 第3層間絶縁膜

54 第4層間絶縁膜

61 第1キャップ絶縁膜

62 第2キャップ絶縁膜

63 第3キャップ絶縁膜

70、70a 基板

71 素子分離層

90、90a 抵抗変化型不揮発記憶装置(抵抗変化型メモリ)

91 ロジックLSI

100 抵抗変化素子

101 抵抗変化素子

102 制御トランジスタ

103 第1配線

104 コンタクト

105 第1ビア

106 ビット線(又は第2配線)

108 共通線

111 上部電極

112 抵抗変化層

113 下部電極

114 電流パス

115 電流パス

116 電流パス

117 側部

121 ドレイン

122 ワード線(又はゲート)

123 ゲート絶縁膜

124 ソース

125 サイドウォール

131 銅(Cu)

132 バリアメタル

134 銅(Cu)

135 バリアメタル

151 第1層間絶縁膜

152 第2層間絶縁膜

153 第3層間絶縁膜

161 第1キャップ絶縁膜

162 第2キャップ絶縁膜

163 第3キャップ絶縁膜

170 半導体基板

171 素子分離領域

190 抵抗変化型メモリ

MC メモリセル

【特許請求の範囲】

【請求項1】

第1配線と、

前記第1配線上に形成された層間絶縁層と、

前記層間絶縁膜上に形成された第2配線と、

前記第1配線と前記第2配線との間に形成された抵抗変化型素子と

を具備し、

前記層間絶縁層は、前記第1配線と前記第2配線とに挟まれるように形成され、前記第1配線の幅以下の幅を有するホールを備え、

前記抵抗変化型素子は、

前記第1配線と接して、前記ホールの底部に形成された下部電極と、

前記下部電極上に形成された抵抗変化層と、

前記抵抗変化層上に形成された上部電極と

を備え、

前記下部電極、前記抵抗変化層及び前記上部電極は、前記ホールの内部に形成され、

前記第1配線は銅を含み、前記下部電極はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置。

【請求項2】

請求項1に記載の抵抗変化型不揮発性記憶装置において、

前記銅の配向性は(111)面であり、

前記下部電極はルテニウムを含み、

前記ルテニウムの配向性は(002)面である

抵抗変化型不揮発性記憶装置。

【請求項3】

第1配線と、

前記第1配線上に形成された層間絶縁層と、

前記層間絶縁膜上に形成された第2配線と、

前記第1配線と前記第2配線との間に形成された抵抗変化型素子と

を具備し、

前記層間絶縁層は、前記第1配線と前記第2配線とに挟まれるように形成され、前記第1配線の幅以下の幅を有するホールを備え、

前記抵抗変化型素子は、

前記第1配線と接して、前記ホールの底部に形成された下部電極と、

前記下部電極上に形成された抵抗変化層と、

前記抵抗変化層上に形成された上部電極と

を備え、

前記下部電極、前記抵抗変化層及び前記上部電極は、前記ホールの内部に形成され、

前記抵抗変化層及び前記上部電極の端部は、前記第2配線の底面と接する

抵抗変化型不揮発性記憶装置。

【請求項4】

請求項3に記載の抵抗変化型不揮発性記憶装置において、

前記第1配線は銅を含み、

前記下部電極はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置。

【請求項5】

請求項4に記載の抵抗変化型不揮発性記憶装置において、

前記銅の配向性は(111)面であり、

前記下部電極はルテニウムを含み、

前記ルテニウムの配向性は(002)面である

抵抗変化型不揮発性記憶装置。

【請求項6】

請求項3に記載の抵抗変化型不揮発性記憶装置において、

前記第1配線はアルミニウムを含み、

前記下部電極はタングステン、タンタル及びチタニウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置。

【請求項7】

請求項3に記載の抵抗変化型不揮発性記憶装置において、

前記第1配線はシリコンを含み、

前記下部電極はタングステン、タンタル及びチタニウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置。

【請求項8】

請求項1乃至7のいずれか一項に記載の抵抗変化型不揮発性記憶装置において、

前記下部電極は、更に、前記底部から側壁の途中まで形成されている

抵抗変化型不揮発性記憶装置。

【請求項9】

請求項1乃至8のいずれか一項に記載の抵抗変化型不揮発性記憶装置において、

前記抵抗変化層は、前記下部電極とは異なる材料を用いた酸化物を含む

抵抗変化型不揮発性記憶装置。

【請求項10】

複数の抵抗変化型不揮発性記憶装置と、

ただし前記複数の抵抗変化型不揮発性記憶装置は請求項1乃至7のいずれか一項に記載され、

前記複数の抵抗変化型不揮発性記憶装置を用いる論理回路と

を具備する

半導体装置。

【請求項11】

第1配線上に形成された層間絶縁層中に、前記第1配線の幅以下の幅を有するホールを形成する工程と、

前記ホールの内部に抵抗変化型素子を形成する工程と、

前記抵抗変化型素子と接するように前記抵抗変化型素子上に第2配線を形成する工程と

を具備し、

前記抵抗変化型素子を形成する工程は、

前記第1配線と接して、前記ホールの底部に下部電極を形成する工程と、

前記下部電極上に抵抗変化層用の第1膜を形成する工程と、

前記第1膜上に上部電極用の第2膜を形成する工程と、

前記層間絶縁層上の前記第1膜及び前記第2膜を除去する工程と

を備え、

前記第1配線は銅を含み、前記下部電極はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項12】

請求項11に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記銅の配向性は(111)面であり、

前記下部電極はルテニウムを含み、

前記ルテニウムの配向性は(002)面である

抵抗変化型不揮発性記憶装置の製造方法。

【請求項13】

第1配線上に形成された層間絶縁層中に、前記第1配線の幅以下の幅を有するホールを形成する工程と、

前記ホールの内部に抵抗変化型素子を形成する工程と、

前記抵抗変化型素子と接するように前記抵抗変化型素子上に第2配線を形成する工程と

を具備し、

前記抵抗変化型素子を形成する工程は、

前記第1配線と接して、前記ホールの底部に下部電極を形成する工程と、

前記下部電極上に抵抗変化層用の第1膜を形成する工程と、

前記第1膜上に上部電極用の第2膜を形成する工程と、

前記層間絶縁層上の前記第1膜及び前記第2膜を除去する工程と

を備え、

前記抵抗変化層及び前記上部電極の端部は、前記第2配線の底面と接する

抵抗変化型不揮発性記憶装置の製造方法。

【請求項14】

請求項13に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記下部電極を形成する工程は、

前記ホールの内部において前記第1配線上に前記下部電極を選択成長させる工程を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項15】

請求項14に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記第1配線は銅を含み、

前記下部電極はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項16】

請求項15に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記銅の配向性は(111)面であり、

前記下部電極はルテニウムを含み、

前記ルテニウムの配向性は(002)面である

抵抗変化型不揮発性記憶装置の製造方法。

【請求項17】

請求項14に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記第1配線はアルミニウムを含み、

前記下部電極はタングステン、タンタル及びチタニウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項18】

請求項14に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記第1配線はシリコンを含み、

前記下部電極はタングステン、タンタル及びチタニウムからなる群から選択される少なくとも一つの金属を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項19】

請求項13に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記下部電極を形成する工程は、

前記層間絶縁層の表面及び前記ホールの内部の表面を覆うように下部電極用の第3膜を形成する工程と、

前記ホールの底部及び側壁の途中まで前記第3膜を覆うように保護膜を形成する工程と、

前記第3膜のうち、前記保護膜で覆われた部分を除く部分を除去する工程と

前記保護膜を除去する工程と、

を備える

抵抗変化型不揮発性記憶装置の製造方法。

【請求項20】

請求項11乃至19のいずれか一項に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記抵抗変化層は、前記下部電極とは異なる材料を用いた酸化物を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項1】

第1配線と、

前記第1配線上に形成された層間絶縁層と、

前記層間絶縁膜上に形成された第2配線と、

前記第1配線と前記第2配線との間に形成された抵抗変化型素子と

を具備し、

前記層間絶縁層は、前記第1配線と前記第2配線とに挟まれるように形成され、前記第1配線の幅以下の幅を有するホールを備え、

前記抵抗変化型素子は、

前記第1配線と接して、前記ホールの底部に形成された下部電極と、

前記下部電極上に形成された抵抗変化層と、

前記抵抗変化層上に形成された上部電極と

を備え、

前記下部電極、前記抵抗変化層及び前記上部電極は、前記ホールの内部に形成され、

前記第1配線は銅を含み、前記下部電極はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置。

【請求項2】

請求項1に記載の抵抗変化型不揮発性記憶装置において、

前記銅の配向性は(111)面であり、

前記下部電極はルテニウムを含み、

前記ルテニウムの配向性は(002)面である

抵抗変化型不揮発性記憶装置。

【請求項3】

第1配線と、

前記第1配線上に形成された層間絶縁層と、

前記層間絶縁膜上に形成された第2配線と、

前記第1配線と前記第2配線との間に形成された抵抗変化型素子と

を具備し、

前記層間絶縁層は、前記第1配線と前記第2配線とに挟まれるように形成され、前記第1配線の幅以下の幅を有するホールを備え、

前記抵抗変化型素子は、

前記第1配線と接して、前記ホールの底部に形成された下部電極と、

前記下部電極上に形成された抵抗変化層と、

前記抵抗変化層上に形成された上部電極と

を備え、

前記下部電極、前記抵抗変化層及び前記上部電極は、前記ホールの内部に形成され、

前記抵抗変化層及び前記上部電極の端部は、前記第2配線の底面と接する

抵抗変化型不揮発性記憶装置。

【請求項4】

請求項3に記載の抵抗変化型不揮発性記憶装置において、

前記第1配線は銅を含み、

前記下部電極はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置。

【請求項5】

請求項4に記載の抵抗変化型不揮発性記憶装置において、

前記銅の配向性は(111)面であり、

前記下部電極はルテニウムを含み、

前記ルテニウムの配向性は(002)面である

抵抗変化型不揮発性記憶装置。

【請求項6】

請求項3に記載の抵抗変化型不揮発性記憶装置において、

前記第1配線はアルミニウムを含み、

前記下部電極はタングステン、タンタル及びチタニウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置。

【請求項7】

請求項3に記載の抵抗変化型不揮発性記憶装置において、

前記第1配線はシリコンを含み、

前記下部電極はタングステン、タンタル及びチタニウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置。

【請求項8】

請求項1乃至7のいずれか一項に記載の抵抗変化型不揮発性記憶装置において、

前記下部電極は、更に、前記底部から側壁の途中まで形成されている

抵抗変化型不揮発性記憶装置。

【請求項9】

請求項1乃至8のいずれか一項に記載の抵抗変化型不揮発性記憶装置において、

前記抵抗変化層は、前記下部電極とは異なる材料を用いた酸化物を含む

抵抗変化型不揮発性記憶装置。

【請求項10】

複数の抵抗変化型不揮発性記憶装置と、

ただし前記複数の抵抗変化型不揮発性記憶装置は請求項1乃至7のいずれか一項に記載され、

前記複数の抵抗変化型不揮発性記憶装置を用いる論理回路と

を具備する

半導体装置。

【請求項11】

第1配線上に形成された層間絶縁層中に、前記第1配線の幅以下の幅を有するホールを形成する工程と、

前記ホールの内部に抵抗変化型素子を形成する工程と、

前記抵抗変化型素子と接するように前記抵抗変化型素子上に第2配線を形成する工程と

を具備し、

前記抵抗変化型素子を形成する工程は、

前記第1配線と接して、前記ホールの底部に下部電極を形成する工程と、

前記下部電極上に抵抗変化層用の第1膜を形成する工程と、

前記第1膜上に上部電極用の第2膜を形成する工程と、

前記層間絶縁層上の前記第1膜及び前記第2膜を除去する工程と

を備え、

前記第1配線は銅を含み、前記下部電極はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項12】

請求項11に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記銅の配向性は(111)面であり、

前記下部電極はルテニウムを含み、

前記ルテニウムの配向性は(002)面である

抵抗変化型不揮発性記憶装置の製造方法。

【請求項13】

第1配線上に形成された層間絶縁層中に、前記第1配線の幅以下の幅を有するホールを形成する工程と、

前記ホールの内部に抵抗変化型素子を形成する工程と、

前記抵抗変化型素子と接するように前記抵抗変化型素子上に第2配線を形成する工程と

を具備し、

前記抵抗変化型素子を形成する工程は、

前記第1配線と接して、前記ホールの底部に下部電極を形成する工程と、

前記下部電極上に抵抗変化層用の第1膜を形成する工程と、

前記第1膜上に上部電極用の第2膜を形成する工程と、

前記層間絶縁層上の前記第1膜及び前記第2膜を除去する工程と

を備え、

前記抵抗変化層及び前記上部電極の端部は、前記第2配線の底面と接する

抵抗変化型不揮発性記憶装置の製造方法。

【請求項14】

請求項13に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記下部電極を形成する工程は、

前記ホールの内部において前記第1配線上に前記下部電極を選択成長させる工程を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項15】

請求項14に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記第1配線は銅を含み、

前記下部電極はルテニウム、タングステン、コバルト、白金、金、ロジウム、イリジウム及びパラジウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項16】

請求項15に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記銅の配向性は(111)面であり、

前記下部電極はルテニウムを含み、

前記ルテニウムの配向性は(002)面である

抵抗変化型不揮発性記憶装置の製造方法。

【請求項17】

請求項14に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記第1配線はアルミニウムを含み、

前記下部電極はタングステン、タンタル及びチタニウムからなる群から選択される少なくとも一種の金属を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項18】

請求項14に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記第1配線はシリコンを含み、

前記下部電極はタングステン、タンタル及びチタニウムからなる群から選択される少なくとも一つの金属を含む

抵抗変化型不揮発性記憶装置の製造方法。

【請求項19】

請求項13に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記下部電極を形成する工程は、

前記層間絶縁層の表面及び前記ホールの内部の表面を覆うように下部電極用の第3膜を形成する工程と、

前記ホールの底部及び側壁の途中まで前記第3膜を覆うように保護膜を形成する工程と、

前記第3膜のうち、前記保護膜で覆われた部分を除く部分を除去する工程と

前記保護膜を除去する工程と、

を備える

抵抗変化型不揮発性記憶装置の製造方法。

【請求項20】

請求項11乃至19のいずれか一項に記載の抵抗変化型不揮発性記憶装置の製造方法において、

前記抵抗変化層は、前記下部電極とは異なる材料を用いた酸化物を含む

抵抗変化型不揮発性記憶装置の製造方法。

【図1】

【図2】

【図3A】

【図3B】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図7D】

【図7E】

【図7F】

【図7G】

【図7H】

【図7I】

【図8】

【図9A】

【図9B】

【図10A】

【図10B】

【図11A】

【図11B】

【図12A】

【図12B】

【図13A】

【図13B】

【図14A】

【図14B】

【図15A】

【図15B】

【図16】

【図17A】

【図17B】

【図17C】

【図17D】

【図17E】

【図17F】

【図2】

【図3A】

【図3B】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図7D】

【図7E】

【図7F】

【図7G】

【図7H】

【図7I】

【図8】

【図9A】

【図9B】

【図10A】

【図10B】

【図11A】

【図11B】

【図12A】

【図12B】

【図13A】

【図13B】

【図14A】

【図14B】

【図15A】

【図15B】

【図16】

【図17A】

【図17B】

【図17C】

【図17D】

【図17E】

【図17F】

【公開番号】特開2013−62408(P2013−62408A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2011−200500(P2011−200500)

【出願日】平成23年9月14日(2011.9.14)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.RRAM

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成23年9月14日(2011.9.14)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.RRAM

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]