抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、抵抗変化物質を含む半導体素子及びその製造方法に係り、さらに詳細には、印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、該半導体素子を含む不揮発性メモリ装置に関する。

【背景技術】

【0002】

電場/磁場下で、または電流/電圧の印加によって抵抗が変化する物質は、不揮発性メモリ素子または論理回路などで多様に活用されている。例えば、磁気トンネル接合(MTJ:magnetic tunnel junction)素子の場合、磁化方向によって、高抵抗状態と低抵抗状態とを有する抵抗変化物質を利用する。また、抵抗性メモリ(ReRAM:resistance random−access memory)の場合、印加された電圧によって抵抗が変化する遷移金属酸化物を主に利用する。

【0003】

このような抵抗変化物質を利用するメモリ素子や論理回路のような装置は、抵抗変化物質を例にすれば、セット電圧(set voltage)、リセット電圧(reset voltage)または読み取り電圧(read voltage)のような多様な電圧を印加するために、スイッチング素子を必要とする。メモリ素子や論理回路などで、例えば、1個のスイッチング素子と1個の抵抗変化物質とが直列に連結された構造を主に使用することができる。スイッチング素子としては、一般的にトランジスタを使用するが、ダイオードを使用する場合もある。例えば、1個のトランジスタと1個の抵抗変化物質とが連結された構造を1Tr−1R構造と呼んだりもする。

【0004】

最近では、スイッチング素子と抵抗変化物質とを1つの単一素子として統合するための技術が試みられている。この場合、1つの素子がスイッチング機能とメモリ機能とを同時に遂行することが可能である。

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は、印加された電圧によって抵抗が変化する抵抗変化物質を含み、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる半導体素子を提供するものである。

【0006】

本発明はまた、該半導体素子の製造方法を提供するものである。

【課題を解決するための手段】

【0007】

本発明は一類型によれば、絶縁基板と、前記絶縁基板上に配置されたチャネル層と、前記チャネル層の上部表面から前記チャネル層の内部に少なくとも部分的に延びて配置されたゲートと、前記チャネル層の上部で、前記ゲートの両側面にそれぞれ配置されたソース及びドレインと、前記ゲートの周囲を取り囲み、前記ゲートを、前記チャネル層、前記ソース及び前記ドレインから電気的に絶縁させるゲート絶縁膜と、前記絶縁基板と前記ゲートとの間に配置される抵抗変化物質層と、を含む半導体素子が提供される。

【0008】

一実施形態で、前記抵抗変化物質層は、前記ゲートと直接に接触してもよい。

【0009】

他の実施形態で、前記抵抗変化物質層と前記ゲートとの間に、前記ゲート絶縁膜が配置されてもよい。

【0010】

例えば、前記抵抗変化物質層は、丸い底面を有し、前記抵抗変化物質層の前記丸い底面の中心部は、前記絶縁基板と接し、前記丸い底面の周辺部は、前記チャネル層と接してもよい。

【0011】

前記チャネル層は、第1導電型にドーピングされた単結晶半導体からなり、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされた単結晶半導体からなってもよい。

【0012】

前記抵抗変化物質層は、酸素欠乏欠陥が相対的に多い第1抵抗変化物質層、及び酸素欠乏欠陥が相対的に少ない第2抵抗変化物質層を含んでもよい。

【0013】

前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、電流の流れる方向に沿って順に配置されてもよい。

【0014】

例えば、前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、前記絶縁基板上で互いに隣接して配置され、前記第1抵抗変化物質層及び前記第2抵抗変化物質層が、いずれも前記絶縁基板と前記ゲートとに接触してもよい。

【0015】

また、本発明の他の類型によれば、チャネル層と、前記チャネル層の両側上部にそれぞれ配置されたソース及びドレインと、前記ソースと前記ドレインとの間で、前記チャネル層の上部中心領域に配置された抵抗変化物質層と、前記抵抗変化物質層上に配置されたゲートと、前記ゲートの周囲を取り囲むゲート絶縁膜と、を含む半導体素子が提供される。

【0016】

一実施形態で、前記ゲート絶縁膜は、前記ゲートの少なくとも下部面を取り囲むように形成されてもよい。

【0017】

前記ゲート絶縁膜は、前記ゲートの下部面と前記チャネル層との間、及び前記ゲートの下部面と前記抵抗変化物質層との間に配置されてもよい。

【0018】

前記抵抗変化物質層は、前記ゲートと直接接触し、前記ゲート絶縁膜は、前記ゲートの下部面と前記チャネル層との間に配置されてもよい。

【0019】

前記半導体素子は、隣接した他のセルの半導体素子との電気的隔離のために、前記チャネル層の両側面に配置される絶縁膜をさらに含んでもよい。

【0020】

また、前記半導体素子は、前記ソース及び前記ドレインを覆うように形成され、前記ゲートまたは前記ゲート絶縁膜の周囲を取り囲むパッシベーション層をさらに含んでもよい。

【0021】

また、前記半導体素子は、前記パッシベーション層を貫通し、前記ソース及び前記ドレインにそれぞれ電気的に連結されるソース電極とドレイン電極とをさらに含んでもよい。

【0022】

一実施形態で、前記抵抗変化物質層の少なくとも一部は、前記チャネル層の内部に延びており、前記抵抗変化物質層の上部は、前記チャネル層上に突出してもよい。

【0023】

一実施形態で、前記チャネル層は、単結晶半導体基板を第1導電型にドーピングして形成され、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされて形成されてもよい。

【0024】

前記半導体素子は、前記抵抗変化物質層の下部を取り囲む前記チャネル層の一部領域を前記第1導電型に高濃度にドーピングして形成されたドーピング領域をさらに含んでもよい。

【0025】

前記抵抗変化物質層は、酸素欠乏欠陥が相対的に多い第1抵抗変化物質層、及び酸素欠乏欠陥が相対的に少ない第2抵抗変化物質層を含んでもよい。

【0026】

前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、前記ソースと前記ドレインとの間の電流フロー方向に沿って順に配置されてもよい。

【0027】

例えば、前記抵抗変化物質層は、前記ソースと前記ドレインとの間の電流フロー方向に沿って順に配列された前記第1抵抗変化物質層、前記第2抵抗変化物質層、及び前記第1抵抗変化物質層を含んでもよい。

【0028】

本発明のさらに他の類型によれば、絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレインを含む構造を設ける段階と、前記ソースと前記ドレインとの間の前記チャネル層を部分的にエッチングし、前記チャネル層内にリセス領域を形成する段階と、前記リセス領域の内壁に全体的にゲート絶縁膜を形成する段階と、前記絶縁基板の表面が露出されるまで、前記リセス領域の底面にある前記ゲート絶縁膜の一部と前記チャネル層の一部とを除去する段階と、前記リセス領域内の前記絶縁基板の表面上に抵抗変化物質層を形成する段階と、前記リセス領域にゲート電極材料を充填してゲートを形成する段階と、を含む半導体素子の製造方法が提供される。

【0029】

ここで、絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレインを含む構造を設ける前記段階は、絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレイン、前記チャネル層の上部表面上で、前記ソースと前記ドレインとの間に部分的に形成された臨時ゲート、前記臨時ゲートの下部面と側面とを取り囲むゲート絶縁膜、及び前記ゲート絶縁膜と前記臨時ゲートとを取り囲むように、前記チャネル層の上部表面上に形成されたパッシベーション層を含むトランジスタを設ける段階と、前記臨時ゲートが現れるまで、前記パッシベーション層を研磨する段階と、前記チャネル層の上部表面が露出されるまで、前記臨時ゲートと前記ゲート絶縁膜とを選択的にエッチングし、前記パッシベーション層内に貫通ホールを形成する段階と、を含んでもよい。

【0030】

前記貫通ホールを形成する段階で、前記臨時ゲートの下部に形成された前記ゲート絶縁膜が除去され、前記臨時ゲートの側面に形成された前記ゲート絶縁膜は、前記パッシベーション層の前記貫通ホールの側壁に残ってもよい。

【0031】

前記リセス領域を形成する段階は、前記貫通ホールを介して露出された前記チャネル層を部分的にエッチングする段階を含んでもよい。

【0032】

前記半導体素子の製造方法は、前記パッシベーション層にコンタクトホールを形成し、前記コンタクトホール内に電極材料を充填し、前記ソース及び前記ドレインにそれぞれ連結されるソース電極とドレイン電極とを形成する段階をさらに含んでもよい。

【0033】

前記半導体素子の製造方法は、前記リセス領域内の前記絶縁基板の表面上に前記抵抗変化物質層を形成した後、前記抵抗変化物質層上に前記ゲート絶縁膜を形成する段階をさらに含んでもよい。

【0034】

一実施形態で、前記リセス領域が丸い形態の底面を有するように、前記チャネル層をエッチングしてもよい。

【0035】

また、前記リセス領域内の前記絶縁基板の表面上に抵抗変化物質層を形成する段階は、前記リセス領域の内壁に第1抵抗変化物質層を形成し、前記リセス領域の中心にある前記第1抵抗変化物質層を除去する段階と、イオン注入法で、前記第1抵抗変化物質層内に酸素欠乏欠陥を形成する段階と、前記リセス領域の中心部に第2抵抗変化物質層を形成する段階と、を含んでもよい。

【0036】

また、本発明のさらに他の類型によれば、チャネル層、前記チャネル層の両側上部面をドーピングして形成されたソース及びドレイン、前記チャネル層の上部面上で、前記ソースと前記ドレインとの間に配置された臨時ゲート、前記臨時ゲートの下部面と側面とを取り囲むゲート絶縁膜、前記ゲート絶縁膜を取り囲むように、前記チャネル層上に形成されたパッシベーション層を含む構造を設ける段階と、前記ゲート絶縁膜の底面が露出されるように、前記臨時ゲートを除去して開口を形成する段階と、前記開口内の前記ゲート絶縁膜の底面と、前記ゲート絶縁膜下部の前記チャネル層との一部をエッチングし、前記チャネル層内にリセス領域を形成する段階と、前記リセス領域内に抵抗変化物質層を形成する段階と、前記抵抗変化物質層上であって、前記開口内にゲート電極材料を充填してゲートを形成する段階と、を含む半導体素子の製造方法が提供される。

【0037】

前記チャネル層は、単結晶半導体基板を第1導電型にドーピングして形成され、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされて形成されてもよい。

【0038】

前記臨時ゲートを除去して開口を形成する段階で、前記開口の内壁には、前記ゲート絶縁膜が残ってもよい。

【0039】

また、前記リセス領域を形成する段階は、前記開口の底面の中心部が露出されて底面の周辺部が覆われるように、前記開口の内壁をマスクで取り囲む段階と、前記マスクによって覆われていない前記ゲート絶縁膜の底面と、前記チャネル層の一部とを除去する段階と、を含んでもよい。

【0040】

前記半導体素子の製造方法は、前記リセス領域内に抵抗変化物質層を形成する段階後、前記抵抗変化物質層の上部表面を覆うように、前記マスク間に前記ゲート絶縁膜の底面を形成する段階と、前記ゲート絶縁膜の側壁にある前記マスクを除去する段階と、をさらに含んでもよい。

【0041】

また、前記半導体素子の製造方法は、前記リセス領域を形成した後、前記リセス領域周囲の前記チャネル層にイオンを注入することによって、前記リセス領域周囲の前記チャネル層にドーピング領域を形成する段階をさらに含んでもよい。

【0042】

また、前記リセス領域内に抵抗変化物質層を形成する段階は、例えば、前記リセス領域の内壁に第1抵抗変化物質層を形成し、前記リセス領域の中心にある前記第1抵抗変化物質層を除去する段階と、イオン注入法で、前記第1抵抗変化物質層内に酸素欠乏欠陥を形成する段階と、前記リセス領域の中心部に第2抵抗変化物質層を形成する段階と、を含んでもよい。

【発明の効果】

【0043】

本発明の半導体素子は、印加された電圧によって抵抗が変化する抵抗変化物質を含み、スイッチの機能と不揮発性メモリの機能とを同時に遂行することが可能である。特に、該半導体素子の場合、チャネル層の主な材料として、単結晶シリコンを使用し、ソースとドレインとの間に抵抗変化物質を連結させて配置するために、高い駆動速度を得ることが可能である。また前記半導体素子の製造方法は、抵抗変化物質に高熱を加える工程がないために、半導体素子の製造過程で、抵抗変化物質の特性を劣化させる恐れがない。

【図面の簡単な説明】

【0044】

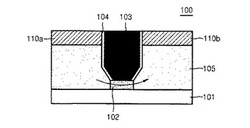

【図1】一実施形態による半導体素子の概略的な構造を示す断面図である。

【図2A】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2B】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2C】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2D】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2E】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2F】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2G】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2H】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図3】他の実施形態による半導体素子の概略的な構造を示す断面図である。

【図4】さらに他の実施形態による半導体素子の概略的な構造を示す断面図である。

【図5】図4に図示された半導体素子の製造過程の一部を概略的に示す断面図である。

【図6】さらに他の実施形態による半導体素子の概略的な構造を示す断面図である。

【図7A】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7B】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7C】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7D】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7E】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7F】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7G】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7H】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7I】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図8】さらに他の実施形態による半導体素子の概略的な構造を示す断面図である。

【図9】さらに他の実施形態による半導体素子の概略的な構造を示す断面図である。

【図10A】図9に図示された半導体素子の製造過程を概略的に示す断面図である。

【図10B】図9に図示された半導体素子の製造過程を概略的に示す断面図である。

【図10C】図9に図示された半導体素子の製造過程を概略的に示す断面図である。

【図11】さらに他の実施形態による半導体素子の概略的な構造を示す断面図である。

【発明を実施するための形態】

【0045】

以下、添付された図面を参照しつつ、抵抗変化物質を含む半導体素子及びその製造方法について詳細に説明する。以下の図面で同じ参照符号は、同じ構成要素を指し、図面上で各構成要素の大きさは、説明の明瞭さ及び便宜さのために誇張されていることがある。

【0046】

図1は、一実施形態による半導体素子100の概略的な構造を示す断面図を図示している。図1を参照すれば、一実施形態による半導体素子100は、絶縁基板101、絶縁基板101上に配置されたチャネル層105、チャネル層105の上部表面からチャネル層105の内部に少なくとも部分的に延びて配置されたゲート103、ゲート103の周囲を取り囲むゲート絶縁膜104、前記チャネル層105上で、ゲート103の両側面にそれぞれ配置されたソース110a及びドレイン110b、並びに絶縁基板101とゲート103との間に配置される抵抗変化物質層102を含んでもよい。ゲート絶縁膜104は、ゲート103の周囲を取り囲みつつ、ゲート103を、チャネル層105並びにソース110a及びドレイン110bから電気的に絶縁させる役割を行う。

【0047】

絶縁基板101は、例えば、SiO2のような材料からなる酸化物基板であってもよい。図1には、絶縁基板101が例示的に1層の絶縁層だけを含むと図示されている。しかし、絶縁基板101は、例えば、SOI(silicon on insulator)のように、シリコン層上にシリコン酸化物層が形成された多層基板であってもよい。

【0048】

絶縁基板101上に形成されたチャネル層105は、例えば、単結晶シリコンからなってもよい。単結晶シリコン以外にも、電子移動度(electron mobility)にすぐれる他の化合物半導体の結晶がチャネル層105の材料として使用されてもよい。また、チャネル層105は、例えば、p型またはn型にドーピングされてもよい。図1に図示されているように、チャネル層105は、一部領域が凹んでリセス領域が形成されているリセス・チャネル(recess channel)構造を有してもよい。

【0049】

ゲート103は、チャネル層105の上部表面からチャネル層105内部の少なくとも一部(すなわち、リセス領域)まで延びて配置されてもよい。ゲート103は、例えば、多結晶シリコン(poly−Si)や金属材料からなってもよい。また、チャネル層105の上部表面には、ゲート103の両側面に、ソース110a及びドレイン110bが配置されてもよい。チャネル層105がp型にドーピングされた単結晶シリコンからなる場合、前記ソース110a及びドレイン110bは、n型にドーピングされた単結晶シリコンからなってもよい。もしチャネル層105がn型にドーピングされた場合には、ソース110a及びドレイン110bは、p型にドーピングされてもよい。図1には、ソース110a及びドレイン110bが単一層として図示されているが、ソース110a及びドレイン110bのそれぞれは、例えば、nドーピング層とn+ドーピング層との二重層構造によって形成されてもよい。一方、ゲート103の周囲を取り囲むゲート絶縁膜104は、チャネル層105、ソース110a及びドレイン110bとゲート103とを電気的に分離する役割を行う。ゲート絶縁膜104として、例えば、SiO2やSiNxのような材料を使用することができ、または、HfSiON、ZrSiONのような高誘電率(high−k)材料を使用することもできる。

【0050】

抵抗変化物質層102は、絶縁基板101とゲート103との間に配置されてもよい。図1に図示されているように、抵抗変化物質層102の下部表面は、絶縁基板101と直接接触し、上部表面は、ゲート103と直接接触し、側面は、チャネル層105と直接接触してもよい。抵抗変化物質層102は、印加電圧によって抵抗が変化する抵抗変化物質からなってもよい。例えば、抵抗変化物質にセット電圧(set voltage)が印加されれば、抵抗変化物質の抵抗が低くなるが、一般的にこのときを、オン(ON)状態と呼ぶ。また、抵抗変化物質にリセット電圧(reset voltage)が印加されれば、抵抗変化物質の抵抗が高くなるが、一般的にこのときを、オフ(OFF)状態と呼ぶ。一般的に、抵抗変化メモリ素子は、抵抗変化物質のこのようなオン状態とオフ状態とのスイッチングを利用してデータを保存することができる。一方、記録されたデータを読み取るときは、抵抗変化物質の抵抗を変化させない読み取り電圧(read voltage)を抵抗変化物質に印加することができる。

【0051】

抵抗変化物質層102に使われるこのような抵抗変化物質としては、例えば、遷移金属酸化物(TMO:transition metal oxide)を挙げることができる。例えば、抵抗変化層102は、Ni酸化物、Cu酸化物、Ti酸化物、Co酸化物、Hf酸化物、Zr酸化物、Zn酸化物、W酸化物、Nb酸化物、TiNi酸化物、LiNi酸化物、Al酸化物、InZn酸化物、V酸化物、SrZr酸化物、SrTi酸化物、Cr酸化物、Fe酸化物、Ta酸化物及びそれらの混合物のうち、少なくともいずれか一つによって形成されてもよい。それ以外にも、Pr1−xCaxMnO3(PCMO)、SrTiO3(STO)のような多成分系金属酸化物、固体電解質物質などのように、電圧/電流印加による抵抗変化特性を有すると知られている抵抗変化物質などが使用されてもよい。

【0052】

前述の構造を有する半導体素子100の動作は、次の通り説明することができる。半導体素子100は、抵抗変化物質層102をチャネルの一部として含むトランジスタの構造を有するので、ゲート103にスレショルド電圧より低い電圧が印加されれば、半導体素子100は、OFF状態にあることになる。従って、ソース110a及びドレイン110bに電圧が印加されても、チャネル層105と抵抗変化物質層102とには、電流が流れない。

【0053】

ゲート103に、スレショルド電圧以上の電圧が印加されれば、半導体素子100は、ON状態となる。それにより、チャネル層105と抵抗変化物質層102とを介して、ソース110aとドレイン110bとの間に電流が流れることになる。図1に図示されているように、チャネル層105は、抵抗変化物質層102によって2つの部分に分離されているために、ソース110aとドレイン110bとの間に流れる電流は、抵抗変化物質層102を必ず通過することになる。このとき、ソース110aとドレイン110bとの電位差によって、抵抗変化物質層102の抵抗が変化しうる。

【0054】

例えば、ソース110aとドレイン110bとの電位差がセット電圧に該当すれば、抵抗変化物質層102の抵抗が低くなる。それにより、ソース−ドレイン間の電流が増加する。また、ソース110aとドレイン110bとの電位差がリセット電圧に該当すれば、抵抗変化物質層102の抵抗が高くなる。それにより、ソース−ドレイン間の電流が低くなる。そして、ソース110aとドレイン110bとの電位差が読み取り電圧に該当すれば、抵抗変化物質層102の抵抗は、変化しない。このとき、ソース−ドレイン間の電流を測定し、抵抗変化物質層102の抵抗状態を読み取ることができる。従って、ゲート103に印加される電圧によって、半導体素子100のON/OFFスイッチングが可能であり、ソース110a及びドレイン110bに印加される電圧によって、抵抗変化物質層102の抵抗を変化させたり、抵抗値を読み取る動作を遂行したりすることができる。

【0055】

図2Aないし図2Hは、図1に図示された半導体素子100の製造過程を概略的に示す断面図である。以下、図2Aないし図2Hを参照しつつ、一実施形態による半導体素子100の製造方法について説明する。

【0056】

初めに、図2Aに図示されているように、一般的なトランジスタの製造方法によって、絶縁基板101上にトップゲート型トランジスタを設ける。すなわち、図2Aを参照すれば、絶縁基板101、p型チャネル層105、チャネル層105の上部表面上に部分的に形成されたゲート絶縁膜104a及びゲート113、チャネル層105の上部領域で、ゲート113の両側に形成されたn型ソース110a及びn型ドレイン110b、並びに前記ゲート絶縁膜104a及びゲート113を取り囲むように、チャネル層105の上部表面上に形成されたパッシベーション層106を含むトップゲート型トランジスタが設けられる。p型チャネル層105、n型ソース110a及びn型ドレイン110bの代わりに、n型チャネル層105、p型ソース110a及びp型ドレイン110bが使用されてもよい。ソース110aは、nドーピング領域111aと、前記nドーピング領域111aの上部をさらに高濃度にドーピングして形成されたn+ドーピング領域112aとを有してもよい。同様に、ドレイン110bは、nドーピング領域111bと、n+ドーピング領域112bとを有してもよい。ここで、ゲート113は、最終的に形成される半導体素子100のゲート103ではなく、単に臨時のゲートであってもよい。

【0057】

前述のトランジスタが設けられれば、図2Bに図示されているように、一般的な化学機械研磨(CMP:chemical mechanical polishing)方式で、ゲート113が現れるまでパッシベーション層106を除去する。ゲート113が現れれば、図2Cに図示されているように、チャネル層105の上部表面が露出されるまで、乾式エッチング方式で、ゲート113とゲート絶縁膜104aとを選択的にエッチングして除去する。それにより、ゲート113が除去されつつ、パッシベーション層106内に、貫通ホール107が形成される。このとき、ゲート絶縁膜104aは、ゲート113の下部に形成された部分だけ除去され、ゲート113の側面に形成された部分は、依然としてパッシベーション層106の貫通ホール107の側壁に残ることになる。

【0058】

その後には、図2Dを参照すれば、貫通ホール107を介して露出されたチャネル層105を部分的にエッチングし、チャネル層105内にリセス領域108を形成することができる。このとき、リセス領域108の底面は、チャネル層105内に形成されてもよい。前述の過程で、ゲート絶縁膜104aの下部にあるソース110a及びドレイン110bの一部領域が共に除去されてもよい。次に、図2Eを参照すれば、リセス領域108の内壁に、すなわち、前記露出されたチャネル層105、ソース110a及びドレイン110bの表面に、全体的にゲート絶縁膜104bを形成する。それにより、図2Eに図示されているように、前記露出されたチャネル層105、ソース110a及びドレイン110bの表面は、ゲート絶縁膜104bで完全に覆われる。このとき、チャネル層105、ソース110a及びドレイン110bの表面に形成された下部のゲート絶縁膜104bと、パッシベーション層106の貫通ホール107の側壁に形成された上部のゲート絶縁膜104aとが連結され、1層のゲート絶縁膜104が形成される。

【0059】

次に、図2Fに図示されているように、異方性エッチング方式を利用し、絶縁基板101の表面が露出されるまで、リセス領域108の底面にあるゲート絶縁膜104bの一部と、チャネル層105の一部とを順次除去する。このように、絶縁基板101が露出されれば、図2Gに図示されているように、例えば、化学的気相蒸着法(CVD)や物理的気相蒸着法(PVD)を利用し、リセス領域108内の絶縁基板101の表面上に抵抗変化物質層102を形成する。図2Gには、抵抗変化物質層102が下部ゲート絶縁膜104bの全体を覆うと図示されているが、必ずしもこれに限定されるものではない。抵抗変化物質層102は、リセス領域108内に部分的に充填され、下部ゲート絶縁膜104bの一部が露出されてもよい。

【0060】

最後に、図2Hに図示されているように、貫通ホール107とリセス領域108とにゲート電極材料を充填し、ゲート103を形成することができる。その後、ゲート103両側のパッシベーション層106に、エッチングによってコンタクトホールを形成し、コンタクトホール内に電極材料を充填し、ソース110a及びドレイン110bにそれぞれ連結されるソース電極109aとドレイン電極109bとを形成することができる。または、貫通ホール107内とリセス領域108内にゲート103を形成する前に、貫通ホール107両側のパッシベーション層106をエッチングし、コンタクトホールを初めに形成することもできる。その後、貫通ホール107及びリセス領域108、及びその両側のコンタクトホールの内部に電極材料を充填し、ゲート103と、ソース電極109aと、ドレイン電極109bとを同時に形成することも可能である。

【0061】

抵抗変化物質層102は、一般的に、高温で抵抗変化特性を失いやすい。従って、半導体素子100を製造する過程で、抵抗変化物質層102を初めに形成した後、高温処理工程が遂行される場合には、抵抗変化物質層102が劣化され、動作の信頼性が低下しうる。しかし、図2Aないし図2Hで説明した方式で半導体素子100を製造する場合、抵抗変化物質層102を形成した後には、高温処理工程が遂行されないために、高温によって抵抗変化物質層102が劣化したり変形したりするリスクが少ない。

【0062】

一方、図1及び図2Aないし図2Hに図示された実施形態では、抵抗変化物質層102が、上部のゲート103と直接に接触している。しかし、抵抗変化物質層102とゲート103との間に、ゲート絶縁膜104がさらに配置されることも可能である。図3は、他の実施形態による半導体素子200の概略的な構造を示す断面図である。図3に図示された実施形態の場合、抵抗変化物質層102とゲート103との間に、ゲート絶縁膜104がさらに配置されているという点で、図1に図示された実施形態と違いがある。図3に図示された半導体素子200を製造する方法は、次の通りである。初めに、図2Aないし図2Gに図示された工程を順次遂行する。そして、図2Gに図示された工程で、抵抗変化物質層102を形成した後、抵抗変化物質層102上に、ゲート絶縁膜104を形成する。その後、図2Hで説明した方式でゲート103を形成すれば、図3に図示された半導体素子200を得ることができる。

【0063】

また図4は、さらに他の実施形態による半導体素子300の概略的な構造を示す断面図である。図1及び図3に図示された半導体素子100、200の場合、チャネル層105内のリセス領域108は、平らな底面を有し、抵抗変化物質層102も、平らな底面を有する。しかし、図4に図示された半導体素子300で、チャネル層105のリセス領域108は、丸い形態の底面を有し、同様に抵抗変化物質層102も、丸い形態の底面を有してもよい。従って、抵抗変化物質層102の丸い底面の中心部は、絶縁基板101と接し、丸い底面の周辺部は、チャネル層105と接してもよい。この場合、工程誤差による半導体素子300のスレショルド電圧の変化を減らすことができ、半導体素子300のスレショルド電圧を安定的に維持することができる。

【0064】

図4に図示された半導体素子300の製造工程は、図2Aないし図2Cに図示された工程をそのまま含んでもよい。図2Cの工程を遂行した後、図5に図示されているように、例えば、異方性エッチング方式で、チャネル層105内のリセス領域108が丸い形態の底面を有するように、チャネル層105をエッチングしてもよい。その後、図2Eないし図2Hに図示された工程を遂行すれば、図4に図示された丸い形態のリセス・チャネルを有する半導体素子300を得ることができる。

【0065】

以上で説明した半導体素子100、200、300は、SOIのような絶縁基板101上に形成され、リセス構造のチャネル層105を有する。しかし、前述の構造の半導体素子100、200、300のような機能を有する半導体素子を、例えば、シリコンのような半導体バルク基板上に形成することも可能である。図6は、さらに他の実施形態による半導体素子400の概略的な構造を示す断面図である。図6を参照すれば、本実施形態による半導体素子400は、チャネル層401、前記チャネル層401の両側上部にそれぞれ配置されたソース410a及びドレイン410b、前記ソース410aとドレイン410bとの間にあるチャネル層401の上部中心領域に配置された抵抗変化物質層402、前記抵抗変化物質層402上に配置されたゲート403、及び前記ゲート403の周囲を取り囲むゲート絶縁膜404を含んでもよい。図6に図示されているように、ゲート絶縁膜404は、ゲート403の少なくとも下部面を取り囲み、選択的にゲート403の周囲面をさらに取り囲むように形成される。図6には、ゲート絶縁膜404が、ゲート403と抵抗変化物質層402との間にも配置されていると図示されているが、抵抗変化物質層402は、ゲート403と直接接触することもできる。その場合、ゲート絶縁膜404は、ゲート403の下部面と、抵抗変化物質層402との間には配置されず、ゲート403の下部面とチャネル層401との間にのみ配置されてもよい。

【0066】

図6に図示されているように、チャネル層401の両側面には、隣接した他のセルの半導体素子との電気的隔離のために、絶縁膜415a、415bがさらに配置されてもよい。絶縁膜415a、415bは、例えば、STI(shallow trench isolation)であってもよい。また、絶縁膜415a、415b、ソース410a及びドレイン410bを覆うように、パッシベーション層406がさらに形成される。パッシベーション層406は、ゲート403またはゲート絶縁膜404の周囲を取り囲むように形成される。また、前記パッシベーション層406を貫通し、ソース410a及びドレイン410bにそれぞれ電気的に連結されるソース電極409aとドレイン電極409bとがさらに形成される。図6で、ソース410a及びドレイン410bは、単一層として図示されているが、前述のように、ドーピング濃度の異なった2層の層を有することもできる。

【0067】

前記抵抗変化物質層402の少なくとも一部は、図6に図示されているように、チャネル層401の内部に延びている。また、図6の例で、抵抗変化物質層402がチャネル層401上に突出していると図示されているが、必ずしもこれに限定されるものではない。例えば、抵抗変化物質層402の上部表面は、チャネル層401の上部表面と同じ高さに形成されてもよく、チャネル層401の上部表面より若干低い高さに形成されてもよい。

【0068】

図6の実施形態で、チャネル層401は、例えば、単結晶シリコンバルク基板をp型にドーピングして形成することができる。この場合、ソース410a及びドレイン410bは、n型にドーピングされる。その代わりに、チャネル層401は、単結晶シリコンバルク基板をn型にドーピングして形成することもできる。その場合には、ソース410a及びドレイン410bは、p型にドーピングされる。また、チャネル層401は、シリコン以外に、他の化合物半導体の単結晶基板に形成されてもよい。

【0069】

図7Aないし図7Iは、図6に図示された半導体素子400の製造過程を概略的に示す断面図である。以下、図7Aないし図7Iを参照しつつ、一実施形態による半導体素子400の製造方法について説明する。

【0070】

初めに、図7Aに図示されているように、一般的なトランジスタの製造方法によって、単結晶シリコンバルク基板上に、トップゲート型トランジスタを設ける。すなわち、図7Aを参照すれば、単結晶シリコンバルク基板をドーピングして形成されたチャネル層401、チャネル層401の両側上部面をドーピングして形成されたソース410a及びドレイン410bと、チャネル層401の上部表面上でソース410aとドレイン410bとの間に配置されたゲート絶縁膜404及びゲート413と、チャネル層401の両側面に隣接して形成された絶縁膜415a、415bと、ゲート絶縁膜404、ゲート413、絶縁膜415a、415b、ソース410a及びドレイン410bを覆うパッシベーション層406と、を含むトップゲート型トランジスタが設けられる。例えば、チャネル層401がp型にドーピングされる場合、ソース410a及びドレイン410bは、n型にドーピングされてもよい。また、チャネル層401がn型にドーピングされる場合、ソース410a及びドレイン410bは、p型にドーピングされてもよい。ゲート413は、例えば、多結晶シリコンからなってもよい。ここで、多結晶シリコンゲート413は、最終的に形成される半導体素子400のゲート403ではなく、単に臨時のゲートであってもよい。

【0071】

前述のトランジスタが設けられれば、図7Bに図示されているように、一般的な化学機械研磨(CMP)方式で、ゲート413が現れるまで、パッシベーション層406を除去する。ゲート413が現れれば、図7Cに図示されているように、多結晶シリコンからなるゲート413を、エッチングによって完全に除去する。それにより、ゲート413を取り囲んでいたゲート絶縁膜404だけが残り、ゲート絶縁膜404内には、ゲート413があったところに開口407が形成される。従って、開口407の内壁には、ゲート絶縁膜404が残ることになる。

【0072】

次に、図7Dを参照すれば、ゲート絶縁膜404内の開口407の内壁を、例えば、多結晶シリコンからなるマスク423で取り囲む。それにより、図7Dに図示されているように、開口407の底面の中心部だけが露出され、底面の周辺部は、マスク423によって覆われる。図7Dのマスク423を形成する工程は、例えば、パッシベーション層406及びゲート絶縁膜404上に多結晶シリコンを全体的に一定に蒸着する段階と、エッチングによって上部表面にある多結晶シリコンを除去する段階とを含んでもよい。それにより、パッシベーション層406及びゲート絶縁膜404の上部表面では、多結晶シリコンが除去され、ゲート絶縁膜404内の開口407の内壁には、多結晶シリコンが残り、マスク423が形成される。

【0073】

その後、図7Eを参照すれば、マスク423によって覆われていないゲート絶縁膜404の底面を除去し、次に、ゲート絶縁膜404下部のチャネル層401の一部までもエッチングによって除去する。それにより、図7Eに図示されているように、チャネル層401内には、部分的にリセス領域408が形成され、このとき、リセス領域408の底面は、チャネル層401内に形成される。

【0074】

次に、図7Fを参照すれば、例えば、化学的気相蒸着法(CVD)や物理的気相蒸着法(PVD)を利用し、リセス領域408内に抵抗変化物質層402を充填する。図7Fには、抵抗変化物質層402がチャネル層401の上部表面を越えて、ゲート絶縁膜404まで形成されていると図示されているが、必ずしもこれに限定されるものではない。例えば、抵抗変化物質層402の上部表面は、チャネル層401の上部表面と同じ高さに形成されてもよく、またはチャネル層401の上部表面より若干低い高さに形成されてもよい。

【0075】

抵抗変化物質層402を形成した後には、図7Gに図示されているように、抵抗変化物質層402の上部表面を覆うように、マスク423間にゲート絶縁膜404の底面404aを形成する。それにより、開口407の側壁にあるゲート絶縁膜404が底面404aと連結される。その後、図7Hを参照すれば、ゲート絶縁膜404の側壁にあるマスク423を除去する。それにより、開口407内には、ゲート絶縁膜404だけが残ることになる。

【0076】

最後に、図7Iに図示されているように、開口407内にゲート電極材料を充填し、ゲート403を形成することができる。その後、ゲート403両側のパッシベーション層406にコンタクトホールを形成し、コンタクトホール内に電極材料を充填し、ソース410a及びドレイン410bにそれぞれ連結されるソース電極409aとドレイン電極409bとを形成することができる。または、開口407内にゲート403を形成する前に、開口407両側のパッシベーション層406をエッチングし、コンタクトホールを予め形成することも可能である。その後、開口407及びその両側のコンタクトホールの内部に電極材料を充填し、ゲート403並びにソース電極409a及びドレイン電極409bを同時に形成することも可能である。

【0077】

前述の方法で、図6に図示された半導体素子400を製造することができる。図6には、抵抗変化物質層402とゲート403との間にゲート絶縁膜404が形成されている。しかし、図1に図示された半導体素子100と同様に、ゲート403が抵抗変化物質層402と直接接触することも可能である。その場合、図7Gに図示されたゲート絶縁膜404の底面404aを形成する段階が省略されてもよい。

【0078】

一方、図1、図3及び図4に図示された半導体素子100、200、300の場合には、チャネル層105の両側が抵抗変化物質層102によって分離されており、ソース110aとドレイン110bとの間に流れる電流は、必ず抵抗変化物質層102を通過する。しかし、図6に図示された半導体素子400の場合、チャネル層401が抵抗変化物質層402の下部を介して、ソース410a及びドレイン410bと連結されている。従って、ソース410aとドレイン410bとの間に流れる電流の一部は、抵抗変化物質層402を通過せずに、チャネル層401に流れることもできる。その場合、抵抗変化物質層402を通過する電流の量が十分ではないこともある。

【0079】

図8は、ソース410aとドレイン410bとの間に流れる電流のほとんどが抵抗変化物質層402を通過するように構成された半導体素子500を図示している。図8を参照すれば、本実施形態による半導体素子500は、抵抗変化物質層402の下部を取り囲むチャネル層401の一部領域を高濃度にドーピングして形成された高濃度のドーピング領域420を含む。例えば、チャネル層401がp型にドーピングされ、ソース410a及びドレイン410bがn型にドーピングされた場合、ドーピング領域420は、p+ドーピングされてもよい。また、チャネル層401がn型にドーピングされ、ソース410a及びドレイン410bがp型にドーピングされた場合、ドーピング領域420は、n+ドーピングされてもよい。その場合、ドーピング領域420下部のチャネル層401に迂回して流れる電流がほとんどないために、ほとんどの電流が抵抗変化物質層402に流れる。前記高濃度のドーピング領域420は、例えば、図7Eに図示された段階で、リセス領域408を形成した後、リセス領域408の周囲のチャネル層401にイオンを注入することによって形成されてもよい。そして、図7Fないし図7Iの段階を遂行すれば、図8に図示された半導体素子500が製造される。図8に図示された半導体素子500の構成は、ドーピング領域420以外は、図6に図示された半導体素子400と同一である。

【0080】

以上では、抵抗変化物質層402が単一層で形成された場合について説明した。しかし、抵抗変化物質層402の抵抗変化特性をさらに向上させるために、抵抗変化物質層402は、少なくとも2層を含む多層構造に形成されてもよい。例えば、酸素欠乏欠陥(oxygen vacancy)が相対的に多いTiOx層と、酸素欠乏欠陥が相対的に少ない一般的なTiO2層とを、2つの電極間に電流フロー方向に沿って積層する場合、TiO2層とTiOx層との間を酸素欠乏欠陥が移動しつつ、抵抗変化特性を向上させることができる。

【0081】

図9は、前述のような多層構造の抵抗変化物質層402を含む半導体素子600を図示している。図9を参照すれば、抵抗変化物質層402は、電流の流れる方向に沿って、すなわち、ソース410aからドレイン410bへの方向に沿って、第1抵抗変化物質層402a、第2抵抗変化物質層402b及び第1抵抗変化物質層402aを含んでもよい。例えば、第1抵抗変化物質層402aは、酸素欠乏欠陥が相対的に多いTiOxからなり、第2抵抗変化物質層402bは、酸素欠乏欠陥が相対的に少ないTiO2からなってもよい。代わりに、第1抵抗変化物質層402aがTiO2からなり、第2抵抗変化物質層402bがTiOxからなってもよい。図9に図示された半導体素子600の構造は、抵抗変化物質層402を除けば、図6に図示された半導体素子400の構造と同一である。

【0082】

図10Aないし図10Cは、図9に図示された半導体素子600の製造過程を概略的に示す断面図である。初めに、前述の図7Aないし図7Eに図示された過程を遂行する。それにより、結果として、図10Aに図示されているように、チャネル層401内に、部分的にリセス領域408が形成された状態となる。その後、図10Bを参照すれば、リセス領域408内のチャネル層401の側壁部と、ゲート絶縁膜404の内壁とに、第1抵抗変化物質層402aを形成することができる。例えば、化学的気相蒸着法(CVD)や物理的気相蒸着法(PVD)を利用して、リセス領域408内に全体的に抵抗変化物質を充填した後、エッチングによって、リセス領域408中心部の抵抗変化物質を除去することができる。それにより、リセス領域408内のチャネル層401の側壁部と、ゲート絶縁膜404の内壁部分とにのみ抵抗変化物質が形成される。そして、図10Bに図示されているように、例えば、ハロイオン注入法(halo ion implantation)で抵抗変化物質内にイオンを注入することができる。それにより、酸素欠乏欠陥が内部に形成された第1抵抗変化物質層402aが形成される。

【0083】

その後、図10Cに図示されているように、第1抵抗変化物質層402a間に、すなわち、リセス領域408の中心部に第2抵抗変化物質層402bを形成する。それにより、ソース410aからドレイン410bへの経路に沿って、第1抵抗変化物質層402a、第2抵抗変化物質層402b及び第1抵抗変化物質層402aが順に形成される。その後には、前述の図7Gないし図7Iに図示された過程を遂行する。それにより、図9に図示された半導体素子600が製造される。

【0084】

図9に図示された半導体素子600の場合、第2抵抗変化物質層402bの両側に第1抵抗変化物質層402aが形成された構造を含んでいるが、必ずしもこれに限定されるものではない。例えば、半導体素子600は、単に1層の第1抵抗変化物質層402a及び1層の第2抵抗変化物質層402bのみを含むこともできる。その場合、図10Bに図示された段階で、リセス領域408内に充填された抵抗変化物質をエッチングし、チャネル層401及びゲート絶縁膜404のいずれか一方の内壁にのみ抵抗変化物質を残すことができる。

【0085】

また、図1、図3及び図4に図示された半導体素子100、200、300にも、前述の多層構造の抵抗変化物質層が適用されてもよい。図11は、多層構造の抵抗変化物質層102を含む半導体素子700を図示している。図11を参照すれば、半導体素子700は、絶縁基板101、絶縁基板101上に配置されたチャネル層105、チャネル層105の上部表面からチャネル層105の内部に少なくとも部分的に延びて配置されたゲート103、ゲート103の周囲を取り囲むゲート絶縁膜104、絶縁基板101とゲート103との間に配置されて第1抵抗変化物質層102aと第2抵抗変化物質層102bとを有する抵抗変化物質層102、及び前記チャネル層105上で、ゲート103の両側面にそれぞれ配置されたソース110a及びドレイン110bを含んでもよい。

【0086】

第1抵抗変化物質層102aと第2抵抗変化物質層102bは、図11に図示されているように、両側のチャネル層105間の電流フロー方向に沿って配置されている。従って、第1抵抗変化物質層102aと第2抵抗変化物質層102bは、いずれも絶縁基板101とゲート103とに直接接触するように配置されており、前記絶縁基板101上で互いに隣接して配置されてもよい。図11には、図1に図示された半導体素子100に、多層構造の抵抗変化物質層が適用された例が図示されているが、図3及び図4に図示された半導体素子200、300にも前記多層構造の抵抗変化物質層が同様に適用されてもよい。また、図9に図示された例のように、抵抗変化物質層102は、第1抵抗変化物質層102a、第2抵抗変化物質層102b及び第1抵抗変化物質層102aの3層構造を有することもできる。

【0087】

以上、本発明の理解を助けるために、抵抗変化物質を含む半導体素子及びその製造方法に係わる例示的な実施形態について説明し、かつ添付された図面に図示した。しかし、かような実施形態は、単に本発明を例示するためのものであり、それらを制限するものではないという点を理解せねばならない。そして、本発明は図示して説明した説明に限定されるものではないという点を理解せねばならない。それは、多様な他の変形が、本技術分野で当業者に可能であるためである。

【符号の説明】

【0088】

100、200、300、400、500、600、700 半導体素子

101 絶縁基板

102、402 抵抗変化物質層

102a、402a 第1抵抗変化物質層

102b、402b 第2抵抗変化物質層

103、113、403、413 ゲート

104、104a、104b、404 ゲート絶縁膜

105、401 チャネル層

106、406 パッシベーション層

107 貫通ホール

108 リセス領域

109a、409a ソース電極

109b、409b ドレイン電極

110a、410a ソース

110b、410b ドレイン

111a、111b nドーピング領域

112a、112b n+ドーピング領域

404a 底面

407 開口

408 リセス領域

415a、415b 絶縁膜

420 高濃度ドーピング領域

423 マスク

【技術分野】

【0001】

本発明は、抵抗変化物質を含む半導体素子及びその製造方法に係り、さらに詳細には、印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、該半導体素子を含む不揮発性メモリ装置に関する。

【背景技術】

【0002】

電場/磁場下で、または電流/電圧の印加によって抵抗が変化する物質は、不揮発性メモリ素子または論理回路などで多様に活用されている。例えば、磁気トンネル接合(MTJ:magnetic tunnel junction)素子の場合、磁化方向によって、高抵抗状態と低抵抗状態とを有する抵抗変化物質を利用する。また、抵抗性メモリ(ReRAM:resistance random−access memory)の場合、印加された電圧によって抵抗が変化する遷移金属酸化物を主に利用する。

【0003】

このような抵抗変化物質を利用するメモリ素子や論理回路のような装置は、抵抗変化物質を例にすれば、セット電圧(set voltage)、リセット電圧(reset voltage)または読み取り電圧(read voltage)のような多様な電圧を印加するために、スイッチング素子を必要とする。メモリ素子や論理回路などで、例えば、1個のスイッチング素子と1個の抵抗変化物質とが直列に連結された構造を主に使用することができる。スイッチング素子としては、一般的にトランジスタを使用するが、ダイオードを使用する場合もある。例えば、1個のトランジスタと1個の抵抗変化物質とが連結された構造を1Tr−1R構造と呼んだりもする。

【0004】

最近では、スイッチング素子と抵抗変化物質とを1つの単一素子として統合するための技術が試みられている。この場合、1つの素子がスイッチング機能とメモリ機能とを同時に遂行することが可能である。

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は、印加された電圧によって抵抗が変化する抵抗変化物質を含み、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる半導体素子を提供するものである。

【0006】

本発明はまた、該半導体素子の製造方法を提供するものである。

【課題を解決するための手段】

【0007】

本発明は一類型によれば、絶縁基板と、前記絶縁基板上に配置されたチャネル層と、前記チャネル層の上部表面から前記チャネル層の内部に少なくとも部分的に延びて配置されたゲートと、前記チャネル層の上部で、前記ゲートの両側面にそれぞれ配置されたソース及びドレインと、前記ゲートの周囲を取り囲み、前記ゲートを、前記チャネル層、前記ソース及び前記ドレインから電気的に絶縁させるゲート絶縁膜と、前記絶縁基板と前記ゲートとの間に配置される抵抗変化物質層と、を含む半導体素子が提供される。

【0008】

一実施形態で、前記抵抗変化物質層は、前記ゲートと直接に接触してもよい。

【0009】

他の実施形態で、前記抵抗変化物質層と前記ゲートとの間に、前記ゲート絶縁膜が配置されてもよい。

【0010】

例えば、前記抵抗変化物質層は、丸い底面を有し、前記抵抗変化物質層の前記丸い底面の中心部は、前記絶縁基板と接し、前記丸い底面の周辺部は、前記チャネル層と接してもよい。

【0011】

前記チャネル層は、第1導電型にドーピングされた単結晶半導体からなり、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされた単結晶半導体からなってもよい。

【0012】

前記抵抗変化物質層は、酸素欠乏欠陥が相対的に多い第1抵抗変化物質層、及び酸素欠乏欠陥が相対的に少ない第2抵抗変化物質層を含んでもよい。

【0013】

前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、電流の流れる方向に沿って順に配置されてもよい。

【0014】

例えば、前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、前記絶縁基板上で互いに隣接して配置され、前記第1抵抗変化物質層及び前記第2抵抗変化物質層が、いずれも前記絶縁基板と前記ゲートとに接触してもよい。

【0015】

また、本発明の他の類型によれば、チャネル層と、前記チャネル層の両側上部にそれぞれ配置されたソース及びドレインと、前記ソースと前記ドレインとの間で、前記チャネル層の上部中心領域に配置された抵抗変化物質層と、前記抵抗変化物質層上に配置されたゲートと、前記ゲートの周囲を取り囲むゲート絶縁膜と、を含む半導体素子が提供される。

【0016】

一実施形態で、前記ゲート絶縁膜は、前記ゲートの少なくとも下部面を取り囲むように形成されてもよい。

【0017】

前記ゲート絶縁膜は、前記ゲートの下部面と前記チャネル層との間、及び前記ゲートの下部面と前記抵抗変化物質層との間に配置されてもよい。

【0018】

前記抵抗変化物質層は、前記ゲートと直接接触し、前記ゲート絶縁膜は、前記ゲートの下部面と前記チャネル層との間に配置されてもよい。

【0019】

前記半導体素子は、隣接した他のセルの半導体素子との電気的隔離のために、前記チャネル層の両側面に配置される絶縁膜をさらに含んでもよい。

【0020】

また、前記半導体素子は、前記ソース及び前記ドレインを覆うように形成され、前記ゲートまたは前記ゲート絶縁膜の周囲を取り囲むパッシベーション層をさらに含んでもよい。

【0021】

また、前記半導体素子は、前記パッシベーション層を貫通し、前記ソース及び前記ドレインにそれぞれ電気的に連結されるソース電極とドレイン電極とをさらに含んでもよい。

【0022】

一実施形態で、前記抵抗変化物質層の少なくとも一部は、前記チャネル層の内部に延びており、前記抵抗変化物質層の上部は、前記チャネル層上に突出してもよい。

【0023】

一実施形態で、前記チャネル層は、単結晶半導体基板を第1導電型にドーピングして形成され、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされて形成されてもよい。

【0024】

前記半導体素子は、前記抵抗変化物質層の下部を取り囲む前記チャネル層の一部領域を前記第1導電型に高濃度にドーピングして形成されたドーピング領域をさらに含んでもよい。

【0025】

前記抵抗変化物質層は、酸素欠乏欠陥が相対的に多い第1抵抗変化物質層、及び酸素欠乏欠陥が相対的に少ない第2抵抗変化物質層を含んでもよい。

【0026】

前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、前記ソースと前記ドレインとの間の電流フロー方向に沿って順に配置されてもよい。

【0027】

例えば、前記抵抗変化物質層は、前記ソースと前記ドレインとの間の電流フロー方向に沿って順に配列された前記第1抵抗変化物質層、前記第2抵抗変化物質層、及び前記第1抵抗変化物質層を含んでもよい。

【0028】

本発明のさらに他の類型によれば、絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレインを含む構造を設ける段階と、前記ソースと前記ドレインとの間の前記チャネル層を部分的にエッチングし、前記チャネル層内にリセス領域を形成する段階と、前記リセス領域の内壁に全体的にゲート絶縁膜を形成する段階と、前記絶縁基板の表面が露出されるまで、前記リセス領域の底面にある前記ゲート絶縁膜の一部と前記チャネル層の一部とを除去する段階と、前記リセス領域内の前記絶縁基板の表面上に抵抗変化物質層を形成する段階と、前記リセス領域にゲート電極材料を充填してゲートを形成する段階と、を含む半導体素子の製造方法が提供される。

【0029】

ここで、絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレインを含む構造を設ける前記段階は、絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレイン、前記チャネル層の上部表面上で、前記ソースと前記ドレインとの間に部分的に形成された臨時ゲート、前記臨時ゲートの下部面と側面とを取り囲むゲート絶縁膜、及び前記ゲート絶縁膜と前記臨時ゲートとを取り囲むように、前記チャネル層の上部表面上に形成されたパッシベーション層を含むトランジスタを設ける段階と、前記臨時ゲートが現れるまで、前記パッシベーション層を研磨する段階と、前記チャネル層の上部表面が露出されるまで、前記臨時ゲートと前記ゲート絶縁膜とを選択的にエッチングし、前記パッシベーション層内に貫通ホールを形成する段階と、を含んでもよい。

【0030】

前記貫通ホールを形成する段階で、前記臨時ゲートの下部に形成された前記ゲート絶縁膜が除去され、前記臨時ゲートの側面に形成された前記ゲート絶縁膜は、前記パッシベーション層の前記貫通ホールの側壁に残ってもよい。

【0031】

前記リセス領域を形成する段階は、前記貫通ホールを介して露出された前記チャネル層を部分的にエッチングする段階を含んでもよい。

【0032】

前記半導体素子の製造方法は、前記パッシベーション層にコンタクトホールを形成し、前記コンタクトホール内に電極材料を充填し、前記ソース及び前記ドレインにそれぞれ連結されるソース電極とドレイン電極とを形成する段階をさらに含んでもよい。

【0033】

前記半導体素子の製造方法は、前記リセス領域内の前記絶縁基板の表面上に前記抵抗変化物質層を形成した後、前記抵抗変化物質層上に前記ゲート絶縁膜を形成する段階をさらに含んでもよい。

【0034】

一実施形態で、前記リセス領域が丸い形態の底面を有するように、前記チャネル層をエッチングしてもよい。

【0035】

また、前記リセス領域内の前記絶縁基板の表面上に抵抗変化物質層を形成する段階は、前記リセス領域の内壁に第1抵抗変化物質層を形成し、前記リセス領域の中心にある前記第1抵抗変化物質層を除去する段階と、イオン注入法で、前記第1抵抗変化物質層内に酸素欠乏欠陥を形成する段階と、前記リセス領域の中心部に第2抵抗変化物質層を形成する段階と、を含んでもよい。

【0036】

また、本発明のさらに他の類型によれば、チャネル層、前記チャネル層の両側上部面をドーピングして形成されたソース及びドレイン、前記チャネル層の上部面上で、前記ソースと前記ドレインとの間に配置された臨時ゲート、前記臨時ゲートの下部面と側面とを取り囲むゲート絶縁膜、前記ゲート絶縁膜を取り囲むように、前記チャネル層上に形成されたパッシベーション層を含む構造を設ける段階と、前記ゲート絶縁膜の底面が露出されるように、前記臨時ゲートを除去して開口を形成する段階と、前記開口内の前記ゲート絶縁膜の底面と、前記ゲート絶縁膜下部の前記チャネル層との一部をエッチングし、前記チャネル層内にリセス領域を形成する段階と、前記リセス領域内に抵抗変化物質層を形成する段階と、前記抵抗変化物質層上であって、前記開口内にゲート電極材料を充填してゲートを形成する段階と、を含む半導体素子の製造方法が提供される。

【0037】

前記チャネル層は、単結晶半導体基板を第1導電型にドーピングして形成され、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされて形成されてもよい。

【0038】

前記臨時ゲートを除去して開口を形成する段階で、前記開口の内壁には、前記ゲート絶縁膜が残ってもよい。

【0039】

また、前記リセス領域を形成する段階は、前記開口の底面の中心部が露出されて底面の周辺部が覆われるように、前記開口の内壁をマスクで取り囲む段階と、前記マスクによって覆われていない前記ゲート絶縁膜の底面と、前記チャネル層の一部とを除去する段階と、を含んでもよい。

【0040】

前記半導体素子の製造方法は、前記リセス領域内に抵抗変化物質層を形成する段階後、前記抵抗変化物質層の上部表面を覆うように、前記マスク間に前記ゲート絶縁膜の底面を形成する段階と、前記ゲート絶縁膜の側壁にある前記マスクを除去する段階と、をさらに含んでもよい。

【0041】

また、前記半導体素子の製造方法は、前記リセス領域を形成した後、前記リセス領域周囲の前記チャネル層にイオンを注入することによって、前記リセス領域周囲の前記チャネル層にドーピング領域を形成する段階をさらに含んでもよい。

【0042】

また、前記リセス領域内に抵抗変化物質層を形成する段階は、例えば、前記リセス領域の内壁に第1抵抗変化物質層を形成し、前記リセス領域の中心にある前記第1抵抗変化物質層を除去する段階と、イオン注入法で、前記第1抵抗変化物質層内に酸素欠乏欠陥を形成する段階と、前記リセス領域の中心部に第2抵抗変化物質層を形成する段階と、を含んでもよい。

【発明の効果】

【0043】

本発明の半導体素子は、印加された電圧によって抵抗が変化する抵抗変化物質を含み、スイッチの機能と不揮発性メモリの機能とを同時に遂行することが可能である。特に、該半導体素子の場合、チャネル層の主な材料として、単結晶シリコンを使用し、ソースとドレインとの間に抵抗変化物質を連結させて配置するために、高い駆動速度を得ることが可能である。また前記半導体素子の製造方法は、抵抗変化物質に高熱を加える工程がないために、半導体素子の製造過程で、抵抗変化物質の特性を劣化させる恐れがない。

【図面の簡単な説明】

【0044】

【図1】一実施形態による半導体素子の概略的な構造を示す断面図である。

【図2A】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2B】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2C】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2D】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2E】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2F】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2G】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図2H】図1に図示された半導体素子の製造過程を概略的に示す断面図である。

【図3】他の実施形態による半導体素子の概略的な構造を示す断面図である。

【図4】さらに他の実施形態による半導体素子の概略的な構造を示す断面図である。

【図5】図4に図示された半導体素子の製造過程の一部を概略的に示す断面図である。

【図6】さらに他の実施形態による半導体素子の概略的な構造を示す断面図である。

【図7A】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7B】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7C】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7D】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7E】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7F】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7G】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7H】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図7I】図6に図示された半導体素子の製造過程を概略的に示す断面図である。

【図8】さらに他の実施形態による半導体素子の概略的な構造を示す断面図である。

【図9】さらに他の実施形態による半導体素子の概略的な構造を示す断面図である。

【図10A】図9に図示された半導体素子の製造過程を概略的に示す断面図である。

【図10B】図9に図示された半導体素子の製造過程を概略的に示す断面図である。

【図10C】図9に図示された半導体素子の製造過程を概略的に示す断面図である。

【図11】さらに他の実施形態による半導体素子の概略的な構造を示す断面図である。

【発明を実施するための形態】

【0045】

以下、添付された図面を参照しつつ、抵抗変化物質を含む半導体素子及びその製造方法について詳細に説明する。以下の図面で同じ参照符号は、同じ構成要素を指し、図面上で各構成要素の大きさは、説明の明瞭さ及び便宜さのために誇張されていることがある。

【0046】

図1は、一実施形態による半導体素子100の概略的な構造を示す断面図を図示している。図1を参照すれば、一実施形態による半導体素子100は、絶縁基板101、絶縁基板101上に配置されたチャネル層105、チャネル層105の上部表面からチャネル層105の内部に少なくとも部分的に延びて配置されたゲート103、ゲート103の周囲を取り囲むゲート絶縁膜104、前記チャネル層105上で、ゲート103の両側面にそれぞれ配置されたソース110a及びドレイン110b、並びに絶縁基板101とゲート103との間に配置される抵抗変化物質層102を含んでもよい。ゲート絶縁膜104は、ゲート103の周囲を取り囲みつつ、ゲート103を、チャネル層105並びにソース110a及びドレイン110bから電気的に絶縁させる役割を行う。

【0047】

絶縁基板101は、例えば、SiO2のような材料からなる酸化物基板であってもよい。図1には、絶縁基板101が例示的に1層の絶縁層だけを含むと図示されている。しかし、絶縁基板101は、例えば、SOI(silicon on insulator)のように、シリコン層上にシリコン酸化物層が形成された多層基板であってもよい。

【0048】

絶縁基板101上に形成されたチャネル層105は、例えば、単結晶シリコンからなってもよい。単結晶シリコン以外にも、電子移動度(electron mobility)にすぐれる他の化合物半導体の結晶がチャネル層105の材料として使用されてもよい。また、チャネル層105は、例えば、p型またはn型にドーピングされてもよい。図1に図示されているように、チャネル層105は、一部領域が凹んでリセス領域が形成されているリセス・チャネル(recess channel)構造を有してもよい。

【0049】

ゲート103は、チャネル層105の上部表面からチャネル層105内部の少なくとも一部(すなわち、リセス領域)まで延びて配置されてもよい。ゲート103は、例えば、多結晶シリコン(poly−Si)や金属材料からなってもよい。また、チャネル層105の上部表面には、ゲート103の両側面に、ソース110a及びドレイン110bが配置されてもよい。チャネル層105がp型にドーピングされた単結晶シリコンからなる場合、前記ソース110a及びドレイン110bは、n型にドーピングされた単結晶シリコンからなってもよい。もしチャネル層105がn型にドーピングされた場合には、ソース110a及びドレイン110bは、p型にドーピングされてもよい。図1には、ソース110a及びドレイン110bが単一層として図示されているが、ソース110a及びドレイン110bのそれぞれは、例えば、nドーピング層とn+ドーピング層との二重層構造によって形成されてもよい。一方、ゲート103の周囲を取り囲むゲート絶縁膜104は、チャネル層105、ソース110a及びドレイン110bとゲート103とを電気的に分離する役割を行う。ゲート絶縁膜104として、例えば、SiO2やSiNxのような材料を使用することができ、または、HfSiON、ZrSiONのような高誘電率(high−k)材料を使用することもできる。

【0050】

抵抗変化物質層102は、絶縁基板101とゲート103との間に配置されてもよい。図1に図示されているように、抵抗変化物質層102の下部表面は、絶縁基板101と直接接触し、上部表面は、ゲート103と直接接触し、側面は、チャネル層105と直接接触してもよい。抵抗変化物質層102は、印加電圧によって抵抗が変化する抵抗変化物質からなってもよい。例えば、抵抗変化物質にセット電圧(set voltage)が印加されれば、抵抗変化物質の抵抗が低くなるが、一般的にこのときを、オン(ON)状態と呼ぶ。また、抵抗変化物質にリセット電圧(reset voltage)が印加されれば、抵抗変化物質の抵抗が高くなるが、一般的にこのときを、オフ(OFF)状態と呼ぶ。一般的に、抵抗変化メモリ素子は、抵抗変化物質のこのようなオン状態とオフ状態とのスイッチングを利用してデータを保存することができる。一方、記録されたデータを読み取るときは、抵抗変化物質の抵抗を変化させない読み取り電圧(read voltage)を抵抗変化物質に印加することができる。

【0051】

抵抗変化物質層102に使われるこのような抵抗変化物質としては、例えば、遷移金属酸化物(TMO:transition metal oxide)を挙げることができる。例えば、抵抗変化層102は、Ni酸化物、Cu酸化物、Ti酸化物、Co酸化物、Hf酸化物、Zr酸化物、Zn酸化物、W酸化物、Nb酸化物、TiNi酸化物、LiNi酸化物、Al酸化物、InZn酸化物、V酸化物、SrZr酸化物、SrTi酸化物、Cr酸化物、Fe酸化物、Ta酸化物及びそれらの混合物のうち、少なくともいずれか一つによって形成されてもよい。それ以外にも、Pr1−xCaxMnO3(PCMO)、SrTiO3(STO)のような多成分系金属酸化物、固体電解質物質などのように、電圧/電流印加による抵抗変化特性を有すると知られている抵抗変化物質などが使用されてもよい。

【0052】

前述の構造を有する半導体素子100の動作は、次の通り説明することができる。半導体素子100は、抵抗変化物質層102をチャネルの一部として含むトランジスタの構造を有するので、ゲート103にスレショルド電圧より低い電圧が印加されれば、半導体素子100は、OFF状態にあることになる。従って、ソース110a及びドレイン110bに電圧が印加されても、チャネル層105と抵抗変化物質層102とには、電流が流れない。

【0053】

ゲート103に、スレショルド電圧以上の電圧が印加されれば、半導体素子100は、ON状態となる。それにより、チャネル層105と抵抗変化物質層102とを介して、ソース110aとドレイン110bとの間に電流が流れることになる。図1に図示されているように、チャネル層105は、抵抗変化物質層102によって2つの部分に分離されているために、ソース110aとドレイン110bとの間に流れる電流は、抵抗変化物質層102を必ず通過することになる。このとき、ソース110aとドレイン110bとの電位差によって、抵抗変化物質層102の抵抗が変化しうる。

【0054】

例えば、ソース110aとドレイン110bとの電位差がセット電圧に該当すれば、抵抗変化物質層102の抵抗が低くなる。それにより、ソース−ドレイン間の電流が増加する。また、ソース110aとドレイン110bとの電位差がリセット電圧に該当すれば、抵抗変化物質層102の抵抗が高くなる。それにより、ソース−ドレイン間の電流が低くなる。そして、ソース110aとドレイン110bとの電位差が読み取り電圧に該当すれば、抵抗変化物質層102の抵抗は、変化しない。このとき、ソース−ドレイン間の電流を測定し、抵抗変化物質層102の抵抗状態を読み取ることができる。従って、ゲート103に印加される電圧によって、半導体素子100のON/OFFスイッチングが可能であり、ソース110a及びドレイン110bに印加される電圧によって、抵抗変化物質層102の抵抗を変化させたり、抵抗値を読み取る動作を遂行したりすることができる。

【0055】

図2Aないし図2Hは、図1に図示された半導体素子100の製造過程を概略的に示す断面図である。以下、図2Aないし図2Hを参照しつつ、一実施形態による半導体素子100の製造方法について説明する。

【0056】

初めに、図2Aに図示されているように、一般的なトランジスタの製造方法によって、絶縁基板101上にトップゲート型トランジスタを設ける。すなわち、図2Aを参照すれば、絶縁基板101、p型チャネル層105、チャネル層105の上部表面上に部分的に形成されたゲート絶縁膜104a及びゲート113、チャネル層105の上部領域で、ゲート113の両側に形成されたn型ソース110a及びn型ドレイン110b、並びに前記ゲート絶縁膜104a及びゲート113を取り囲むように、チャネル層105の上部表面上に形成されたパッシベーション層106を含むトップゲート型トランジスタが設けられる。p型チャネル層105、n型ソース110a及びn型ドレイン110bの代わりに、n型チャネル層105、p型ソース110a及びp型ドレイン110bが使用されてもよい。ソース110aは、nドーピング領域111aと、前記nドーピング領域111aの上部をさらに高濃度にドーピングして形成されたn+ドーピング領域112aとを有してもよい。同様に、ドレイン110bは、nドーピング領域111bと、n+ドーピング領域112bとを有してもよい。ここで、ゲート113は、最終的に形成される半導体素子100のゲート103ではなく、単に臨時のゲートであってもよい。

【0057】

前述のトランジスタが設けられれば、図2Bに図示されているように、一般的な化学機械研磨(CMP:chemical mechanical polishing)方式で、ゲート113が現れるまでパッシベーション層106を除去する。ゲート113が現れれば、図2Cに図示されているように、チャネル層105の上部表面が露出されるまで、乾式エッチング方式で、ゲート113とゲート絶縁膜104aとを選択的にエッチングして除去する。それにより、ゲート113が除去されつつ、パッシベーション層106内に、貫通ホール107が形成される。このとき、ゲート絶縁膜104aは、ゲート113の下部に形成された部分だけ除去され、ゲート113の側面に形成された部分は、依然としてパッシベーション層106の貫通ホール107の側壁に残ることになる。

【0058】

その後には、図2Dを参照すれば、貫通ホール107を介して露出されたチャネル層105を部分的にエッチングし、チャネル層105内にリセス領域108を形成することができる。このとき、リセス領域108の底面は、チャネル層105内に形成されてもよい。前述の過程で、ゲート絶縁膜104aの下部にあるソース110a及びドレイン110bの一部領域が共に除去されてもよい。次に、図2Eを参照すれば、リセス領域108の内壁に、すなわち、前記露出されたチャネル層105、ソース110a及びドレイン110bの表面に、全体的にゲート絶縁膜104bを形成する。それにより、図2Eに図示されているように、前記露出されたチャネル層105、ソース110a及びドレイン110bの表面は、ゲート絶縁膜104bで完全に覆われる。このとき、チャネル層105、ソース110a及びドレイン110bの表面に形成された下部のゲート絶縁膜104bと、パッシベーション層106の貫通ホール107の側壁に形成された上部のゲート絶縁膜104aとが連結され、1層のゲート絶縁膜104が形成される。

【0059】

次に、図2Fに図示されているように、異方性エッチング方式を利用し、絶縁基板101の表面が露出されるまで、リセス領域108の底面にあるゲート絶縁膜104bの一部と、チャネル層105の一部とを順次除去する。このように、絶縁基板101が露出されれば、図2Gに図示されているように、例えば、化学的気相蒸着法(CVD)や物理的気相蒸着法(PVD)を利用し、リセス領域108内の絶縁基板101の表面上に抵抗変化物質層102を形成する。図2Gには、抵抗変化物質層102が下部ゲート絶縁膜104bの全体を覆うと図示されているが、必ずしもこれに限定されるものではない。抵抗変化物質層102は、リセス領域108内に部分的に充填され、下部ゲート絶縁膜104bの一部が露出されてもよい。

【0060】

最後に、図2Hに図示されているように、貫通ホール107とリセス領域108とにゲート電極材料を充填し、ゲート103を形成することができる。その後、ゲート103両側のパッシベーション層106に、エッチングによってコンタクトホールを形成し、コンタクトホール内に電極材料を充填し、ソース110a及びドレイン110bにそれぞれ連結されるソース電極109aとドレイン電極109bとを形成することができる。または、貫通ホール107内とリセス領域108内にゲート103を形成する前に、貫通ホール107両側のパッシベーション層106をエッチングし、コンタクトホールを初めに形成することもできる。その後、貫通ホール107及びリセス領域108、及びその両側のコンタクトホールの内部に電極材料を充填し、ゲート103と、ソース電極109aと、ドレイン電極109bとを同時に形成することも可能である。

【0061】

抵抗変化物質層102は、一般的に、高温で抵抗変化特性を失いやすい。従って、半導体素子100を製造する過程で、抵抗変化物質層102を初めに形成した後、高温処理工程が遂行される場合には、抵抗変化物質層102が劣化され、動作の信頼性が低下しうる。しかし、図2Aないし図2Hで説明した方式で半導体素子100を製造する場合、抵抗変化物質層102を形成した後には、高温処理工程が遂行されないために、高温によって抵抗変化物質層102が劣化したり変形したりするリスクが少ない。

【0062】

一方、図1及び図2Aないし図2Hに図示された実施形態では、抵抗変化物質層102が、上部のゲート103と直接に接触している。しかし、抵抗変化物質層102とゲート103との間に、ゲート絶縁膜104がさらに配置されることも可能である。図3は、他の実施形態による半導体素子200の概略的な構造を示す断面図である。図3に図示された実施形態の場合、抵抗変化物質層102とゲート103との間に、ゲート絶縁膜104がさらに配置されているという点で、図1に図示された実施形態と違いがある。図3に図示された半導体素子200を製造する方法は、次の通りである。初めに、図2Aないし図2Gに図示された工程を順次遂行する。そして、図2Gに図示された工程で、抵抗変化物質層102を形成した後、抵抗変化物質層102上に、ゲート絶縁膜104を形成する。その後、図2Hで説明した方式でゲート103を形成すれば、図3に図示された半導体素子200を得ることができる。

【0063】

また図4は、さらに他の実施形態による半導体素子300の概略的な構造を示す断面図である。図1及び図3に図示された半導体素子100、200の場合、チャネル層105内のリセス領域108は、平らな底面を有し、抵抗変化物質層102も、平らな底面を有する。しかし、図4に図示された半導体素子300で、チャネル層105のリセス領域108は、丸い形態の底面を有し、同様に抵抗変化物質層102も、丸い形態の底面を有してもよい。従って、抵抗変化物質層102の丸い底面の中心部は、絶縁基板101と接し、丸い底面の周辺部は、チャネル層105と接してもよい。この場合、工程誤差による半導体素子300のスレショルド電圧の変化を減らすことができ、半導体素子300のスレショルド電圧を安定的に維持することができる。

【0064】

図4に図示された半導体素子300の製造工程は、図2Aないし図2Cに図示された工程をそのまま含んでもよい。図2Cの工程を遂行した後、図5に図示されているように、例えば、異方性エッチング方式で、チャネル層105内のリセス領域108が丸い形態の底面を有するように、チャネル層105をエッチングしてもよい。その後、図2Eないし図2Hに図示された工程を遂行すれば、図4に図示された丸い形態のリセス・チャネルを有する半導体素子300を得ることができる。

【0065】

以上で説明した半導体素子100、200、300は、SOIのような絶縁基板101上に形成され、リセス構造のチャネル層105を有する。しかし、前述の構造の半導体素子100、200、300のような機能を有する半導体素子を、例えば、シリコンのような半導体バルク基板上に形成することも可能である。図6は、さらに他の実施形態による半導体素子400の概略的な構造を示す断面図である。図6を参照すれば、本実施形態による半導体素子400は、チャネル層401、前記チャネル層401の両側上部にそれぞれ配置されたソース410a及びドレイン410b、前記ソース410aとドレイン410bとの間にあるチャネル層401の上部中心領域に配置された抵抗変化物質層402、前記抵抗変化物質層402上に配置されたゲート403、及び前記ゲート403の周囲を取り囲むゲート絶縁膜404を含んでもよい。図6に図示されているように、ゲート絶縁膜404は、ゲート403の少なくとも下部面を取り囲み、選択的にゲート403の周囲面をさらに取り囲むように形成される。図6には、ゲート絶縁膜404が、ゲート403と抵抗変化物質層402との間にも配置されていると図示されているが、抵抗変化物質層402は、ゲート403と直接接触することもできる。その場合、ゲート絶縁膜404は、ゲート403の下部面と、抵抗変化物質層402との間には配置されず、ゲート403の下部面とチャネル層401との間にのみ配置されてもよい。

【0066】

図6に図示されているように、チャネル層401の両側面には、隣接した他のセルの半導体素子との電気的隔離のために、絶縁膜415a、415bがさらに配置されてもよい。絶縁膜415a、415bは、例えば、STI(shallow trench isolation)であってもよい。また、絶縁膜415a、415b、ソース410a及びドレイン410bを覆うように、パッシベーション層406がさらに形成される。パッシベーション層406は、ゲート403またはゲート絶縁膜404の周囲を取り囲むように形成される。また、前記パッシベーション層406を貫通し、ソース410a及びドレイン410bにそれぞれ電気的に連結されるソース電極409aとドレイン電極409bとがさらに形成される。図6で、ソース410a及びドレイン410bは、単一層として図示されているが、前述のように、ドーピング濃度の異なった2層の層を有することもできる。

【0067】

前記抵抗変化物質層402の少なくとも一部は、図6に図示されているように、チャネル層401の内部に延びている。また、図6の例で、抵抗変化物質層402がチャネル層401上に突出していると図示されているが、必ずしもこれに限定されるものではない。例えば、抵抗変化物質層402の上部表面は、チャネル層401の上部表面と同じ高さに形成されてもよく、チャネル層401の上部表面より若干低い高さに形成されてもよい。

【0068】

図6の実施形態で、チャネル層401は、例えば、単結晶シリコンバルク基板をp型にドーピングして形成することができる。この場合、ソース410a及びドレイン410bは、n型にドーピングされる。その代わりに、チャネル層401は、単結晶シリコンバルク基板をn型にドーピングして形成することもできる。その場合には、ソース410a及びドレイン410bは、p型にドーピングされる。また、チャネル層401は、シリコン以外に、他の化合物半導体の単結晶基板に形成されてもよい。

【0069】

図7Aないし図7Iは、図6に図示された半導体素子400の製造過程を概略的に示す断面図である。以下、図7Aないし図7Iを参照しつつ、一実施形態による半導体素子400の製造方法について説明する。

【0070】

初めに、図7Aに図示されているように、一般的なトランジスタの製造方法によって、単結晶シリコンバルク基板上に、トップゲート型トランジスタを設ける。すなわち、図7Aを参照すれば、単結晶シリコンバルク基板をドーピングして形成されたチャネル層401、チャネル層401の両側上部面をドーピングして形成されたソース410a及びドレイン410bと、チャネル層401の上部表面上でソース410aとドレイン410bとの間に配置されたゲート絶縁膜404及びゲート413と、チャネル層401の両側面に隣接して形成された絶縁膜415a、415bと、ゲート絶縁膜404、ゲート413、絶縁膜415a、415b、ソース410a及びドレイン410bを覆うパッシベーション層406と、を含むトップゲート型トランジスタが設けられる。例えば、チャネル層401がp型にドーピングされる場合、ソース410a及びドレイン410bは、n型にドーピングされてもよい。また、チャネル層401がn型にドーピングされる場合、ソース410a及びドレイン410bは、p型にドーピングされてもよい。ゲート413は、例えば、多結晶シリコンからなってもよい。ここで、多結晶シリコンゲート413は、最終的に形成される半導体素子400のゲート403ではなく、単に臨時のゲートであってもよい。

【0071】

前述のトランジスタが設けられれば、図7Bに図示されているように、一般的な化学機械研磨(CMP)方式で、ゲート413が現れるまで、パッシベーション層406を除去する。ゲート413が現れれば、図7Cに図示されているように、多結晶シリコンからなるゲート413を、エッチングによって完全に除去する。それにより、ゲート413を取り囲んでいたゲート絶縁膜404だけが残り、ゲート絶縁膜404内には、ゲート413があったところに開口407が形成される。従って、開口407の内壁には、ゲート絶縁膜404が残ることになる。

【0072】

次に、図7Dを参照すれば、ゲート絶縁膜404内の開口407の内壁を、例えば、多結晶シリコンからなるマスク423で取り囲む。それにより、図7Dに図示されているように、開口407の底面の中心部だけが露出され、底面の周辺部は、マスク423によって覆われる。図7Dのマスク423を形成する工程は、例えば、パッシベーション層406及びゲート絶縁膜404上に多結晶シリコンを全体的に一定に蒸着する段階と、エッチングによって上部表面にある多結晶シリコンを除去する段階とを含んでもよい。それにより、パッシベーション層406及びゲート絶縁膜404の上部表面では、多結晶シリコンが除去され、ゲート絶縁膜404内の開口407の内壁には、多結晶シリコンが残り、マスク423が形成される。

【0073】

その後、図7Eを参照すれば、マスク423によって覆われていないゲート絶縁膜404の底面を除去し、次に、ゲート絶縁膜404下部のチャネル層401の一部までもエッチングによって除去する。それにより、図7Eに図示されているように、チャネル層401内には、部分的にリセス領域408が形成され、このとき、リセス領域408の底面は、チャネル層401内に形成される。

【0074】

次に、図7Fを参照すれば、例えば、化学的気相蒸着法(CVD)や物理的気相蒸着法(PVD)を利用し、リセス領域408内に抵抗変化物質層402を充填する。図7Fには、抵抗変化物質層402がチャネル層401の上部表面を越えて、ゲート絶縁膜404まで形成されていると図示されているが、必ずしもこれに限定されるものではない。例えば、抵抗変化物質層402の上部表面は、チャネル層401の上部表面と同じ高さに形成されてもよく、またはチャネル層401の上部表面より若干低い高さに形成されてもよい。

【0075】

抵抗変化物質層402を形成した後には、図7Gに図示されているように、抵抗変化物質層402の上部表面を覆うように、マスク423間にゲート絶縁膜404の底面404aを形成する。それにより、開口407の側壁にあるゲート絶縁膜404が底面404aと連結される。その後、図7Hを参照すれば、ゲート絶縁膜404の側壁にあるマスク423を除去する。それにより、開口407内には、ゲート絶縁膜404だけが残ることになる。

【0076】

最後に、図7Iに図示されているように、開口407内にゲート電極材料を充填し、ゲート403を形成することができる。その後、ゲート403両側のパッシベーション層406にコンタクトホールを形成し、コンタクトホール内に電極材料を充填し、ソース410a及びドレイン410bにそれぞれ連結されるソース電極409aとドレイン電極409bとを形成することができる。または、開口407内にゲート403を形成する前に、開口407両側のパッシベーション層406をエッチングし、コンタクトホールを予め形成することも可能である。その後、開口407及びその両側のコンタクトホールの内部に電極材料を充填し、ゲート403並びにソース電極409a及びドレイン電極409bを同時に形成することも可能である。

【0077】

前述の方法で、図6に図示された半導体素子400を製造することができる。図6には、抵抗変化物質層402とゲート403との間にゲート絶縁膜404が形成されている。しかし、図1に図示された半導体素子100と同様に、ゲート403が抵抗変化物質層402と直接接触することも可能である。その場合、図7Gに図示されたゲート絶縁膜404の底面404aを形成する段階が省略されてもよい。

【0078】

一方、図1、図3及び図4に図示された半導体素子100、200、300の場合には、チャネル層105の両側が抵抗変化物質層102によって分離されており、ソース110aとドレイン110bとの間に流れる電流は、必ず抵抗変化物質層102を通過する。しかし、図6に図示された半導体素子400の場合、チャネル層401が抵抗変化物質層402の下部を介して、ソース410a及びドレイン410bと連結されている。従って、ソース410aとドレイン410bとの間に流れる電流の一部は、抵抗変化物質層402を通過せずに、チャネル層401に流れることもできる。その場合、抵抗変化物質層402を通過する電流の量が十分ではないこともある。

【0079】

図8は、ソース410aとドレイン410bとの間に流れる電流のほとんどが抵抗変化物質層402を通過するように構成された半導体素子500を図示している。図8を参照すれば、本実施形態による半導体素子500は、抵抗変化物質層402の下部を取り囲むチャネル層401の一部領域を高濃度にドーピングして形成された高濃度のドーピング領域420を含む。例えば、チャネル層401がp型にドーピングされ、ソース410a及びドレイン410bがn型にドーピングされた場合、ドーピング領域420は、p+ドーピングされてもよい。また、チャネル層401がn型にドーピングされ、ソース410a及びドレイン410bがp型にドーピングされた場合、ドーピング領域420は、n+ドーピングされてもよい。その場合、ドーピング領域420下部のチャネル層401に迂回して流れる電流がほとんどないために、ほとんどの電流が抵抗変化物質層402に流れる。前記高濃度のドーピング領域420は、例えば、図7Eに図示された段階で、リセス領域408を形成した後、リセス領域408の周囲のチャネル層401にイオンを注入することによって形成されてもよい。そして、図7Fないし図7Iの段階を遂行すれば、図8に図示された半導体素子500が製造される。図8に図示された半導体素子500の構成は、ドーピング領域420以外は、図6に図示された半導体素子400と同一である。

【0080】

以上では、抵抗変化物質層402が単一層で形成された場合について説明した。しかし、抵抗変化物質層402の抵抗変化特性をさらに向上させるために、抵抗変化物質層402は、少なくとも2層を含む多層構造に形成されてもよい。例えば、酸素欠乏欠陥(oxygen vacancy)が相対的に多いTiOx層と、酸素欠乏欠陥が相対的に少ない一般的なTiO2層とを、2つの電極間に電流フロー方向に沿って積層する場合、TiO2層とTiOx層との間を酸素欠乏欠陥が移動しつつ、抵抗変化特性を向上させることができる。

【0081】

図9は、前述のような多層構造の抵抗変化物質層402を含む半導体素子600を図示している。図9を参照すれば、抵抗変化物質層402は、電流の流れる方向に沿って、すなわち、ソース410aからドレイン410bへの方向に沿って、第1抵抗変化物質層402a、第2抵抗変化物質層402b及び第1抵抗変化物質層402aを含んでもよい。例えば、第1抵抗変化物質層402aは、酸素欠乏欠陥が相対的に多いTiOxからなり、第2抵抗変化物質層402bは、酸素欠乏欠陥が相対的に少ないTiO2からなってもよい。代わりに、第1抵抗変化物質層402aがTiO2からなり、第2抵抗変化物質層402bがTiOxからなってもよい。図9に図示された半導体素子600の構造は、抵抗変化物質層402を除けば、図6に図示された半導体素子400の構造と同一である。

【0082】

図10Aないし図10Cは、図9に図示された半導体素子600の製造過程を概略的に示す断面図である。初めに、前述の図7Aないし図7Eに図示された過程を遂行する。それにより、結果として、図10Aに図示されているように、チャネル層401内に、部分的にリセス領域408が形成された状態となる。その後、図10Bを参照すれば、リセス領域408内のチャネル層401の側壁部と、ゲート絶縁膜404の内壁とに、第1抵抗変化物質層402aを形成することができる。例えば、化学的気相蒸着法(CVD)や物理的気相蒸着法(PVD)を利用して、リセス領域408内に全体的に抵抗変化物質を充填した後、エッチングによって、リセス領域408中心部の抵抗変化物質を除去することができる。それにより、リセス領域408内のチャネル層401の側壁部と、ゲート絶縁膜404の内壁部分とにのみ抵抗変化物質が形成される。そして、図10Bに図示されているように、例えば、ハロイオン注入法(halo ion implantation)で抵抗変化物質内にイオンを注入することができる。それにより、酸素欠乏欠陥が内部に形成された第1抵抗変化物質層402aが形成される。

【0083】

その後、図10Cに図示されているように、第1抵抗変化物質層402a間に、すなわち、リセス領域408の中心部に第2抵抗変化物質層402bを形成する。それにより、ソース410aからドレイン410bへの経路に沿って、第1抵抗変化物質層402a、第2抵抗変化物質層402b及び第1抵抗変化物質層402aが順に形成される。その後には、前述の図7Gないし図7Iに図示された過程を遂行する。それにより、図9に図示された半導体素子600が製造される。

【0084】

図9に図示された半導体素子600の場合、第2抵抗変化物質層402bの両側に第1抵抗変化物質層402aが形成された構造を含んでいるが、必ずしもこれに限定されるものではない。例えば、半導体素子600は、単に1層の第1抵抗変化物質層402a及び1層の第2抵抗変化物質層402bのみを含むこともできる。その場合、図10Bに図示された段階で、リセス領域408内に充填された抵抗変化物質をエッチングし、チャネル層401及びゲート絶縁膜404のいずれか一方の内壁にのみ抵抗変化物質を残すことができる。

【0085】

また、図1、図3及び図4に図示された半導体素子100、200、300にも、前述の多層構造の抵抗変化物質層が適用されてもよい。図11は、多層構造の抵抗変化物質層102を含む半導体素子700を図示している。図11を参照すれば、半導体素子700は、絶縁基板101、絶縁基板101上に配置されたチャネル層105、チャネル層105の上部表面からチャネル層105の内部に少なくとも部分的に延びて配置されたゲート103、ゲート103の周囲を取り囲むゲート絶縁膜104、絶縁基板101とゲート103との間に配置されて第1抵抗変化物質層102aと第2抵抗変化物質層102bとを有する抵抗変化物質層102、及び前記チャネル層105上で、ゲート103の両側面にそれぞれ配置されたソース110a及びドレイン110bを含んでもよい。

【0086】

第1抵抗変化物質層102aと第2抵抗変化物質層102bは、図11に図示されているように、両側のチャネル層105間の電流フロー方向に沿って配置されている。従って、第1抵抗変化物質層102aと第2抵抗変化物質層102bは、いずれも絶縁基板101とゲート103とに直接接触するように配置されており、前記絶縁基板101上で互いに隣接して配置されてもよい。図11には、図1に図示された半導体素子100に、多層構造の抵抗変化物質層が適用された例が図示されているが、図3及び図4に図示された半導体素子200、300にも前記多層構造の抵抗変化物質層が同様に適用されてもよい。また、図9に図示された例のように、抵抗変化物質層102は、第1抵抗変化物質層102a、第2抵抗変化物質層102b及び第1抵抗変化物質層102aの3層構造を有することもできる。

【0087】

以上、本発明の理解を助けるために、抵抗変化物質を含む半導体素子及びその製造方法に係わる例示的な実施形態について説明し、かつ添付された図面に図示した。しかし、かような実施形態は、単に本発明を例示するためのものであり、それらを制限するものではないという点を理解せねばならない。そして、本発明は図示して説明した説明に限定されるものではないという点を理解せねばならない。それは、多様な他の変形が、本技術分野で当業者に可能であるためである。

【符号の説明】

【0088】

100、200、300、400、500、600、700 半導体素子

101 絶縁基板

102、402 抵抗変化物質層

102a、402a 第1抵抗変化物質層

102b、402b 第2抵抗変化物質層

103、113、403、413 ゲート

104、104a、104b、404 ゲート絶縁膜

105、401 チャネル層

106、406 パッシベーション層

107 貫通ホール

108 リセス領域

109a、409a ソース電極

109b、409b ドレイン電極

110a、410a ソース

110b、410b ドレイン

111a、111b nドーピング領域

112a、112b n+ドーピング領域

404a 底面

407 開口

408 リセス領域

415a、415b 絶縁膜

420 高濃度ドーピング領域

423 マスク

【特許請求の範囲】

【請求項1】

絶縁基板と、

前記絶縁基板上に配置されたチャネル層と、

前記チャネル層の上部表面から前記チャネル層の内部に少なくとも部分的に延びて配置されたゲートと、

前記チャネル層の上部で、前記ゲートの両側面にそれぞれ配置されたソース及びドレインと、

前記ゲートの周囲を取り囲み、前記ゲートを、前記チャネル層、前記ソース及び前記ドレインから電気的に絶縁させるゲート絶縁膜と、

前記絶縁基板と前記ゲートとの間に配置される抵抗変化物質層と、を含む半導体素子。

【請求項2】

前記抵抗変化物質層は、前記ゲートと直接に接触することを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記抵抗変化物質層と前記ゲートとの間に、前記ゲート絶縁膜が配置されていることを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記抵抗変化物質層は、丸い底面を有し、前記抵抗変化物質層の前記丸い底面の中心部は、前記絶縁基板と接し、前記丸い底面の周辺部は、前記チャネル層と接することを特徴とする請求項1に記載の半導体素子。

【請求項5】

前記チャネル層は、第1導電型にドーピングされた単結晶半導体からなり、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされた単結晶半導体からなることを特徴とする請求項1に記載の半導体素子。

【請求項6】

前記抵抗変化物質層は、酸素欠乏欠陥が相対的に多い第1抵抗変化物質層、及び酸素欠乏欠陥が相対的に少ない第2抵抗変化物質層を含むことを特徴とする請求項1に記載の半導体素子。

【請求項7】

前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、電流の流れる方向に沿って順に配置されたことを特徴とする請求項6に記載の半導体素子。

【請求項8】

前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、前記絶縁基板上で互いに隣接して配置され、前記第1抵抗変化物質層及び前記第2抵抗変化物質層がいずれも前記絶縁基板と前記ゲートとに接触することを特徴とする請求項6に記載の半導体素子。

【請求項9】

チャネル層と、

前記チャネル層の両側上部にそれぞれ配置されたソース及びドレインと、

前記ソースと前記ドレインとの間で、前記チャネル層の上部中心領域に配置された抵抗変化物質層と、

前記抵抗変化物質層上に配置されたゲートと、

前記ゲートの周囲を取り囲むゲート絶縁膜と、を含む半導体素子。

【請求項10】

前記ゲート絶縁膜は、前記ゲートの少なくとも下部面を取り囲むように形成されることを特徴とする請求項9に記載の半導体素子。

【請求項11】

前記ゲート絶縁膜は、前記ゲートの下部面と前記チャネル層との間、及び前記ゲートの下部面と前記抵抗変化物質層との間に配置されることを特徴とする請求項10に記載の半導体素子。

【請求項12】

前記抵抗変化物質層は、前記ゲートと直接接触し、前記ゲート絶縁膜は、前記ゲートの下部面と前記チャネル層との間に配置されることを特徴とする請求項10に記載の半導体素子。

【請求項13】

隣接した他のセルの半導体素子との電気的隔離のために、前記チャネル層の両側面に配置される絶縁膜をさらに含むことを特徴とする請求項9に記載の半導体素子。

【請求項14】

前記ソース及び前記ドレインを覆うように形成され、前記ゲートまたは前記ゲート絶縁膜の周囲を取り囲むパッシベーション層をさらに含むことを特徴とする請求項9に記載の半導体素子。

【請求項15】

前記パッシベーション層を貫通し、前記ソース及び前記ドレインにそれぞれ電気的に連結されるソース電極とドレイン電極とをさらに含むことを特徴とする請求項14に記載の半導体素子。

【請求項16】

前記抵抗変化物質層の少なくとも一部は、前記チャネル層の内部に延びており、前記抵抗変化物質層の上部は、前記チャネル層上に突出して形成されることを特徴とする請求項9に記載の半導体素子。

【請求項17】

前記チャネル層は、単結晶半導体基板を第1導電型にドーピングして形成され、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされて形成されることを特徴とする請求項9に記載の半導体素子。

【請求項18】

前記抵抗変化物質層の下部を取り囲む前記チャネル層の一部領域を前記第1導電型に高濃度にドーピングして形成されたドーピング領域をさらに含むことを特徴とする請求項17に記載の半導体素子。

【請求項19】

前記抵抗変化物質層は、酸素欠乏欠陥が相対的に多い第1抵抗変化物質層、及び酸素欠乏欠陥が相対的に少ない第2抵抗変化物質層を含むことを特徴とする請求項9に記載の半導体素子。

【請求項20】

前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、前記ソースと前記ドレインとの間の電流フロー方向に沿って順に配置されていることを特徴とする請求項19に記載の半導体素子。

【請求項21】

前記抵抗変化物質層は、前記ソースと前記ドレインとの間の電流フロー方向に沿って順に配列された前記第1抵抗変化物質層、前記第2抵抗変化物質層、及び前記第1抵抗変化物質層を含むことを特徴とする請求項19に記載の半導体素子。

【請求項22】

絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレインを含む構造を設ける段階と、

前記ソースと前記ドレインとの間の前記チャネル層を部分的にエッチングし、前記チャネル層内にリセス領域を形成する段階と、

前記リセス領域の内壁に全体的にゲート絶縁膜を形成する段階と、

前記絶縁基板の表面が露出されるまで、前記リセス領域の底面にある前記ゲート絶縁膜の一部と前記チャネル層の一部とを除去する段階と、

前記リセス領域内の前記絶縁基板の表面上に抵抗変化物質層を形成する段階と、

前記リセス領域にゲート電極材料を充填してゲートを形成する段階と、を含む半導体素子の製造方法。

【請求項23】

絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレインを含む構造を設ける前記段階は、

絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレイン、前記チャネル層の上部表面上で、前記ソースと前記ドレインとの間に部分的に形成された臨時ゲート、前記臨時ゲートの下部面と側面とを取り囲むゲート絶縁膜、及び前記ゲート絶縁膜と前記臨時ゲートとを取り囲むように、前記チャネル層の上部表面上に形成されたパッシベーション層を含むトランジスタを設ける段階と、

前記臨時ゲートが現れるまで、前記パッシベーション層を研磨する段階と、

前記チャネル層の上部表面が露出されるまで、前記臨時ゲートと前記ゲート絶縁膜とを選択的にエッチングし、前記パッシベーション層内に貫通ホールを形成する段階と、を含むことを特徴とする請求項22に記載の半導体素子の製造方法。

【請求項24】

前記貫通ホールを形成する段階で、前記臨時ゲートの下部に形成された前記ゲート絶縁膜が除去され、前記臨時ゲートの側面に形成された前記ゲート絶縁膜は、前記パッシベーション層の前記貫通ホールの側壁に残っていることを特徴とする請求項23に記載の半導体素子の製造方法。

【請求項25】

前記リセス領域を形成する段階は、前記貫通ホールを介して露出された前記チャネル層を部分的にエッチングする段階を含むことを特徴とする請求項23に記載の半導体素子の製造方法。

【請求項26】

前記パッシベーション層にコンタクトホールを形成し、前記コンタクトホール内に電極材料を充填し、前記ソース及び前記ドレインにそれぞれ連結されるソース電極とドレイン電極とを形成する段階をさらに含むことを特徴とする請求項23に記載の半導体素子の製造方法。

【請求項27】

前記リセス領域内の前記絶縁基板の表面上に前記抵抗変化物質層を形成した後、前記抵抗変化物質層上に前記ゲート絶縁膜を形成する段階をさらに含むことを特徴とする請求項22に記載の半導体素子の製造方法。

【請求項28】

前記リセス領域が丸い形態の底面を有するように、前記チャネル層をエッチングすることを特徴とする請求項22に記載の半導体素子の製造方法。

【請求項29】

前記リセス領域内の前記絶縁基板の表面上に抵抗変化物質層を形成する段階は、

前記リセス領域の内壁に第1抵抗変化物質層を形成し、前記リセス領域の中心にある前記第1抵抗変化物質層を除去する段階と、

イオン注入法で、前記第1抵抗変化物質層内に酸素欠乏欠陥を形成する段階と、

前記リセス領域の中心部に第2抵抗変化物質層を形成する段階と、を含むことを特徴とする請求項22に記載の半導体素子の製造方法。

【請求項30】

チャネル層、前記チャネル層の両側上部面をドーピングして形成されたソース及びドレイン、前記チャネル層の上部面上で、前記ソースと前記ドレインとの間に配置された臨時ゲート、前記臨時ゲートの下部面と側面とを取り囲むゲート絶縁膜、前記ゲート絶縁膜を取り囲むように、前記チャネル層上に形成されたパッシベーション層を含む構造を設ける段階と、

前記ゲート絶縁膜の底面が露出されるように、前記臨時ゲートを除去して開口を形成する段階と、

前記開口内の前記ゲート絶縁膜の底面と、前記ゲート絶縁膜下部の前記チャネル層との一部をエッチングし、前記チャネル層内にリセス領域を形成する段階と、

前記リセス領域内に抵抗変化物質層を形成する段階と、

前記抵抗変化物質層上であって、前記開口内にゲート電極材料を充填してゲートを形成する段階と、を含む半導体素子の製造方法。

【請求項31】

前記チャネル層は、単結晶半導体基板を第1導電型にドーピングして形成され、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされて形成されることを特徴とする請求項30に記載の半導体素子の製造方法。

【請求項32】

前記臨時ゲートを除去して開口を形成する段階で、前記開口の内壁には、前記ゲート絶縁膜が残っていることを特徴とする請求項30に記載の半導体素子の製造方法。

【請求項33】

前記リセス領域を形成する段階は、

前記開口の底面の中心部が露出されて底面の周辺部が覆われるように、前記開口の内壁をマスクで取り囲む段階と、

前記マスクによって覆われていない前記ゲート絶縁膜の底面と、前記チャネル層の一部とを除去する段階と、を含むことを特徴とする請求項32に記載の半導体素子の製造方法。

【請求項34】

前記リセス領域内に抵抗変化物質層を形成する段階後、

前記抵抗変化物質層の上部表面を覆うように、前記マスク間に前記ゲート絶縁膜の底面を形成する段階と、

前記ゲート絶縁膜の側壁にある前記マスクを除去する段階と、をさらに含むことを特徴とする請求項33に記載の半導体素子の製造方法。

【請求項35】

前記リセス領域を形成した後、前記リセス領域周囲の前記チャネル層にイオンを注入することによって、前記リセス領域周囲の前記チャネル層にドーピング領域を形成する段階をさらに含むことを特徴とする請求項30に記載の半導体素子の製造方法。

【請求項36】

前記リセス領域内に抵抗変化物質層を形成する段階は、

前記リセス領域の内壁に第1抵抗変化物質層を形成し、前記リセス領域の中心にある前記第1抵抗変化物質層を除去する段階と、

イオン注入法で、前記第1抵抗変化物質層内に酸素欠乏欠陥を形成する段階と、

前記リセス領域の中心部に第2抵抗変化物質層を形成する段階と、を含むことを特徴とする請求項30に記載の半導体素子の製造方法。

【請求項1】

絶縁基板と、

前記絶縁基板上に配置されたチャネル層と、

前記チャネル層の上部表面から前記チャネル層の内部に少なくとも部分的に延びて配置されたゲートと、

前記チャネル層の上部で、前記ゲートの両側面にそれぞれ配置されたソース及びドレインと、

前記ゲートの周囲を取り囲み、前記ゲートを、前記チャネル層、前記ソース及び前記ドレインから電気的に絶縁させるゲート絶縁膜と、

前記絶縁基板と前記ゲートとの間に配置される抵抗変化物質層と、を含む半導体素子。

【請求項2】

前記抵抗変化物質層は、前記ゲートと直接に接触することを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記抵抗変化物質層と前記ゲートとの間に、前記ゲート絶縁膜が配置されていることを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記抵抗変化物質層は、丸い底面を有し、前記抵抗変化物質層の前記丸い底面の中心部は、前記絶縁基板と接し、前記丸い底面の周辺部は、前記チャネル層と接することを特徴とする請求項1に記載の半導体素子。

【請求項5】

前記チャネル層は、第1導電型にドーピングされた単結晶半導体からなり、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされた単結晶半導体からなることを特徴とする請求項1に記載の半導体素子。

【請求項6】

前記抵抗変化物質層は、酸素欠乏欠陥が相対的に多い第1抵抗変化物質層、及び酸素欠乏欠陥が相対的に少ない第2抵抗変化物質層を含むことを特徴とする請求項1に記載の半導体素子。

【請求項7】

前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、電流の流れる方向に沿って順に配置されたことを特徴とする請求項6に記載の半導体素子。

【請求項8】

前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、前記絶縁基板上で互いに隣接して配置され、前記第1抵抗変化物質層及び前記第2抵抗変化物質層がいずれも前記絶縁基板と前記ゲートとに接触することを特徴とする請求項6に記載の半導体素子。

【請求項9】

チャネル層と、

前記チャネル層の両側上部にそれぞれ配置されたソース及びドレインと、

前記ソースと前記ドレインとの間で、前記チャネル層の上部中心領域に配置された抵抗変化物質層と、

前記抵抗変化物質層上に配置されたゲートと、

前記ゲートの周囲を取り囲むゲート絶縁膜と、を含む半導体素子。

【請求項10】

前記ゲート絶縁膜は、前記ゲートの少なくとも下部面を取り囲むように形成されることを特徴とする請求項9に記載の半導体素子。

【請求項11】

前記ゲート絶縁膜は、前記ゲートの下部面と前記チャネル層との間、及び前記ゲートの下部面と前記抵抗変化物質層との間に配置されることを特徴とする請求項10に記載の半導体素子。

【請求項12】

前記抵抗変化物質層は、前記ゲートと直接接触し、前記ゲート絶縁膜は、前記ゲートの下部面と前記チャネル層との間に配置されることを特徴とする請求項10に記載の半導体素子。

【請求項13】

隣接した他のセルの半導体素子との電気的隔離のために、前記チャネル層の両側面に配置される絶縁膜をさらに含むことを特徴とする請求項9に記載の半導体素子。

【請求項14】

前記ソース及び前記ドレインを覆うように形成され、前記ゲートまたは前記ゲート絶縁膜の周囲を取り囲むパッシベーション層をさらに含むことを特徴とする請求項9に記載の半導体素子。

【請求項15】

前記パッシベーション層を貫通し、前記ソース及び前記ドレインにそれぞれ電気的に連結されるソース電極とドレイン電極とをさらに含むことを特徴とする請求項14に記載の半導体素子。

【請求項16】

前記抵抗変化物質層の少なくとも一部は、前記チャネル層の内部に延びており、前記抵抗変化物質層の上部は、前記チャネル層上に突出して形成されることを特徴とする請求項9に記載の半導体素子。

【請求項17】

前記チャネル層は、単結晶半導体基板を第1導電型にドーピングして形成され、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされて形成されることを特徴とする請求項9に記載の半導体素子。

【請求項18】

前記抵抗変化物質層の下部を取り囲む前記チャネル層の一部領域を前記第1導電型に高濃度にドーピングして形成されたドーピング領域をさらに含むことを特徴とする請求項17に記載の半導体素子。

【請求項19】

前記抵抗変化物質層は、酸素欠乏欠陥が相対的に多い第1抵抗変化物質層、及び酸素欠乏欠陥が相対的に少ない第2抵抗変化物質層を含むことを特徴とする請求項9に記載の半導体素子。

【請求項20】

前記第1抵抗変化物質層及び前記第2抵抗変化物質層は、前記ソースと前記ドレインとの間の電流フロー方向に沿って順に配置されていることを特徴とする請求項19に記載の半導体素子。

【請求項21】

前記抵抗変化物質層は、前記ソースと前記ドレインとの間の電流フロー方向に沿って順に配列された前記第1抵抗変化物質層、前記第2抵抗変化物質層、及び前記第1抵抗変化物質層を含むことを特徴とする請求項19に記載の半導体素子。

【請求項22】

絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレインを含む構造を設ける段階と、

前記ソースと前記ドレインとの間の前記チャネル層を部分的にエッチングし、前記チャネル層内にリセス領域を形成する段階と、

前記リセス領域の内壁に全体的にゲート絶縁膜を形成する段階と、

前記絶縁基板の表面が露出されるまで、前記リセス領域の底面にある前記ゲート絶縁膜の一部と前記チャネル層の一部とを除去する段階と、

前記リセス領域内の前記絶縁基板の表面上に抵抗変化物質層を形成する段階と、

前記リセス領域にゲート電極材料を充填してゲートを形成する段階と、を含む半導体素子の製造方法。

【請求項23】

絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレインを含む構造を設ける前記段階は、

絶縁基板、前記絶縁基板上のチャネル層、前記チャネル層の上部領域の両側にそれぞれ形成されたソース及びドレイン、前記チャネル層の上部表面上で、前記ソースと前記ドレインとの間に部分的に形成された臨時ゲート、前記臨時ゲートの下部面と側面とを取り囲むゲート絶縁膜、及び前記ゲート絶縁膜と前記臨時ゲートとを取り囲むように、前記チャネル層の上部表面上に形成されたパッシベーション層を含むトランジスタを設ける段階と、

前記臨時ゲートが現れるまで、前記パッシベーション層を研磨する段階と、

前記チャネル層の上部表面が露出されるまで、前記臨時ゲートと前記ゲート絶縁膜とを選択的にエッチングし、前記パッシベーション層内に貫通ホールを形成する段階と、を含むことを特徴とする請求項22に記載の半導体素子の製造方法。

【請求項24】

前記貫通ホールを形成する段階で、前記臨時ゲートの下部に形成された前記ゲート絶縁膜が除去され、前記臨時ゲートの側面に形成された前記ゲート絶縁膜は、前記パッシベーション層の前記貫通ホールの側壁に残っていることを特徴とする請求項23に記載の半導体素子の製造方法。

【請求項25】

前記リセス領域を形成する段階は、前記貫通ホールを介して露出された前記チャネル層を部分的にエッチングする段階を含むことを特徴とする請求項23に記載の半導体素子の製造方法。

【請求項26】

前記パッシベーション層にコンタクトホールを形成し、前記コンタクトホール内に電極材料を充填し、前記ソース及び前記ドレインにそれぞれ連結されるソース電極とドレイン電極とを形成する段階をさらに含むことを特徴とする請求項23に記載の半導体素子の製造方法。

【請求項27】

前記リセス領域内の前記絶縁基板の表面上に前記抵抗変化物質層を形成した後、前記抵抗変化物質層上に前記ゲート絶縁膜を形成する段階をさらに含むことを特徴とする請求項22に記載の半導体素子の製造方法。

【請求項28】

前記リセス領域が丸い形態の底面を有するように、前記チャネル層をエッチングすることを特徴とする請求項22に記載の半導体素子の製造方法。

【請求項29】

前記リセス領域内の前記絶縁基板の表面上に抵抗変化物質層を形成する段階は、

前記リセス領域の内壁に第1抵抗変化物質層を形成し、前記リセス領域の中心にある前記第1抵抗変化物質層を除去する段階と、

イオン注入法で、前記第1抵抗変化物質層内に酸素欠乏欠陥を形成する段階と、

前記リセス領域の中心部に第2抵抗変化物質層を形成する段階と、を含むことを特徴とする請求項22に記載の半導体素子の製造方法。

【請求項30】

チャネル層、前記チャネル層の両側上部面をドーピングして形成されたソース及びドレイン、前記チャネル層の上部面上で、前記ソースと前記ドレインとの間に配置された臨時ゲート、前記臨時ゲートの下部面と側面とを取り囲むゲート絶縁膜、前記ゲート絶縁膜を取り囲むように、前記チャネル層上に形成されたパッシベーション層を含む構造を設ける段階と、

前記ゲート絶縁膜の底面が露出されるように、前記臨時ゲートを除去して開口を形成する段階と、

前記開口内の前記ゲート絶縁膜の底面と、前記ゲート絶縁膜下部の前記チャネル層との一部をエッチングし、前記チャネル層内にリセス領域を形成する段階と、

前記リセス領域内に抵抗変化物質層を形成する段階と、

前記抵抗変化物質層上であって、前記開口内にゲート電極材料を充填してゲートを形成する段階と、を含む半導体素子の製造方法。

【請求項31】

前記チャネル層は、単結晶半導体基板を第1導電型にドーピングして形成され、前記ソース及び前記ドレインは、前記第1導電型と電気的に反対になる第2導電型にドーピングされて形成されることを特徴とする請求項30に記載の半導体素子の製造方法。

【請求項32】

前記臨時ゲートを除去して開口を形成する段階で、前記開口の内壁には、前記ゲート絶縁膜が残っていることを特徴とする請求項30に記載の半導体素子の製造方法。

【請求項33】

前記リセス領域を形成する段階は、

前記開口の底面の中心部が露出されて底面の周辺部が覆われるように、前記開口の内壁をマスクで取り囲む段階と、

前記マスクによって覆われていない前記ゲート絶縁膜の底面と、前記チャネル層の一部とを除去する段階と、を含むことを特徴とする請求項32に記載の半導体素子の製造方法。

【請求項34】

前記リセス領域内に抵抗変化物質層を形成する段階後、

前記抵抗変化物質層の上部表面を覆うように、前記マスク間に前記ゲート絶縁膜の底面を形成する段階と、

前記ゲート絶縁膜の側壁にある前記マスクを除去する段階と、をさらに含むことを特徴とする請求項33に記載の半導体素子の製造方法。

【請求項35】

前記リセス領域を形成した後、前記リセス領域周囲の前記チャネル層にイオンを注入することによって、前記リセス領域周囲の前記チャネル層にドーピング領域を形成する段階をさらに含むことを特徴とする請求項30に記載の半導体素子の製造方法。

【請求項36】

前記リセス領域内に抵抗変化物質層を形成する段階は、

前記リセス領域の内壁に第1抵抗変化物質層を形成し、前記リセス領域の中心にある前記第1抵抗変化物質層を除去する段階と、

イオン注入法で、前記第1抵抗変化物質層内に酸素欠乏欠陥を形成する段階と、

前記リセス領域の中心部に第2抵抗変化物質層を形成する段階と、を含むことを特徴とする請求項30に記載の半導体素子の製造方法。

【図1】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2H】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図7D】

【図7E】

【図7F】

【図7G】

【図7H】

【図7I】

【図8】

【図9】

【図10A】

【図10B】

【図10C】

【図11】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2H】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図7D】

【図7E】

【図7F】

【図7G】

【図7H】

【図7I】

【図8】

【図9】

【図10A】

【図10B】

【図10C】

【図11】

【公開番号】特開2013−33923(P2013−33923A)

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願番号】特願2012−99588(P2012−99588)

【出願日】平成24年4月25日(2012.4.25)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願日】平成24年4月25日(2012.4.25)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]