抵抗変化素子及びそのプログラミング方法

【課題】誤書き込み、及び誤動作を防止し、高信頼化、及び高密度化が可能な抵抗変化素子の提供。

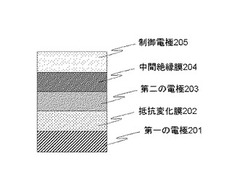

【解決手段】第一の電極(201)と、抵抗変化膜(202)と、第二の電極(203)と、中間絶縁膜(204)と、制御電極(205)と、をこの順に積層した積層構造を備え、前記抵抗変化層(202)と前記中間絶縁膜(204)が直接接していない。

【解決手段】第一の電極(201)と、抵抗変化膜(202)と、第二の電極(203)と、中間絶縁膜(204)と、制御電極(205)と、をこの順に積層した積層構造を備え、前記抵抗変化層(202)と前記中間絶縁膜(204)が直接接していない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に抵抗変化素子及びそのプログラミング方法に関する。

【背景技術】

【0002】

半導体装置のうち、特にシリコンデバイスは、微細化(スケーリング則:Mooreの法則)によってデバイスの集積化・低電力化が進められ、3年4倍のペースで開発が進められてきた。近年、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)のゲート長は20nm以下となり、リソグラフィプロセスの高騰(装置価格及びマスクセット価格)、及びデバイス寸法の物理的限界(動作限界・ばらつき限界)により、これまでのスケーリング則とは異なるアプローチでのデバイス性能の改善が求められている。

【0003】

近年、ゲートアレイとスタンダードセルの中間的な位置づけとしてFPGAと呼ばれる再書き換え可能なプログラマブルロジックデバイスが開発されている。FPGAは、顧客自身がチップの製造後に任意の回路構成を行うことを可能とするものである。FPGAは、多層配線層の内部に抵抗変化素子を有し、顧客自身が任意に配線の電気的接続をできるようにしたものである。このようなFPGAを搭載した半導体装置を用いることで、回路の自由度を向上させることができるようになる。

【0004】

抵抗変化素子としては、

(A)遷移金属酸化物を用いたReRAM(Resistance Random Access Memory)や、

(B)固体電解質層を用いたNanoBridge(NEC社の登録商標)

などがある。

【0005】

一方、混載メモリについては、揮発性のeDRAM(embedded Dynamic Random Access Memory)、不揮発性のフラッシュメモリ等が用いられている。eDRAMでは、記憶した情報が電源を切ると消失してしまう。フラッシュメモリでは高、電圧(5V以上)が必要とされる。このため、低電圧(1V以下)で動作するロジックLSIへの混載には不向きである点等が課題となっていた。

【0006】

<バイポーラ型抵抗変化素子>

バイポーラ型固体電解質スイッチ素子は、OFF状態(高抵抗状態)とON状態(低抵抗状態)との切り替えに逆極性の電圧が必要なスイッチ素子である。ここで、典型的なバイポーラ型抵抗変化素子の動作特性について図16(A)乃至(D)を用いて説明する。

【0007】

例えば、第一電極、抵抗変化素子、第二電極から構成されるバイポーラ型抵抗変化素子の場合には、第一電極に正電圧を印加すると(図16(A))、所望のセット電圧を閾値電圧として、OFF状態(高抵抗状態)からON状態(低抵抗状態へ遷移する)。

【0008】

続いて、ON状態の抵抗変化素子において、再び第一電極に正電圧を印加した場合には(図16(B))、オーミックな電流−電圧特性を示す。

【0009】

続いて、第一電極に負電圧を印加すると(図16(C))、所望のセット電圧を閾値電圧として、ON状態(低抵抗状態)からOFF状態(高抵抗状態へ遷移する)。

【0010】

さらに、続いて、ON状態の抵抗変化素子において、再び第一電極に正電圧を印加すると(図16(D))、所望の閾値電圧(リセット電圧)において、ON状態からOFF状態へ遷移する。

【0011】

このように、

第一電極に正電圧を印加した場合にのみ、OFF状態からON状態へ遷移し、

第一電極に負電圧を印加した場合にのみ、ON状態からOFF状態への遷移

が生じる素子をバイポーラ型抵抗変化素子として定義する。

【0012】

<バイポーラ型抵抗変化素子における電極の定義>

ここで、バイポーラ型抵抗変化素子に用いられる電極を定義する。図16で説明したように、正電圧を印加した場合にOFF状態からON状態に遷移する電極を「第一の電極」、あるいは「活性電極」と定義する。

【0013】

逆に正電圧を印加した場合にON状態からOFF状態に遷移する電極を「第二の電極」、あるいは「不活性電極」と定義する。

【0014】

二つの異なる抵抗変化素子を接続する場合に、各抵抗変化素子の電極同士を電気的に接続することになる。この場合、二つの異なる抵抗変化素子の活性電極同士、あるいは、不活性電極同士が電気的に接続されている、あるいは一体化されていることを、「同一極性同士の電極の接続」というものとする。

【0015】

<固体電解質層型抵抗変化素子の説明>

上記したバイポーラ型抵抗変化素子の例として、非特許文献1には、固体電解質層(イオンが電界等の印加によって自由に動くことのできる固体)中における金属イオン移動と電気化学反応とを利用したスイッチング素子が開示されている。非特許文献1に開示されたスイッチング素子は、固体電解質層、該固体電解質層に一側と該一側と反対側の各面に当接して対向配置された第1電極及び第2電極の3層から構成されている。このうち、第1電極は、固体電解質層に金属イオンを供給するための役割を果たしている。第2電極からは、金属イオンは供給されない。

【0016】

以下では、このスイッチング素子の動作について簡単に説明する。

【0017】

第1の電極を接地して第2電極に負電圧を印加すると、第1電極の金属が金属イオンになって固体電解質層に溶解する。そして、固体電解質層中の金属イオンが固体電解質層中に金属になって析出する。固体電解質層中に析出した金属により、第1電極と第2電極を接続する金属架橋が形成される。金属架橋により第1電極と第2電極が電気的に接続することで、スイッチング素子はオン状態になる。

【0018】

一方、上記オン状態で、第1電極を接地して第2電極に正電圧を印加すると、金属架橋の一部が切れる。これにより、第1電極と第2電極との電気的接続が切れ、スイッチング素子はオフ状態になる。なお、電気的接続が完全に切れる前の段階から、第1電極及び第2電極間の抵抗が大きくなったり、電極間容量が変化したりする等、その電気特性が変化し、最終的に電気的接続が切れる。

【0019】

また、上記オフ状態からオン状態にするには、再び第1の電極を接地して第2電極に負電圧を印加すればよい。

【0020】

固体電解質層型抵抗変化素子によるスイッチング素子として、非特許文献1では、固体電解質層を介して第1、第2の電極が配置され、それらの間の導通状態を制御する2端子型のスイッチング素子の構成及び動作が開示されている。

【0021】

このような固体電解質層型抵抗変化素子によるスイッチング素子は、半導体スイッチ(MOSFET(Metal Oxide Semiconductor Field Effect Transistor)等)よりもサイズが小さく、オン抵抗が小さいという特徴を持っている。このため、プログラマブルロジックデバイスへの適用に有望であると考えられている。

【0022】

また、このスイッチング素子においては、その導通状態(オン又はオフ)は印加電圧をオフにしてもそのまま維持される。このため、不揮発性のメモリ素子としての応用も考えられる。例えば、トランジスタ等の選択素子1個とスイッチング素子1個とを含むメモリセルを基本単位として、このメモリセルを縦方向と横方向にそれぞれ複数配列する。このように配列することで、ワード線及びビット線で複数のメモリセルの中から任意のメモリセルを選択することが可能となる。そして、選択したメモリセルのスイッチング素子の導通状態をセンスし、スイッチング素子のオン又はオフの状態から情報「1」又は「0」のいずれの情報が格納されているかを読み取ることが可能な不揮発性メモリを実現できる

【0023】

なお、不揮発性の可変抵抗素子に関して、特許文献1には、第1の電極と、第2の電極と、第1の電極及び第2の電極の双方に接続する可変抵抗体と、誘電層を介して可変抵抗体に接続する制御電極を備え、誘電層は第2の可変抵抗体の側面に接した構成が開示されている。

【先行技術文献】

【特許文献】

【0024】

【特許文献1】特開2010−153591号公報

【非特許文献】

【0025】

【非特許文献1】Shunichi Kaeriyama et al., "A Nonvolatile Programmable Solid-Electrolyte Nanometer Switch", IEEE Journal of Solid-State Circuits, Vol.40, No.1, pp.168-176, January 2005.

【発明の概要】

【発明が解決しようとする課題】

【0026】

以下に関連技術の分析を与える。

【0027】

前述したような2端子型抵抗変化素子を半導体装置上に形成してプログラミングする場合、例えば信号線の伝達先を不揮発的に切り替えるスイッチに適用する場合、プログラミングのための制御信号線と、プログラミング後にON状態となった抵抗変化素子を介して伝搬する信号線とが独立していないため、プログラミングの制御が難しく、誤動作を生じ易い、という問題点を有している。

【0028】

本発明は、上記問題点を解消すべく全く新たに創案されたものであって、その主たる目的は、誤書き込み、及び誤動作を防止し、高信頼化、及び高密度化が可能な抵抗変化素子、及びそのプログラミング方法を提供することにある。

【課題を解決するための手段】

【0029】

本発明によれば、第一の電極と、抵抗変化層(抵抗変化膜)と、第二の電極と、中間絶縁膜と、制御電極と、をこの順に積層した積層構造を備え、前記抵抗変化層と前記中間絶縁膜が直接接していない抵抗変化素子が提供される。

【0030】

本発明によれば、上記抵抗変化素子に対して、前記第一の電極と制御電極との間に規則的に交番する電圧を印加し、過渡的に流れる交流電流を両電極間に流すことによって前記抵抗変化素子の抵抗値を遷移させる、プログラミング方法が提供される。

【発明の効果】

【0031】

本発明によれば、抵抗変化素子の誤書き込み、及び誤動作を防止し、高信頼化、及び高密度化を可能としている。

【図面の簡単な説明】

【0032】

【図1】(A)は関連技術(比較例)の2端子抵抗変化素子回路の等価回路、(B)は第一の実施形態の制御端子付き抵抗変化素子の等価回路を示す図である。

【図2】第一の実施形態の構成を示す図である。

【図3】第一の実施形態の構成の一例を示す図である。

【図4】(A)は関連技術の2端子抵抗変化素子を二つ使用した相補型抵抗変化素子回路、(B)は、第二の実施形態の制御端子付き抵抗変化素子の等価回路を示す図である。

【図5】第二の実施形態の構成を示す図である。

【図6】第二の実施形態の構成の一例を示す図である。

【図7】第三の実施形態の構成を等価回路で示す図である。

【図8】第四の実施形態の構成を等価回路で示す図である。

【図9】第五の実施形態の構成を説明する図である。

【図10】実施例1の半導体装置の断面を模式的に示す図である。

【図11】(A)乃至(C)は実施例2の製造工程における断面を模式的に示す工程断面図である。

【図12】(A)乃至(C)は実施例2の製造工程における断面を工程順に模式的に示す工程断面図である。

【図13】(A)及び(B)は実施例2の製造工程における断面を工程順に模式的に示す工程断面図である。

【図14】(A)及び(B)は実施例2の製造工程における断面を工程順に模式的に示す工程断面図である。

【図15】実施例2の製造工程における断面を示す工程断面図である。

【図16】(A)乃至(D)は典型的なバイポーラ型抵抗変化素子の動作特性を説明する図である。

【図17】第六の実施形態を説明する図である。

【図18】第六の実施形態の動作を説明する波形図である。

【発明を実施するための形態】

【0033】

本発明の第1の形態においては、例えば図2を参照すると、第一の電極(201)と、抵抗変化層(抵抗変化膜)(202)と、第二の電極(203)を有する抵抗変化素子において、第二の電極(203)に接する中間絶縁膜(204)と、中間絶縁膜(204)に接する制御電極(205)を備える。

【0034】

第一の電極(201)と制御電極(205)間に電圧を印加することで、抵抗変化膜(202)の抵抗状態を変化させ、かつ、第二の電極(203)を利用して抵抗状態の読み出しや、信号の入出力がなされる電気回路を有する半導体装置を構成することができる。

【0035】

制御電極(205)は、中間絶縁膜(204)によって第二の電極(203)と絶縁分離されているため、制御電極(205)に印加されるプログラミング信号と、第一の電極(201)と第二の電極(202)間を伝搬するロジック信号/読み出し信号とを分離することができる。

【0036】

かかる本発明によれば、抵抗変化層の抵抗状態を、抵抗変化層とは直接接しない中間絶縁膜(204)を介して絶縁分離された制御電極(205)への電圧印加で行うことによって、プログラミングのための制御信号線と、プログラミング後に接続される信号線(もしくは読み出し線)を独立させることができる。このため、抵抗変化素子の誤書き込み、及び誤動作を防止することができる。

【0037】

第一の電極(201)と制御電極(205)間に印加された電圧は、抵抗変化膜(202)と中間絶縁膜(204)とで電圧分割される。例えば、より小さい制御電圧で抵抗変化素子の抵抗状態をOFF状態からON状態へ変化させる(プログラミングする)ためには、印加した制御電圧の大半が抵抗変化素子に印加させることが好ましい。

【0038】

そのため、第二の電極(203)に蓄積する電荷を一定とした場合、中間絶縁膜(204)の比誘電率が、抵抗変化膜(202)の比誘電率よりも大きいことが好ましい。さらに、中間絶縁膜(204)の厚さは、抵抗変化膜(202)の厚さよりも薄いことが好ましい。

【0039】

例えば、第一の電極(201)は、金属イオンを供給する活性電極(図3の301)を含む構成としてもよい。また、抵抗変化層(202)は、イオン化した金属が伝導する固体電解質層(図3の302)を含む構成としてもよい。さらに、第二の電極(203)は、前記金属イオンと反応しない不活性電極(図3の303)を含む構成としてもよい。

【0040】

前記中間絶縁膜(204、304)は、ハフニア膜、アルミナ膜、ジルコニア膜、イットリア膜、シリコン窒素膜、シリコン炭化窒素膜、シリコン酸化膜のいずれかを含むことが好ましい。

【0041】

前記制御電極(205、305)は、Ta、Ti、TaN、TiN、W、Alのいずれを含むことが好ましい。

【0042】

本発明の第2の形態によれば、相補型構造抵抗変化素子を有するクロスバースイッチ回路を有する半導体装置が提供される。

【0043】

本発明の第2の形態においては、例えば図5を参照すると、半導体素子基板上に形成された、バイポーラ型抵抗変化素子において、第一の電極と、抵抗変化層と、第二の電極と、中間絶縁膜と、制御電極とがこの順に積層した、積層構造を備える、少なくとも2つの抵抗変化素子であって、前記2つの抵抗変化素子の、抵抗変化層(502)同士、第二の電極(503)同士、中間絶縁膜(504)同士、及び制御電極(505)同士が一体化している構成としてもよい。

【0044】

半導体装置において、前記抵抗変化素子は、

半導体装置内の多層配線層に形成され、前記第一電極は下部電極を兼ねた配線(図10の3)であって、

前記抵抗変化膜(図10の9)との間に絶縁性バリア膜(図10の7)が介在し、

前記絶縁性バリア膜(図10の7)は開口部を有し、

前記抵抗変化膜(図10の9)は、前記開口部において前記下部電極兼配線(3)と接する構成としてもよい。

【0045】

前記抵抗変化素子構造において、前記絶縁性バリア膜(7)は一つの開口部を有し、それぞれ独立した下部電極兼配線(3)上に開口されており、上部電極は二つの抵抗変化素子間で電気的に一体化した構成としてもよい。

【0046】

前記抵抗変化素子構造において、それぞれ独立した少なくとも2本の下部電極兼配線の双方に接続するように前記絶縁性バリア膜は一つの開口部を有する構成としてもよい。

【0047】

本発明の第3の形態においては、前記固体電解質層は、少なくともSiOxCy、TaSiOx、TaOx、ZrOx、HrOx、SiOx、TiOx、有機物を主成分とする材料のいずれかを含む。

【0048】

前記第一の電極は、銅を含む構成としてもよい。前記第二の電極は、Ru、あるいはPtかを含む構成としてもよい。絶縁性バリア膜は、SiC、SiCN、SiNのいずれかを含む構成としてもよい。

【0049】

前記第二の電極は、固体電解質と接する面にRu、中間絶縁膜に接する面にTaを含む積層電極(Ru/Ta)としてもよい。

【0050】

本発明の第4の形態において、半導体装置の製造方法は、半導体基板上の多層配線層の内部に抵抗変化素子を有する半導体装置の製造にあたり、

下層配線上に絶縁性バリア膜(図10の7)を形成する工程と、

前記絶縁性バリア膜上に開口部パターンを有するハードマスク膜(図11(C)の8)を形成する工程と、

前記ハードマスク膜をマスクとして、前記開口部パターンから露出する前記絶縁性バリア膜を反応性ドライエッチングにより、前記絶縁性バリア膜に、前記下層配線に通ずるととともに、壁面が前記配線から離れるにしたがい広くなったテーパ面となった開口部を形成する工程(図12(A))と、

前記抵抗変化膜(図10、図12(C)の9)を形成する工程と、

前記上部電極(図10の10、11、13)を形成する工程と、

を含む。

【0051】

前記絶縁性バリア膜上に開口部を形成する工程において、2本の異なる下層配線の双方に連続した一つの開口部を形成するようにしてもよい。

【0052】

前記配線を形成する工程は、前記抵抗変化膜の前記下部電極とならない他の配線を同時に形成し、

前記プラグを形成する工程では、前記他の配線上に他のプラグを形成する半導体装置の製造方法であることが好ましい。

【0053】

本発明の第5の形態において、前記抵抗変化層をOFF状態からON状態へ、もしくはON状態からOFF状態へ抵抗値を遷移させるためには、書き込み電圧を前記抵抗変化層の両端に印加する際に、書き込み電流が流れることが好ましい。前記抵抗変化層と前記中間絶縁膜を流れるリーク電流が少なすぎると、書き込み電流が不十分となる可能性がある。この場合、第一の電極と制御電極の間に交番する電圧を印加し、交流電流を両電極間に流すようにしてもよい。

【0054】

さらに、本発明の第5の形態において、前記抵抗変化層の両端に印加される電圧波形が上昇時と下降時で異なる時間変化をもたせるようにしてもよい。このようにすることで、容量性の電流の時間変化は電圧の時間変化の微分値に比例するため、交流電流の各々の極性に対して、異なるピーク電流値を設定することができる。

【0055】

このピーク電流値の差によって、抵抗変化素子をON状態もしくはOFF状態に状態遷移させることができる。

【0056】

例えば、バイポーラ型抵抗変化素子において、第一の電極から不活性電極側に電流を流すことで、OFF状態からON状態に抵抗値が遷移する場合を考えると、第一の電極から不活性電極に流れる電流のピーク値を高くし、逆方向のピーク値を低くすることによって、交流電流によるプログラミングを可能としている。

【0057】

半導体装置内の多層配線層の内部に抵抗変化素子を有するフィールドプログラマブルゲートアレイ、混載メモリを搭載した半導体装置に適用して好適とされる。以下、いくつかの実施形態について説明する。

【0058】

<実施形態1>

図1(A)は、関連技術(比較例)の2端子抵抗変化素子回路の等価回路、図1(B)は、本実施形態に係る制御端子付き抵抗変化素子の等価回路を示す。図1(A)、(B)において、101は抵抗変化素子、102、103は端子である。図1(B)に示すように、本発明の実施形態では、制御信号の入出力を行う制御端子104を有する。

【0059】

本発明の第一の実施形態に係る半導体装置について、図1(B)、図2、図3を参照して説明する。図2は、図1(B)の第一の実施形態の抵抗変化素子の断面構成を模式的に示す図である。図2を参照すると、抵抗変化素子は、第一の電極201、抵抗変化膜202、第二の電極203、中間絶縁膜204、制御電極205がこの順に積層されている。

【0060】

例えば、抵抗変化素子が、金属イオンの析出を利用した固体電解質スイッチである場合には、第一の電極201は、図3の活性電極301、抵抗変化膜202は図3の固体電解質層302、第二の電極203は図3の不活性電極303である。

【0061】

固体電解質スイッチをOFF状態からON状態へ遷移させる場合には、第一の電極201(活性電極301)を接地し、制御電極205(305)に負電圧を印加すると、抵抗変化膜202(固体電解質層302)と中間絶縁膜204間で電圧分割された電圧が、抵抗変化膜202(固体電解質層302)に印加され、図3の金属架橋306が形成される。

【0062】

ここで、できるだけ電圧値が小さな制御電圧で、固体電解質スイッチの抵抗状態を変化させるためには、抵抗変化膜202(固体電解質層302)と中間絶縁膜204(絶縁膜304)の抵抗値が同じ場合には、中間絶縁膜204(絶縁膜304)の比誘電率が抵抗変化膜202(固体電解質層302)よりも大きくし、膜厚は薄いことが好ましい。

【0063】

例えば、抵抗変化膜202(固体電解質層302)は、有機膜を主成分とする膜(例えば、比誘電率:3.0、膜厚:5nm)を含む。

【0064】

中間絶縁膜204(絶縁膜304)は、ハフニア(HfOx;比誘電率:20、膜厚:6nm)を含む。

【0065】

このとき、直列接続における電荷の分布から、抵抗変化膜202(固体電解質層302)、及び中間絶縁膜204(絶縁膜304)に印加される電圧の比率は1:20となる。すわなち、制御電極205(305)に、例えば2Vを印加すると、抵抗変化膜202(固体電解質層302)に約1.9V印加することができる。

【0066】

また、抵抗値の観点からも、中間絶縁膜204(絶縁膜304)の膜厚が抵抗変化膜202(固体電解質層302)よりも薄いことが好ましい。

【0067】

抵抗変化膜202(固体電解質層302)としては低密度な膜を用いることが好ましい。このため、緻密な材料から構成される中間絶縁膜204(絶縁膜304)と比べるとリーク電流が大きくなる傾向がある。

【0068】

それぞれの抵抗値を等しくするためには、抵抗変化膜202(固体電解質層302)の膜厚よりも中間絶縁膜204(絶縁膜304)の膜厚を薄くすることでリーク電流レベルを一致させることもできるようになる。

【0069】

ここで、本実施形態における、誤書き込み、誤動作不良の改善要因について説明する。

【0070】

制御電極を有しない抵抗変化素子の場合(図1(A)参照)、第一の電極201と第二の電極203に直接電位差を生じさせることで、抵抗変化膜202の抵抗状態を変化(プログラミング)させる。

【0071】

一方、本実施形態によれば、抵抗変化層202の抵抗状態を、抵抗変化層202とは直接接しない中間絶縁膜204を介して絶縁分離されている制御電極(205)へ電圧を印加することによって、プログラミングのための制御信号線と、プログラミング後に接続される信号線(もしくは読み出し線)を独立させることができる。このため、抵抗変化素子の誤書き込み、及び誤動作を防止することができる。

【0072】

<実施形態2>

次に本発明の第二の実施形態について説明する。第二の実施形態では、不活性電極(第二の電極)同士が接続された相補型抵抗変化素子を例に説明する。図4(A)は、関連技術の2端子抵抗変化素子を二つ使用した相補型抵抗変化素子回路、図4(B)は、第二の実施形態による制御端子付き抵抗変化素子の回路を示す図である。

【0073】

図4(A)の構成では、抵抗変化素子401aと抵抗変化素子401bは、活性電極同士が接続され、活性電極に接続された端子402a、402bを介して、入出力を行う。抵抗変化素子401aと抵抗変化素子401bの不活性電極にトランジスタ(MOSトランジスタ)405のソース又はドレイン端子を接続して制御する。

【0074】

一方、第二の実施形態の抵抗変化素子では、図4(B)に示すように、トランジスタを接続することなく、制御信号の入出力を行う制御端子404を有する構造としている。このため、図4(A)のトランジスタ相当分の回路面積が削減される。抵抗変化素子抵抗変化素子(スイッチ)の面積を低減することができる。

【0075】

次に、第二の実施形態の抵抗変化素子について、活性電極同士が電気的に接続される構造について、図5、図6を用いて説明する。

【0076】

図5に示す例では、2つの抵抗変化素子を有し、前記抵抗変化素子の抵抗変化膜502同士、第二の電極503同士、中間絶縁膜504同士、制御電極505同士が接続され、未接続の二つの第一の電極501a、501bから入出力がなされる。

【0077】

第一の実施の形態のように、制御電極505に電圧を印加することで、抵抗変化膜502の抵抗状態を変化させ、抵抗状態を不揮発に記憶することができる、

【0078】

二つの抵抗変化素子を有することで、未接続の二つの第一の電極(第一の電極501aと第一の電極501b)の間で、抵抗値の読み出し、あるいは信号の入出力を行うことができる。

【0079】

このとき、制御電極505は、第一の電極501a、第一の電極501b、及び、第二の電極503とは絶縁分離されているため、プログラム用の制御信号と、ロジック信号(読み出し信号)とが混線することはない。

【0080】

図6に示す例では、2つのバイポーラ型の固体電解質スイッチを有し、前記抵抗変化素子の固体電解質602同士、不活性電極603同士、中間絶縁膜604同士、制御電極605同士が接続され、かつ未接続の二つの第一の電極(第一の活性電極601a、第二の活性電極601b)から入出力がなされる。

【0081】

スイッチング素子をオン状態(低抵抗状態)にするためには、制御電極605に電圧が印加されることで、第一の活性電極601a、及び第二の活性電極601bのそれぞれから金属架橋606a及び606bが固体電解質602内に形成され、第一の活性電極601aと不活性電極603と第二の活性電極601bが電気的に接続される。

【0082】

このとき、第一の実施形態と同じく、制御電極605は、中間絶縁膜604を介して不活性電極とは絶縁分離されているため、活性電極と不活性電極の接続状態によらず、分離されている。

【0083】

<実施形態3>

次に本発明の第三の実施形態について説明する。第三の実施形態では、制御電極を有する抵抗変化素子(第一の実施形態)を、アレイ状に配置したスイッチ(クロスバースイッチ)として用いることで、スイッチ素子の小面積化を図ることができるようになる。

【0084】

図7は、第三の実施形態の構成を示す図である。図7には、抵抗変化素子をアレイ上に配置し、クロスバースイッチとした構成が等価回路で示されている。図7を参照すると、抵抗変化素子701aは、図2の第一の電極201と接続する端子702aと、第二電極203と接続する端子703a、及び制御電極205と接続する制御端子704aを有する。水平線705a、705bの各水平線上で隣り合う抵抗変化素子の第二の電極203と接続する端子同士は接続され、垂直線706a、bの各垂直線上で隣り合う抵抗変化素子の第一の電極201と接続する端子同士も接続されている。対角線707上に配置された抵抗変化素子の制御電極205同士が接続されている。すなわち、抵抗変化素子701aは、水平線705a、垂直線706a、対角線707aの交点に位置する。

【0085】

ここで、図7において、全ての抵抗変化素子がオフ状態であるとし、抵抗変化素子701aをオン状態にプログラミングする場合について説明する。

【0086】

・垂直線706aにセット電圧を印加し、それ以外の垂直線には、セット電圧の半分の電圧を印加し、

・水平線はすべてフローティングとし、

・対角線707aは接地電位とし、それ以外の対角線はセット電圧の半分の電圧を印加する。

【0087】

このような電圧印加を行うことで、クロスーバーアレイ内の抵抗変化素子701aのみの第一の電極(図2の201)−制御電極(図2の205)間にセット電圧が印加され、プログラミングを行うことができる。

【0088】

非選択の抵抗変化素子には最大でもセット電圧の半分の電圧しか印加されないため、オン状態にプログラミングされることはない。

【0089】

オン状態の抵抗変化素子701aをオフ状態にプログラミングする場合には、

・対角線は全てフローティングにし、

・水平線705aにセット電圧を印加し、それ以外の水平線にはセット電圧の半分の電圧を印加し、

・垂直線706aは接地電位とし、それ以外の垂直線はセット電圧の半分の電圧を印加する。

【0090】

このような電圧印加を行うことで、制御端子を用いて選択した交点に位置する抵抗変化素子のプログラミングを行い、任意の抵抗状態にすることができる。

【0091】

このような操作を各交点について繰り返すことで、クロスバースイッチとして所望の接続状態が得ることができる。

【0092】

このとき、制御端子同士を接続している対角線は、抵抗変化素子の抵抗状態によらず、常に抵抗変化素子とは絶縁分離されているため、プログラミングの精度が向上する。

【0093】

<実施形態4>

次に本発明の第四の実施形態について説明する。第四の実施形態では、制御電極を有する相補型抵抗変化素子(図5参照)をアレイ上に配置したスイッチ(クロスバースイッチ)として用いることで、スイッチ素子の小面積化を図る。

【0094】

相補型抵抗変化素子は、図5に示すように、

・二つの抵抗変化素子間で電圧分割される点と、

・バイポーラ型抵抗変化素子が互いに異なるセット電圧方向で直列接続される点

から、

相補型抵抗変化素子のOFF時におけるディスターブに対する信頼性が改善する。さらに、制御端子を加えることで、よりプログラミングの制御性を向上することができる。

【0095】

図8は、第四の実施形態の構成を示す図である。図8には、相補抵抗変化素子をアレイ上に配置し、クロスバースイッチとした時の構成が等価回路で示されている。図8を参照すると、抵抗変化素子801a、及び抵抗変化素子801bのそれぞれの第一の電極と接続する端子803aと802aが、水平線805a、及び垂直線806aに接続している。

【0096】

抵抗変化素子801a及び801bの第二電極同士と接続する制御端子804aは対角線807bに接続している。すなわち、抵抗変化素子801a及び801bは、水平線805a、垂直線806a、対角線807bの交点に位置する。

【0097】

ここで、全ての抵抗変化素子がオフ状態であるとし、抵抗変化素子801a及び801bの双方をオン状態として、クロスバーの交点をオン状態にプログラミングする場合について説明する。

【0098】

まず、抵抗変化素子801aをオン状態にするために、

・水平線805aにセット電圧を印加し、それ以外の水平線にはセット電圧の半分の電圧を印加し、

・垂直線はすべてフローティングとし、

・対角線807bは接地電位とし、それ以外の対角線はセット電圧の半分の電圧を印加する。

【0099】

このような電圧印加を行うことで、抵抗変化素子801aのみの第一の電極−制御電極間にセット電圧が印加され、プログラミングを行うことができる。

【0100】

非選択の抵抗変化素子には最大でもセット電圧の半分の電圧しか印加されないため、オン状態にプログラミングされることはない。

【0101】

つづいて、抵抗変化素子801bをオン状態にするため、

・垂直線806aにセット電圧を印加し、それ以外の垂直線にはセット電圧の半分の電圧を印加し、

・水平線は全てフローティングとし、

・対角線807bは接地電位とし、それ以外の対角線はセット電圧の半分の電圧を印加する。

【0102】

このような電圧印加を行うことで、抵抗変化素子801bのみの第一の電極−制御電極間にセット電圧が印加され、プログラミングを行うことができるようになる。

【0103】

このように抵抗変化素子801a及び801bの双方がオン状態になることで、垂直線806aと水平線805aを接続することができるようになる。

【0104】

<実施形態5>

次に本発明の第五の実施形態について説明する。第五の実施形態では、第三の実施形態及び第四の実施形態4のクロスバースイッチの構成において、対角線の共有化を行うことで、対角線につながるプログラミングドライバーの数を削減し、低面積化をすることができるようになる。

【0105】

図9は、対角線の共有化を行った場合のクロスバースイッチへの適用形態を説明する図である。図中は5×5の抵抗変化素子がマトリックス上に配置されている。

【0106】

このとき、5本の対角線906a〜906eまでが配置され、それぞれが5つの抵抗変化素子と接続されており、接続されている抵抗変化素子は、行・列内に一つだけ接続されている。すなわち、nxnのクロスバースイッチの場合、それぞれn個の抵抗変化素子と接続された、計n本の対角線を有する構成とすることで、クロスバースイッチに用いる対角線の小面積化を図ることができる。

【0107】

次に、上記した抵抗変化素子を含む半導体装置の一具体例とその製造方法の一例について詳細に説明する。

【0108】

半導体基板上の多層配線層の内部に抵抗変化素子を有する半導体装置の製造方法は、下部電極(例えば図2の第一の電極201)を兼務した配線上に、抵抗変化膜(例えば図2の202)、上部電極(例えば図2の第二の電極203)をこの順に形成する工程と、前記上部電極(図2の203)上に、絶縁膜(例えば図2の中間絶縁膜204)を介して上層配線(例えば図2の制御電極205)を形成する工程を形成する工程と、を含む。以下、より具体的な実施例について説明する。

【0109】

<実施例1>

本発明に係る抵抗変化素子の一具体例について説明する。図10は、実施例1の半導体装置の構成を模式的に示した部分断面図である。

【0110】

実施例1の半導体装置は、半導体基板上の銅多層配線層の内部に抵抗変化素子22を有する装置である。

【0111】

多層配線層は、半導体基板(図示せず)上にて、層間絶縁膜4、絶縁性バリア膜7、層間絶縁膜16、及び絶縁性バリア膜21の順に積層した絶縁積層体を有する。

【0112】

第1配線3は、層間絶縁膜4に形成された配線溝にバリアメタル6を介して銅5が埋め込まれている。

【0113】

第2配線17は、層間絶縁膜16に形成された配線溝に、バリアメタル20を介して、銅18が埋め込まれており、層間絶縁膜16に形成された下穴にプラグ19が埋め込まれており、第2配線17とプラグ19が一体となっており、第2配線17及びプラグ19の側面乃至底面がバリアメタル20によって覆われている。

【0114】

多層配線層は、絶縁性バリア膜7に形成された開口部にて、下部電極となる第1配線3、絶縁性バリア膜7の開口部の壁面、乃至絶縁性バリア膜7上に、抵抗変化膜9、第1上部電極10、及び第2上部電極11の順に積層した抵抗変化素子22が形成されている。抵抗変化膜9、第1上部電極10、第2上部電極11、中間絶縁膜12、第3上部電極13の積層体からなる。

【0115】

実施例1によれば、第1配線3を抵抗変化素子22の下部電極とすることで、すなわち、第1配線3が抵抗変化素子22の下部電極を兼ねることで、工程数を簡略化しながら、電極抵抗を下げるこができる。

【0116】

例えば、通常のCu(銅)ダマシン配線プロセスへの追加工程として、少なくとも3枚のマスクセットを作成するだけで、抵抗変化素子を搭載することができる。このため、抵抗変化素子の低抵抗化と低コスト化を同時に達成することができる。

【0117】

抵抗変化素子22は、抵抗変化型不揮発素子であり、例えば、固体電解質層中における金属イオン移動と電気化学反応とを利用したスイッチング素子とすることができる。

【0118】

抵抗変化素子22は、下部電極となる第1配線3と、プラグ19と電気的に接続された上部電極11、13とを有する構成となっている。

【0119】

抵抗変化素子22は、絶縁性バリア膜7に形成された開口部の領域にて、抵抗変化膜9と第1配線3とが直接接している。また第3上部電極13上にて、プラグ19と第3上部電極13とがバリアメタル20を介して電気的に接続されている。

【0120】

抵抗変化素子22は、電圧の印加、あるいは電流を流すことで、ON/OFFの制御が行われる。例えば、抵抗変化膜9中への第1配線3に係る金属の電界拡散を利用してON/OFFの制御を行う。

【0121】

第3上部電極13及びバリアメタル20は、同一の材料で構成されている。このようにすることで、プラグ19のバリアメタル20と抵抗変化素子22の第3上部電極13とが一体化し、接触抵抗を低減し、かつ、密着性の向上による信頼性の向上を実現することができる。

【0122】

半導体基板は、半導体素子が形成された基板である。半導体基板には、例えば、

・シリコン基板、

・単結晶基板、

・SOI(Silicon on Insulator)基板、

・TFT(Thin Film Transistor)基板、

・液晶製造用基板等の基板を用いることができる。

【0123】

図10の層間絶縁膜4は、半導体基板上に形成された絶縁膜である。層間絶縁膜4には、例えば、シリコン酸化膜、シリコン酸化膜よりも比誘電率の低い低誘電率膜(例えば、SiOCH膜)等を用いることができる。層間絶縁膜4は、複数の絶縁膜を積層したものであってもよい。層間絶縁膜4には、第1配線3を埋め込むための配線溝が形成されており、当該配線溝にバリアメタル6を介して銅5が埋め込まれている。

【0124】

絶縁性バリア膜7は、層間絶縁膜4、16間に介在したバリア性を有する絶縁膜である。絶縁性バリア膜7は、第1配線3用の配線溝の加工時にエッチングストップ層としての役割を有する。絶縁性バリア膜7は、第1配線3を含む層間絶縁膜4上に形成され、第1配線3に係る金属(例えば、Cu)の酸化を防いだり、層間絶縁膜4中への第1配線3に係る金属の拡散を防いだり、上部電極11、10、及び抵抗変化膜9の加工時にエッチングストップ層としての役割を有する。

【0125】

絶縁性バリア膜7には、例えば、SiC膜、SiCN膜、SiN膜、及び、それらの積層構造等を用いることができる。

【0126】

絶縁性バリア膜7は、第1配線3上にて開口部を有する。絶縁性バリア膜7の開口部においては、第1配線3(の銅5)と抵抗変化膜9が接している。この絶縁性バリア膜7の開口部は、第1配線3の領域内に形成されている。このようにすることで、凹凸の小さい第1配線3の表面上に抵抗変化素子22を形成することができる。絶縁性バリア膜7の開口部の壁面は第1配線3から離れるにしたがい広くなったテーパ面となっている。

【0127】

層間絶縁膜16は、絶縁性バリア膜7上に形成された絶縁膜である。層間絶縁膜16には、例えば、シリコン酸化膜、シリコン酸化膜よりも比誘電率の低い低誘電率膜(例えば、SiOCH膜)等を用いることができる。層間絶縁膜16は、複数の絶縁膜を積層したものであってもよい。

【0128】

第1配線3は、層間絶縁膜4に形成された配線溝にバリアメタル6を介して埋め込まれた配線である。第1配線3は、抵抗変化素子22の下部電極を兼ね、抵抗変化膜9と直接接している。なお、第1配線3と抵抗変化膜9の間には、電極層等が挿入されていてもよい。電極層が形成される場合は、電極層と抵抗変化膜9は連続工程にて堆積され、連続工程にて加工される。

【0129】

バリアメタル6は、第1配線3に係る金属が層間絶縁膜4や下層へ拡散することを防止するために、配線の側面乃至底面を被覆する、バリア性を有する導電性膜である。

【0130】

バリアメタル6には、例えば、第1配線3がCuを主成分とする金属元素からなる場合には、タンタル(Ta)、窒化タンタル(TaN)、窒化チタン(TiN)、炭窒化タングステン(WCN)のような高融点金属やその窒化物等、またはそれらの積層膜を用いることができる。

【0131】

抵抗変化膜9は、抵抗が変化する膜である。抵抗変化膜9は、第1配線3(下部電極)に係る金属の作用(拡散、イオン伝動等)により抵抗が変化する材料を用いることができる。

【0132】

抵抗変化素子22の抵抗変化を金属イオンの析出によって行う場合には、イオン伝導可能な固体電解質膜が用いられる。例えば、Taを含む酸化物絶縁膜であって、Ta2O5、TaSiO等を用いることができる。

【0133】

また、抵抗変化膜9は、例えば、下からTa2O5、TaSiOの順に積層した積層構造とすることができる。あるいは、抵抗変化膜9は有機物を主成分とした膜とすることができる。

【0134】

このような積層構造とすることで、抵抗変化膜9を固体電解質層として用いた場合には、低抵抗時(ON時)に、イオン伝導層内部に形成される金属イオン(例えば、銅イオン)よる架橋を、有機物を主成分とする層で分断し、OFF時に金属イオンを容易に回収することができるようになる。この結果、スイッチング特性を向上させることができる。

【0135】

抵抗変化膜9は、第1配線3、絶縁性バリア膜7の開口部のテーパ面、乃至絶縁性バリア膜7上に形成されている。

【0136】

抵抗変化膜9は、第1配線3と抵抗変化膜9の接続部の外周部分が少なくとも絶縁性バリア膜7の開口部のテーパ面上に沿って配設されている。開口部下の第1の配線3は、第一の実施形態における第一の電極(図2の201)に相当する。

【0137】

第1上部電極10は、抵抗変化素子22の上部電極における下層側の電極であり、抵抗変化膜9と直接接している。第一の実施形態における第二の電極(図2の203)に相当する。

【0138】

第1上部電極10には、第1配線3に係る金属よりもイオン化しにくく、抵抗変化膜9において拡散、イオン電導しにくい金属が用いられ、酸化の自由エネルギーの絶対値が小さい金属材料とすることが好ましい。

【0139】

第1上部電極10には、例えば、Pt、Ru等を用いることができる。また、第1上部電極10には、Pt、Ru等の金属材料を主成分として酸素を添加してもよく、また酸素を添加した層との積層構造にしてもよい。

【0140】

第2上部電極11は、抵抗変化素子22の上部電極における上層側の電極であり、第1上部電極10上に形成されている。

【0141】

第2上部電極11は、第1上部電極10を保護する役割を有する。すなわち、第2上部電極11が第1上部電極10を保護することで、プロセス中の第1上部電極10へのダメージを抑制し、抵抗変化素子22のスイッチング特性を維持することができる。

【0142】

第2上部電極11には、例えば、Ta、Ti、W、Alあるいはそれらの窒化物等を用いることができる。

【0143】

中間絶縁膜12は、第2上部電極11と第3上部電極13とを絶縁分離する膜である。中間絶縁膜12は、例えば、ハフニア膜、アルミナ膜、ジルコニア膜、イットリア膜、シリコン窒素膜、シリコン炭化窒素膜、シリコン酸化膜から選択することができ、抵抗変化膜9よりも比誘電率が大きく、膜厚が薄いことが好ましい。スパッタリング法やALD(Atomic layer deposition)法等を用いて形成することができ、成長温度は350℃以下であることが好ましい。

【0144】

第3上部電極13はプラグ19を形成する際のホール形成時にエッチンストッパーとしての役割を果たす。第3上部電極13は、抵抗変化素子22にダメージを与えることなく、さらに抵抗変化膜9からの酸素の脱離を防ぐ機能を有する。

【0145】

第3上部電極13は、バリアメタル20を介したプラグ(コンタクトプラグ)19との接触抵抗を低減するために、バリアメタル20と同じ材料であることが好ましく、Ta、あるいはその窒化物であることが好ましい。第3上部電極は第一の実施形態における制御電極(図2の205)に相当する。

【0146】

層間絶縁膜16には、例えば、シリコン酸化膜、SiOC膜、シリコン酸化膜よりも比誘電率の低い低誘電率膜(例えば、SiOCH膜)等を用いることができる。層間絶縁膜16は、複数の絶縁膜を積層したものであってもよい。

【0147】

層間絶縁膜16には、プラグ19を埋め込むための下穴が形成されており、当該下穴にバリアメタル20を介してプラグ19が埋め込まれている。

【0148】

バリアメタル20は、第2配線17(プラグ19を含む)に係る金属が層間絶縁膜16や下層へ拡散することを防止するために、第2配線17及びプラグ19の側面乃至底面を被覆する、バリア性を有する導電性膜である。

【0149】

バリアメタル20には、例えば、タンタル(Ta)、窒化タンタル(TaN)、窒化チタン(TiN)、炭窒化タングステン(WCN)のような高融点金属やその窒化物等、またはそれらの積層膜を用いることができる。

【0150】

絶縁性バリア膜(バリア絶縁膜)21は、第2配線17を含む層間絶縁膜16上に形成され、第2配線17に係る金属(例えば、Cu)の酸化を防ぐ役割や、上層への第2配線17に係る金属の拡散を防ぐ役割を有する絶縁膜である。絶縁性バリア膜21には、例えば、SiC膜、SiCN膜、SiN膜、及びそれらの積層構造等を用いることができる。

【0151】

<実施例2>

次に、実施例2として、半導体装置の製造方法について図面を用いて説明する。実施例2の製造方法は、第1乃至第四の実施形態、実施例1に示した半導体装置を形成するため方法の一例である。図11乃至図15は、本発明の実施例1に係る半導体装置の製造方法を工程順に模式的に示した工程断面図である。なお、図11乃至図15は、単に図面作成の都合で分図されている。

【0152】

まず、半導体基板(例えば、半導体素子が形成された基板)上に層間絶縁膜2(例えば、シリコン酸化膜、膜厚300nm(nano-meter))を堆積し、その後、リソグラフィ法(フォトレジスト形成、ドライエッチング、フォトレジスト除去を含む)を用いて、層間絶縁膜4に配線溝を形成し、その後、当該配線溝にバリアメタル6(例えば、TaN/Ta、膜厚5nm/5nm)を介して第1配線(図10の3)の銅5を埋め込む(ステップA1;図11(A)参照)。

【0153】

ステップA1において、層間絶縁膜2は、プラズマCVD法によって形成することができる。ここで、プラズマCVD(Chemical Vapor Deposition)法とは、例えば、気体原料、あるいは液体原料を気化させることで減圧下の反応室に連続的に供給し、プラズマエネルギーによって、分子を励起状態にし、気相反応、あるいは基板表面反応等によって基板上に連続膜を形成する手法である。

【0154】

また、ステップA1において、第1配線(5、6:図10の3に対応)は、例えば、PVD(Physical Vapor Deposition)法によってバリアメタル6(例えば、TaN/Taの積層膜)を形成し、PVD法によるCuシードの形成後、電解めっき法によって銅5を配線溝内に埋設し、200℃以上の温度で熱処理後、CMP(Chemical Mechanical Polishing)法によって配線溝内以外の余剰の銅を除去することで形成することができる。

【0155】

このような一連の銅配線の形成方法は、当該技術分野における一般的な手法を用いることができる。ここで、CMP法とは、多層配線形成プロセス中に生じるウェハ表面の凹凸を、研磨液をウェハ表面に流しながら回転させた研磨パッドに接触させて研磨することによって平坦化する方法である。溝に埋め込まれた余剰の銅を研磨することによって埋め込み配線(ダマシン配線)を形成したり、層間絶縁膜を研磨することで平坦化を行う。

【0156】

次に、第1配線(5、6)を含む層間絶縁膜4上に絶縁性バリア膜7(例えば、SiCN膜、膜厚30nm)を形成する(ステップA2;図11(B)参照)。ここで、絶縁性バリア膜7は、プラズマCVD法によって形成することができる。絶縁性バリア膜7の膜厚は、10nm〜50nm程度であることが好ましい。

【0157】

次に、絶縁性バリア膜7上にハードマスク膜8(例えば、シリコン酸化膜)を形成する(ステップA3;図11(C)参照)。

【0158】

このとき、ハードマスク膜8は、ドライエッチング加工におけるエッチング選択比を大きく保つ観点から、絶縁性バリア膜7とは異なる材料であることが好ましく、絶縁膜であっても導電膜であってもよい。ハードマスク膜8には、例えば、シリコン酸化膜、シリコン窒化膜、TiN、Ti、Ta、TaN等を用いることができ、SiN/SiO2の積層体を用いることができる。

【0159】

次に、ハードマスク膜8上にフォトレジスト(図示せず)を用いて開口部をパターニングし、フォトレジストをマスクとしてドライエッチングすることによりハードマスク膜8に開口部パターンを形成し、その後、酸素プラズマアッシング等によってフォトレジストを剥離する(ステップA4;図12(A)参照)。このとき、ドライエッチングは必ずしも絶縁性バリア膜7の上面で停止している必要はなく、絶縁性バリア膜7の内部にまで到達していてもよい。

【0160】

次に、ハードマスク膜8(図12(A)の8)をマスクとして、ハードマスク膜8の開口部から露出する絶縁性バリア膜7をエッチバック(ドライエッチング)することにより、絶縁性バリア膜7に開口部を形成して、絶縁性バリア膜7の開口部から第1配線3を露出させる。このとき、開口部は層間絶縁膜内部にまで達していても良い。その後、アミン系の剥離液等で有機剥離処理を行うことで、第1配線(5,6)の露出面に形成された酸化銅を除去するとともに、エッチバック時に発生したエッチング複生成物等を除去する(ステップA5;図12(B)参照)。

【0161】

ステップA5において、ハードマスク膜(図12(A)の8)は、エッチバック中に完全に除去されることが好ましいが、絶縁材料である場合にはそのまま残存してもよい。また、絶縁性バリア膜7の開口部の形状は、円形、正方形、四角形とし、円の直径、あるいは四角形の一辺の長さは20nmから500nmとすることができる。

【0162】

また、ステップA5において、絶縁性バリア膜7をエッチバックでは、反応性ドライエッチングを用いることで、絶縁性バリア膜7の開口部の壁面をテーパ面とすることができる。反応性ドライエッチングでは、エッチングガスとしてフルオロカーボンを含むガスを用いることができる。

【0163】

次に、ステップA6において、第1配線(5,6)を含む絶縁性バリア膜7上に抵抗変化膜9(例えば、SiC3O1、TaSiO、Ta2O5、ZrO、HfO等、膜厚は4〜10nm)を堆積する(ステップA7;図12(C)参照)。ここで、抵抗変化膜9は、PVD法やCVD法を用いて形成することができる。

【0164】

ステップA7では、絶縁性バリア膜7の開口部は、ステップA5の有機剥離処理によって水分等が付着しているため、抵抗変化膜9の堆積前に250℃〜350℃程度の温度にて、減圧下で熱処理を加えて脱ガスしておくことが好ましい。この際、銅表面を再度酸化させないよう、真空下、あるいは窒素雰囲気等にする等の注意が必要である。

【0165】

また、ステップA7では、抵抗変化膜9の堆積前に、絶縁性バリア膜7の開口部から露出する第1配線(5、6)に対して、H2ガスを用いた、ガスクリーニング、あるいはプラズマクリーニング処理を行ってもよい。このようにすることで、抵抗変化膜9を形成する際に、第1配線(5、6)の銅5)の酸化を抑制することができ、プロセス中の銅の熱拡散(物質移動)を抑制することができるようになる。

【0166】

さらに、ステップA7では、抵抗変化膜9の堆積前に、PVD法を用いて薄膜のTi(2nm以下)(図示せず)を堆積することで、第一配線5銅の酸化を抑制してもよい。薄膜のTi層は抵抗変化膜9の形成中に酸化されて、チタン酸化物となる。

【0167】

また、ステップA7では、抵抗変化膜9として、固体電解質層を用いたタイプではなく、遷移金属酸化物(例えば、TiO、NiO等)や、HfOx、ZrOx、TaOxを用いた抵抗変化膜を用いる場合には、抵抗変化膜9を堆積する前に、下部電極(図示せず)を成膜してもよい。

【0168】

下部電極には、例えば、Ti、TiN、W、WN、Ta、TaN、Ru、RuOx等を用いることができ、例えば、それらの積層構造(例えば、TaN(下層)/Ru(上層))であっても良い。この時、積層構造の合計膜厚は、抵抗変化素子9をビア層間絶縁膜内部に形成する都合上、素子段差と表面ラフネスを低減するため、絶縁性バリア膜7よりも薄いことが必要であり、好ましくは10nm以下であると良い。

【0169】

また、ステップA7では、抵抗変化膜9を段差のある開口部10にカバレッジよく埋め込む必要があるため、プラズマCVD法を用いて行うことが好ましい。

【0170】

次に、抵抗変化膜9上に第1上部電極10(例えば、Ru、膜厚10nm)及び第2上部電極11(例えば、Ta、膜厚10nm)、中間絶縁膜12(たとえはHfOx),第3上部電極13(例えばTa)をこの順に形成する(ステップA8)。

【0171】

次に、第3上部電極13上にハードマスク膜a(例えば、SiN膜、膜厚30nm)、及びハードマスク膜b(例えば、SiO2膜、膜厚200nm)をこの順に積層する(ステップA9、図示せず)。

【0172】

ステップA9において、ハードマスク膜a及びハードマスク膜bは、プラズマCVD法を用いて成膜することができる。ハードマスク膜a、bは当該技術分野における一般的なプラズマCVD法を用いて形成することができる。また、ハードマスク膜aとハードマスク膜bとは、異なる種類の膜であることが好ましく、例えば、ハードマスク膜aをSiN膜とし、ハードマスク膜bをSiO2膜とすることができる。

【0173】

次に、ステップA10において、ハードマスク膜上に、抵抗変化素子22をパターニングするためのフォトレジスト(図示せず)を形成し、その後、当該フォトレジストをマスクとして、ハードマスク膜aが表れるまでハードマスク膜bをドライエッチングし、その後、酸素プラズマアッシングと有機剥離を用いてフォトレジストを除去する。

【0174】

次に、ハードマスク膜をマスクとして、ハードマスク膜b、第3上部電極13、中間絶縁膜12、第二上部電極11、第1上部電極10、抵抗変化膜9を連続的にドライエッチングする(ステップA11、図13(A))。このとき、ハードマスク膜は、エッチバック中に完全に除去されることが好ましいが(図13(A))、そのまま残存してもよい。

【0175】

ステップA11において、例えば、第3上部電極11がTaの場合には、Cl2系のRIE(Reactive Ion Etching)で加工することができる。第1上部電極10がRuの場合には、Cl2/O2の混合ガスでRIE加工することができる。また、抵抗変化膜9のエッチングでは、下面の絶縁性バリア膜7上でドライエッチングを停止させる必要がある。

【0176】

抵抗変化膜9がTaを含む酸化物であり、絶縁性バリア膜7がSiN膜やSiCN膜である場合には、CF4系、CF4/Cl2系、CF4/Cl2/Ar/N2系等の混合ガスでエッチング条件を調節することでRIE加工することができる。

【0177】

このようなハードマスクRIE法を用いることで、抵抗変化素子部をレジスト除去のための酸素プラズマアッシングに曝すことなく、抵抗変化素子22を加工をすることができる。また、加工後に酸素プラズマによって酸化処理する場合には、レジストの剥離時間に依存することなく酸化プラズマ処理を照射することができるようになる。

【0178】

次に、抵抗変化素子22上に、層間絶縁膜16(例えばSiO2)(図13(B))、平坦化し(ステップA12;図14(A))、層間絶縁膜16−2、ハードマスク膜15をさらに堆積する(ステップA13;図14(B))。

【0179】

その後、第2配線17(図10参照)用の配線溝、及びプラグ19用の下穴を形成し、銅デュアルダマシン配線プロセスを用いて、当該配線溝及び当該下穴内に、バリアメタル20(例えば、TaN/Ta)を介して第2配線17(例えば、Cu)及びプラグ19(例えば、Cu)を同時に形成し、その後、第2配線17を含む層間絶縁膜16上に絶縁性バリア膜21(例えば、SiCN膜)を堆積する(ステップA14;図15参照)。なお、図15の断面図は、図5に対応している。図15の第1配線3a(バリアメタル6a、銅5a)は図5の第一電極201a、第1配線3b(バリアメタル6b、銅5b)は図5の第一電極201bに対応している。

【0180】

また、ステップA13、A14において、層間絶縁膜16及び16−2はプラズマCVD法で形成することができる。

【0181】

また、ステップA13において、抵抗変化素子22によって形成される段差を解消するため、層間絶縁膜16を厚く堆積し、CMPによって層間絶縁膜16を削り込んで平坦化し、層間絶縁膜16を所望の膜厚としてもよい(図14(A)参照。)。

【0182】

本実施例によれば、第1配線(5、6:図10の3)を抵抗変化素子22の下部電極とすることで、すなわち、第1配線(5、6)が抵抗変化素子22の下部電極を兼ねることで、抵抗変化素子22の小型化による高密度化を実現するとともに、相補型の抵抗変化素子を形成することができる。このため、信頼性を向上させることができる。

【0183】

通常のCuダマシン配線プロセスに追加工程として、2PR(Photo Regist)のマスクセットを作成するだけで、抵抗変化素子22を搭載することができ、装置の低コスト化を同時に達成することができるようになる。さらに、銅配線によって構成される最先端のデバイスの内部にも抵抗変化素子22を搭載して、装置の性能を向上させることができる。

【0184】

<実施形態6>

次に、本発明の第六の実施形態を説明する。図17は、第六の実施形態の抵抗変化素子のプログラミング回路について示す。プログラミング動作の説明に最低限必要な部分のみを残して抜き出したものである。プログラミング回路は状況に応じてさまざまに変形して利用し得る。

【0185】

図17において、1701及び1702は、抵抗変化素子の第一の電極を表し、それぞれに対して書き込み選択用のスイッチ1703及び1704が接続されており、制御電極1710、書き込み電圧源1709を有する。

【0186】

以下では、スイッチ1703を閉じて(クローズ、導通状態)、スイッチ1704を開放し(オープン、非導通状態)、端子1701側を、OFF状態からON状態に遷移させる場合を説明する。

【0187】

まず、第一のステップにおいて、スイッチ1705を閉じ、キャパシタ1708を充電する。

【0188】

次に第二のステップにおいて、スイッチ1705を開放し、スイッチ1706を閉じる。このとき、制御電極1710には電荷が蓄積されるが、その速度は、スイッチ1706の駆動能力に比例する。

【0189】

第三のステップにおいて、スイッチ1706を開放し、スイッチ1707を閉じる。すると、制御電極1710に蓄えられた電荷は、スイッチ1707を通じてGND(グランド)電位側に放電される。

【0190】

以上の第一のステップから第三のステップを繰り返すことで、所望の交流電流を抵抗変化素子に印加することができる。図17において、各スイッチ1703〜1706には、電界効果型トランジスタ(Field Effect Transistor:FET)を使用することができる。

【0191】

図18は、第六の実施形態において、抵抗変化素子をプログラミングするための、図17の制御電極1710の電圧波形と電流波形の典型例を示す波形図である。

【0192】

例えば、制御電極1710への電荷蓄積の時定数を電荷放出の時定数よりも短く設定することで、制御電極1710から端子1701の向きに流れる電流のピーク値を逆方向の電流のピーク値よりも大きくするとよい。こうするためには、スイッチ1706の駆動力(電流駆動能力)をスイッチ1707の駆動力よりも大とし、瞬間的により大きな電流が流せるようにすると良い。スイッチ1706及びスイッチ1707の駆動力は、スイッチ1706、1707を構成する電界効果トランジスタ(FET)のゲート幅(W)(ゲート幅を大とすると、FETの相互コンダクタンスが増大する)、もしくは、それぞれの電界効果トランジスタに印加されるゲート電圧(ゲート・ソース間電圧)によって調整することができる(例えばFETのゲート・ソース間電圧を大とするとドレイン・ソース間電流が増大する)。

【0193】

キャパシタ1708の容量は、一例として、制御電極の容量の10倍以上とすることが好ましく、例えば制御電極の容量が0.5fF(femto farad)であるときには、5fFのキャパシタンスを設定することが好ましい。

【0194】

端子1702側の抵抗変化素子は、スイッチ1703を開放して、スイッチ1704を閉じて、同様に第一のステップから第三のステップを繰り返すことによりプログラムすることができる。

【0195】

また、抵抗変化素子を、ON状態からOFF状態へ遷移させる際には、スイッチ1706と1707の駆動力の関係を逆になるように回路を構成するとよい。

【0196】

以上、幾つかの実施形態、実施例を説明したが、これら実施形態及び実施例は単に実例を挙げて発明を説明するためのものであって、限定することを意味するものではない。

【0197】

例えば、CMOS回路を有する半導体製造装置技術に関して詳しく説明し、半導体基板上の銅多層配線内部に抵抗変化素子を形勢する例について説明したが、本発明は上記に限定されるものではなく、例えば、

・DRAM(Dynamic Random Access Memory)、

・SRAM(Static Random Access Memory)、

・一括消去型の書き換え可能な不揮発性メモリであるフラッシュメモリ(あるいはEEPROM:Electrically Erasable and Programmable Read Only Memory)、

・FRAM(Ferro Electric Random Access Memory)、

・MRAM(Magnetic Random Access Memory)、

・抵抗変化型メモリ、

・バイポーラトランジスタ

等のようなメモリ回路を有する半導体製品、あるいは、

マイクロプロセッサ等の論理回路を有する半導体製品、あるいは、

これらを同時に掲載したボードやパッケージの銅配線上へも適用することができる。

【0198】

また、本発明は、半導体装置への電子回路装置、光回路装置、量子回路装置、マイクロマシン、MEMS(Micro Electro Mechanical Systems)等の接合にも適用することができる。

【0199】

また、本発明ではスイッチ機能での実施例を中心に説明したが、不揮発性と抵抗変化特性の双方を利用したメモリ素子に用いることもできる。

【0200】

本発明による基板の接合方法は、そのできあがりからも、確認することができる。具体的には、例えば、デバイスの断面をTEM(Transmission Electron Microscope;透過型電子顕微鏡)観察することで、多層配線に銅配線が用いられていることを確認し、抵抗変化素子が搭載されている場合には、当該抵抗変化素子が積層構造であることかた、該積層構造内部に中間絶縁膜を備えているかを観察することで確認することができ、本発明を実施した構造であるかを確認することができる。

【0201】

さらにTEMに加え、例えばEDX(Energy Dispersive X-ray Spectroscopy;エネルギー分散型X線分光法)や、EELS(Electron Energy-Loss Spectroscopy;電子エネルギー損失分光法)等の組成分析を行うことで、本発明を実施した構造であるか否かの確認を行うことができる。

【0202】

なお、上記の特許文献、非特許文献の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素(各請求項の各要素、各実施例の各要素、各図面の各要素等を含む)の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0203】

3、3a、3b 第1配線

4 層間絶縁膜

5、5a、5b 銅

6、6a、6b、20 バリアメタル

7 絶縁性バリア膜

8 ハードマスク膜

9 抵抗変化膜

10 第1上部電極

11 第2上部電極

12 中間絶縁膜

13 第3上部電極

15 ハードマスク膜

16、16−2 層間絶縁膜

17 第2配線

18 Cu(銅)

19 プラグ

20 バリアメタル

21 絶縁性バリア膜

22、701a、801a、801b、901 抵抗変化素子

101、401a、401b、701a、801a、801b 抵抗変化素子

102、103、402a、402b、702a、703a、802a、803a 端子

104、404 制御端子

201、501a、501b 第一の電極

202、502 抵抗変化層(抵抗変化膜)

203、503、 第二の電極

204、304、504、604 中間絶縁膜

205、305、505、605 制御電極

301、601a、601b 活性電極

302、602 固体電解質層(固体電解質)

303、603 不活性電極

306、606a、606b 金属架橋

405 トランジスタ

704a 制御端子

705a、705b、805a、805b 水平線

706a、706b、806a、806b 垂直線

707a、707b、707c、807a、807b、807c、906a〜906e 対角線

804a 制御端子

1701、1702 端子

1703〜1707 スイッチ

1708 キャパシタ(容量)

1709 書き込み電圧源

1710 制御電極

【技術分野】

【0001】

本発明は、半導体装置に関し、特に抵抗変化素子及びそのプログラミング方法に関する。

【背景技術】

【0002】

半導体装置のうち、特にシリコンデバイスは、微細化(スケーリング則:Mooreの法則)によってデバイスの集積化・低電力化が進められ、3年4倍のペースで開発が進められてきた。近年、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)のゲート長は20nm以下となり、リソグラフィプロセスの高騰(装置価格及びマスクセット価格)、及びデバイス寸法の物理的限界(動作限界・ばらつき限界)により、これまでのスケーリング則とは異なるアプローチでのデバイス性能の改善が求められている。

【0003】

近年、ゲートアレイとスタンダードセルの中間的な位置づけとしてFPGAと呼ばれる再書き換え可能なプログラマブルロジックデバイスが開発されている。FPGAは、顧客自身がチップの製造後に任意の回路構成を行うことを可能とするものである。FPGAは、多層配線層の内部に抵抗変化素子を有し、顧客自身が任意に配線の電気的接続をできるようにしたものである。このようなFPGAを搭載した半導体装置を用いることで、回路の自由度を向上させることができるようになる。

【0004】

抵抗変化素子としては、

(A)遷移金属酸化物を用いたReRAM(Resistance Random Access Memory)や、

(B)固体電解質層を用いたNanoBridge(NEC社の登録商標)

などがある。

【0005】

一方、混載メモリについては、揮発性のeDRAM(embedded Dynamic Random Access Memory)、不揮発性のフラッシュメモリ等が用いられている。eDRAMでは、記憶した情報が電源を切ると消失してしまう。フラッシュメモリでは高、電圧(5V以上)が必要とされる。このため、低電圧(1V以下)で動作するロジックLSIへの混載には不向きである点等が課題となっていた。

【0006】

<バイポーラ型抵抗変化素子>

バイポーラ型固体電解質スイッチ素子は、OFF状態(高抵抗状態)とON状態(低抵抗状態)との切り替えに逆極性の電圧が必要なスイッチ素子である。ここで、典型的なバイポーラ型抵抗変化素子の動作特性について図16(A)乃至(D)を用いて説明する。

【0007】

例えば、第一電極、抵抗変化素子、第二電極から構成されるバイポーラ型抵抗変化素子の場合には、第一電極に正電圧を印加すると(図16(A))、所望のセット電圧を閾値電圧として、OFF状態(高抵抗状態)からON状態(低抵抗状態へ遷移する)。

【0008】

続いて、ON状態の抵抗変化素子において、再び第一電極に正電圧を印加した場合には(図16(B))、オーミックな電流−電圧特性を示す。

【0009】

続いて、第一電極に負電圧を印加すると(図16(C))、所望のセット電圧を閾値電圧として、ON状態(低抵抗状態)からOFF状態(高抵抗状態へ遷移する)。

【0010】

さらに、続いて、ON状態の抵抗変化素子において、再び第一電極に正電圧を印加すると(図16(D))、所望の閾値電圧(リセット電圧)において、ON状態からOFF状態へ遷移する。

【0011】

このように、

第一電極に正電圧を印加した場合にのみ、OFF状態からON状態へ遷移し、

第一電極に負電圧を印加した場合にのみ、ON状態からOFF状態への遷移

が生じる素子をバイポーラ型抵抗変化素子として定義する。

【0012】

<バイポーラ型抵抗変化素子における電極の定義>

ここで、バイポーラ型抵抗変化素子に用いられる電極を定義する。図16で説明したように、正電圧を印加した場合にOFF状態からON状態に遷移する電極を「第一の電極」、あるいは「活性電極」と定義する。

【0013】

逆に正電圧を印加した場合にON状態からOFF状態に遷移する電極を「第二の電極」、あるいは「不活性電極」と定義する。

【0014】

二つの異なる抵抗変化素子を接続する場合に、各抵抗変化素子の電極同士を電気的に接続することになる。この場合、二つの異なる抵抗変化素子の活性電極同士、あるいは、不活性電極同士が電気的に接続されている、あるいは一体化されていることを、「同一極性同士の電極の接続」というものとする。

【0015】

<固体電解質層型抵抗変化素子の説明>

上記したバイポーラ型抵抗変化素子の例として、非特許文献1には、固体電解質層(イオンが電界等の印加によって自由に動くことのできる固体)中における金属イオン移動と電気化学反応とを利用したスイッチング素子が開示されている。非特許文献1に開示されたスイッチング素子は、固体電解質層、該固体電解質層に一側と該一側と反対側の各面に当接して対向配置された第1電極及び第2電極の3層から構成されている。このうち、第1電極は、固体電解質層に金属イオンを供給するための役割を果たしている。第2電極からは、金属イオンは供給されない。

【0016】

以下では、このスイッチング素子の動作について簡単に説明する。

【0017】

第1の電極を接地して第2電極に負電圧を印加すると、第1電極の金属が金属イオンになって固体電解質層に溶解する。そして、固体電解質層中の金属イオンが固体電解質層中に金属になって析出する。固体電解質層中に析出した金属により、第1電極と第2電極を接続する金属架橋が形成される。金属架橋により第1電極と第2電極が電気的に接続することで、スイッチング素子はオン状態になる。

【0018】

一方、上記オン状態で、第1電極を接地して第2電極に正電圧を印加すると、金属架橋の一部が切れる。これにより、第1電極と第2電極との電気的接続が切れ、スイッチング素子はオフ状態になる。なお、電気的接続が完全に切れる前の段階から、第1電極及び第2電極間の抵抗が大きくなったり、電極間容量が変化したりする等、その電気特性が変化し、最終的に電気的接続が切れる。

【0019】

また、上記オフ状態からオン状態にするには、再び第1の電極を接地して第2電極に負電圧を印加すればよい。

【0020】

固体電解質層型抵抗変化素子によるスイッチング素子として、非特許文献1では、固体電解質層を介して第1、第2の電極が配置され、それらの間の導通状態を制御する2端子型のスイッチング素子の構成及び動作が開示されている。

【0021】

このような固体電解質層型抵抗変化素子によるスイッチング素子は、半導体スイッチ(MOSFET(Metal Oxide Semiconductor Field Effect Transistor)等)よりもサイズが小さく、オン抵抗が小さいという特徴を持っている。このため、プログラマブルロジックデバイスへの適用に有望であると考えられている。

【0022】

また、このスイッチング素子においては、その導通状態(オン又はオフ)は印加電圧をオフにしてもそのまま維持される。このため、不揮発性のメモリ素子としての応用も考えられる。例えば、トランジスタ等の選択素子1個とスイッチング素子1個とを含むメモリセルを基本単位として、このメモリセルを縦方向と横方向にそれぞれ複数配列する。このように配列することで、ワード線及びビット線で複数のメモリセルの中から任意のメモリセルを選択することが可能となる。そして、選択したメモリセルのスイッチング素子の導通状態をセンスし、スイッチング素子のオン又はオフの状態から情報「1」又は「0」のいずれの情報が格納されているかを読み取ることが可能な不揮発性メモリを実現できる

【0023】

なお、不揮発性の可変抵抗素子に関して、特許文献1には、第1の電極と、第2の電極と、第1の電極及び第2の電極の双方に接続する可変抵抗体と、誘電層を介して可変抵抗体に接続する制御電極を備え、誘電層は第2の可変抵抗体の側面に接した構成が開示されている。

【先行技術文献】

【特許文献】

【0024】

【特許文献1】特開2010−153591号公報

【非特許文献】

【0025】

【非特許文献1】Shunichi Kaeriyama et al., "A Nonvolatile Programmable Solid-Electrolyte Nanometer Switch", IEEE Journal of Solid-State Circuits, Vol.40, No.1, pp.168-176, January 2005.

【発明の概要】

【発明が解決しようとする課題】

【0026】

以下に関連技術の分析を与える。

【0027】

前述したような2端子型抵抗変化素子を半導体装置上に形成してプログラミングする場合、例えば信号線の伝達先を不揮発的に切り替えるスイッチに適用する場合、プログラミングのための制御信号線と、プログラミング後にON状態となった抵抗変化素子を介して伝搬する信号線とが独立していないため、プログラミングの制御が難しく、誤動作を生じ易い、という問題点を有している。

【0028】

本発明は、上記問題点を解消すべく全く新たに創案されたものであって、その主たる目的は、誤書き込み、及び誤動作を防止し、高信頼化、及び高密度化が可能な抵抗変化素子、及びそのプログラミング方法を提供することにある。

【課題を解決するための手段】

【0029】

本発明によれば、第一の電極と、抵抗変化層(抵抗変化膜)と、第二の電極と、中間絶縁膜と、制御電極と、をこの順に積層した積層構造を備え、前記抵抗変化層と前記中間絶縁膜が直接接していない抵抗変化素子が提供される。

【0030】

本発明によれば、上記抵抗変化素子に対して、前記第一の電極と制御電極との間に規則的に交番する電圧を印加し、過渡的に流れる交流電流を両電極間に流すことによって前記抵抗変化素子の抵抗値を遷移させる、プログラミング方法が提供される。

【発明の効果】

【0031】

本発明によれば、抵抗変化素子の誤書き込み、及び誤動作を防止し、高信頼化、及び高密度化を可能としている。

【図面の簡単な説明】

【0032】

【図1】(A)は関連技術(比較例)の2端子抵抗変化素子回路の等価回路、(B)は第一の実施形態の制御端子付き抵抗変化素子の等価回路を示す図である。

【図2】第一の実施形態の構成を示す図である。

【図3】第一の実施形態の構成の一例を示す図である。

【図4】(A)は関連技術の2端子抵抗変化素子を二つ使用した相補型抵抗変化素子回路、(B)は、第二の実施形態の制御端子付き抵抗変化素子の等価回路を示す図である。

【図5】第二の実施形態の構成を示す図である。

【図6】第二の実施形態の構成の一例を示す図である。

【図7】第三の実施形態の構成を等価回路で示す図である。

【図8】第四の実施形態の構成を等価回路で示す図である。

【図9】第五の実施形態の構成を説明する図である。

【図10】実施例1の半導体装置の断面を模式的に示す図である。

【図11】(A)乃至(C)は実施例2の製造工程における断面を模式的に示す工程断面図である。

【図12】(A)乃至(C)は実施例2の製造工程における断面を工程順に模式的に示す工程断面図である。

【図13】(A)及び(B)は実施例2の製造工程における断面を工程順に模式的に示す工程断面図である。

【図14】(A)及び(B)は実施例2の製造工程における断面を工程順に模式的に示す工程断面図である。

【図15】実施例2の製造工程における断面を示す工程断面図である。

【図16】(A)乃至(D)は典型的なバイポーラ型抵抗変化素子の動作特性を説明する図である。

【図17】第六の実施形態を説明する図である。

【図18】第六の実施形態の動作を説明する波形図である。

【発明を実施するための形態】

【0033】

本発明の第1の形態においては、例えば図2を参照すると、第一の電極(201)と、抵抗変化層(抵抗変化膜)(202)と、第二の電極(203)を有する抵抗変化素子において、第二の電極(203)に接する中間絶縁膜(204)と、中間絶縁膜(204)に接する制御電極(205)を備える。

【0034】

第一の電極(201)と制御電極(205)間に電圧を印加することで、抵抗変化膜(202)の抵抗状態を変化させ、かつ、第二の電極(203)を利用して抵抗状態の読み出しや、信号の入出力がなされる電気回路を有する半導体装置を構成することができる。

【0035】

制御電極(205)は、中間絶縁膜(204)によって第二の電極(203)と絶縁分離されているため、制御電極(205)に印加されるプログラミング信号と、第一の電極(201)と第二の電極(202)間を伝搬するロジック信号/読み出し信号とを分離することができる。

【0036】

かかる本発明によれば、抵抗変化層の抵抗状態を、抵抗変化層とは直接接しない中間絶縁膜(204)を介して絶縁分離された制御電極(205)への電圧印加で行うことによって、プログラミングのための制御信号線と、プログラミング後に接続される信号線(もしくは読み出し線)を独立させることができる。このため、抵抗変化素子の誤書き込み、及び誤動作を防止することができる。

【0037】

第一の電極(201)と制御電極(205)間に印加された電圧は、抵抗変化膜(202)と中間絶縁膜(204)とで電圧分割される。例えば、より小さい制御電圧で抵抗変化素子の抵抗状態をOFF状態からON状態へ変化させる(プログラミングする)ためには、印加した制御電圧の大半が抵抗変化素子に印加させることが好ましい。

【0038】

そのため、第二の電極(203)に蓄積する電荷を一定とした場合、中間絶縁膜(204)の比誘電率が、抵抗変化膜(202)の比誘電率よりも大きいことが好ましい。さらに、中間絶縁膜(204)の厚さは、抵抗変化膜(202)の厚さよりも薄いことが好ましい。

【0039】

例えば、第一の電極(201)は、金属イオンを供給する活性電極(図3の301)を含む構成としてもよい。また、抵抗変化層(202)は、イオン化した金属が伝導する固体電解質層(図3の302)を含む構成としてもよい。さらに、第二の電極(203)は、前記金属イオンと反応しない不活性電極(図3の303)を含む構成としてもよい。

【0040】

前記中間絶縁膜(204、304)は、ハフニア膜、アルミナ膜、ジルコニア膜、イットリア膜、シリコン窒素膜、シリコン炭化窒素膜、シリコン酸化膜のいずれかを含むことが好ましい。

【0041】

前記制御電極(205、305)は、Ta、Ti、TaN、TiN、W、Alのいずれを含むことが好ましい。

【0042】

本発明の第2の形態によれば、相補型構造抵抗変化素子を有するクロスバースイッチ回路を有する半導体装置が提供される。

【0043】

本発明の第2の形態においては、例えば図5を参照すると、半導体素子基板上に形成された、バイポーラ型抵抗変化素子において、第一の電極と、抵抗変化層と、第二の電極と、中間絶縁膜と、制御電極とがこの順に積層した、積層構造を備える、少なくとも2つの抵抗変化素子であって、前記2つの抵抗変化素子の、抵抗変化層(502)同士、第二の電極(503)同士、中間絶縁膜(504)同士、及び制御電極(505)同士が一体化している構成としてもよい。

【0044】

半導体装置において、前記抵抗変化素子は、

半導体装置内の多層配線層に形成され、前記第一電極は下部電極を兼ねた配線(図10の3)であって、

前記抵抗変化膜(図10の9)との間に絶縁性バリア膜(図10の7)が介在し、

前記絶縁性バリア膜(図10の7)は開口部を有し、

前記抵抗変化膜(図10の9)は、前記開口部において前記下部電極兼配線(3)と接する構成としてもよい。

【0045】

前記抵抗変化素子構造において、前記絶縁性バリア膜(7)は一つの開口部を有し、それぞれ独立した下部電極兼配線(3)上に開口されており、上部電極は二つの抵抗変化素子間で電気的に一体化した構成としてもよい。

【0046】

前記抵抗変化素子構造において、それぞれ独立した少なくとも2本の下部電極兼配線の双方に接続するように前記絶縁性バリア膜は一つの開口部を有する構成としてもよい。

【0047】

本発明の第3の形態においては、前記固体電解質層は、少なくともSiOxCy、TaSiOx、TaOx、ZrOx、HrOx、SiOx、TiOx、有機物を主成分とする材料のいずれかを含む。

【0048】

前記第一の電極は、銅を含む構成としてもよい。前記第二の電極は、Ru、あるいはPtかを含む構成としてもよい。絶縁性バリア膜は、SiC、SiCN、SiNのいずれかを含む構成としてもよい。

【0049】

前記第二の電極は、固体電解質と接する面にRu、中間絶縁膜に接する面にTaを含む積層電極(Ru/Ta)としてもよい。

【0050】

本発明の第4の形態において、半導体装置の製造方法は、半導体基板上の多層配線層の内部に抵抗変化素子を有する半導体装置の製造にあたり、

下層配線上に絶縁性バリア膜(図10の7)を形成する工程と、

前記絶縁性バリア膜上に開口部パターンを有するハードマスク膜(図11(C)の8)を形成する工程と、

前記ハードマスク膜をマスクとして、前記開口部パターンから露出する前記絶縁性バリア膜を反応性ドライエッチングにより、前記絶縁性バリア膜に、前記下層配線に通ずるととともに、壁面が前記配線から離れるにしたがい広くなったテーパ面となった開口部を形成する工程(図12(A))と、

前記抵抗変化膜(図10、図12(C)の9)を形成する工程と、

前記上部電極(図10の10、11、13)を形成する工程と、

を含む。

【0051】

前記絶縁性バリア膜上に開口部を形成する工程において、2本の異なる下層配線の双方に連続した一つの開口部を形成するようにしてもよい。

【0052】

前記配線を形成する工程は、前記抵抗変化膜の前記下部電極とならない他の配線を同時に形成し、

前記プラグを形成する工程では、前記他の配線上に他のプラグを形成する半導体装置の製造方法であることが好ましい。

【0053】

本発明の第5の形態において、前記抵抗変化層をOFF状態からON状態へ、もしくはON状態からOFF状態へ抵抗値を遷移させるためには、書き込み電圧を前記抵抗変化層の両端に印加する際に、書き込み電流が流れることが好ましい。前記抵抗変化層と前記中間絶縁膜を流れるリーク電流が少なすぎると、書き込み電流が不十分となる可能性がある。この場合、第一の電極と制御電極の間に交番する電圧を印加し、交流電流を両電極間に流すようにしてもよい。

【0054】

さらに、本発明の第5の形態において、前記抵抗変化層の両端に印加される電圧波形が上昇時と下降時で異なる時間変化をもたせるようにしてもよい。このようにすることで、容量性の電流の時間変化は電圧の時間変化の微分値に比例するため、交流電流の各々の極性に対して、異なるピーク電流値を設定することができる。

【0055】

このピーク電流値の差によって、抵抗変化素子をON状態もしくはOFF状態に状態遷移させることができる。

【0056】

例えば、バイポーラ型抵抗変化素子において、第一の電極から不活性電極側に電流を流すことで、OFF状態からON状態に抵抗値が遷移する場合を考えると、第一の電極から不活性電極に流れる電流のピーク値を高くし、逆方向のピーク値を低くすることによって、交流電流によるプログラミングを可能としている。

【0057】

半導体装置内の多層配線層の内部に抵抗変化素子を有するフィールドプログラマブルゲートアレイ、混載メモリを搭載した半導体装置に適用して好適とされる。以下、いくつかの実施形態について説明する。

【0058】

<実施形態1>

図1(A)は、関連技術(比較例)の2端子抵抗変化素子回路の等価回路、図1(B)は、本実施形態に係る制御端子付き抵抗変化素子の等価回路を示す。図1(A)、(B)において、101は抵抗変化素子、102、103は端子である。図1(B)に示すように、本発明の実施形態では、制御信号の入出力を行う制御端子104を有する。

【0059】

本発明の第一の実施形態に係る半導体装置について、図1(B)、図2、図3を参照して説明する。図2は、図1(B)の第一の実施形態の抵抗変化素子の断面構成を模式的に示す図である。図2を参照すると、抵抗変化素子は、第一の電極201、抵抗変化膜202、第二の電極203、中間絶縁膜204、制御電極205がこの順に積層されている。

【0060】

例えば、抵抗変化素子が、金属イオンの析出を利用した固体電解質スイッチである場合には、第一の電極201は、図3の活性電極301、抵抗変化膜202は図3の固体電解質層302、第二の電極203は図3の不活性電極303である。

【0061】

固体電解質スイッチをOFF状態からON状態へ遷移させる場合には、第一の電極201(活性電極301)を接地し、制御電極205(305)に負電圧を印加すると、抵抗変化膜202(固体電解質層302)と中間絶縁膜204間で電圧分割された電圧が、抵抗変化膜202(固体電解質層302)に印加され、図3の金属架橋306が形成される。

【0062】

ここで、できるだけ電圧値が小さな制御電圧で、固体電解質スイッチの抵抗状態を変化させるためには、抵抗変化膜202(固体電解質層302)と中間絶縁膜204(絶縁膜304)の抵抗値が同じ場合には、中間絶縁膜204(絶縁膜304)の比誘電率が抵抗変化膜202(固体電解質層302)よりも大きくし、膜厚は薄いことが好ましい。

【0063】

例えば、抵抗変化膜202(固体電解質層302)は、有機膜を主成分とする膜(例えば、比誘電率:3.0、膜厚:5nm)を含む。

【0064】

中間絶縁膜204(絶縁膜304)は、ハフニア(HfOx;比誘電率:20、膜厚:6nm)を含む。

【0065】

このとき、直列接続における電荷の分布から、抵抗変化膜202(固体電解質層302)、及び中間絶縁膜204(絶縁膜304)に印加される電圧の比率は1:20となる。すわなち、制御電極205(305)に、例えば2Vを印加すると、抵抗変化膜202(固体電解質層302)に約1.9V印加することができる。

【0066】

また、抵抗値の観点からも、中間絶縁膜204(絶縁膜304)の膜厚が抵抗変化膜202(固体電解質層302)よりも薄いことが好ましい。

【0067】

抵抗変化膜202(固体電解質層302)としては低密度な膜を用いることが好ましい。このため、緻密な材料から構成される中間絶縁膜204(絶縁膜304)と比べるとリーク電流が大きくなる傾向がある。

【0068】

それぞれの抵抗値を等しくするためには、抵抗変化膜202(固体電解質層302)の膜厚よりも中間絶縁膜204(絶縁膜304)の膜厚を薄くすることでリーク電流レベルを一致させることもできるようになる。

【0069】

ここで、本実施形態における、誤書き込み、誤動作不良の改善要因について説明する。

【0070】

制御電極を有しない抵抗変化素子の場合(図1(A)参照)、第一の電極201と第二の電極203に直接電位差を生じさせることで、抵抗変化膜202の抵抗状態を変化(プログラミング)させる。

【0071】

一方、本実施形態によれば、抵抗変化層202の抵抗状態を、抵抗変化層202とは直接接しない中間絶縁膜204を介して絶縁分離されている制御電極(205)へ電圧を印加することによって、プログラミングのための制御信号線と、プログラミング後に接続される信号線(もしくは読み出し線)を独立させることができる。このため、抵抗変化素子の誤書き込み、及び誤動作を防止することができる。

【0072】

<実施形態2>

次に本発明の第二の実施形態について説明する。第二の実施形態では、不活性電極(第二の電極)同士が接続された相補型抵抗変化素子を例に説明する。図4(A)は、関連技術の2端子抵抗変化素子を二つ使用した相補型抵抗変化素子回路、図4(B)は、第二の実施形態による制御端子付き抵抗変化素子の回路を示す図である。

【0073】

図4(A)の構成では、抵抗変化素子401aと抵抗変化素子401bは、活性電極同士が接続され、活性電極に接続された端子402a、402bを介して、入出力を行う。抵抗変化素子401aと抵抗変化素子401bの不活性電極にトランジスタ(MOSトランジスタ)405のソース又はドレイン端子を接続して制御する。

【0074】

一方、第二の実施形態の抵抗変化素子では、図4(B)に示すように、トランジスタを接続することなく、制御信号の入出力を行う制御端子404を有する構造としている。このため、図4(A)のトランジスタ相当分の回路面積が削減される。抵抗変化素子抵抗変化素子(スイッチ)の面積を低減することができる。

【0075】

次に、第二の実施形態の抵抗変化素子について、活性電極同士が電気的に接続される構造について、図5、図6を用いて説明する。

【0076】

図5に示す例では、2つの抵抗変化素子を有し、前記抵抗変化素子の抵抗変化膜502同士、第二の電極503同士、中間絶縁膜504同士、制御電極505同士が接続され、未接続の二つの第一の電極501a、501bから入出力がなされる。

【0077】

第一の実施の形態のように、制御電極505に電圧を印加することで、抵抗変化膜502の抵抗状態を変化させ、抵抗状態を不揮発に記憶することができる、

【0078】

二つの抵抗変化素子を有することで、未接続の二つの第一の電極(第一の電極501aと第一の電極501b)の間で、抵抗値の読み出し、あるいは信号の入出力を行うことができる。

【0079】

このとき、制御電極505は、第一の電極501a、第一の電極501b、及び、第二の電極503とは絶縁分離されているため、プログラム用の制御信号と、ロジック信号(読み出し信号)とが混線することはない。

【0080】

図6に示す例では、2つのバイポーラ型の固体電解質スイッチを有し、前記抵抗変化素子の固体電解質602同士、不活性電極603同士、中間絶縁膜604同士、制御電極605同士が接続され、かつ未接続の二つの第一の電極(第一の活性電極601a、第二の活性電極601b)から入出力がなされる。

【0081】

スイッチング素子をオン状態(低抵抗状態)にするためには、制御電極605に電圧が印加されることで、第一の活性電極601a、及び第二の活性電極601bのそれぞれから金属架橋606a及び606bが固体電解質602内に形成され、第一の活性電極601aと不活性電極603と第二の活性電極601bが電気的に接続される。

【0082】

このとき、第一の実施形態と同じく、制御電極605は、中間絶縁膜604を介して不活性電極とは絶縁分離されているため、活性電極と不活性電極の接続状態によらず、分離されている。

【0083】

<実施形態3>

次に本発明の第三の実施形態について説明する。第三の実施形態では、制御電極を有する抵抗変化素子(第一の実施形態)を、アレイ状に配置したスイッチ(クロスバースイッチ)として用いることで、スイッチ素子の小面積化を図ることができるようになる。

【0084】

図7は、第三の実施形態の構成を示す図である。図7には、抵抗変化素子をアレイ上に配置し、クロスバースイッチとした構成が等価回路で示されている。図7を参照すると、抵抗変化素子701aは、図2の第一の電極201と接続する端子702aと、第二電極203と接続する端子703a、及び制御電極205と接続する制御端子704aを有する。水平線705a、705bの各水平線上で隣り合う抵抗変化素子の第二の電極203と接続する端子同士は接続され、垂直線706a、bの各垂直線上で隣り合う抵抗変化素子の第一の電極201と接続する端子同士も接続されている。対角線707上に配置された抵抗変化素子の制御電極205同士が接続されている。すなわち、抵抗変化素子701aは、水平線705a、垂直線706a、対角線707aの交点に位置する。

【0085】

ここで、図7において、全ての抵抗変化素子がオフ状態であるとし、抵抗変化素子701aをオン状態にプログラミングする場合について説明する。

【0086】

・垂直線706aにセット電圧を印加し、それ以外の垂直線には、セット電圧の半分の電圧を印加し、

・水平線はすべてフローティングとし、

・対角線707aは接地電位とし、それ以外の対角線はセット電圧の半分の電圧を印加する。

【0087】

このような電圧印加を行うことで、クロスーバーアレイ内の抵抗変化素子701aのみの第一の電極(図2の201)−制御電極(図2の205)間にセット電圧が印加され、プログラミングを行うことができる。

【0088】

非選択の抵抗変化素子には最大でもセット電圧の半分の電圧しか印加されないため、オン状態にプログラミングされることはない。

【0089】

オン状態の抵抗変化素子701aをオフ状態にプログラミングする場合には、

・対角線は全てフローティングにし、

・水平線705aにセット電圧を印加し、それ以外の水平線にはセット電圧の半分の電圧を印加し、

・垂直線706aは接地電位とし、それ以外の垂直線はセット電圧の半分の電圧を印加する。

【0090】

このような電圧印加を行うことで、制御端子を用いて選択した交点に位置する抵抗変化素子のプログラミングを行い、任意の抵抗状態にすることができる。

【0091】

このような操作を各交点について繰り返すことで、クロスバースイッチとして所望の接続状態が得ることができる。

【0092】

このとき、制御端子同士を接続している対角線は、抵抗変化素子の抵抗状態によらず、常に抵抗変化素子とは絶縁分離されているため、プログラミングの精度が向上する。

【0093】

<実施形態4>

次に本発明の第四の実施形態について説明する。第四の実施形態では、制御電極を有する相補型抵抗変化素子(図5参照)をアレイ上に配置したスイッチ(クロスバースイッチ)として用いることで、スイッチ素子の小面積化を図る。

【0094】

相補型抵抗変化素子は、図5に示すように、

・二つの抵抗変化素子間で電圧分割される点と、

・バイポーラ型抵抗変化素子が互いに異なるセット電圧方向で直列接続される点

から、

相補型抵抗変化素子のOFF時におけるディスターブに対する信頼性が改善する。さらに、制御端子を加えることで、よりプログラミングの制御性を向上することができる。

【0095】

図8は、第四の実施形態の構成を示す図である。図8には、相補抵抗変化素子をアレイ上に配置し、クロスバースイッチとした時の構成が等価回路で示されている。図8を参照すると、抵抗変化素子801a、及び抵抗変化素子801bのそれぞれの第一の電極と接続する端子803aと802aが、水平線805a、及び垂直線806aに接続している。

【0096】

抵抗変化素子801a及び801bの第二電極同士と接続する制御端子804aは対角線807bに接続している。すなわち、抵抗変化素子801a及び801bは、水平線805a、垂直線806a、対角線807bの交点に位置する。

【0097】

ここで、全ての抵抗変化素子がオフ状態であるとし、抵抗変化素子801a及び801bの双方をオン状態として、クロスバーの交点をオン状態にプログラミングする場合について説明する。

【0098】

まず、抵抗変化素子801aをオン状態にするために、

・水平線805aにセット電圧を印加し、それ以外の水平線にはセット電圧の半分の電圧を印加し、

・垂直線はすべてフローティングとし、

・対角線807bは接地電位とし、それ以外の対角線はセット電圧の半分の電圧を印加する。

【0099】

このような電圧印加を行うことで、抵抗変化素子801aのみの第一の電極−制御電極間にセット電圧が印加され、プログラミングを行うことができる。

【0100】

非選択の抵抗変化素子には最大でもセット電圧の半分の電圧しか印加されないため、オン状態にプログラミングされることはない。

【0101】

つづいて、抵抗変化素子801bをオン状態にするため、

・垂直線806aにセット電圧を印加し、それ以外の垂直線にはセット電圧の半分の電圧を印加し、

・水平線は全てフローティングとし、

・対角線807bは接地電位とし、それ以外の対角線はセット電圧の半分の電圧を印加する。

【0102】

このような電圧印加を行うことで、抵抗変化素子801bのみの第一の電極−制御電極間にセット電圧が印加され、プログラミングを行うことができるようになる。

【0103】

このように抵抗変化素子801a及び801bの双方がオン状態になることで、垂直線806aと水平線805aを接続することができるようになる。

【0104】

<実施形態5>

次に本発明の第五の実施形態について説明する。第五の実施形態では、第三の実施形態及び第四の実施形態4のクロスバースイッチの構成において、対角線の共有化を行うことで、対角線につながるプログラミングドライバーの数を削減し、低面積化をすることができるようになる。

【0105】

図9は、対角線の共有化を行った場合のクロスバースイッチへの適用形態を説明する図である。図中は5×5の抵抗変化素子がマトリックス上に配置されている。

【0106】

このとき、5本の対角線906a〜906eまでが配置され、それぞれが5つの抵抗変化素子と接続されており、接続されている抵抗変化素子は、行・列内に一つだけ接続されている。すなわち、nxnのクロスバースイッチの場合、それぞれn個の抵抗変化素子と接続された、計n本の対角線を有する構成とすることで、クロスバースイッチに用いる対角線の小面積化を図ることができる。

【0107】

次に、上記した抵抗変化素子を含む半導体装置の一具体例とその製造方法の一例について詳細に説明する。

【0108】

半導体基板上の多層配線層の内部に抵抗変化素子を有する半導体装置の製造方法は、下部電極(例えば図2の第一の電極201)を兼務した配線上に、抵抗変化膜(例えば図2の202)、上部電極(例えば図2の第二の電極203)をこの順に形成する工程と、前記上部電極(図2の203)上に、絶縁膜(例えば図2の中間絶縁膜204)を介して上層配線(例えば図2の制御電極205)を形成する工程を形成する工程と、を含む。以下、より具体的な実施例について説明する。

【0109】

<実施例1>

本発明に係る抵抗変化素子の一具体例について説明する。図10は、実施例1の半導体装置の構成を模式的に示した部分断面図である。

【0110】

実施例1の半導体装置は、半導体基板上の銅多層配線層の内部に抵抗変化素子22を有する装置である。

【0111】

多層配線層は、半導体基板(図示せず)上にて、層間絶縁膜4、絶縁性バリア膜7、層間絶縁膜16、及び絶縁性バリア膜21の順に積層した絶縁積層体を有する。

【0112】

第1配線3は、層間絶縁膜4に形成された配線溝にバリアメタル6を介して銅5が埋め込まれている。

【0113】

第2配線17は、層間絶縁膜16に形成された配線溝に、バリアメタル20を介して、銅18が埋め込まれており、層間絶縁膜16に形成された下穴にプラグ19が埋め込まれており、第2配線17とプラグ19が一体となっており、第2配線17及びプラグ19の側面乃至底面がバリアメタル20によって覆われている。

【0114】

多層配線層は、絶縁性バリア膜7に形成された開口部にて、下部電極となる第1配線3、絶縁性バリア膜7の開口部の壁面、乃至絶縁性バリア膜7上に、抵抗変化膜9、第1上部電極10、及び第2上部電極11の順に積層した抵抗変化素子22が形成されている。抵抗変化膜9、第1上部電極10、第2上部電極11、中間絶縁膜12、第3上部電極13の積層体からなる。

【0115】

実施例1によれば、第1配線3を抵抗変化素子22の下部電極とすることで、すなわち、第1配線3が抵抗変化素子22の下部電極を兼ねることで、工程数を簡略化しながら、電極抵抗を下げるこができる。

【0116】

例えば、通常のCu(銅)ダマシン配線プロセスへの追加工程として、少なくとも3枚のマスクセットを作成するだけで、抵抗変化素子を搭載することができる。このため、抵抗変化素子の低抵抗化と低コスト化を同時に達成することができる。

【0117】

抵抗変化素子22は、抵抗変化型不揮発素子であり、例えば、固体電解質層中における金属イオン移動と電気化学反応とを利用したスイッチング素子とすることができる。

【0118】

抵抗変化素子22は、下部電極となる第1配線3と、プラグ19と電気的に接続された上部電極11、13とを有する構成となっている。

【0119】

抵抗変化素子22は、絶縁性バリア膜7に形成された開口部の領域にて、抵抗変化膜9と第1配線3とが直接接している。また第3上部電極13上にて、プラグ19と第3上部電極13とがバリアメタル20を介して電気的に接続されている。

【0120】

抵抗変化素子22は、電圧の印加、あるいは電流を流すことで、ON/OFFの制御が行われる。例えば、抵抗変化膜9中への第1配線3に係る金属の電界拡散を利用してON/OFFの制御を行う。

【0121】

第3上部電極13及びバリアメタル20は、同一の材料で構成されている。このようにすることで、プラグ19のバリアメタル20と抵抗変化素子22の第3上部電極13とが一体化し、接触抵抗を低減し、かつ、密着性の向上による信頼性の向上を実現することができる。

【0122】

半導体基板は、半導体素子が形成された基板である。半導体基板には、例えば、

・シリコン基板、

・単結晶基板、

・SOI(Silicon on Insulator)基板、

・TFT(Thin Film Transistor)基板、

・液晶製造用基板等の基板を用いることができる。

【0123】

図10の層間絶縁膜4は、半導体基板上に形成された絶縁膜である。層間絶縁膜4には、例えば、シリコン酸化膜、シリコン酸化膜よりも比誘電率の低い低誘電率膜(例えば、SiOCH膜)等を用いることができる。層間絶縁膜4は、複数の絶縁膜を積層したものであってもよい。層間絶縁膜4には、第1配線3を埋め込むための配線溝が形成されており、当該配線溝にバリアメタル6を介して銅5が埋め込まれている。

【0124】

絶縁性バリア膜7は、層間絶縁膜4、16間に介在したバリア性を有する絶縁膜である。絶縁性バリア膜7は、第1配線3用の配線溝の加工時にエッチングストップ層としての役割を有する。絶縁性バリア膜7は、第1配線3を含む層間絶縁膜4上に形成され、第1配線3に係る金属(例えば、Cu)の酸化を防いだり、層間絶縁膜4中への第1配線3に係る金属の拡散を防いだり、上部電極11、10、及び抵抗変化膜9の加工時にエッチングストップ層としての役割を有する。

【0125】

絶縁性バリア膜7には、例えば、SiC膜、SiCN膜、SiN膜、及び、それらの積層構造等を用いることができる。

【0126】

絶縁性バリア膜7は、第1配線3上にて開口部を有する。絶縁性バリア膜7の開口部においては、第1配線3(の銅5)と抵抗変化膜9が接している。この絶縁性バリア膜7の開口部は、第1配線3の領域内に形成されている。このようにすることで、凹凸の小さい第1配線3の表面上に抵抗変化素子22を形成することができる。絶縁性バリア膜7の開口部の壁面は第1配線3から離れるにしたがい広くなったテーパ面となっている。

【0127】

層間絶縁膜16は、絶縁性バリア膜7上に形成された絶縁膜である。層間絶縁膜16には、例えば、シリコン酸化膜、シリコン酸化膜よりも比誘電率の低い低誘電率膜(例えば、SiOCH膜)等を用いることができる。層間絶縁膜16は、複数の絶縁膜を積層したものであってもよい。

【0128】

第1配線3は、層間絶縁膜4に形成された配線溝にバリアメタル6を介して埋め込まれた配線である。第1配線3は、抵抗変化素子22の下部電極を兼ね、抵抗変化膜9と直接接している。なお、第1配線3と抵抗変化膜9の間には、電極層等が挿入されていてもよい。電極層が形成される場合は、電極層と抵抗変化膜9は連続工程にて堆積され、連続工程にて加工される。

【0129】

バリアメタル6は、第1配線3に係る金属が層間絶縁膜4や下層へ拡散することを防止するために、配線の側面乃至底面を被覆する、バリア性を有する導電性膜である。

【0130】

バリアメタル6には、例えば、第1配線3がCuを主成分とする金属元素からなる場合には、タンタル(Ta)、窒化タンタル(TaN)、窒化チタン(TiN)、炭窒化タングステン(WCN)のような高融点金属やその窒化物等、またはそれらの積層膜を用いることができる。

【0131】

抵抗変化膜9は、抵抗が変化する膜である。抵抗変化膜9は、第1配線3(下部電極)に係る金属の作用(拡散、イオン伝動等)により抵抗が変化する材料を用いることができる。

【0132】

抵抗変化素子22の抵抗変化を金属イオンの析出によって行う場合には、イオン伝導可能な固体電解質膜が用いられる。例えば、Taを含む酸化物絶縁膜であって、Ta2O5、TaSiO等を用いることができる。

【0133】

また、抵抗変化膜9は、例えば、下からTa2O5、TaSiOの順に積層した積層構造とすることができる。あるいは、抵抗変化膜9は有機物を主成分とした膜とすることができる。

【0134】

このような積層構造とすることで、抵抗変化膜9を固体電解質層として用いた場合には、低抵抗時(ON時)に、イオン伝導層内部に形成される金属イオン(例えば、銅イオン)よる架橋を、有機物を主成分とする層で分断し、OFF時に金属イオンを容易に回収することができるようになる。この結果、スイッチング特性を向上させることができる。

【0135】

抵抗変化膜9は、第1配線3、絶縁性バリア膜7の開口部のテーパ面、乃至絶縁性バリア膜7上に形成されている。

【0136】

抵抗変化膜9は、第1配線3と抵抗変化膜9の接続部の外周部分が少なくとも絶縁性バリア膜7の開口部のテーパ面上に沿って配設されている。開口部下の第1の配線3は、第一の実施形態における第一の電極(図2の201)に相当する。

【0137】

第1上部電極10は、抵抗変化素子22の上部電極における下層側の電極であり、抵抗変化膜9と直接接している。第一の実施形態における第二の電極(図2の203)に相当する。

【0138】

第1上部電極10には、第1配線3に係る金属よりもイオン化しにくく、抵抗変化膜9において拡散、イオン電導しにくい金属が用いられ、酸化の自由エネルギーの絶対値が小さい金属材料とすることが好ましい。

【0139】

第1上部電極10には、例えば、Pt、Ru等を用いることができる。また、第1上部電極10には、Pt、Ru等の金属材料を主成分として酸素を添加してもよく、また酸素を添加した層との積層構造にしてもよい。

【0140】

第2上部電極11は、抵抗変化素子22の上部電極における上層側の電極であり、第1上部電極10上に形成されている。

【0141】

第2上部電極11は、第1上部電極10を保護する役割を有する。すなわち、第2上部電極11が第1上部電極10を保護することで、プロセス中の第1上部電極10へのダメージを抑制し、抵抗変化素子22のスイッチング特性を維持することができる。

【0142】

第2上部電極11には、例えば、Ta、Ti、W、Alあるいはそれらの窒化物等を用いることができる。

【0143】

中間絶縁膜12は、第2上部電極11と第3上部電極13とを絶縁分離する膜である。中間絶縁膜12は、例えば、ハフニア膜、アルミナ膜、ジルコニア膜、イットリア膜、シリコン窒素膜、シリコン炭化窒素膜、シリコン酸化膜から選択することができ、抵抗変化膜9よりも比誘電率が大きく、膜厚が薄いことが好ましい。スパッタリング法やALD(Atomic layer deposition)法等を用いて形成することができ、成長温度は350℃以下であることが好ましい。

【0144】

第3上部電極13はプラグ19を形成する際のホール形成時にエッチンストッパーとしての役割を果たす。第3上部電極13は、抵抗変化素子22にダメージを与えることなく、さらに抵抗変化膜9からの酸素の脱離を防ぐ機能を有する。

【0145】

第3上部電極13は、バリアメタル20を介したプラグ(コンタクトプラグ)19との接触抵抗を低減するために、バリアメタル20と同じ材料であることが好ましく、Ta、あるいはその窒化物であることが好ましい。第3上部電極は第一の実施形態における制御電極(図2の205)に相当する。

【0146】

層間絶縁膜16には、例えば、シリコン酸化膜、SiOC膜、シリコン酸化膜よりも比誘電率の低い低誘電率膜(例えば、SiOCH膜)等を用いることができる。層間絶縁膜16は、複数の絶縁膜を積層したものであってもよい。

【0147】

層間絶縁膜16には、プラグ19を埋め込むための下穴が形成されており、当該下穴にバリアメタル20を介してプラグ19が埋め込まれている。

【0148】

バリアメタル20は、第2配線17(プラグ19を含む)に係る金属が層間絶縁膜16や下層へ拡散することを防止するために、第2配線17及びプラグ19の側面乃至底面を被覆する、バリア性を有する導電性膜である。

【0149】

バリアメタル20には、例えば、タンタル(Ta)、窒化タンタル(TaN)、窒化チタン(TiN)、炭窒化タングステン(WCN)のような高融点金属やその窒化物等、またはそれらの積層膜を用いることができる。

【0150】

絶縁性バリア膜(バリア絶縁膜)21は、第2配線17を含む層間絶縁膜16上に形成され、第2配線17に係る金属(例えば、Cu)の酸化を防ぐ役割や、上層への第2配線17に係る金属の拡散を防ぐ役割を有する絶縁膜である。絶縁性バリア膜21には、例えば、SiC膜、SiCN膜、SiN膜、及びそれらの積層構造等を用いることができる。

【0151】

<実施例2>

次に、実施例2として、半導体装置の製造方法について図面を用いて説明する。実施例2の製造方法は、第1乃至第四の実施形態、実施例1に示した半導体装置を形成するため方法の一例である。図11乃至図15は、本発明の実施例1に係る半導体装置の製造方法を工程順に模式的に示した工程断面図である。なお、図11乃至図15は、単に図面作成の都合で分図されている。

【0152】

まず、半導体基板(例えば、半導体素子が形成された基板)上に層間絶縁膜2(例えば、シリコン酸化膜、膜厚300nm(nano-meter))を堆積し、その後、リソグラフィ法(フォトレジスト形成、ドライエッチング、フォトレジスト除去を含む)を用いて、層間絶縁膜4に配線溝を形成し、その後、当該配線溝にバリアメタル6(例えば、TaN/Ta、膜厚5nm/5nm)を介して第1配線(図10の3)の銅5を埋め込む(ステップA1;図11(A)参照)。

【0153】

ステップA1において、層間絶縁膜2は、プラズマCVD法によって形成することができる。ここで、プラズマCVD(Chemical Vapor Deposition)法とは、例えば、気体原料、あるいは液体原料を気化させることで減圧下の反応室に連続的に供給し、プラズマエネルギーによって、分子を励起状態にし、気相反応、あるいは基板表面反応等によって基板上に連続膜を形成する手法である。

【0154】

また、ステップA1において、第1配線(5、6:図10の3に対応)は、例えば、PVD(Physical Vapor Deposition)法によってバリアメタル6(例えば、TaN/Taの積層膜)を形成し、PVD法によるCuシードの形成後、電解めっき法によって銅5を配線溝内に埋設し、200℃以上の温度で熱処理後、CMP(Chemical Mechanical Polishing)法によって配線溝内以外の余剰の銅を除去することで形成することができる。

【0155】

このような一連の銅配線の形成方法は、当該技術分野における一般的な手法を用いることができる。ここで、CMP法とは、多層配線形成プロセス中に生じるウェハ表面の凹凸を、研磨液をウェハ表面に流しながら回転させた研磨パッドに接触させて研磨することによって平坦化する方法である。溝に埋め込まれた余剰の銅を研磨することによって埋め込み配線(ダマシン配線)を形成したり、層間絶縁膜を研磨することで平坦化を行う。

【0156】

次に、第1配線(5、6)を含む層間絶縁膜4上に絶縁性バリア膜7(例えば、SiCN膜、膜厚30nm)を形成する(ステップA2;図11(B)参照)。ここで、絶縁性バリア膜7は、プラズマCVD法によって形成することができる。絶縁性バリア膜7の膜厚は、10nm〜50nm程度であることが好ましい。

【0157】

次に、絶縁性バリア膜7上にハードマスク膜8(例えば、シリコン酸化膜)を形成する(ステップA3;図11(C)参照)。

【0158】

このとき、ハードマスク膜8は、ドライエッチング加工におけるエッチング選択比を大きく保つ観点から、絶縁性バリア膜7とは異なる材料であることが好ましく、絶縁膜であっても導電膜であってもよい。ハードマスク膜8には、例えば、シリコン酸化膜、シリコン窒化膜、TiN、Ti、Ta、TaN等を用いることができ、SiN/SiO2の積層体を用いることができる。

【0159】

次に、ハードマスク膜8上にフォトレジスト(図示せず)を用いて開口部をパターニングし、フォトレジストをマスクとしてドライエッチングすることによりハードマスク膜8に開口部パターンを形成し、その後、酸素プラズマアッシング等によってフォトレジストを剥離する(ステップA4;図12(A)参照)。このとき、ドライエッチングは必ずしも絶縁性バリア膜7の上面で停止している必要はなく、絶縁性バリア膜7の内部にまで到達していてもよい。

【0160】

次に、ハードマスク膜8(図12(A)の8)をマスクとして、ハードマスク膜8の開口部から露出する絶縁性バリア膜7をエッチバック(ドライエッチング)することにより、絶縁性バリア膜7に開口部を形成して、絶縁性バリア膜7の開口部から第1配線3を露出させる。このとき、開口部は層間絶縁膜内部にまで達していても良い。その後、アミン系の剥離液等で有機剥離処理を行うことで、第1配線(5,6)の露出面に形成された酸化銅を除去するとともに、エッチバック時に発生したエッチング複生成物等を除去する(ステップA5;図12(B)参照)。

【0161】

ステップA5において、ハードマスク膜(図12(A)の8)は、エッチバック中に完全に除去されることが好ましいが、絶縁材料である場合にはそのまま残存してもよい。また、絶縁性バリア膜7の開口部の形状は、円形、正方形、四角形とし、円の直径、あるいは四角形の一辺の長さは20nmから500nmとすることができる。

【0162】

また、ステップA5において、絶縁性バリア膜7をエッチバックでは、反応性ドライエッチングを用いることで、絶縁性バリア膜7の開口部の壁面をテーパ面とすることができる。反応性ドライエッチングでは、エッチングガスとしてフルオロカーボンを含むガスを用いることができる。

【0163】

次に、ステップA6において、第1配線(5,6)を含む絶縁性バリア膜7上に抵抗変化膜9(例えば、SiC3O1、TaSiO、Ta2O5、ZrO、HfO等、膜厚は4〜10nm)を堆積する(ステップA7;図12(C)参照)。ここで、抵抗変化膜9は、PVD法やCVD法を用いて形成することができる。

【0164】

ステップA7では、絶縁性バリア膜7の開口部は、ステップA5の有機剥離処理によって水分等が付着しているため、抵抗変化膜9の堆積前に250℃〜350℃程度の温度にて、減圧下で熱処理を加えて脱ガスしておくことが好ましい。この際、銅表面を再度酸化させないよう、真空下、あるいは窒素雰囲気等にする等の注意が必要である。

【0165】

また、ステップA7では、抵抗変化膜9の堆積前に、絶縁性バリア膜7の開口部から露出する第1配線(5、6)に対して、H2ガスを用いた、ガスクリーニング、あるいはプラズマクリーニング処理を行ってもよい。このようにすることで、抵抗変化膜9を形成する際に、第1配線(5、6)の銅5)の酸化を抑制することができ、プロセス中の銅の熱拡散(物質移動)を抑制することができるようになる。

【0166】

さらに、ステップA7では、抵抗変化膜9の堆積前に、PVD法を用いて薄膜のTi(2nm以下)(図示せず)を堆積することで、第一配線5銅の酸化を抑制してもよい。薄膜のTi層は抵抗変化膜9の形成中に酸化されて、チタン酸化物となる。

【0167】

また、ステップA7では、抵抗変化膜9として、固体電解質層を用いたタイプではなく、遷移金属酸化物(例えば、TiO、NiO等)や、HfOx、ZrOx、TaOxを用いた抵抗変化膜を用いる場合には、抵抗変化膜9を堆積する前に、下部電極(図示せず)を成膜してもよい。

【0168】

下部電極には、例えば、Ti、TiN、W、WN、Ta、TaN、Ru、RuOx等を用いることができ、例えば、それらの積層構造(例えば、TaN(下層)/Ru(上層))であっても良い。この時、積層構造の合計膜厚は、抵抗変化素子9をビア層間絶縁膜内部に形成する都合上、素子段差と表面ラフネスを低減するため、絶縁性バリア膜7よりも薄いことが必要であり、好ましくは10nm以下であると良い。

【0169】

また、ステップA7では、抵抗変化膜9を段差のある開口部10にカバレッジよく埋め込む必要があるため、プラズマCVD法を用いて行うことが好ましい。

【0170】

次に、抵抗変化膜9上に第1上部電極10(例えば、Ru、膜厚10nm)及び第2上部電極11(例えば、Ta、膜厚10nm)、中間絶縁膜12(たとえはHfOx),第3上部電極13(例えばTa)をこの順に形成する(ステップA8)。

【0171】

次に、第3上部電極13上にハードマスク膜a(例えば、SiN膜、膜厚30nm)、及びハードマスク膜b(例えば、SiO2膜、膜厚200nm)をこの順に積層する(ステップA9、図示せず)。

【0172】

ステップA9において、ハードマスク膜a及びハードマスク膜bは、プラズマCVD法を用いて成膜することができる。ハードマスク膜a、bは当該技術分野における一般的なプラズマCVD法を用いて形成することができる。また、ハードマスク膜aとハードマスク膜bとは、異なる種類の膜であることが好ましく、例えば、ハードマスク膜aをSiN膜とし、ハードマスク膜bをSiO2膜とすることができる。

【0173】

次に、ステップA10において、ハードマスク膜上に、抵抗変化素子22をパターニングするためのフォトレジスト(図示せず)を形成し、その後、当該フォトレジストをマスクとして、ハードマスク膜aが表れるまでハードマスク膜bをドライエッチングし、その後、酸素プラズマアッシングと有機剥離を用いてフォトレジストを除去する。

【0174】

次に、ハードマスク膜をマスクとして、ハードマスク膜b、第3上部電極13、中間絶縁膜12、第二上部電極11、第1上部電極10、抵抗変化膜9を連続的にドライエッチングする(ステップA11、図13(A))。このとき、ハードマスク膜は、エッチバック中に完全に除去されることが好ましいが(図13(A))、そのまま残存してもよい。

【0175】

ステップA11において、例えば、第3上部電極11がTaの場合には、Cl2系のRIE(Reactive Ion Etching)で加工することができる。第1上部電極10がRuの場合には、Cl2/O2の混合ガスでRIE加工することができる。また、抵抗変化膜9のエッチングでは、下面の絶縁性バリア膜7上でドライエッチングを停止させる必要がある。

【0176】

抵抗変化膜9がTaを含む酸化物であり、絶縁性バリア膜7がSiN膜やSiCN膜である場合には、CF4系、CF4/Cl2系、CF4/Cl2/Ar/N2系等の混合ガスでエッチング条件を調節することでRIE加工することができる。

【0177】

このようなハードマスクRIE法を用いることで、抵抗変化素子部をレジスト除去のための酸素プラズマアッシングに曝すことなく、抵抗変化素子22を加工をすることができる。また、加工後に酸素プラズマによって酸化処理する場合には、レジストの剥離時間に依存することなく酸化プラズマ処理を照射することができるようになる。

【0178】

次に、抵抗変化素子22上に、層間絶縁膜16(例えばSiO2)(図13(B))、平坦化し(ステップA12;図14(A))、層間絶縁膜16−2、ハードマスク膜15をさらに堆積する(ステップA13;図14(B))。

【0179】

その後、第2配線17(図10参照)用の配線溝、及びプラグ19用の下穴を形成し、銅デュアルダマシン配線プロセスを用いて、当該配線溝及び当該下穴内に、バリアメタル20(例えば、TaN/Ta)を介して第2配線17(例えば、Cu)及びプラグ19(例えば、Cu)を同時に形成し、その後、第2配線17を含む層間絶縁膜16上に絶縁性バリア膜21(例えば、SiCN膜)を堆積する(ステップA14;図15参照)。なお、図15の断面図は、図5に対応している。図15の第1配線3a(バリアメタル6a、銅5a)は図5の第一電極201a、第1配線3b(バリアメタル6b、銅5b)は図5の第一電極201bに対応している。

【0180】

また、ステップA13、A14において、層間絶縁膜16及び16−2はプラズマCVD法で形成することができる。

【0181】

また、ステップA13において、抵抗変化素子22によって形成される段差を解消するため、層間絶縁膜16を厚く堆積し、CMPによって層間絶縁膜16を削り込んで平坦化し、層間絶縁膜16を所望の膜厚としてもよい(図14(A)参照。)。

【0182】

本実施例によれば、第1配線(5、6:図10の3)を抵抗変化素子22の下部電極とすることで、すなわち、第1配線(5、6)が抵抗変化素子22の下部電極を兼ねることで、抵抗変化素子22の小型化による高密度化を実現するとともに、相補型の抵抗変化素子を形成することができる。このため、信頼性を向上させることができる。

【0183】

通常のCuダマシン配線プロセスに追加工程として、2PR(Photo Regist)のマスクセットを作成するだけで、抵抗変化素子22を搭載することができ、装置の低コスト化を同時に達成することができるようになる。さらに、銅配線によって構成される最先端のデバイスの内部にも抵抗変化素子22を搭載して、装置の性能を向上させることができる。

【0184】

<実施形態6>

次に、本発明の第六の実施形態を説明する。図17は、第六の実施形態の抵抗変化素子のプログラミング回路について示す。プログラミング動作の説明に最低限必要な部分のみを残して抜き出したものである。プログラミング回路は状況に応じてさまざまに変形して利用し得る。

【0185】

図17において、1701及び1702は、抵抗変化素子の第一の電極を表し、それぞれに対して書き込み選択用のスイッチ1703及び1704が接続されており、制御電極1710、書き込み電圧源1709を有する。

【0186】

以下では、スイッチ1703を閉じて(クローズ、導通状態)、スイッチ1704を開放し(オープン、非導通状態)、端子1701側を、OFF状態からON状態に遷移させる場合を説明する。

【0187】

まず、第一のステップにおいて、スイッチ1705を閉じ、キャパシタ1708を充電する。

【0188】

次に第二のステップにおいて、スイッチ1705を開放し、スイッチ1706を閉じる。このとき、制御電極1710には電荷が蓄積されるが、その速度は、スイッチ1706の駆動能力に比例する。

【0189】

第三のステップにおいて、スイッチ1706を開放し、スイッチ1707を閉じる。すると、制御電極1710に蓄えられた電荷は、スイッチ1707を通じてGND(グランド)電位側に放電される。

【0190】

以上の第一のステップから第三のステップを繰り返すことで、所望の交流電流を抵抗変化素子に印加することができる。図17において、各スイッチ1703〜1706には、電界効果型トランジスタ(Field Effect Transistor:FET)を使用することができる。

【0191】

図18は、第六の実施形態において、抵抗変化素子をプログラミングするための、図17の制御電極1710の電圧波形と電流波形の典型例を示す波形図である。

【0192】

例えば、制御電極1710への電荷蓄積の時定数を電荷放出の時定数よりも短く設定することで、制御電極1710から端子1701の向きに流れる電流のピーク値を逆方向の電流のピーク値よりも大きくするとよい。こうするためには、スイッチ1706の駆動力(電流駆動能力)をスイッチ1707の駆動力よりも大とし、瞬間的により大きな電流が流せるようにすると良い。スイッチ1706及びスイッチ1707の駆動力は、スイッチ1706、1707を構成する電界効果トランジスタ(FET)のゲート幅(W)(ゲート幅を大とすると、FETの相互コンダクタンスが増大する)、もしくは、それぞれの電界効果トランジスタに印加されるゲート電圧(ゲート・ソース間電圧)によって調整することができる(例えばFETのゲート・ソース間電圧を大とするとドレイン・ソース間電流が増大する)。

【0193】

キャパシタ1708の容量は、一例として、制御電極の容量の10倍以上とすることが好ましく、例えば制御電極の容量が0.5fF(femto farad)であるときには、5fFのキャパシタンスを設定することが好ましい。

【0194】

端子1702側の抵抗変化素子は、スイッチ1703を開放して、スイッチ1704を閉じて、同様に第一のステップから第三のステップを繰り返すことによりプログラムすることができる。

【0195】

また、抵抗変化素子を、ON状態からOFF状態へ遷移させる際には、スイッチ1706と1707の駆動力の関係を逆になるように回路を構成するとよい。

【0196】

以上、幾つかの実施形態、実施例を説明したが、これら実施形態及び実施例は単に実例を挙げて発明を説明するためのものであって、限定することを意味するものではない。

【0197】

例えば、CMOS回路を有する半導体製造装置技術に関して詳しく説明し、半導体基板上の銅多層配線内部に抵抗変化素子を形勢する例について説明したが、本発明は上記に限定されるものではなく、例えば、

・DRAM(Dynamic Random Access Memory)、

・SRAM(Static Random Access Memory)、

・一括消去型の書き換え可能な不揮発性メモリであるフラッシュメモリ(あるいはEEPROM:Electrically Erasable and Programmable Read Only Memory)、

・FRAM(Ferro Electric Random Access Memory)、

・MRAM(Magnetic Random Access Memory)、

・抵抗変化型メモリ、

・バイポーラトランジスタ

等のようなメモリ回路を有する半導体製品、あるいは、

マイクロプロセッサ等の論理回路を有する半導体製品、あるいは、

これらを同時に掲載したボードやパッケージの銅配線上へも適用することができる。

【0198】

また、本発明は、半導体装置への電子回路装置、光回路装置、量子回路装置、マイクロマシン、MEMS(Micro Electro Mechanical Systems)等の接合にも適用することができる。

【0199】

また、本発明ではスイッチ機能での実施例を中心に説明したが、不揮発性と抵抗変化特性の双方を利用したメモリ素子に用いることもできる。

【0200】

本発明による基板の接合方法は、そのできあがりからも、確認することができる。具体的には、例えば、デバイスの断面をTEM(Transmission Electron Microscope;透過型電子顕微鏡)観察することで、多層配線に銅配線が用いられていることを確認し、抵抗変化素子が搭載されている場合には、当該抵抗変化素子が積層構造であることかた、該積層構造内部に中間絶縁膜を備えているかを観察することで確認することができ、本発明を実施した構造であるかを確認することができる。

【0201】

さらにTEMに加え、例えばEDX(Energy Dispersive X-ray Spectroscopy;エネルギー分散型X線分光法)や、EELS(Electron Energy-Loss Spectroscopy;電子エネルギー損失分光法)等の組成分析を行うことで、本発明を実施した構造であるか否かの確認を行うことができる。

【0202】

なお、上記の特許文献、非特許文献の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素(各請求項の各要素、各実施例の各要素、各図面の各要素等を含む)の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0203】

3、3a、3b 第1配線

4 層間絶縁膜

5、5a、5b 銅

6、6a、6b、20 バリアメタル

7 絶縁性バリア膜

8 ハードマスク膜

9 抵抗変化膜

10 第1上部電極

11 第2上部電極

12 中間絶縁膜

13 第3上部電極

15 ハードマスク膜

16、16−2 層間絶縁膜

17 第2配線

18 Cu(銅)

19 プラグ

20 バリアメタル

21 絶縁性バリア膜

22、701a、801a、801b、901 抵抗変化素子

101、401a、401b、701a、801a、801b 抵抗変化素子

102、103、402a、402b、702a、703a、802a、803a 端子

104、404 制御端子

201、501a、501b 第一の電極

202、502 抵抗変化層(抵抗変化膜)

203、503、 第二の電極

204、304、504、604 中間絶縁膜

205、305、505、605 制御電極

301、601a、601b 活性電極

302、602 固体電解質層(固体電解質)

303、603 不活性電極

306、606a、606b 金属架橋

405 トランジスタ

704a 制御端子

705a、705b、805a、805b 水平線

706a、706b、806a、806b 垂直線

707a、707b、707c、807a、807b、807c、906a〜906e 対角線

804a 制御端子

1701、1702 端子

1703〜1707 スイッチ

1708 キャパシタ(容量)

1709 書き込み電圧源

1710 制御電極

【特許請求の範囲】

【請求項1】

第一の電極と、抵抗変化層と、第二の電極と、中間絶縁膜と、制御電極と、をこの順に積層した積層構造を備え、前記抵抗変化層と前記中間絶縁膜が直接接していない、ことを特徴とする抵抗変化素子。

【請求項2】

前記中間絶縁膜の比誘電率が前記抵抗変化層の比誘電率よりも大きい、ことを特徴とする、請求項1に記載の抵抗変化素子。

【請求項3】

前記中間絶縁膜の厚さが前記抵抗変化層の厚さよりも薄い、ことを特徴とする、請求項1に記載の抵抗変化素子。

【請求項4】

前記第一の電極は金属イオンを供給する活性電極からなり、

前記抵抗変化層はイオン化した金属が伝導する固体電解質層からなり、

前記第二の電極は前記金属イオンと反応しない不活性電極からなる、ことを特徴とする、請求項1乃至3のいずれか1項に記載の抵抗変化素子。

【請求項5】

前記中間絶縁膜が、ハフニア膜、アルミナ膜、ジルコニア膜、イットリア膜、シリコン窒素膜、シリコン炭化窒素膜、シリコン酸化膜の少なくとも1を含む、ことを特徴とする請求項1乃至3のいずれか1項に記載の抵抗変化素子。

【請求項6】

前記制御電極は、Ta、Ti、TaN、TiN、W、Al、の少なくとも1つを含む、ことを特徴とする請求項1乃至4のいずれか1項に記載の抵抗変化素子。

【請求項7】

半導体素子基板上に形成された、少なくとも二つの、請求項1乃至6のいずれか1項に記載の抵抗変化素子を備え、

少なくとも二つの前記抵抗変化素子の、前記抵抗変化層同士、前記第二の電極同士、前記中間絶縁膜同士、及び制御電極同士が一体化している、ことを特徴とする抵抗変化素子。

【請求項8】

半導体素子基板上に形成された、少なくとも二つの前記抵抗変化素子の各々が、

金属イオンの供給源となる活性電極と、

イオン化した金属が伝導する固体電解質層と、

不活性電極と、

絶縁膜と、制御電極とがこの順に積層した、積層構造を備え、

少なくとも二つの前記抵抗変化素子の、固体電解質層同士、不活性電極同士、中間絶縁膜同士、及び制御電極同士が一体化している、ことを特徴とする請求項7に記載の抵抗変化素子。

【請求項9】

請求項1乃至8のいずれか1項に記載の前記抵抗変化素子に対して、

前記第一の電極と前記制御電極との間に規則的に交番する電圧を印加し、過渡的に流れる交流電流を両電極間に流すことによって、前記抵抗変化素子の抵抗値を遷移させることを特徴とする、抵抗変化素子のプログラミング方法。

【請求項10】

前記交番する電圧の時間微分値の絶対値又はそのピーク値が、前記電圧の上昇時と下降時で異なり、前記絶対値もしくはそのピーク値の大きさの違いによって前記抵抗変化素子の抵抗値を遷移させる請求項9記載の抵抗変化素子のプログラミング方法。

【請求項1】

第一の電極と、抵抗変化層と、第二の電極と、中間絶縁膜と、制御電極と、をこの順に積層した積層構造を備え、前記抵抗変化層と前記中間絶縁膜が直接接していない、ことを特徴とする抵抗変化素子。

【請求項2】

前記中間絶縁膜の比誘電率が前記抵抗変化層の比誘電率よりも大きい、ことを特徴とする、請求項1に記載の抵抗変化素子。

【請求項3】

前記中間絶縁膜の厚さが前記抵抗変化層の厚さよりも薄い、ことを特徴とする、請求項1に記載の抵抗変化素子。

【請求項4】

前記第一の電極は金属イオンを供給する活性電極からなり、

前記抵抗変化層はイオン化した金属が伝導する固体電解質層からなり、

前記第二の電極は前記金属イオンと反応しない不活性電極からなる、ことを特徴とする、請求項1乃至3のいずれか1項に記載の抵抗変化素子。

【請求項5】

前記中間絶縁膜が、ハフニア膜、アルミナ膜、ジルコニア膜、イットリア膜、シリコン窒素膜、シリコン炭化窒素膜、シリコン酸化膜の少なくとも1を含む、ことを特徴とする請求項1乃至3のいずれか1項に記載の抵抗変化素子。

【請求項6】

前記制御電極は、Ta、Ti、TaN、TiN、W、Al、の少なくとも1つを含む、ことを特徴とする請求項1乃至4のいずれか1項に記載の抵抗変化素子。

【請求項7】

半導体素子基板上に形成された、少なくとも二つの、請求項1乃至6のいずれか1項に記載の抵抗変化素子を備え、

少なくとも二つの前記抵抗変化素子の、前記抵抗変化層同士、前記第二の電極同士、前記中間絶縁膜同士、及び制御電極同士が一体化している、ことを特徴とする抵抗変化素子。

【請求項8】

半導体素子基板上に形成された、少なくとも二つの前記抵抗変化素子の各々が、

金属イオンの供給源となる活性電極と、

イオン化した金属が伝導する固体電解質層と、

不活性電極と、

絶縁膜と、制御電極とがこの順に積層した、積層構造を備え、

少なくとも二つの前記抵抗変化素子の、固体電解質層同士、不活性電極同士、中間絶縁膜同士、及び制御電極同士が一体化している、ことを特徴とする請求項7に記載の抵抗変化素子。

【請求項9】

請求項1乃至8のいずれか1項に記載の前記抵抗変化素子に対して、

前記第一の電極と前記制御電極との間に規則的に交番する電圧を印加し、過渡的に流れる交流電流を両電極間に流すことによって、前記抵抗変化素子の抵抗値を遷移させることを特徴とする、抵抗変化素子のプログラミング方法。

【請求項10】

前記交番する電圧の時間微分値の絶対値又はそのピーク値が、前記電圧の上昇時と下降時で異なり、前記絶対値もしくはそのピーク値の大きさの違いによって前記抵抗変化素子の抵抗値を遷移させる請求項9記載の抵抗変化素子のプログラミング方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−77681(P2013−77681A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−216256(P2011−216256)

【出願日】平成23年9月30日(2011.9.30)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.FRAM

【国等の委託研究の成果に係る記載事項】(出願人による申告)国等の委託研究の成果に係る特許出願(平成22年度経済産業省産業技術研究開発委託費「低炭素社会を実現する超低電圧デバイスプロジェクト)」委託研究、産業技術力強化法第19条の適用を受ける特許出願)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月30日(2011.9.30)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.FRAM

【国等の委託研究の成果に係る記載事項】(出願人による申告)国等の委託研究の成果に係る特許出願(平成22年度経済産業省産業技術研究開発委託費「低炭素社会を実現する超低電圧デバイスプロジェクト)」委託研究、産業技術力強化法第19条の適用を受ける特許出願)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

[ Back to top ]