接続孔を形成する工程を有する配線構造の形成方法

【目的】 接続孔を形成する工程を有する配線構造の形成について、段差のある下地上に形成した層間絶縁膜に深さの異なる接続孔を形成する場合も、オーバーエッチングの問題が生じず、よって特性の良好な配線構造が得られる技術を提供する。

【構成】 半導体装置製造における多層ポリSi配線プロセス等について、SiO2 等から成る段差を有する下地1上に形成した層間絶縁膜3に接続孔5a,5bを形成する際、段差底部1aに該当する層間絶縁膜3に深い接続孔5aを形成し、段差上部1bに該当する層間絶縁膜に浅い接続孔5bを形成することを同時に行う場合に、上記浅い接続孔5bの形成部位の底部にSiN等のエッチング速度の小さい材料層11bを予め形成しておく。

【構成】 半導体装置製造における多層ポリSi配線プロセス等について、SiO2 等から成る段差を有する下地1上に形成した層間絶縁膜3に接続孔5a,5bを形成する際、段差底部1aに該当する層間絶縁膜3に深い接続孔5aを形成し、段差上部1bに該当する層間絶縁膜に浅い接続孔5bを形成することを同時に行う場合に、上記浅い接続孔5bの形成部位の底部にSiN等のエッチング速度の小さい材料層11bを予め形成しておく。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は、接続孔を形成する工程を有する配線構造の形成方法に関する。本発明は、接続孔を備えた各種の配線構造について内用でき、例えば半導体装置における配線構造についてこれを形成する場合に利用することができる。

【0002】

【従来の技術】半導体装置の製造においては、平坦化した層間絶縁膜に接続孔を開孔する工程が行われることがあるが、この場合、層間絶縁膜に段差があると、段差上部(層間膜の膜厚がその部分は小さい)に形成される接続孔と、段差下部(層間膜の膜厚がその部分は大きい)に形成される接続孔とでは、深さが異なることになる。このような接続孔を同時にエッチングで形成すると、浅い接続孔には過剰にエッチングがかかることになって、不都合が生ずることがある。

【0003】例えば、この問題は、多層配線構造を備える半導体装置について見られる。即ち、最近のLSI等では、デバイス特性の向上や微細化への対応のため多層配線特に多層ポリSi配線等の多層配線プロセスが使われている。特にメモリーではセル内と周辺回路内で多層ポリSi配線の使い方が異なるため、それらで配線の下部(例えばAl配線の下地)の高さが異なってくる。このため、例えば図9に示すように下地1の高さが異なって段差となっているところにAl配線2a,2bを形成し、平坦化層間膜3により層間平坦化を行うと、図示のように層間膜3の厚さが異なってしまう。即ち、下地1の段差底部1a上における配線2a上の層間膜3の膜厚3aは厚く、下地1の段差上部1b上における配線2b上の層間膜3の膜厚3bは薄い。つまり3a>3bとなる。このままフォトリソグラフィー技術を用いてコンタクトホールパターン4を形成し、コンタクトホール5a,5bを開孔すると、次の問題が生ずる。図9はコンタクト開孔のためのエッチングの途中を示し、浅いコンタクトホール5bが開孔された状態を示す。このとき深いコンタクトホール5aは形成途中にある。更にエッチングを進めて、図10のようにホール5a,5bを開孔すると、浅いコンタクトホール5bに過剰にオーバーエッチングがかかるようになる。この結果例えば配線2bとエッチングガスの反応により浅いコンタクトで反応生成物が生じる。例えば図示従来例の場合、Ti/AlCu/Ti配線2a,2b上にTiN膜6a,6bが形成されているが、浅いコンタクトホール5bにおいてTiN膜6b上にTiのフッ化物50が生じたりする。これによりコンタクト抵抗の増大が生じるという問題があった。なお、従来技術では、図10のホール開孔後、コンタクトホール5a,5bを埋め込み材7a,7bとして例えばWで埋め込み(図11)、更にその上に第2配線である上層配線8a,8b(ここではTi/AlCu/Ti配線)及びその上にTiN膜4a,4bを形成して、図12のような多層配線構造とする。図中符号10はポリSi配線である。

【0004】

【発明の目的】本発明は上記従来技術の問題点を解決して、接続孔を形成する工程を有する配線構造の形成について、段差のある下地上に形成した層間絶縁膜に深さの異なる接続孔を形成する場合も、オーバーエッチングの問題が生じず、よって特性の良好な配線構造が得られる技術を提供することを目的とする。

【0005】

【目的を達成するための手段】本発明は、段差を有する下地上に形成した層間絶縁膜に接続孔を形成する工程を有する配線構造の形成方法において、段差底部に該当する層間絶縁膜に深い接続孔を形成し、段差上部に該当する層間絶縁膜に浅い接続孔を形成することを同時に行う場合に、上記浅い接続孔形成部位の底部にエッチング速度の小さい材料層を予め形成しておくことを特徴とする接続孔を形成する工程を有する配線構造の形成方法であって、これにより上記目的を達成するものである。

【0006】この場合、段差を有する絶縁膜上に導電膜を形成する工程と、エッチング速度の小さい材料層を形成する工程と、上記深い接続孔形成部位しておける該エッチング速度の小さい材料層を除去する工程と、上記導電膜をパターニングする工程と、層間絶縁膜を形成して層間平坦化を行う工程と、接続孔をエッチングにより形成する工程とを備えることができる。

【0007】また本発明において、上記接続孔の形成後、第2の導電膜を形成する工程と、該第2の導電膜をパターニングする工程を行うこができる。

【0008】

【作用】本発明によれば、段差を有する下地の層間絶縁膜について、段差底部に該当する層間絶縁膜に深い接続孔を形成し、段差上部に該当する層間絶縁膜に浅い接続孔を形成することを同時に行う場合に、浅い接続孔形成部位の底部にエッチング速度の小さい材料層を予め形成しておくので、深い接続孔がエッチングされる間、浅い接続孔の形成部位の底部にあるこのエッチング速度の小さい材料層がエッチングされ、結果的に同時に接続孔の開孔が行われて、浅い接続孔の形成部位においてもオーバーエッチングが生じない。

【0009】

【実施例】以下本発明の実施例について、詳述する。但し当然のことではあるが、本発明は以下の実施例により限定を受けるものではない。

【0010】実施例1この実施例は、本発明を、微細化した半導体装置製造における多層ポリSi配線プロセスについて具体化したものである。図1ないし図8を参照する。

【0011】本実施例では、段差を有する下地1(ここではSiO2 )上に形成した層間絶縁膜3に接続孔5a,5bを形成する工程(図5及び図6)を有する配線構造の形成方法において、段差底部1aに該当する層間絶縁膜3に深い接続孔5aを形成し、段差上部1bに該当する層間絶縁膜に浅い接続孔5bを形成することを同時に行う場合に、上記浅い接続孔5bの形成部位の底部にエッチング速度の小さい材料層11bを予め形成しておく(図3ないし図5、特に図5参照)構成とする。

【0012】本実施例の場合、下地1として段差を有する絶縁膜(SiO2 膜)上に導電膜(配線2a,2b形成用の導電膜2)を形成する工程と、エッチング速度の小さい材料層11(ここではSiN層)を形成する工程と(図1)、上記深い接続孔形成部位における該エッチング速度の小さい材料層11を除去する工程(図2)と、上記導電膜をパターニングする工程(図3)と、層間絶縁膜3を形成して層間平坦化を行う工程(図4)と、接続孔5a,5bをエッチングにより形成する工程(図5及び図6)を備えた構成とする。

【0013】また本実施例では、上記接続孔5a,5bの形成後、第2の導電膜を形成する工程と、該第2の導電膜をパターニングする工程を行う(図8)。この第2の導電膜により、図8に示す第2配線8a,8b(上層配線)を形成する。

【0014】特に本実施例では、段差を有し、平坦でない絶縁層(下地1)上にAlを主成分とする導電膜2を全面に形成する工程と、TiN、TiONなどのリソグラフィーの反射防止膜6(ここではTiN)を形成する工程と、エッチング速度の小さい材料11としてSiN(シリコンナイトライド)を全面に形成して図1のようにする工程と、リソグラフィーを用いて深い部分の該材料11(SiN)を除去して図2のようにする工程と、リソグラフィーを用いて導電膜2をパターニングして図3のように配線2a,2bを形成する工程と、SiO2 を主成分とする絶縁層を用いて層間平坦化を行って図4の構造を得る工程と、リソグラフィー技術を用いて接続孔5a,5b(コンタクトホール)を開孔する工程(図5、図6)と、Alを主成分とする第2の導電膜を全面に形成する工程とリソグラフィーを用いて第2の導電膜をパターニングする工程(図8)を含んで、多層配線構造を形成する。

【0015】更に詳しくは、本実施例では以下の工程により、多層ポリSi配線を形成する。

【0016】500nm程度の段差のある下地1である絶縁膜(ここではSiO2 )上にスパッタ法により下層から順にTi/AlCu/Ti/TiN(100/500/5/20nm)を連続で成膜して、積層膜を形成する(図1参照)。図1中、符号2でTi/AlCu/Tiから成る導電層を示し、符号6で反射防止膜とするTiNを示す。続いて、P−CVD法により、SiNを100nm形成する。このSiNは、エッチング速度の小さい材料層11をなすものである。以上により図1の構造とした。なお、バリア層を介さず、Al系材料上に直接SiN膜を形成するように構成することも可能である。

【0017】その後、低い部分即ち段差底部1a上のエッチング速度の小さい材料層11(SiN)をリソグラフィー技術を用いて除去する(図2)。符号40で、このときのマスクとしたレジストを示す。

【0018】さらに、リソグラフィー技術を用いて導電膜2をパターニングし、配線パターンを形成する(図3)。このときのマスクとしたレジストを符号4a,4bで示す。

【0019】続いて、層間絶縁膜31として、P−TEOSをP−CVD法により100nm形成した後、更に層間絶縁膜32としてO3 TEOSを1000nm形成し、全面エッチバックにより平坦化を行う。さらに層間絶縁膜33としてP−TEOSをP−CVD法により400nm形成することで、層間絶縁膜3が形成される(図3)。層間絶縁膜3の厚さは、例えば、深い部分で1000nmとすると、浅い部分で500nm程度になる。

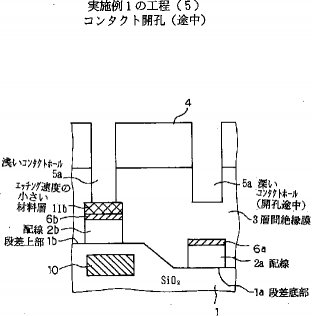

【0020】コンタクトパターン4をリソグラフィー技術により形成した後、異方性エッチングによりコンタクトを開孔し、接続孔5a,5bを形成する(図5、図6参照)。図5以降においては、3層のTEOSにより形成されたSiO2 膜は一体の層間絶縁膜3として図示する。

【0021】コンタクト開孔のためのエッチングは、C4 F8 /CO系ガスを使うことによって、エッチング速度の小さい材料層11であるSiNのエッチングレートが1/5以下になるように落とすことができる。このため浅いコンタクトホール5bでも深いコンタクトホール5aでも、エッチング時間はほぼ等しくなる。

【0022】この結果浅いコンタクトホール5bの底部に長時間のオーバーエッチングがかからないので、エッチングガスと配線との反応生成物の発生を低く抑えることができる。コンタクト開孔後、埋め込み導電材7a,7bとしてブランケット(Blk)−W埋め込みにより、コンタクトホール5a,5bを埋め込む(図7)。

【0023】更に、上層の導電層としてTi/AlCu/Ti/TiN(20/500/5/200nm)を全面に形成した後、リソグラフィーによりパターン化することで、上層配線(第2配線)8a,8bが形成される(図8)。なお図8中、9a,9bはこのときの反射防止膜とするTiN層である。

【0024】この実施例によれば、本発明を採用するこにより、深さの異なる接続孔5a,5b(コンタクトホール)において、深さの浅いコンタクトホール5bに過剰のオーバーエッチングがかからないので、エッチングガスと配線との反応生成物の発生を抑えることができ、コンタクト特性が改善される。

【0025】

【発明の効果】本発明の接続孔を形成する工程を有する配線構造の形成方法によれば、段差のある下地上に形成した層間絶縁膜に深さの異なる接続孔を形成する場合も、オーバーエッチングの問題が生じず、よって特性の良好な配線構造が得られるという効果がもたらされる。

【図面の簡単な説明】

【図1】 実施例1の工程を順に断面図で示すものである(1)。

【図2】 実施例1の工程を順に断面図で示すものである(2)。

【図3】 実施例1の工程を順に断面図で示すものである(3)。

【図4】 実施例1の工程を順に断面図で示すものである(4)。

【図5】 実施例1の工程を順に断面図で示すものである(5)。

【図6】 実施例1の工程を順に断面図で示すものである(6)。

【図7】 実施例1の工程を順に断面図で示すものである(7)。

【図8】 実施例1の工程を順に断面図で示すものである(8)。

【図9】 従来技術の工程を順に断面図で示すものである(1)。

【図10】 従来技術の工程を順に断面図で示すものである(2)。

【図11】 従来技術の工程を順に断面図で示すものである(3)。

【図12】 従来技術の工程を順に断面図で示すものである(4)。

【符号の説明】

1 下地(絶縁膜)

10 ポリSi層

2 導電層(Ti/AlCu/Ti)

2a,2b配線(下層の第1配線)

3 層間絶縁膜

31 P−TEOS

32 O3 TEOS

33 P−TEOS

4,4a,4b,40レジスト

5a 深い接続孔(深いコンタクトホール)

5b 浅い接続孔(浅いコンタクトホール)

6 反射防止膜(TiN層)

7a,7b埋め込み導電材料(Blk−W)

8a,8b第2(上層)配線

11,11a,11bエッチング速度の小さい材料層(SiN層)

【0001】

【産業上の利用分野】本発明は、接続孔を形成する工程を有する配線構造の形成方法に関する。本発明は、接続孔を備えた各種の配線構造について内用でき、例えば半導体装置における配線構造についてこれを形成する場合に利用することができる。

【0002】

【従来の技術】半導体装置の製造においては、平坦化した層間絶縁膜に接続孔を開孔する工程が行われることがあるが、この場合、層間絶縁膜に段差があると、段差上部(層間膜の膜厚がその部分は小さい)に形成される接続孔と、段差下部(層間膜の膜厚がその部分は大きい)に形成される接続孔とでは、深さが異なることになる。このような接続孔を同時にエッチングで形成すると、浅い接続孔には過剰にエッチングがかかることになって、不都合が生ずることがある。

【0003】例えば、この問題は、多層配線構造を備える半導体装置について見られる。即ち、最近のLSI等では、デバイス特性の向上や微細化への対応のため多層配線特に多層ポリSi配線等の多層配線プロセスが使われている。特にメモリーではセル内と周辺回路内で多層ポリSi配線の使い方が異なるため、それらで配線の下部(例えばAl配線の下地)の高さが異なってくる。このため、例えば図9に示すように下地1の高さが異なって段差となっているところにAl配線2a,2bを形成し、平坦化層間膜3により層間平坦化を行うと、図示のように層間膜3の厚さが異なってしまう。即ち、下地1の段差底部1a上における配線2a上の層間膜3の膜厚3aは厚く、下地1の段差上部1b上における配線2b上の層間膜3の膜厚3bは薄い。つまり3a>3bとなる。このままフォトリソグラフィー技術を用いてコンタクトホールパターン4を形成し、コンタクトホール5a,5bを開孔すると、次の問題が生ずる。図9はコンタクト開孔のためのエッチングの途中を示し、浅いコンタクトホール5bが開孔された状態を示す。このとき深いコンタクトホール5aは形成途中にある。更にエッチングを進めて、図10のようにホール5a,5bを開孔すると、浅いコンタクトホール5bに過剰にオーバーエッチングがかかるようになる。この結果例えば配線2bとエッチングガスの反応により浅いコンタクトで反応生成物が生じる。例えば図示従来例の場合、Ti/AlCu/Ti配線2a,2b上にTiN膜6a,6bが形成されているが、浅いコンタクトホール5bにおいてTiN膜6b上にTiのフッ化物50が生じたりする。これによりコンタクト抵抗の増大が生じるという問題があった。なお、従来技術では、図10のホール開孔後、コンタクトホール5a,5bを埋め込み材7a,7bとして例えばWで埋め込み(図11)、更にその上に第2配線である上層配線8a,8b(ここではTi/AlCu/Ti配線)及びその上にTiN膜4a,4bを形成して、図12のような多層配線構造とする。図中符号10はポリSi配線である。

【0004】

【発明の目的】本発明は上記従来技術の問題点を解決して、接続孔を形成する工程を有する配線構造の形成について、段差のある下地上に形成した層間絶縁膜に深さの異なる接続孔を形成する場合も、オーバーエッチングの問題が生じず、よって特性の良好な配線構造が得られる技術を提供することを目的とする。

【0005】

【目的を達成するための手段】本発明は、段差を有する下地上に形成した層間絶縁膜に接続孔を形成する工程を有する配線構造の形成方法において、段差底部に該当する層間絶縁膜に深い接続孔を形成し、段差上部に該当する層間絶縁膜に浅い接続孔を形成することを同時に行う場合に、上記浅い接続孔形成部位の底部にエッチング速度の小さい材料層を予め形成しておくことを特徴とする接続孔を形成する工程を有する配線構造の形成方法であって、これにより上記目的を達成するものである。

【0006】この場合、段差を有する絶縁膜上に導電膜を形成する工程と、エッチング速度の小さい材料層を形成する工程と、上記深い接続孔形成部位しておける該エッチング速度の小さい材料層を除去する工程と、上記導電膜をパターニングする工程と、層間絶縁膜を形成して層間平坦化を行う工程と、接続孔をエッチングにより形成する工程とを備えることができる。

【0007】また本発明において、上記接続孔の形成後、第2の導電膜を形成する工程と、該第2の導電膜をパターニングする工程を行うこができる。

【0008】

【作用】本発明によれば、段差を有する下地の層間絶縁膜について、段差底部に該当する層間絶縁膜に深い接続孔を形成し、段差上部に該当する層間絶縁膜に浅い接続孔を形成することを同時に行う場合に、浅い接続孔形成部位の底部にエッチング速度の小さい材料層を予め形成しておくので、深い接続孔がエッチングされる間、浅い接続孔の形成部位の底部にあるこのエッチング速度の小さい材料層がエッチングされ、結果的に同時に接続孔の開孔が行われて、浅い接続孔の形成部位においてもオーバーエッチングが生じない。

【0009】

【実施例】以下本発明の実施例について、詳述する。但し当然のことではあるが、本発明は以下の実施例により限定を受けるものではない。

【0010】実施例1この実施例は、本発明を、微細化した半導体装置製造における多層ポリSi配線プロセスについて具体化したものである。図1ないし図8を参照する。

【0011】本実施例では、段差を有する下地1(ここではSiO2 )上に形成した層間絶縁膜3に接続孔5a,5bを形成する工程(図5及び図6)を有する配線構造の形成方法において、段差底部1aに該当する層間絶縁膜3に深い接続孔5aを形成し、段差上部1bに該当する層間絶縁膜に浅い接続孔5bを形成することを同時に行う場合に、上記浅い接続孔5bの形成部位の底部にエッチング速度の小さい材料層11bを予め形成しておく(図3ないし図5、特に図5参照)構成とする。

【0012】本実施例の場合、下地1として段差を有する絶縁膜(SiO2 膜)上に導電膜(配線2a,2b形成用の導電膜2)を形成する工程と、エッチング速度の小さい材料層11(ここではSiN層)を形成する工程と(図1)、上記深い接続孔形成部位における該エッチング速度の小さい材料層11を除去する工程(図2)と、上記導電膜をパターニングする工程(図3)と、層間絶縁膜3を形成して層間平坦化を行う工程(図4)と、接続孔5a,5bをエッチングにより形成する工程(図5及び図6)を備えた構成とする。

【0013】また本実施例では、上記接続孔5a,5bの形成後、第2の導電膜を形成する工程と、該第2の導電膜をパターニングする工程を行う(図8)。この第2の導電膜により、図8に示す第2配線8a,8b(上層配線)を形成する。

【0014】特に本実施例では、段差を有し、平坦でない絶縁層(下地1)上にAlを主成分とする導電膜2を全面に形成する工程と、TiN、TiONなどのリソグラフィーの反射防止膜6(ここではTiN)を形成する工程と、エッチング速度の小さい材料11としてSiN(シリコンナイトライド)を全面に形成して図1のようにする工程と、リソグラフィーを用いて深い部分の該材料11(SiN)を除去して図2のようにする工程と、リソグラフィーを用いて導電膜2をパターニングして図3のように配線2a,2bを形成する工程と、SiO2 を主成分とする絶縁層を用いて層間平坦化を行って図4の構造を得る工程と、リソグラフィー技術を用いて接続孔5a,5b(コンタクトホール)を開孔する工程(図5、図6)と、Alを主成分とする第2の導電膜を全面に形成する工程とリソグラフィーを用いて第2の導電膜をパターニングする工程(図8)を含んで、多層配線構造を形成する。

【0015】更に詳しくは、本実施例では以下の工程により、多層ポリSi配線を形成する。

【0016】500nm程度の段差のある下地1である絶縁膜(ここではSiO2 )上にスパッタ法により下層から順にTi/AlCu/Ti/TiN(100/500/5/20nm)を連続で成膜して、積層膜を形成する(図1参照)。図1中、符号2でTi/AlCu/Tiから成る導電層を示し、符号6で反射防止膜とするTiNを示す。続いて、P−CVD法により、SiNを100nm形成する。このSiNは、エッチング速度の小さい材料層11をなすものである。以上により図1の構造とした。なお、バリア層を介さず、Al系材料上に直接SiN膜を形成するように構成することも可能である。

【0017】その後、低い部分即ち段差底部1a上のエッチング速度の小さい材料層11(SiN)をリソグラフィー技術を用いて除去する(図2)。符号40で、このときのマスクとしたレジストを示す。

【0018】さらに、リソグラフィー技術を用いて導電膜2をパターニングし、配線パターンを形成する(図3)。このときのマスクとしたレジストを符号4a,4bで示す。

【0019】続いて、層間絶縁膜31として、P−TEOSをP−CVD法により100nm形成した後、更に層間絶縁膜32としてO3 TEOSを1000nm形成し、全面エッチバックにより平坦化を行う。さらに層間絶縁膜33としてP−TEOSをP−CVD法により400nm形成することで、層間絶縁膜3が形成される(図3)。層間絶縁膜3の厚さは、例えば、深い部分で1000nmとすると、浅い部分で500nm程度になる。

【0020】コンタクトパターン4をリソグラフィー技術により形成した後、異方性エッチングによりコンタクトを開孔し、接続孔5a,5bを形成する(図5、図6参照)。図5以降においては、3層のTEOSにより形成されたSiO2 膜は一体の層間絶縁膜3として図示する。

【0021】コンタクト開孔のためのエッチングは、C4 F8 /CO系ガスを使うことによって、エッチング速度の小さい材料層11であるSiNのエッチングレートが1/5以下になるように落とすことができる。このため浅いコンタクトホール5bでも深いコンタクトホール5aでも、エッチング時間はほぼ等しくなる。

【0022】この結果浅いコンタクトホール5bの底部に長時間のオーバーエッチングがかからないので、エッチングガスと配線との反応生成物の発生を低く抑えることができる。コンタクト開孔後、埋め込み導電材7a,7bとしてブランケット(Blk)−W埋め込みにより、コンタクトホール5a,5bを埋め込む(図7)。

【0023】更に、上層の導電層としてTi/AlCu/Ti/TiN(20/500/5/200nm)を全面に形成した後、リソグラフィーによりパターン化することで、上層配線(第2配線)8a,8bが形成される(図8)。なお図8中、9a,9bはこのときの反射防止膜とするTiN層である。

【0024】この実施例によれば、本発明を採用するこにより、深さの異なる接続孔5a,5b(コンタクトホール)において、深さの浅いコンタクトホール5bに過剰のオーバーエッチングがかからないので、エッチングガスと配線との反応生成物の発生を抑えることができ、コンタクト特性が改善される。

【0025】

【発明の効果】本発明の接続孔を形成する工程を有する配線構造の形成方法によれば、段差のある下地上に形成した層間絶縁膜に深さの異なる接続孔を形成する場合も、オーバーエッチングの問題が生じず、よって特性の良好な配線構造が得られるという効果がもたらされる。

【図面の簡単な説明】

【図1】 実施例1の工程を順に断面図で示すものである(1)。

【図2】 実施例1の工程を順に断面図で示すものである(2)。

【図3】 実施例1の工程を順に断面図で示すものである(3)。

【図4】 実施例1の工程を順に断面図で示すものである(4)。

【図5】 実施例1の工程を順に断面図で示すものである(5)。

【図6】 実施例1の工程を順に断面図で示すものである(6)。

【図7】 実施例1の工程を順に断面図で示すものである(7)。

【図8】 実施例1の工程を順に断面図で示すものである(8)。

【図9】 従来技術の工程を順に断面図で示すものである(1)。

【図10】 従来技術の工程を順に断面図で示すものである(2)。

【図11】 従来技術の工程を順に断面図で示すものである(3)。

【図12】 従来技術の工程を順に断面図で示すものである(4)。

【符号の説明】

1 下地(絶縁膜)

10 ポリSi層

2 導電層(Ti/AlCu/Ti)

2a,2b配線(下層の第1配線)

3 層間絶縁膜

31 P−TEOS

32 O3 TEOS

33 P−TEOS

4,4a,4b,40レジスト

5a 深い接続孔(深いコンタクトホール)

5b 浅い接続孔(浅いコンタクトホール)

6 反射防止膜(TiN層)

7a,7b埋め込み導電材料(Blk−W)

8a,8b第2(上層)配線

11,11a,11bエッチング速度の小さい材料層(SiN層)

【特許請求の範囲】

【請求項1】段差を有する下地上に形成した層間絶縁膜に接続孔を形成する工程を有する配線構造の形成方法において、段差底部に該当する層間絶縁膜に深い接続孔を形成し、段差上部に該当する層間絶縁膜に浅い接続孔を形成することを同時に行う場合に、上記浅い接続孔形成部位の底部にエッチング速度の小さい材料層を予め形成しておくことを特徴とする接続孔を形成する工程を有する配線構造の形成方法。

【請求項2】段差を有する絶縁膜上に導電膜を形成する工程と、エッチング速度の小さい材料層を形成する工程と、上記深い接続孔形成部位しておける該エッチング速度の小さい材料層を除去する工程と、上記導電膜をパターニングする工程と、層間絶縁膜を形成して層間平坦化を行う工程と、接続孔をエッチングにより形成する工程とを備えることを特徴とする請求項1に記載の接続孔を形成する工程を有する配線構造の形成方法。

【請求項3】上記接続孔の形成後、第2の導電膜を形成する工程と、該第2の導電膜をパターニングする工程を行うことを特徴とする請求項2に記載の接続孔を形成する工程を有する配線構造の形成方法。

【請求項1】段差を有する下地上に形成した層間絶縁膜に接続孔を形成する工程を有する配線構造の形成方法において、段差底部に該当する層間絶縁膜に深い接続孔を形成し、段差上部に該当する層間絶縁膜に浅い接続孔を形成することを同時に行う場合に、上記浅い接続孔形成部位の底部にエッチング速度の小さい材料層を予め形成しておくことを特徴とする接続孔を形成する工程を有する配線構造の形成方法。

【請求項2】段差を有する絶縁膜上に導電膜を形成する工程と、エッチング速度の小さい材料層を形成する工程と、上記深い接続孔形成部位しておける該エッチング速度の小さい材料層を除去する工程と、上記導電膜をパターニングする工程と、層間絶縁膜を形成して層間平坦化を行う工程と、接続孔をエッチングにより形成する工程とを備えることを特徴とする請求項1に記載の接続孔を形成する工程を有する配線構造の形成方法。

【請求項3】上記接続孔の形成後、第2の導電膜を形成する工程と、該第2の導電膜をパターニングする工程を行うことを特徴とする請求項2に記載の接続孔を形成する工程を有する配線構造の形成方法。

【図1】

【図2】

【図3】

【図4】

【図6】

【図7】

【図10】

【図11】

【図5】

【図8】

【図9】

【図12】

【図2】

【図3】

【図4】

【図6】

【図7】

【図10】

【図11】

【図5】

【図8】

【図9】

【図12】

【公開番号】特開平9−17862

【公開日】平成9年(1997)1月17日

【国際特許分類】

【出願番号】特願平7−161927

【出願日】平成7年(1995)6月28日

【出願人】(000002185)ソニー株式会社 (34,172)

【公開日】平成9年(1997)1月17日

【国際特許分類】

【出願日】平成7年(1995)6月28日

【出願人】(000002185)ソニー株式会社 (34,172)

[ Back to top ]