描画装置

【課題】 同じ表示情報を繰り返し読み出す処理を不要にして処理の高速化を図ることができる描画装置を提供する。

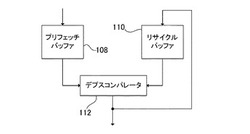

【解決手段】 プリフェッチバッファ108は、メインRAM25から、ソート後の構造体インスタンスを順次読み込み、読み込んだ順番で構造体インスタンスを出力するFIFO構造のバッファである。リサイクルバッファ110は、次の描画サイクルでも使用される(再利用できる)構造体インスタンスを格納するFIFO構造のバッファである。デプスコンパレータ112は、プリフェッチバッファ108から取り出した構造体インスタンスに含まれるデプス値と、リサイクルバッファ110から取り出した構造体インスタンスに含まれるデプス値と、を比較して、より奥に表示されるべき構造体インスタンスを選択して、後段に出力する。

【解決手段】 プリフェッチバッファ108は、メインRAM25から、ソート後の構造体インスタンスを順次読み込み、読み込んだ順番で構造体インスタンスを出力するFIFO構造のバッファである。リサイクルバッファ110は、次の描画サイクルでも使用される(再利用できる)構造体インスタンスを格納するFIFO構造のバッファである。デプスコンパレータ112は、プリフェッチバッファ108から取り出した構造体インスタンスに含まれるデプス値と、リサイクルバッファ110から取り出した構造体インスタンスに含まれるデプス値と、を比較して、より奥に表示されるべき構造体インスタンスを選択して、後段に出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フレームバッファを使用せずに品質の高い三次元イメージの表示を可能とする描画装置及びその関連技術に関する。

【背景技術】

【0002】

従来では、三次元イメージを表示する場合、1フレーム以上のイメージデータを描画することが可能なフレームバッファやビデオメモリを、画像生成装置に実装するのが一般的であった(特開平6−348861号公報、特開平7−282270号公報)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平6−348861号公報

【特許文献2】特開平7−282270号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、画像生成装置にフレームバッファ等を実装しようとすると、少なくとも一つのイメージ全体を格納する容量のメモリが必要不可欠となり、コストが高くなる。高品質の三次元イメージを表示するために、ダブルバッファ方式を採用すると、少なくとも二つのフレームバッファを格納可能な容量のメモリが必要となるため、更にコストが高くなる。

【0005】

一方、二次元イメージを表示する場合は、必ずしもフレームバッファは必要なく、ラインバッファでも十分である。しかし、ラインバッファを用いて、三次元イメージを表示しようとすると、従来の画像生成装置の描画能力では、描画可能なポリゴンの数が限られてくる等、見る者が満足するような品質の高い表示を行うことが困難である。

【0006】

そこで、本発明は、少ない記憶容量の、描画のためのバッファを用いながらも、品質の高い三次元イメージの表示を可能とする描画装置及びその関連技術を提供することを目的とする。

【0007】

また、本発明の他の目的は、少ない記憶容量の、描画のためのバッファを用いながらも、半透明合成を可能として、より品質の高い三次元イメージの表示を可能とする描画装置及びその関連技術を提供することである。

【0008】

さらに、本発明の他の目的は、インタレーススキャンによる表示を行う場合においても、少ない記憶容量の、描画のためのバッファを用いながらも、品質の高い三次元イメージの表示を可能とする描画装置及びその関連技術を提供することである。

【課題を解決するための手段】

【0009】

本発明の第1の観点によれば、描画装置は、それぞれが複数のピクセルから構成される平行な複数のラインを、そのラインに垂直な方向に並べて構成されるスクリーンに、多角形状のグラフィック要素を含むグラフィック要素ごとの表示情報に基づいて、前記グラフィック要素の組み合わせからなるスクリーンイメージを表示するための描画を行う描画装置であって、前記表示情報に含まれる、前記グラフィック要素の前記ラインに垂直な方向の位置を示す座標が、昇順あるいは降順のいずれかで並ぶように、前記グラフィック要素ごとの前記表示情報を並べ替えるソート手段と、前記ソート手段が並べ替えた前記表示情報を順番に読み出して、読み出した前記表示情報に基づいて、対応する前記グラフィック要素の描画を実行する描画手段と、を備える。

【0010】

この構成によれば、グラフィック要素のラインに垂直な方向の位置を示す座標が、昇順あるいは降順のいずれかで並ぶように、グラフィック要素ごとの表示情報を並べ替えている(ソート)。従って、ソート後の表示情報を順番に読み出して、描画処理を行うだけでよいため、描画のたびに、全ての表示情報の中から、そのとき描画すべき表示情報を検索する処理が不要になり、処理を高速化できる。以上の結果、1フレーム以上のイメージを格納するための大容量のバッファ(フレームバッファ等)を実装する必要は必ずしもなく、より容量の小さいバッファ(ラインバッファや、1ラインに満たないピクセルを描画するピクセルバッファ等)を実装した場合であっても、多くのグラフィック要素を組み合わせたスクリーンイメージの表示が可能になる。特に、二次元イメージ表示のための描画処理と比較して、高い処理能力が必要な三次元イメージ表示のための描画処理にも好適である。

【0011】

ここで、昇順とは、小さいほうから大きいほうへの順に並べることを意味し、降順とは、大きいほうから小さいほうへの順に並べることを意味する。

【0012】

上記描画装置において、前記描画手段は、前記スクリーンを構成する前記ピクセルのうち第1の所定数分のピクセル情報を格納可能であって、格納した前記ピクセル情報を前記スクリーンイメージを表示するために出力し、出力した前記ピクセル情報が格納されていた位置に、前記スクリーンイメージを表示するための新たなピクセル情報を格納する第1バッファ(例えば、図1のラインバッファLB1,LB2に相当)と、第2の所定数分の前記グラフィック要素の前記表示情報を格納可能であって、前記表示情報に基づく前記ピクセル情報が前記第1バッファに格納された後に、当該表示情報に基づく他のピクセル情報を前記第1バッファに格納するために、当該表示情報が再利用可能なときに、再利用のために送られてくる順番で、当該表示情報を格納し、前記第1バッファが前記新たなピクセル情報を格納する期間が到来したときに、格納した順番で前記表示情報を出力する第2バッファ(例えば、図1のリサイクルバッファ110に相当)と、前記ソート手段が並べ替えた順番で読み出された前記表示情報のうち、前記第1バッファに格納すべき期間が到来した前記新たなピクセル情報を生成するための前記表示情報に含まれる表示深度情報と、前記第2バッファから出力される前記表示情報に含まれる表示深度情報と、を比較し、予め定められた規則に従って、いずれかの前記表示情報を選択して先に出力する比較手段と、前記比較手段から出力された前記表示情報に基づいて前記ピクセル情報を生成し、前記生成したピクセル情報を前記第1バッファに書き込む書き込み手段と、を含む。

【0013】

この構成によれば、第1バッファへの新たなピクセル情報の書き込み(新たなピクセルの描画)のために、表示情報が再利用可能な場合は、その表示情報は、第2バッファに格納される。このため、同じ表示情報を使用する新たなピクセルの描画のたびに、ソート後の全ての表示情報が格納されたメモリから、その同じ表示情報を繰り返し読み出す処理が不要になって、より処理の高速化を図ることができる。

【0014】

また、比較手段を設けて、ソート手段が並べ替えた順番で新たに読み出された表示情報と、再利用のための第2バッファに格納された表示情報と、の描画順序(つまり、これら表示情報に基づくピクセルの描画順序)を判定している。このため、判定終了後に、再利用可能な表示情報を第2バッファに送って順番に格納するだけで、第2バッファには、再利用可能な表示情報について、適切な描画順序で表示情報が格納される。このように、第2バッファには、再利用可能な表示情報について適切な描画順序で格納されているところ、これらは、ソート手段が並べ替えた順番で新たに読み出された表示情報との間で、さらに描画順序が判定されるので、常に適切な描画順序での描画が可能となる。

【0015】

上記描画装置において、複数の前記グラフィック要素を表示する場合であって、その複数のグラフィック要素の前記座標が同じ場合、前記ソート手段は、その複数のグラフィック要素に対しては、前記表示情報に含まれる表示深度情報が示す表示深度の昇順あるいは降順のいずれかで前記表示情報を並べる。

【0016】

この構成によれば、複数のグラフィック要素を表示する場合であって、その複数のグラフィック要素の座標が同じ場合、スクリーンを構成する各ラインにおいて、表示深度の昇順あるいは降順のいずれかで表示情報が並べられる。従って、各ラインにおいて、表示情報に基づくグラフィック要素は、表示深度の大きいもの順あるいは小さいもの順のいずれかで描画される。表示深度の昇順で表示情報を並べる場合は、グラフィック要素は、表示深度が小さいもの順で描画されるので、仮に表示深度が大きいグラフィック要素の描画処理が間に合わなかった場合でも、表示後の見た目の印象を良くすることができる。一方、表示深度の降順で表示情報を並べる場合は、グラフィック要素は、表示深度が大きいもの順で描画されるので、半透明合成を適切に行うことができる。何故ならば、半透明のグラフィック要素の描画色は、当該グラフィック要素の奥にあるグラフィック要素の描画色に依存するため、グラフィック要素を奥から順に描画する必要がある。

【0017】

この描画装置において、複数の前記グラフィック要素が、前記スクリーンの先頭ラインに表示すべきピクセルを含む場合、前記ソート手段は、その複数のグラフィック要素に対しては、前記座標の大小に関係なく、前記表示深度の昇順あるいは降順のいずれかで前記表示情報を並べる。

【0018】

この構成によれば、複数のグラフィック要素が、スクリーンの先頭ラインに表示すべきピクセルを含む場合、それらの座標に関係なく、つまり、それらの座標を同一とみなして、表示深度の昇順あるいは降順のいずれかで表示情報が並べられる。従って、先頭ラインにおいて、表示情報に基づくグラフィック要素は、表示深度の大きいもの順あるいは小さいもの順のいずれかで描画される。表示情報を表示座標順(グラフィック要素の、ラインに垂直な方向の位置を示す座標順)でソートし、表示座標の同じものについては表示深度順でソートする場合、先頭ラインの描画においては、必ずしも表示深度の昇順または降順での描画が保証されないが、この構成によれば、先頭ラインから表示深度順での描画を行うことが可能となる。表示深度の昇順で並べる効果及び降順で並べる効果は上記と同様である。

【0019】

上記描画装置において、前記ソート手段は、所定数分の前記グラフィック要素の前記表示情報の並べ替えが完了するたびに、その旨を前記描画手段に通知し、前記描画手段は、前記ソート手段からの前記通知を受けて、並べ替えが完了した前記表示情報を順次読み出す。

【0020】

この構成によれば、表示情報のソートが確定するたびに、その都度、その旨の通知がなされるので、描画手段は、全表示情報のソートの完了を待つことなく、逐次、表示情報を読み込むことができる。

【0021】

この描画装置において、前記所定数分の前記グラフィック要素の前記表示情報は、1つ分の前記グラフィック要素の前記表示情報である。

【0022】

この構成によれば、1つ分のグラフィック要素のソートが確定するたびに、その旨の通知がなされるので、描画手段は、ソートが確定したグラフィック要素の表示情報をソート完了直後から読み込むことができる。

【0023】

上記描画装置において、前記描画手段は、第1バッファ及び第2バッファに加えて、さらに、第3バッファ(例えば、図1のプリフェッチバッファ108に相当)を含み、この第3バッファは、第3の所定数分の前記グラフィック要素の前記表示情報を格納可能であって、前記ソート手段が並べ替えた順番で読み出される前記表示情報を、読み出された順番で格納し、前記第1バッファに格納すべき期間が到来した前記新たなピクセル情報を生成するための前記表示情報を格納された順番で出力し、前記比較手段は、前記第3バッファから出力される前記表示情報に含まれる表示深度情報と、再利用のために送られてきた順番で格納された前記第2バッファから出力される前記表示情報に含まれる表示深度情報と、を比較し、前記予め定められた規則に従って、いずれかの前記表示情報を選択して先に出力する。

【0024】

この構成によれば、第3バッファが設けられ、この第3バッファは、ソート手段がソートした順番での表示情報の入力タイミングと比較手段への表示情報の出力タイミングとの緩衝機構である。これにより、ソート手段がソートした順番での表示情報の入力の、描画手段にとっての待ち時間を削減できる。

【0025】

上記描画装置において、前記予め定められた規則は、前記比較の結果、大きい前記表示深度を示す前記表示深度情報を含む前記表示情報を選択することである。

【0026】

この構成によれば、グラフィック要素は、表示深度の大きいもの順で描画される。その結果、半透明合成を適切に行うことができる。

【0027】

上記描画装置において、前記ソート手段が並べ替えを実行する際の前記グラフィック要素の前記座標は、前記グラフィック要素の頂点の座標であって、最も大きい座標あるいは最も小さい座標のいずれかである。

【0028】

この構成によれば、全てのグラフィック要素に対して同じ条件でソートができるので、正しい描画順序で描画を行うことができる。

【0029】

上記描画装置において、前記第1バッファは、少なくとも1つの前記ラインを構成する複数の前記ピクセル情報を格納するバッファである。

【0030】

この構成によれば、フレームバッファを使用する場合よりもコストを低く抑えることができる。また、1ラインに満たないピクセルを格納するピクセルバッファを使用する場合よりも簡素な回路構成で(簡単な制御で)描画を実現できる。

【0031】

上記描画装置において、前記ソート手段は、前記表示情報の並べ替えを、ヒープソートにより実行する。

【0032】

この構成によれば、表示情報のソートが1つずつ確定されるので、ソートの確定のたびに、その旨を通知する機構を容易に実現できる。また、全表示情報のソートに必要な時間のバラツキを少なくできる。

【0033】

上記描画装置において、前記ソート手段は、前記グラフィック要素としてのポリゴンを表示するための前記表示情報と、前記グラフィック要素としてのスプライトを表示するための前記表示情報と、で独立して前記並べ替えを実行する。

【0034】

この構成によれば、ポリゴンのための表示情報と、スプライトのための表示情報と、の形式及びサイズが異なっている場合でも容易にソートが可能であり、表示情報を格納するためのメモリ領域の使用効率も高まる。

【0035】

この描画装置において、前記描画手段は、前記ソート手段が並べ替えた前記ポリゴンのための前記表示情報と、前記ソート手段が並べ替えた前記スプライトのための前記表示情報と、を前記ソート手段による並べ替えの規則に準じてマージソートするマージソート手段をさらに含む。

【0036】

この構成によれば、ポリゴン及びスプライトが独立してソートされた場合であっても、描画処理の前にポリゴンのための表示情報群とスプライトのための表示情報群がマージソートされるため、適切な描画処理が可能となる。

【0037】

本発明の第2の観点によると、描画装置は、それぞれが複数のピクセルから構成される平行な複数のラインを、そのラインに垂直な方向に並べて構成されるスクリーンに、多角形状のグラフィック要素を含むグラフィック要素ごとの表示情報に基づいて、インタレーススキャンにより前記グラフィック要素の組み合わせからなるスクリーンイメージを表示するための描画を行う描画装置であって、偶数フィールドを表示するために、前記グラフィック要素ごとの表示情報を、第1の規則に従って並べ替え、かつ、奇数フィールドを表示するために、前記グラフィック要素ごとの表示情報を、第2の規則に従って並べ替えるソート手段と、前記奇数フィールドを表示する場合、その表示のために前記ソート手段が並べ替えた前記表示情報を順番に読み出して、読み出した前記表示情報に基づいて、対応する前記グラフィック要素の描画を実行し、かつ、前記偶数フィールドを表示する場合、その表示のために前記ソート手段が並べ替えた前記表示情報を順番に読み出して、読み出した前記表示情報に基づいて、対応する前記グラフィック要素の描画を実行する描画手段と、を備え、前記第1の規則は、前記表示情報に含まれる、前記グラフィック要素の前記ラインに垂直な方向の位置を示す座標が、昇順あるいは降順のいずれかで並ぶように、前記グラフィック要素ごとの前記表示情報を並べ替える際に、前記座標が、スキャンする奇数ライン又はその1つ前の偶数ラインを示す前記グラフィック要素については、当該グラフィック要素の前記座標が同一であるとして、前記表示情報に含まれる表示深度情報が示す表示深度の昇順あるいは降順のいずれかで前記表示情報を並べることであり、前記第2の規則は、前記表示情報に含まれる、前記グラフィック要素の前記座標が、昇順あるいは降順のいずれかで並ぶように、前記グラフィック要素ごとの前記表示情報を並べ替える際に、前記座標が、スキャンする偶数ライン又はその1つ前の奇数ラインを示す前記グラフィック要素については、前記座標が同一であるとして、前記表示情報に含まれる表示深度情報が示す表示深度の昇順あるいは降順のいずれかで前記表示情報を並べることである。

【0038】

この構成によれば、第1の観点による発明と同様の作用効果を奏することに加えて、次の作用効果を奏する。インタレーススキャンによってスクリーンイメージが表示される場合、表示座標(グラフィック要素の、ラインに垂直な方向の位置を示す座標)が飛び越し走査により飛び越されたラインを示す表示情報と、表示座標が描画対象のラインを示す表示情報とが、表示対象ラインの描画処理において共に読み出される。したがって、これらの表示情報の示す表示座標を同じ値とみなし、表示深度順にソートを行うことにより、インタレーススキャンの場合でも表示深度順での描画処理が保証される。表示深度の昇順で並べる効果及び降順で並べる効果は上記と同様である。

【0039】

以上の結果、インタレーススキャンによる表示を行う場合においても、少ない記憶容量の、描画のためのバッファ(第1バッファ)を用いながらも、品質の高い三次元イメージの表示を実現できる。

【0040】

上記描画装置において、前記描画手段は、前記スクリーンを構成する前記ピクセルのうち第1の所定数分のピクセル情報を格納可能であって、格納した前記ピクセル情報を前記スクリーンイメージを表示するために出力し、出力した前記ピクセル情報が格納されていた位置に、前記スクリーンイメージを表示するための新たなピクセル情報を格納する第1バッファと、第2の所定数分の前記グラフィック要素の前記表示情報が格納可能であって、前記表示情報に基づく前記ピクセル情報が前記第1バッファに格納された後に、当該表示情報に基づく他のピクセル情報を前記第1バッファに格納するために、当該表示情報が再利用可能なときに、再利用のために送られてくる順番で、当該表示情報を格納し、前記第1バッファが前記新たなピクセル情報を格納する期間が到来したときに、格納した順番で前記表示情報を出力する第2バッファと、前記奇数フィールドを表示する場合、その表示のために前記ソート手段が並べ替えた順番で読み出された前記表示情報のうち、前記第1バッファに格納すべき期間が到来した前記新たなピクセル情報を生成するための前記表示情報に含まれる前記表示深度情報と、前記第2バッファから出力される前記表示情報に含まれる前記表示深度情報と、を比較し、予め定められた規則に従って、いずれかの前記表示情報を選択して先に出力し、前記偶数フィールドを表示する場合、その表示のために前記ソート手段が並べ替えた順番で読み出された前記表示情報のうち、前記第1バッファに格納すべき期間が到来した前記新たなピクセル情報を生成するための前記表示情報に含まれる前記表示深度情報と、前記第2バッファから出力される前記表示情報に含まれる前記表示深度情報と、を比較し、前記予め定められた規則に従って、いずれかの前記表示情報を選択して先に出力する比較手段と、前記比較手段から出力された前記表示情報に基づいて前記ピクセル情報を生成し、前記生成したピクセル情報を前記第1バッファに書き込む書き込み手段と、を含む。

【0041】

この構成によれば、第1の観点による発明に加えた第2バッファ及び比較手段と同様の第2バッファ及び比較手段を有している。このため、その場合と同様の作用効果を奏する。

【0042】

上記描画装置において、複数の前記グラフィック要素が、前記スクリーンの先頭ラインに表示すべきピクセルを含む場合、前記ソート手段は、前記第1の規則及び前記第2の規則を適用せず、その複数のグラフィック要素に対しては、前記表示深度の昇順あるいは降順のいずれかで前記表示情報を並べる。

【0043】

この構成によれば、第1の観点による発明に加えた、複数のグラフィック要素がスクリーンの先頭ラインに表示すべきピクセルを含む場合の並べ替えの規則と同じ規則を有している。このため、その場合と同様の作用効果を奏する。

【0044】

上記描画装置において、前記ソート手段は、所定数分(好ましくは、1つ分)の前記グラフィック要素の前記表示情報の並べ替えが完了するたびに、その旨を前記描画手段に通知し、かつ、前記奇数フィールドを表示するための前記並べ替えを、当該奇数フィールドを表示する直前の垂直ブランキング期間の開始直後に実行開始し、前記偶数フィールドを表示するための前記並べ替えを、当該偶数フィールドを表示する直前の垂直ブランキング期間の開始直後に実行開始する。

【0045】

ソートが確定する毎にその旨を通知することにより、描画手段はソートの完了を待たずに描画処理を行うことが可能であるが、さらにこの構成によれば、垂直ブランキング期間の開始直後にソートが実行開始されるので、ソート前の演算処理のために余裕を持ったより十分な時間を確保できる。

【0046】

本発明の新規な特徴は、請求の範囲に記載されている。しかしながら、発明そのもの及びその他の特徴と効果は、添付図面を参照して具体的な実施例の詳細な説明を読むことにより容易に理解される。

【図面の簡単な説明】

【0047】

【図1】図1(a)は、本発明の実施の形態によるYSU19が実行するソートルール1を説明するための、スクリーンSCRに表示されたポリゴン#0〜#7の例示図である。図1(b)は、ソートルール1に従ったソートの例示図である。

【図2】図2(a)は、YSU19が実行するソートルール2を説明するための、スクリーンSCRに表示されたポリゴン#0〜#7の例示図である。図2(b)は、ソートルール2に従ったソートの例示図である。

【図3】図3(a)は、YSU19が実行するソートルール3を説明するための、スクリーンSCRに表示されたポリゴン#0〜#7の例示図である。図3(b)は、ソートルール3に従ったソートの例示図である。

【図4】図4は、本発明の実施の形態によるRPU19の前段部分の説明図である。

【図5】図5(a)は、RPU9のプリフェッチバッファ108、リサイクルバッファ110、及びデプスコンパレータ112の処理を説明するための、スクリーンSCRに表示されたポリゴンの例示図である。図5(b)は、RPU9による描画処理の前処理としてのYSU19によるソーティング結果の例示図である。

【図6】図6(a)は、図5(a)のラインLcの1つ前のラインの表示のための描画が終了した直後の、プリフェッチバッファ108及びリサイクルバッファ110の格納状態を示す図である。図6(b)は、ポリゴン#1,#2及び#4の対応するピクセルをラインLcに描画する際のポリゴン構造体インスタンスの流れを示す図である。図6(c)は、ポリゴン#1,#2及び#4の対応するピクセルをラインLcに描画する際のポリゴン構造体インスタンスの流れを示す図である。図6(d)は、ポリゴン#1,#2及び#4の対応するピクセルをラインLcに描画する際のポリゴン構造体インスタンスの流れを示す図である。図6(e)は、ラインLcの表示のための描画が終了した直後の、プリフェッチバッファ108及びリサイクルバッファ110の格納状態を示す図である。

【図7】図7(a)は、図5(b)のポリゴン構造体インスタンス#0,#3,#1及び#2がプリフェッチバッファ108に格納された状態を示す図である。図7(b)は、図5(a)のポリゴン#0及び#3の対応するピクセルをラインLaに描画する際のポリゴン構造体インスタンスの流れを示す図である。図7(c)は、図5(a)のポリゴン#0及び#3の対応するピクセルをラインLaに描画する際のポリゴン構造体インスタンスの流れを示す図である。図7(d)は、ポリゴン#0及び#3の表示最終ラインLbの描画に至るまでのポリゴン構造体インスタンスの流れを示す図である。図7(e)は、ポリゴン#0及び#3の表示最終ラインLbの描画でのポリゴン構造体インスタンスの流れを示す図である。

【図8】図8は、インタレーススキャンによる表示を行う場合のYSU19によるソートルール4の説明図である。

【図9】図9(a)は、インタレーススキャンによる表示を行う場合のソート処理をモード1のタイミングで行う場合の説明図である。図9(b)は、インタレーススキャンによる表示を行う場合のソート処理をモード2のタイミングで行う場合の説明図である。

【図10】図10は、本発明の実施の形態によるマルチメディアプロセッサ1の内部構成を示すブロック図である。

【図11】図11は、図10のマルチメディアプロセッサ1によるグラフィックス処理の流れの概要を示すフローチャートである。

【図12】図12は、図10のRPU9の内部構成を示すブロック図である。

【図13】図13は、テクスチャマッピングモードのポリゴン構造体の構成を示す図である。

【図14】図14は、テクスチャアトリビュート構造体の構成を示す図である。

【図15】図15は、グーローシェーディングモードのポリゴン構造体の構成を示す図である。

【図16】図16(a)は、シザリングディセーブル時のスプライト構造体の構成を示す図である。図16(b)は、シザリングイネーブル時のスプライト構造体の構成を示す図である。

【図17】図17は、スライサ118による、グーローシェーディングモードのポリゴンに対する処理の説明図である。

【図18】図18は、スライサ118による、テクスチャマッピングモードのポリゴンに対する処理の説明図である。

【図19】図19は、スライサ118によるスプライトに対する処理の説明図である。

【図20】図20は、ピクセルディザ122によるディザリングの説明図である。

【図21】図21は、バイリニアフィルタ130によるバイリニアフィルタリングの説明図である。

【図22】図22は、図10のYSU19による配列AのYソート完了後のヒープ構造を示す図である。

【図23】図23は、図22のヒープ構造のメインRAM25への格納方法の説明図である。

【図24】図24は、図10のYSU19によるポリゴン構造体配列のYソート処理の全体的な流れの一例を示すフローチャートである。

【図25】図25は、図24のステップS21のヒープ構築処理の流れの一例を示すフローチャートである。

【図26】図26は、ダウンヒープ処理の流れの一例を示すフローチャートである。

【図27】図27は、順位比較処理の流れの一例を示すフローチャートである。

【発明を実施するための形態】

【0048】

以下、本発明の実施の形態について、図面を参照しながら説明する。なお、図中、同一または相当部分については同一の参照符号を付してその説明を援用する。数式中「・」は乗算を意味する。

【0049】

まず、本発明の実施の形態による3次元イメージ表示のための描画処理の原理を説明する。本実施の形態では、描画処理の前処理として、後述のYソーティングユニット(以下、「YSU」と呼ぶ。)19によるソート(「Yソート」と呼ぶこともある。)処理が実行される。ソートの対象は、構造体配列の各要素である。構造体配列は、二次元空間に投影された三次元立体の各面の形状を表すための多角形状のグラフィック要素であるポリゴンのための構造体配列(以下、「ポリゴン構造体配列」と呼ぶ。)と、スクリーンに平行な矩形状のグラフィック要素であるスプライトのための構造体配列(以下、「スプライト構造体配列」と呼ぶ。)と、が後述のメインRAM(random access memory)25に用意される。ポリゴン構造体配列の要素は、「ポリゴン構造体インスタンス」であり、スプライト構造体配列の要素は、「スプライト構造体インスタンス」である。ただし、両者を区別して説明する必要がないときは、単に「構造体インスタンス」と呼ぶこともある。

【0050】

ポリゴン構造体配列に格納された各ポリゴン構造体インスタンスは、ポリゴンごとの表示情報(スクリーンにおける頂点座標、テクスチャマッピングモードでのテクスチャパターンに関する情報及びグーローシェーディングモードでのカラーデータ(RGBのカラーコンポーネント)を含む。)であり、1つのポリゴン構造体インスタンスに1つのポリゴンが対応している。スプライト構造体配列に格納された各スプライト構造体インスタンスは、スプライトごとの表示情報(スクリーンにおける座標及びテクスチャパターンに関する情報を含む。)であり、1つのスプライト構造体インスタンスに1つのスプライトが対応している。これらについては、後で詳述する。

【0051】

以下、YSU19によるソートルール1,2及び3について説明するが、その前に座標系について説明する。ディスプレイ装置(図示せず)への実際の表示に用いられる二次元座標系をスクリーン座標系と呼ぶ。本実施の形態では、スクリーン座標系は、水平方向2048ピクセル×垂直方向1024ピクセルの2次元ピクセル配列から構成される。座標原点は左上にあり、水平右方向がX軸の正、垂直下方向がY軸の正に相当する。ただし、実際に表示される領域は、スクリーン座標系の全空間ではなく一部の空間である。この表示領域をスクリーンと呼ぶことにする。

【0052】

図1(a)は、YSU19が実行するソートルール1を説明するための、スクリーンSCRに表示されたポリゴン#0〜#7の例示図である。図1(b)は、ソートルール1に従ったソートの例示図である。図1(b)に示すように、ポリゴン構造体配列PSには、図1(a)のポリゴン#0〜#7に対応するポリゴン構造体インスタンス#0〜#7が格納されている。なお、対応するポリゴン及びポリゴン構造体インスタンスには、同一の参照符号を付している。

【0053】

YSU19は、ポリゴン#0〜#7のY座標が小さい順に、各ポリゴン構造体インスタンス#0〜#7を並べ替える。この場合、ポリゴンの3頂点のY座標のうち、最も小さいY座標(以下、「最小Y座標」と呼ぶ。)が、この並べ替えで用いるポリゴンのY座標とする。

【0054】

このソートの結果、図1(b)の右側に示すように、最小Y座標が小さい順に、各ポリゴン構造体インスタンス#0〜#7が並べ替えられる。

【0055】

以上のように、最小Y座標が小さい順に、各ポリゴン構造体インスタンスを並べ替えることをソートルール1と呼ぶ。

【0056】

ただし、最小Y座標が同一である複数のポリゴンも存在しうる。この場合は、ソートルール2に従う。

【0057】

図2(a)は、YSU19が実行するソートルール2を説明するための、スクリーンSCRに表示されたポリゴン#0〜#7の例示図である。図2(b)は、ソートルール2に従ったソートの例示図である。図2(a)に示すように、スクリーンSCRにおいて、ポリゴン#0、#1、及び#7の最小Y座標は、共に「Ys」であり同一である。この場合、YSU19は、各ポリゴン構造体インスタンス#0、#1、及び#7に含まれるデプス値が大きい順に、各ポリゴン構造体インスタンス#0、#1、及び#7を並べ替える。

【0058】

このソートの結果、図2(b)の右側に示すように、ポリゴン構造体インスタンス#0、#1、及び#7については、デプス値が大きい順に並べ替えられている。

【0059】

デプス値(「表示深度情報」と呼ぶこともある。)は、描画対象のピクセルが重なった場合、どのピクセルを先に描画するかを示す情報であり、その値が大きいほど先に(奥に)描画され、その値が小さいほど後で(手前に)描画される。つまり、デプス値が大きいほどスクリーンSCRの奥に表示することが示され、小さいほど手前に表示することが示される。

【0060】

以上のように、最小Y座標が同じである複数のポリゴンについては、デプス値が大きい順に、各ポリゴン構造体インスタンスを並べることがソートルール2である。

【0061】

ただし、YSU19は、スクリーンSCRの先頭ラインに表示されるピクセルを持つ複数のポリゴンについては、最小Y座標が異なっている場合でも、それらが同一であるとみなして、ソートルール1ではなく、ソートルール2に従って、各ポリゴン構造体インスタンスの並べ替えを行う。つまり、スクリーンSCRの先頭ラインに表示されるピクセルを持つポリゴンが複数存在する場合は、最小Y座標が同一であるとみなして(つまり、最小Y座標の値に関係なく)、デプス値が大きい順に並べ替えられる。これをソートルール3と呼ぶことにする。

【0062】

図3(a)は、YSU19が実行するソートルール3を説明するための、スクリーンSCRに表示されたポリゴン#0〜#7の例示図である。図3(b)は、ソートルール3に従ったソートの例示図である。図3(a)に示すように、スクリーンSCRの先頭ラインに表示されるピクセルを持つポリゴン#2、#5、及び#7の最小Y座標は、異なっている。この場合、YSU19は、ポリゴン#2、#5、及び#7の最小Y座標が同一であるとみなして、各ポリゴン構造体インスタンス#2、#5、及び#7に含まれるデプス値が大きい順に、各ポリゴン構造体インスタンス#2、#5、及び#7を並べ替える。

【0063】

このソートの結果、図3(b)の右側に示すように、ポリゴン構造体インスタンス#2、#5、及び#7については、デプス値が大きい順に並べ替えられている。

【0064】

以上のように、先頭ラインに表示されるピクセルを持つ複数のポリゴンについては、最小Y座標が異なっている場合でも、ソートルール1ではなく、最小Y座標が同一であるとみなして、ソートルール2に従い、デプス値の大きい順に、各ポリゴン構造体インスタンスを並べ替えることがソートルール3である。

【0065】

上記のソートルール1〜3は、スプライト構造体配列の各スプライト構造体インスタンスを並べ替える際にも適用される。ここで、スプライトの最小Y座標は、スプライトの4頂点のY座標のうち、最も小さいY座標である。

【0066】

後で詳述するが、本実施の形態では、ポリゴン構造体のサイズは、128ビットであり、スプライト構造体のサイズは、64ビットである。このように、ポリゴンとスプライトでは、構造体のサイズが異なるので、構造体インスタンスの並べ替えは、ポリゴン構造体配列とスプライト構造体配列とで、それぞれ別個に行われる。

【0067】

ここで、ソートルール1によるソートを行う効果を説明する。比較のため、各ラインの描画のたびに、該当ラインに描画すべきポリゴン構造体インスタンス及びスプライト構造体インスタンスを、全ポリゴン構造体インスタンス及び全スプライト構造体インスタンスから検索して、描画処理を行うことを想定する。この比較例では、各ラインの描画のたびに、全ポリゴン構造体インスタンス及び全スプライト構造体インスタンスからの検索処理が必要となり、高速処理ができず、多くのポリゴン及びスプライトの表示ができない場合も発生して、十分な三次元イメージの表示が不可能な場合もある。

【0068】

この点、本実施の形態のように、最小Y座標が小さい順に、各ポリゴン構造体インスタンス及び各スプライト構造体インスタンスを予めソートしておくことにより、ソート後の各ポリゴン構造体インスタンス及び各スプライト構造体インスタンスを順番に読み出して、描画処理を行うだけでよい。この際に、最小Y座標が描画対象位置のY座標より大きい構造体インスタンスがソート済みの構造体配列より読み出された場合に、そのラインの描画処理を停止することにより、不要な構造体インスタンスの検索処理を全く行わずに済む。その結果、比較例のような検索処理が不要になって、処理の高速化を図ることができ、多くのポリゴン及びスプライトの表示が可能になって、十分な三次元イメージの表示が可能になる。

【0069】

但し、本実施の形態では、ピクセルを格納するバッファに対する描画処理を水平ライン単位で行っているので、対象となる水平ラインに描画すべきピクセルを持つポリゴン及びスプライトの構造体インスタンスを、水平ライン毎に順番に読み出して処理する必要がある。

【0070】

そこで、本実施の形態においては、後述するように、複数ラインに跨るポリゴン及びスプライトの構造体インスタンスを再利用することにより、それらをメモリから毎回取得することを避ける機構、新たにメモリから読み出した構造体インスタンスと再利用のためのバッファに格納された構造体インスタンスとの描画順序を判定する機構、及び全てのピクセルを描画し終えた構造体インスタンスを再利用のためのバッファに格納せずに破棄する機構を備える。

【0071】

上記のように、表示先頭ラインでの複数グラフィック要素(ポリゴン、スプライト)の描画や、同じラインで最小Y座標が同一の複数グラフィック要素の描画の場合に、ソートルール2及び3を追加したのは、各ラインにおいて、必ず、デプス値が大きいものから描画されるようにするためである。本実施の形態においては、ソート済みの構造体配列から読み出された構造体インスタンスのデプス値と、再利用のためのバッファから読み出された構造体インスタンスのデプス値とを比較し、より大きいデプス値を持つ構造体インスタンスを先に描画する機構を備えているので、ソートルール2及び3の追加によって、全ての構造体インスタンスに対して、必ずデプス値が大きいものから描画を行うことを保証できる。

【0072】

このように、各ラインにおいて、デプス値の大きい、より奥に表示されるべきグラフィック要素から先に描画処理を行うようにしたのは、半透明合成を実現するためである。奥に描画されるべき不透明のグラフィック要素が、手前に描画されるべき半透明のグラフィック要素の後に描画された場合、透けて見えるべき両者が重なった部分の描画を正しく処理することができない。このため、各ラインにおいて、デプス値の大きい、より奥に表示されるべきグラフィック要素から先に描画処理を行うのである。

【0073】

さて、YSU19によるソート後の各構造体インスタンスは、メインRAM25から、後述のレンダリングプロセッシングユニット(以下、「RPU」と呼ぶ。)9に読み込まれ、描画処理に利用される。この描画処理の前段の処理を説明する。ここで、本実施の形態では、後述のラインバッファLB1あるいはLB2にデータを書き込むことを描画と呼ぶ。各ラインバッファLB1及びLB2は、スクリーンの1ラインに対応したピクセルのデータを格納する。

【0074】

図4は、本発明の実施の形態によるRPU19の前段部分の説明図である。図4に示すように、RPU19は、その前段部分に、プリフェッチバッファ108、リサイクルバッファ110、及びデプスコンパレータ112を含む。

【0075】

プリフェッチバッファ108は、メインRAM25から、ソート後の構造体インスタンスを順次読み込み、読み込んだ順番で構造体インスタンスを出力するFIFO(first−in first−out)構造のバッファである。つまり、プリフェッチバッファ108には、YSU19により並べ替えられた順番で構造インスタンスが格納される。そして、格納された構造インスタンスは、対応するポリゴンあるいはスプライトの表示のための描画サイクルにおいて、格納された順番で出力される。プリフェッチバッファ108は、メインRAM25からの入力タイミングとデプスコンパレータ112への出力タイミングの緩衝機構として用意されている。これは、メインRAM25は、RPU19以外の機能ユニットと共有されているため、メインRAM25からのデータ取得に待ち時間が発生し得るためである。

【0076】

リサイクルバッファ110は、次の描画サイクルでも使用される(つまり、再利用できる)構造体インスタンスを格納するFIFO構造のバッファである。従って、リサイクルバッファ110に格納された構造体インスタンスは、次の描画サイクルで使用される。1描画サイクルは、1ラインの表示を行うための描画期間である。つまり、1描画サイクルは、ラインバッファLB1あるいはLB2のいずれかに、対応するラインの表示のために必要な全てのデータの描画が行われる期間である。

【0077】

デプスコンパレータ112は、プリフェッチバッファ108から取り出した構造体インスタンスに含まれるデプス値と、リサイクルバッファ110から取り出した構造体インスタンスに含まれるデプス値と、を比較して、より大きなデプス値を持つ(つまり、より奥に表示されるべき)構造体インスタンスを選択して、後段に出力する。

【0078】

この場合、選択された構造体インスタンスが、次の描画サイクルでも使用される(つまり、次のラインの描画にも使用される)場合は、後段に出力されるとともに、リサイクルバッファ110にも出力され書き込まれる。ただし、選択された構造体インスタンスが、次の描画サイクルで使用されない(つまり、次のラインの描画には使用されない)場合は、後段に出力されるだけで、リサイクルバッファ110には書き込まれない。

【0079】

従って、リサイクルバッファ110には、現ラインの描画に使用される構造体インスタンスであって、次ラインの描画にも使用される構造体インスタンスのみが、デプス値の大きい順に格納される。以下、具体例を挙げながら説明する。

【0080】

図5(a)は、RPU9のプリフェッチバッファ108、リサイクルバッファ110、及びデプスコンパレータ112の処理を説明するための、スクリーンSCRに表示されたポリゴンの例示図である。図5(b)は、RPU9による描画処理の前処理としてのYSU19によるソーティング結果の例示図である。

【0081】

図6(a)は、図5(a)のラインLcの1つ前のラインの表示のための描画が終了した直後の、プリフェッチバッファ108及びリサイクルバッファ110の格納状態を示す図、図6(b)〜図6(d)は、ポリゴン#1,#2及び#4に含まれる、ラインLcに対応するピクセルを描画する際のポリゴン構造体インスタンスの流れを示す図、図6(e)は、ラインLcへの表示のための描画が終了した直後の、プリフェッチバッファ108及びリサイクルバッファ110の格納状態を示す図、である。

【0082】

図6(a)に示すように、図5(a)のラインLcの1つ前のラインの表示のための描画が終了した直後では、プリフェッチバッファ108には、図5(b)に示したソート後の並びの順で、ポリゴン構造体インスタンス#4,#7,#6及び#5が格納され、リサイクルバッファ110には、デプス値が大きい順番で、ポリゴン構造体インスタンス#1及#2が格納されている。なお、ポリゴン構造体インスタンス#0及び#3は、ラインLcに表示されないため、リサイクルバッファ110には格納されていない。

【0083】

そして、図6(b)に示すように、デプスコンパレータ112は、プリフェッチバッファ108の先頭のポリゴン構造体インスタンス#4と、リサイクルバッファ110の先頭のポリゴン構造体インスタンス#1と、に含まれるデプス値を比較し、デプス値が大きいポリゴン構造体インスタンス#1を選択して、後段に出力するとともに、ポリゴン構造体インスタンス#1は、リサイクルバッファ110に送られる。なぜなら、ポリゴン#1は、次のラインにも表示されため、次の描画サイクルでも利用されるからである。この場合、ポリゴン構造体インスタンス#4は、デプスコンパレータ112に選択されていないので、プリフェッチバッファ108のリードポインタは、次に進まず、ポリゴン構造体インスタンス#4を指したままである。

【0084】

次に、図6(c)に示すように、デプスコンパレータ112は、プリフェッチバッファ108の先頭のポリゴン構造体インスタンス#4と、リサイクルバッファ110の先頭のポリゴン構造体インスタンス#2と、に含まれるデプス値を比較し、デプス値が大きいポリゴン構造体インスタンス#4を選択して、後段に出力するとともに、ポリゴン構造体インスタンス#4は、リサイクルバッファ110に送られる。なぜなら、ポリゴン#4は、次のラインにも表示されため、次の描画サイクルでも利用されるからである。この場合、ポリゴン構造体インスタンス#2は、デプスコンパレータ112に選択されていないので、リサイクルバッファ110のリードポインタは、次に進まず、ポリゴン構造体インスタンス#2を指したままである。

【0085】

そして、図6(d)に示すように、デプスコンパレータ112は、リサイクルバッファ110の先頭のポリゴン構造体インスタンス#2を読み込んで、後段に出力するとともに、ポリゴン構造体インスタンス#2は、リサイクルバッファ110に送られる。なぜなら、ポリゴン#2は、次のラインにも表示されるため、次の描画サイクルでも利用されるからである。

【0086】

以上の結果、ラインLcの表示のための描画が終了した直後では、リサイクルバッファ110には、次のラインの描画に利用されるポリゴン構造体インスタンス#1,#4及び#2が、デプス値の大きい順に格納される。なお、ラインLcには、ポリゴン#7は表示されないため、図6(e)において、ポリゴン構造体インスタンス#7は、プリフェッチバッファ108から読み出されない。

【0087】

図7(a)は、図5(b)のポリゴン構造体インスタンス#0,#3,#1及び#2がプリフェッチバッファ108に格納された状態を示す図、図7(b)及び図7(c)は、図5(a)のポリゴン#0及び#3に含まれる、ラインLaに対応するピクセルを描画する際のポリゴン構造体インスタンスの流れを示す図、図7(d)は、ポリゴン#0及び#3の表示最終ラインLbに至るまでのポリゴン構造体インスタンスの流れを示す図、図7(e)は、ポリゴン#0及び#3の表示最終ラインLbでのポリゴン構造体インスタンスの流れを示す図、である。

【0088】

図7(a)に示すように、図5(a)の先頭ラインLaへの表示のための描画の前に、プリフェッチバッファ108には、図5(b)に示したソート後のポリゴン構造体インスタンスが、その並びの順で格納される。

【0089】

そして、図7(b)に示すように、プリフェッチバッファ108の先頭のポリゴン構造体インスタンス#0が、デプスコンパレータ112に読み込まれ、デプスコンパレータ112は、このポリゴン構造体インスタンス#0を後段に出力するとともに、ポリゴン構造体インスタンス#0は、リサイクルバッファ110に送られ格納される。なぜなら、ポリゴン#0は、次のラインにも表示されため、次の描画サイクルでも利用されるからである。なお、プリフェッチバッファ108には、メインRAM25から読み出されたポリゴン構造体インスタンス#4が書き込まれる。

【0090】

次に、図7(c)に示すように、プリフェッチバッファ108の先頭のポリゴン構造体インスタンス#3が、デプスコンパレータ112に読み込まれ、後段に出力されるとともに、ポリゴン構造体インスタンス#3は、リサイクルバッファ110に送られ格納される。なぜなら、ポリゴン#3も、次のラインに表示されため、次の描画サイクルでも利用されるからである。なお、プリフェッチバッファ108には、メインRAM25から読み出されたポリゴン構造体インスタンス#7が書き込まれる。

【0091】

先頭ラインLaの表示のための描画が終了すると、次のラインの表示のための描画をすべく、図7(d)に示すように、デプスコンパレータ112は、リサイクルバッファ110から、ポリゴン構造体インスタンス#0を読み出して、後段に出力するとともに、ポリゴン構造体インスタンス#0は、リサイクルバッファ110に送られ格納される。なぜなら、ポリゴン#0は、引き続き次のラインに表示されるため、次の描画サイクルでも利用されるからである。続いて、デプスコンパレータ112は、リサイクルバッファ110から、ポリゴン構造体インスタンス#3を読み出して、後段に出力するとともに、ポリゴン構造体インスタンス#3は、リサイクルバッファ110に送られ格納される。なぜなら、ポリゴン#3もまた、引き続き次のラインに表示されるため、次の描画サイクルでも利用されるからである。このような処理が、ポリゴン#0及び#3の描画が終了するまで繰り返される。なお、ポリゴン#1は未だ表示されないため、プリフェッチバッファ108からは読み出されない。

【0092】

そして、図7(e)に示すように、ラインLbへポリゴン#0及び#3を表示するための描画処理では、デプスコンパレータ112は、リサイクルバッファ110から、ポリゴン構造体インスタンス#0を読み出して、後段に出力するが、ポリゴン構造体インスタンス#0は、リサイクルバッファ110には送られない。なぜなら、ポリゴン#0は、次のラインでは表示されず不要だからである。続いて、デプスコンパレータ112は、リサイクルバッファ110から、ポリゴン構造体インスタンス#3を読み出して、後段に出力するが、ポリゴン構造体インスタンス#3は、リサイクルバッファ110に送られない。なぜなら、ポリゴン#3もまた、次のラインには表示されず不要だからである。

【0093】

上記では、ポリゴンのみをスクリーンSCRに表示する場合を例に挙げたため、プリフェッチバッファ108に読み込まれる構造体インスタンスは、ポリゴン構造体インスタンスのみであった。しかし、後述するように、ソート後のポリゴン構造体インスタンスと、ソート後のスプライト構造体インスタンスと、はソートルール1〜3に従ってマージソートされるため、マージソート後の構造体インスタンスが、プリフェッチバッファ108に格納されることになる。従って、ポリゴン及びスプライトの双方を表示する場合は、ソートルール1〜3に従った順番で、プリフェッチバッファ108に、各構造体インスタンスが格納され、上記のような処理が行われる。

【0094】

以上のように、デプスコンパレータ112及びリサイクルバッファ110を設け、次の描画サイクルで利用する構造体インスタンスを、デプス値の大きい順に格納していった。これにより、YSU19によるソートルール1のソートを行うにもかかわらず、各ラインにおいて、必ず、デプス値の大きいグラフィック要素(ポリゴン、スプライト)から描画処理が行われる。

【0095】

さて、上記のソートルール1〜3は、ノンインタレーススキャンによる表示を行う場合に限らず、インタレーススキャンによる表示を行う場合にも、同様に適用される。ただし、インタレーススキャンの場合は、ソートルール1〜3だけでなく、次のようなソートルール4をさらに加えることが望ましい。

【0096】

インタレーススキャンの場合でも、上記ソートルール1〜3が適用される。ただし、奇数フィールドを表示するためのソートでは、奇数ラインに表示されるポリゴンの最小Y座標及び/又はその奇数ラインの1つ前の偶数ラインに表示されるポリゴンの最小Y座標とが同一であるとみなして、ソートルール2によるソートを行う。ただし、先頭の奇数ラインは除く。なぜなら、その1つ前の偶数ラインが存在しないからである。一方、偶数フィールドを表示するためのソートでは、偶数ラインに表示されるポリゴンの最小Y座標及び/又はその偶数ラインの1つ前の奇数ラインに表示されるポリゴンの最小Y座標とが同一であるとみなして、ソートルール2によるソートを行う。このようなソートをソートルール4と呼ぶ。

【0097】

図8は、インタレーススキャンによる表示を行う場合のYSU19によるソートルール4の説明図である。図8に示すように、スクリーンSCRに、ポリゴン#0〜#3を表示する場合を想定し、まず、奇数フィールドを表示するためのソート処理を考える。図中、上から第二番目の奇数ラインに注目する。

【0098】

この場合、ソートルール4によれば、第二番目の奇数ラインに初めて表示されるポリゴン#2の最小Y座標とその1つ前の偶数ラインに初めて表示されるポリゴン#1の最小Y座標と、が同一であるとみなして、デプス値の大きい順に、ポリゴン構造体インスタンス#2、次にポリゴン構造体インスタンス#1と並べられる。

【0099】

図8の例では、ソートルール1〜4によるソートの結果、奇数フィールドの表示のために、ポリゴン構造体インスタンスは、#0、#2、#1、及び#3の順番で並べ替えられる。ちなみに、ソートルール1〜3のみでは、ポリゴン構造体インスタンスは、#0、#1、#2、及び#3の順番で並べ替えられる。

【0100】

次に、偶数フィールドを表示するためのソート処理を考え、図中、一番上の偶数ラインに注目する。この場合、ソートルール4によれば、一番上の偶数ラインに初めて表示されるポリゴン#1の最小Y座標とその1つ前の奇数ラインに初めて表示されるポリゴン#0の最小Y座標と、が同一であるとみなして、デプス値の大きい順に、ポリゴン構造体インスタンス#1、次にポリゴン構造体インスタンス#0と並べられる。

【0101】

図8の例では、ソートルール1〜4によるソートの結果、偶数フィールドの表示のために、ポリゴン構造体インスタンスは、#1、#0、#3、及び#2の順番で並べ替えられる。ちなみに、ソートルール1〜3のみでは、ポリゴン構造体インスタンスは、#0、#1、#2、及び#3の順番で並べ替えられる。

【0102】

上記ソートルール4は、ソートルール1〜3に加えて、スプライト構造体配列の各スプライト構造体インスタンスを並べ替える際にも適用される。

【0103】

ここで、インタレーススキャンの場合に、ソートルール4を追加した理由を説明する。図8において、ソートルール1〜3のみでソートを行う場合を想定する。この場合、ポリゴン構造体インスタンス#0,#1,#2及び#3という順番で、最小Y座標が小さい順にソートが行われる。すると、奇数フィールドを表示する場合、例えば、図中、上から第一番目の奇数ラインの描画が終了した直後では、プリフェッチバッファ108の先頭には、ポリゴン構造体インスタンス#1が、リサイクルバッファ110の先頭には、ポリゴン構造体インスタンス#0がある。従って、図中、上から第二番目の奇数ラインの描画を行う際、ポリゴン#1,#2及び#0という順番で描画が行われる。このように、この奇数ラインでは、デプス値が大きい順に、描画が行われなくなる。

【0104】

ソートルール4を追加することにより、奇数フィールドを表示する場合、ポリゴン構造体インスタンス#0,#2,#1及び#3という順番に並べ替えが行われる。すると、奇数フィールドを表示する場合、例えば、図中、上から第一番目の奇数ラインの描画が終了した直後では、プリフェッチバッファ108の出口には、ポリゴン構造体インスタンス#2が、リサイクルバッファ110の出口には、ポリゴン構造体インスタンス#0がある。従って、図中、上から第二番目の奇数ラインの描画を行う際、ポリゴン#2,#1及び#0という順番で、デプス値の大きい順に描画処理が実行される。

【0105】

以上のことは、偶数フィールドを表示する際にも言える。

【0106】

さて、インタレーススキャンによる表示を行うためのソート処理においては、ソートを実行するタイミングによって、奇数フィールド用のソート処理と偶数フィールド用のソート処理を行うタイミングが異なる。そこで、本実施の形態では、モード1とモード2の二つのソートのモードが用意されている。これらを図面を用いて説明する。

【0107】

図9(a)は、インタレーススキャンによる表示を行う場合のソート処理をモード1のタイミングで行う場合の説明図、図9(b)は、インタレーススキャンによる表示を行う場合のソート処理をモード2のタイミングで行う場合の説明図、である。

【0108】

図9(a)に示すように、モード1では、YSU19は、偶数フィールドBが表示される前に表示される奇数フィールドAの表示中に、当該偶数フィールドBを表示するためのソートBを行う。従って、偶数フィールドBのための、ポリゴン構造体配列やスプライト構造体配列に代入する値(つまり各構造体インスタンスの値)の計算B及びソートBの双方の処理は、当該偶数フィールドBの1つ前に表示される奇数フィールドAの表示中に全て完了しなければならない。なぜなら、計算Bの結果に基づいて、ソートBが行われるからである。

【0109】

同様に、モード1では、YSU19は、奇数フィールドAが表示される前に表示される偶数フィールドBの表示中に、当該奇数フィールドAを表示するためのソートAを行う。従って、奇数フィールドAのための、ポリゴン構造体配列やスプライト構造体配列に代入する値の計算A及びソートAの双方の処理は、当該奇数フィールドAの1つ前に表示される偶数フィールドBの表示中に全て完了しなければならない。なぜなら、計算Aの結果に基づいて、ソートAが行われるからである。

【0110】

一方、モード2では、図9(b)に示すように、YSU19は、直前の垂直ブランキング期間中及び奇数フィールドAの表示中に、当該奇数フィールドAのためのソートAを実行する。奇数フィールドAのための計算Aは、当該奇数フィールドAの1つ前の偶数フィールドBの表示中に行われる。同様に、モード2では、YSU19は、直前の垂直ブランキング期間中及び偶数フィールドBの表示中に、当該偶数フィールドBのためのソートBを実行する。偶数フィールドBのための計算Bは、当該偶数フィールドBの1つ前の奇数フィールドAの表示中に行われる。

【0111】

従って、モード2では、奇数フィールドAの表示中に、奇数フィールドAのためのソートAと偶数フィールドBのための計算Bとを並列に実行することができ、また、偶数フィールドBの表示中に、偶数フィールドBのためのソートBと奇数フィールドAのための計算Aとを並列に実行することができる。その結果、計算A及びBのための期間を十分に確保できる。

【0112】

本実施の形態では、全構造体インスタンスのソートの完了を待つことなく、順位の高いものから構造体インスタンスが1つ確定するたびに、その都度、RPU9に構造体インスタンスが読み込まれ、描画処理を行うことができる機能が用意されている。具体的には、ソートされるポリゴン構造体配列のソート済みポリゴン構造体インスタンスが確定するたび、YSU19からRPU9にパルス信号PPL(後述)が伝達され、RPU9は、このパルス信号PPLの数をカウントし、カウント値を超えない範囲の数のポリゴン構造体インスタンスをメインRAM25から読み出す。また、スプライト構造体配列のソート及び読み出しについても、同様の機能が用意されている。このため、モード2のように、表示中のフィールドに対する各構造体インスタンスのソートを、直前の垂直ブランキング期間及びフィールド表示中に実行できる。

【0113】

順位の高いものから1つずつ構造体インスタンスを送り出すことができるソート技法の一例として、本実施の形態では、ヒープソートを採用している。また、ヒープソートを採用する他の利点として、ソート性能が安定している、すなわちソートに必要な時間にばらつきが少ないことが挙げられる。

【0114】

図10は、本発明の実施の形態によるマルチメディアプロセッサ1の内部構成を示すブロック図である。図10に示すように、このマルチメディアプロセッサは、外部メモリインタフェース3、DMAC(direct memory access controller)4、中央演算処理装置(以下、「CPU」と呼ぶ。)5、CPUローカルRAM7、レンダリングプロセッシングユニット(以下、「RPU」と呼ぶ。)9、カラーパレットRAM11、サウンドプロセシングユニット(以下、「SPU」と呼ぶ。)13、SPUローカルRAM15、ジオメトリエンジン(以下、「GE」と呼ぶ。)17、Yソーティングユニット(以下、「YSU」と呼ぶ。)19、外部インタフェースブロック21、メインRAMアクセスアービタ23、メインRAM25、I/Oバス27、ビデオDAC(digital to analog converter)29、オーディオDACブロック31、及びA/Dコンバータ(以下、「ADC」と呼ぶ。)33を具備する。メインRAM25及び外部メモリ50を区別して説明する必要がないときは、「メモリMEM」と表記する。

【0115】

CPU5は、メモリMEMに格納されたプログラムを実行して、各種演算やシステム全体の制御を行う。また、CPU5は、DMAC4にプログラム及びデータの転送要求を行うこともできるし、DMAC4を介さずに、外部メモリインタフェース3及び外部バス51を通じて、外部メモリ50から直接プログラムコードをフェッチし、外部メモリ50に直接データアクセスを行うこともできる。

【0116】

グラフィックス処理に関するCPU5の処理として、メモリMEMに格納されたプログラムを実行して、各オブジェクト及び各スプライトの拡大・縮小、回転、及び/又は平行移動のパラメータ、視点座標(カメラ座標)、並びに視線ベクトルの算出等を行う。ここで、1または複数のポリゴンから構成され、同じ拡大・縮小、回転、及び平行移動の変換が適用される単位を「オブジェクト」と呼ぶ。

【0117】

I/Oバス27は、CPU5をバスマスタとするシステム制御用のバスであり、バススレイブである各機能ユニット(外部メモリインタフェース3、DMAC4、RPU9、SPU13、GE17、YSU19、外部インタフェースブロック21、及びADC33)の制御レジスタ及びローカルRAM7,11,15へのアクセスに用いられる。このようにして、これらの機能ユニットは、I/Oバス27を通じて、CPU5により制御される。

【0118】

CPUローカルRAM7は、CPU5専用のRAMであり、サブルーチンコールや割り込み時におけるデータの退避などを行うためのスタック領域、及びCPU5のみが扱う変数の格納領域等として使用される。

【0119】

本発明の特徴の1つであるRPU9は、ポリゴン及びスプライトから構成される三次元イメージをリアルタイムに生成する。具体的には、RPU9は、YSU19によるソート済みの、ポリゴン構造体配列の各構造体インスタンス及びスプライト構造体配列の各構造体インスタンスを、メインRAM25から読み出し、上述したデプスコンパレータ112等による処理及び後述する様々な処理を実行して、スクリーンのスキャンに合わせて水平ラインごとにイメージを生成する。生成されたイメージは、コンポジットビデオ信号波形を示すデータストリームに変換され、ビデオDAC29に出力される。また、RPU9は、DMAC4に対して、ポリゴン及びスプライトのテクスチャパターンデータの取り込みのためのDMA転送要求を行う機能を有する。RPU9については、後で詳述する。

【0120】

テクスチャパターンデータとは、ポリゴンまたはスプライトに貼り付けられる2次元の画素配列データであり、各画素データは、カラーパレットRAM11のエントリを指定するための情報の一部である。このように、本実施の形態では、カラーの指定には、間接指定方式を採用する。以降、テクスチャパターンデータの画素を「テクセル」と呼称し、スクリーンに表示されるイメージを構成する画素を指す「ピクセル」とは区別して使用する。従って、テクスチャパターンデータは、テクセルデータの集合である。

【0121】

ビデオDAC29は、アナログのビデオ信号を生成するためのデジタル/アナログ変換器である。ビデオDAC29は、RPU9から入力されたデータストリームをアナログのコンポジットビデオ信号に変換し、ビデオ信号出力端子(図示せず)からテレビジョンモニタ等(図示せず)に出力する。

【0122】

カラーパレットRAM11は、本実施の形態では512色すなわち512エントリのカラーパレットからなる。RPU9は、テクスチャパターンデータに含まれるテクセルデータをカラーパレットのエントリを指定するインデックスの一部として、カラーパレットRAM11を参照し、テクスチャパターンデータを、カラーデータ(RGBのカラーコンポーネント)に変換する。

【0123】

SPU13は、PCM(pulse code modulation)波形データ(以下、「ウェーブデータ」と呼ぶ。)、アンプリチュードデータ、及びメインボリュームデータを生成する。具体的には、SPU13は、最大64チャンネル分のウェーブデータを生成して時分割多重化するとともに、最大64チャンネル分のエンベロープデータを生成してチャンネルボリュームデータと乗算し、アンプリチュードデータを時分割多重化する。そして、SPU13は、メインボリュームデータ、時分割多重化されたウェーブデータ、及び時分割多重化されたアンプリチュードデータを、オーディオDACブロック31に出力する。また、SPU13は、DMAC4に対して、ウェーブデータ及びエンベロープデータの取り込みのためのDMA転送要求を行う機能を有する。

【0124】

オーディオDACブロック31は、SPU13から入力されたウェーブデータ、アンプリチュードデータ、及びメインボリュームデータをそれぞれアナログ信号に変換し、結果をアナログ乗算して、アナログオーディオ信号を生成する。このアナログオーディオ信号は、オーディオ信号出力端子(図示せず)からテレビジョンモニタ等(図示せず)のオーディオ入力端子(図示せず)に出力される。

【0125】

SPUローカルRAM15は、SPU13がウェーブ再生及びエンベロープ生成を行う際に用いるパラメータ(例えば、ウェーブデータやエンベロープデータの格納アドレスやピッチ情報など)を格納する。

【0126】

GE17は、三次元イメージを表示するための幾何演算を実行する。具体的には、GE17は、行列積、ベクトルアフィン変換、ベクトル直交変換、透視投影変換、頂点明度/ポリゴン明度計算(ベクトル内積)、及びポリゴン裏面カリング処理(ベクトル外積)などの演算を実行する。

【0127】

本発明の特徴の1つであるYSU19は、メインRAM25に格納されているポリゴン構造体配列の各構造体インスタンス及びスプライト構造体配列の各構造体インスタンスを、ソートルール1〜4に従ってソートする。この場合、ポリゴン構造体配列とスプライト構造体配列とで、別個にソートが行われる。

【0128】

外部メモリインタフェース3は、外部バス51を介して、外部メモリ50からのデータの読み出し、及び外部メモリ50へのデータの書き込みを司る。この場合、外部メモリインタフェース3は、図示しないEBI優先順位テーブルに従って、CPU5及びDMAC4からの外部バスアクセス要求要因(外部バス51へのアクセスを要求する要因)を調停して、いずれか1つの外部バスアクセス要求要因を選択する。そして、選択した外部バスアクセス要求要因に対して外部バス51へのアクセスを許可する。EBI優先順位テーブルは、CPU5からの複数種類の外部バスアクセス要求要因及びDMAC4からの外部バスアクセス要求要因の優先順位を定めたテーブルである。

【0129】

外部バスアクセス要求要因として、CPU5に含まれる図示しないIPL(initial program loader)によるブロック転送要求、CPU5によるデータアクセス要求、CPU5による命令フェッチ要求、及びDMAC4によるDMA要求がある。

【0130】

DMAC4は、メインRAM25と、外部バス51に接続された外部メモリ50と、の間でDMA転送を行う。この場合、DMAC4は、図示しないDMA優先順位テーブルに従って、CPU5、RPU9、及びSPU13からのDMA転送要求要因(DMA転送を要求する要因)を調停して、いずれか1つのDMA転送要求要因を選択する。そして、外部メモリインタフェース3に対して、DMA要求を行う。DMA優先順位テーブルは、CPU5、RPU9、及びSPU13からのDMA要求要因の優先順位を定めたテーブルである。

【0131】

SPU13のDMA要求要因として、(1)ウェーブデータをウェーブバッファに転送すること、(2)エンベロープデータをエンベロープバッファに転送すること、がある。ウェーブバッファ及びエンベロープバッファは、それぞれメインRAM25上に設定されるウェーブデータ及びエンベロープデータのテンポラリ格納領域である。なお、SPU13の2つのDMA要求要因間の調停は、SPU13内のハードウェア(図示せず)で行われ、DMAC4は関知しない。

【0132】

RPU9のDMA要求要因として、テクスチャパターンデータをテクスチャバッファに転送すること、がある。テクスチャバッファは、メインRAM25上に設定されるテクスチャパターンデータのテンポラリ格納領域である。

【0133】

CPU5のDMA要求要因として、(1)仮想記憶管理においてページミスが発生した場合のページ転送、(2)アプリケーションプログラム等が要求するデータ転送、がある。なお、CPU5内で複数のDMA転送要求が同時に発生した場合は、その調停はCPU5で実行されるソフトウェアにて行われ、DMAC4は関知しない。

【0134】

DMAC4は、LZ77アルゴリズムに基づくデータ伸張機能を備えており、CPU5によるDMA転送要求に対して、外部メモリ50に格納された圧縮データを伸張しながらDMA転送することが可能である。

【0135】

外部インタフェースブロック21は、周辺装置54とのインタフェースであり、24チャンネルのプログラマブルなデジタル入出力(I/O)ポートを含む。24チャンネルのI/Oポートの各々は、4チャンネル分のマウスインタフェース機能、4チャンネル分のライトガンインタフェース機能、2チャンネル分の汎用タイマ/カウンタ、1チャンネル分の調歩同期式シリアルインタフェース機能、1チャンネル分の汎用パラレル/シリアル変換ポート機能のうち1または複数に内部接続されている。

【0136】

ADC33は、4チャンネルのアナログ入力ポートに接続され、これらを介して、アナログ入力装置52から入力されたアナログ信号をデジタル信号に変換する。例えば、マイク音声等のアナログ入力信号をサンプリングしてデジタルデータに変換する。

【0137】

メインRAMアクセスアービタ23は、機能ユニット(CPU5、RPU9、GE17、YSU19、DMAC4、及び外部インタフェースブロック21(汎用パラレル/シリアル変換ポート)からのメインRAM25へのアクセス要求を調停して、いずれかの機能ユニットにアクセス許可を出す。

【0138】

メインRAM25は、CPU5のワーク領域、変数格納領域、および仮想記憶管理領域等として利用される。また、メインRAM25は、CPU5が他の機能ユニットに受け渡すデータの格納領域、RPU9及びSPU13が外部メモリ50からDMAによって取得したデータの格納領域、GE17及びYSU19の入力データ及び出力データの格納領域等としても使用される。

【0139】

外部バス51は、外部メモリ50にアクセスするためのバスである。CPU5およびDMAC4から、外部メモリインタフェース3を介してアクセスされる。外部バス51のアドレスバスは、30ビットから成り、最大で1Gバイト(=8Gビット)の外部メモリ50を接続することができる。外部バス51のデータバスは、16ビットから成り、8ビット又は16ビットのデータバス幅を持つ外部メモリ50を接続できる。異なるデータバス幅を持つ外部メモリを同時に接続可能であり、アクセスする外部メモリによってデータバス幅を自動的に切り替える機能が備えられる。

【0140】

次に、マルチメディアプロセッサ1によるグラフィックス処理の概要を説明する。

【0141】

図11は、図10のマルチメディアプロセッサ1によるグラフィックス処理の流れの概要を示すフローチャートである。図11に示すように、ステップS1にて、CPU5は、各オブジェクト(1または複数のポリゴンから構成され、同じ拡大・縮小、回転、及び平行移動の変換が適用される単位)及び各スプライトの拡大・縮小、回転、及び平行移動のパラメータを算出する。算出されたパラメータから、各オブジェクト及び各スプライトに対し、拡大・縮小、回転、及び平行移動のための変換行列が生成される。これらの変換行列は、各オブジェクト及び各スプライトのローカルな座標系(ローカル座標系)から、全てのオブジェクト及び全てのスプライトを統一の座標系で表現する直交座標系(ワールド座標系)への変換に用いられる。

【0142】

また、CPU5は、視点(カメラ)座標、対象点座標、及び視線ベクトルの更新等を行う。これらのパラメータから、ワールド座標系から視点を中心とした直交座標系(ビュー座標系)への変換行列が生成される。

【0143】

ステップS2にて、GE17は、各オブジェクト及び各スプライトに対し、拡大・縮小、回転、及び平行移動のための変換行列が複数存在する場合、それらの変換行列の行列積を求めることにより、複数の変換行列を単一の変換行列に合成する。さらに、GE17は、合成された変換行列と、座標系変換のための変換行列と、の行列積を求めて、オブジェクト頂点座標配列、オブジェクト法線ベクトル配列、及びスプライト座標を変換するための変換行列をそれぞれ合成する。

【0144】

ステップS3にて、GE17は、合成された変換行列を用い、オブジェクト頂点座標配列、オブジェクト法線ベクトル配列、及びスプライト座標の幾何変換を行う。また、GE17は、変換後のオブジェクト法線ベクトル配列と光源ベクトルとの内積を演算し、オブジェクトの各頂点または面(ポリゴン)の明度を算出する。このような幾何変換及びライティングの結果は、ポリゴン構造体配列及びスプライト構造体配列に格納される。

【0145】

ステップS4にて、RPU9による描画処理が行われる前に、YSU19は、ソートルール1〜4に従って、ポリゴン構造体インスタンスおよびスプライト構造体インスタンスをソートする。

【0146】

ステップS5にて、RPU9は、YSU19によるソート後のポリゴン構造体インスタンスおよびスプライト構造体インスタンスを読み出すとともに、テクスチャマッピングモードのポリゴン及びスプライトの属性を示すテクスチャアトリビュート構造体インスタンスを読み出しつつ、各水平表示ラインのピクセルデータ列を生成する。また、テクスチャマッピングモードのポリゴン及びスプライトのピクセルデータ列生成には、これらに貼り付けるテクスチャパターンデータを、外部メモリ50から読み出すことが必要とされる。このようなピクセルデータ列生成処理を「ラスタライジング」と呼ぶ。

【0147】

本実施の形態では、ポリゴンの描画モードとして、テクスチャマッピングを用いて描画を行うテクスチャマッピングモードと、グーローシェーディングを用いてポリゴンの描画を行うグーローシェーディングモードと、を実装している。テクスチャマッピングは、二次元の格子状に並べられたテクセルのパターンをポリゴン表面に貼り付ける描画手法である。グーローシェーディングは、少ない個数のポリゴンで擬似的に滑らかな曲面を表現するために用いられるスムーズシェーディングの一種である。グーローシェーディングでは、独立に指定されたポリゴンの頂点色を直線補完することでポリゴン内の各ピクセルの描画色を求める。

【0148】

また、RPU9は、シザリングを実行する。シザリングとは、ポリゴン及びスプライトのピクセルデータ列生成時に、指定されたビューポートの領域からはみ出している部分を切り取って表示しないようにする処理である。生成されたピクセルデータ列は、RPU9内のラインバッファLB1あるいはLB2に書き込まれるが、この際に書き込みピクセルが半透明色に設定されている場合、ラインバッファ内のピクセルのカラーと書き込みピクセルのカラーを混ぜ合わせるカラーブレンディングが行われる。

【0149】

ステップS6にて、RPU9は、ラインバッファLB1あるいはLB2から表示対象の各ピクセルの情報を読み出し、同期信号及びカラーバースト信号等を追加してコンポジットビデオ信号のデジタルデータストリームを生成する。生成されたデータストリームは、ビデオDAC29に入力され、ビデオDAC29からは、アナログのコンポジットビデオ信号が出力される。

【0150】

次に、RPU9の詳細を説明する。

【0151】

図12は、図10のRPU9の内部構成を示すブロック図である。図12に示すように、RPU9は、RPU内メインRAMアクセスアービタ100、ポリゴンプリフェッチャ102、スプライトプリフェッチャ104、マージソータ106、プリフェッチバッファ108、リサイクルバッファ110、デプスコンパレータ112、バーテックスソータ114、バーテックスエキスパンダ116、スライサ118、ピクセルステッパ120、ピクセルディザ122、テクセルマッパ124、テクスチャキャッシュブロック126、バイリニアフィルタ130、カラーブレンダ132、ラインバッファブロック134、ビデオエンコーダ136、ビデオタイミングジェネレータ138、メモリマネージャ140、及びDMACインタフェース142を含む。ラインバッファブロック134は、各々スクリーンの1水平ラインに対応するラインバッファLB1及びLB2を含む。なお、図12では、説明の便宜のため、カラーパレットRAM11をRPU9に含めて記載している。

【0152】

RPU内メインRAMアクセスアービタ100は、ポリゴンプリフェッチャ102、スプライトプリフェッチャ104、及びメモリマネージャ140からメインRAM25へのアクセス要求を調停して、いずれかにアクセス要求の許可を出す。許可されたアクセス要求は、メインRAMアクセスアービタ23に出力され、マルチメディアプロセッサ1内の他の機能ユニットからのアクセス要求との間で調停が行われる。

【0153】

ポリゴンプリフェッチャ102は、メインRAM25から、YSU19によるソート後の各ポリゴン構造体インスタンスを取り込む。ポリゴンプリフェッチャ102には、YSU19から、パルスPPLが入力される。YSU19は、ソートにおいて順位の高いものからポリゴン構造体インスタンスが1つ確定するたびに、パルスPPLを出力する。従って、ポリゴンプリフェッチャ102は、ポリゴン構造体配列の全ポリゴン構造体インスタンスのうち、いくつのポリゴン構造体インスタンスのソートが完了したかを知ることができる。

【0154】

このため、ポリゴンプリフェッチャ102は、全ポリゴン構造体インスタンスのソートの完了を待つことなく、順位の高いものからポリゴン構造体インスタンスが1つ確定するたびに、その都度、ポリゴン構造体インスタンスを取得できる。その結果、フレームの表示中に、当該フレームのためのポリゴン構造体インスタンスのソートを行うことができる。また、インタレーススキャンによる表示を行う場合にも、前述のモード2(図9(b)参照)を用いることにより、フィールドの表示中に当該フィールドのためのソートを行っても、正しい描画結果が得られる。なお、ポリゴンプリフェッチャ102は、ビデオタイミングジェネレータ138からの垂直走査カウント信号VCから、フレームおよびフィールドの切り替わりを知ることができる。

【0155】

スプライトプリフェッチャ104は、メインRAM25から、YSU19によるソート後の各スプライト構造体インスタンスを取り込む。スプライトプリフェッチャ104には、YSU19から、パルスSPLが入力される。YSU19は、ソートにおいて順位の高いものからスプライト構造体インスタンスが1つ確定するたびに、パルスSPLを出力する。従って、スプライトプリフェッチャ104は、スプライト構造体配列の全スプライト構造体インスタンスのうち、いくつのスプライト構造体インスタンスのソートが完了したかを知ることができる。

【0156】

このため、スプライトプリフェッチャ104は、全スプライト構造体インスタンスのソートの完了を待つことなく、順位の高いものからスプライト構造体インスタンスが1つ確定するたびに、その都度、スプライト構造体インスタンスを取得できる。その結果、フレームの表示中に、当該フレームのためのスプライト構造体インスタンスのソートを行うことができる。また、インタレーススキャンによる表示を行う場合にも、前述のモード2(図9(b)参照)を用いることにより、フィールドの表示中に当該フィールドのためのソートを行っても、正しい描画結果が得られる。なお、スプライトプリフェッチャ104は、ビデオタイミングジェネレータ138からの垂直走査カウント信号VCから、フレームおよびフィールドの切り替わりを知ることができる。

【0157】

ここで、ポリゴン構造体、テクスチャアトリビュート構造体、およびスプライト構造体の構成について詳しく説明する。

【0158】

図13は、テクスチャマッピングモードのポリゴン構造体の例示図である。図13に示すように、本実施の形態では、このポリゴン構造体は、128ビットで構成されている。このポリゴン構造体のメンバTypeは、ポリゴンの描画モードを示し、テクスチャマッピングモードのポリゴンに対しては「0」が設定される。メンバAy,Ax,By,Bx,Cy及びCxは、それぞれ、ポリゴンの、頂点AのY座標、頂点AのX座標、頂点BのY座標、頂点BのX座標、頂点CのY座標、及び頂点CのX座標を示す。これらのY座標及びX座標は、スクリーン座標系の値である。

【0159】

メンバBw,Cw,Light及びTsegmentは、それぞれ、ポリゴンの、頂点Bのパースペクティブコレクト用パラメータ(=Az/Bz)、頂点Cのパースペクティブコレクト用パラメータ(=Az/Cz)、明度、及びテクスチャパターンデータの格納位置情報を示す。

【0160】

メンバTattribute,Map,Filter,Depth及びViewportは、それぞれ、テクスチャアトリビュート構造体のインデックス、テクスチャパターンデータのフォーマット種別、バイリニアフィルタリングあるいはニアレストネイバーのいずれかを示すフィルタリングモード、デプス値、及びシザリングのビューポート指定情報を示す。バイリニアフィルタリング及びニアレストネイバーについては後述する。

【0161】

以上が、テクスチャマッピングモードのポリゴン構造体の各メンバの内容であり、1つのポリゴン構造体のインスタンス(ポリゴン構造体に代入された値)により1つのポリゴンが定義される。

【0162】

図14は、テクスチャアトリビュート構造体の例示図である。図14に示すように、本実施の形態では、このテクスチャアトリビュート構造体は、32ビットで構成されている。このテクスチャアトリビュート構造体のメンバWidth,Height,M,N,Bit及びPaletteは、それぞれ、テクスチャの幅(単位:テクセル数)より「1」小さい値、テクスチャの高さ(単位:テクセル数)より「1」小さい値、「Width」の上位からのマスクビット数、「Height」の上位からのマスクビット数、カラーモード(1ピクセル当りのビット数−1)、及びパレットブロックナンバを示す。カラーパレットの512色のエントリは、選択されたカラーモードに応じて複数のブロックに分割されており、メンバPaletteにより、使用するパレットブロックが示される。

【0163】

テクスチャアトリビュート構造体のインスタンスは、描画ポリゴン毎に1つずつ用意されるものではなく、64個のテクスチャアトリビュート構造体インスタンスが、テクスチャマッピングモードの全ポリゴン構造体インスタンス及び全スプライト構造体インスタンスで共有される。

【0164】

図15は、グーローシェーディングモードのポリゴン構造体の例示図である。図15に示すように、本実施の形態では、グーローシェーディングモードのポリゴン構造体は、128ビットで構成されており、メンバAx(11ビット),Ay(10ビット),Bx(11ビット),By(10ビット),Cx(11ビット),Cy(10ビット),Ac(15ビット),Bc(15ビット),Cc(15ビット),Depth(12ビット),Viewport(2ビット)及びNalpha(3ビット)を有する。

【0165】

メンバTypeは、ポリゴンの描画モードを示し、グーローシェーディングモードのポリゴンに対しては「1」が設定される。メンバAy,Ax,By,Bx,Cy及びCxは、それぞれ、ポリゴンの、頂点AのY座標、頂点AのX座標、頂点BのY座標、頂点BのX座標、頂点CのY座標、及び頂点CのX座標を示す。これらのY座標及びX座標は、スクリーン座標系の値である。

【0166】

メンバAc,Bc,及びCcは、それぞれ、ポリゴンの、頂点Aのカラーデータ(RGB各5ビット)、頂点Bのカラーデータ(RGB各5ビット)、及び頂点Cのカラーデータ(RGB各5ビット)を示す。

【0167】

メンバDepth,Viewport及びNalphaは、それぞれ、デプス値、シザリングのビューポート指定情報、及びアルファブレンディングで使用する(1−α)を示す。(1−α)は透明度を示し、「000(二進数)」が透明度0%、すなわち完全不透明を表し、「111(二進数)」が透明度87.5%を表す。

【0168】

以上が、グーローシェーディングモードのポリゴン構造体の各メンバの内容であり、1つのポリゴン構造体のインスタンス(ポリゴン構造体に代入された値)により1つのポリゴンが定義される。

【0169】

図16(a)は、シザリングディセーブル時のスプライト構造体の例示図、図16(b)は、シザリングイネーブル時のスプライト構造体の例示図である。図16(a)に示すように、本実施の形態では、シザリングディセーブル時のスプライト構造体は、64ビットで構成されている。このスプライト構造体のメンバAx及びAyは、それぞれ、スプライトの左上のX座標及びY座標を示す。これらのY座標及びX座標は、スクリーン座標系の値である。

【0170】

メンバDepth,Filter及びTattributeは、それぞれ、デプス値、フィルタリングモード(バイリニアフィルタリングあるいはニアレストネイバー)、及びテクスチャアトリビュート構造体のインデックスを示す。メンバZoomX,ZoomY及びTsegmentは、それぞれ、X軸方向のスプライト拡大率(拡縮率)、Y軸方向のスプライト拡大率(拡縮率)、及びテクスチャパターンデータの格納位置情報を示す。

【0171】

図16(b)に示すように、本実施の形態では、シザリングイネーブル時のスプライト構造体は、64ビットで構成されている。このスプライト構造体のメンバAx及びAyは、それぞれ、スプライトの左上のX座標及びY座標を示す。これらのY座標及びX座標は、スクリーン座標系の値である。

【0172】

メンバDepth,Scissor,Viewport,Filter及びTattributeは、それぞれ、デプス値、シザリング適用フラグ、シザリングのビューポート指定情報、フィルタリングモード(バイリニアフィルタリングあるいはニアレストネイバー)、及びテクスチャアトリビュート構造体のインデックスを示す。メンバZoomX,ZoomY及びTsegmentは、それぞれ、X軸方向のスプライト拡大率(拡縮率)、Y軸方向のスプライト拡大率(拡縮率)、及びテクスチャパターンデータの格納位置情報を示す。

【0173】

シザリングイネーブル時のスプライト構造体においては、シザリングディセーブル時のスプライト構造体に比べ、X座標及びY座標のビット数がそれぞれ1ビット少ない。シザリングイネーブル時にスプライトがスクリーンに配置される際には、後述のバーテックスエキスパンダ116によって、X座標に512ピクセル分のオフセット、Y座標に256ピクセル分のオフセットが加えられる。また、デプス値のビット数も1ビット少ないが、シザリングイネーブル時には、後述のテクセルマッパ124によって、構造体に格納されているデプス値のLSB側に1ビットの「0」が付加され、シザリングディセーブル時と同様に8ビットのデプス値として扱われる。

【0174】

以上が、シザリングディセーブル時及びシザリングイネーブル時のスプライト構造体の各メンバの内容であり、1つのスプライト構造体のインスタンス(スプライト構造体に代入された値)により1つのスプライトが定義される。スプライトのテクスチャアトリビュート構造体の構成は、図14のポリゴンのテクスチャアトリビュート構造体の構成と同じである。テクスチャアトリビュート構造体のインスタンスは、描画スプライト毎に1つずつ用意されるものではなく、64個のテクスチャアトリビュート構造体インスタンスが、テクスチャマッピングモードの全ポリゴン構造体インスタンス及び全スプライト構造体インスタンスで共有される。

【0175】

図12に戻って、マージソータ106は、ポリゴンプリフェッチャ102及びスプライトプリフェッチャ104から、それぞれ、ポリゴン構造体インスタンス及びそれに付随するテクスチャアトリビュート構造体インスタンス、並びに、スプライト構造体インスタンス及びそれに付随するテクスチャアトリビュート構造体インスタンスを受け取り、上述したYSU19によるソートルール1〜4と同じソートルール1〜4に従って、マージソートを実行し、結果をプリフェッチバッファ108に送出する。

【0176】

つまり、マージソータ106は、ソートルール1〜4に従って、ポリゴン構造体インスタンスを選択した場合、テクスチャマッピングモードのポリゴンについては、ポリゴン構造体インスタンスをポリゴン/スプライトデータPSD(128ビット)として、それに付随するテクスチャアトリビュート構造体インスタンスをテクスチャアトリビュート構造体インスタンスTAI(32ビット)として、プリフェッチバッファ108に出力する。

【0177】

また、マージソータ106は、ソートルール1〜4に従って、ポリゴン構造体インスタンスを選択した場合、グーローシェーディングモードのポリゴンについては、ポリゴン構造体インスタンスをポリゴン/スプライトデータPSD(128ビット)として、テクスチャアトリビュート構造体インスタンスTAI(32ビット)の全ビットを「0」として、プリフェッチバッファ108に出力する。

【0178】

一方、マージソータ106は、ソートルール1〜4に従って、スプライト構造体インスタンスを選択した場合、スプライト構造体インスタンスをポリゴン/スプライトデータPSD(128ビット)として、それに付随するテクスチャアトリビュート構造体インスタンスをテクスチャアトリビュート構造体インスタンスTAI(32ビット)として、プリフェッチバッファ108に出力する。ただし、この場合のポリゴン/スプライトデータPSDは、有効データがLSBから詰められ、上位64ビットは「0」を示す。

【0179】

上で詳述したプリフェッチバッファ108は、マージソータ106から、マージソート後の構造体インスタンス(つまり、ポリゴン/スプライトデータPSD及びテクスチャアトリビュート構造体インスタンスTAI)を順次読み込み、読み込んだ順番で構造体インスタンスを出力するFIFO(first−in first−out)構造のバッファである。つまり、プリフェッチバッファ108には、マージソータ106により並べ替えられた順番で構造インスタンスが格納される。そして、格納された構造インスタンスは、対応するポリゴンあるいはスプライトの表示のための描画サイクルにおいて、格納された順番で出力される。なお、プリフェッチバッファ108は、ビデオタイミングジェネレータ138からの垂直走査カウント信号VCから、描画中の水平ラインを知ることができる。つまり、描画サイクルの切り替わりを知ることができる。本実施の形態では、例えば、プリフェッチバッファ108は、物理的にはリサイクルバッファ110とバッファを共有することが可能であり、リサイクルバッファ110のエントリ数を含め、(128ビット+32ビット)×128エントリとする。

【0180】

上で詳述したリサイクルバッファ110は、次の描画サイクルでも使用される(つまり、再利用できる)構造体インスタンス(つまり、ポリゴン/スプライトデータPSD及びテクスチャアトリビュート構造体インスタンスTAI)を、スライサ118から受け取って格納するFIFO構造のバッファである。従って、リサイクルバッファ110に格納された構造体インスタンスは、次の描画サイクルで使用される。本実施の形態では、例えば、リサイクルバッファ110は、物理的にはプリフェッチバッファ108とバッファを共有することが可能であり、プリフェッチバッファ108のエントリ数を含め、(128ビット+32ビット)×128エントリとする。

【0181】

上で詳述したデプスコンパレータ112は、プリフェッチバッファ108の先頭の構造体インスタンスに含まれるデプス値と、リサイクルバッファ110の先頭の構造体インスタンスに含まれるデプス値と、を比較して、より大きなデプス値を持つ(つまり、より奥に表示されるべき)構造体インスタンスを選択して、後段に出力する。この場合、デプスコンパレータ112は、選択した構造体インスタンスがポリゴン構造体インスタンスの場合は、バーテックスソータ114へ出力し、スプライト構造体インスタンスの場合は、バーテックスエキスパンダ116に出力する。また、デプスコンパレータ112は、選択した構造体インスタンスをスライサ118に出力する。なお、デプスコンパレータ112は、ビデオタイミングジェネレータ138からの垂直走査カウント信号VCから、描画中の水平ラインを知ることができる。つまり、描画サイクルの切り替わりを知ることができる。

【0182】

バーテックスエキスパンダ116は、受け取ったスプライト構造体インスタンスに含まれる、スプライトの左上の頂点座標(Ax,Ay)、Y軸方向の拡大率ZoomY、及びX軸方向の拡大率ZoomX、並びに、当該スプライト構造体インスタンスに付随するテクスチャアトリビュート構造体インスタンスに含まれる、テクスチャの幅より「1」小さい値Width及び高さより「1」小さい値Heightに基づいて、当該スプライトの頂点の座標(スクリーン座標系におけるXY座標およびUV座標系におけるUV座標)を算出し、ポリゴン/スプライト共通データCI(208ビット)としてスライサ118へ出力する。ただし、ポリゴン/スプライト共通データCIの後述のフィールドWG*(*=0,1,2)は、常に「0x0040」(=1.0)として出力される。バーテックスエキスパンダ116が出力するポリゴン/スプライト共通データCIの構造(形式)は、バーテックスソータ114が出力するポリゴン/スプライト共通データCIの構造(形式)と同じである。

【0183】

バーテックスエキスパンダ116は、受け取ったスプライト構造体インスタンスに含まれる、スプライトの左上の頂点座標(Ax,Ay)、Y軸方向の拡大率ZoomY、及びX軸方向の拡大率ZoomX、並びに、当該スプライト構造体インスタンスに付随するテクスチャアトリビュート構造体インスタンスに含まれる、テクスチャの幅より「1」小さい値Width及び高さより「1」小さい値Heightに基づいて、当該スプライトの頂点の座標(スクリーン座標系におけるXY座標およびUV座標系におけるUV座標)を算出し、ポリゴン/スプライト共通データCI(208ビット)としてスライサ118へ出力する。ただし、ポリゴン/スプライト共通データCIの後述のフィールドWG*(*=0,1,2)は、常に「0x0040」(=1.0)として出力される。バーテックスエキスパンダ116が出力するポリゴン/スプライト共通データCIの構造(形式)は、バーテックスソータ114が出力するポリゴン/スプライト共通データCIの構造(形式)と同じである。

【0184】

ここで、スクリーン座標系は上述の通りである。UV座標系は、テクスチャを構成する各テクセルが、ポリゴンあるいはスプライトにマッピングされる態様で配置される二次元直交座標系である。

【0185】

バーテックスソータ114は、受け取ったポリゴン構造体インスタンス及びそれに付随するテクスチャアトリビュート構造体インスタンスから、ポリゴンの各頂点のパラメータ(XYUV座標、パースペクティブコレクト用パラメータ、及びカラーデータ)を取得及び算出し、各頂点のパラメータをY座標が小さい順に並べ替えて、ポリゴン/スプライト共通データCIとしてスライサ118へ出力する。頂点の出現順は、早いほうから頂点0、頂点1、及び頂点2とする。

【0186】

つまり、テクスチャマッピングモードでは、バーテックスソータ114は、演算結果、つまり、各頂点0〜2のパラメータ(XY座標、パースペクティブコレクト後のUV座標、及びパースペクティブコレクト用パラメータ)を、ポリゴン/スプライト共通データCIとして、スライサ118に出力する。

【0187】

また、グーローシェーディングモードでは、バーテックスソータ114は、演算結果、つまり、各頂点0〜2のパラメータ(XY座標、及びカラーデータ)を、ポリゴン/スプライト共通データCIとして、スライサ118に出力する。

【0188】

バーテックスソータ114が出力するポリゴン/スプライト共通データCIの構成(形式)は、バーテックスエキスパンダ116が出力するポリゴン/スプライト共通データCIの構成(形式)と同じである。

【0189】

バーテックスソータ114及びバーテックスエキスパンダ116が出力するポリゴン/スプライト共通データCIの構成を説明する。ポリゴン/スプライト共通データCIは、フィールドF(1ビット),WG*(各16ビット),VR*(各16ビット),UB*(各16ビット),Y*(各10ビット)及びX*(各11ビット)からなる(計208ビット)。*=0,1,2であり、頂点を示す。

【0190】

フィールドFは、ポリゴン/スプライト共通データCIが、ポリゴンについてのものであるか、スプライトについてのものであるか、を示すフラグフィールドである。従って、バーテックスソータ114は、ポリゴンを示す「1」をフィールドFに格納する。一方、バーテックスエキスパンダ116は、スプライトを示す「0」をフィールドFに格納する。

【0191】

バーテックスエキスパンダ116から出力されるポリゴン/スプライト共通データCIでは、フィールドVR*,UB*,Y*及びX*は、それぞれ頂点*のV座標、U座標、Y座標、及びX座標である。この場合、フィールドWG*には、「0x0040」(=1.0)が格納される。上述したように、頂点*の出現順は、早いほうから頂点0、頂点1、及び頂点2である。

【0192】

バーテックスソータ114から出力される、テクスチャマッピングの対象であるポリゴン/スプライト共通データCIでは、フィールドWG*,VR*,UB*,Y*及びX*は、それぞれ頂点*のパースペクティブコレクト用パラメータ、パースペクティブコレクト済みV座標、パースペクティブコレクト済みU座標、Y座標、及びX座標である。

【0193】

バーテックスソータ114から出力される、グーローシェーディングの対象であるポリゴン/スプライト共通データCIでは、フィールドWG*,VR*,UB*,Y*及びX*は、それぞれ頂点*の緑成分、赤成分、青成分、Y座標、及びX座標である。

【0194】

図17〜図19を用いてスライサ118の動作を説明する。図17は、スライサ118による、グーローシェーディングモードのポリゴンに対する処理の説明図である。図17に示すように、スライサ118は、与えられたポリゴン/スプライト共通データCIにより定義されるポリゴン(三角形)と、描画対象の水平ラインと、の交点のXY座標(Xs,Ys)及び(Xe,Ye)を求める。ここで、ポリゴンに対しては、描画対象の水平ラインと交わらない辺が存在する側の交点を終端(Xe,Ye)とし、当該辺が存在しない側の交点を始端(Xs,Ys)とする。

【0195】

そして、スライサ118は、描画Y座標YrがY0≦Yr<Y1の範囲では、頂点0のRGB値(VR0,WG0,UB0)及び頂点2のRGB値(VR2,WG2,UB2)に基づいて、直線補間により、交点始端のRGB値(Rs,Gs,Bs)を算出するとともに、頂点0のRGB値(VR0,WG0,UB0)及び頂点1のRGB値(VR1,WG1,UB1)に基づいて、直線補間により、交点終端のRGB値(Re,Ge,Be)を算出する。また、スライサ118は、描画Y座標YrがY1≦Yr≦Y2の範囲では、頂点0のRGB値(VR0,WG0,UB0)及び頂点2のRGB値(VR2,WG2,UB2)に基づいて、直線補間により、交点始端のRGB値(Rs,Gs,Bs)を算出するとともに、頂点1のRGB値(VR1,WG1,UB1)及び頂点2のRGB値(VR2,WG2,UB2)に基づいて、直線補間により、交点終端のRGB値(Re,Ge,Be)を算出する。

【0196】

そして、スライサ118は、ΔR、ΔG、ΔB及びΔXgを算出する。ここで、ΔR、ΔG、ΔBは、描画対象の水平ラインにおけるΔXgあたりのR、G、Bそれぞれの変化量であり、ΔXgは、描画対象の水平ラインにおける1ピクセルあたりのX座標の変化量である。ΔXgは、「+1」または「−1」のいずれかとなる。

【0197】

ΔR=(Re−Rs)/(Xe−Xs)

ΔG=(Ge−Gs)/(Xe−Xs)

ΔB=(Be−Bs)/(Xe−Xs)

ΔXg=(Xe−Xs)/│Xe−Xs│

【0198】

スライサ118は、デプスコンパレータ112から受け取った構造体インスタンスと共に、算出したXs,Rs,Gs,Bs,Xe,ΔR,ΔG,ΔB及びΔXgを、ピクセルステッパ120へ送出する。また、スライサ118は、バーテックスソータ114から受け取ったポリゴン/スプライト共通データCIが、次の描画サイクルでも使用される場合は、リサイクルバッファ110に、デプスコンパレータ112から受け取った構造体インスタンスを書き込む。なお、ビデオタイミングジェネレータ138からの垂直走査カウント信号VC及びポリゴンの頂点座標から、次の描画サイクルでの使用の有無を知ることができる。

【0199】

図18は、スライサ118による、テクスチャマッピングモードのポリゴンに対する処理の説明図である。図18に示すように、スライサ118は、与えられたポリゴン/スプライト共通データCIにより定義されるポリゴン(三角形)と、描画対象の水平ラインと、の交点座標である始端(Xs,Ys)及び終端(Xe,Ye)を求める。この点は、グーローシェーディングモードのポリゴンに対する処理と同じである。

【0200】

ここで、パースペクティブコレクト機能について説明する。透視投影変換された三次元イメージを表現するテクスチャマッピングにおいて、スクリーン上の描画ピクセルに対応するテクセルを、ポリゴンの各頂点座標に対応する、UV空間のテクスチャの各頂点座標の単なる線形補完によって求めると、マッピングされたイメージが歪んでしまうことがある。この歪みを解消するのがパースペクティブコレクト機能であり、具体的には、以下のような処理が行われる。

【0201】

ポリゴンの各頂点A,B,CをUV空間へ写像したときの座標を、(Au,Av),(Bu,Bv),(Cu,Cv)とする。また、各頂点A,B,Cのビュー座標を(Ax,Ay,Az),(Bx,By,Bz),(Cx,Cy,Cz)とする。そして、(Au/Az,Av/Az,1/Az),(Bu/Bz,Bv/Bz,1/Bz),(Cu/Cz,Cv/Cz,1/Cz)の線形補間によって求められた値(u/z,v/z,1/z)のu/zに1/zの逆数を乗じた値uおよびv/zに1/zの逆数を乗じた値v、つまり(u,v)をテクセル座標(U,V)としてテクセルデータを取得することにより、透視投影変換後の正確なテクスチャマッピングを実現する。ここで、ビュー座標とは、ビュー座標系の座標である。ビュー座標系は、XYZの三軸から成る三次元直交座標系であり、視点を原点とし、視線をZ軸の正とする。

【0202】

本実施の形態では、1/Az,1/Bz,1/Czを頂点毎に設定する代りに、それぞれの値にAzを掛け合わせた値、すなわち、Az/Az(=Aw),Az/Bz(=Bw),Az/Cz(=Cw)をポリゴン構造体に設定する(図13参照)。但し、頂点Aに対するパラメータAwは常に「1」となるため、ポリゴン構造体には設定しない。

【0203】

従って、本実施の形態では、(Au・Aw,Av・Aw,Aw),(Bu・Bw,Bv・Bw,Bw),(Cu・Cw,Cv・Cw,Cw)の線形補間によって求められた値(u・w,v・w,w)のu・wに1/wを乗じた値uおよびv・wに1/wを乗じた値v、つまり(u,v)をテクセル座標(U,V)としてテクセルデータを取得することにより、透視投影変換後の正確なテクスチャマッピングを実現する。

【0204】

このことを念頭においた上で、スライサ118は、描画Y座標YrがY0≦Yr<Y1の範囲では、頂点0の(UB0,VR0,WG0)、及び頂点2の(UB2,VR2,WG2)に基づいて、直線補間により、交点始端の(Us,Vs,Ws)を算出するとともに、頂点0の(UB0,VR0,WG0)、及び頂点1の(UB1,VR1,WG1)に基づいて、直線補間により、交点終端の(Ue,Ve,We)を算出する。また、スライサ118は、描画Y座標YrがY1≦Yr≦Y2の範囲では、頂点0の(UB0,VR0,WG0)、及び頂点2の(UB2,VR2,WG2)に基づいて、直線補間により、交点始端の(Us,Vs,Ws)を算出するとともに、頂点1の(UB1,VR1,WG1)、及び頂点2の(UB2,VR2,WG2)に基づいて、直線補間により、交点終端の(Ue,Ve,We)を算出する。

【0205】

このことを、頂点間のY座標がBy≦Ay<Cyであり、描画Y座標YrがY1≦Yr≦Y2の範囲である場合を例に挙げて説明する。そうすると、スライサ118は、頂点0の(UB0,VR0,WG0)=(Bu・Bw,Bv・Bw,Bw)、及び頂点2の(UB2,VR2,WG2)=(Cu・Cw,Cv・Cw,Cw)に基づいて、直線補間により、交点始端の(Us,Vs,Ws)を算出するとともに、頂点1の(UB1,VR1,WG1)=(Au・Aw,Av・Aw,Aw)、及び頂点2の(UB2,VR2,WG2)=(Cu・Cw,Cv・Cw,Cw)に基づいて、直線補間により、交点終端の(Ue,Ve,We)を算出する。

【0206】

次に、スライサ118は、ΔU、ΔV、ΔW及びΔXtを算出する。ここで、ΔU、ΔV、ΔWは、描画対象の水平ラインにおけるΔXtあたりのU座標(=u・w)、V座標(=v・w)、パースペクティブコレクト用パラメータW(=w)それぞれの変化量であり、ΔXtは、描画対象の水平ラインにおける1ピクセルあたりのX座標の変化量である。ΔXtは、「+1」または「−1」のいずれかとなる。

【0207】

ΔU=(Ue−Us)/(Xe−Xs)

ΔV=(Ve−Vs)/(Xe−Xs)

ΔW=(We−Ws)/(Xe−Xs)

ΔXt=(Xe−Xs)/│Xe−Xs│

【0208】

スライサ118は、デプスコンパレータ112から受け取った構造体インスタンスと共に、算出したXs,Us,Vs,Ws,Xe,ΔU,ΔV,ΔW及びΔXtを、ピクセルステッパ120へ送出する。また、スライサ118は、バーテックスソータ114から受け取ったポリゴン/スプライト共通データCIが、次の描画サイクルでも使用される場合は、リサイクルバッファ110に、デプスコンパレータ112から受け取った構造体インスタンスを書き込む。なお、ビデオタイミングジェネレータ138からの垂直走査カウント信号VC及びポリゴンの頂点座標から、次の描画サイクルでの使用の有無を知ることができる。

【0209】

図19は、スライサ118によるスプライトに対する処理の説明図である。図19に示すように、スライサ118は、与えられたポリゴン/スプライト共通データCIにより定義されるスプライト(矩形)と、描画対象の水平ラインと、の交点座標(Xs,Ys)及び(Xe,Ye)を求める。ここで、スプライトに対しては、先に描画される側の交点を始端(Xs,Ys)とし、後に描画される側の交点を終端(Xe,Ye)とする。

【0210】

スプライトの各頂点0,1,2,3をUV空間へ写像したときの座標は、(UB0,VR0),(UB1,VR1),(UB2,VR2),(UB3,VR3)である。ここで、UB3,VR3はスライサ118に入力されないが、それぞれ下記のようにスライサ118内で求められる。

【0211】

UB3=UB1

VR3=VR2

【0212】

スライサ118は、頂点0の(UB0,VR0)及び頂点2の(UB2,VR2)に基づいて、直線補間により、交点始端のUV座標(Us,Vs)を算出するとともに、頂点1の(UB1,VR1)及び頂点3の(UB3,VR3)に基づいて、直線補間により、交点終端のUV座標(Ue,Ve)を算出する。

【0213】

そして、スライサ118は、ΔUおよびΔVを算出する。ここで、ΔU、ΔVは、描画対象の水平ラインにおけるΔXsあたりのU座標、V座標それぞれの変化量である。ΔXsは、描画対象の水平ラインにおける1ピクセルあたりのX座標の変化量であるが、常に「1」となるので、算出は行わない。

【0214】

ΔU=(Ue−Us)/(Xe−Xs)

ΔV=(Ve−Vs)/(Xe−Xs)

ΔXs=(Xe−Xs)/│Xe−Xs│=1

【0215】

スライサ118は、デプスコンパレータ112から受け取った構造体インスタンスと共に、算出したXs,Us,Vs,Xe,ΔU,ΔV及びΔXsを、ピクセルステッパ120へ送出する。また、スライサ118は、バーテックスエキスパンダ116から受け取ったポリゴン/スプライト共通データCIが、次の描画サイクルでも使用される場合は、リサイクルバッファ110に、デプスコンパレータ112から受け取った構造体インスタンスを書き込む。なお、ビデオタイミングジェネレータ138からの垂直走査カウント信号VC及びスプライトの頂点座標から、次の描画サイクルでの使用の有無を知ることができる。

【0216】

ここで、スライサ118は、ポリゴン/スプライト共通データCIのフィールドFから、ポリゴンおよびスプライトの別を認識でき、ポリゴン構造体インスタンスのメンバTypeから、グーローシェーディング及びテクスチャマッピングの別を認識できる。

【0217】

図12に戻って、ピクセルステッパ120は、グーローシェーディングモードのポリゴンについては、スライサ118から与えられたパラメータ(Xs,Rs,Gs,Bs,Xe,ΔR,ΔG,ΔB及びΔXg)から、描画対象ピクセルの描画X座標とRGB値を求め、(1−α)値とともにピクセルディザ122に送出する。具体的には、ピクセルステッパ120は、交点の始端(描画開始端)Xsの赤成分Rsに、1ピクセル当たりの赤成分の変化量ΔRを順次加えていき、各ピクセルの赤成分RXを求める。この処理を、交点の終端(描画終了端)Xeに到達するまで行う。緑成分GX及び青成分BXについても同様である。また、交点の始端XsにΔXsを順次加えていき、描画X座標Xrを求める。なお、X=0〜|Xe−Xs|であり、整数である。

【0218】

RX=ΔXg・ΔR・X+Rs

GX=ΔXg・ΔG・X+Gs

BX=ΔXg・ΔB・X+Bs

Xr=ΔXs・X+Xs

【0219】

ピクセルステッパ120は、求めた各ピクセルのRGB値(RX,GX,BX)、並びに描画X座標Xrを、(1−α)値並びにデプス値(Depth)とともに、ピクセルディザ122に出力する。

【0220】

また、ピクセルステッパ120は、テクスチャマッピングモードのポリゴンについては、スライサ118から与えられたパラメータ(Xs,Us,Vs,Ws,Xe,ΔU,ΔV,ΔW及びΔXt)から、描画対象ピクセルをUV空間へ写像したときの座標(U,V)を求める。具体的には、ピクセルステッパ120は、交点の始端(描画開始端)Xsのパースペクティブコレクト用パラメータWsに、1ピクセル当たりのパースペクティブコレクト用パラメータの変化量ΔWを順次加えていき、各ピクセルのパースペクティブコレクト用パラメータWXを求める。この処理を、交点の終端(描画終了端)Xeに到達するまで行う。なお、X=0〜|Xe−Xs|であり、整数である。

【0221】

WX=ΔXt・ΔW・X+Ws

【0222】

ピクセルステッパ120は、交点の始端(描画開始端)XsのU座標(=u・w)Usに、1ピクセル当たりのU座標の変化量ΔUを順次加えていき、求めた値にWXの逆数を掛け合わせ、各ピクセルのU座標UXを求める。この処理を、交点の終端(描画終了端)Xeに到達するまで行う。V座標(=v・w)VXについても同様である。また、交点の始端XsにΔXsを順次加えていき、描画X座標Xrを求める。なお、X=0〜|Xe−Xs|であり、整数である。

【0223】

UX=(ΔXt・ΔU・X+Us)・(1/WX)

VX=(ΔXt・ΔV・X+Vs)・(1/WX)

Xr=ΔXs・X+Xs

【0224】

ピクセルステッパ120は、求めた各ピクセルのUV座標(UX,VX)並びに描画X座標Xrを、スライサ118から受け取った構造体インスタンス(テクスチャマッピングのポリゴン構造体インスタンス及びテクスチャアトリビュート構造体インスタンス)とともにテクセルマッパ124に出力する。

【0225】

さらに、ピクセルステッパ120は、スプライトについては、スライサ118から与えられたスプライトのパラメータ(Xs,Us,Vs,Xe,ΔU,ΔV及びΔXs)から描画対象ピクセルをUV空間へ写像したときの座標(U,V)を求める。具体的には、ピクセルステッパ120は、交点の始端(描画開始端)XsのU座標Usに、1ピクセル当たりのU座標の変化量ΔUを順次加えていき、各ピクセルのU座標UXを求める。この処理を、交点の終端(描画終了端)Xeに到達するまで行う。V座標VXについても同様である。また、交点の始端XsにΔXs、すなわち「1」を順次加えていき、描画X座標Xrを求める。なお、X=0〜|Xe−Xs|であり、整数である。

【0226】

UX=ΔXs・ΔU・X+Us

VX=ΔXs・ΔV・X+Vs

Xr=X+Xs

【0227】

ピクセルステッパ120は、求めた各ピクセルのUV座標(UX,VX)、並びに描画X座標Xrを、スライサ118から受け取った構造体インスタンス(スプライト構造体インスタンス及びテクスチャアトリビュート構造体インスタンス)とともにテクセルマッパ124に出力する。

【0228】

ピクセルディザ122は、ピクセルステッパ120から与えられたRGB値の小数部にノイズを加え、マッハバンドを目立たなくするディザリングを実行する。なお、ピクセルディザ122は、ディザリング後のピクセルのRGB値を、描画X座標Xr,(1−α)値,及びデプス値とともにカラーブレンダ132に出力する。

【0229】

図20は、ピクセルディザ122によるディザリングの説明図である。図20に示すように、ディザパターンは、2×2の格子状のピクセルブロックを単位としてRPU9の制御レジスタ(図示せず)に設定される。描画ピクセルのスクリーン座標系XY座標のLSBの値によって、4つのパターン「00」,「01」,「10」,「11」のどれが適用されるかが決定される。

【0230】

各パターンは2ビットの大きさで、RGB値のそれぞれの小数部に加算される。加算の結果、整数部へのキャリーが発生する場合には、キャリーが整数部に加算される。実際に表示色として用いられる部分はRGB値の整数部であるので、ディザパターンとして設定した値が全て同じでない限り、色の境界部にノイズが現れ、マッハバンドを目立たなくする。

【0231】

図12に戻って、テクセルマッパ124は、テクスチャアトリビュート構造体のメンバFilterが「0」を示している場合には座標(UX,VX)の近傍4つのテクセルデータを指し示す4組のワードアドレスWADとビットアドレスBADを、メンバFilterが「1」を示している場合には座標(UX,VX)に最も近い1つのテクセルデータを指し示す1組のワードアドレスWADとビットアドレスBADを算出して出力する。また、メンバFilterが「0」を示している場合には、バイリニアフィルタリングにおける各テクセルの係数部に相当するバイリニアフィルタパラメータBFPを算出して出力する。更に、シザリングイネーブル時のスプライトと、シザリングディセーブル時のスプライトと、ポリゴンとで互いに異なるデプス値(メンバDepth)の形式を統一して出力する。

【0232】

テクスチャキャッシュブロック126は、テクセルマッパ124から出力されたワードアドレスWAD、ビットアドレスBAD、構造体インスタンスのメンバTsegmentから、各テクセルのアドレスを算出する。算出されたアドレスが指し示すテクセルデータが既にキャッシュに格納されている場合、格納されているテクセルデータ及びアトリビュート構造体のメンバPaletteから、カラーパレットRAM11のエントリを選択するインデックスを生成し、カラーパレットRAM11に出力する。

【0233】

一方、当該テクセルデータが、キャッシュに格納されていない場合は、テクスチャキャッシュブロック126は、メモリマネージャ140に対して、テクセルデータの取得指示を出す。メモリマネージャ140は、メインRAM25から該当するテクスチャパターンデータを取得して、テクスチャキャッシュブロック126のキャッシュに格納する。また、メモリマネージャ140は、マージソータ106からの指示で、後段で必要になるテクスチャパターンデータを、外部メモリ50から取得して、メインRAM25に格納する。

【0234】

この際、メモリマネージャ140は、テクスチャマッピングモードのポリゴン用のテクスチャパターンデータについては、1ポリゴンにマッピングされるデータ全体を一括して取得し、メインRAM25に格納するのに対し、スプライト用のテクスチャパターンデータについては、1スプライトにマッピングされるデータをライン単位で取得し、メインRAM25に格納する。これは、描画対象の水平ラインに含まれるピクセル群をUV空間に写像すると、ポリゴンの場合はUV空間中のあらゆる直線上に写像される可能性があるのに対し、スプライトの場合はU軸に平行な直線上にのみ写像されるからである。

【0235】

本実施の形態では、テクスチャキャッシュブロック126のキャッシュは、64ビット×4エントリとし、ブロック置換アルゴリズムは、LRU(least recently used)とする。

【0236】

カラーパレットRAM11は、テクスチャキャッシュブロック126から入力されたテクセルデータとメンバPaletteとが連接されたインデックスが示すエントリに含まれるRGB値及び半透明合成のための(1−α)値を、バイリニアフィルタ130に出力する。バイリニアフィルタパラメータBFP、デプス値、及び描画X座標Xrについては、そのままバイリニアフィルタ130に出力される。

【0237】

バイリニアフィルタ130は、バイリニアフィルタリングを実行する。テクスチャマッピングにおいて、最も単純なピクセル描画色の算出方法は、UV空間に写像されたピクセル座標(UX,VX)に最も近いテクセル座標に位置するテクセルのカラーデータを取得し、取得したカラーデータからピクセルの描画色を算出する方法である。この手法を「ニアレストネイバー」と呼ぶ。

【0238】

但し、隣り合うピクセルをUV空間に写像した際の2点間の距離が1テクセル分の距離より極めて小さい場合、すなわち、スクリーン上でテクスチャが大きく拡大されてマッピングされる場合には、ニアレストネイバーではテクセルの境界が明瞭に表示されてしまうため、粗いモザイク状のテクスチャマッピングとなってしまう。このような問題を解消する手法として、バイリニアフィルタリングを実行する。

【0239】

図21は、バイリニアフィルタ130によるバイリニアフィルタリングの説明図である。図21に示すように、バイリニアフィルタ130は、UV空間に写像されたピクセル座標(UX,VX)の近傍4テクセルのRGB値及び(1−α)値の加重平均を算出し、ピクセルの描画色を決定する。これにより、テクセルのカラーが滑らかに補完され、マッピング結果におけるテクセルの境界が目立たなくなる。具体的には、バイリニアフィルタリングは次式(バイリニアフィルタリングの式)により実行される。ただし、次式において、「u」はU座標UXの小数部、「v」はV座標VXの小数部、「nu」は(1−u)、「nv」は(1−v)、である。

【0240】

R=R0・nu・nv+R1・u・nv+R2・nu・v+R3・u・v

G=G0・nu・nv+G1・u・nv+G2・nu・v+G3・u・v

B=B0・nu・nv+B1・u・nv+B2・nu・v+B3・u・v

A=A0・nu・nv+A1・u・nv+A2・nu・v+A3・u・v

【0241】

ここで、R0,R1,R2及びR3は、それぞれ、上記4テクセルのR値であり、G0,G1,G2及びG3は、それぞれ、上記4テクセルのG値であり、B0,B1,B2及びB3は、それぞれ、上記4テクセルのB値であり、A0,A1,A2及びA3は、それぞれ、上記4テクセルの(1−α)値である。

【0242】

バイリニアフィルタ130は、算出したピクセルのRGB値並びにA値(つまり(1−α)値)を、デプス値並びに描画X座標Xrとともに、カラーブレンダ132に出力する。

【0243】

図12を参照して、カラーブレンダ132の説明の前に、ラインバッファブロック134について説明する。ラインバッファブロック134は、ラインバッファLB1及びLB2を含み、一方のラインバッファが表示用に使用されているときは、他方のラインバッファが描画用に使用され、表示用と描画用とを交互に切り替えて使用するダブルバッファ方式を採用する。表示用に使用されているラインバッファLB1あるいはLB2は、ビデオタイミングジェネレータ138からの水平走査カウント信号HC及び垂直走査カウント信号VCに従って、ピクセルごとのRGB値を、ビデオエンコーダ136に出力する。

【0244】

カラーブレンダ132は、半透明合成を実行する。具体的には、次の通りである。カラーブレンダ132は、ピクセルディザ122あるいはバイリニアフィルタ130から与えられたピクセルのRGB値及び(1−α)値と、描画対象のラインバッファLBの描画対象ピクセル位置(描画X座標Xrが示すピクセル)に格納されているRGB値とを用い、次式により、アルファブレンディングを実行し、結果を同じラインバッファLBの描画対象ピクセル位置に書き込む。

【0245】

Rb=Rf・(1−αr)+Rr

Gb=Gf・(1−αr)+Gr

Bb=Bf・(1−αr)+Br

αb=αf・(1−αr)+αr

【0246】

ここで、「1−αr」は、ピクセルディザ122あるいはバイリニアフィルタ130から与えられた(1−α)値である。「Rr」、「Gr」及び「Br」は、それぞれ、ピクセルディザ122あるいはバイリニアフィルタ130から与えられたRGB値である。「Rf」、「Gf」及び「Bf」は、それぞれ、描画用に使用されているラインバッファLBの描画対象ピクセル位置から取得したRGB値である。一般的なアルファブレンディングのアルゴリズムにおいては、上式のRr,Gr,およびBrの項は、それぞれRr・αr、Gr・αr、およびBr・αrとなるが、本実施の形態では、予めRr・αr,Gr・αr,およびBr・αrの計算結果をRr、Gr、およびBrとして用意しておくことにより、演算回路の簡略化を行っている。

【0247】

ビデオエンコーダ136は、表示用に使用されているラインバッファLB1あるいはLB2から入力されたRGB値と、ビデオタイミングジェネレータ138から入力されたタイミング情報(複合同期信号SYN、複合ブランキング信号BLK、バーストフラグ信号BST、及びライン交番信号LA等)と、を信号VSに対応したコンポジットビデオ信号を表すデータストリームVDに変換する。信号VSは、テレビジョン方式(NTSCやPAL等)を指示する信号である。

【0248】

ビデオタイミングジェネレータ138は、入力されるクロックを基に、水平走査カウント信号HC及び垂直走査カウント信号VC、並びに、複合同期信号SYN、複合ブランキング信号BLK、バーストフラグ信号BST、及びライン交番信号LA等のタイミング信号を生成する。水平走査カウント信号HCは、システムクロックの1周期毎にカウントアップされ、1水平ラインのスキャンが終了すると、リセットされる。また、垂直走査カウント信号VCは、1/2水平ラインのスキャンが終了するたびにカウントアップされ、1フレームあるいは1フィールドのスキャンが終了すると、垂直走査カウント信号VCはリセットされる。

【0249】

さて、次に、図10のYSU19によるソート処理の詳細を図面を参照しながら説明する。上述したように、YSU19によるソート処理で採用するソート手法は、ヒープソートである。

【0250】

上記のように、ポリゴン構造体配列のソート処理とスプライト構造体配列のソート処理とは別個に行われる。しかし、それぞれにおいて、同じソート処理が実行されるので、後述の図22及び図23において、配列およびその要素は、ポリゴン構造体配列のソート処理の場合には、それぞれポリゴン構造体配列およびポリゴン構造体インスタンスを指し、スプライト構造体配列のソート処理の場合には、それぞれスプライト構造体配列およびスプライト構造体インスタンスを指す。

【0251】

一般に、配列の要素は、値を代入するための、インデックスが付された変数(入れ物)として定義されたり、あるいは、インデックスが付された変数に代入された値そのものとして定義されたりする。本実施の形態では、両者を区別する必要があるときは、変数(入れ物)としての配列の要素を「要素」、その変数に代入された値を「要素値」又は「要素の値」と呼ぶ。

【0252】

図22は、図10のYSU19による配列Aのヒープ構築後のヒープ構造を示す図である。図22では、配列Aの要素数を10個とし、Yソート前の要素A[0]〜A[9]の要素値をそれぞれ要素値ev0〜ev9と表す。

【0253】

図22を参照して、本実施の形態におけるヒープ構造は、二分木の構造を持ち、1つの親に対して2つの子が接続される。但し、ヒープ構造の末端においては、子を1つしか持たない親が存在する場合がある。親は子に対して高い順位を持つが、2つの子の間の順位については、特にルールは定められていない。

【0254】

ここで、順位とは、ソートルール1〜4(ノンインタレーススキャンの場合はソートルール1〜3)で定められる構造体インスタンス間(ポリゴン構造体配列のYソートの場合にはポリゴン構造体インスタンス間、スプライト構造体配列のYソートの場合にはスプライト構造体インスタンス間)の優先順位を指す。つまり、順位とは、ソートルール1〜4(ノンインタレーススキャンの場合はソートルール1〜3)で定められる要素値間(ポリゴン構造体配列のYソートの場合にはポリゴン構造体配列の要素値間、スプライト構造体配列のYソートの場合にはスプライト構造体配列の要素値間)の優先順位を指す。木構造の上位ほど順位が高いので、図22の例では、要素値ev3が最も順位の高い要素値である。

【0255】

メインRAM25へのヒープ構造の格納方法を説明する。一般的なヒープ構造の場合、最も順位の高い親の要素値から順に、メモリ上の配列の先頭から格納される。ヒープソートにおいては、ソート結果が1つずつ確定するため、一般的には、メモリ領域を効率的に用いるために、順位が確定した要素値は、ヒープ構造の末端の子の要素値と入れ替えられて格納される。従って、最も順位の高い親の要素値は、配列の末尾に格納されて、ヒープ構造から切り離される。これに対して、本実施の形態では、一般的な順序とは逆の順序で、ヒープ構造をメモリ上の配列に格納する。この点を、図22のヒープ構造を例に挙げながら説明する。

【0256】

図23は、図22のヒープ構造のメインRAM25への格納方法の説明図である。図23(a)及び図22に示すように、本実施の形態のヒープ構造においては、最も順位の高い親の要素値から順に、メインRAM25上の配列Aの末尾から格納される。そして、図23(b)に示すように、順位が確定し配列Aの末尾A[9]に格納された最も順位の高い親の要素値ev3と、配列Aの先頭A[0]に格納されたヒープ構造の末端の子の要素値ev5と、が入れ替えられ、要素値ev3が格納された先頭の要素A[0]は、ヒープ構造から切り離される。理由は次の通りである。

【0257】

上記のように、YSU19は、順位(ソート結果)が1つ確定する度にパルス信号(ポリゴンの場合パルス信号PPL、スプライトの場合パルス信号SPL)の1パルスをRPU9に出力する。これらのパルス信号を受けて、RPU9は、順位が確定した要素値、つまり、順位が確定した構造体インスタンスを、配列の先頭から読み出して描画処理を行う。このため、一般的な順序とは逆の順序で、ヒープ構造をメインRAM25上の配列に格納する。

【0258】

配列の1要素のサイズについて説明する。配列の1要素のサイズは、ポリゴン構造体とスプライト構造体とで異なる。ポリゴン構造体の場合、配列の1要素(1個のポリゴン構造体インスタンス)は16バイトで構成され、スプライト構造体の場合、配列の1要素(1個のスプライト構造体インスタンス)は8バイトで構成される(図13、図15、及び図16参照)。但し、ポリゴン構造体インスタンスとスプライト構造体インスタンスとは別々の配列に格納されるため、メインRAM25上の同じ配列内に異なるサイズの要素が混在することはない。また、YSU19は、ポリゴン構造体配列のソートとスプライト構造体配列のソートとを独立に行う。

【0259】

次に、YSU19によるポリゴン構造体配列のYソート処理をフローチャートを用いて説明する。YSU19によるスプライト構造体配列のYソート処理は、ポリゴン構造体配列のYソート処理と同様の流れで行われるので説明を省略する。

【0260】

図24は、図10のYSU19によるポリゴン構造体配列のYソート処理の全体的な流れの一例を示すフローチャートである。なお、図24及び後述の図25〜図27において、特に明示しない限り、配列というときは、ポリゴン構造体配列を指す。

【0261】

図24を参照して、ステップS20にて、YSU19は、配列のソートの開始前に、ソート対象となる当該配列の先頭アドレスをYSU19内の制御レジスタ「Polygon_Array_YSU_Base_Address」(図示せず)から取得し、かつ、当該配列の要素数「s」をYSU19内の制御レジスタ「Number_of_Sorted_Polygons」(図示せず)から取得する。なお、図22及び図23の例では、s=10である。

【0262】

ちなみに、スプライト構造体配列のソートを行う場合には、当該スプライト構造体配列の先頭アドレスをYSU19内の制御レジスタ「Sprite_Array_YSU_Base_Address」(図示せず)から取得し、かつ、当該スプライト構造体配列の要素数「s#」をYSU19内の制御レジスタ「Number_of_Sorted_Sprites」(図示せず)から取得する。

【0263】

次のステップS21にて、YSU19は、ヒープ構造を構築する(ヒープ構築処理)。ヒープ構築処理の詳細は後述する。この処理の完了後、配列全体がヒープ構造となり、それぞれの要素の接続において、親の要素の順位が子の要素の順位より高いことが保証される。したがって、ヒープ構築処理後、最も順位の高い親、すなわち「根(root)」の親の要素の順位は、配列の全要素中で最も高いことが確定する。

【0264】

以降、YSU19は、順位の高いものから要素が1つ確定するたびに、「根」の親の要素の値と、ヒープ構造の末端の子の要素の値と、を交換する(入れ替える)。これは、順位の確定した「根」の親の要素をヒープ構造から切り離し、メインRAM25上の配列の先頭から順に整列させることを意味する。

【0265】

従って、YSU19は、ステップS21の次のステップS22にて、最も順位の高い要素として確定した親の要素の値、つまり要素[s−1]の値と、ヒープ構造の末端の子の要素の値、つまり要素[0]の値と、を交換するために、変数iに「0」を設定し、続くステップS23にて、要素[0]の値と要素[s−1]の値とを交換する。つまり、要素[0]の値を要素[s−1]へ、要素[s−1]の値を要素[0]へ、代入する。この交換後、要素[0]はヒープ構造から切り離される。なお、図22及び図23の例では、要素A[0]の値ev5と要素A[9]の値ev3とが交換される。

【0266】

ステップS27の後のステップS23においては、YSU19は、その時のヒープ構造における最も順位の高い要素として確定した親の要素の値、つまり要素[s−1]の値と、その時のヒープ構造の末端の子の要素の値、つまりインクリメント後(ステップS25)の要素[i]の値と、を交換する。つまり、要素[i]の値を要素[s−1]へ、要素[s−1]の値を要素[i]へ、代入する。この交換後、要素[i]はヒープ構造から切り離される。

【0267】

続くステップS24にて、YSU19は、1個の要素の順位確定を通知すべく、パルス信号PPLの1パルスをRPU9に出力する。ちなみに、スプライト構造体配列のソートの場合には、パルス信号SPLの1パルスをRPU9に出力する。次のステップS25にて、YSU19は、変数iの値をインクリメントする。従って、変数iは常にヒープ構造の末端を指し示すように設定される。これは、インクリメント前の要素[i]がヒープ構造から切り離され、インクリメント後の要素[i]が新たにヒープ構造の末端となったことを意味する。

【0268】

ステップS25で変数iをインクリメントした後の値が「s−1」と同じ場合は、ソートが完了していないヒープ構造に含まれる要素は、要素[s−1]のみということになる。これは、全ての要素値のソートが完了したことを意味する。従って、YSU19は、ステップS26にて、i=s−1と判断したときは、ステップS28に進んで、最後の要素値の順位確定を示すパルス信号PPL(スプライトの場合はパルス信号SPL)を1パルス出力し、Yソート処理を終了する。

【0269】

一方、YSU19は、ステップS26にて、変数iが「s−1」と等しくないと判断したときは、Yソート処理が完了していないので、ステップS27に進む。

【0270】

この時点では、ステップS23の交換処理により、ヒープ構造の末端の子の要素の値が「根」の親の位置に格納されているため、ヒープ構造は崩れている。この状態からヒープ構造を再構築するために、ステップS27にて、YSU19は、「ダウンヒープ処理」を行う。ここでは、「根」の親から順に、いずれかの子の要素の順位が親の要素より高い場合に、子の要素の値と親の要素の値とを入れ替え、入れ替えた後の子の要素を新たな親の要素として、同じ処理をヒープ構造の末端まで行う処理を「ダウンヒープ処理」と呼称する。ダウンヒープ処理の詳細は後述する。

【0271】

ステップS27では、要素[s−1]を処理開始時の親とし、「s−i」をヒープ構造の要素数とするダウンヒープ処理を行う。ダウンヒープ処理完了に伴い、ヒープ構造が再構築される。したがって、ステップS27終了後の「根」の親は、その時点のヒープ構造で最も高い順位であることが確定する。その後、ステップS23に戻って、ソート処理が継続される。

【0272】

図25は、図24のステップS21のヒープ構築処理の流れの一例を示すフローチャートである。図25を参照して、ステップS40にて、YSU19は、変数jに「0」を設定する。変数jは、ダウンヒープ処理における最初の子の要素を指し示すものであり、初期状態では、ヒープ構造全体の末端の要素、すなわち要素[0]を指し示す。

【0273】

続くステップS41にて、YSU19は、要素[j]の親の要素[p]を特定する。親の要素[p]のインデックス「p」は、以下の計算式により算出される。次式において、「s」はヒープ構造全体の要素数である。但し、右辺の除算の商は常に整数で得られるものとし、剰余は切り捨てる。

【0274】

p=s−(s−j)/2

【0275】

ステップS42にて、YSU19は、ステップS41で特定した親の要素[p]を親とし、「s」をヒープ構造全体の要素数とするダウンヒープ処理を行う。ダウンヒープ処理の詳細は後述する。

【0276】

ステップS42のダウンヒープ処理完了後、ステップS43にて、YSU19は、変数jの値をインクリメントする。そして、ステップS44にて、YSU19は、インクリメント後の変数jの値が「s−1」より小さければ、ステップS41へ戻る。一方、インクリメント後の変数jの値が「s−1」に等しければ、YSU19は、ヒープ構築処理を終了し、図24のステップS22に進む。

【0277】

図26は、ダウンヒープ処理の流れの一例を示すフローチャートである。このダウンヒープ処理は、図24のステップS27及び図25のステップS42において実行される。

【0278】

図26を参照して、ステップS60にて、YSU19は、親の要素のインデックスと、対象となるヒープ構造の要素数とから、親に対する子の個数がいくつであるかを特定する。YSU19は、親の要素のインデックスを「p」とし、対象となるヒープ構造の要素数を「s」としたときに、2(s−p)の値が「s」より小さい場合には子の個数が2個、「s」と同じ場合には子の個数が1個、「s」より大きい場合には子の個数が0個であるとする。

【0279】

ステップS61において、YSU19は、子の個数が「0」と判定すると、ダウンヒープ処理を終了する。また、ステップS62にて、YSU19は、子の個数が「1」と判定すると、ステップS63に進んで、その1つの子を親との比較対象として設定し、ステップS66に進む。一方、ステップS62にて、YSU19は、子の個数が「1」でない、つまり、「2」と判定すると、ステップS64に進む。

【0280】

ステップS64では、YSU19は、子の個数が「2」であるので、どちらの子がより順位が高いかを判定するために、順位比較処理を行う。順位比較処理の詳細は後述する。そして、ステップS65にて、YSU19は、順位比較処理の結果、順位の高い方の子を親との比較対象として設定し、ステップS66に進む。

【0281】

ステップS63の後あるいはステップS65の後のステップS66では、YSU19は、比較対象に設定された子の要素と、親の要素との順位比較処理を行う。比較処理の結果、ステップS67にて、YSU19が親の順位が高いと判定した場合、そこでダウンヒープ処理は終了する。一方、子の順位が高いと判定した場合、ステップS68にて、YSU19は、比較対象の子の要素の値と、親の要素の値とを交換する。交換後、ステップS69にて、YSU19は、値が交換された子の要素(つまり、交換前の親の要素の値を格納している要素)を、新たな親として設定し、ステップS60に戻る。

【0282】

図27は、順位比較処理の流れの一例を示すフローチャートである。この順位比較処理は、図26のステップS64及びS66において実行される。順位比較処理では、ソートルール1〜4(ノンインタレーススキャンの場合はソートルール1〜3)に基づいて、2つのポリゴン構造体インスタンス間で順位を比較する。つまり、順位比較処理では、ソートルール1〜4(ノンインタレーススキャンの場合はソートルール1〜3)に基づいて、配列の2つの要素間で順位を比較する。ここで、比較対象の2つの要素(ポリゴン構造体インスタンス)をそれぞれ要素「A」及び「B」と表記する。

【0283】

ステップS80にて、YSU19は、要素「A」及び「B」ごとに、最小Y座標と描画先頭ライン(描画上端ライン)のY座標と、を比較する。この例では、比較対象の要素「A」及び「B」は、ポリゴン構造体インスタンスであるので、メンバAy,By及びCy(図13及び図15参照)のうち最も小さな値が、最小Y座標として扱われる。ちなみに、比較対象の要素「A」及び「B」が、スプライト構造体インスタンスである場合、シザリングイネーブル時はメンバAyの値+256が、シザリングディセーブル時はメンバAyの値そのものが、最小Y座標として扱われる(図16参照)。

【0284】

ステップS81にて、YSU19は、要素「A」の最小Y座標のみが、描画先頭ラインのY座標以下であると判断した場合、すなわち、要素「A」に基づくポリゴンのみが、描画先頭ラインと交わるか、あるいは、描画先頭ラインより上にあると判断した場合、ステップS82に進み、要素「A」の順位が高いと判定し、順位比較処理を終了する(ソートルール1)。

【0285】

ステップS83にて、YSU19は、要素「B」の最小Y座標のみが、描画先頭ラインのY座標以下であると判断した場合、すなわち、要素「B」に基づくポリゴンのみが、描画先頭ラインと交わるか、あるいは、描画先頭ラインより上にあると判断した場合、ステップS84に進み、要素「B」の順位が高いと判定し、順位比較処理を終了する(ソートルール1)。

【0286】

要素「A」及び「B」の双方の最小Y座標が、描画先頭ラインのY座標以下である場合は、要素「A」及び「B」のそれぞれに基づくポリゴンが、描画先頭ラインと交わるか、あるいは、描画先頭ラインより上にあることを意味する。要素「A」及び「B」の双方の最小Y座標が描画先頭ラインより上にある場合、要素「A」及び「B」に基づくポリゴンは、スクリーンに描画されないため、ソートルール1によって判定される順位は描画結果に影響を与えない。この点、スプライトについても同様である。

【0287】

従って、ステップS85にて、YSU19は、要素「A」及び「B」の双方の最小Y座標が描画先頭ラインのY座標以下であると判断した場合、つまり、要素「A」及び「B」に基づく双方のポリゴンが、描画先頭ラインと交わっていると判断した場合、ステップS86に進んで、要素「A」及び「B」間の順位を、最小Y座標の比較でなく、デプス値の比較により定める(ソートルール3)。

【0288】

この場合、ポリゴン構造体にメンバDepthがあり(図13及び図15参照)、この値の大小により順位が判定される。スプライトの場合も同様であり、スプライト構造体のメンバDepthの値の大小により順位が判定される(図16参照)。メンバDepthのビット数は、ポリゴン構造体と、シザリングイネーブル時のスプライト構造体と、シザリングディセーブル時のスプライト構造体と、で異なるが、YSU19が比較するのは、同一フォーマットの構造体インスタンス同士であるため、単純にメンバDepthの値を比較するだけで大小判定を行うことができる。

【0289】

ステップS86に続くステップS87にて、YSU19は、デプス値の比較の結果、要素「A」のデプス値が、要素「B」のデプス値以上であると判断した場合、ステップS88に進んで、要素「A」の順位が高いと判定し、順位比較処理を終了する。一方、YSU19は、デプス値の比較の結果、要素「A」のデプス値が、要素「B」のデプス値より小さいと判断した場合、ステップS89に進んで、要素「B」の順位が高いと判定し、順位比較処理を終了する。

【0290】

一方、ステップS85において、YSU19は、要素「A」及び「B」の双方の最小Y座標が、描画先頭ラインのY座標より大きいと判定した場合、ステップS90に進んで、双方の最小Y座標同士を比較する。但し、インタレーススキャンモードでの順位比較処理においては、描画対象となるフィールドのライン上にある最小Y座標の値と、その1つ前のフィールドのライン上にある、1つ小さい最小Y座標の値と、が同じであるとして、比較を行う(ソートルール4)。一方、ノンインタレーススキャンモードでの順位比較処理においては、単純に最小Y座標の大小が比較される。

【0291】

そして、ステップS91にて、YSU19は、要素「A」及び「B」の双方の最小Y座標が同じであると判定した場合、ステップS86に進んで、デプス値の比較により、要素「A」及び「B」の順位を判定する(ソートルール2)。一方、ステップS91にて、YSU19が、要素「A」及び「B」の最小Y座標が異なると判定した場合、ステップS92に進む。

【0292】

ステップS92では、YSU19は、要素「A」の最小Y座標が、要素「B」の最小Y座標より小さいと判断した場合、ステップS93に進んで、要素「A」の順位が高いと判定して、順位比較処理を終了する(ソートルール1)。一方、YSU19は、要素「A」の最小Y座標が、要素「B」の最小Y座標以上であると判断した場合、ステップS94に進んで、要素「B」の順位が高いと判定して、順位比較処理を終了する(ソートルール1)。

【0293】

なお、図24〜図27において、ポリゴン構造体配列のYソート処理を例に挙げて説明したが、同様の処理が、スプライト構造体配列のYソート処理でも行われる。

【0294】

さて、以上のように、本実施の形態によれば、グラフィック要素(ポリゴン、スプライト)の最小Y座標が、昇順(小から大の順)で並ぶように、つまり、グラフィック要素の出現順で、グラフィック要素ごとの構造体インスタンスを並べ替えている(ソート)。また、1度描画で用いられた構造体インスタンスは、リサイクルバッファに格納され、描画対象ラインのY座標が当該構造体インスタンスの最大Y座標(ポリゴンについては3頂点のY座標のうち最も大きいY座標、スプライトについては4頂点のY座標のうち最も大きいY座標)を超えるまで再利用される。

【0295】

従って、ソート後の構造体インスタンスを順番に読み出して、描画処理を行うだけでよいため、描画のたびに、全ての構造体インスタンスの中から、そのとき描画すべき構造体インスタンスを検索する処理が不要になり、処理を高速化できる。以上の結果、1フレーム以上のイメージを格納するための大容量のバッファ(フレームバッファ等)を実装する必要は必ずしもなく、より容量の小さいバッファ(ラインバッファや、1ラインに満たないピクセルを描画するピクセルバッファ等)を実装した場合であっても、多くのグラフィック要素を組み合わせた三次元イメージの表示が可能になる。

【0296】

一般的な技術により、ラインバッファあるいはピクセルバッファに描画を行おうとすると、1ラインごとあるいは所定数のピクセルごとに、全構造体インスタンスの中から、描画対象の構造体インスタンスを検索しなければならないが、本実施の形態では、YSU19により、予め、最小Y座標の昇順で(つまりグラフィック要素の出現順で)ソートが行われているため、そのような検索処理が不要になる。また、そのような検索処理を行っていたのでは、多くのグラフィック要素を組み合わせた三次元イメージの表示が困難になる。ちなみに、フレームバッファを実装するときは、1フレーム分のイメージを格納できるので、そもそも、そのような検索処理は不要で、デプス値の大きいものから順に描画していけばよい。

【0297】

また、本実施の形態によれば、ラインバッファLB1あるいはLB2への新たなピクセル情報の書き込み(新たなピクセルの描画)のために、構造体インスタンスが再利用可能な場合は、その構造体インスタンスは、リサイクルバッファ110に格納される。このため、同じ構造体インスタンスを使用する新たなピクセルの描画のたびに、ソート後の全ての構造体インスタンスが格納されたメインRAM25から、その同じ構造体インスタンスを繰り返し読み出す処理が不要になって、より処理の高速化を図ることができる。

【0298】

また、デプスコンパレータ112を設けて、YSU19が並べ替えた順番で新たに読み出された構造体インスタンスと、再利用のためのリサイクルバッファ110に格納された構造体インスタンスと、の描画順序(つまり、これら構造体インスタンスに基づくピクセルの描画順序)を判定している。このため、判定終了後に、再利用可能な構造体インスタンスをリサイクルバッファ110に送って順番に格納するだけで、リサイクルバッファ110には、再利用可能な構造体インスタンスについて、適切な描画順序で(つまり、デプス値が大きいものが先頭に来る順で)構造体インスタンスが格納される。このように、リサイクルバッファ110には、再利用可能な構造体インスタンスについて適切な描画順序で格納されているところ、これらは、YSU19が並べ替えた順番で新たに読み出された構造体インスタンスとの間で、さらに描画順序が判定されるので、常に適切な描画順序での(つまり、デプス値が大きいもの順での)描画が可能となる。

【0299】

さらに、本実施の形態によれば、複数のグラフィック要素を表示する場合であって、その複数のグラフィック要素の最小Y座標が同じ場合、ソートルール2が適用され、スクリーンを構成する各ラインにおいて、デプス値の降順(大から小の順)で構造体インスタンスが並べられる。従って、各ラインにおいて、構造体インスタンスに基づくグラフィック要素は、デプス値の大きいもの順で描画される。

【0300】

ここで、構造体インスタンスを最小Y座標の小さいもの順でソートし(ソートルール1)、最小Y座標の同じものについてはデプス値の大きいもの順でソートする場合(ソートルール2)、つまり、ソートルール1及び2のみでは、表示先頭ラインの描画においては、必ずしもデプス値の大きいもの順での描画が保証されない。

【0301】

しかし、本実施の形態では、複数のグラフィック要素が、スクリーンの先頭ラインに表示すべきピクセルを含む場合、ソートルール3が適用され、それらの最小Y座標に関係なく、つまり、それらの最小Y座標を同一とみなして、デプス値の降順で構造体インスタンスが並べられる。従って、先頭ラインにおいても、構造体インスタンスに基づくグラフィック要素は、デプス値の大きいもの順で描画される。

【0302】

以上の結果、全ラインにおいて、グラフィック要素は、必ずデプス値が大きいもの順で描画されるので、半透明合成を適切に行うことができる。何故ならば、半透明のグラフィック要素の描画色は、当該グラフィック要素の奥にあるグラフィック要素の描画色に依存するため、グラフィック要素を奥から順に描画する必要がある。

【0303】

さらに、本実施の形態によれば、プリフェッチバッファ108が設けられ、このプリフェッチバッファ108は、YSU19がソートした順番での構造体インスタンスの入力タイミングとデプスコンパレータ112への構造体インスタンスの出力タイミングとの緩衝機構である。これにより、YSU19がソートした順番での構造体インスタンスの入力の、RPU9にとっての待ち時間を削減できる。

【0304】

さらに、本実施の形態によれば、ラインバッファLB1,LB2を実装しているので、フレームバッファを使用する場合よりもコストを低く抑えることができるし、また、1ラインのピクセル数に満たない数のピクセルデータを格納するピクセルバッファを使用する場合よりも簡素な回路構成で(簡単な制御で)描画を実現できる。

【0305】

さらに、本実施の形態によれば、ポリゴン構造体インスタンスと、スプライト構造体インスタンスと、で別個にソートを行っているので、ポリゴン構造体インスタンスと、スプライト構造体インスタンスと、の形式及びサイズが異なっている場合でも容易にソートが可能であり、構造体インスタンスを格納するためのメモリ領域の使用効率も高まる。

【0306】

このように、ポリゴン構造体インスタンス及びスプライト構造体インスタンスが独立してソートされた場合であっても、マージソータ106を設けることで、描画処理の前にポリゴン構造体インスタンス群とスプライト構造体インスタンス群がマージソートされるため、適切な描画処理が可能となる。

【0307】

さらに、本実施の形態によれば、ノンインタレーススキャンのみならず、インタレーススキャンにも対応している。具体的には次の通りである。

【0308】

インタレーススキャンによってイメージが表示される場合、最小Y座標が飛び越し走査により飛び越されたラインを示す構造体インスタンスと、最小Y座標が描画対象のラインを示す構造体インスタンスとが、表示対象ラインの描画処理において共に読み出される。したがって、これらの構造体インスタンスの示す最小Y座標を同じ値とみなし、デプス値の大きいもの順にソートを行うことにより、インタレーススキャンの場合でもデプス値の大きいもの順での描画処理が保証される。そこで、奇数フィールド表示のときと偶数フィールド表示のときとで異なるソートを行うソートルール4を設けている。

【0309】

以上の結果、ノンインタレーススキャンのみならず、インタレーススキャンによる表示を行う場合においても、デプス値の大きいものから描画されるので、適切な半透明合成を実現できる。

【0310】

さらに、本実施の形態によれば、YSU19は、ソートにおいて順位の高いものから構造体インスタンスが1つ確定するたびに、その都度、パルスPPL,SPLを、RPU9に出力する。このため、YSU9は、全構造体インスタンスのソートの完了を待つことなく、逐次、構造体インスタンスを読み込むことができる。さらに、表示中のフィールドに対する各構造体インスタンスのソートを、直前の垂直ブランキング期間あるいは当該フィールド表示中に実行開始することにより、ソート前の演算のために余裕を持ったより十分な時間を確保できる。

【0311】

特に、上述のモード2においては、垂直ブランキング期間の開始直後にソートを実行しているので、ソート前の演算のために余裕を持ったより十分な時間を確保できる(図9(a)参照)。

【0312】

さらに、本実施の形態によれば、YSU19が実装するソート技法は、ヒープソートであるため、構造体インスタンスのソート結果が1つずつ確定され、ソート結果の確定のたびに、パルスPPL,SPLを出力する機構を容易に実現できる。また、全構造体インスタンスのソートに必要な時間のバラツキを少なくできる。

【0313】

さらに、本実施の形態によれば、ソートルール1〜4において、対象の座標を最小Y座標としている。このため、全てのグラフィック要素に対して同じ条件でソートができるので、正しい描画順序で描画を行うことができる。

【0314】

なお、本発明は、上記の実施の形態に限られるものではなく、その要旨を逸脱しない範囲で種々の態様において実施することが可能であり、例えば、以下のような変形も可能である。

【0315】

(1)上記では、カラーブレンダ132による半透明合成を行っているため、各ラインにおいて、グラフィック要素(ポリゴン、スプライト)は、デプス値が大きいものから先に描画した。しかし、半透明合成を行わない場合は、デプス値が小さいものから描画することが好ましい。なぜなら、デプス値が小さい、より手前に表示されるべきグラフィック要素から先に描画することにより、描画能力や1ラインに描画するグラフィック要素の数が多すぎる等の理由により、仮に、1ラインに描画すべき全てのグラフィック要素の描画が、表示までに間に合わなかった場合でも、デプス値が大きい、より奥に表示されるべきグラフィック要素から先に描画する場合と比較して、表示後の見た目の印象が良くなるからである。また、デプス値が小さいグラフィック要素から描画することにより、より奥に表示されるべきグラフィック要素については、既に描画されたグラフィック要素と重なる部分については、描画が不要であるため、処理の高速化を図ることができるからである。

【0316】

(2)上記では、描画のため、スクリーンの1ライン分のデータを格納可能なラインバッファLB1,LB2をRPU9内に設けた。ただし、1ライン分より少ないピクセル数分のデータを格納する2つのピクセルバッファをRPU9内に設けることもできる。また、K(Kは2以上の整数)ライン分のデータを格納可能な2つのバッファをRPU9内に設けることもできる。

【0317】

(3)上記では、RPU9において、ダブルバッファ方式を採用したが、シングルバッファ方式を採用することもできるし、3以上のバッファを使用する方式を採用することもできる。

【0318】

(4)上記では、プリフェッチバッファ108の記憶容量とリサイクルバッファ110の記憶容量とを同一にする例を挙げたが、異ならせることもできる。

【0319】

(5)上記では、YSU19は、1つのポリゴン構造体インスタンスのソートが確定するたびに、パルスPPLを出力したが、所定数のポリゴン構造体インスタンスのソートが確定するたびに、パルスPPLを出力することもできる。パルスSPLについても同様である。

【0320】

(6)上記では、テクスチャデータの色の指定に、カラーパレットを用いる間接指定方式を採用したが、各テクセルの色を直接指定する直接指定方式を採用することもできる。

【0321】

以上、本発明を実施例により詳細に説明したが、当業者にとっては、本発明が本願中に説明した実施例に限定されるものではないということは明らかである。本発明は、請求の範囲の記載により定まる本発明の趣旨及び範囲を逸脱することなく修正及び変更態様として実施することができる。従って、本願の記載は、例示説明を目的とするものであり、本発明に対して何ら制限的な意味を有するものではない。

【技術分野】

【0001】

本発明は、フレームバッファを使用せずに品質の高い三次元イメージの表示を可能とする描画装置及びその関連技術に関する。

【背景技術】

【0002】

従来では、三次元イメージを表示する場合、1フレーム以上のイメージデータを描画することが可能なフレームバッファやビデオメモリを、画像生成装置に実装するのが一般的であった(特開平6−348861号公報、特開平7−282270号公報)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平6−348861号公報

【特許文献2】特開平7−282270号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、画像生成装置にフレームバッファ等を実装しようとすると、少なくとも一つのイメージ全体を格納する容量のメモリが必要不可欠となり、コストが高くなる。高品質の三次元イメージを表示するために、ダブルバッファ方式を採用すると、少なくとも二つのフレームバッファを格納可能な容量のメモリが必要となるため、更にコストが高くなる。

【0005】

一方、二次元イメージを表示する場合は、必ずしもフレームバッファは必要なく、ラインバッファでも十分である。しかし、ラインバッファを用いて、三次元イメージを表示しようとすると、従来の画像生成装置の描画能力では、描画可能なポリゴンの数が限られてくる等、見る者が満足するような品質の高い表示を行うことが困難である。

【0006】

そこで、本発明は、少ない記憶容量の、描画のためのバッファを用いながらも、品質の高い三次元イメージの表示を可能とする描画装置及びその関連技術を提供することを目的とする。

【0007】

また、本発明の他の目的は、少ない記憶容量の、描画のためのバッファを用いながらも、半透明合成を可能として、より品質の高い三次元イメージの表示を可能とする描画装置及びその関連技術を提供することである。

【0008】

さらに、本発明の他の目的は、インタレーススキャンによる表示を行う場合においても、少ない記憶容量の、描画のためのバッファを用いながらも、品質の高い三次元イメージの表示を可能とする描画装置及びその関連技術を提供することである。

【課題を解決するための手段】

【0009】

本発明の第1の観点によれば、描画装置は、それぞれが複数のピクセルから構成される平行な複数のラインを、そのラインに垂直な方向に並べて構成されるスクリーンに、多角形状のグラフィック要素を含むグラフィック要素ごとの表示情報に基づいて、前記グラフィック要素の組み合わせからなるスクリーンイメージを表示するための描画を行う描画装置であって、前記表示情報に含まれる、前記グラフィック要素の前記ラインに垂直な方向の位置を示す座標が、昇順あるいは降順のいずれかで並ぶように、前記グラフィック要素ごとの前記表示情報を並べ替えるソート手段と、前記ソート手段が並べ替えた前記表示情報を順番に読み出して、読み出した前記表示情報に基づいて、対応する前記グラフィック要素の描画を実行する描画手段と、を備える。

【0010】

この構成によれば、グラフィック要素のラインに垂直な方向の位置を示す座標が、昇順あるいは降順のいずれかで並ぶように、グラフィック要素ごとの表示情報を並べ替えている(ソート)。従って、ソート後の表示情報を順番に読み出して、描画処理を行うだけでよいため、描画のたびに、全ての表示情報の中から、そのとき描画すべき表示情報を検索する処理が不要になり、処理を高速化できる。以上の結果、1フレーム以上のイメージを格納するための大容量のバッファ(フレームバッファ等)を実装する必要は必ずしもなく、より容量の小さいバッファ(ラインバッファや、1ラインに満たないピクセルを描画するピクセルバッファ等)を実装した場合であっても、多くのグラフィック要素を組み合わせたスクリーンイメージの表示が可能になる。特に、二次元イメージ表示のための描画処理と比較して、高い処理能力が必要な三次元イメージ表示のための描画処理にも好適である。

【0011】

ここで、昇順とは、小さいほうから大きいほうへの順に並べることを意味し、降順とは、大きいほうから小さいほうへの順に並べることを意味する。

【0012】

上記描画装置において、前記描画手段は、前記スクリーンを構成する前記ピクセルのうち第1の所定数分のピクセル情報を格納可能であって、格納した前記ピクセル情報を前記スクリーンイメージを表示するために出力し、出力した前記ピクセル情報が格納されていた位置に、前記スクリーンイメージを表示するための新たなピクセル情報を格納する第1バッファ(例えば、図1のラインバッファLB1,LB2に相当)と、第2の所定数分の前記グラフィック要素の前記表示情報を格納可能であって、前記表示情報に基づく前記ピクセル情報が前記第1バッファに格納された後に、当該表示情報に基づく他のピクセル情報を前記第1バッファに格納するために、当該表示情報が再利用可能なときに、再利用のために送られてくる順番で、当該表示情報を格納し、前記第1バッファが前記新たなピクセル情報を格納する期間が到来したときに、格納した順番で前記表示情報を出力する第2バッファ(例えば、図1のリサイクルバッファ110に相当)と、前記ソート手段が並べ替えた順番で読み出された前記表示情報のうち、前記第1バッファに格納すべき期間が到来した前記新たなピクセル情報を生成するための前記表示情報に含まれる表示深度情報と、前記第2バッファから出力される前記表示情報に含まれる表示深度情報と、を比較し、予め定められた規則に従って、いずれかの前記表示情報を選択して先に出力する比較手段と、前記比較手段から出力された前記表示情報に基づいて前記ピクセル情報を生成し、前記生成したピクセル情報を前記第1バッファに書き込む書き込み手段と、を含む。

【0013】

この構成によれば、第1バッファへの新たなピクセル情報の書き込み(新たなピクセルの描画)のために、表示情報が再利用可能な場合は、その表示情報は、第2バッファに格納される。このため、同じ表示情報を使用する新たなピクセルの描画のたびに、ソート後の全ての表示情報が格納されたメモリから、その同じ表示情報を繰り返し読み出す処理が不要になって、より処理の高速化を図ることができる。

【0014】

また、比較手段を設けて、ソート手段が並べ替えた順番で新たに読み出された表示情報と、再利用のための第2バッファに格納された表示情報と、の描画順序(つまり、これら表示情報に基づくピクセルの描画順序)を判定している。このため、判定終了後に、再利用可能な表示情報を第2バッファに送って順番に格納するだけで、第2バッファには、再利用可能な表示情報について、適切な描画順序で表示情報が格納される。このように、第2バッファには、再利用可能な表示情報について適切な描画順序で格納されているところ、これらは、ソート手段が並べ替えた順番で新たに読み出された表示情報との間で、さらに描画順序が判定されるので、常に適切な描画順序での描画が可能となる。

【0015】

上記描画装置において、複数の前記グラフィック要素を表示する場合であって、その複数のグラフィック要素の前記座標が同じ場合、前記ソート手段は、その複数のグラフィック要素に対しては、前記表示情報に含まれる表示深度情報が示す表示深度の昇順あるいは降順のいずれかで前記表示情報を並べる。

【0016】

この構成によれば、複数のグラフィック要素を表示する場合であって、その複数のグラフィック要素の座標が同じ場合、スクリーンを構成する各ラインにおいて、表示深度の昇順あるいは降順のいずれかで表示情報が並べられる。従って、各ラインにおいて、表示情報に基づくグラフィック要素は、表示深度の大きいもの順あるいは小さいもの順のいずれかで描画される。表示深度の昇順で表示情報を並べる場合は、グラフィック要素は、表示深度が小さいもの順で描画されるので、仮に表示深度が大きいグラフィック要素の描画処理が間に合わなかった場合でも、表示後の見た目の印象を良くすることができる。一方、表示深度の降順で表示情報を並べる場合は、グラフィック要素は、表示深度が大きいもの順で描画されるので、半透明合成を適切に行うことができる。何故ならば、半透明のグラフィック要素の描画色は、当該グラフィック要素の奥にあるグラフィック要素の描画色に依存するため、グラフィック要素を奥から順に描画する必要がある。

【0017】

この描画装置において、複数の前記グラフィック要素が、前記スクリーンの先頭ラインに表示すべきピクセルを含む場合、前記ソート手段は、その複数のグラフィック要素に対しては、前記座標の大小に関係なく、前記表示深度の昇順あるいは降順のいずれかで前記表示情報を並べる。

【0018】

この構成によれば、複数のグラフィック要素が、スクリーンの先頭ラインに表示すべきピクセルを含む場合、それらの座標に関係なく、つまり、それらの座標を同一とみなして、表示深度の昇順あるいは降順のいずれかで表示情報が並べられる。従って、先頭ラインにおいて、表示情報に基づくグラフィック要素は、表示深度の大きいもの順あるいは小さいもの順のいずれかで描画される。表示情報を表示座標順(グラフィック要素の、ラインに垂直な方向の位置を示す座標順)でソートし、表示座標の同じものについては表示深度順でソートする場合、先頭ラインの描画においては、必ずしも表示深度の昇順または降順での描画が保証されないが、この構成によれば、先頭ラインから表示深度順での描画を行うことが可能となる。表示深度の昇順で並べる効果及び降順で並べる効果は上記と同様である。

【0019】

上記描画装置において、前記ソート手段は、所定数分の前記グラフィック要素の前記表示情報の並べ替えが完了するたびに、その旨を前記描画手段に通知し、前記描画手段は、前記ソート手段からの前記通知を受けて、並べ替えが完了した前記表示情報を順次読み出す。

【0020】

この構成によれば、表示情報のソートが確定するたびに、その都度、その旨の通知がなされるので、描画手段は、全表示情報のソートの完了を待つことなく、逐次、表示情報を読み込むことができる。

【0021】

この描画装置において、前記所定数分の前記グラフィック要素の前記表示情報は、1つ分の前記グラフィック要素の前記表示情報である。

【0022】

この構成によれば、1つ分のグラフィック要素のソートが確定するたびに、その旨の通知がなされるので、描画手段は、ソートが確定したグラフィック要素の表示情報をソート完了直後から読み込むことができる。

【0023】

上記描画装置において、前記描画手段は、第1バッファ及び第2バッファに加えて、さらに、第3バッファ(例えば、図1のプリフェッチバッファ108に相当)を含み、この第3バッファは、第3の所定数分の前記グラフィック要素の前記表示情報を格納可能であって、前記ソート手段が並べ替えた順番で読み出される前記表示情報を、読み出された順番で格納し、前記第1バッファに格納すべき期間が到来した前記新たなピクセル情報を生成するための前記表示情報を格納された順番で出力し、前記比較手段は、前記第3バッファから出力される前記表示情報に含まれる表示深度情報と、再利用のために送られてきた順番で格納された前記第2バッファから出力される前記表示情報に含まれる表示深度情報と、を比較し、前記予め定められた規則に従って、いずれかの前記表示情報を選択して先に出力する。

【0024】

この構成によれば、第3バッファが設けられ、この第3バッファは、ソート手段がソートした順番での表示情報の入力タイミングと比較手段への表示情報の出力タイミングとの緩衝機構である。これにより、ソート手段がソートした順番での表示情報の入力の、描画手段にとっての待ち時間を削減できる。

【0025】

上記描画装置において、前記予め定められた規則は、前記比較の結果、大きい前記表示深度を示す前記表示深度情報を含む前記表示情報を選択することである。

【0026】

この構成によれば、グラフィック要素は、表示深度の大きいもの順で描画される。その結果、半透明合成を適切に行うことができる。

【0027】

上記描画装置において、前記ソート手段が並べ替えを実行する際の前記グラフィック要素の前記座標は、前記グラフィック要素の頂点の座標であって、最も大きい座標あるいは最も小さい座標のいずれかである。

【0028】

この構成によれば、全てのグラフィック要素に対して同じ条件でソートができるので、正しい描画順序で描画を行うことができる。

【0029】

上記描画装置において、前記第1バッファは、少なくとも1つの前記ラインを構成する複数の前記ピクセル情報を格納するバッファである。

【0030】

この構成によれば、フレームバッファを使用する場合よりもコストを低く抑えることができる。また、1ラインに満たないピクセルを格納するピクセルバッファを使用する場合よりも簡素な回路構成で(簡単な制御で)描画を実現できる。

【0031】

上記描画装置において、前記ソート手段は、前記表示情報の並べ替えを、ヒープソートにより実行する。

【0032】

この構成によれば、表示情報のソートが1つずつ確定されるので、ソートの確定のたびに、その旨を通知する機構を容易に実現できる。また、全表示情報のソートに必要な時間のバラツキを少なくできる。

【0033】

上記描画装置において、前記ソート手段は、前記グラフィック要素としてのポリゴンを表示するための前記表示情報と、前記グラフィック要素としてのスプライトを表示するための前記表示情報と、で独立して前記並べ替えを実行する。

【0034】

この構成によれば、ポリゴンのための表示情報と、スプライトのための表示情報と、の形式及びサイズが異なっている場合でも容易にソートが可能であり、表示情報を格納するためのメモリ領域の使用効率も高まる。

【0035】

この描画装置において、前記描画手段は、前記ソート手段が並べ替えた前記ポリゴンのための前記表示情報と、前記ソート手段が並べ替えた前記スプライトのための前記表示情報と、を前記ソート手段による並べ替えの規則に準じてマージソートするマージソート手段をさらに含む。

【0036】

この構成によれば、ポリゴン及びスプライトが独立してソートされた場合であっても、描画処理の前にポリゴンのための表示情報群とスプライトのための表示情報群がマージソートされるため、適切な描画処理が可能となる。

【0037】

本発明の第2の観点によると、描画装置は、それぞれが複数のピクセルから構成される平行な複数のラインを、そのラインに垂直な方向に並べて構成されるスクリーンに、多角形状のグラフィック要素を含むグラフィック要素ごとの表示情報に基づいて、インタレーススキャンにより前記グラフィック要素の組み合わせからなるスクリーンイメージを表示するための描画を行う描画装置であって、偶数フィールドを表示するために、前記グラフィック要素ごとの表示情報を、第1の規則に従って並べ替え、かつ、奇数フィールドを表示するために、前記グラフィック要素ごとの表示情報を、第2の規則に従って並べ替えるソート手段と、前記奇数フィールドを表示する場合、その表示のために前記ソート手段が並べ替えた前記表示情報を順番に読み出して、読み出した前記表示情報に基づいて、対応する前記グラフィック要素の描画を実行し、かつ、前記偶数フィールドを表示する場合、その表示のために前記ソート手段が並べ替えた前記表示情報を順番に読み出して、読み出した前記表示情報に基づいて、対応する前記グラフィック要素の描画を実行する描画手段と、を備え、前記第1の規則は、前記表示情報に含まれる、前記グラフィック要素の前記ラインに垂直な方向の位置を示す座標が、昇順あるいは降順のいずれかで並ぶように、前記グラフィック要素ごとの前記表示情報を並べ替える際に、前記座標が、スキャンする奇数ライン又はその1つ前の偶数ラインを示す前記グラフィック要素については、当該グラフィック要素の前記座標が同一であるとして、前記表示情報に含まれる表示深度情報が示す表示深度の昇順あるいは降順のいずれかで前記表示情報を並べることであり、前記第2の規則は、前記表示情報に含まれる、前記グラフィック要素の前記座標が、昇順あるいは降順のいずれかで並ぶように、前記グラフィック要素ごとの前記表示情報を並べ替える際に、前記座標が、スキャンする偶数ライン又はその1つ前の奇数ラインを示す前記グラフィック要素については、前記座標が同一であるとして、前記表示情報に含まれる表示深度情報が示す表示深度の昇順あるいは降順のいずれかで前記表示情報を並べることである。

【0038】

この構成によれば、第1の観点による発明と同様の作用効果を奏することに加えて、次の作用効果を奏する。インタレーススキャンによってスクリーンイメージが表示される場合、表示座標(グラフィック要素の、ラインに垂直な方向の位置を示す座標)が飛び越し走査により飛び越されたラインを示す表示情報と、表示座標が描画対象のラインを示す表示情報とが、表示対象ラインの描画処理において共に読み出される。したがって、これらの表示情報の示す表示座標を同じ値とみなし、表示深度順にソートを行うことにより、インタレーススキャンの場合でも表示深度順での描画処理が保証される。表示深度の昇順で並べる効果及び降順で並べる効果は上記と同様である。

【0039】

以上の結果、インタレーススキャンによる表示を行う場合においても、少ない記憶容量の、描画のためのバッファ(第1バッファ)を用いながらも、品質の高い三次元イメージの表示を実現できる。

【0040】