携帯可能電子装置、および、携帯可能電子装置におけるデータ処理方法

【課題】通信の不具合によってデータ異常が発生した場合、データ異常となったデータを正常なデータに更新することができ、ICカードおよびICカードのデータメモリを効率的に運用できる。

【解決手段】種々のデータを記憶するデータメモリ22と、リーダライタとのデータ通信を行うための通信部25と、リーダライタから与えられるコマンドに応じた種々の処理を実行するCPU21とを有するICカード1は、リーダライタから受信したコマンドが異常データ確認コマンドである場合、データメモリ22に記憶されているデータのうちデータ異常となっているデータを検出し、データ異常が検出されたデータを示す情報を含むレスポンスデータをリーダライタへ通知し、データ異常が検出されたデータを示す情報をリータライタへ通知した後に当該リーダライタからデータ異常が検出されたデータに対する更新を要求する異常データ更新コマンドを受信した場合、当該異常データ更新コマンドに応じて異常データ更新を実行する。

【解決手段】種々のデータを記憶するデータメモリ22と、リーダライタとのデータ通信を行うための通信部25と、リーダライタから与えられるコマンドに応じた種々の処理を実行するCPU21とを有するICカード1は、リーダライタから受信したコマンドが異常データ確認コマンドである場合、データメモリ22に記憶されているデータのうちデータ異常となっているデータを検出し、データ異常が検出されたデータを示す情報を含むレスポンスデータをリーダライタへ通知し、データ異常が検出されたデータを示す情報をリータライタへ通知した後に当該リーダライタからデータ異常が検出されたデータに対する更新を要求する異常データ更新コマンドを受信した場合、当該異常データ更新コマンドに応じて異常データ更新を実行する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、たとえば、書込み或いは書換えが可能な不揮発性メモリ、および、CPUなどを有するIC(集積回路)チップを内蔵し、外部から供給されるコマンドに基づいて各種処理を実行するICカード等の携帯可能電子装置、および、携帯可能電子装置におけるデータ処理方法に関する。

【背景技術】

【0002】

近年、携帯可能な電子装置としてのICカードが様々な分野で広く普及してきている。ICカードは、CPU、各種メモリおよび通信インターフェースなどを有するICチップが内蔵されている。このようなICカードは、たとえば、キャッシュカード、IDカード、プリペイドカード、ポイントカードなどの運用形態で利用される。このようなICカードは、各種の用途で使用する各種データを様々な形式のファイルでデータメモリに記憶する。たとえば、ICカードは、データ列(レコード)単位でデータを格納するファイルを用いて、ICカードを用いた取引処理の履歴を示すログデータをデータ列ごとに記憶する。

【0003】

また、ICカードは、一般に、外部装置であるリーダライタからの電源供給を受けつつ、外部装置からのコマンドに応じた処理を実行する。このようなICカードでは、処理を実行中に外部装置からの電源供給が遮断されると、処理が強制的に中断される。たとえば、所定位置にセットされているICカードへリーダライタから電源を供給するシステムでは、上記所定位置からICカードが引き抜かれると、電源供給が遮断されて処理が強制的に中断することになる。

【0004】

データの書込みあるいは書換え等のデータ更新処理中に処理が中断すると、当該データは、正しい状態に更新されず、破壊された状態となることが多い。特に、非接触式のICカードは、無線通信でリーダライタからの電源供給を受ける形態である。このため、非接触式のICカードは、処理中に電源供給が遮断されやすく、上記のようなデータ破壊が発生する可能性も高い。データが正しい状態に更新できなかった場合、従来のICカードは、データの破壊が発生したものとして、当該データの記憶領域を使用不可としたり、ICカード自体を破棄(交換)したりする。しかしながら、セキュリティ攻撃ではない通信の不具合などによりデータ破壊が生じた場合に、当該データの記憶領域を破棄したり、ICカード自体を破棄したりする形態では、ICカードを効率的に運用できない。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−282989号公報

【特許文献2】特開2004−258624号公報

【非特許文献】

【0006】

【非特許文献1】ISO/IEC7816−4

【発明の概要】

【発明が解決しようとする課題】

【0007】

この発明の一形態は、データ異常が発生した場合であっても、正常なデータに更新することができる携帯可能電子装置および携帯可能電子装置におけるデータ処理方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

この発明の一形態としての携帯可能電子装置は、種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により前記外部装置から異常データ確認コマンドを受信した場合、前記記憶手段に記憶されているデータのうちデータ異常となっているデータを検出する検出手段と、この検出手段によりデータ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する通知手段とを有する。

【0009】

この発明の一形態としての携帯可能電子装置は、種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータに対する異常データ更新が可能か否かを判定する実行条件判定手段と、この実行条件判定手段により異常データ更新として指定されたデータの更新が可能であると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する異常データ更新手段とを有する。

【0010】

この発明の一形態としての携帯可能電子装置におけるデータ処理方法は、種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により受信したコマンドに応じた処理を実行する処理手段とを有する携帯可能電子装置における方法であって、前記外部装置から受信したコマンドが異常データ確認コマンドである場合、前記記憶手段に記憶されているデータのうちデータ異常となっているデータを検出し、前記検出によりデータ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する。

【0011】

この発明の一形態としての携帯可能電子装置におけるデータ処理方法は、種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により受信したコマンドに応じた処理を実行する処理手段とを有する携帯可能電子装置における方法であって、前記外部装置から異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータに対する異常データ更新が実行可能か否かを判定し、この判定により異常データ更新コマンドで指定されたデータの更新が実行可能であると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する。

【発明の効果】

【0012】

この発明の一形態は、データ異常が発生した場合であっても、正常なデータに更新することができる携帯可能電子装置および携帯可能電子装置におけるデータ処理方法を提供できる。

【図面の簡単な説明】

【0013】

【図1】図1は、ICカード(携帯可能電子装置)を含むICカードシステムの構成例を概略的に示す図である。

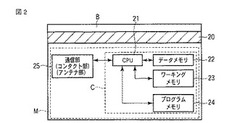

【図2】図2は、ICカードのハードウエア構成例を概略的に示すブロック図である。

【図3】図3は、データメモリに格納されるファイルの構成例を示す図である。

【図4】図4は、データ管理情報の構成例を示す図である。

【図5】図5は、制御情報により制御(設定)されるデータのフォーマットを示す図である。

【図6】図6は、ICカードが正常な処理を行う場合のICカードとリーダライタとの通信手順を概略的に説明するための図である。

【図7】図7は、ICカードでデータの更新エラーが発生した場合のICカードとリーダライタとの通信手順を概略的に説明するための図である。

【図8】図8は、異常データ確認コマンドの構成例を示す図である。

【図9】図9は、異常データ確認コマンドに対するレスポンスデータの構成例を示す図である。

【図10】図10は、異常データ更新コマンドの構成例を示す図である。

【図11】図11は、異常データ更新コマンドに対するレスポンスデータの構成例を示す図である。

【図12】図12は、異常データ確認処理の流れを説明するためのフローチャートである。

【図13】図13は、異常データ更新処理の流れを説明するためのフローチャートである。

【発明を実施するための形態】

【0014】

以下、この発明の実施の形態について図面を参照して説明する。

図1は、本発明の実施の形態に係るICカード(携帯可能電子装置)1を含むICカードシステムの構成例を概略的に示すものである。

図1に示すように、本ICカードシステムは、情報センタ2、通信網3、PC4、リーダライタ5などにより構成されている。上記情報センタ2は、通信網3を介してPC4に接続されている。上記情報センタ2は、本ICカードシステムに利用されるデータを総括的に管理するサーバ装置である。本ICカードシステムにおいて、上記情報センタ2は、各PC4に対する上位装置として機能する。また、上記通信網3は、たとえば、公衆電話網あるいは公衆無線通信網などの通信網である。

【0015】

上記PC4は、パーソナルコンピュータなどの電子計算機である。上記PC4は、リーダライタ5に接続される。上記PC4は、上記リーダライタ5によりICカード1へコマンドを送信する機能、ICカード1から受信したデータを基に種々の処理を行う機能などを有している。

上記PC4は、図1に示すように、演算部11、ハードディスクドライブ(HDD)12、キーボード13、および、ディスプレイ14などを有している。

【0016】

上記演算部11は、CPU15、および、メモリ16などを有している。上記CPU15は、演算処理などのデータ処理を行うユニットである。上記CPU15は、プログラムに従ってデータ処理を行う。上記メモリ16は、作業用のデータを一時的に格納するワーキングメモリ、CPU15が実行するプログラムあるいは制御データなどが記憶されているプログラムメモリなどを有している。このような構成により、上記演算部11では、CPU15が上記メモリ16に記憶されているプログラムを実行することにより、種々の処理を実現している。

【0017】

上記ハードディスクドライブ(HDD)12は、書換え可能な大容量の不揮発性メモリである。上記HDD12は、補助記憶装置として機能する。たとえば、上記HDD12には、機密情報としての電子データファイル1,2,3,・・・が格納される。これらのHDD12に格納される電子データファイルのデータは、上記演算部11による制御に従ってリーダライタ5を介してICカード1へ送信できるようになっている。上記キーボード13は、当該PC4の操作員が操作する操作部として機能する。上記キーボード13は、操作員が種々の操作指示あるいはデータなどを入力するためのものである。上記ディスプレイ14は、上記PC4の制御により種々の情報を表示する表示装置である。

【0018】

上記リーダライタ5は、上記ICカード1との通信を行うためのインターフェース装置である。上記リーダライタ5は、図示しない内部メモリおよび通信制御部などを有する外部装置である。また、上記リーダライタ5は、上記ICカード1の通信方式に応じたインターフェースにより構成される。たとえば、上記ICカード1が接触型のICカードである場合、上記リーダライタ5は、ICカード1のコンタクト部と物理的かつ電気的に接続するための接触部などにより構成される。また、上記ICカード1が非接触型のICカードである場合、上記リーダライタ5は、ICカード1との無線通信を行うためのアンテナおよび通信制御などにより構成される。上記リーダライタ5では、上記ICカード1に対する電源供給、クロック供給、リセット制御、データの送受信が行われるようになっている。このような機能によってリーダライタ5は、上記PC4による制御に基づいて上記ICカード1の活性化(起動)、種々のコマンドの送信、及び送信したコマンドに対する応答の受信などを行なう。

【0019】

次に、上記ICカード1のハードウエア構成例について説明する。

上記ICカード1は、上記リーダライタ5を介してPC4などの上位装置から電力供給を受けた際、活性化される(動作可能な状態になる)ようになっている。例えば、上記ICカード1が接触型の通信機能を具備している場合、つまり、ICカード1が接触型のICカードで構成される場合、上記ICカード1は、通信インターフェースとしてのコンタクト部を介してリーダライタ5からの動作電源及び動作クロックの供給を受けて活性化される。

【0020】

また、上記ICカード1が非接触型の通信機能を具備している場合、つまり、上記ICカード1が非接触式のICカードで構成される場合、上記ICカード1は、通信インターフェースとしてのアンテナ及び変復調回路などを介してリーダライタ5からの電波を受信し、その電波から図示しない電源部により動作電源及び動作クロックを生成して活性化するようになっている。

【0021】

図2は、本実施の形態に係るICカード1のハードウエア構成例を概略的に示すブロック図である。

上記ICカード1は、本体Bを構成する筐体内にモジュールMが内蔵されている。上記モジュールMは、1つまたは複数のICチップCと通信用の外部インターフェース(通信部)とが接続された状態で一体的に形成され、ICカード1の本体B内に埋設されている。また、上記ICカード1のモジュールMは、図2に示すように、CPU(制御素子)21、データメモリ22、ワーキングメモリ23、プログラムメモリ24、および、通信部25などを有してしている。また、図2に示す構成例では、本体Bには、磁気ストライプ20が設けられている。

【0022】

上記CPU21は、当該ICカード1全体の制御を司るものである。上記CPU21は、上記プログラムメモリ24あるいは上記データメモリ22に記憶されている制御プログラムおよび制御データに基づいて動作することにより、種々の機能を実現する。たとえば、上記CPU21は、オペレーティングシステムのプログラムを実行することにより、当該ICカード1の基本的な動作制御を行う。また、上記CPU21は、当該ICカード1の利用目的に応じたアプリケーションプログラムを実行することにより、当該ICカード1の運用形態に応じた種々の動作制御を行う。

【0023】

上記データメモリ22は、例えば、EEPROM(Electrically Erasable Programmable Read Only Memory)あるいはフラッシュROMなどのデータの書き込み及び書換えが可能な不揮発性のメモリにより構成される。上記データメモリ22には、当該ICカード1の運用用途に応じた制御プログラムあるいは種々のデータが書込まれる。上記データメモリ22には、当該ICカード1の規格に応じた種々のファイルが定義され、それらのファイルに種々のデータが書き込まれる。上記データメモリ22に格納されるファイルの例については、後述する。

【0024】

上記ワーキングメモリ23は、RAMなどの揮発性のメモリである。また、上記ワーキングメモリ23は、CPU21が処理中のデータなどを一時保管するバッファとしても機能する。たとえば、上記ワーキングメモリ23には、カレント状態となっているファイルあるいはアプリケーションを示す情報なども格納される。

上記プログラムメモリ24は、予め制御用のプログラムや制御データなどが記憶されているマスクROMなどの不揮発性のメモリである。上記プログラムメモリ24には、当該ICカードの製造段階で制御プログラムあるいは制御データなどが記憶された状態でICカード1内に組み込まれる。上記プログラムメモリ24に記憶されている制御プログラムあるいは制御データは、当該ICカードの基本的な動作を司るものであり、予め当該ICカード1の仕様に応じて組み込まれるものである。

【0025】

上記通信部25は、上記リーダライタ5を介して上記PC4と通信するためのインターフェースである。当該ICカード1が接触型のICカードとして実現される場合、上記通信部25は、上記リーダライタ5と物理的かつ電気的に接触して信号の送受信を行うための通信制御部とコンタクト部とにより構成される。また、当該ICカード1が非接触型のICカードとして実現される場合、上記通信部25は、上記リーダライタ5との無線通信を行うための変復調回路などの通信制御部および電波を送受信するためのアンテナなどにより構成される。

【0026】

次に、上記データメモリ22に格納されるファイルについて説明する。

図3は、上記データメモリ22に格納されるファイルの構成例を示す図である。

図3では、複数のアプリケーションに関する情報が記憶される複数のファイルの構成例を示している。図3に示すようなファイル構成は、ISO/IEC7816−4で定義されている事項に基づくものである。図3に示すファイル構成では、ISO/IEC7816−4に定義される種々のファイルをツリー構造で管理する。

【0027】

図3に示すように、上記データメモリ22には、MF(Master File)、DF(Dedicated File)およびEF(Elementary File)などからなる階層構造を有する複数のファイルが定義される。図3に示す例では、最上階層のマスターファイル(MF)31の次の階層には、第1EF(キーEF)32、第1DF(DF1)33、第2DF(DF2)34および第3DF(DF3)35が存在している。上記第1DF(DF1)33の配下として、DF1の次の階層には、DF1の第1EF(EF1−1)36、および、DF1の第2EF(EF1−2)37が存在している。上記第2DF(DF2)34の配下として、DF2の次の階層には、DF2の第1EF(EF2−1)38、および、DF2の第2EF(EF2−2)39が存在している。

【0028】

上記MF31は、上記データメモリ22に格納されている各種ファイルに対するファイル構成において、最上位に位置する。上記各DF(DF1、DF2、DF3)は、それぞれアプリケーションに対応して設けられる。上記各DFは、各アプリケーションに相当するフォルダとして機能する。このため、上記データメモリ22には、少なくともアプリケーション数に相当する数のDFが定義される。上記各EFは、実データを格納するデータファイルである。すなわち、DFの配下の各EFは、DFが対応するアプリケーションで使用されるデータを格納する。また、EFは、図3に示すように、MF31直下の階層に設けることも可能である。図3に示す上記キーEF32は、アクセス権を確立するためのキー(鍵情報)などを格納するデータファイルである。

【0029】

また、DFに相当するアプリケーションの例としては、例えば、クレジット、IDカード、ポイントシステム等が挙げられる。図3に示す例では、DFに相当するアプリケーションとして、X社向けのアプリケーション(例えば、X社用クレジットカードのDF)、A社向けのアプリケーション(例えば、A社用ポイントシステムのDF)、および、B社向けのアプリケーション(例えば、B社用ポイントシステムのDF)を想定する。図3に示すファイル構成において、X社向けのアプリケーション、A社向けのアプリケーション、および、B社向けのアプリケーションは、それぞれDF1、DF2、DF3が設けられる。この場合、DF1の配下では、X社向けのアプリケーションで使用されるデータがEF1−1およびEF1−2に格納される。また、DF2の配下では、A社向けのアプリケーションで使用されるデータがEF2−1およびEF2−2に格納される。

【0030】

次に、データ管理情報の構成例について説明する。

図4は、データ管理情報の構成例を示す図である。

上記データメモリ22内における各々のデータは、図4に示すようなデータ管理情報で管理される。

上記データ管理情報40は、データメモリ(EEPROM)22内における管理領域に記憶される。上記データ管理情報40は、データ登録数41、制御情報42、および、空き領域43により構成される。

【0031】

上記データ登録数41は、当該管理領域に登録されている制御情報の総数を示すデータである。上記データ登録数41のデータは、管理対象とするデータ(つまり、制御情報)の追加および削除により変化する。上記制御情報42は、登録されている制御情報(群)である。上記空き領域43は、制御情報を追加登録することが可能な空き領域である。

【0032】

上記制御情報42は、図4に示すように、上記データ識別子情報45、上記設定アドレス情報46、上記設定可能サイズ情報47、および、上記セキュリティ条件情報48などから構成される。

上記データ識別子情報45は、データ(データ列)を識別するための識別子を示す情報である。上記データ識別子情報45は、外部装置がデータを指定するために用いられる。たとえば、ICカード1がリーダライタ5からアクセス対象とするデータの識別子を指定するコマンドを受信した場合、ICカード1は、指定された識別子と一致するデータ識別子情報45をアクセス対象のデータとして検索する。この結果として、ICカード1は、指定された識別子と一致するデータ識別子情報45のデータをアクセス対象とする。

【0033】

上記設定アドレス情報46は、上記データ識別子情報45で示される識別子が付与されているデータが記憶されているデータメモリ22上におけるアドレス(先頭アドレス)を示す情報である。すなわち、上記データ識別子情報45で示される識別子のデータは、設定アドレス情報46により示されるデータメモリ22上のアドレスに配置されている。

【0034】

上記設定可能サイズ情報47は、データとして設定可能なサイスを示す情報である。つまり、各制御情報が対応するデータは、上記設定可能サイズ情報47により定義される範囲内において、可変長で設定可能である。たとえば、上記設定可能サイズ情報47で指定される範囲を満足されていない場合(たとえば、指定範囲を超えるデータの書込みコマンドを受けた場合)、当該データに対するアクセスは、排除(禁止)される。

【0035】

上記セキュリティ条件情報48は、データに対するセキュリテイ条件を示す情報である。つまり、上記セキュリティ条件情報48は、当該制御情報のデータにアクセス(読出しあるいは書込み)する場合に、満足されるべきセキュリティ条件を示す。たとえば、上記セキュリティ条件情報48により示される条件が満足されていない場合、当該データへのアクセスは、排除(禁止)される。

【0036】

また、本実施の形態では、セキュリティ条件情報48としては、後述する異常データ確認コマンド(あるいは異常データ更新コマンド)に対する実行の可否を示す情報が格納される。データ異常であっても、外部装置からのデータ更新を受けないデータについては、セキュリティ条件情報48として異常データ確認コマンドの実行を不可を設定する。たとえば、如何なる条件であっても一切のデータ更新を禁止するようなデータに対しては、セキュリティ条件情報48として異常データ確認コマンドの実行不可が設定される。

【0037】

ただし、後述する異常データ更新コマンドは、通常のデータ更新とは異なり、後述するようなセキュリティ条件を満たした場合にのみ実行されるコマンドである。つまり、後述する異常データ更新処理は、セキュリティ性を確保した状態でのみ実行される処理である。このため、セキュリティ条件情報48により異常データ確認コマンドの実行を許可するデータであっても、当該データのセキュリティ性が高いものを想定している。

【0038】

たとえば、データ異常(エラー状態)となった場合にはそのままの状態で保持しておきたいデータについては、セキュリティ条件情報48として異常データ確認コマンドの実行不可が設定され、データ異常(エラー状態)となった場合には正しいデータに書き換えておきたいデータについては、セキュリティ条件情報48として異常データ確認コマンドの実行許可が設定される。

【0039】

次に、各データの構成について説明する。

図5は、上記のような制御情報により制御(設定)されるデータのフォーマットを示す図である。

図5に示すように、各データ50は、データ長管理情報51およびデータ部52により構成される。図5に示すデータ50は、データファイル全体であっても良いし、データファイル内のレコードであっても良い。上記データ長管理情報51は、当該データのヘッダ情報であり、データ部52のサイズを示す情報などである。上記データ部52は、当該データのデータ本体である。

【0040】

図5に示す構成例において、上記データ部52には、複数のデータ列53(53A、53B)が格納可能である。図5に示す例では、データ部52には、データ列53Aとデータ列53Bとが格納されている。各データ列53(53A、53B)は、ぞれぞれ識別子55(55A、55B)、長さ56(56A、56B)、実データ57(57A、57B)およびデータ正当性管理情報58(58A、58B)を有する。

【0041】

上記識別子55は、各データ50内におけるデータ列53を識別するための情報である。上記識別子55は、各データ列53ごとにユニークな情報である。上記長さ56は、実データ57のサイズを示す情報である。すなわち、上記長さ56に連続し、かつ、当該長さ56で示すデータ長分のデータは、当該識別子55で特定されるデータ列53における実データ57である。

【0042】

上記実データ57は、当該データ列53におけるデータの実体(本体)である。すなわち、上記識別子55、上記長さ56および上記データ正当性管理情報58が当該データ列の管理情報であるとすれば、それらの管理情報で管理されるデータの実体が実データ57である。。

上記データ正当性管理情報58は、データ列の正当性を確認するための管理情報である。たとえば、上記データ正当性管理情報58には、識別子、長さおよび実データの排他的論理和などにより、当該データ列の正当性を確認するのに使用される。

【0043】

次に、上記のようなデータに対するアクセスの手順について説明する。

まず、上記データに対する正常処理としてのアクセスの手順について説明する。

図6は、ICカード1が正常な処理を行う場合のICカード1とリーダライタ5との通信手順を概略的に説明するための図である。

【0044】

図6に示すように、ICカード1は、リーダライタ5からのリセット信号を受けて、ATR信号をリーダライタ5へ送り返す。ICカード1からATR信号を受信したリーダライタ5は、各種の取引コマンド(各データへのアクセス要求を含む種々のコマンド)を順次送信する。これらの取引コマンドに応じて、ICカード1は、データのアクセス制御を含む種々の処理を実行する。これの処理が正常に終了した場合、ICカード1は、リーダライタ5に対して正常終了および異常なしを示す応答を送信する。

【0045】

次に、上記データに対する処理にエラー(異常)が発生した場合のアクセスの手順について説明する。

図7は、ICカード1でデータの更新エラーが発生した場合のICカード1とリーダライタ5との通信手順を概略的に説明するための図である。

図7に示すように、ICカード1は、リーダライタ5からのリセット信号を受けて、ATR信号をリーダライタ5へ送り返す。ICカード1からATR信号を受信したリーダライタ5は、各種の取引コマンド(各データへのアクセス要求を含む種々のコマンド)を順次送信する。

【0046】

これらの取引コマンドのうちのデータ更新コマンドに対する処理にエラーが発生したものとする。たとえば、データ更新処理中にリーダライタ5からの電源供給が強制的に停止された場合(ICカード1が所定の処理位置から引き抜かれた場合など)、ICカード1では、データ更新がエラーとなる。たとえば、図5に示すデータ列53Aの更新処理がエラーとなった場合(実データ57Aの書換えが途中で中断された場合)、実データ57Aは、異常な値となる。この場合、当該データ列53Aは、データ正当性管理情報に基づく正当性の確認によって異常状態であることが判定される。

【0047】

このようなデータ更新エラーとなった後に、再び、リーダライタ5からのリセット信号を受けた場合、ICカード1は、ATR信号をリーダライタ5へ送り返す。ICカード1からATR信号を受信したリーダライタ5は、各種の取引コマンド(各データへのアクセス要求を含む種々のコマンド)を順次送信する。このような取引コマンドを受信した場合、ICカード1は、前回の取引処理が正常終了していない状態である旨の応答(異常有りを示す応答)をリーダライタ5へ通知する。

【0048】

ICカード1から前回の取引処理が正常終了していない旨の応答を受信した場合、上記リーダライタ5は、異常データの有無の確認を要求する異常データ確認コマンドを送信する。異常データ確認コマンドを受信した場合、ICカード1は、データメモリ22に記憶されている各データ列についてデータ異常があるか否かを判定する処理を行う。データ異常となっているデータ列を発見すると、ICカード1は、データ異常となっているデータ列を示す識別子を含む応答をリーダライタ5へ送信する。

【0049】

異常データの識別子を示す情報を受信した場合、リーダライタ5は、異常データとなっているデータ列に対する処理を行う。たとえば、ICカード1のデータメモリ22に記憶すべき情報をリーダライタ5の上位装置(たとえば、情報センタ2あるいはPC4)で管理している場合、つまり、異常と判定されたデータ列に書込むべき正しいデータを上位装置が管理している場合、リーダライタ5は、上位装置から異常と判定されたデータ列に書込むべき正しいデータを受信する。異常と判定されたデータ列に書込むべき正しいデータを受信した場合、リーダライタ5は、異常と判定されたデータ列を正しいデータで更新する旨のコマンド(通常のデータ更新コマンドとは異なる異常データ更新コマンド)をICカード1へ送信する。

【0050】

上記異常データ更新コマンドを受信すると、ICカード1は、指定されたデータ(異常データ)を正しいデータに更新する処理を行う。上記異常データ更新コマンドに応じたデータの更新が正常に完了すると、ICカード1は、更新完了を示す応答をリーダライタ5へ送信する。以上の処理によれば、ICカード1およびICカードシステムでは、データ更新処理において強制的な処理の中断によって発生したデータ異常を確実に確認することでできる。さらに、ICカード1およびICカードシステムでは、データ異常が確認されたデータを正しいデータに更新することが可能である。

【0051】

次に、上記異常データ確認コマンドについて説明する。

図8は、異常データ確認コマンド60の構成例を示す図である。

図8に示す異常データ確認コマンド60は、上述したように、リーダライタ5がICカード1に対して異常データの確認を指示する命令電文である。

【0052】

上記異常データ確認コマンド60は、コマンドヘッダ部61とLc部62とにより構成される。さらに、コマンドヘッダ部61は、コマンドの分類(CLA:class)63、命令(INS:instruction)64、第1パラメータ(P1)65および第2パラメータ(P2)66により構成されている。

【0053】

上記CLA63およびINS64は、当該コマンドが異常データ確認コマンドであることを示す情報が格納される。上記CLA63およびINS64としては、異常データ確認コマンドに対応づけたコード情報が格納される。上記ICカード1のCPU21は、CLA63およびINS64におけるコード情報が異常データ確認コマンドであることを判別する機能を有している。このような機能は、CPU21がプログラムメモリ24に記憶されているプログラムを実行することにより実現される。

【0054】

上記第1パラメータ65および第2パラメータ66は、当該異常データ確認コマンドのパラメータを示す情報である。たとえば、第1パラメータ65および第2パラメータ66には、異常データの確認対象とする範囲を限定する場合に、異常データの確認対象とする範囲を示すパラメータが格納される。Lc部62は、当該コマンドにデータが添付される場合にデータの長さを示す情報が格納される。ただし、本実施の形態では、異常データ確認コマンド60にはデータが添付されないものとする。

【0055】

図9は、異常データ確認コマンド60に対するレスポンスデータ70の構成例を示す図である。

図9に示すレスポンスデータ70は、リーダライタ5からの異常データ確認コマンドに対する処理を実行した後、ICカード1がリーダライタ5へ出力する応答電文である。このレスポンスデータ70は、データ部71、第1ステータスコード72および第2ステータスコード73から構成される。データ部71は、異常データの識別子を示す情報が格納される。ステータスコード72及び73は、当該レスポンスデータ70が異常データの確認結果として、異常なデータと判定されたデータ列を通知する情報であることを示すコードが格納される。

【0056】

図10は、異常データ更新コマンド80の構成例を示す図である。

図10に示す異常データ更新コマンド80は、上述したように、リーダライタ5がICカード1に対してデータ異常となっているデータを正しいデータに更新する異常データ更新処理の実行を要求する命令電文である。

上記異常データ更新コマンド80は、コマンドヘッダ部81、Lc部82およびデータ部83により構成される。さらに、コマンドヘッダ部81は、コマンドの分類(CLA:class)84、命令(INS:instruction)85、第1パラメータ(P1)86、第2パラメータ(P2)87を有する。

【0057】

上記CLA84およびINS85は、当該コマンドが異常データ更新コマンドであることを示す情報が格納される。上記CLA84およびINS85としては、異常データ更新コマンドに対応づけたコード情報が格納される。上記ICカード1のCPU21は、CLA84およびINS85におけるコード情報が異常データ更新コマンドであることを判別する機能を有している。このような機能は、CPU21がプログラムメモリ24に記憶されているプログラムを実行することにより実現される。なお、上記異常データ更新コマンドは、通常のデータ更新コマンドとは異なるコマンドである。従って、異常データ更新コマンドに対しては、通常のデータ更新コマンドとは異なるコード情報が定義される。

【0058】

上記第1パラメータ86および第2パラメータ87は、当該異常データ更新コマンドのパラメータを示す情報である。たとえば、上記第1パラメータ86には、異常データの更新対象となるデータ列を格納しているデータファイルとしてのEFを示すEF−IDが格納される。また、上記第2パラメータ87には、書き換え対象となるデータ列を示す識別子が格納される。

【0059】

上記Lc部82は、当該コマンドに添付されるデータの長さを示す情報(Lc)が格納される。図10に示す例では、異常データ更新コマンド80には、データ部83に更新すべきデータ列全体のデータが添付される。すなわち、上記データ部83に格納されるデータは、更新すべきデータ列全体のデータ(識別子+長さ+正常な実データ)である。上記Lc部82は、データ部83に格納されるデータ全体の長さを示す情報が格納される。

【0060】

図11は、異常データ更新コマンド80に対するレスポンスデータ90の構成例を示す図である。

図11に示すレスポンスデータ90は、リーダライタ5からの異常データ更新コマンド80に対する処理を実行した後、ICカード1がリーダライタ5へ出力する応答電文である。このレスポンスデータ90は、第1ステータスコード91および第2ステータスコード92から構成される。第1ステータスコード91及び第2ステータスコード92は、異常データ更新コマンド80に対する異常データの更新結果を示す情報である。たとえば、データ列を正常なデータに更新する処理が完了した場合、レスポンスデータ90のステータスコード91及び92は、異常データの更新完了を示すコードが格納される。

【0061】

次に、上記のような異常データ確認コマンド60に応じて実行する異常データ確認処理について詳細に説明する。

図12は、異常データ確認処理の流れを説明するためのフローチャートである。なお、図12に示すような各処理は、たとえば、CPU21がプログラムメモリ24に記憶されているプログラムを実行することにより実現される機能であるものとする。

【0062】

上記リーダライタ5からコマンドを受信した場合、上記ICカード1のCPU21は、コマンドヘッダ部におけるCLAおよびINSを確認することにより受信したコマンドの内容を判別する。ここでは、受信したコマンドのコマンドヘッダ部におけるCLAおよびINSが異常データ確認コマンド60を示すコード情報であるものとする。つまり、ICカード1は、異常データ確認コマンド60を受信したものとする(ステップS11)。

【0063】

上記異常データ確認コマンド60を受信した場合、上記CPU21は、データメモリ22の管理領域に記憶されているデータ管理情報から1つ目の制御情報42(#1)を読み込む(ステップS12)。1つ目の制御情報42を読み込むと、上記CPU21は、読み込んだ制御情報42における設定アドレス情報46に基づいて、当該制御情報42が対応するデータ列53全体として、識別子55、長さ56、実データ57およびデータ正当性管理情報58をワーキングメモリ23に読み出す(ステップS13)。

【0064】

1つのデータ列53全体をワーキングメモリ23上に読み出すと、CPU21は、当該データ列としての識別子、長さ、および、実データに対して、データの正当性を確認するための所定の演算を行う(ステップS14)。この演算は、データ正当性管理情報と比較するための値を算出するための演算(誤りチェック演算)である。この演算内容については、特定の方式に限定されるものではない。たとえば、上記演算は、全データのアンド演算であっても良いし、XOR(排他的論理和)演算であっても良いし、CRC演算であっても良い。上記演算が完了すると、CPU21は、上記演算により算出した値と当該データ列におけるデータ正当性管理情報として読み出した値とを比較することにより両者が一致するか否かを判定する(ステップS15)。

【0065】

上記比較の結果として両者が一致すると判定した場合(ステップS15、YES)、CPU21は、当該制御情報に対応するデータ列にはデータ異常がないものと判断する。この場合、CPU21は、次の制御情報が存在するか否かを判断する(ステップS16)。たとえば、次の制御情報が存在するか否かは、データ登録数と読み込んだ制御情報との数とに基づいて判定される。次の制御情報が存在すると判断した場合(ステップS16、YES)、CPU21は、データ管理情報から次の制御情報を読み込む(ステップS17)。次の制御情報を読み込むと、CPU21は、上記ステップS13へ戻り、上述した処理を繰り返し実行する。また、次の制御情報が無いと判断した場合(ステップS16、NO)、CPU21は、実行条件不備であることを示すステータスコードをセットしたレスポンスデータ(応答電文)をリーダライタ5へ送信する。

【0066】

また、上記比較の結果として上記演算により算出した値とデータ正当性管理情報の値とが一致しないと判定した場合(ステップS15、NO)、CPU21は、当該制御情報に対応するデータ列にはデータ異常があるものと判断する。この場合、CPU21は、当該制御情報42におけるセキュリティ条件情報48に基づいて、当該制御情報42が対応するデータ列53に対して異常データ確認コマンド60が実行可能か否かを確認する(ステップS20)。たとえば、当該データ列に対する異常データ確認コマンド60が実行不可である場合(ステップS20、実行不可)、CPU21は、セキュリティ異常であることを示すステータスコードをセットしたレスポンスデータ(応答電文)をリーダライタ5へ送信する(ステップS21)。

【0067】

また、当該データ列に対する異常データ確認コマンド60が実行許可である場合(ステップS20、実行許可)、CPU21は、ワーキングメモリ23に、異常データ確認コマンドに対する処理(つまり、異常データ確認処理)が正常したことを示す情報を記録する(ステップS22)。このワーキングメモリ23に記録した情報(異常データ確認処理が正常終了済みを示す情報)は、少なくとも後述する異常データ更新コマンドが実行されるまで保持される。これは、異常データ確認処理の正常終了済みであることが、後述する異常データ更新処理の実行条件となるためである。

【0068】

上記ワーキングメモリ23に異常データ確認処理済みである旨を記録すると、CPU21は、上記ワーキングメモリ23にデータが異常らしいと判定したデータ列の先頭アドレスとして当該データ列の識別子が記憶されているデータメモリ22上の先頭アドレスを記録する(ステップS23)。さらに、CPU21は、ワーキングメモリ23に記録した先頭アドレスに基づいて、データ異常があると判定されたデータ列の識別子を読み出す。データ異常があると判定されたデータ列の識別子を読み込むと、CPU21は、データ異常があるデータ列の識別子を示す情報をデータ部71にセットし、異常データ確認処理が正常終了したことを示すステータスコードをセットしたレスポンスデータ(応答電文)70をリーダライタ5へ送信する(ステップS24)。

【0069】

次に、上記のような異常データ更新コマンド80に応じて実行する異常データ更新処理について詳細に説明する。

図13は、異常データ更新処理の流れを説明するためのフローチャートである。なお、図13に示すような各処理は、たとえば、CPU21がプログラムメモリ24に記憶されているプログラムを実行することにより実現される機能であるものとする。

【0070】

上記リーダライタ5からコマンドを受信した場合、上記ICカード1のCPU21は、コマンドヘッダ部におけるCLAおよびINSを確認することにより受信したコマンドの内容を判別する。ここでは、受信したコマンドのコマンドヘッダ部81におけるCLA84およびINS85が異常データ更新コマンド80を示すコード情報であるものとする。つまり、ICカード1は、異常データ更新コマンド80を受信したものとする(ステップS31)。

【0071】

上記異常データ更新コマンド80を受信した場合、上記CPU21は、まず、異常データ確認コマンドが正常終了済みであるか否かを判定する(ステップS32)。この判定は、異常データ確認コマンドに対する応答状況を確認することにより実行される。上述した異常データ確認処理が実施済みである場合、上記ワーキングメモリ23には、異常データ確認処理が正常終了済みであることを示す情報が記録されている。したがって、CPU21は、ワーキングメモリ23に記憶されている情報を確認することにより、異常データ確認処理が終了済みか否かを確認する。

【0072】

上記ステップS32は、異常データ更新処理の実行条件を判定する処理である。本実施の形態では、異常データ確認コマンドが正常終了済みであることを異常データ更新処理の実行条件として想定している。ただし、異常データ更新処理の実行条件は、上記の例に限定されるものではなく、異常データ更新(たとえば、通常のデータ更新コマンドでは更新不可となるデータの更新)に対するセキュリティ性が確保できるものであれば良い。たとえば、異常データ更新処理は、異常データ確認コマンドが正常終了した直後であることを実行条件としても良い。この場合、異常データ確認コマンドの正常終了を外部装置へ通知した直後に、当該外部装置から異常データ更新コマンドを受信した場合にのみ、異常データ更新処理を開始する。

【0073】

この確認の結果として異常データ確認処理が実行済みでないと判断した場合(ステップS32、NO)、CPU21は、異常データ更新処理を実行するための条件が満たされていない(実行条件不備である)旨のステータスコードをセットした応答電文をリータライタ5へ送信する(ステップS33)。

【0074】

また、上記確認により異常データ確認処理が実行済みであると判断した場合(ステップS32、YES)、CPU21は、受信した異常データ更新コマンドで指定されたデータ列(つまり、異常データ更新処理の対象とするデータ列)が正当であるか否かを確認する(ステップS34)。すなわち、上記ステップS34の処理として、CPU21は、受信した異常データ更新コマンドにおけるデータ部に格納されているデータ列の識別子と上記異常データ確認処理によりデータ異常と判定されたデータ列の識別子とを比較する。上記異常データ確認処理において、ワーキングメモリ23には、データ異常と判定されたデータ列の識別子の先頭アドレスを示す情報が記録されている。従って、CPU21は、ワーキングメモリ23に記録されている先頭アドレスに基づいて、データ異常があると判定されたデータ列の識別子を読み出す。すなわち、CPU21は、読み出した識別子と異常データ確認コマンドのデータ部に格納されている識別子とが一致するか否かを判断する。

【0075】

上記判断によりデータ異常と判定されたデータ列の識別子と異常データ確認コマンドのデータ部に格納された識別子とが一致しないと判定した場合(ステップS34、NO)、CPU21は、異常データ更新処理が不可である旨のステータスコードをセットしたレスポンスデータ(応答電文)を上記リーダライタ5へ送信する(ステップS35)。この場合、CPU21は、データ異常と判定されたデータ列の識別子が異常データ確認コマンドで指定されたデータ列の識別子と不一致である旨を通知するようにしても良い。ただし、セキュリティにおける問題の可能性がある場合、上記レスポンスデータ90には更新処理が不可となった理由を示す情報を含めないようにする。

【0076】

また、上記判断によりデータ異常が判定されたデータ列の識別子と異常データ確認コマンド80のデータ部83に格納された識別子とが一致すると判定した場合(ステップS34、YES)、CPU21は、さらに、当該識別子で指定されるデータ列の長さが正当であるか否かを確認する(ステップS36)。上記ステップS36の処理として、CPU21は、受信した異常データ更新コマンドのデータ部83に格納された更新用のデータの長さ(つまり、異常データ更新コマンドのLc部82に格納される長さ)とデータ異常が判定されたデータ列の長さ(ワーキングメモリ23に記録されている先頭アドレスにより識別子の記憶位置が特定されるデータ列の長さ)とが一致するか否かを判定する。

【0077】

上記判定により更新用のデータの長さとデータ異常が判定されたデータ列の長さとが一致しないと判定した場合(ステップS36、NO)、CPU21は、異常データ更新処理が不可である旨のステータスコードをセットしたレスポンスデータ(応答電文)90を上記リーダライタ5へ送信する(ステップS37)。この場合、CPU21は、データ異常と判定されたデータ列の長さ、あるいは、異常データ確認コマンドで指定された更新用のデータの長さが異常である旨を通知するようにしても良い。ただし、セキュリティにおける問題の可能性がある場合、上記レスポンスデータ90には、更新処理が不可となった理由を示す情報を含めないようにする。

【0078】

また、上記判定により更新用のデータの長さとデータ異常が判定されたデータ列の長さとが一致すると判定した場合(ステップS36、YES)、CPU21は、当該異常データ更新コマンド80のデータ部83に格納されている更新用のデータ(識別子、長さ、および、実データ)に対する所定の演算(誤りチェック用の演算)によりデータ正当性管理情報を算出する(ステップS38)。これにより、データ異常が判定されたデータ列に対する正しい値として、識別子、長さ、実データおよびデータ正当性管理情報が得られる。

【0079】

上記データ正当性管理情報を算出することによりデータ列全体の正しい値が得られると、CPU21は、データ異常が判定されたデータ列全体を、当該データ列の正しい値として得られた識別子、長さ、実データおよいびデータ正当性管理情報に書き換える(ステップS39)。すなわち、CPU21は、ワーキングメモリ23に記録しているデータ異常が判定されたデータ列の先頭アドレスから、異常データ更新コマンドのデータ部として与えられたデータ(識別子、長さおよび実データ)と所定の演算により算出されたデータ正当性管理情報とを上書きする。

【0080】

上記のようなデータ異常が判定されたデータ列全体に対するデータの書換えが完了すると、CPU21は、異常データ更新処理が正常終了したことを示すステータスコードをセットしたレスポンスデータ(応答電文)90を上記リーダライタ5へ送信する(ステップS40)。

【0081】

上記のように、本実施形態では、ICカード1は、リーダライタ5から受信したコマンドが異常データ確認コマンドである場合、データメモリ22に記憶されているデータ列からデータ異常となっているデータ列を検出し、データ異常が検出されたデータ列を示す識別子を含む異常データ確認処理の正常終了を示す応答をリーダライタ5へ送信する。さらに、上記ICカード1は、上記リーダライタ5から異常データ更新コマンドを受信した場合、異常データ更新処理の実行条件が満たされていれば、当該異常データ更新コマンドに応じてデータ異常となったデータを正しいデータに更新する処理を実行する。異常データ更新処理の実行条件としては、異常データ確認処理が正常終了済みであること、あるいは、異常データ確認処理が正常終了した直後であること等がある。

【0082】

上記のような実施の形態によれば、ICカード1では、通信の不具合によってデータ異常が発生した場合、データ異常となったデータを正常なデータに更新することができる。この結果として、データ異常が発生してもICカード1におけるデータメモリ22の記憶領域あるいはICカード1自体を無駄にすることなく、ICカード1およびICカード1におけるデータ領域の効率的な運用が実現できる。

【符号の説明】

【0083】

B…本体、M…モジュール、C…ICチップ、1…ICカード、2…情報センタ、4…PC、5…リーダライタ、21…CPU(制御素子)、22…データメモリ、23…ワーキングメモリ、24…プログラムメモリ、25…通信部、40…データ管理情報、42…制御情報、45…データ識別子情報、46…設定アドレス情報、47…設定可能サイズ情報、48…セキュリティ条件情報、53(53A、53B)…データ列、55(55A、55B)…識別子、56(56A、56B)…長さ、57(57A、57B)…実データ、58(58A、58B)…データ正当性管理情報。

【技術分野】

【0001】

この発明は、たとえば、書込み或いは書換えが可能な不揮発性メモリ、および、CPUなどを有するIC(集積回路)チップを内蔵し、外部から供給されるコマンドに基づいて各種処理を実行するICカード等の携帯可能電子装置、および、携帯可能電子装置におけるデータ処理方法に関する。

【背景技術】

【0002】

近年、携帯可能な電子装置としてのICカードが様々な分野で広く普及してきている。ICカードは、CPU、各種メモリおよび通信インターフェースなどを有するICチップが内蔵されている。このようなICカードは、たとえば、キャッシュカード、IDカード、プリペイドカード、ポイントカードなどの運用形態で利用される。このようなICカードは、各種の用途で使用する各種データを様々な形式のファイルでデータメモリに記憶する。たとえば、ICカードは、データ列(レコード)単位でデータを格納するファイルを用いて、ICカードを用いた取引処理の履歴を示すログデータをデータ列ごとに記憶する。

【0003】

また、ICカードは、一般に、外部装置であるリーダライタからの電源供給を受けつつ、外部装置からのコマンドに応じた処理を実行する。このようなICカードでは、処理を実行中に外部装置からの電源供給が遮断されると、処理が強制的に中断される。たとえば、所定位置にセットされているICカードへリーダライタから電源を供給するシステムでは、上記所定位置からICカードが引き抜かれると、電源供給が遮断されて処理が強制的に中断することになる。

【0004】

データの書込みあるいは書換え等のデータ更新処理中に処理が中断すると、当該データは、正しい状態に更新されず、破壊された状態となることが多い。特に、非接触式のICカードは、無線通信でリーダライタからの電源供給を受ける形態である。このため、非接触式のICカードは、処理中に電源供給が遮断されやすく、上記のようなデータ破壊が発生する可能性も高い。データが正しい状態に更新できなかった場合、従来のICカードは、データの破壊が発生したものとして、当該データの記憶領域を使用不可としたり、ICカード自体を破棄(交換)したりする。しかしながら、セキュリティ攻撃ではない通信の不具合などによりデータ破壊が生じた場合に、当該データの記憶領域を破棄したり、ICカード自体を破棄したりする形態では、ICカードを効率的に運用できない。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−282989号公報

【特許文献2】特開2004−258624号公報

【非特許文献】

【0006】

【非特許文献1】ISO/IEC7816−4

【発明の概要】

【発明が解決しようとする課題】

【0007】

この発明の一形態は、データ異常が発生した場合であっても、正常なデータに更新することができる携帯可能電子装置および携帯可能電子装置におけるデータ処理方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

この発明の一形態としての携帯可能電子装置は、種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により前記外部装置から異常データ確認コマンドを受信した場合、前記記憶手段に記憶されているデータのうちデータ異常となっているデータを検出する検出手段と、この検出手段によりデータ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する通知手段とを有する。

【0009】

この発明の一形態としての携帯可能電子装置は、種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータに対する異常データ更新が可能か否かを判定する実行条件判定手段と、この実行条件判定手段により異常データ更新として指定されたデータの更新が可能であると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する異常データ更新手段とを有する。

【0010】

この発明の一形態としての携帯可能電子装置におけるデータ処理方法は、種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により受信したコマンドに応じた処理を実行する処理手段とを有する携帯可能電子装置における方法であって、前記外部装置から受信したコマンドが異常データ確認コマンドである場合、前記記憶手段に記憶されているデータのうちデータ異常となっているデータを検出し、前記検出によりデータ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する。

【0011】

この発明の一形態としての携帯可能電子装置におけるデータ処理方法は、種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により受信したコマンドに応じた処理を実行する処理手段とを有する携帯可能電子装置における方法であって、前記外部装置から異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータに対する異常データ更新が実行可能か否かを判定し、この判定により異常データ更新コマンドで指定されたデータの更新が実行可能であると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する。

【発明の効果】

【0012】

この発明の一形態は、データ異常が発生した場合であっても、正常なデータに更新することができる携帯可能電子装置および携帯可能電子装置におけるデータ処理方法を提供できる。

【図面の簡単な説明】

【0013】

【図1】図1は、ICカード(携帯可能電子装置)を含むICカードシステムの構成例を概略的に示す図である。

【図2】図2は、ICカードのハードウエア構成例を概略的に示すブロック図である。

【図3】図3は、データメモリに格納されるファイルの構成例を示す図である。

【図4】図4は、データ管理情報の構成例を示す図である。

【図5】図5は、制御情報により制御(設定)されるデータのフォーマットを示す図である。

【図6】図6は、ICカードが正常な処理を行う場合のICカードとリーダライタとの通信手順を概略的に説明するための図である。

【図7】図7は、ICカードでデータの更新エラーが発生した場合のICカードとリーダライタとの通信手順を概略的に説明するための図である。

【図8】図8は、異常データ確認コマンドの構成例を示す図である。

【図9】図9は、異常データ確認コマンドに対するレスポンスデータの構成例を示す図である。

【図10】図10は、異常データ更新コマンドの構成例を示す図である。

【図11】図11は、異常データ更新コマンドに対するレスポンスデータの構成例を示す図である。

【図12】図12は、異常データ確認処理の流れを説明するためのフローチャートである。

【図13】図13は、異常データ更新処理の流れを説明するためのフローチャートである。

【発明を実施するための形態】

【0014】

以下、この発明の実施の形態について図面を参照して説明する。

図1は、本発明の実施の形態に係るICカード(携帯可能電子装置)1を含むICカードシステムの構成例を概略的に示すものである。

図1に示すように、本ICカードシステムは、情報センタ2、通信網3、PC4、リーダライタ5などにより構成されている。上記情報センタ2は、通信網3を介してPC4に接続されている。上記情報センタ2は、本ICカードシステムに利用されるデータを総括的に管理するサーバ装置である。本ICカードシステムにおいて、上記情報センタ2は、各PC4に対する上位装置として機能する。また、上記通信網3は、たとえば、公衆電話網あるいは公衆無線通信網などの通信網である。

【0015】

上記PC4は、パーソナルコンピュータなどの電子計算機である。上記PC4は、リーダライタ5に接続される。上記PC4は、上記リーダライタ5によりICカード1へコマンドを送信する機能、ICカード1から受信したデータを基に種々の処理を行う機能などを有している。

上記PC4は、図1に示すように、演算部11、ハードディスクドライブ(HDD)12、キーボード13、および、ディスプレイ14などを有している。

【0016】

上記演算部11は、CPU15、および、メモリ16などを有している。上記CPU15は、演算処理などのデータ処理を行うユニットである。上記CPU15は、プログラムに従ってデータ処理を行う。上記メモリ16は、作業用のデータを一時的に格納するワーキングメモリ、CPU15が実行するプログラムあるいは制御データなどが記憶されているプログラムメモリなどを有している。このような構成により、上記演算部11では、CPU15が上記メモリ16に記憶されているプログラムを実行することにより、種々の処理を実現している。

【0017】

上記ハードディスクドライブ(HDD)12は、書換え可能な大容量の不揮発性メモリである。上記HDD12は、補助記憶装置として機能する。たとえば、上記HDD12には、機密情報としての電子データファイル1,2,3,・・・が格納される。これらのHDD12に格納される電子データファイルのデータは、上記演算部11による制御に従ってリーダライタ5を介してICカード1へ送信できるようになっている。上記キーボード13は、当該PC4の操作員が操作する操作部として機能する。上記キーボード13は、操作員が種々の操作指示あるいはデータなどを入力するためのものである。上記ディスプレイ14は、上記PC4の制御により種々の情報を表示する表示装置である。

【0018】

上記リーダライタ5は、上記ICカード1との通信を行うためのインターフェース装置である。上記リーダライタ5は、図示しない内部メモリおよび通信制御部などを有する外部装置である。また、上記リーダライタ5は、上記ICカード1の通信方式に応じたインターフェースにより構成される。たとえば、上記ICカード1が接触型のICカードである場合、上記リーダライタ5は、ICカード1のコンタクト部と物理的かつ電気的に接続するための接触部などにより構成される。また、上記ICカード1が非接触型のICカードである場合、上記リーダライタ5は、ICカード1との無線通信を行うためのアンテナおよび通信制御などにより構成される。上記リーダライタ5では、上記ICカード1に対する電源供給、クロック供給、リセット制御、データの送受信が行われるようになっている。このような機能によってリーダライタ5は、上記PC4による制御に基づいて上記ICカード1の活性化(起動)、種々のコマンドの送信、及び送信したコマンドに対する応答の受信などを行なう。

【0019】

次に、上記ICカード1のハードウエア構成例について説明する。

上記ICカード1は、上記リーダライタ5を介してPC4などの上位装置から電力供給を受けた際、活性化される(動作可能な状態になる)ようになっている。例えば、上記ICカード1が接触型の通信機能を具備している場合、つまり、ICカード1が接触型のICカードで構成される場合、上記ICカード1は、通信インターフェースとしてのコンタクト部を介してリーダライタ5からの動作電源及び動作クロックの供給を受けて活性化される。

【0020】

また、上記ICカード1が非接触型の通信機能を具備している場合、つまり、上記ICカード1が非接触式のICカードで構成される場合、上記ICカード1は、通信インターフェースとしてのアンテナ及び変復調回路などを介してリーダライタ5からの電波を受信し、その電波から図示しない電源部により動作電源及び動作クロックを生成して活性化するようになっている。

【0021】

図2は、本実施の形態に係るICカード1のハードウエア構成例を概略的に示すブロック図である。

上記ICカード1は、本体Bを構成する筐体内にモジュールMが内蔵されている。上記モジュールMは、1つまたは複数のICチップCと通信用の外部インターフェース(通信部)とが接続された状態で一体的に形成され、ICカード1の本体B内に埋設されている。また、上記ICカード1のモジュールMは、図2に示すように、CPU(制御素子)21、データメモリ22、ワーキングメモリ23、プログラムメモリ24、および、通信部25などを有してしている。また、図2に示す構成例では、本体Bには、磁気ストライプ20が設けられている。

【0022】

上記CPU21は、当該ICカード1全体の制御を司るものである。上記CPU21は、上記プログラムメモリ24あるいは上記データメモリ22に記憶されている制御プログラムおよび制御データに基づいて動作することにより、種々の機能を実現する。たとえば、上記CPU21は、オペレーティングシステムのプログラムを実行することにより、当該ICカード1の基本的な動作制御を行う。また、上記CPU21は、当該ICカード1の利用目的に応じたアプリケーションプログラムを実行することにより、当該ICカード1の運用形態に応じた種々の動作制御を行う。

【0023】

上記データメモリ22は、例えば、EEPROM(Electrically Erasable Programmable Read Only Memory)あるいはフラッシュROMなどのデータの書き込み及び書換えが可能な不揮発性のメモリにより構成される。上記データメモリ22には、当該ICカード1の運用用途に応じた制御プログラムあるいは種々のデータが書込まれる。上記データメモリ22には、当該ICカード1の規格に応じた種々のファイルが定義され、それらのファイルに種々のデータが書き込まれる。上記データメモリ22に格納されるファイルの例については、後述する。

【0024】

上記ワーキングメモリ23は、RAMなどの揮発性のメモリである。また、上記ワーキングメモリ23は、CPU21が処理中のデータなどを一時保管するバッファとしても機能する。たとえば、上記ワーキングメモリ23には、カレント状態となっているファイルあるいはアプリケーションを示す情報なども格納される。

上記プログラムメモリ24は、予め制御用のプログラムや制御データなどが記憶されているマスクROMなどの不揮発性のメモリである。上記プログラムメモリ24には、当該ICカードの製造段階で制御プログラムあるいは制御データなどが記憶された状態でICカード1内に組み込まれる。上記プログラムメモリ24に記憶されている制御プログラムあるいは制御データは、当該ICカードの基本的な動作を司るものであり、予め当該ICカード1の仕様に応じて組み込まれるものである。

【0025】

上記通信部25は、上記リーダライタ5を介して上記PC4と通信するためのインターフェースである。当該ICカード1が接触型のICカードとして実現される場合、上記通信部25は、上記リーダライタ5と物理的かつ電気的に接触して信号の送受信を行うための通信制御部とコンタクト部とにより構成される。また、当該ICカード1が非接触型のICカードとして実現される場合、上記通信部25は、上記リーダライタ5との無線通信を行うための変復調回路などの通信制御部および電波を送受信するためのアンテナなどにより構成される。

【0026】

次に、上記データメモリ22に格納されるファイルについて説明する。

図3は、上記データメモリ22に格納されるファイルの構成例を示す図である。

図3では、複数のアプリケーションに関する情報が記憶される複数のファイルの構成例を示している。図3に示すようなファイル構成は、ISO/IEC7816−4で定義されている事項に基づくものである。図3に示すファイル構成では、ISO/IEC7816−4に定義される種々のファイルをツリー構造で管理する。

【0027】

図3に示すように、上記データメモリ22には、MF(Master File)、DF(Dedicated File)およびEF(Elementary File)などからなる階層構造を有する複数のファイルが定義される。図3に示す例では、最上階層のマスターファイル(MF)31の次の階層には、第1EF(キーEF)32、第1DF(DF1)33、第2DF(DF2)34および第3DF(DF3)35が存在している。上記第1DF(DF1)33の配下として、DF1の次の階層には、DF1の第1EF(EF1−1)36、および、DF1の第2EF(EF1−2)37が存在している。上記第2DF(DF2)34の配下として、DF2の次の階層には、DF2の第1EF(EF2−1)38、および、DF2の第2EF(EF2−2)39が存在している。

【0028】

上記MF31は、上記データメモリ22に格納されている各種ファイルに対するファイル構成において、最上位に位置する。上記各DF(DF1、DF2、DF3)は、それぞれアプリケーションに対応して設けられる。上記各DFは、各アプリケーションに相当するフォルダとして機能する。このため、上記データメモリ22には、少なくともアプリケーション数に相当する数のDFが定義される。上記各EFは、実データを格納するデータファイルである。すなわち、DFの配下の各EFは、DFが対応するアプリケーションで使用されるデータを格納する。また、EFは、図3に示すように、MF31直下の階層に設けることも可能である。図3に示す上記キーEF32は、アクセス権を確立するためのキー(鍵情報)などを格納するデータファイルである。

【0029】

また、DFに相当するアプリケーションの例としては、例えば、クレジット、IDカード、ポイントシステム等が挙げられる。図3に示す例では、DFに相当するアプリケーションとして、X社向けのアプリケーション(例えば、X社用クレジットカードのDF)、A社向けのアプリケーション(例えば、A社用ポイントシステムのDF)、および、B社向けのアプリケーション(例えば、B社用ポイントシステムのDF)を想定する。図3に示すファイル構成において、X社向けのアプリケーション、A社向けのアプリケーション、および、B社向けのアプリケーションは、それぞれDF1、DF2、DF3が設けられる。この場合、DF1の配下では、X社向けのアプリケーションで使用されるデータがEF1−1およびEF1−2に格納される。また、DF2の配下では、A社向けのアプリケーションで使用されるデータがEF2−1およびEF2−2に格納される。

【0030】

次に、データ管理情報の構成例について説明する。

図4は、データ管理情報の構成例を示す図である。

上記データメモリ22内における各々のデータは、図4に示すようなデータ管理情報で管理される。

上記データ管理情報40は、データメモリ(EEPROM)22内における管理領域に記憶される。上記データ管理情報40は、データ登録数41、制御情報42、および、空き領域43により構成される。

【0031】

上記データ登録数41は、当該管理領域に登録されている制御情報の総数を示すデータである。上記データ登録数41のデータは、管理対象とするデータ(つまり、制御情報)の追加および削除により変化する。上記制御情報42は、登録されている制御情報(群)である。上記空き領域43は、制御情報を追加登録することが可能な空き領域である。

【0032】

上記制御情報42は、図4に示すように、上記データ識別子情報45、上記設定アドレス情報46、上記設定可能サイズ情報47、および、上記セキュリティ条件情報48などから構成される。

上記データ識別子情報45は、データ(データ列)を識別するための識別子を示す情報である。上記データ識別子情報45は、外部装置がデータを指定するために用いられる。たとえば、ICカード1がリーダライタ5からアクセス対象とするデータの識別子を指定するコマンドを受信した場合、ICカード1は、指定された識別子と一致するデータ識別子情報45をアクセス対象のデータとして検索する。この結果として、ICカード1は、指定された識別子と一致するデータ識別子情報45のデータをアクセス対象とする。

【0033】

上記設定アドレス情報46は、上記データ識別子情報45で示される識別子が付与されているデータが記憶されているデータメモリ22上におけるアドレス(先頭アドレス)を示す情報である。すなわち、上記データ識別子情報45で示される識別子のデータは、設定アドレス情報46により示されるデータメモリ22上のアドレスに配置されている。

【0034】

上記設定可能サイズ情報47は、データとして設定可能なサイスを示す情報である。つまり、各制御情報が対応するデータは、上記設定可能サイズ情報47により定義される範囲内において、可変長で設定可能である。たとえば、上記設定可能サイズ情報47で指定される範囲を満足されていない場合(たとえば、指定範囲を超えるデータの書込みコマンドを受けた場合)、当該データに対するアクセスは、排除(禁止)される。

【0035】

上記セキュリティ条件情報48は、データに対するセキュリテイ条件を示す情報である。つまり、上記セキュリティ条件情報48は、当該制御情報のデータにアクセス(読出しあるいは書込み)する場合に、満足されるべきセキュリティ条件を示す。たとえば、上記セキュリティ条件情報48により示される条件が満足されていない場合、当該データへのアクセスは、排除(禁止)される。

【0036】

また、本実施の形態では、セキュリティ条件情報48としては、後述する異常データ確認コマンド(あるいは異常データ更新コマンド)に対する実行の可否を示す情報が格納される。データ異常であっても、外部装置からのデータ更新を受けないデータについては、セキュリティ条件情報48として異常データ確認コマンドの実行を不可を設定する。たとえば、如何なる条件であっても一切のデータ更新を禁止するようなデータに対しては、セキュリティ条件情報48として異常データ確認コマンドの実行不可が設定される。

【0037】

ただし、後述する異常データ更新コマンドは、通常のデータ更新とは異なり、後述するようなセキュリティ条件を満たした場合にのみ実行されるコマンドである。つまり、後述する異常データ更新処理は、セキュリティ性を確保した状態でのみ実行される処理である。このため、セキュリティ条件情報48により異常データ確認コマンドの実行を許可するデータであっても、当該データのセキュリティ性が高いものを想定している。

【0038】

たとえば、データ異常(エラー状態)となった場合にはそのままの状態で保持しておきたいデータについては、セキュリティ条件情報48として異常データ確認コマンドの実行不可が設定され、データ異常(エラー状態)となった場合には正しいデータに書き換えておきたいデータについては、セキュリティ条件情報48として異常データ確認コマンドの実行許可が設定される。

【0039】

次に、各データの構成について説明する。

図5は、上記のような制御情報により制御(設定)されるデータのフォーマットを示す図である。

図5に示すように、各データ50は、データ長管理情報51およびデータ部52により構成される。図5に示すデータ50は、データファイル全体であっても良いし、データファイル内のレコードであっても良い。上記データ長管理情報51は、当該データのヘッダ情報であり、データ部52のサイズを示す情報などである。上記データ部52は、当該データのデータ本体である。

【0040】

図5に示す構成例において、上記データ部52には、複数のデータ列53(53A、53B)が格納可能である。図5に示す例では、データ部52には、データ列53Aとデータ列53Bとが格納されている。各データ列53(53A、53B)は、ぞれぞれ識別子55(55A、55B)、長さ56(56A、56B)、実データ57(57A、57B)およびデータ正当性管理情報58(58A、58B)を有する。

【0041】

上記識別子55は、各データ50内におけるデータ列53を識別するための情報である。上記識別子55は、各データ列53ごとにユニークな情報である。上記長さ56は、実データ57のサイズを示す情報である。すなわち、上記長さ56に連続し、かつ、当該長さ56で示すデータ長分のデータは、当該識別子55で特定されるデータ列53における実データ57である。

【0042】

上記実データ57は、当該データ列53におけるデータの実体(本体)である。すなわち、上記識別子55、上記長さ56および上記データ正当性管理情報58が当該データ列の管理情報であるとすれば、それらの管理情報で管理されるデータの実体が実データ57である。。

上記データ正当性管理情報58は、データ列の正当性を確認するための管理情報である。たとえば、上記データ正当性管理情報58には、識別子、長さおよび実データの排他的論理和などにより、当該データ列の正当性を確認するのに使用される。

【0043】

次に、上記のようなデータに対するアクセスの手順について説明する。

まず、上記データに対する正常処理としてのアクセスの手順について説明する。

図6は、ICカード1が正常な処理を行う場合のICカード1とリーダライタ5との通信手順を概略的に説明するための図である。

【0044】

図6に示すように、ICカード1は、リーダライタ5からのリセット信号を受けて、ATR信号をリーダライタ5へ送り返す。ICカード1からATR信号を受信したリーダライタ5は、各種の取引コマンド(各データへのアクセス要求を含む種々のコマンド)を順次送信する。これらの取引コマンドに応じて、ICカード1は、データのアクセス制御を含む種々の処理を実行する。これの処理が正常に終了した場合、ICカード1は、リーダライタ5に対して正常終了および異常なしを示す応答を送信する。

【0045】

次に、上記データに対する処理にエラー(異常)が発生した場合のアクセスの手順について説明する。

図7は、ICカード1でデータの更新エラーが発生した場合のICカード1とリーダライタ5との通信手順を概略的に説明するための図である。

図7に示すように、ICカード1は、リーダライタ5からのリセット信号を受けて、ATR信号をリーダライタ5へ送り返す。ICカード1からATR信号を受信したリーダライタ5は、各種の取引コマンド(各データへのアクセス要求を含む種々のコマンド)を順次送信する。

【0046】

これらの取引コマンドのうちのデータ更新コマンドに対する処理にエラーが発生したものとする。たとえば、データ更新処理中にリーダライタ5からの電源供給が強制的に停止された場合(ICカード1が所定の処理位置から引き抜かれた場合など)、ICカード1では、データ更新がエラーとなる。たとえば、図5に示すデータ列53Aの更新処理がエラーとなった場合(実データ57Aの書換えが途中で中断された場合)、実データ57Aは、異常な値となる。この場合、当該データ列53Aは、データ正当性管理情報に基づく正当性の確認によって異常状態であることが判定される。

【0047】

このようなデータ更新エラーとなった後に、再び、リーダライタ5からのリセット信号を受けた場合、ICカード1は、ATR信号をリーダライタ5へ送り返す。ICカード1からATR信号を受信したリーダライタ5は、各種の取引コマンド(各データへのアクセス要求を含む種々のコマンド)を順次送信する。このような取引コマンドを受信した場合、ICカード1は、前回の取引処理が正常終了していない状態である旨の応答(異常有りを示す応答)をリーダライタ5へ通知する。

【0048】

ICカード1から前回の取引処理が正常終了していない旨の応答を受信した場合、上記リーダライタ5は、異常データの有無の確認を要求する異常データ確認コマンドを送信する。異常データ確認コマンドを受信した場合、ICカード1は、データメモリ22に記憶されている各データ列についてデータ異常があるか否かを判定する処理を行う。データ異常となっているデータ列を発見すると、ICカード1は、データ異常となっているデータ列を示す識別子を含む応答をリーダライタ5へ送信する。

【0049】

異常データの識別子を示す情報を受信した場合、リーダライタ5は、異常データとなっているデータ列に対する処理を行う。たとえば、ICカード1のデータメモリ22に記憶すべき情報をリーダライタ5の上位装置(たとえば、情報センタ2あるいはPC4)で管理している場合、つまり、異常と判定されたデータ列に書込むべき正しいデータを上位装置が管理している場合、リーダライタ5は、上位装置から異常と判定されたデータ列に書込むべき正しいデータを受信する。異常と判定されたデータ列に書込むべき正しいデータを受信した場合、リーダライタ5は、異常と判定されたデータ列を正しいデータで更新する旨のコマンド(通常のデータ更新コマンドとは異なる異常データ更新コマンド)をICカード1へ送信する。

【0050】

上記異常データ更新コマンドを受信すると、ICカード1は、指定されたデータ(異常データ)を正しいデータに更新する処理を行う。上記異常データ更新コマンドに応じたデータの更新が正常に完了すると、ICカード1は、更新完了を示す応答をリーダライタ5へ送信する。以上の処理によれば、ICカード1およびICカードシステムでは、データ更新処理において強制的な処理の中断によって発生したデータ異常を確実に確認することでできる。さらに、ICカード1およびICカードシステムでは、データ異常が確認されたデータを正しいデータに更新することが可能である。

【0051】

次に、上記異常データ確認コマンドについて説明する。

図8は、異常データ確認コマンド60の構成例を示す図である。

図8に示す異常データ確認コマンド60は、上述したように、リーダライタ5がICカード1に対して異常データの確認を指示する命令電文である。

【0052】

上記異常データ確認コマンド60は、コマンドヘッダ部61とLc部62とにより構成される。さらに、コマンドヘッダ部61は、コマンドの分類(CLA:class)63、命令(INS:instruction)64、第1パラメータ(P1)65および第2パラメータ(P2)66により構成されている。

【0053】

上記CLA63およびINS64は、当該コマンドが異常データ確認コマンドであることを示す情報が格納される。上記CLA63およびINS64としては、異常データ確認コマンドに対応づけたコード情報が格納される。上記ICカード1のCPU21は、CLA63およびINS64におけるコード情報が異常データ確認コマンドであることを判別する機能を有している。このような機能は、CPU21がプログラムメモリ24に記憶されているプログラムを実行することにより実現される。

【0054】

上記第1パラメータ65および第2パラメータ66は、当該異常データ確認コマンドのパラメータを示す情報である。たとえば、第1パラメータ65および第2パラメータ66には、異常データの確認対象とする範囲を限定する場合に、異常データの確認対象とする範囲を示すパラメータが格納される。Lc部62は、当該コマンドにデータが添付される場合にデータの長さを示す情報が格納される。ただし、本実施の形態では、異常データ確認コマンド60にはデータが添付されないものとする。

【0055】

図9は、異常データ確認コマンド60に対するレスポンスデータ70の構成例を示す図である。

図9に示すレスポンスデータ70は、リーダライタ5からの異常データ確認コマンドに対する処理を実行した後、ICカード1がリーダライタ5へ出力する応答電文である。このレスポンスデータ70は、データ部71、第1ステータスコード72および第2ステータスコード73から構成される。データ部71は、異常データの識別子を示す情報が格納される。ステータスコード72及び73は、当該レスポンスデータ70が異常データの確認結果として、異常なデータと判定されたデータ列を通知する情報であることを示すコードが格納される。

【0056】

図10は、異常データ更新コマンド80の構成例を示す図である。

図10に示す異常データ更新コマンド80は、上述したように、リーダライタ5がICカード1に対してデータ異常となっているデータを正しいデータに更新する異常データ更新処理の実行を要求する命令電文である。

上記異常データ更新コマンド80は、コマンドヘッダ部81、Lc部82およびデータ部83により構成される。さらに、コマンドヘッダ部81は、コマンドの分類(CLA:class)84、命令(INS:instruction)85、第1パラメータ(P1)86、第2パラメータ(P2)87を有する。

【0057】

上記CLA84およびINS85は、当該コマンドが異常データ更新コマンドであることを示す情報が格納される。上記CLA84およびINS85としては、異常データ更新コマンドに対応づけたコード情報が格納される。上記ICカード1のCPU21は、CLA84およびINS85におけるコード情報が異常データ更新コマンドであることを判別する機能を有している。このような機能は、CPU21がプログラムメモリ24に記憶されているプログラムを実行することにより実現される。なお、上記異常データ更新コマンドは、通常のデータ更新コマンドとは異なるコマンドである。従って、異常データ更新コマンドに対しては、通常のデータ更新コマンドとは異なるコード情報が定義される。

【0058】

上記第1パラメータ86および第2パラメータ87は、当該異常データ更新コマンドのパラメータを示す情報である。たとえば、上記第1パラメータ86には、異常データの更新対象となるデータ列を格納しているデータファイルとしてのEFを示すEF−IDが格納される。また、上記第2パラメータ87には、書き換え対象となるデータ列を示す識別子が格納される。

【0059】

上記Lc部82は、当該コマンドに添付されるデータの長さを示す情報(Lc)が格納される。図10に示す例では、異常データ更新コマンド80には、データ部83に更新すべきデータ列全体のデータが添付される。すなわち、上記データ部83に格納されるデータは、更新すべきデータ列全体のデータ(識別子+長さ+正常な実データ)である。上記Lc部82は、データ部83に格納されるデータ全体の長さを示す情報が格納される。

【0060】

図11は、異常データ更新コマンド80に対するレスポンスデータ90の構成例を示す図である。

図11に示すレスポンスデータ90は、リーダライタ5からの異常データ更新コマンド80に対する処理を実行した後、ICカード1がリーダライタ5へ出力する応答電文である。このレスポンスデータ90は、第1ステータスコード91および第2ステータスコード92から構成される。第1ステータスコード91及び第2ステータスコード92は、異常データ更新コマンド80に対する異常データの更新結果を示す情報である。たとえば、データ列を正常なデータに更新する処理が完了した場合、レスポンスデータ90のステータスコード91及び92は、異常データの更新完了を示すコードが格納される。

【0061】

次に、上記のような異常データ確認コマンド60に応じて実行する異常データ確認処理について詳細に説明する。

図12は、異常データ確認処理の流れを説明するためのフローチャートである。なお、図12に示すような各処理は、たとえば、CPU21がプログラムメモリ24に記憶されているプログラムを実行することにより実現される機能であるものとする。

【0062】

上記リーダライタ5からコマンドを受信した場合、上記ICカード1のCPU21は、コマンドヘッダ部におけるCLAおよびINSを確認することにより受信したコマンドの内容を判別する。ここでは、受信したコマンドのコマンドヘッダ部におけるCLAおよびINSが異常データ確認コマンド60を示すコード情報であるものとする。つまり、ICカード1は、異常データ確認コマンド60を受信したものとする(ステップS11)。

【0063】

上記異常データ確認コマンド60を受信した場合、上記CPU21は、データメモリ22の管理領域に記憶されているデータ管理情報から1つ目の制御情報42(#1)を読み込む(ステップS12)。1つ目の制御情報42を読み込むと、上記CPU21は、読み込んだ制御情報42における設定アドレス情報46に基づいて、当該制御情報42が対応するデータ列53全体として、識別子55、長さ56、実データ57およびデータ正当性管理情報58をワーキングメモリ23に読み出す(ステップS13)。

【0064】

1つのデータ列53全体をワーキングメモリ23上に読み出すと、CPU21は、当該データ列としての識別子、長さ、および、実データに対して、データの正当性を確認するための所定の演算を行う(ステップS14)。この演算は、データ正当性管理情報と比較するための値を算出するための演算(誤りチェック演算)である。この演算内容については、特定の方式に限定されるものではない。たとえば、上記演算は、全データのアンド演算であっても良いし、XOR(排他的論理和)演算であっても良いし、CRC演算であっても良い。上記演算が完了すると、CPU21は、上記演算により算出した値と当該データ列におけるデータ正当性管理情報として読み出した値とを比較することにより両者が一致するか否かを判定する(ステップS15)。

【0065】

上記比較の結果として両者が一致すると判定した場合(ステップS15、YES)、CPU21は、当該制御情報に対応するデータ列にはデータ異常がないものと判断する。この場合、CPU21は、次の制御情報が存在するか否かを判断する(ステップS16)。たとえば、次の制御情報が存在するか否かは、データ登録数と読み込んだ制御情報との数とに基づいて判定される。次の制御情報が存在すると判断した場合(ステップS16、YES)、CPU21は、データ管理情報から次の制御情報を読み込む(ステップS17)。次の制御情報を読み込むと、CPU21は、上記ステップS13へ戻り、上述した処理を繰り返し実行する。また、次の制御情報が無いと判断した場合(ステップS16、NO)、CPU21は、実行条件不備であることを示すステータスコードをセットしたレスポンスデータ(応答電文)をリーダライタ5へ送信する。

【0066】

また、上記比較の結果として上記演算により算出した値とデータ正当性管理情報の値とが一致しないと判定した場合(ステップS15、NO)、CPU21は、当該制御情報に対応するデータ列にはデータ異常があるものと判断する。この場合、CPU21は、当該制御情報42におけるセキュリティ条件情報48に基づいて、当該制御情報42が対応するデータ列53に対して異常データ確認コマンド60が実行可能か否かを確認する(ステップS20)。たとえば、当該データ列に対する異常データ確認コマンド60が実行不可である場合(ステップS20、実行不可)、CPU21は、セキュリティ異常であることを示すステータスコードをセットしたレスポンスデータ(応答電文)をリーダライタ5へ送信する(ステップS21)。

【0067】

また、当該データ列に対する異常データ確認コマンド60が実行許可である場合(ステップS20、実行許可)、CPU21は、ワーキングメモリ23に、異常データ確認コマンドに対する処理(つまり、異常データ確認処理)が正常したことを示す情報を記録する(ステップS22)。このワーキングメモリ23に記録した情報(異常データ確認処理が正常終了済みを示す情報)は、少なくとも後述する異常データ更新コマンドが実行されるまで保持される。これは、異常データ確認処理の正常終了済みであることが、後述する異常データ更新処理の実行条件となるためである。

【0068】

上記ワーキングメモリ23に異常データ確認処理済みである旨を記録すると、CPU21は、上記ワーキングメモリ23にデータが異常らしいと判定したデータ列の先頭アドレスとして当該データ列の識別子が記憶されているデータメモリ22上の先頭アドレスを記録する(ステップS23)。さらに、CPU21は、ワーキングメモリ23に記録した先頭アドレスに基づいて、データ異常があると判定されたデータ列の識別子を読み出す。データ異常があると判定されたデータ列の識別子を読み込むと、CPU21は、データ異常があるデータ列の識別子を示す情報をデータ部71にセットし、異常データ確認処理が正常終了したことを示すステータスコードをセットしたレスポンスデータ(応答電文)70をリーダライタ5へ送信する(ステップS24)。

【0069】

次に、上記のような異常データ更新コマンド80に応じて実行する異常データ更新処理について詳細に説明する。

図13は、異常データ更新処理の流れを説明するためのフローチャートである。なお、図13に示すような各処理は、たとえば、CPU21がプログラムメモリ24に記憶されているプログラムを実行することにより実現される機能であるものとする。

【0070】

上記リーダライタ5からコマンドを受信した場合、上記ICカード1のCPU21は、コマンドヘッダ部におけるCLAおよびINSを確認することにより受信したコマンドの内容を判別する。ここでは、受信したコマンドのコマンドヘッダ部81におけるCLA84およびINS85が異常データ更新コマンド80を示すコード情報であるものとする。つまり、ICカード1は、異常データ更新コマンド80を受信したものとする(ステップS31)。

【0071】

上記異常データ更新コマンド80を受信した場合、上記CPU21は、まず、異常データ確認コマンドが正常終了済みであるか否かを判定する(ステップS32)。この判定は、異常データ確認コマンドに対する応答状況を確認することにより実行される。上述した異常データ確認処理が実施済みである場合、上記ワーキングメモリ23には、異常データ確認処理が正常終了済みであることを示す情報が記録されている。したがって、CPU21は、ワーキングメモリ23に記憶されている情報を確認することにより、異常データ確認処理が終了済みか否かを確認する。

【0072】

上記ステップS32は、異常データ更新処理の実行条件を判定する処理である。本実施の形態では、異常データ確認コマンドが正常終了済みであることを異常データ更新処理の実行条件として想定している。ただし、異常データ更新処理の実行条件は、上記の例に限定されるものではなく、異常データ更新(たとえば、通常のデータ更新コマンドでは更新不可となるデータの更新)に対するセキュリティ性が確保できるものであれば良い。たとえば、異常データ更新処理は、異常データ確認コマンドが正常終了した直後であることを実行条件としても良い。この場合、異常データ確認コマンドの正常終了を外部装置へ通知した直後に、当該外部装置から異常データ更新コマンドを受信した場合にのみ、異常データ更新処理を開始する。

【0073】

この確認の結果として異常データ確認処理が実行済みでないと判断した場合(ステップS32、NO)、CPU21は、異常データ更新処理を実行するための条件が満たされていない(実行条件不備である)旨のステータスコードをセットした応答電文をリータライタ5へ送信する(ステップS33)。

【0074】

また、上記確認により異常データ確認処理が実行済みであると判断した場合(ステップS32、YES)、CPU21は、受信した異常データ更新コマンドで指定されたデータ列(つまり、異常データ更新処理の対象とするデータ列)が正当であるか否かを確認する(ステップS34)。すなわち、上記ステップS34の処理として、CPU21は、受信した異常データ更新コマンドにおけるデータ部に格納されているデータ列の識別子と上記異常データ確認処理によりデータ異常と判定されたデータ列の識別子とを比較する。上記異常データ確認処理において、ワーキングメモリ23には、データ異常と判定されたデータ列の識別子の先頭アドレスを示す情報が記録されている。従って、CPU21は、ワーキングメモリ23に記録されている先頭アドレスに基づいて、データ異常があると判定されたデータ列の識別子を読み出す。すなわち、CPU21は、読み出した識別子と異常データ確認コマンドのデータ部に格納されている識別子とが一致するか否かを判断する。

【0075】

上記判断によりデータ異常と判定されたデータ列の識別子と異常データ確認コマンドのデータ部に格納された識別子とが一致しないと判定した場合(ステップS34、NO)、CPU21は、異常データ更新処理が不可である旨のステータスコードをセットしたレスポンスデータ(応答電文)を上記リーダライタ5へ送信する(ステップS35)。この場合、CPU21は、データ異常と判定されたデータ列の識別子が異常データ確認コマンドで指定されたデータ列の識別子と不一致である旨を通知するようにしても良い。ただし、セキュリティにおける問題の可能性がある場合、上記レスポンスデータ90には更新処理が不可となった理由を示す情報を含めないようにする。

【0076】

また、上記判断によりデータ異常が判定されたデータ列の識別子と異常データ確認コマンド80のデータ部83に格納された識別子とが一致すると判定した場合(ステップS34、YES)、CPU21は、さらに、当該識別子で指定されるデータ列の長さが正当であるか否かを確認する(ステップS36)。上記ステップS36の処理として、CPU21は、受信した異常データ更新コマンドのデータ部83に格納された更新用のデータの長さ(つまり、異常データ更新コマンドのLc部82に格納される長さ)とデータ異常が判定されたデータ列の長さ(ワーキングメモリ23に記録されている先頭アドレスにより識別子の記憶位置が特定されるデータ列の長さ)とが一致するか否かを判定する。

【0077】

上記判定により更新用のデータの長さとデータ異常が判定されたデータ列の長さとが一致しないと判定した場合(ステップS36、NO)、CPU21は、異常データ更新処理が不可である旨のステータスコードをセットしたレスポンスデータ(応答電文)90を上記リーダライタ5へ送信する(ステップS37)。この場合、CPU21は、データ異常と判定されたデータ列の長さ、あるいは、異常データ確認コマンドで指定された更新用のデータの長さが異常である旨を通知するようにしても良い。ただし、セキュリティにおける問題の可能性がある場合、上記レスポンスデータ90には、更新処理が不可となった理由を示す情報を含めないようにする。

【0078】

また、上記判定により更新用のデータの長さとデータ異常が判定されたデータ列の長さとが一致すると判定した場合(ステップS36、YES)、CPU21は、当該異常データ更新コマンド80のデータ部83に格納されている更新用のデータ(識別子、長さ、および、実データ)に対する所定の演算(誤りチェック用の演算)によりデータ正当性管理情報を算出する(ステップS38)。これにより、データ異常が判定されたデータ列に対する正しい値として、識別子、長さ、実データおよびデータ正当性管理情報が得られる。

【0079】

上記データ正当性管理情報を算出することによりデータ列全体の正しい値が得られると、CPU21は、データ異常が判定されたデータ列全体を、当該データ列の正しい値として得られた識別子、長さ、実データおよいびデータ正当性管理情報に書き換える(ステップS39)。すなわち、CPU21は、ワーキングメモリ23に記録しているデータ異常が判定されたデータ列の先頭アドレスから、異常データ更新コマンドのデータ部として与えられたデータ(識別子、長さおよび実データ)と所定の演算により算出されたデータ正当性管理情報とを上書きする。

【0080】

上記のようなデータ異常が判定されたデータ列全体に対するデータの書換えが完了すると、CPU21は、異常データ更新処理が正常終了したことを示すステータスコードをセットしたレスポンスデータ(応答電文)90を上記リーダライタ5へ送信する(ステップS40)。

【0081】

上記のように、本実施形態では、ICカード1は、リーダライタ5から受信したコマンドが異常データ確認コマンドである場合、データメモリ22に記憶されているデータ列からデータ異常となっているデータ列を検出し、データ異常が検出されたデータ列を示す識別子を含む異常データ確認処理の正常終了を示す応答をリーダライタ5へ送信する。さらに、上記ICカード1は、上記リーダライタ5から異常データ更新コマンドを受信した場合、異常データ更新処理の実行条件が満たされていれば、当該異常データ更新コマンドに応じてデータ異常となったデータを正しいデータに更新する処理を実行する。異常データ更新処理の実行条件としては、異常データ確認処理が正常終了済みであること、あるいは、異常データ確認処理が正常終了した直後であること等がある。

【0082】

上記のような実施の形態によれば、ICカード1では、通信の不具合によってデータ異常が発生した場合、データ異常となったデータを正常なデータに更新することができる。この結果として、データ異常が発生してもICカード1におけるデータメモリ22の記憶領域あるいはICカード1自体を無駄にすることなく、ICカード1およびICカード1におけるデータ領域の効率的な運用が実現できる。

【符号の説明】

【0083】

B…本体、M…モジュール、C…ICチップ、1…ICカード、2…情報センタ、4…PC、5…リーダライタ、21…CPU(制御素子)、22…データメモリ、23…ワーキングメモリ、24…プログラムメモリ、25…通信部、40…データ管理情報、42…制御情報、45…データ識別子情報、46…設定アドレス情報、47…設定可能サイズ情報、48…セキュリティ条件情報、53(53A、53B)…データ列、55(55A、55B)…識別子、56(56A、56B)…長さ、57(57A、57B)…実データ、58(58A、58B)…データ正当性管理情報。

【特許請求の範囲】

【請求項1】

種々のデータを記憶する記憶手段と、

外部装置とのデータ通信を行うための通信手段と、

前記通信手段により前記外部装置から異常データ確認コマンドを受信した場合、前記記憶手段に記憶されているデータのうちデータ異常となっているデータを検出する検出手段と、

この検出手段によりデータ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する通知手段と、

を有することを特徴とする携帯可能電子装置。

【請求項2】

さらに、前記通知手段によりデータ異常が検出されたデータを示す情報を前記外部装置へ通知した後に、前記通信手段により前記データ異常が検出されたデータに対する更新を要求する異常データ更新コマンドを前記外部装置から受信した場合、前記異常データ更新コマンドに応じて前記データ異常が検出されたデータの更新を行う異常データ更新手段を有する、

ことを特徴とする前記請求項1に記載の携帯可能電子装置。

【請求項3】

さらに、前記通知手段によりデータ異常が検出されたデータを示す情報を前記外部装置へ通知した直後に、前記通信手段により前記データ異常が検出されたデータに対する更新を要求する異常データ更新コマンドを前記外部装置から受信した場合にのみ、前記異常データ更新コマンドに応じて前記データ異常が検出されたデータの更新を行う異常データ更新手段を有する、

ことを特徴とする前記請求項1に記載の携帯可能電子装置。

【請求項4】

前記検出手段は、正当性管理情報が付与されているデータに対する所定の演算で得られる値と前記正当性管理情報とが一致するか否かにより前記正当性管理情報が付与されているデータにおける異常の有無を検出する、

ことを特徴とする前記請求項1に記載の携帯可能電子装置。

【請求項5】

さらに、前記検出手段によりデータ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を許可するか不可とするかを判定する判定手段を有し、

前記通知手段は、前記判定手段により前記データ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を不可とする設定であると判定した場合、セキュリティ異常である旨を前記外部装置へ通知し、前記判定手段により前記データ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を許可する設定である場合、前記データ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する、

ことを特徴とする前記請求項1に記載の携帯可能電子装置。

【請求項6】

種々のデータを記憶する記憶手段と、

外部装置とのデータ通信を行うための通信手段と、

前記通信手段により前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータに対する異常データ更新が可能か否かを判定する実行条件判定手段と、

この実行条件判定手段により異常データ更新として指定されたデータの更新が可能であると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する異常データ更新手段と、

を有することを特徴とする携帯可能電子装置。

【請求項7】

前記実行条件判定手段は、前記通信手段により前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータをデータ異常が検出されたデータとして前記外部装置に通知済みであるか否かを判定し、

前記異常データ更新手段は、前記実行条件判定手段により前記異常データ更新コマンドで指定されたデータを前記データ異常が検出されたデータとして通知済みであると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する、

ことを特徴とする前記請求項6に記載の携帯可能電子装置。

【請求項8】

前記実行条件判定手段は、前記通信手段により前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータをデータ異常が検出されたデータとして前記外部装置に通知した直後であるか否かを判定し、

前記異常データ更新手段は、前記実行条件判定手段により前記異常データ更新コマンドで指定されたデータを前記データ異常が検出されたデータとして通知した直後であると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する、

ことを特徴とする前記請求項6に記載の携帯可能電子装置。

【請求項9】

種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により受信したコマンドに応じた処理を実行する処理手段とを有する携帯可能電子装置におけるデータ処理方法であって、

前記外部装置から受信したコマンドが異常データ確認コマンドである場合、前記記憶手段に記憶されているデータのうちデータ異常となっているデータを検出し、

前記検出によりデータ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する、

を有することを特徴とする携帯可能電子装置におけるデータ処理方法。

【請求項10】

さらに、前記データ異常が検出されたデータを示す情報を前記外部装置へ通知した後に、前記外部装置から前記データ異常が検出されたデータに対する更新を要求する異常データ更新コマンドを受信した場合、前記異常データ更新コマンドに応じて前記データ異常が検出されたデータの更新を行う、

ことを特徴とする前記請求項9に記載の携帯可能電子装置におけるデータ処理方法。

【請求項11】

さらに、前記データ異常が検出されたデータを示す情報を前記外部装置へ通知した直後に、前記外部装置から前記データ異常が検出されたデータに対する更新を要求する異常データ更新コマンドを受信した場合にのみ、前記異常データ更新コマンドに応じて前記データ異常が検出されたデータの更新を行う、

ことを特徴とする前記請求項9に記載の携帯可能電子装置におけるデータ処理方法。

【請求項12】

前記データ異常となっているデータの検出は、正当性管理情報が付与されているデータに対する所定の演算で得られる値と前記正当性管理情報とが一致するか否かにより前記正当性管理情報が付与されているデータにおける異常の有無を検出する、

ことを特徴とする前記請求項9に記載の携帯可能電子装置におけるデータ処理方法。

【請求項13】

さらに、前記検出によりデータ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を許可するか不可とするかを判定し、

前記通知は、前記判定により前記データ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を不可とする設定であると判定した場合、セキュリティ異常である旨を前記外部装置へ通知し、前記判定により前記データ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を許可する設定である場合、前記データ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する、

ことを特徴とする前記請求項9に記載の携帯可能電子装置におけるデータ処理方法。

【請求項14】

種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により受信したコマンドに応じた処理を実行する処理手段とを有する携帯可能電子装置におけるデータ処理方法であって、

前記外部装置から異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータに対する異常データ更新が実行可能か否かを判定し、

この判定により異常データ更新コマンドで指定されたデータの更新が実行可能であると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する、

ことを特徴とする携帯可能電子装置におけるデータ処理方法。

【請求項15】

前記判定は、前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータをデータ異常が検出されたデータとして前記外部装置に通知済みであるか否かを判定し、

前記異常データ更新は、前記判定により前記異常データ更新コマンドで指定されたデータを前記データ異常が検出されたデータとして通知済みであると判定された場合に、前記異常データ更新コマンドで要求された異常データ更新を実行する、

ことを特徴とする前記請求項14に記載の携帯可能電子装置におけるデータ処理方法。

【請求項16】

前記判定は、前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータをデータ異常が検出されたデータとして前記外部装置に通知した直後であるか否かを判定し、

前記異常データ更新は、前記判定により前記異常データ更新コマンドで指定されたデータを前記データ異常が検出されたデータとして通知した直後であると判定された場合にのみ、前記異常データ更新コマンドで要求された異常データ更新を実行する、

ことを特徴とする前記請求項14に記載の携帯可能電子装置におけるデータ処理方法。

【請求項1】

種々のデータを記憶する記憶手段と、

外部装置とのデータ通信を行うための通信手段と、

前記通信手段により前記外部装置から異常データ確認コマンドを受信した場合、前記記憶手段に記憶されているデータのうちデータ異常となっているデータを検出する検出手段と、

この検出手段によりデータ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する通知手段と、

を有することを特徴とする携帯可能電子装置。

【請求項2】

さらに、前記通知手段によりデータ異常が検出されたデータを示す情報を前記外部装置へ通知した後に、前記通信手段により前記データ異常が検出されたデータに対する更新を要求する異常データ更新コマンドを前記外部装置から受信した場合、前記異常データ更新コマンドに応じて前記データ異常が検出されたデータの更新を行う異常データ更新手段を有する、

ことを特徴とする前記請求項1に記載の携帯可能電子装置。

【請求項3】

さらに、前記通知手段によりデータ異常が検出されたデータを示す情報を前記外部装置へ通知した直後に、前記通信手段により前記データ異常が検出されたデータに対する更新を要求する異常データ更新コマンドを前記外部装置から受信した場合にのみ、前記異常データ更新コマンドに応じて前記データ異常が検出されたデータの更新を行う異常データ更新手段を有する、

ことを特徴とする前記請求項1に記載の携帯可能電子装置。

【請求項4】

前記検出手段は、正当性管理情報が付与されているデータに対する所定の演算で得られる値と前記正当性管理情報とが一致するか否かにより前記正当性管理情報が付与されているデータにおける異常の有無を検出する、

ことを特徴とする前記請求項1に記載の携帯可能電子装置。

【請求項5】

さらに、前記検出手段によりデータ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を許可するか不可とするかを判定する判定手段を有し、

前記通知手段は、前記判定手段により前記データ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を不可とする設定であると判定した場合、セキュリティ異常である旨を前記外部装置へ通知し、前記判定手段により前記データ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を許可する設定である場合、前記データ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する、

ことを特徴とする前記請求項1に記載の携帯可能電子装置。

【請求項6】

種々のデータを記憶する記憶手段と、

外部装置とのデータ通信を行うための通信手段と、

前記通信手段により前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータに対する異常データ更新が可能か否かを判定する実行条件判定手段と、

この実行条件判定手段により異常データ更新として指定されたデータの更新が可能であると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する異常データ更新手段と、

を有することを特徴とする携帯可能電子装置。

【請求項7】

前記実行条件判定手段は、前記通信手段により前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータをデータ異常が検出されたデータとして前記外部装置に通知済みであるか否かを判定し、

前記異常データ更新手段は、前記実行条件判定手段により前記異常データ更新コマンドで指定されたデータを前記データ異常が検出されたデータとして通知済みであると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する、

ことを特徴とする前記請求項6に記載の携帯可能電子装置。

【請求項8】

前記実行条件判定手段は、前記通信手段により前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータをデータ異常が検出されたデータとして前記外部装置に通知した直後であるか否かを判定し、

前記異常データ更新手段は、前記実行条件判定手段により前記異常データ更新コマンドで指定されたデータを前記データ異常が検出されたデータとして通知した直後であると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する、

ことを特徴とする前記請求項6に記載の携帯可能電子装置。

【請求項9】

種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により受信したコマンドに応じた処理を実行する処理手段とを有する携帯可能電子装置におけるデータ処理方法であって、

前記外部装置から受信したコマンドが異常データ確認コマンドである場合、前記記憶手段に記憶されているデータのうちデータ異常となっているデータを検出し、

前記検出によりデータ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する、

を有することを特徴とする携帯可能電子装置におけるデータ処理方法。

【請求項10】

さらに、前記データ異常が検出されたデータを示す情報を前記外部装置へ通知した後に、前記外部装置から前記データ異常が検出されたデータに対する更新を要求する異常データ更新コマンドを受信した場合、前記異常データ更新コマンドに応じて前記データ異常が検出されたデータの更新を行う、

ことを特徴とする前記請求項9に記載の携帯可能電子装置におけるデータ処理方法。

【請求項11】

さらに、前記データ異常が検出されたデータを示す情報を前記外部装置へ通知した直後に、前記外部装置から前記データ異常が検出されたデータに対する更新を要求する異常データ更新コマンドを受信した場合にのみ、前記異常データ更新コマンドに応じて前記データ異常が検出されたデータの更新を行う、

ことを特徴とする前記請求項9に記載の携帯可能電子装置におけるデータ処理方法。

【請求項12】

前記データ異常となっているデータの検出は、正当性管理情報が付与されているデータに対する所定の演算で得られる値と前記正当性管理情報とが一致するか否かにより前記正当性管理情報が付与されているデータにおける異常の有無を検出する、

ことを特徴とする前記請求項9に記載の携帯可能電子装置におけるデータ処理方法。

【請求項13】

さらに、前記検出によりデータ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を許可するか不可とするかを判定し、

前記通知は、前記判定により前記データ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を不可とする設定であると判定した場合、セキュリティ異常である旨を前記外部装置へ通知し、前記判定により前記データ異常が検出されたデータに対応するセキュリティ条件がデータ異常の確認を許可する設定である場合、前記データ異常が検出されたデータを示す情報を含むレスポンスデータを前記外部装置へ通知する、

ことを特徴とする前記請求項9に記載の携帯可能電子装置におけるデータ処理方法。

【請求項14】

種々のデータを記憶する記憶手段と、外部装置とのデータ通信を行うための通信手段と、前記通信手段により受信したコマンドに応じた処理を実行する処理手段とを有する携帯可能電子装置におけるデータ処理方法であって、

前記外部装置から異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータに対する異常データ更新が実行可能か否かを判定し、

この判定により異常データ更新コマンドで指定されたデータの更新が実行可能であると判定された場合、前記異常データ更新コマンドで要求された異常データ更新を実行する、

ことを特徴とする携帯可能電子装置におけるデータ処理方法。

【請求項15】

前記判定は、前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータをデータ異常が検出されたデータとして前記外部装置に通知済みであるか否かを判定し、

前記異常データ更新は、前記判定により前記異常データ更新コマンドで指定されたデータを前記データ異常が検出されたデータとして通知済みであると判定された場合に、前記異常データ更新コマンドで要求された異常データ更新を実行する、

ことを特徴とする前記請求項14に記載の携帯可能電子装置におけるデータ処理方法。

【請求項16】

前記判定は、前記外部装置からの異常データ更新コマンドを受信した場合、当該異常データ更新コマンドで指定されたデータをデータ異常が検出されたデータとして前記外部装置に通知した直後であるか否かを判定し、

前記異常データ更新は、前記判定により前記異常データ更新コマンドで指定されたデータを前記データ異常が検出されたデータとして通知した直後であると判定された場合にのみ、前記異常データ更新コマンドで要求された異常データ更新を実行する、

ことを特徴とする前記請求項14に記載の携帯可能電子装置におけるデータ処理方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2011−13831(P2011−13831A)

【公開日】平成23年1月20日(2011.1.20)

【国際特許分類】

【出願番号】特願2009−155995(P2009−155995)

【出願日】平成21年6月30日(2009.6.30)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成23年1月20日(2011.1.20)

【国際特許分類】

【出願日】平成21年6月30日(2009.6.30)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]