撮像装置、情報処理装置、情報処理システムおよびフレームデータ出力同期化方法

【課題】カメラ入力とディスプレイ出力を同期動作させる。

【解決手段】ホスト端末20のずれ時間監視部34は、撮像装置12からのフレームデータの入力タイミングと、ディスプレイ16の出力周波数から得られる当該フレームデータの理想的な入力タイミングとのずれを監視する。動作周期調整部36は、入力タイミングのずれの大きさに応じて、撮像装置12における1フレームあたりの動作周期を調整する要求信号を送信する。撮像装置12のHカウンタ部42は、撮像装置12における垂直同期信号を起点として水平同期信号の出力をカウントし、所定の走査ラインで信号を発生させる。VSync調整カウンタ部44は、Hカウンタ部42からの信号を起点としてピクセルクロックをカウントし、ピクセルクロックに対し設定された値で垂直同期信号を発生させる。

【解決手段】ホスト端末20のずれ時間監視部34は、撮像装置12からのフレームデータの入力タイミングと、ディスプレイ16の出力周波数から得られる当該フレームデータの理想的な入力タイミングとのずれを監視する。動作周期調整部36は、入力タイミングのずれの大きさに応じて、撮像装置12における1フレームあたりの動作周期を調整する要求信号を送信する。撮像装置12のHカウンタ部42は、撮像装置12における垂直同期信号を起点として水平同期信号の出力をカウントし、所定の走査ラインで信号を発生させる。VSync調整カウンタ部44は、Hカウンタ部42からの信号を起点としてピクセルクロックをカウントし、ピクセルクロックに対し設定された値で垂直同期信号を発生させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、カメラを入力インターフェースに用いる情報処理技術に関する。

【背景技術】

【0002】

近年、ウェブカメラなど、撮影した映像のデータをリアルタイムに転送し、ディスプレイに表示する技術が幅広い分野で利用されている。例えば、ビデオチャットや監視カメラのように、撮影した映像をそのまま表示するもののほか、ユーザの頭部など体の一部をビデオカメラで撮影し、目、口、手などの所定の領域を抽出して別の画像で置換し、ディスプレイに表示するゲームなどもある(例えば、特許文献1)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】欧州特許出願公開第0999518号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記のような技術において、カメラとディスプレイが非同期である場合、カメラとディスプレイを中継するホスト端末において同期用バッファを準備し、フレーム単位で出力タイミングを調整していた。この態様においては、調整によって余ったフレームを破棄したり、同じフレームを2回表示したりする必要がある。このような同期処理によって不安定で大きなレイテンシが生じ、カメラ入力から表示までの応答性を低下させるほか、同期用バッファが必要不可欠となり記憶領域を圧迫するなどの問題があった。インターフェースが非同期でクロックを共有できないUSBカメラにおいては特に、同期処理が困難であった。

【0005】

本発明はこうした課題に鑑みてなされたものであり、その目的は、カメラ入力とディスプレイ出力を容易に同期動作させることのできる画像処理技術を提供することにある。

【課題を解決するための手段】

【0006】

本発明のある態様は撮像装置に関する。この撮像装置は、撮像素子が撮像した動画像の各フレームデータを垂直同期信号の周波数で走査ライン順に出力する出力制御部と、出力制御部が出力するフレームデータの出力時刻と、動画像を即時表示するディスプレイにおける出力周波数に基づく基準出力時刻とのずれが所定のしきい値を超えたとき、垂直同期信号の発生タイミングの設定を変更する垂直同期信号調整部と、を備えたことを特徴とする。

【0007】

本発明の別の態様は情報処理装置に関する。この情報処理装置は、接続した撮像装置から順次入力される各フレームデータの入力時刻を取得し、当該フレームデータの出力先のディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視するずれ時間監視部と、ずれが所定のしきい値を超えたとき、撮像装置における垂直同期信号の発生タイミングを調整する要求信号を撮像装置に送信する動作周期調整部と、を備えたことを特徴とする。

【0008】

本発明のさらに別の態様は情報処理システムに関する。この情報処理システムは、動画像を撮影する撮像装置と、当該動画像のフレームデータを順次取得しディスプレイに出力する情報処理装置と、を備えた情報処理システムであって、情報処理装置は、撮像装置から入力される各フレームデータの入力時刻を取得し、ディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視するずれ時間監視部と、ずれが所定のしきい値を超えたとき、撮像装置における垂直同期信号の発生タイミングを調整する要求信号を撮像装置に送信する動作周期調整部と、を備え、撮像装置は、フレームの最終走査ラインにおいて、画素値の出力周波数を有するピクセルクロックのエッジの数をピクセルカウント値としてカウントし、要求信号を取得した際、垂直同期信号を発生させるピクセルカウント値の設定を変更する垂直同期信号調整部を備えたことを特徴とする。

【0009】

本発明のさらに別の態様はフレームデータ出力同期化方法に関する。このフレームデータ出力同期化方法は、撮像装置が、撮影した動画像を即時表示するディスプレイにおけるフレームデータ出力処理と、自らのフレームデータ出力処理を同期させる方法であって、各フレームデータを垂直同期信号の周波数で走査ライン順に出力するステップと、出力するフレームデータの出力時刻と、ディスプレイにおける出力周波数に基づく基準出力時刻とのずれが所定のしきい値を超えたとき、垂直同期信号の発生タイミングの設定を変更するステップと、を含むことを特徴とする。

【0010】

なお、以上の構成要素の任意の組合せ、本発明の表現を方法、装置、システム、コンピュータプログラム、コンピュータプログラムを記録した記録媒体などの間で変換したものもまた、本発明の態様として有効である。

【発明の効果】

【0011】

本発明によると、カメラ入力とディスプレイ出力を容易に同期動作させることができる。

【図面の簡単な説明】

【0012】

【図1】本実施の形態を適用できる情報処理システムの構成例を示す図である。

【図2】カメラ入力とビデオ出力の同期処理を実現する従来技術におけるシステム構成を示す図である。

【図3】図2で示した構成によってフレームデータ出力タイミングの調整を行うときの、撮像装置からの出力データ、同期用バッファにおけるデータ、フレームメモリにおけるデータの変遷を示す図である。

【図4】撮像装置とディスプレイが同期している場合の撮像装置からの出力データ、入力バッファにおけるデータ、フレームメモリにおけるデータの変遷を示す図である。

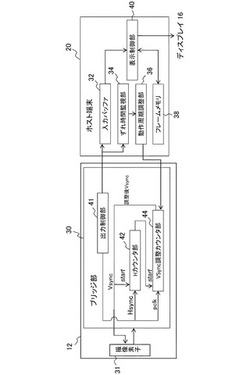

【図5】本実施の形態における撮像装置とホスト端末の構成を示す図である。

【図6】本実施の形態の撮像装置において発生させる信号を説明するための図である。

【図7】本実施の形態の撮像装置における垂直同期信号の発生タイミングの調整原理を説明するための図である。

【図8】本実施の形態において撮像装置からの1フレームあたりの入力周期を調整する処理の手順を示すフローチャートである。

【図9】本実施の形態において撮像装置からの入力周期を調整した場合における、撮像装置からの出力データ、入力バッファにおけるデータ、フレームメモリにおけるデータの変遷を示す図である。

【図10】ホスト端末に同期用バッファを設けた状態で本実施の形態の撮像装置を接続した場合の、撮像装置からの出力データ、同期用バッファにおけるデータ、フレームメモリにおけるデータの変遷を示す図である。

【発明を実施するための形態】

【0013】

図1は本実施の形態を適用できる情報処理システムの構成例を示す。情報処理システム10は、ユーザ1などの対象物をビデオ撮影する撮像装置12、撮影した動画像データの表示を制御するホスト端末20、動画像を表示するディスプレイ16を含む。撮像装置12、ホスト端末20、ディスプレイ16のうちいずれか2つ、または全てが組み合わされて一体的に装備されていてもよい。また、撮像装置12は必ずしもディスプレイ16の上に設置されていなくてもよい。さらにユーザ1は人でなくてもよく、その数も限定されない。

【0014】

撮像装置12は、CCD(Charge Coupled Device)またはCMOS(Complementary Metal Oxide Semiconductor)等の撮像素子を備えたデジタルビデオカメラである。撮像装置12が撮影した動画像のフレームデータは逐次、ホスト端末20に送信される。ホスト端末20は、送信されたフレームデータを、ディスプレイ16の出力タイミングに合わせてディスプレイ16に出力する。なおホスト端末20はフレームデータを用いて画像出力制御以外の所定の処理を行ってもよい。例えばユーザ1の姿をキャラクタ化して仮想世界の画像を生成しディスプレイ16に表示させることによりゲームなどを実現することができるが、このような技術は一般的なものを適用できるためここでは言及しない。

【0015】

ディスプレイ16は、ホスト端末20の制御のもと入力されたフレームデータを画像として表示する。ディスプレイ16は、画像を出力するディスプレイおよび音声を出力するスピーカを有するテレビであってよく、例えば液晶テレビ、プラズマテレビ、PCディスプレイ等である。

【0016】

本実施の形態では、このような情報処理システム10において撮像装置12によるカメラ入力とディスプレイ16によるビデオ出力とが非同期である場合に、低コストかつ容易に同期をとる。まず本実施の形態の効果を明らかにするために、このような場合に適用できる同期処理の既存手法について説明する。

【0017】

図2はカメラ入力とビデオ出力の同期処理を実現する従来技術におけるシステム構成を示している。なお同図は従来技術における構成を示しているため、撮像装置12a、ホスト端末20aとして本実施の形態の各装置と区別するが、接続形態は図1で示したのと同様である。ホスト端末20aは、撮像装置12aから、撮像装置の出力周波数で入力されるフレームデータを、ディスプレイ16の出力周波数で出力する必要がある。

【0018】

そのためホスト端末20aには、ディスプレイ16の出力周波数に合わせて書き換えられるフレームメモリ26の他に、撮像装置12aとフレームメモリ26との間でフレームデータをバッファしてタイミング調整を行うための同期用バッファ22を備える必要がある。さらにホスト端末20aは、フレームメモリ26からディスプレイ16へのフレームデータの出力を制御する表示制御部24を備える。

【0019】

図3は図2で示した構成によってフレームデータ出力タイミングの調整を行うときの、撮像装置12aからの出力データ(上段)、同期用バッファ22におけるデータ(中段3列)、フレームメモリ26におけるデータ(下段2列)の変遷を示している。例えば撮像装置12aは60fpsのフレームレートで撮影およびデータ入力を行い、ディスプレイ16は59.94fpsのフレームレートで動画表示を行うとする。この場合、撮像装置12aからホスト端末20aへのフレームデータ入力周期は1フレームあたり16.0msec、ホスト端末20aからディスプレイ16への出力周期は1フレームあたり16.7msecである。

【0020】

同図は横軸に時間経過を示し、1フレーム分に対応する期間を1つの矩形で表している。矩形内の文字はフレーム番号を表す。同図上端の凡例にあるように、矩形内の実線および点線の斜線はそれぞれ、走査ラインを走査することによるデータの出力期間(scan out)、および入力期間(scan in)を表している。また網掛けで示された矩形はデータの保持期間を表している。

【0021】

まず撮像装置12aでは、時刻t0において、第nフレームの撮像および出力が開始される。するとホスト端末20aにおける同期用バッファ22の第1バッファ22aには、時刻t1から、撮像が終了した走査ライン順に第nフレームのデータが格納される。第nフレームのデータを全て格納し終える時刻t2までの時間は上述の通り16.0msecである。表示制御部24は、その前のフレーム、すなわち第(n−1)フレームのデータをフレームメモリ26へ格納し終えた時刻t3から、フレームメモリ26の第1領域26aへ第nフレームのデータを格納し始める。

【0022】

なお同期用バッファ22の矩形列の下に示されるΔtの幅を有するマーカーは、直上の矩形が表すフレームデータの読み出し期間を示している。第nフレームの読み出し期間、すなわち時刻t3からΔtの間は、当該バッファへの別のデータの書き込みはできない。フレームメモリ26の第1領域26aへ書き出された第nフレームのデータは、その前の第(n−1)フレームの表示が終了した時刻t4から、ディスプレイ16へ出力され、画像が表示される。第nフレームの表示開始時刻t4から終了時刻t5までの時間は上述の通り16.7msecである。

【0023】

このような処理を、撮像装置12aにおける撮影の進捗に応じて取得された各フレームデータに対して同様に行う。すなわち撮像装置12aおよび同期用バッファ22は、16.0msecを1フレームあたりの処理周期として動作し、フレームメモリ26およびディスプレイ16は、16.7msecを1フレームあたりの処理周期として動作する。同図に示すようにフレームメモリ26は、ディスプレイ16へ出力中のフレームデータを格納する領域と、その次のフレームを格納する領域とを分け、第1領域26a、第2領域26bを交互に使用することにより、円滑な画像表示を行う。

【0024】

一方、同期用バッファ22は、あるフレームのデータを格納し終えたタイミングと、それを読み出すタイミングが、撮像装置12aとディスプレイ16の動作周波数の違いによってずれていく。結果としてほとんどの期間において、フレームデータを格納する際に、その2つ前のフレームデータの読み出しが完了していない状況となる。例えば第(n+2)フレームのデータの格納が開始される時刻Tでは、2つ前の第nフレームのデータが読み出し中である。

【0025】

このため、第nフレームのデータを格納している第1バッファ22aを、第(n+2)フレームのデータの格納先とはできない。このように、あるフレームデータの格納開始時に、2つ前のフレームのデータの読み出しが完了していない状況が発生する環境においては、同期用バッファ22として、第1バッファ22a、第2バッファ22b、第3バッファ22c、の3つのバッファを用意し、循環して使用する必要がある。

【0026】

3つのバッファを使用した場合、基本的には各フレームのデータ保持期間は、格納処理の期間を除くと2周期分となる。つまり同期用バッファ22に同じフレームのデータを保持できる期間は、バッファの数に依存して有限である。しかしディスプレイ16側の動作周期が撮像装置12a側の動作周期より長い場合、同期用バッファ22における各フレームデータの保持期間に対し、それを読み出す期間が徐々に後へずれていく。そしてやがては読み出し期間がデータ保持期間を超過してしまうことになる。このようにして、データが同期用バッファ22に格納されているにも関わらずディスプレイ16に表示しきれないフレームが発生する。この場合、当該フレームデータを破棄し、その次のフレームデータを読み出して表示せざるを得なくなる。

【0027】

図3の例では、第(n+6)フレームの読み出しを終えた時刻t6の次にあるべき、第(n+7)フレームを読み出す期間が、第(n+7)フレームのデータ保持期間を超えてしまう。そのため第7フレームをとばし、時刻t7において、格納済みの第(n+8)フレームのデータ読み出しを開始している。この例ではディスプレイ16側の動作周期が撮像装置12a側の基本周期より長いため、余ったフレームデータが消費されずに破棄されたが、動作周期の大小関係が逆であれば、表示に必要なフレームデータが不足し、同じフレームを2周期分表示せざるを得なくなる。

【0028】

このように、撮像装置12aとディスプレイ16が非同期に動作する場合、同期用バッファ22におけるフレームデータの保持期間と、それを読み出す期間とを比較し、その結果によってデータの破棄や2回表示など複雑な処理を発生させる必要がある。また、動作周期の差によって同期用バッファとして必要なバッファ領域の数が増える。

【0029】

さらに、ディスプレイ16の周波数に同期させてホスト端末が画像処理を行う場合、処理対象となるフレームが1つ破棄されてしまうとことによって生じる不具合も考えられる。例えば被写体の一部をトラッキングする場合、前のフレームとの時間間隔が開いてしまうと、可動範囲が増大するため探索領域を広げる必要が生じる。そのためトラッキング処理に要する時間が増え、レイテンシ増加の要因となる。

【0030】

撮像装置とディスプレイの設定動作周波数がたとえ同じであっても、内蔵する発振回路の精度によって同様のずれが生じる可能性もある。そこで本実施の形態では、撮像装置12内部の垂直同期信号のタイミングをピクセルカウント単位で調整することにより、撮像装置12からのデータ入力とディスプレイ16へのデータ出力の周期のずれを所定の範囲に収め、少なくとも1フレーム分の時間差が生じないようにする。

【0031】

図4は撮像装置とディスプレイが同期している場合の撮像装置からの出力データ(上段)、入力バッファにおけるデータ(中段2列)、フレームメモリにおけるデータ(下段2列)の変遷を示している。図の表し方は図3と同様であるが、この場合、撮像装置からの入力データを格納するメモリは、「同期用バッファ」ではなく、ホスト端末20内部の処理に用いるための「入力バッファ」として機能する。撮像装置とディスプレイの動作周期は例えば、いずれも16.0msecであったとする。

【0032】

この場合、同図に示すように、フレームデータのフレームメモリへの読み出しは、常時、入力バッファへの当該データの格納が完了した直後から開始でき、その2つの時刻がずれることはない。結果として入力バッファもフレームメモリと同様に、撮像装置から入力されたフレームデータを書き込むためのバッファと、フレームメモリへ読み出すためのバッファのみで構成できる。また上述のように、ずれが蓄積していくことによるフレーム単位の調整が必要ないため、処理を単純化でき突発的なレイテンシの増大を抑えることができる。

【0033】

本実施の形態では、撮像装置とディスプレイの動作周波数が異なっていても、図4で示した同期動作に近い状況を作り出す。具体的には撮像装置12において、1フレーム分として定義される時間、すなわち垂直同期信号(VSync)の間隔を、ピクセルカウント単位で調整し、ディスプレイにおける1フレームの表示周期を目標にした動作周期の合わせ込みを行う。この態様は発振回路の精度に起因したずれに対しても有効である。図5は本実施の形態における撮像装置12とホスト端末20の構成を示している。

【0034】

図5に示す各機能ブロックは、ハードウェア的には、CPU(Central Processing Unit)、RAM(Random Access Memory)、ROM(Read Only Memory)、カウンタ回路などの構成で実現でき、ソフトウェア的にはデータ入出力機能、データ保持機能などの諸機能を発揮するプログラムで実現される。したがって、これらの機能ブロックがハードウェアのみ、ソフトウェアのみ、またはそれらの組合せによっていろいろな形で実現できることは当業者には理解されるところであり、いずれかに限定されるものではない。

【0035】

ホスト端末20は、撮像装置12から入力されたフレームデータを一時格納する入力バッファ32、ディスプレイ16に出力するフレームデータを一時格納するフレームメモリ38、入力バッファ32からフレームメモリ38へのフレームデータの書き出し、フレームメモリ26からディスプレイ16へのフレームデータの出力を制御する表示制御部40を含む。

【0036】

入力バッファ32、フレームメモリ38、および表示制御部40は、図2で示したホスト端末20aにおける同期用バッファ22、フレームメモリ26、および表示制御部24と同様の機能を有する。ただし図4について説明したのと同様、本実施の形態も同期用バッファを用いた調整を行う必要がないため、同期用バッファ22に代えて入力バッファ32を備える。入力バッファ32は図4に示したのと同様、2つのバッファ領域を備えればよい。

【0037】

ホスト端末20はさらに、撮像装置12からのフレームデータの入力タイミングと、ディスプレイ16の出力周波数から得られる当該フレームデータの理想的な入力タイミングとのずれを監視するずれ時間監視部34、入力タイミングのずれの大きさに応じて、撮像装置12における1フレームあたりの動作周期を調整する要求信号を送信する動作周期調整部36を含む。

【0038】

撮像装置12は、撮像素子31とブリッジ部30を含む。撮像素子31は上記のとおりCCDまたはCMOS等のセンサである。ブリッジ部30は、フレームデータのホスト端末20への出力を制御する出力制御部41、撮像装置12における垂直同期信号を起点として水平同期信号(HSync)の出力をカウントし、所定の走査ラインで信号を発生させるHカウンタ部42、Hカウンタ部42からの信号を起点としてピクセルクロックをカウントし、ピクセルクロックに対し設定された値で垂直同期信号を発生させるVSync調整カウンタ部44を含む。

【0039】

出力制御部41は、撮像素子31が撮影した結果得られたフレームのデータを、USBなどのインターフェースを介して、走査ライン順にホスト端末20へ送出する。さらにフレームデータに含まれる各種同期信号の情報を分離し、Hカウンタ部42、VSync調整カウンタ部44に適宜供給する。出力制御部41が行う処理は一般的な技術を適用できるため詳細には言及しない。Hカウンタ部42およびVSync調整カウンタ部44と、ホスト端末20のずれ時間監視部34および動作周期調整部36の詳細な動作は後に述べる。

【0040】

次に図5で示した構成によって、撮像装置12からの入力とディスプレイ16への出力を同期させる原理を説明する。図6は撮像装置12において発生させる信号を説明するための図である。なおこれらの信号は一般的な撮像装置で発生される信号であり、本実施の形態ではそれを利用することができる。同図において右方向が、各走査ラインにおける画素単位の時間経過を、下方向が、走査ライン単位の時間経過を示している。同図中央の矩形のうち白抜きの領域が画素値の入出力期間を表し、網掛けの領域が水平帰線期間(HBlank)および垂直帰線期間(VBlank)を示している。

【0041】

まず横方向に表された、各走査ラインにおける時間経過は、図の上端に示すように、ピクセルクロック(PCLK)の立ち上がりエッジ周期PT(=1/PCLK)を1単位とする。ピクセルクロックは画素値の出力周波数を有する。そして走査ラインごとに、画素値の出力期間を表すデータイネーブル信号(DE)、走査ラインの終点のタイミングを表す水平同期信号(HSync)が発生する。図の縦方向に表された、走査ライン単位の時間経過は、水平同期信号の出力周期を1単位とする。そしてフレームごとに、値を持つ走査ラインの出力期間を表すデータイネーブル信号(DE)、フレームの終点のタイミングを表す垂直同期信号(VSync)が発生する。

【0042】

ここで、水平帰線期間を含めた次の走査ラインまでのピクセルクロックのカウント値をHTotal、垂直帰線期間を含めた次のフレームまでの走査ラインのカウント値をVTotalとすると、撮像装置12で撮影されホスト端末20へ入力されるフレームのフレームレートR(fps)は、

R(fps)=PCLK(Hz)/(HTotal×VTotal)

である。すなわち1フレームあたりの入力周期Tint(sec)は、

Tint(sec)=1/R(fps)=(HTotal×VTotal)/PCLK(Hz)=HTotal×VTotal×PT(sec)

である。

【0043】

本実施の形態では、撮像装置12から入力されるフレームデータの1フレームあたりの入力周期Tintを、ディスプレイ16における1フレームあたりの出力周期に合わせることにより同期動作に近い状況を作り出す。そこで本実施の形態ではまず、HTotalおよびVTotalを調整して走査ライン数単位で大まかな合わせ込みを行った後、実際の時間のずれを監視して、調整の結果決定した、フレームの最後の走査ラインの入力期間におけるピクセルカウントの単位で微調整を行う。

【0044】

走査ライン数単位での調整は、ディスプレイ16における出力フレームレートをターゲットフレームレートTAとしたとき、次の式を満足するようにHTotalおよびVTotalを定めることによって行う。

PCLK/(HTotal×VTotal) < TA < PCLK/HTotal×(VTotal-1)

上式の各項の逆数をとり、周期で比較すると次の式となる。

PT×HTotal×(VTotal-1) < 1/TA < PT × HTotal×VTotal

【0045】

すなわち、垂直同期信号直後のフレームの始点から、最後から2番目の走査ラインの走査完了までに要するピクセルクロック単位の時間「PT×HTotal×(VTotal-1)」と、当該始点から最後の走査ラインの走査完了までに要する時間「PT × HTotal×VTotal」の間に、ディスプレイ16の1フレームあたりの出力周期が入るように、HTotalおよびVTotalを調整する。これにより、ピクセルカウント単位の微調整は最後の走査ラインの走査時間内に限定することができる。

【0046】

図7は撮像装置12における垂直同期信号の発生タイミングの調整原理を説明するための図である。同図における矩形は図6と同様、水平同期信号、垂直同期信号を含めた、1フレームの入力期間を表している。そして当該矩形を左から右に横切る矢印は、走査ラインを模式的に示している。ここで、ディスプレイ16において1フレームの表示が終了する時刻が線50に対応するとすると、上記の式により決定した最後の走査ライン上、厳密にはVTotal−1のカウントとVTotalのカウントの間の時間に、線50が位置することになる。

【0047】

HTotalおよびVTotalの調整は走査ライン単位のものであるため、ディスプレイ16の出力周波数に応じてあらかじめ決定しておく。例えば撮像装置12やホスト端末20の内部メモリに、ディスプレイの出力周波数と、適切なHTotalおよびVTotalの値を対応づけたテーブルを準備しておき、ディスプレイ16が接続されたときに実際の出力周波数に応じてテーブルを参照したうえ決定してもよい。場合によってはピクセルクロック自体を上式による調整対象としてもよい。

【0048】

このようにHTotalおよびVTotalを決定したら、その後は実際の時間のずれを監視しながらピクセルカウント単位の微調整を行う。この調整は定性的には、最後の走査ライン上にあるべき当該フレームとしての終点、すなわち図7における最後の矢印52の先端を、線50に近づける調整となる。調整によって得られた終点で垂直同期信号を発生させ、次のフレームの撮像を開始すれば、撮像装置12からの1フレームあたりの入力周期と、ディスプレイ16への1フレームあたりの出力周期がおよそ等しくなる。

【0049】

ピクセルカウント単位での時間計測では厳密な計測時間に対し丸め誤差が発生すること、撮像装置やディスプレイの周波数にはそれぞれ揺らぎがあること、処理の負荷などを考慮すると、時間のずれが所定量蓄積した時点で、矢印52の長さ、すなわち最後の走査ラインにおいて垂直同期信号を発生させるまでのピクセルカウント値を調整するのが効率的である。以後、このようなピクセルカウント値を「最終ライン期間」と呼ぶ。

【0050】

実際の調整処理は、最後の走査ラインにおいて線50までの距離より短い最終ライン期間MF、および線50までの距離より長い最終ライン期間MSをあらかじめ決定しておき、それらを切り替えることによって行う。短い方の最終ライン期間MFおよび長い方の最終ライン期間MSは次の式を満足する値である。

PT×(HTotal×(VTotal-1)+ MF) < 1/TA < PT ×(HTotal×(VTotal-1)+ MS)

そして撮像装置12からの入力がディスプレイ16への出力より早すぎる場合は長い最終ライン期間MSを、遅すぎる場合は短い最終ライン期間MFを設定することにより、撮像装置12からの1フレームあたりの入力周期を調整する。

【0051】

2つの最終ライン期間MFおよびMSを、線50で示された、ディスプレイ16による1フレームの出力終了時刻を挟む直近の整数値とすると、MFおよびMSは以下の式から決定できる。

MF = floor(FIT/PT - HTotal (VTotal -1 ))

MS = ceil(FIT/PT - HTotal (VTotal -1))

ここでfloor(x)はx以下の最大の整数、ceil(x)はx以上の最小の整数を出力する関数である。またFITは1/TAで与えられる、ディスプレイ16の1フレームの表示周期である。

【0052】

さらに撮像装置12およびディスプレイ16における動作周波数の揺らぎをの幅を考慮し、2つの最終ライン期間MFおよびMSを以下のように決定して両者の差を大きくしてもよい。

MF = floor(FIT/PT - HTotal (VTotal -1 ))- dz/2

MS = ceil(FIT/PT - HTotal (VTotal -1))+ dz/2

ここでdzは揺らぎの幅を考慮した補正値であり、あらかじめ決定しておく。

【0053】

次に、以上のような調整を図5に示した構成によって実現するときの処理手順を示す。図8は本実施の形態において撮像装置12からの1フレームあたりの入力周期を調整する処理の手順を示すフローチャートである。同フローチャートはユーザがホスト端末20に対し、動画像の撮影とそれを用いた画像の表示を含む機能の実行を指示し、ホスト端末20が撮像装置12に撮影の開始を要求したときに処理が開始される。

【0054】

まず撮像装置12において、最終ライン期間Mに初期値M0を設定する(S10)。初期値M0は0からHTotalまでのいずれの値でもよく、MFまたはMSでもよい。次に撮像装置12は動画撮影を開始する(S12)。そして出力制御部41は、フレーム番号Nに0を代入したうえ(N14)、第0番目のフレームのデータを走査ライン順にホスト端末20へ入力していく(S16)。このときHカウンタ部42は、垂直同期信号の発生を受けてカウント値を0とした後、水平同期信号の出力をカウントしていくことで入力済みの走査ラインの数Hを監視する。

【0055】

撮像装置12から入力されたデータをホスト端末20が取得し、ディスプレイ16への出力を開始することにより、ディスプレイ16に動画像が表示される(S18)。撮像装置12では、ホスト端末20へ入力済みの走査ラインの数HがVTotal−1に達しない間は、各走査ラインのデータ出力を継続する(S20のN、S16)。出力済みの走査ラインの数HがVTotal−1に達したら(S20のY)、最後の走査ラインVTotalのデータをホスト端末20へ入力していく。このときVSync調整カウンタ部44は、走査ラインの数HがVTotal−1に達したことをHカウンタ部42から受けてカウント値を0とした後、ピクセルクロックの立ち上がりエッジをカウントしていく。

【0056】

ピクセルカウント値Pが最終ライン期間Mに達しない間は、データ入力を継続する(S24のN、S22)。ピクセルカウント値Pが、最終ライン期間Mに達したら(S24のY)、 VSync調整カウンタ部44は、垂直同期信号を撮像素子31およびHカウンタ部42に出力する(S26)。

【0057】

ホスト端末20のずれ時間監視部34は、1フレーム分のデータが撮像装置12から入力される都度、受信時のタイムスタンプを取得する。そして、第0フレームのデータ入力開始から第Nフレームのデータ入力完了までの実際の時間と、ディスプレイ16の出力周波数で入力動作がなされたときの想定時間との差、すなわちずれが、あらかじめ準備したしきい値を超えたか否かを判定する(S30)。しきい値を超えている場合は(S30のY)、撮像装置12のVSync調整カウンタ部44が保持している最終ライン期間Mに、MFまたはMSの値を設定し直す(S32)。

【0058】

ずれ量Dは例えば次の式で求められる。

D = |time_stump(N)- FIT×N|

ここでtime_stump(N)は、第0フレームの入力開始から第Nフレームの入力完了までのタイムスタンプの差である。このタイムスタンプを、ホスト端末20が出力するビデオクロック由来の周波数制御用電圧VCTにより計測することで、ホスト端末20内で制御がなされるFITの実際の時間に基づき正確に比較することができる。

【0059】

上述のようにずれ量Dがしきい値dwより大きければ、最終ライン期間Mを設定し直す。このとき、time_stump(N)- FIT×Nが正の値であれば撮像装置12からの入力が遅いため短い方の最終ライン期間MFを設定する。負の値であれば撮像装置12からの入力が速いため長い方の最終ライン期間MFを設定する。撮像装置12における最終ライン期間の更新は、実際には最後の走査ライン以外のデータをホスト端末20へ入力しているS16、S20の処理ステップの期間中に行ってよい。ずれ量Dがしきい値dwを超えていない場合は、そのままの設定を維持する(S30のN)。

【0060】

ユーザからの指示入力などにより処理を終了する必要が生じない間は(S34のN、S38のN)、撮像装置12においてフレーム番号をインクリメントしながら(S36)、以上の処理を繰り返す。この間、撮像装置12における撮影、ホスト端末20へのフレームデータ入力、ディスプレイ16へのフレームデータ出力、およびディスプレイ16における動画像の表示は継続して行われているものとする。処理終了の必要が生じたら、撮像装置12、ホスト端末20の双方で処理を終了する(S34のY、S38のY)。

【0061】

図9は本実施の形態によって撮像装置12からの入力周期を調整した場合における、撮像装置12からの出力データ(上段)、入力バッファ32におけるデータ(中段2列)、フレームメモリ38におけるデータ(下段2列)の変遷を示している。図の表し方は図4と同様である。また同図では、撮像装置12における出力対象のフレームを表す各矩形の上に、当該フレームに対する最終ライン期間Mの設定値を示している。

【0062】

まず撮像装置12から第nフレームが出力される時刻t0において、最終ライン期間Mには、短い方の最終ライン期間MFが設定されている。この設定により、撮像装置12からの1フレームあたりのデータ入力周期は、ディスプレイ16への1フレームあたりのデータ出力周期よりわずかに短い状態となっている。

【0063】

図4で説明したように、撮像装置12からの入力とディスプレイ16への出力が完全に同期していると、入力バッファ32への格納が完了したフレームデータは直後にディスプレイ16に出力される。本実施の形態でも上記のとおりVTotal、HTotalを調整したうえで、ピクセルカウント単位でディスプレイの出力周波数への合わせ混みを行っているため、図4に近い状態が得られている。

【0064】

一方、フレーム処理が進捗していくと、撮像装置12からの入力周期とディスプレイ6への出力周期の微妙なずれが蓄積していく。同図では、各フレームのデータが入力バッファ32に格納し終えた時刻と、当該データのフレームメモリ38への読み出しが開始される時刻とのずれ時間をD0、D1、D2、・・・として表している。例えば第n+1フレームのデータを入力バッファ32に格納し終えた時刻t1から、当該データの読み出し開始時刻t2までの時間のずれがD1である。

【0065】

この時間のずれは、撮像装置12からの1フレームあたりの入力周期とディスプレイ16への1フレームあたりの出力周期の差に起因するものであり、ひいては、ずれ時間監視部34がしきい値判定をする値に対応する。上述のとおり最終ライン期間Mとして小さい方の値MFが設定されている場合、撮像装置12からの入力周期がディスプレイ16への出力周期より短いため、データの入力が完了する時刻がその読み出しを開始する時刻より前にずれていき、D0、D1、D2、D3、とその値が増えていく。そしてD4でしきい値dwを超える。

【0066】

動作周期調整部36はこの結果を受け、VSync調整カウンタ部44が保持する最終ライン期間Mを、長い方の最終ライン期間MSに設定し直すように要求信号を送信する(S40)。この設定により撮像装置12からの入力周期がディスプレイ16への出力周期より長くなるため、ずれ時間はその後のD5で減少に転じ、D6、D7、D8、D9と減少していく。さらにフレーム処理が進捗すると、やがてずれ時間は撮像装置12からの入力が遅れる方向に増えていきくため、しきい値dwを超えた時点で最終ライン期間Mを、短い方の最終ライン期間MFに設定し直す(図示せず)。

【0067】

このようにすることで、撮像装置12からのフレームデータの格納が完了する時刻と、ディスプレイ16への出力が開始される時刻との差が最大でもしきい値dw程度に抑えられるため、1フレーム分のデータの余りや不足が生じることがなくなる。結果として、つじつまを合わせるためにデータを破棄したり同じフレームを2回表示したりする必要がなくなり、不安定なレイテンシの発生を抑制できる。さらに図9に示したように入力バッファ32は2つのバッファ領域のみで充足する。

【0068】

本実施の形態の撮像装置12は、最終ライン期間Mの設定を更新しなければ、既存の非同期の撮像装置と同様に動作する。したがって用途に合わせて同期/非同期を切り替えるようにしてもよい。図10は、図2で示したようにホスト端末20に同期用バッファ22を設けた状態で本実施の形態の撮像装置12を接続した場合の、撮像装置12からの出力データ(上段)、同期用バッファ22におけるデータ(中段3列)、フレームメモリ26におけるデータ(下段2列)の変遷を示している。

【0069】

図3で示したように、同期用バッファ22のみでの運用では、ディスプレイ16側の動作周期が撮像装置12側のそれより長い場合、同期用バッファ22における各フレームのデータの保持期間に対し、それを読み出す期間が徐々に後にずれていく。逆に短い場合は、徐々に前にずれていく。本実施の形態を導入し、最終ライン期間Mを適切に設定することにより、同図に示すように、同期用バッファ22におけるデータ保持期間のうちおよそ前半の期間で各フレームのデータを読み出すことができる。

【0070】

結果として、ディスプレイ16の周波数に合わせたデータ読み出しが行われても、本来のフレーム順で確実にデータへアクセスでき、余分な処理の必要が生じない。また表示しきれないフレームのデータを破棄するような事態が生じないため、フレームの時間間隔が一定に保たれる。これにより、読み出されたフレームデータを用いてトラッキングなどの処理を行う場合でも、フレームを破棄したことに起因する処理の負荷や精度の変動が発生しない。

【0071】

以上述べた本実施の形態によれば、撮像装置で撮影した動画をリアルタイムでディスプレイに表示するシステムにおいて、撮像装置からホスト端末へのフレームデータの入力周期を、ホスト端末からディスプレイへの出力周期に近づけるように、垂直同期信号の発生タイミングを調整する。このためまず、走査ラインの長さおよび数による調整を事前に行っておき、実際の時間のずれを監視しながら、最後の走査ラインにおける垂直同期信号の発生タイミングをピクセルカウント単位で調整する。

【0072】

これによりピクセルクロックの立ち上がりエッジ周期レベル、すなわちディスプレイの出力周期の100万分の1程度での時間調整を低コストで実現できる。走査ラインの数のみを調整する場合、フレームによって撮影時間の変動が比較的大きくなり、ローリングシャッターを有する撮像素子において露出の変動を引き起こす可能性があるが、本実施の形態のように微少時間での調整によれば、露出への影響は無視できるレベルとなる。

【0073】

また調整は、時間のずれが所定量、累積した時点で、設定値を更新し直すのみであるため、処理コストへの影響が少ない。さらに、2つの最終ライン期間の差分や、時間のずれに対するしきい値によって、装置自体が持つ動作周波数の揺らぎを吸収したタイミングでの調整が可能であるため、高頻度に無駄な調整を行い余計に処理の負荷がかかるといった不都合が発生しない。結果として、低コストかつ処理の負荷への影響を少なく、動画撮影から表示までを低レイテンシで応答性よく実行できる。

【0074】

以上、本発明を実施の形態をもとに説明した。上記実施の形態は例示であり、それらの各構成要素や各処理プロセスの組合せにいろいろな変形例が可能なこと、またそうした変形例も本発明の範囲にあることは当業者に理解されるところである。

【0075】

例えば本実施の形態における撮像装置は一眼の撮像素子からなっていたが、ステレオカメラなど複数のカメラを備えた構成としてもよい。この場合、VSync調整カウンタ部から発生させた垂直同期信号を全てのカメラに与えることにより、複数のカメラからの映像をディスプレイの出力と同期させることが容易にできる。

【符号の説明】

【0076】

10 情報処理システム、 12 撮像装置、 16 ディスプレイ、 20 ホスト端末、 30 ブリッジ部、 32 入力バッファ、 34 ずれ時間監視部、 36 動作周期調整部、 38 フレームメモリ、 40 表示制御部、 41 出力制御部、 42 Hカウンタ部、 44 VSync調整カウンタ部。

【技術分野】

【0001】

本発明は、カメラを入力インターフェースに用いる情報処理技術に関する。

【背景技術】

【0002】

近年、ウェブカメラなど、撮影した映像のデータをリアルタイムに転送し、ディスプレイに表示する技術が幅広い分野で利用されている。例えば、ビデオチャットや監視カメラのように、撮影した映像をそのまま表示するもののほか、ユーザの頭部など体の一部をビデオカメラで撮影し、目、口、手などの所定の領域を抽出して別の画像で置換し、ディスプレイに表示するゲームなどもある(例えば、特許文献1)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】欧州特許出願公開第0999518号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記のような技術において、カメラとディスプレイが非同期である場合、カメラとディスプレイを中継するホスト端末において同期用バッファを準備し、フレーム単位で出力タイミングを調整していた。この態様においては、調整によって余ったフレームを破棄したり、同じフレームを2回表示したりする必要がある。このような同期処理によって不安定で大きなレイテンシが生じ、カメラ入力から表示までの応答性を低下させるほか、同期用バッファが必要不可欠となり記憶領域を圧迫するなどの問題があった。インターフェースが非同期でクロックを共有できないUSBカメラにおいては特に、同期処理が困難であった。

【0005】

本発明はこうした課題に鑑みてなされたものであり、その目的は、カメラ入力とディスプレイ出力を容易に同期動作させることのできる画像処理技術を提供することにある。

【課題を解決するための手段】

【0006】

本発明のある態様は撮像装置に関する。この撮像装置は、撮像素子が撮像した動画像の各フレームデータを垂直同期信号の周波数で走査ライン順に出力する出力制御部と、出力制御部が出力するフレームデータの出力時刻と、動画像を即時表示するディスプレイにおける出力周波数に基づく基準出力時刻とのずれが所定のしきい値を超えたとき、垂直同期信号の発生タイミングの設定を変更する垂直同期信号調整部と、を備えたことを特徴とする。

【0007】

本発明の別の態様は情報処理装置に関する。この情報処理装置は、接続した撮像装置から順次入力される各フレームデータの入力時刻を取得し、当該フレームデータの出力先のディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視するずれ時間監視部と、ずれが所定のしきい値を超えたとき、撮像装置における垂直同期信号の発生タイミングを調整する要求信号を撮像装置に送信する動作周期調整部と、を備えたことを特徴とする。

【0008】

本発明のさらに別の態様は情報処理システムに関する。この情報処理システムは、動画像を撮影する撮像装置と、当該動画像のフレームデータを順次取得しディスプレイに出力する情報処理装置と、を備えた情報処理システムであって、情報処理装置は、撮像装置から入力される各フレームデータの入力時刻を取得し、ディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視するずれ時間監視部と、ずれが所定のしきい値を超えたとき、撮像装置における垂直同期信号の発生タイミングを調整する要求信号を撮像装置に送信する動作周期調整部と、を備え、撮像装置は、フレームの最終走査ラインにおいて、画素値の出力周波数を有するピクセルクロックのエッジの数をピクセルカウント値としてカウントし、要求信号を取得した際、垂直同期信号を発生させるピクセルカウント値の設定を変更する垂直同期信号調整部を備えたことを特徴とする。

【0009】

本発明のさらに別の態様はフレームデータ出力同期化方法に関する。このフレームデータ出力同期化方法は、撮像装置が、撮影した動画像を即時表示するディスプレイにおけるフレームデータ出力処理と、自らのフレームデータ出力処理を同期させる方法であって、各フレームデータを垂直同期信号の周波数で走査ライン順に出力するステップと、出力するフレームデータの出力時刻と、ディスプレイにおける出力周波数に基づく基準出力時刻とのずれが所定のしきい値を超えたとき、垂直同期信号の発生タイミングの設定を変更するステップと、を含むことを特徴とする。

【0010】

なお、以上の構成要素の任意の組合せ、本発明の表現を方法、装置、システム、コンピュータプログラム、コンピュータプログラムを記録した記録媒体などの間で変換したものもまた、本発明の態様として有効である。

【発明の効果】

【0011】

本発明によると、カメラ入力とディスプレイ出力を容易に同期動作させることができる。

【図面の簡単な説明】

【0012】

【図1】本実施の形態を適用できる情報処理システムの構成例を示す図である。

【図2】カメラ入力とビデオ出力の同期処理を実現する従来技術におけるシステム構成を示す図である。

【図3】図2で示した構成によってフレームデータ出力タイミングの調整を行うときの、撮像装置からの出力データ、同期用バッファにおけるデータ、フレームメモリにおけるデータの変遷を示す図である。

【図4】撮像装置とディスプレイが同期している場合の撮像装置からの出力データ、入力バッファにおけるデータ、フレームメモリにおけるデータの変遷を示す図である。

【図5】本実施の形態における撮像装置とホスト端末の構成を示す図である。

【図6】本実施の形態の撮像装置において発生させる信号を説明するための図である。

【図7】本実施の形態の撮像装置における垂直同期信号の発生タイミングの調整原理を説明するための図である。

【図8】本実施の形態において撮像装置からの1フレームあたりの入力周期を調整する処理の手順を示すフローチャートである。

【図9】本実施の形態において撮像装置からの入力周期を調整した場合における、撮像装置からの出力データ、入力バッファにおけるデータ、フレームメモリにおけるデータの変遷を示す図である。

【図10】ホスト端末に同期用バッファを設けた状態で本実施の形態の撮像装置を接続した場合の、撮像装置からの出力データ、同期用バッファにおけるデータ、フレームメモリにおけるデータの変遷を示す図である。

【発明を実施するための形態】

【0013】

図1は本実施の形態を適用できる情報処理システムの構成例を示す。情報処理システム10は、ユーザ1などの対象物をビデオ撮影する撮像装置12、撮影した動画像データの表示を制御するホスト端末20、動画像を表示するディスプレイ16を含む。撮像装置12、ホスト端末20、ディスプレイ16のうちいずれか2つ、または全てが組み合わされて一体的に装備されていてもよい。また、撮像装置12は必ずしもディスプレイ16の上に設置されていなくてもよい。さらにユーザ1は人でなくてもよく、その数も限定されない。

【0014】

撮像装置12は、CCD(Charge Coupled Device)またはCMOS(Complementary Metal Oxide Semiconductor)等の撮像素子を備えたデジタルビデオカメラである。撮像装置12が撮影した動画像のフレームデータは逐次、ホスト端末20に送信される。ホスト端末20は、送信されたフレームデータを、ディスプレイ16の出力タイミングに合わせてディスプレイ16に出力する。なおホスト端末20はフレームデータを用いて画像出力制御以外の所定の処理を行ってもよい。例えばユーザ1の姿をキャラクタ化して仮想世界の画像を生成しディスプレイ16に表示させることによりゲームなどを実現することができるが、このような技術は一般的なものを適用できるためここでは言及しない。

【0015】

ディスプレイ16は、ホスト端末20の制御のもと入力されたフレームデータを画像として表示する。ディスプレイ16は、画像を出力するディスプレイおよび音声を出力するスピーカを有するテレビであってよく、例えば液晶テレビ、プラズマテレビ、PCディスプレイ等である。

【0016】

本実施の形態では、このような情報処理システム10において撮像装置12によるカメラ入力とディスプレイ16によるビデオ出力とが非同期である場合に、低コストかつ容易に同期をとる。まず本実施の形態の効果を明らかにするために、このような場合に適用できる同期処理の既存手法について説明する。

【0017】

図2はカメラ入力とビデオ出力の同期処理を実現する従来技術におけるシステム構成を示している。なお同図は従来技術における構成を示しているため、撮像装置12a、ホスト端末20aとして本実施の形態の各装置と区別するが、接続形態は図1で示したのと同様である。ホスト端末20aは、撮像装置12aから、撮像装置の出力周波数で入力されるフレームデータを、ディスプレイ16の出力周波数で出力する必要がある。

【0018】

そのためホスト端末20aには、ディスプレイ16の出力周波数に合わせて書き換えられるフレームメモリ26の他に、撮像装置12aとフレームメモリ26との間でフレームデータをバッファしてタイミング調整を行うための同期用バッファ22を備える必要がある。さらにホスト端末20aは、フレームメモリ26からディスプレイ16へのフレームデータの出力を制御する表示制御部24を備える。

【0019】

図3は図2で示した構成によってフレームデータ出力タイミングの調整を行うときの、撮像装置12aからの出力データ(上段)、同期用バッファ22におけるデータ(中段3列)、フレームメモリ26におけるデータ(下段2列)の変遷を示している。例えば撮像装置12aは60fpsのフレームレートで撮影およびデータ入力を行い、ディスプレイ16は59.94fpsのフレームレートで動画表示を行うとする。この場合、撮像装置12aからホスト端末20aへのフレームデータ入力周期は1フレームあたり16.0msec、ホスト端末20aからディスプレイ16への出力周期は1フレームあたり16.7msecである。

【0020】

同図は横軸に時間経過を示し、1フレーム分に対応する期間を1つの矩形で表している。矩形内の文字はフレーム番号を表す。同図上端の凡例にあるように、矩形内の実線および点線の斜線はそれぞれ、走査ラインを走査することによるデータの出力期間(scan out)、および入力期間(scan in)を表している。また網掛けで示された矩形はデータの保持期間を表している。

【0021】

まず撮像装置12aでは、時刻t0において、第nフレームの撮像および出力が開始される。するとホスト端末20aにおける同期用バッファ22の第1バッファ22aには、時刻t1から、撮像が終了した走査ライン順に第nフレームのデータが格納される。第nフレームのデータを全て格納し終える時刻t2までの時間は上述の通り16.0msecである。表示制御部24は、その前のフレーム、すなわち第(n−1)フレームのデータをフレームメモリ26へ格納し終えた時刻t3から、フレームメモリ26の第1領域26aへ第nフレームのデータを格納し始める。

【0022】

なお同期用バッファ22の矩形列の下に示されるΔtの幅を有するマーカーは、直上の矩形が表すフレームデータの読み出し期間を示している。第nフレームの読み出し期間、すなわち時刻t3からΔtの間は、当該バッファへの別のデータの書き込みはできない。フレームメモリ26の第1領域26aへ書き出された第nフレームのデータは、その前の第(n−1)フレームの表示が終了した時刻t4から、ディスプレイ16へ出力され、画像が表示される。第nフレームの表示開始時刻t4から終了時刻t5までの時間は上述の通り16.7msecである。

【0023】

このような処理を、撮像装置12aにおける撮影の進捗に応じて取得された各フレームデータに対して同様に行う。すなわち撮像装置12aおよび同期用バッファ22は、16.0msecを1フレームあたりの処理周期として動作し、フレームメモリ26およびディスプレイ16は、16.7msecを1フレームあたりの処理周期として動作する。同図に示すようにフレームメモリ26は、ディスプレイ16へ出力中のフレームデータを格納する領域と、その次のフレームを格納する領域とを分け、第1領域26a、第2領域26bを交互に使用することにより、円滑な画像表示を行う。

【0024】

一方、同期用バッファ22は、あるフレームのデータを格納し終えたタイミングと、それを読み出すタイミングが、撮像装置12aとディスプレイ16の動作周波数の違いによってずれていく。結果としてほとんどの期間において、フレームデータを格納する際に、その2つ前のフレームデータの読み出しが完了していない状況となる。例えば第(n+2)フレームのデータの格納が開始される時刻Tでは、2つ前の第nフレームのデータが読み出し中である。

【0025】

このため、第nフレームのデータを格納している第1バッファ22aを、第(n+2)フレームのデータの格納先とはできない。このように、あるフレームデータの格納開始時に、2つ前のフレームのデータの読み出しが完了していない状況が発生する環境においては、同期用バッファ22として、第1バッファ22a、第2バッファ22b、第3バッファ22c、の3つのバッファを用意し、循環して使用する必要がある。

【0026】

3つのバッファを使用した場合、基本的には各フレームのデータ保持期間は、格納処理の期間を除くと2周期分となる。つまり同期用バッファ22に同じフレームのデータを保持できる期間は、バッファの数に依存して有限である。しかしディスプレイ16側の動作周期が撮像装置12a側の動作周期より長い場合、同期用バッファ22における各フレームデータの保持期間に対し、それを読み出す期間が徐々に後へずれていく。そしてやがては読み出し期間がデータ保持期間を超過してしまうことになる。このようにして、データが同期用バッファ22に格納されているにも関わらずディスプレイ16に表示しきれないフレームが発生する。この場合、当該フレームデータを破棄し、その次のフレームデータを読み出して表示せざるを得なくなる。

【0027】

図3の例では、第(n+6)フレームの読み出しを終えた時刻t6の次にあるべき、第(n+7)フレームを読み出す期間が、第(n+7)フレームのデータ保持期間を超えてしまう。そのため第7フレームをとばし、時刻t7において、格納済みの第(n+8)フレームのデータ読み出しを開始している。この例ではディスプレイ16側の動作周期が撮像装置12a側の基本周期より長いため、余ったフレームデータが消費されずに破棄されたが、動作周期の大小関係が逆であれば、表示に必要なフレームデータが不足し、同じフレームを2周期分表示せざるを得なくなる。

【0028】

このように、撮像装置12aとディスプレイ16が非同期に動作する場合、同期用バッファ22におけるフレームデータの保持期間と、それを読み出す期間とを比較し、その結果によってデータの破棄や2回表示など複雑な処理を発生させる必要がある。また、動作周期の差によって同期用バッファとして必要なバッファ領域の数が増える。

【0029】

さらに、ディスプレイ16の周波数に同期させてホスト端末が画像処理を行う場合、処理対象となるフレームが1つ破棄されてしまうとことによって生じる不具合も考えられる。例えば被写体の一部をトラッキングする場合、前のフレームとの時間間隔が開いてしまうと、可動範囲が増大するため探索領域を広げる必要が生じる。そのためトラッキング処理に要する時間が増え、レイテンシ増加の要因となる。

【0030】

撮像装置とディスプレイの設定動作周波数がたとえ同じであっても、内蔵する発振回路の精度によって同様のずれが生じる可能性もある。そこで本実施の形態では、撮像装置12内部の垂直同期信号のタイミングをピクセルカウント単位で調整することにより、撮像装置12からのデータ入力とディスプレイ16へのデータ出力の周期のずれを所定の範囲に収め、少なくとも1フレーム分の時間差が生じないようにする。

【0031】

図4は撮像装置とディスプレイが同期している場合の撮像装置からの出力データ(上段)、入力バッファにおけるデータ(中段2列)、フレームメモリにおけるデータ(下段2列)の変遷を示している。図の表し方は図3と同様であるが、この場合、撮像装置からの入力データを格納するメモリは、「同期用バッファ」ではなく、ホスト端末20内部の処理に用いるための「入力バッファ」として機能する。撮像装置とディスプレイの動作周期は例えば、いずれも16.0msecであったとする。

【0032】

この場合、同図に示すように、フレームデータのフレームメモリへの読み出しは、常時、入力バッファへの当該データの格納が完了した直後から開始でき、その2つの時刻がずれることはない。結果として入力バッファもフレームメモリと同様に、撮像装置から入力されたフレームデータを書き込むためのバッファと、フレームメモリへ読み出すためのバッファのみで構成できる。また上述のように、ずれが蓄積していくことによるフレーム単位の調整が必要ないため、処理を単純化でき突発的なレイテンシの増大を抑えることができる。

【0033】

本実施の形態では、撮像装置とディスプレイの動作周波数が異なっていても、図4で示した同期動作に近い状況を作り出す。具体的には撮像装置12において、1フレーム分として定義される時間、すなわち垂直同期信号(VSync)の間隔を、ピクセルカウント単位で調整し、ディスプレイにおける1フレームの表示周期を目標にした動作周期の合わせ込みを行う。この態様は発振回路の精度に起因したずれに対しても有効である。図5は本実施の形態における撮像装置12とホスト端末20の構成を示している。

【0034】

図5に示す各機能ブロックは、ハードウェア的には、CPU(Central Processing Unit)、RAM(Random Access Memory)、ROM(Read Only Memory)、カウンタ回路などの構成で実現でき、ソフトウェア的にはデータ入出力機能、データ保持機能などの諸機能を発揮するプログラムで実現される。したがって、これらの機能ブロックがハードウェアのみ、ソフトウェアのみ、またはそれらの組合せによっていろいろな形で実現できることは当業者には理解されるところであり、いずれかに限定されるものではない。

【0035】

ホスト端末20は、撮像装置12から入力されたフレームデータを一時格納する入力バッファ32、ディスプレイ16に出力するフレームデータを一時格納するフレームメモリ38、入力バッファ32からフレームメモリ38へのフレームデータの書き出し、フレームメモリ26からディスプレイ16へのフレームデータの出力を制御する表示制御部40を含む。

【0036】

入力バッファ32、フレームメモリ38、および表示制御部40は、図2で示したホスト端末20aにおける同期用バッファ22、フレームメモリ26、および表示制御部24と同様の機能を有する。ただし図4について説明したのと同様、本実施の形態も同期用バッファを用いた調整を行う必要がないため、同期用バッファ22に代えて入力バッファ32を備える。入力バッファ32は図4に示したのと同様、2つのバッファ領域を備えればよい。

【0037】

ホスト端末20はさらに、撮像装置12からのフレームデータの入力タイミングと、ディスプレイ16の出力周波数から得られる当該フレームデータの理想的な入力タイミングとのずれを監視するずれ時間監視部34、入力タイミングのずれの大きさに応じて、撮像装置12における1フレームあたりの動作周期を調整する要求信号を送信する動作周期調整部36を含む。

【0038】

撮像装置12は、撮像素子31とブリッジ部30を含む。撮像素子31は上記のとおりCCDまたはCMOS等のセンサである。ブリッジ部30は、フレームデータのホスト端末20への出力を制御する出力制御部41、撮像装置12における垂直同期信号を起点として水平同期信号(HSync)の出力をカウントし、所定の走査ラインで信号を発生させるHカウンタ部42、Hカウンタ部42からの信号を起点としてピクセルクロックをカウントし、ピクセルクロックに対し設定された値で垂直同期信号を発生させるVSync調整カウンタ部44を含む。

【0039】

出力制御部41は、撮像素子31が撮影した結果得られたフレームのデータを、USBなどのインターフェースを介して、走査ライン順にホスト端末20へ送出する。さらにフレームデータに含まれる各種同期信号の情報を分離し、Hカウンタ部42、VSync調整カウンタ部44に適宜供給する。出力制御部41が行う処理は一般的な技術を適用できるため詳細には言及しない。Hカウンタ部42およびVSync調整カウンタ部44と、ホスト端末20のずれ時間監視部34および動作周期調整部36の詳細な動作は後に述べる。

【0040】

次に図5で示した構成によって、撮像装置12からの入力とディスプレイ16への出力を同期させる原理を説明する。図6は撮像装置12において発生させる信号を説明するための図である。なおこれらの信号は一般的な撮像装置で発生される信号であり、本実施の形態ではそれを利用することができる。同図において右方向が、各走査ラインにおける画素単位の時間経過を、下方向が、走査ライン単位の時間経過を示している。同図中央の矩形のうち白抜きの領域が画素値の入出力期間を表し、網掛けの領域が水平帰線期間(HBlank)および垂直帰線期間(VBlank)を示している。

【0041】

まず横方向に表された、各走査ラインにおける時間経過は、図の上端に示すように、ピクセルクロック(PCLK)の立ち上がりエッジ周期PT(=1/PCLK)を1単位とする。ピクセルクロックは画素値の出力周波数を有する。そして走査ラインごとに、画素値の出力期間を表すデータイネーブル信号(DE)、走査ラインの終点のタイミングを表す水平同期信号(HSync)が発生する。図の縦方向に表された、走査ライン単位の時間経過は、水平同期信号の出力周期を1単位とする。そしてフレームごとに、値を持つ走査ラインの出力期間を表すデータイネーブル信号(DE)、フレームの終点のタイミングを表す垂直同期信号(VSync)が発生する。

【0042】

ここで、水平帰線期間を含めた次の走査ラインまでのピクセルクロックのカウント値をHTotal、垂直帰線期間を含めた次のフレームまでの走査ラインのカウント値をVTotalとすると、撮像装置12で撮影されホスト端末20へ入力されるフレームのフレームレートR(fps)は、

R(fps)=PCLK(Hz)/(HTotal×VTotal)

である。すなわち1フレームあたりの入力周期Tint(sec)は、

Tint(sec)=1/R(fps)=(HTotal×VTotal)/PCLK(Hz)=HTotal×VTotal×PT(sec)

である。

【0043】

本実施の形態では、撮像装置12から入力されるフレームデータの1フレームあたりの入力周期Tintを、ディスプレイ16における1フレームあたりの出力周期に合わせることにより同期動作に近い状況を作り出す。そこで本実施の形態ではまず、HTotalおよびVTotalを調整して走査ライン数単位で大まかな合わせ込みを行った後、実際の時間のずれを監視して、調整の結果決定した、フレームの最後の走査ラインの入力期間におけるピクセルカウントの単位で微調整を行う。

【0044】

走査ライン数単位での調整は、ディスプレイ16における出力フレームレートをターゲットフレームレートTAとしたとき、次の式を満足するようにHTotalおよびVTotalを定めることによって行う。

PCLK/(HTotal×VTotal) < TA < PCLK/HTotal×(VTotal-1)

上式の各項の逆数をとり、周期で比較すると次の式となる。

PT×HTotal×(VTotal-1) < 1/TA < PT × HTotal×VTotal

【0045】

すなわち、垂直同期信号直後のフレームの始点から、最後から2番目の走査ラインの走査完了までに要するピクセルクロック単位の時間「PT×HTotal×(VTotal-1)」と、当該始点から最後の走査ラインの走査完了までに要する時間「PT × HTotal×VTotal」の間に、ディスプレイ16の1フレームあたりの出力周期が入るように、HTotalおよびVTotalを調整する。これにより、ピクセルカウント単位の微調整は最後の走査ラインの走査時間内に限定することができる。

【0046】

図7は撮像装置12における垂直同期信号の発生タイミングの調整原理を説明するための図である。同図における矩形は図6と同様、水平同期信号、垂直同期信号を含めた、1フレームの入力期間を表している。そして当該矩形を左から右に横切る矢印は、走査ラインを模式的に示している。ここで、ディスプレイ16において1フレームの表示が終了する時刻が線50に対応するとすると、上記の式により決定した最後の走査ライン上、厳密にはVTotal−1のカウントとVTotalのカウントの間の時間に、線50が位置することになる。

【0047】

HTotalおよびVTotalの調整は走査ライン単位のものであるため、ディスプレイ16の出力周波数に応じてあらかじめ決定しておく。例えば撮像装置12やホスト端末20の内部メモリに、ディスプレイの出力周波数と、適切なHTotalおよびVTotalの値を対応づけたテーブルを準備しておき、ディスプレイ16が接続されたときに実際の出力周波数に応じてテーブルを参照したうえ決定してもよい。場合によってはピクセルクロック自体を上式による調整対象としてもよい。

【0048】

このようにHTotalおよびVTotalを決定したら、その後は実際の時間のずれを監視しながらピクセルカウント単位の微調整を行う。この調整は定性的には、最後の走査ライン上にあるべき当該フレームとしての終点、すなわち図7における最後の矢印52の先端を、線50に近づける調整となる。調整によって得られた終点で垂直同期信号を発生させ、次のフレームの撮像を開始すれば、撮像装置12からの1フレームあたりの入力周期と、ディスプレイ16への1フレームあたりの出力周期がおよそ等しくなる。

【0049】

ピクセルカウント単位での時間計測では厳密な計測時間に対し丸め誤差が発生すること、撮像装置やディスプレイの周波数にはそれぞれ揺らぎがあること、処理の負荷などを考慮すると、時間のずれが所定量蓄積した時点で、矢印52の長さ、すなわち最後の走査ラインにおいて垂直同期信号を発生させるまでのピクセルカウント値を調整するのが効率的である。以後、このようなピクセルカウント値を「最終ライン期間」と呼ぶ。

【0050】

実際の調整処理は、最後の走査ラインにおいて線50までの距離より短い最終ライン期間MF、および線50までの距離より長い最終ライン期間MSをあらかじめ決定しておき、それらを切り替えることによって行う。短い方の最終ライン期間MFおよび長い方の最終ライン期間MSは次の式を満足する値である。

PT×(HTotal×(VTotal-1)+ MF) < 1/TA < PT ×(HTotal×(VTotal-1)+ MS)

そして撮像装置12からの入力がディスプレイ16への出力より早すぎる場合は長い最終ライン期間MSを、遅すぎる場合は短い最終ライン期間MFを設定することにより、撮像装置12からの1フレームあたりの入力周期を調整する。

【0051】

2つの最終ライン期間MFおよびMSを、線50で示された、ディスプレイ16による1フレームの出力終了時刻を挟む直近の整数値とすると、MFおよびMSは以下の式から決定できる。

MF = floor(FIT/PT - HTotal (VTotal -1 ))

MS = ceil(FIT/PT - HTotal (VTotal -1))

ここでfloor(x)はx以下の最大の整数、ceil(x)はx以上の最小の整数を出力する関数である。またFITは1/TAで与えられる、ディスプレイ16の1フレームの表示周期である。

【0052】

さらに撮像装置12およびディスプレイ16における動作周波数の揺らぎをの幅を考慮し、2つの最終ライン期間MFおよびMSを以下のように決定して両者の差を大きくしてもよい。

MF = floor(FIT/PT - HTotal (VTotal -1 ))- dz/2

MS = ceil(FIT/PT - HTotal (VTotal -1))+ dz/2

ここでdzは揺らぎの幅を考慮した補正値であり、あらかじめ決定しておく。

【0053】

次に、以上のような調整を図5に示した構成によって実現するときの処理手順を示す。図8は本実施の形態において撮像装置12からの1フレームあたりの入力周期を調整する処理の手順を示すフローチャートである。同フローチャートはユーザがホスト端末20に対し、動画像の撮影とそれを用いた画像の表示を含む機能の実行を指示し、ホスト端末20が撮像装置12に撮影の開始を要求したときに処理が開始される。

【0054】

まず撮像装置12において、最終ライン期間Mに初期値M0を設定する(S10)。初期値M0は0からHTotalまでのいずれの値でもよく、MFまたはMSでもよい。次に撮像装置12は動画撮影を開始する(S12)。そして出力制御部41は、フレーム番号Nに0を代入したうえ(N14)、第0番目のフレームのデータを走査ライン順にホスト端末20へ入力していく(S16)。このときHカウンタ部42は、垂直同期信号の発生を受けてカウント値を0とした後、水平同期信号の出力をカウントしていくことで入力済みの走査ラインの数Hを監視する。

【0055】

撮像装置12から入力されたデータをホスト端末20が取得し、ディスプレイ16への出力を開始することにより、ディスプレイ16に動画像が表示される(S18)。撮像装置12では、ホスト端末20へ入力済みの走査ラインの数HがVTotal−1に達しない間は、各走査ラインのデータ出力を継続する(S20のN、S16)。出力済みの走査ラインの数HがVTotal−1に達したら(S20のY)、最後の走査ラインVTotalのデータをホスト端末20へ入力していく。このときVSync調整カウンタ部44は、走査ラインの数HがVTotal−1に達したことをHカウンタ部42から受けてカウント値を0とした後、ピクセルクロックの立ち上がりエッジをカウントしていく。

【0056】

ピクセルカウント値Pが最終ライン期間Mに達しない間は、データ入力を継続する(S24のN、S22)。ピクセルカウント値Pが、最終ライン期間Mに達したら(S24のY)、 VSync調整カウンタ部44は、垂直同期信号を撮像素子31およびHカウンタ部42に出力する(S26)。

【0057】

ホスト端末20のずれ時間監視部34は、1フレーム分のデータが撮像装置12から入力される都度、受信時のタイムスタンプを取得する。そして、第0フレームのデータ入力開始から第Nフレームのデータ入力完了までの実際の時間と、ディスプレイ16の出力周波数で入力動作がなされたときの想定時間との差、すなわちずれが、あらかじめ準備したしきい値を超えたか否かを判定する(S30)。しきい値を超えている場合は(S30のY)、撮像装置12のVSync調整カウンタ部44が保持している最終ライン期間Mに、MFまたはMSの値を設定し直す(S32)。

【0058】

ずれ量Dは例えば次の式で求められる。

D = |time_stump(N)- FIT×N|

ここでtime_stump(N)は、第0フレームの入力開始から第Nフレームの入力完了までのタイムスタンプの差である。このタイムスタンプを、ホスト端末20が出力するビデオクロック由来の周波数制御用電圧VCTにより計測することで、ホスト端末20内で制御がなされるFITの実際の時間に基づき正確に比較することができる。

【0059】

上述のようにずれ量Dがしきい値dwより大きければ、最終ライン期間Mを設定し直す。このとき、time_stump(N)- FIT×Nが正の値であれば撮像装置12からの入力が遅いため短い方の最終ライン期間MFを設定する。負の値であれば撮像装置12からの入力が速いため長い方の最終ライン期間MFを設定する。撮像装置12における最終ライン期間の更新は、実際には最後の走査ライン以外のデータをホスト端末20へ入力しているS16、S20の処理ステップの期間中に行ってよい。ずれ量Dがしきい値dwを超えていない場合は、そのままの設定を維持する(S30のN)。

【0060】

ユーザからの指示入力などにより処理を終了する必要が生じない間は(S34のN、S38のN)、撮像装置12においてフレーム番号をインクリメントしながら(S36)、以上の処理を繰り返す。この間、撮像装置12における撮影、ホスト端末20へのフレームデータ入力、ディスプレイ16へのフレームデータ出力、およびディスプレイ16における動画像の表示は継続して行われているものとする。処理終了の必要が生じたら、撮像装置12、ホスト端末20の双方で処理を終了する(S34のY、S38のY)。

【0061】

図9は本実施の形態によって撮像装置12からの入力周期を調整した場合における、撮像装置12からの出力データ(上段)、入力バッファ32におけるデータ(中段2列)、フレームメモリ38におけるデータ(下段2列)の変遷を示している。図の表し方は図4と同様である。また同図では、撮像装置12における出力対象のフレームを表す各矩形の上に、当該フレームに対する最終ライン期間Mの設定値を示している。

【0062】

まず撮像装置12から第nフレームが出力される時刻t0において、最終ライン期間Mには、短い方の最終ライン期間MFが設定されている。この設定により、撮像装置12からの1フレームあたりのデータ入力周期は、ディスプレイ16への1フレームあたりのデータ出力周期よりわずかに短い状態となっている。

【0063】

図4で説明したように、撮像装置12からの入力とディスプレイ16への出力が完全に同期していると、入力バッファ32への格納が完了したフレームデータは直後にディスプレイ16に出力される。本実施の形態でも上記のとおりVTotal、HTotalを調整したうえで、ピクセルカウント単位でディスプレイの出力周波数への合わせ混みを行っているため、図4に近い状態が得られている。

【0064】

一方、フレーム処理が進捗していくと、撮像装置12からの入力周期とディスプレイ6への出力周期の微妙なずれが蓄積していく。同図では、各フレームのデータが入力バッファ32に格納し終えた時刻と、当該データのフレームメモリ38への読み出しが開始される時刻とのずれ時間をD0、D1、D2、・・・として表している。例えば第n+1フレームのデータを入力バッファ32に格納し終えた時刻t1から、当該データの読み出し開始時刻t2までの時間のずれがD1である。

【0065】

この時間のずれは、撮像装置12からの1フレームあたりの入力周期とディスプレイ16への1フレームあたりの出力周期の差に起因するものであり、ひいては、ずれ時間監視部34がしきい値判定をする値に対応する。上述のとおり最終ライン期間Mとして小さい方の値MFが設定されている場合、撮像装置12からの入力周期がディスプレイ16への出力周期より短いため、データの入力が完了する時刻がその読み出しを開始する時刻より前にずれていき、D0、D1、D2、D3、とその値が増えていく。そしてD4でしきい値dwを超える。

【0066】

動作周期調整部36はこの結果を受け、VSync調整カウンタ部44が保持する最終ライン期間Mを、長い方の最終ライン期間MSに設定し直すように要求信号を送信する(S40)。この設定により撮像装置12からの入力周期がディスプレイ16への出力周期より長くなるため、ずれ時間はその後のD5で減少に転じ、D6、D7、D8、D9と減少していく。さらにフレーム処理が進捗すると、やがてずれ時間は撮像装置12からの入力が遅れる方向に増えていきくため、しきい値dwを超えた時点で最終ライン期間Mを、短い方の最終ライン期間MFに設定し直す(図示せず)。

【0067】

このようにすることで、撮像装置12からのフレームデータの格納が完了する時刻と、ディスプレイ16への出力が開始される時刻との差が最大でもしきい値dw程度に抑えられるため、1フレーム分のデータの余りや不足が生じることがなくなる。結果として、つじつまを合わせるためにデータを破棄したり同じフレームを2回表示したりする必要がなくなり、不安定なレイテンシの発生を抑制できる。さらに図9に示したように入力バッファ32は2つのバッファ領域のみで充足する。

【0068】

本実施の形態の撮像装置12は、最終ライン期間Mの設定を更新しなければ、既存の非同期の撮像装置と同様に動作する。したがって用途に合わせて同期/非同期を切り替えるようにしてもよい。図10は、図2で示したようにホスト端末20に同期用バッファ22を設けた状態で本実施の形態の撮像装置12を接続した場合の、撮像装置12からの出力データ(上段)、同期用バッファ22におけるデータ(中段3列)、フレームメモリ26におけるデータ(下段2列)の変遷を示している。

【0069】

図3で示したように、同期用バッファ22のみでの運用では、ディスプレイ16側の動作周期が撮像装置12側のそれより長い場合、同期用バッファ22における各フレームのデータの保持期間に対し、それを読み出す期間が徐々に後にずれていく。逆に短い場合は、徐々に前にずれていく。本実施の形態を導入し、最終ライン期間Mを適切に設定することにより、同図に示すように、同期用バッファ22におけるデータ保持期間のうちおよそ前半の期間で各フレームのデータを読み出すことができる。

【0070】

結果として、ディスプレイ16の周波数に合わせたデータ読み出しが行われても、本来のフレーム順で確実にデータへアクセスでき、余分な処理の必要が生じない。また表示しきれないフレームのデータを破棄するような事態が生じないため、フレームの時間間隔が一定に保たれる。これにより、読み出されたフレームデータを用いてトラッキングなどの処理を行う場合でも、フレームを破棄したことに起因する処理の負荷や精度の変動が発生しない。

【0071】

以上述べた本実施の形態によれば、撮像装置で撮影した動画をリアルタイムでディスプレイに表示するシステムにおいて、撮像装置からホスト端末へのフレームデータの入力周期を、ホスト端末からディスプレイへの出力周期に近づけるように、垂直同期信号の発生タイミングを調整する。このためまず、走査ラインの長さおよび数による調整を事前に行っておき、実際の時間のずれを監視しながら、最後の走査ラインにおける垂直同期信号の発生タイミングをピクセルカウント単位で調整する。

【0072】

これによりピクセルクロックの立ち上がりエッジ周期レベル、すなわちディスプレイの出力周期の100万分の1程度での時間調整を低コストで実現できる。走査ラインの数のみを調整する場合、フレームによって撮影時間の変動が比較的大きくなり、ローリングシャッターを有する撮像素子において露出の変動を引き起こす可能性があるが、本実施の形態のように微少時間での調整によれば、露出への影響は無視できるレベルとなる。

【0073】

また調整は、時間のずれが所定量、累積した時点で、設定値を更新し直すのみであるため、処理コストへの影響が少ない。さらに、2つの最終ライン期間の差分や、時間のずれに対するしきい値によって、装置自体が持つ動作周波数の揺らぎを吸収したタイミングでの調整が可能であるため、高頻度に無駄な調整を行い余計に処理の負荷がかかるといった不都合が発生しない。結果として、低コストかつ処理の負荷への影響を少なく、動画撮影から表示までを低レイテンシで応答性よく実行できる。

【0074】

以上、本発明を実施の形態をもとに説明した。上記実施の形態は例示であり、それらの各構成要素や各処理プロセスの組合せにいろいろな変形例が可能なこと、またそうした変形例も本発明の範囲にあることは当業者に理解されるところである。

【0075】

例えば本実施の形態における撮像装置は一眼の撮像素子からなっていたが、ステレオカメラなど複数のカメラを備えた構成としてもよい。この場合、VSync調整カウンタ部から発生させた垂直同期信号を全てのカメラに与えることにより、複数のカメラからの映像をディスプレイの出力と同期させることが容易にできる。

【符号の説明】

【0076】

10 情報処理システム、 12 撮像装置、 16 ディスプレイ、 20 ホスト端末、 30 ブリッジ部、 32 入力バッファ、 34 ずれ時間監視部、 36 動作周期調整部、 38 フレームメモリ、 40 表示制御部、 41 出力制御部、 42 Hカウンタ部、 44 VSync調整カウンタ部。

【特許請求の範囲】

【請求項1】

撮像素子が撮像した動画像の各フレームデータを垂直同期信号の周波数で走査ライン順に出力する出力制御部と、

前記出力制御部が出力するフレームデータの出力時刻と、動画像を即時表示するディスプレイにおける出力周波数に基づく基準出力時刻とのずれが所定のしきい値を超えたとき、垂直同期信号の発生タイミングの設定を変更する垂直同期信号調整部と、

を備えたことを特徴とする撮像装置。

【請求項2】

前記垂直同期信号調整部は、フレームの最終走査ラインにおいて、画素値の出力周波数を有するピクセルクロックのエッジの数をピクセルカウント値としてカウントし、垂直同期信号を発生させるピクセルカウント値の設定を変化させることを特徴とする請求項1に記載の撮像装置。

【請求項3】

フレームの各走査ラインの走査周期を表すピクセルカウント値と、フレームの走査ラインの数は、前記ディスプレイにおける出力周波数に基づく1フレームあたりの走査時間の基準終了時刻が、前記撮像装置におけるフレームの最終走査ラインの走査期間中に到来するように設定されていることを特徴とする請求項2に記載の撮像装置。

【請求項4】

前記垂直同期信号調整部は、前記フレームデータの出力時刻と前記基準出力時刻の前後関係によって、あらかじめ定められた、前記ディスプレイにおける出力周波数に基づく1フレームあたりの走査時間の基準終了時刻より遅いタイミングのピクセルカウント値と、当該基準終了時刻より早いタイミングのピクセルカウント値を、垂直同期信号を発生させるピクセルカウント値として切り替えて設定することを特徴とする請求項1または2に記載の撮像装置。

【請求項5】

接続した撮像装置から順次入力される各フレームデータの入力時刻を取得し、当該フレームデータの出力先のディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視するずれ時間監視部と、

前記ずれが所定のしきい値を超えたとき、前記撮像装置における垂直同期信号の発生タイミングを調整する要求信号を前記撮像装置に送信する動作周期調整部と、

を備えたことを特徴とする情報処理装置。

【請求項6】

動画像を撮影する撮像装置と、当該動画像のフレームデータを順次取得しディスプレイに出力する情報処理装置と、を備えた情報処理システムであって、

前記情報処理装置は、

前記撮像装置から入力される各フレームデータの入力時刻を取得し、前記ディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視するずれ時間監視部と、

前記ずれが所定のしきい値を超えたとき、前記撮像装置における垂直同期信号の発生タイミングを調整する要求信号を前記撮像装置に送信する動作周期調整部と、

を備え、前記撮像装置は、

フレームの最終走査ラインにおいて、画素値の出力周波数を有するピクセルクロックのエッジの数をピクセルカウント値としてカウントし、前記要求信号を取得した際、垂直同期信号を発生させるピクセルカウント値の設定を変更する垂直同期信号調整部を備えたことを特徴とする情報処理システム。

【請求項7】

撮像装置が、撮影した動画像を即時表示するディスプレイにおけるフレームデータ出力処理と、自らのフレームデータ出力処理を同期させる方法であって、

各フレームデータを垂直同期信号の周波数で走査ライン順に出力するステップと、

出力するフレームデータの出力時刻と、前記ディスプレイにおける出力周波数に基づく基準出力時刻とのずれが所定のしきい値を超えたとき、前記垂直同期信号の発生タイミングの設定を変更するステップと、

を含むことを特徴とするフレームデータ出力同期化方法。

【請求項8】

接続した撮像装置から順次入力される各フレームデータの入力時刻を取得し、当該フレームデータの出力先のディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視する機能と、

前記ずれが所定のしきい値を超えたとき、前記撮像装置における垂直同期信号の発生タイミングを調整する要求信号を前記撮像装置に送信する機能と、

をコンピュータに実現させることを特徴とするコンピュータプログラム。

【請求項9】

接続した撮像装置から順次入力される各フレームデータの入力時刻を取得し、当該フレームデータの出力先のディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視する機能と、

前記ずれが所定のしきい値を超えたとき、前記撮像装置における垂直同期信号の発生タイミングを調整する要求信号を前記撮像装置に送信する機能と、

をコンピュータに実現させることを特徴とするコンピュータプログラムを記録した記録媒体。

【請求項1】

撮像素子が撮像した動画像の各フレームデータを垂直同期信号の周波数で走査ライン順に出力する出力制御部と、

前記出力制御部が出力するフレームデータの出力時刻と、動画像を即時表示するディスプレイにおける出力周波数に基づく基準出力時刻とのずれが所定のしきい値を超えたとき、垂直同期信号の発生タイミングの設定を変更する垂直同期信号調整部と、

を備えたことを特徴とする撮像装置。

【請求項2】

前記垂直同期信号調整部は、フレームの最終走査ラインにおいて、画素値の出力周波数を有するピクセルクロックのエッジの数をピクセルカウント値としてカウントし、垂直同期信号を発生させるピクセルカウント値の設定を変化させることを特徴とする請求項1に記載の撮像装置。

【請求項3】

フレームの各走査ラインの走査周期を表すピクセルカウント値と、フレームの走査ラインの数は、前記ディスプレイにおける出力周波数に基づく1フレームあたりの走査時間の基準終了時刻が、前記撮像装置におけるフレームの最終走査ラインの走査期間中に到来するように設定されていることを特徴とする請求項2に記載の撮像装置。

【請求項4】

前記垂直同期信号調整部は、前記フレームデータの出力時刻と前記基準出力時刻の前後関係によって、あらかじめ定められた、前記ディスプレイにおける出力周波数に基づく1フレームあたりの走査時間の基準終了時刻より遅いタイミングのピクセルカウント値と、当該基準終了時刻より早いタイミングのピクセルカウント値を、垂直同期信号を発生させるピクセルカウント値として切り替えて設定することを特徴とする請求項1または2に記載の撮像装置。

【請求項5】

接続した撮像装置から順次入力される各フレームデータの入力時刻を取得し、当該フレームデータの出力先のディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視するずれ時間監視部と、

前記ずれが所定のしきい値を超えたとき、前記撮像装置における垂直同期信号の発生タイミングを調整する要求信号を前記撮像装置に送信する動作周期調整部と、

を備えたことを特徴とする情報処理装置。

【請求項6】

動画像を撮影する撮像装置と、当該動画像のフレームデータを順次取得しディスプレイに出力する情報処理装置と、を備えた情報処理システムであって、

前記情報処理装置は、

前記撮像装置から入力される各フレームデータの入力時刻を取得し、前記ディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視するずれ時間監視部と、

前記ずれが所定のしきい値を超えたとき、前記撮像装置における垂直同期信号の発生タイミングを調整する要求信号を前記撮像装置に送信する動作周期調整部と、

を備え、前記撮像装置は、

フレームの最終走査ラインにおいて、画素値の出力周波数を有するピクセルクロックのエッジの数をピクセルカウント値としてカウントし、前記要求信号を取得した際、垂直同期信号を発生させるピクセルカウント値の設定を変更する垂直同期信号調整部を備えたことを特徴とする情報処理システム。

【請求項7】

撮像装置が、撮影した動画像を即時表示するディスプレイにおけるフレームデータ出力処理と、自らのフレームデータ出力処理を同期させる方法であって、

各フレームデータを垂直同期信号の周波数で走査ライン順に出力するステップと、

出力するフレームデータの出力時刻と、前記ディスプレイにおける出力周波数に基づく基準出力時刻とのずれが所定のしきい値を超えたとき、前記垂直同期信号の発生タイミングの設定を変更するステップと、

を含むことを特徴とするフレームデータ出力同期化方法。

【請求項8】

接続した撮像装置から順次入力される各フレームデータの入力時刻を取得し、当該フレームデータの出力先のディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視する機能と、

前記ずれが所定のしきい値を超えたとき、前記撮像装置における垂直同期信号の発生タイミングを調整する要求信号を前記撮像装置に送信する機能と、

をコンピュータに実現させることを特徴とするコンピュータプログラム。

【請求項9】

接続した撮像装置から順次入力される各フレームデータの入力時刻を取得し、当該フレームデータの出力先のディスプレイにおける出力周波数に基づく基準入力時刻からのずれを監視する機能と、

前記ずれが所定のしきい値を超えたとき、前記撮像装置における垂直同期信号の発生タイミングを調整する要求信号を前記撮像装置に送信する機能と、

をコンピュータに実現させることを特徴とするコンピュータプログラムを記録した記録媒体。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−34039(P2013−34039A)

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願番号】特願2011−167800(P2011−167800)

【出願日】平成23年7月29日(2011.7.29)

【出願人】(310021766)株式会社ソニー・コンピュータエンタテインメント (417)

【Fターム(参考)】

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願日】平成23年7月29日(2011.7.29)

【出願人】(310021766)株式会社ソニー・コンピュータエンタテインメント (417)

【Fターム(参考)】

[ Back to top ]