撮像装置

【課題】表示させる動画像に残像効果を持たせて、急激な構図変化をしたときであっても、主被写体を見失ってしまうことを防止する。

【解決手段】光電荷を生成し蓄積するフォトダイオード101と、前記フォトダイオードに接続され前記光電荷を転送する転送トランジスタ102と、前記転送トランジスタに接続された前記光電荷を蓄積する蓄積容量とを備え、前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを実行する第1の駆動モードと、電荷のリセットを非実行する第2の駆動モードとを有する。

【解決手段】光電荷を生成し蓄積するフォトダイオード101と、前記フォトダイオードに接続され前記光電荷を転送する転送トランジスタ102と、前記転送トランジスタに接続された前記光電荷を蓄積する蓄積容量とを備え、前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを実行する第1の駆動モードと、電荷のリセットを非実行する第2の駆動モードとを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は画像を生成するための撮像装置の改良に関するもので、特に連続して生成される画像に対して残像効果を付加することが可能な撮像装置に関するものである。

【背景技術】

【0002】

画像を生成するための撮像装置の機能として、1シーンのみを撮像する静止画モードと連続した複数のシーンを撮像する動画モードがあることは良く知られている。またこれら撮像された静止画や動画を表示、記録することが可能な撮像装置も種々製品化されている。

【0003】

ところで電子シャッタを用いて高速移動する被写体を動画モードで撮像し表示した場合、動画像としては不自然な映像になるという問題がある。その対策として特許文献1では、1フィールド(1フレーム)の間に、感光部に蓄積された電荷の掃捨処理と、転送処理とを所定の時間の中で交互に繰り返し且つ、電荷の掃捨量を制御することにより、残像効果を持ち自然で連続的な解像度の高い画像を生成する提案がされている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001-197373号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

一般的にこれらの撮像装置には、被写体の構図を決めるために動画モードで撮像された画像を表示装置で表示する機能も有するが、人ごみなど複数の類似した被写体があったり、周囲輝度が暗い場合などに急激な構図変化をさせると、主被写体を見失ってしまうという問題を有している。

【0006】

このことを図9を用いて説明する。

【0007】

図9(a)、(b)は夜空の星を撮像した際、同図(a)から(b)に構図変化させた様子を示している。このように星を主被写体にした場合、周囲に類似の星が多くまた周囲が暗いために目的の星を見失うことが多い。

【0008】

このような構図変化の際に主被写体を見失わないように、表示させる動画像に残像効果を持たせ主被写体を追跡しやすいようにすることが考えられる。

【0009】

図9(c)はこのことを説明する図で、同図内に主被写体の星を太線で示し残像を線で表現している。図9(a)から(c)に構図変化させたときにも、残像があることで主被写体の星が追跡しやすいことがわかる。

【0010】

残像効果を持たせる技術としては、前述の特開2001-197373号があるが、この技術は1フレーム内で残像効果を持たせる技術であり、高速移動する被写体を自然に表示する効果はあるものの、数フレームにわたって残像効果を得ることができないため、所望の追跡効果を得ることはできない。

【0011】

また、撮像された連続画像をメモリに記憶して後段の画像処理で残像効果を得ることも考えられるが、処理回路規模が大きくなることが懸念される。

【課題を解決するための手段】

【0012】

本発明は、上記課題を鑑みて提案されるものであり、残像効果を持たせる手段として、

光を受光して光電荷を生成し蓄積するフォトダイオードと、前記フォトダイオードに接続され前記光電荷を転送する転送トランジスタと、前記転送トランジスタに接続された前記光電荷を蓄積する蓄積容量とを備え、

前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを実行する第1の駆動モードと、

前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを非実行する第2の駆動モードとを有するようにする。

【0013】

また、前記撮像装置は、前記フォトダイオードが光電荷を蓄積した信号を読み出すとともに、読み出された信号を画像として表示する手段と、

前記信号のうち1フレームのみを読み出し表示する静止画撮影モードと

前記信号の読み出しと表示を連続した複数のフレームで繰り返す動画撮影モードとを有し

前記動画撮影モードの時に前記第2の駆動モードで駆動するようにする。

【発明の効果】

【0014】

本発明により、表示させる動画像に残像効果を持たせ主被写体を追跡しやすいようにすることが出来るため、被写体の構図を決めるための所謂EVF動作中に人ごみなど複数の類似した被写体があったり、周囲輝度が暗い場合などに急激な構図変化をしたときであっても、主被写体を見失ってしまうということを防止することが可能となる。

【0015】

特に夜空の星を撮像した際でも、目的の星を見失うことを防止することが可能となる。

【0016】

また、残像効果を持たせる駆動を所謂EVF動作中にや、被写体輝度が暗い場合のみに限定することで、通常は残像効果の無い自然な映像を提供することが可能である。

【図面の簡単な説明】

【0017】

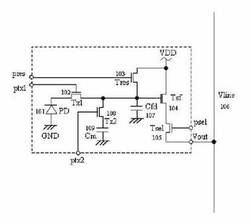

【図1】本発明第1の実施例における画素構成図

【図2】本発明第1の実施例における撮像素子の構成図

【図3(a)】本発明第1、第2の実施例第2のモードを説明するタイミングチャート(その1)

【図3(b)】本発明第1、第2の実施例第2のモードを説明するタイミングチャート(その2)

【図4】本発明第2の実施例における画素構成図

【図5】本発明第3の実施例における画素構成図

【図6】本発明第3の実施例を説明するタイミングチャート

【図7】本発明第1の実施例における撮像装置の全体構成図

【図8】本発明第1の実施例における撮像装置の動作を説明するフローチャート

【図9】従来例を説明する図

【発明を実施するための形態】

【0018】

[実施例1]

図1は本発明の撮像装置の実施形態を示した図であり、CMOS型固体撮像装置の画素セルPixelの構成例を示す回路図である。

【0019】

光信号電荷を発生するフォトダイオード(PD)101は、この例ではアノード側が接地されている。フォトダイオード(PD)101のカソード側は、転送MOSトランジスタ(Tx1)102を介してフローティングディフュージョン(Cfd)107および増幅MOSトランジスタ(Tsf)104のゲートに接続されている。また、上記フローティングディフュージョン(Cfd)107および増幅MOSトランジスタ(Tsf)104のゲート電位は、リセットMOSトランジスタ(Tres)103により共通電源(VDD)とショートされることで固定電位にリセットされる。さらに、上記増幅MOSトランジスタ(Tsf)104は、ドレインが電源VDDに接続され、ソースが選択MOSトランジスタ(Tsel)105のドレインに接続されている。また、選択MOSトランジスタ(Tsel)105のソースは、同一列で共通な垂直出力線(Vline)106に接続されることで画素出力される。更に、上記フローティングディフュージョン(Cfd)107と並列に転送MOSトランジスタ(Tx2)108を介して画素メモリ(Cm)109が接続されている。また破線で囲まれた部分は1つの画素を構成しており、撮像装置内にはm行×n列の画素が配置されている。

【0020】

上記転送MOSトランジスタ(Tx1)102のゲートは、横方向に延長して配置される第1の行選択線(垂直走査線)ptx1に接続される。同じ行に配置された他の画素セルPixelの同様の転送MOSトランジスタ102のゲートも、上記第1の行選択線Ptx1に共通に接続される。

【0021】

上記リセットMOSトランジスタ103のゲートは、横方向に延長して配置される第2の行選択線(垂直走査線)presに接続される。同じ行に配置された他の画素セルPixelの同様のリセットMOSトランジスタ103のゲートも、上記第2の行選択線presに共通に接続される。

【0022】

上記選択MOSトランジスタ105のゲートは、横方向に延長して配置される第3の行選択線(垂直走査線)pselに接続される。同じ行に配置された他の画素セルPixelの同様の選択MOSトランジスタ105のゲートも、上記第3の行選択線pselに共通に接続される。

【0023】

上記転送MOSトランジスタ(Tx2)108のゲートは、横方向に延長して配置される第4の行選択線(垂直走査線)ptx2に接続される。同じ行に配置された他の画素セルPixelの同様の転送MOSトランジスタ108のゲートも、上記第4の行選択線ptx2に共通に接続される。

【0024】

これら第1〜第4の行選択線ptx1、 pres、 psel、ptx2は、不図示の垂直シフトレジスタに接続され信号電圧が供給される。また、残りの行においても同様の構成の画素セルPixelと、行選択線が設けられ、同様に不図示の垂直シフトレジスタにより形成された信号電圧が順次供給されることで、全画素信号を読み出すことが可能な構成となっている。

【0025】

図3は上記図1のCMOS型撮像装置で残像効果を出す場合と出さない場合の制御を行うタイミングチャートであり、1行目の行選択線 Pres_1、Ptx1_1、Ptx2_1パルス 2行目の行選択線 Pres_2、Ptx1_2、Ptx2_2パルス のタイミング及び、1、2行目における各画素のリセット直後の信号を後段のメモリに転送するパルス(N読み)タイミングと光電荷信号を後段の別のメモリに転送するパルス(S読み)タイミングを示している。φPHは水平シフトレジスタパルスであり、このパルスにより一行のすべての画素信号(n列分)を更に後段の処理回路(不図示)に送る。

【0026】

ここでは1、2行目のパルス信号しか示していないが、実際にはm行分のパルス信号が供給される。

【0027】

Psel信号は、行毎に出力されるだけなのでここでは省略している。また、各タイミングにおける1行目のフォトダイオード(PD)101の電荷及び、フローティングディフュージョン(Cfd)107と画素メモリ(Cm)109の電位をそれぞれVcfd、Vcmとして示している。

【0028】

図2は、本発明第1の実施例における撮像素子の構成図であり、ここでは画素が3行×3列に配置された様子を示している。

【0029】

各行で共通の駆動パルスは垂直走査回路から出力され、各列の垂直出力線信号は垂直走査回路内の後処理回路に入力され、その後の信号は水平走査回路によって後段の回路に転送される。

【0030】

図3(a)で残像効果を出す場合の動作を説明する。

【0031】

まず、T1のタイミングでPres_1、Pres_2、Ptx1_1、Ptx2_1、Ptx1_2、Ptx2_2パルスを“L”→“H”→“L”とすることで、Tres、Tx1、Tx2をオン/オフして全画素分のPD101、Cm109、Cfd107をそれぞれ電源VDDに接続/切り離しすることでリセットする。そのときPD101の電荷はゼロで、Vcfd、Vcm電位はVDDに応じた所定電位である。

【0032】

その直後に1行目全列画素が選択され(不図示)、1行目のN読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段のメモリに記憶する(N読み)。

【0033】

その後T2のタイミングでPtx1_1、Ptx2_1パルスを“L”→“H”→“L”とすることで、1行目のTx1、Tx2をオン/オフして1行目全列分のPD101で発生した電荷Qをフローティングディフュージョン(Cfd)107と画素メモリ(Cm)109に完全転送する。

【0034】

このときの電荷Qはフローティングディフュージョン容量Cfdと画素メモリ容量Cmで容量分割されることで、Vcfd電位とVcm電位となる。但し、ここではPD101はリセットされて間もないのでほとんど電荷蓄積されておらず、Qpd、Vcfd、Vcmはほぼリセットされたときと等価であり、その様子を図2のQpd、Vcfd、Vcmで示している。

【0035】

1行目のPD101の電荷が完全転送された直後から、1行目のPD101は次の蓄積が開始されている。

【0036】

その直後S読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段の別メモリに記憶する(S読み)。

【0037】

その後、後段の処理回路(不図示)でS読み信号−N読み信号の演算を行いながら、水平シフトレジスタパルスφPHにより一行のすべての画素信号(n列分)を更に後段の処理回路(不図示)に送る。

【0038】

1行目の信号転送が終了すると2行目が選択され(不図示)、2行目のN読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段のメモリに記憶する(N読み)。その後Ptx1_2、Ptx2_2パルスを“L”→“H”→“L”とすることで、2行目のTx1、Tx2をオン/オフして2行目全列分のPD101で発生した電荷Qをフローティングディフュージョン(Cfd)107と画素メモリ(Cm)109に完全転送する。

【0039】

2行目のPD101の電荷が完全転送された直後から、2行目のPD101は次の蓄積が開始されている。

【0040】

その直後S読みパルスを“L”→“H”→“L”とすることで、2行目全列分のVcfdを垂直出力線(Vline)106を介して後段の別メモリに記憶する(S読み)。

【0041】

その後、後段の処理回路(不図示)でS読み信号−N読み信号の演算を行いながら、水平シフトレジスタパルスφPHにより一行のすべての画素信号(n列分)を更に後段の処理回路(不図示)に送る。

【0042】

この動作を1行目からm行目まで繰り返すことで、撮像素子全画素の信号を読みだす。図2では2本の斜線でその動作を省略しており、ここまでが1stフレームの動作である。

【0043】

次に、T3のタイミングでPres_1パルスのみを“L”→“H”→“L”とすることで、1行目全列分のTresをオン/オフしてCfd107を電源VDDに接続/切り離しすることでリセットする。そのときPD101は蓄積が継続され、Cm109はリセットされていない。従って、Vcfd電位はVDDに応じた所定電位になるが、Vcmは前フレームの電位がそのまま残っている。但し、前フレームでVcmはほとんどリセット状態であったのでここでもリセット状態とほぼ等価の状態である。

【0044】

その直後にN読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段のメモリに記憶する(N読み)。

【0045】

その後T4のタイミングでPtx1_1、Ptx2_1パルスを“L”→“H”→“L”とすることで、1行目全列分のTx1、Tx2をオン/オフしてPD101で発生した電荷Q1をフローティングディフュージョン(Cfd)107と画素メモリ(Cm)109に完全転送する。

【0046】

このときCm109はリセットされていないので、Cfd、Cm上では前フレームの電荷Qの一部 Q×(Cm/(Cfd+Cm)) と新たに蓄積された電荷Q1が足し合わされた電荷が容量分割された電位で収束し、その様子を図2のVcfd、Vcmで示している。但し、前フレームでPD101の電荷Qはほとんどリセット状態であったのでCm109もリセット状態とほぼ等価の状態であり、新たに蓄積された電荷Q1がそのままCfdとCmに振り分けられることになる。

【0047】

1行目のPD101の電荷が完全転送された直後から、1行目のPD101は次の蓄積が開始されている。

【0048】

その直後S読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段の別メモリに記憶する(S読み)。

【0049】

その後の処理は、1stフレームと同様に後段の処理回路(不図示)でS読み信号−N読み信号の演算を行いながら、水平シフトレジスタパルスφPHにより一行のすべての画素信号(n列分)を更に後段の処理回路(不図示)に送る。

【0050】

1行目信号の水平転送中にPres_2パルスのみを“L”→“H”→“L”とすることで、2行目全列分のTresをオン/オフしてCfd107を電源VDDに接続/切り離しすることでリセットし、1行目信号の水平転送が終了すると2行目が選択され(不図示)、1行目と同様に、N読み、PD電荷完全転送、S読み、水平転送の一連の動作を行う。以降の説明は省略するが、1stフレームと同様の動作が行われるものとする。図2では2本の斜線でその動作を省略しており、ここまでが2ndフレームの動作である。

【0051】

次に、T5のタイミングでPres_1パルスのみを“L”→“H”→“L”とすることで、1行目全列分のTresをオン/オフしてCfd107を電源VDDに接続/切り離しすることでリセットする。そのときPD101は蓄積が継続され、Cm109はリセットされていない。従って、Vcfd電位はVDDに応じた所定電位になるが、Vcmは前フレームの電位がそのまま残っている。

【0052】

その直後にN読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段のメモリに記憶する(N読み)。

【0053】

その後T6のタイミングでPtx1_1、Ptx2_1パルスを“L”→“H”→“L”とすることで、1行目全列分のTx1、Tx2をオン/オフしてPD101で発生した電荷Q2をフローティングディフュージョン(Cfd)107と画素メモリ(Cm)109に完全転送する。

【0054】

このときCm109はリセットされていないので、Cfd、Cm上では前フレームの電荷Q1の一部 Q1×(Cm/(Cfd+Cm)) と新たに蓄積された電荷Q2が足し合わされた電荷が容量分割された電位で収束し、その様子を図2のVcfd、Vcmで示している。

【0055】

1行目のPD101の電荷が完全転送された直後から、1行目のPD101は次の蓄積が開始されている。

【0056】

その直後S読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段の別メモリに記憶する(S読み)。

【0057】

その後の処理は、1stフレームと同様に後段の処理回路(不図示)でS読み信号−N読み信号の演算を行いながら、水平シフトレジスタパルスφPHにより一行のすべての画素信号(n列分)を更に後段の処理回路(不図示)に送る。

【0058】

1行目信号の水平転送が終了すると2行目が選択され(不図示)、2ndフレームと同様の動作が行われる。図2では2本の斜線でその動作を省略しており、ここまでが3rdフレームの動作である。

【0059】

以降、これら動作を繰り返せば、T6のタイミング以降で、

前フレームの総合電荷×(Cm/(Cfd+Cm))

が必ず加算されることになる。このことはつまり残像効果を出していることになる。

【0060】

具体的には2ndフレーム目以降でCm109をリセットしていないことでこの効果を出している。

【0061】

図3(b)は上記図1のCMOS型撮像装置で残像効果を出さない制御を行うタイミングチャートであり、図2との違いは、2ndフレーム目以降でPres_1、Pres_2パルスを“L”→“H”→“L”とするタイミングで、Ptx2_1、Ptx2_2を“L”→“H”→“L”とすることで、Cm109、Cfd107をそれぞれリセットしている。そのため図2のように残像効果は得られず、Vfdはフレーム毎にPD101で蓄積された電荷のみに応じた電位となる。

【0062】

図1の画素構成で、図2の駆動方法では残像効果を得られ、図3(b)の駆動方法では残像効果を得られないことから、後述するように撮像装置の用途に応じて(例えば静止画モードや動画モード)使い分けることが可能である。

【0063】

ここで、図2の駆動方法で被写体構図が固定の場合は、Vfdは前フレームの電荷の影響を受け不自然な変化をし続けるが、Cfd > Cmの関係にすることでVfdの不自然な変化を極力防止できる。

【0064】

次にデジタルカメラなどの撮像装置における動作についてについて説明する。

【0065】

図7はデジタルカメラなどの撮像装置の構成を示すブロック図である。同図において701は撮像素子でありCCDまたはCMOSセンサが使用される。

【0066】

702は撮像素子からの信号を増幅しAD変換等を行う信号処理回路AFEであり後述するタイミング発生回路704からタイミングなどを受け取りそれに従って動作する。703はDSP(DigitalSignalProseccer)であり、信号処理回路702からのデータに対して各種補正処理等を行なう。

【0067】

またDSP703では、ROM706、RAM707等各種メモリの制御、記録媒体708への映像データの書き込み処理が行なわれる。

【0068】

704は、撮像素子701、信号処理回路702、DSP703にクロック信号や制御信号を供給するタイミング発生回路であるTG(TimingGenerator)であり、CPU705により制御される。

【0069】

705はDSP703、TG704の制御、及び測光・測距など不図示の各部を使ったカメラ機能の制御を行なうCPUである。709〜711の各スイッチが接続され、それぞれの状態に応じた処理を実行する。

【0070】

706はカメラの制御プログラムや補正テーブルなどを記憶するROMである。707はDSP703で処理される映像データや補正データを一時的に記憶するRAMである。RAM707はROM706より高速のアクセスが可能である。

【0071】

708は撮影された映像を保存するコンパクトフラッシュ(登録商標)カード(以下CF)等の記録媒体であり、不図示のコネクタを介してカメラと接続される。

【0072】

709はカメラを起動させるための電源スイッチ、710は測光処理、測距処理、被写体映像をリアルタイムに外部に表示する所謂EVF動作等の撮影準備動作開始を指示するシャッタースイッチSW1、711は不図示のミラー及びシャッターを駆動し、撮像素子701から読み出した信号を信号処理回路702、DSP703を介して記録媒体708に書き込む一連の撮像動作の開始を指示するシャッタースイッチSW2である。712はカメラの撮影モード(例えば連続撮影(動画)モード、単写モード、ストロボ発光モードなど)を指示するためのモードダイアルスイッチ、713は被写体までの距離を測定するための測距回路、714は被写体輝度を測定するための測光回路、715は撮影した映像を外部に表示するための表示装置である。

【0073】

図8は図1の撮像素子を用いた図7の構成の撮像装置の動作を説明するフローチャートである。

【0074】

まずステップ801で709電源スイッチがONかどうかを判定し、OFFであればステップ801を繰り返す。ONであればステップ802で撮影準備動作を開始させるスイッチ710SW1がONかどうかを判定する。OFFであればステップ801へ戻り、ONであればステップ803へ移行する。

【0075】

ステップ803では、測距回路713により被写体までの距離を測定するとともに、測光回路714で被写体の輝度を測定する。続くステップ804で不図示のメカシャッタ開き撮像素子に光を入射させた状態にする。

【0076】

その後ステップ805では、ステップ803の測光結果が被写体輝度があらかじめ設定された輝度より暗い場合は、星を含む夜景撮影であると判断しステップ806へ移行し図2で説明した画素メモリをリセットせず残像効果を出す駆動方法(第2のモード)で蓄積及び読み出しを行う。ステップ805で被写体輝度が明るい場合は夜景以外の被写体の撮影と判断しステップ807に移行し、図3(b)で説明した画素メモリをリセットし残像効果を出さない駆動方法(第1のモード)で蓄積及び読み出しを行う。

【0077】

次のステップ808で外部表示装置715への映像表示を行い、ステップ809では静止画撮影を開始させるためのスイッチ711SW2がONされているかどうかを判定し、OFFであれば、ステップ802へ戻り次のフレームの動作に移る。つまり、ステップ802〜ステップ809までの動作で、撮影と表示を連続的に行う所謂EVF動作を行っている。

【0078】

ステップ809でスイッチ711SW2がONと判定されるとステップ810に移行し、前記ステップ803で得られた測光、測距情報を基に静止画として最適な露出やピント位置で、撮像素子の蓄積を図3(b)で説明した画素メモリをリセットし残像効果を出さない駆動方法(第1のモード)で行う。ここでは静止画撮影なので、まずメカシャッタを一旦閉じた上で図3(b)の駆動を開始し、1stフレーム目の動作を行い、測光情報を基に全行の蓄積期間中に不図示のメカシャッタを開き、ステップ811で所定の露光量に達したところで不図示のメカシャッタを閉じる。

【0079】

その後ステップ812で図3(b)の2フレーム目の動作(第1のモード)を行うことで全画素読み出しを行い、ステップ813で外部表示装置715への映像表示を行い、ステップ814で静止画映像信号を708記録媒体に記録して終了する。

【0080】

つまりステップ802〜809では、被写体(周囲)輝度が暗い場合は星を含む夜景撮影と判断し、このとき所謂EVF動作が行われていたら、撮影構図を変化させたときに主被写体を見失う可能性があるものとして、残像効果を出す駆動方法(第2のモード)で蓄積読み出しを行うようにしているため、主被写体の追跡が容易となる。

【0081】

また、被写体(周囲)輝度が明るい場合や静止画撮影の場合は残像効果を出さないように駆動する(第1のモード)ため前フレームの影響を受けない自然な画像を得ることができる。

【0082】

ここで、ステップ809でスイッチ711SW2を静止画撮影を開始させるためのスイッチとしているが、スイッチ711は動画記録を開始させるスイッチであるとしても良い。つまり所謂EVF動作の時は被写体状況(輝度)によって残像効果を出したり出さなかったりするが、動画記録時には残像効果を出さない駆動方法(第1のモード)で蓄積読み出しを行うようにすることで、記録された映像は前フレームの影響を受けない自然な映像にすることができる。

【0083】

また、残像効果を持たせる駆動を所謂EVF動作中にや、被写体輝度が暗い場合のみに限定することで、通常は残像効果の無い自然な映像を提供することが可能である。

【0084】

[実施例2]

図4は本発明の撮像装置の第2の実施形態を示した図であり、CMOS型固体撮像装置の画素セルPixelの構成例を示す回路図である。

【0085】

同図の401〜407までは図1の101〜107と同じであるので説明を省略する。

【0086】

フローティングディフュージョン(Cfd)407と並列に転送MOSトランジスタ(Tx2、Tx3、Tx4)408、410、412を介して画素メモリ(Cm2、Cm3、Cm4)409、411、413が接続されており、各画素メモリの容量は Cm2 < Cm3 < Cm4 である。

【0087】

また全画素共通のSI_Data信号は画素メモリを選択するためのデータで、selector417に入力され、その出力tx2、tx3、tx4と転送信号ptx2がANDゲート414、415、416に入力されることで画素メモリCm2〜Cm4が選択的に接続される。

【0088】

第1〜第4の行選択線ptx1、 pres、psel、ptx2は、図1と同様の構成で信号が入力され、図3(a)と同様の信号が入力される。

【0089】

図4の構成においても、図2の駆動方法では残像効果を得られ、図3(b)の駆動方法では残像効果を得られないことから、後述するように撮像装置の用途に応じて(例えば静止画モードや動画モード)使い分けることが可能である。

【0090】

また、画素メモリCm2、Cm3、Cm4のどれを選択するかで、残像量をコントロールすることができるため、例えば製造時のメモリ容量のばらつきを抑え一定の残像効果を得るためや、状況に応じて残像効果を変化させたりすることが可能である。

【0091】

[実施例3]

図5は本発明の撮像装置の第3の実施形態を示した図であり、CMOS型固体撮像装置の画素セルPixelの構成例を示す回路図である。

【0092】

光信号電荷を発生するフォトダイオード(PD)501は、この例ではアノード側が接地されている。フォトダイオード(PD)501のカソード側は、転送MOSトランジスタ(Tx1)502、(Tx2)508を介してフローティングディフュージョン(Cfd)507および増幅MOSトランジスタ(Tsf)504のゲートに接続されている。また、上記フローティングディフュージョン(Cfd)507および増幅MOSトランジスタ(Tsf)504のゲート電位は、リセットMOSトランジスタ(Tres1)503により共通電源(VDD)とショートされることで固定電位にリセットされる。また、上記フォトダイオード(PD)501は、リセットMOSトランジスタ(Tres2)510により共通電源(VDD)とショートされることで蓄積電荷をリセットされる。さらに、上記増幅MOSトランジスタ(Tsf)504は、ドレインが電源VDDに接続され、ソースが選択MOSトランジスタ(Tsel)505のドレインに接続されている。また、選択MOSトランジスタ(Tsel)505のソースは、同一列で共通な垂直出力線(Vline)506に接続されることで画素出力される。更に、転送MOSトランジスタ(Tx1)502、(Tx2)508の間に画素メモリ(Cm)509が接続されていて、転送MOSトランジスタ(Tx2)508をオンさせることで、画素メモリ(Cm)509が上記フローティングディフュージョン(Cfd)507と並列に接続できるようになっている。また破線で囲まれた部分は1つの画素を構成しており、撮像装置内にはm行×n列の画素が配置されている。

【0093】

つまり図1との差は、転送MOSトランジスタ(Tx2)508、画素メモリ(Cm)509の配置の違いと、フォトダイオード(PD)501のカソード側に専用のリセットMOSトランジスタ(Tres2)510及びその制御線Pres2を配置している点である。

【0094】

図6は上記図5のCMOS型撮像装置で残像効果を出す場合と残像効果を出さない場合(Ptx2破線)の制御を行うタイミングチャートである。

【0095】

図3との差は、図5でフォトダイオード(PD)501のカソード側に専用のリセットMOSトランジスタ(Tres2)510及びその制御線Pres2を配置しているので、Pres2パルスを追加している点であり、その他のパルスは図3と同じ駆動方法なので説明を省略する。

【0096】

Pres2パルスは1stフレームのみPres1_1、Pres1_2と同じタイミングで“L”→“H”→“L”とすることで、PD501、Cm509、Cfd507をそれぞれリセットさせている。

【0097】

このようなタイミングで駆動することで、図1の構成と同様に残像効果を出したり残像効果を出さなかったりすることができる。

【符号の説明】

【0098】

701:撮像素子

702:AFE(アナログフロントエンド)

703:DSP(DigitalSignalProseccer)

704:タイミング発生回路

705:CPU

506:ROM

707:RAM

708:記録媒体

709:電源スイッチ

510:シャッタースイッチSW1

711:シャッタースイッチSW2

712:モードダイアル

713:測距回路

714:測光回路

715:表示装置

101、401、501:フォトダイオード

102、103、104、105、108、402、403、404、405、408、410、412、502、503、404、505、508、510:MOSトランジスタ

107、407、507:フローティングディフュージョン

109、409、411、413、509:画素メモリ

506:垂直出力線

【技術分野】

【0001】

本発明は画像を生成するための撮像装置の改良に関するもので、特に連続して生成される画像に対して残像効果を付加することが可能な撮像装置に関するものである。

【背景技術】

【0002】

画像を生成するための撮像装置の機能として、1シーンのみを撮像する静止画モードと連続した複数のシーンを撮像する動画モードがあることは良く知られている。またこれら撮像された静止画や動画を表示、記録することが可能な撮像装置も種々製品化されている。

【0003】

ところで電子シャッタを用いて高速移動する被写体を動画モードで撮像し表示した場合、動画像としては不自然な映像になるという問題がある。その対策として特許文献1では、1フィールド(1フレーム)の間に、感光部に蓄積された電荷の掃捨処理と、転送処理とを所定の時間の中で交互に繰り返し且つ、電荷の掃捨量を制御することにより、残像効果を持ち自然で連続的な解像度の高い画像を生成する提案がされている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001-197373号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

一般的にこれらの撮像装置には、被写体の構図を決めるために動画モードで撮像された画像を表示装置で表示する機能も有するが、人ごみなど複数の類似した被写体があったり、周囲輝度が暗い場合などに急激な構図変化をさせると、主被写体を見失ってしまうという問題を有している。

【0006】

このことを図9を用いて説明する。

【0007】

図9(a)、(b)は夜空の星を撮像した際、同図(a)から(b)に構図変化させた様子を示している。このように星を主被写体にした場合、周囲に類似の星が多くまた周囲が暗いために目的の星を見失うことが多い。

【0008】

このような構図変化の際に主被写体を見失わないように、表示させる動画像に残像効果を持たせ主被写体を追跡しやすいようにすることが考えられる。

【0009】

図9(c)はこのことを説明する図で、同図内に主被写体の星を太線で示し残像を線で表現している。図9(a)から(c)に構図変化させたときにも、残像があることで主被写体の星が追跡しやすいことがわかる。

【0010】

残像効果を持たせる技術としては、前述の特開2001-197373号があるが、この技術は1フレーム内で残像効果を持たせる技術であり、高速移動する被写体を自然に表示する効果はあるものの、数フレームにわたって残像効果を得ることができないため、所望の追跡効果を得ることはできない。

【0011】

また、撮像された連続画像をメモリに記憶して後段の画像処理で残像効果を得ることも考えられるが、処理回路規模が大きくなることが懸念される。

【課題を解決するための手段】

【0012】

本発明は、上記課題を鑑みて提案されるものであり、残像効果を持たせる手段として、

光を受光して光電荷を生成し蓄積するフォトダイオードと、前記フォトダイオードに接続され前記光電荷を転送する転送トランジスタと、前記転送トランジスタに接続された前記光電荷を蓄積する蓄積容量とを備え、

前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを実行する第1の駆動モードと、

前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを非実行する第2の駆動モードとを有するようにする。

【0013】

また、前記撮像装置は、前記フォトダイオードが光電荷を蓄積した信号を読み出すとともに、読み出された信号を画像として表示する手段と、

前記信号のうち1フレームのみを読み出し表示する静止画撮影モードと

前記信号の読み出しと表示を連続した複数のフレームで繰り返す動画撮影モードとを有し

前記動画撮影モードの時に前記第2の駆動モードで駆動するようにする。

【発明の効果】

【0014】

本発明により、表示させる動画像に残像効果を持たせ主被写体を追跡しやすいようにすることが出来るため、被写体の構図を決めるための所謂EVF動作中に人ごみなど複数の類似した被写体があったり、周囲輝度が暗い場合などに急激な構図変化をしたときであっても、主被写体を見失ってしまうということを防止することが可能となる。

【0015】

特に夜空の星を撮像した際でも、目的の星を見失うことを防止することが可能となる。

【0016】

また、残像効果を持たせる駆動を所謂EVF動作中にや、被写体輝度が暗い場合のみに限定することで、通常は残像効果の無い自然な映像を提供することが可能である。

【図面の簡単な説明】

【0017】

【図1】本発明第1の実施例における画素構成図

【図2】本発明第1の実施例における撮像素子の構成図

【図3(a)】本発明第1、第2の実施例第2のモードを説明するタイミングチャート(その1)

【図3(b)】本発明第1、第2の実施例第2のモードを説明するタイミングチャート(その2)

【図4】本発明第2の実施例における画素構成図

【図5】本発明第3の実施例における画素構成図

【図6】本発明第3の実施例を説明するタイミングチャート

【図7】本発明第1の実施例における撮像装置の全体構成図

【図8】本発明第1の実施例における撮像装置の動作を説明するフローチャート

【図9】従来例を説明する図

【発明を実施するための形態】

【0018】

[実施例1]

図1は本発明の撮像装置の実施形態を示した図であり、CMOS型固体撮像装置の画素セルPixelの構成例を示す回路図である。

【0019】

光信号電荷を発生するフォトダイオード(PD)101は、この例ではアノード側が接地されている。フォトダイオード(PD)101のカソード側は、転送MOSトランジスタ(Tx1)102を介してフローティングディフュージョン(Cfd)107および増幅MOSトランジスタ(Tsf)104のゲートに接続されている。また、上記フローティングディフュージョン(Cfd)107および増幅MOSトランジスタ(Tsf)104のゲート電位は、リセットMOSトランジスタ(Tres)103により共通電源(VDD)とショートされることで固定電位にリセットされる。さらに、上記増幅MOSトランジスタ(Tsf)104は、ドレインが電源VDDに接続され、ソースが選択MOSトランジスタ(Tsel)105のドレインに接続されている。また、選択MOSトランジスタ(Tsel)105のソースは、同一列で共通な垂直出力線(Vline)106に接続されることで画素出力される。更に、上記フローティングディフュージョン(Cfd)107と並列に転送MOSトランジスタ(Tx2)108を介して画素メモリ(Cm)109が接続されている。また破線で囲まれた部分は1つの画素を構成しており、撮像装置内にはm行×n列の画素が配置されている。

【0020】

上記転送MOSトランジスタ(Tx1)102のゲートは、横方向に延長して配置される第1の行選択線(垂直走査線)ptx1に接続される。同じ行に配置された他の画素セルPixelの同様の転送MOSトランジスタ102のゲートも、上記第1の行選択線Ptx1に共通に接続される。

【0021】

上記リセットMOSトランジスタ103のゲートは、横方向に延長して配置される第2の行選択線(垂直走査線)presに接続される。同じ行に配置された他の画素セルPixelの同様のリセットMOSトランジスタ103のゲートも、上記第2の行選択線presに共通に接続される。

【0022】

上記選択MOSトランジスタ105のゲートは、横方向に延長して配置される第3の行選択線(垂直走査線)pselに接続される。同じ行に配置された他の画素セルPixelの同様の選択MOSトランジスタ105のゲートも、上記第3の行選択線pselに共通に接続される。

【0023】

上記転送MOSトランジスタ(Tx2)108のゲートは、横方向に延長して配置される第4の行選択線(垂直走査線)ptx2に接続される。同じ行に配置された他の画素セルPixelの同様の転送MOSトランジスタ108のゲートも、上記第4の行選択線ptx2に共通に接続される。

【0024】

これら第1〜第4の行選択線ptx1、 pres、 psel、ptx2は、不図示の垂直シフトレジスタに接続され信号電圧が供給される。また、残りの行においても同様の構成の画素セルPixelと、行選択線が設けられ、同様に不図示の垂直シフトレジスタにより形成された信号電圧が順次供給されることで、全画素信号を読み出すことが可能な構成となっている。

【0025】

図3は上記図1のCMOS型撮像装置で残像効果を出す場合と出さない場合の制御を行うタイミングチャートであり、1行目の行選択線 Pres_1、Ptx1_1、Ptx2_1パルス 2行目の行選択線 Pres_2、Ptx1_2、Ptx2_2パルス のタイミング及び、1、2行目における各画素のリセット直後の信号を後段のメモリに転送するパルス(N読み)タイミングと光電荷信号を後段の別のメモリに転送するパルス(S読み)タイミングを示している。φPHは水平シフトレジスタパルスであり、このパルスにより一行のすべての画素信号(n列分)を更に後段の処理回路(不図示)に送る。

【0026】

ここでは1、2行目のパルス信号しか示していないが、実際にはm行分のパルス信号が供給される。

【0027】

Psel信号は、行毎に出力されるだけなのでここでは省略している。また、各タイミングにおける1行目のフォトダイオード(PD)101の電荷及び、フローティングディフュージョン(Cfd)107と画素メモリ(Cm)109の電位をそれぞれVcfd、Vcmとして示している。

【0028】

図2は、本発明第1の実施例における撮像素子の構成図であり、ここでは画素が3行×3列に配置された様子を示している。

【0029】

各行で共通の駆動パルスは垂直走査回路から出力され、各列の垂直出力線信号は垂直走査回路内の後処理回路に入力され、その後の信号は水平走査回路によって後段の回路に転送される。

【0030】

図3(a)で残像効果を出す場合の動作を説明する。

【0031】

まず、T1のタイミングでPres_1、Pres_2、Ptx1_1、Ptx2_1、Ptx1_2、Ptx2_2パルスを“L”→“H”→“L”とすることで、Tres、Tx1、Tx2をオン/オフして全画素分のPD101、Cm109、Cfd107をそれぞれ電源VDDに接続/切り離しすることでリセットする。そのときPD101の電荷はゼロで、Vcfd、Vcm電位はVDDに応じた所定電位である。

【0032】

その直後に1行目全列画素が選択され(不図示)、1行目のN読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段のメモリに記憶する(N読み)。

【0033】

その後T2のタイミングでPtx1_1、Ptx2_1パルスを“L”→“H”→“L”とすることで、1行目のTx1、Tx2をオン/オフして1行目全列分のPD101で発生した電荷Qをフローティングディフュージョン(Cfd)107と画素メモリ(Cm)109に完全転送する。

【0034】

このときの電荷Qはフローティングディフュージョン容量Cfdと画素メモリ容量Cmで容量分割されることで、Vcfd電位とVcm電位となる。但し、ここではPD101はリセットされて間もないのでほとんど電荷蓄積されておらず、Qpd、Vcfd、Vcmはほぼリセットされたときと等価であり、その様子を図2のQpd、Vcfd、Vcmで示している。

【0035】

1行目のPD101の電荷が完全転送された直後から、1行目のPD101は次の蓄積が開始されている。

【0036】

その直後S読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段の別メモリに記憶する(S読み)。

【0037】

その後、後段の処理回路(不図示)でS読み信号−N読み信号の演算を行いながら、水平シフトレジスタパルスφPHにより一行のすべての画素信号(n列分)を更に後段の処理回路(不図示)に送る。

【0038】

1行目の信号転送が終了すると2行目が選択され(不図示)、2行目のN読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段のメモリに記憶する(N読み)。その後Ptx1_2、Ptx2_2パルスを“L”→“H”→“L”とすることで、2行目のTx1、Tx2をオン/オフして2行目全列分のPD101で発生した電荷Qをフローティングディフュージョン(Cfd)107と画素メモリ(Cm)109に完全転送する。

【0039】

2行目のPD101の電荷が完全転送された直後から、2行目のPD101は次の蓄積が開始されている。

【0040】

その直後S読みパルスを“L”→“H”→“L”とすることで、2行目全列分のVcfdを垂直出力線(Vline)106を介して後段の別メモリに記憶する(S読み)。

【0041】

その後、後段の処理回路(不図示)でS読み信号−N読み信号の演算を行いながら、水平シフトレジスタパルスφPHにより一行のすべての画素信号(n列分)を更に後段の処理回路(不図示)に送る。

【0042】

この動作を1行目からm行目まで繰り返すことで、撮像素子全画素の信号を読みだす。図2では2本の斜線でその動作を省略しており、ここまでが1stフレームの動作である。

【0043】

次に、T3のタイミングでPres_1パルスのみを“L”→“H”→“L”とすることで、1行目全列分のTresをオン/オフしてCfd107を電源VDDに接続/切り離しすることでリセットする。そのときPD101は蓄積が継続され、Cm109はリセットされていない。従って、Vcfd電位はVDDに応じた所定電位になるが、Vcmは前フレームの電位がそのまま残っている。但し、前フレームでVcmはほとんどリセット状態であったのでここでもリセット状態とほぼ等価の状態である。

【0044】

その直後にN読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段のメモリに記憶する(N読み)。

【0045】

その後T4のタイミングでPtx1_1、Ptx2_1パルスを“L”→“H”→“L”とすることで、1行目全列分のTx1、Tx2をオン/オフしてPD101で発生した電荷Q1をフローティングディフュージョン(Cfd)107と画素メモリ(Cm)109に完全転送する。

【0046】

このときCm109はリセットされていないので、Cfd、Cm上では前フレームの電荷Qの一部 Q×(Cm/(Cfd+Cm)) と新たに蓄積された電荷Q1が足し合わされた電荷が容量分割された電位で収束し、その様子を図2のVcfd、Vcmで示している。但し、前フレームでPD101の電荷Qはほとんどリセット状態であったのでCm109もリセット状態とほぼ等価の状態であり、新たに蓄積された電荷Q1がそのままCfdとCmに振り分けられることになる。

【0047】

1行目のPD101の電荷が完全転送された直後から、1行目のPD101は次の蓄積が開始されている。

【0048】

その直後S読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段の別メモリに記憶する(S読み)。

【0049】

その後の処理は、1stフレームと同様に後段の処理回路(不図示)でS読み信号−N読み信号の演算を行いながら、水平シフトレジスタパルスφPHにより一行のすべての画素信号(n列分)を更に後段の処理回路(不図示)に送る。

【0050】

1行目信号の水平転送中にPres_2パルスのみを“L”→“H”→“L”とすることで、2行目全列分のTresをオン/オフしてCfd107を電源VDDに接続/切り離しすることでリセットし、1行目信号の水平転送が終了すると2行目が選択され(不図示)、1行目と同様に、N読み、PD電荷完全転送、S読み、水平転送の一連の動作を行う。以降の説明は省略するが、1stフレームと同様の動作が行われるものとする。図2では2本の斜線でその動作を省略しており、ここまでが2ndフレームの動作である。

【0051】

次に、T5のタイミングでPres_1パルスのみを“L”→“H”→“L”とすることで、1行目全列分のTresをオン/オフしてCfd107を電源VDDに接続/切り離しすることでリセットする。そのときPD101は蓄積が継続され、Cm109はリセットされていない。従って、Vcfd電位はVDDに応じた所定電位になるが、Vcmは前フレームの電位がそのまま残っている。

【0052】

その直後にN読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段のメモリに記憶する(N読み)。

【0053】

その後T6のタイミングでPtx1_1、Ptx2_1パルスを“L”→“H”→“L”とすることで、1行目全列分のTx1、Tx2をオン/オフしてPD101で発生した電荷Q2をフローティングディフュージョン(Cfd)107と画素メモリ(Cm)109に完全転送する。

【0054】

このときCm109はリセットされていないので、Cfd、Cm上では前フレームの電荷Q1の一部 Q1×(Cm/(Cfd+Cm)) と新たに蓄積された電荷Q2が足し合わされた電荷が容量分割された電位で収束し、その様子を図2のVcfd、Vcmで示している。

【0055】

1行目のPD101の電荷が完全転送された直後から、1行目のPD101は次の蓄積が開始されている。

【0056】

その直後S読みパルスを“L”→“H”→“L”とすることで、1行目全列分のVcfdを垂直出力線(Vline)106を介して後段の別メモリに記憶する(S読み)。

【0057】

その後の処理は、1stフレームと同様に後段の処理回路(不図示)でS読み信号−N読み信号の演算を行いながら、水平シフトレジスタパルスφPHにより一行のすべての画素信号(n列分)を更に後段の処理回路(不図示)に送る。

【0058】

1行目信号の水平転送が終了すると2行目が選択され(不図示)、2ndフレームと同様の動作が行われる。図2では2本の斜線でその動作を省略しており、ここまでが3rdフレームの動作である。

【0059】

以降、これら動作を繰り返せば、T6のタイミング以降で、

前フレームの総合電荷×(Cm/(Cfd+Cm))

が必ず加算されることになる。このことはつまり残像効果を出していることになる。

【0060】

具体的には2ndフレーム目以降でCm109をリセットしていないことでこの効果を出している。

【0061】

図3(b)は上記図1のCMOS型撮像装置で残像効果を出さない制御を行うタイミングチャートであり、図2との違いは、2ndフレーム目以降でPres_1、Pres_2パルスを“L”→“H”→“L”とするタイミングで、Ptx2_1、Ptx2_2を“L”→“H”→“L”とすることで、Cm109、Cfd107をそれぞれリセットしている。そのため図2のように残像効果は得られず、Vfdはフレーム毎にPD101で蓄積された電荷のみに応じた電位となる。

【0062】

図1の画素構成で、図2の駆動方法では残像効果を得られ、図3(b)の駆動方法では残像効果を得られないことから、後述するように撮像装置の用途に応じて(例えば静止画モードや動画モード)使い分けることが可能である。

【0063】

ここで、図2の駆動方法で被写体構図が固定の場合は、Vfdは前フレームの電荷の影響を受け不自然な変化をし続けるが、Cfd > Cmの関係にすることでVfdの不自然な変化を極力防止できる。

【0064】

次にデジタルカメラなどの撮像装置における動作についてについて説明する。

【0065】

図7はデジタルカメラなどの撮像装置の構成を示すブロック図である。同図において701は撮像素子でありCCDまたはCMOSセンサが使用される。

【0066】

702は撮像素子からの信号を増幅しAD変換等を行う信号処理回路AFEであり後述するタイミング発生回路704からタイミングなどを受け取りそれに従って動作する。703はDSP(DigitalSignalProseccer)であり、信号処理回路702からのデータに対して各種補正処理等を行なう。

【0067】

またDSP703では、ROM706、RAM707等各種メモリの制御、記録媒体708への映像データの書き込み処理が行なわれる。

【0068】

704は、撮像素子701、信号処理回路702、DSP703にクロック信号や制御信号を供給するタイミング発生回路であるTG(TimingGenerator)であり、CPU705により制御される。

【0069】

705はDSP703、TG704の制御、及び測光・測距など不図示の各部を使ったカメラ機能の制御を行なうCPUである。709〜711の各スイッチが接続され、それぞれの状態に応じた処理を実行する。

【0070】

706はカメラの制御プログラムや補正テーブルなどを記憶するROMである。707はDSP703で処理される映像データや補正データを一時的に記憶するRAMである。RAM707はROM706より高速のアクセスが可能である。

【0071】

708は撮影された映像を保存するコンパクトフラッシュ(登録商標)カード(以下CF)等の記録媒体であり、不図示のコネクタを介してカメラと接続される。

【0072】

709はカメラを起動させるための電源スイッチ、710は測光処理、測距処理、被写体映像をリアルタイムに外部に表示する所謂EVF動作等の撮影準備動作開始を指示するシャッタースイッチSW1、711は不図示のミラー及びシャッターを駆動し、撮像素子701から読み出した信号を信号処理回路702、DSP703を介して記録媒体708に書き込む一連の撮像動作の開始を指示するシャッタースイッチSW2である。712はカメラの撮影モード(例えば連続撮影(動画)モード、単写モード、ストロボ発光モードなど)を指示するためのモードダイアルスイッチ、713は被写体までの距離を測定するための測距回路、714は被写体輝度を測定するための測光回路、715は撮影した映像を外部に表示するための表示装置である。

【0073】

図8は図1の撮像素子を用いた図7の構成の撮像装置の動作を説明するフローチャートである。

【0074】

まずステップ801で709電源スイッチがONかどうかを判定し、OFFであればステップ801を繰り返す。ONであればステップ802で撮影準備動作を開始させるスイッチ710SW1がONかどうかを判定する。OFFであればステップ801へ戻り、ONであればステップ803へ移行する。

【0075】

ステップ803では、測距回路713により被写体までの距離を測定するとともに、測光回路714で被写体の輝度を測定する。続くステップ804で不図示のメカシャッタ開き撮像素子に光を入射させた状態にする。

【0076】

その後ステップ805では、ステップ803の測光結果が被写体輝度があらかじめ設定された輝度より暗い場合は、星を含む夜景撮影であると判断しステップ806へ移行し図2で説明した画素メモリをリセットせず残像効果を出す駆動方法(第2のモード)で蓄積及び読み出しを行う。ステップ805で被写体輝度が明るい場合は夜景以外の被写体の撮影と判断しステップ807に移行し、図3(b)で説明した画素メモリをリセットし残像効果を出さない駆動方法(第1のモード)で蓄積及び読み出しを行う。

【0077】

次のステップ808で外部表示装置715への映像表示を行い、ステップ809では静止画撮影を開始させるためのスイッチ711SW2がONされているかどうかを判定し、OFFであれば、ステップ802へ戻り次のフレームの動作に移る。つまり、ステップ802〜ステップ809までの動作で、撮影と表示を連続的に行う所謂EVF動作を行っている。

【0078】

ステップ809でスイッチ711SW2がONと判定されるとステップ810に移行し、前記ステップ803で得られた測光、測距情報を基に静止画として最適な露出やピント位置で、撮像素子の蓄積を図3(b)で説明した画素メモリをリセットし残像効果を出さない駆動方法(第1のモード)で行う。ここでは静止画撮影なので、まずメカシャッタを一旦閉じた上で図3(b)の駆動を開始し、1stフレーム目の動作を行い、測光情報を基に全行の蓄積期間中に不図示のメカシャッタを開き、ステップ811で所定の露光量に達したところで不図示のメカシャッタを閉じる。

【0079】

その後ステップ812で図3(b)の2フレーム目の動作(第1のモード)を行うことで全画素読み出しを行い、ステップ813で外部表示装置715への映像表示を行い、ステップ814で静止画映像信号を708記録媒体に記録して終了する。

【0080】

つまりステップ802〜809では、被写体(周囲)輝度が暗い場合は星を含む夜景撮影と判断し、このとき所謂EVF動作が行われていたら、撮影構図を変化させたときに主被写体を見失う可能性があるものとして、残像効果を出す駆動方法(第2のモード)で蓄積読み出しを行うようにしているため、主被写体の追跡が容易となる。

【0081】

また、被写体(周囲)輝度が明るい場合や静止画撮影の場合は残像効果を出さないように駆動する(第1のモード)ため前フレームの影響を受けない自然な画像を得ることができる。

【0082】

ここで、ステップ809でスイッチ711SW2を静止画撮影を開始させるためのスイッチとしているが、スイッチ711は動画記録を開始させるスイッチであるとしても良い。つまり所謂EVF動作の時は被写体状況(輝度)によって残像効果を出したり出さなかったりするが、動画記録時には残像効果を出さない駆動方法(第1のモード)で蓄積読み出しを行うようにすることで、記録された映像は前フレームの影響を受けない自然な映像にすることができる。

【0083】

また、残像効果を持たせる駆動を所謂EVF動作中にや、被写体輝度が暗い場合のみに限定することで、通常は残像効果の無い自然な映像を提供することが可能である。

【0084】

[実施例2]

図4は本発明の撮像装置の第2の実施形態を示した図であり、CMOS型固体撮像装置の画素セルPixelの構成例を示す回路図である。

【0085】

同図の401〜407までは図1の101〜107と同じであるので説明を省略する。

【0086】

フローティングディフュージョン(Cfd)407と並列に転送MOSトランジスタ(Tx2、Tx3、Tx4)408、410、412を介して画素メモリ(Cm2、Cm3、Cm4)409、411、413が接続されており、各画素メモリの容量は Cm2 < Cm3 < Cm4 である。

【0087】

また全画素共通のSI_Data信号は画素メモリを選択するためのデータで、selector417に入力され、その出力tx2、tx3、tx4と転送信号ptx2がANDゲート414、415、416に入力されることで画素メモリCm2〜Cm4が選択的に接続される。

【0088】

第1〜第4の行選択線ptx1、 pres、psel、ptx2は、図1と同様の構成で信号が入力され、図3(a)と同様の信号が入力される。

【0089】

図4の構成においても、図2の駆動方法では残像効果を得られ、図3(b)の駆動方法では残像効果を得られないことから、後述するように撮像装置の用途に応じて(例えば静止画モードや動画モード)使い分けることが可能である。

【0090】

また、画素メモリCm2、Cm3、Cm4のどれを選択するかで、残像量をコントロールすることができるため、例えば製造時のメモリ容量のばらつきを抑え一定の残像効果を得るためや、状況に応じて残像効果を変化させたりすることが可能である。

【0091】

[実施例3]

図5は本発明の撮像装置の第3の実施形態を示した図であり、CMOS型固体撮像装置の画素セルPixelの構成例を示す回路図である。

【0092】

光信号電荷を発生するフォトダイオード(PD)501は、この例ではアノード側が接地されている。フォトダイオード(PD)501のカソード側は、転送MOSトランジスタ(Tx1)502、(Tx2)508を介してフローティングディフュージョン(Cfd)507および増幅MOSトランジスタ(Tsf)504のゲートに接続されている。また、上記フローティングディフュージョン(Cfd)507および増幅MOSトランジスタ(Tsf)504のゲート電位は、リセットMOSトランジスタ(Tres1)503により共通電源(VDD)とショートされることで固定電位にリセットされる。また、上記フォトダイオード(PD)501は、リセットMOSトランジスタ(Tres2)510により共通電源(VDD)とショートされることで蓄積電荷をリセットされる。さらに、上記増幅MOSトランジスタ(Tsf)504は、ドレインが電源VDDに接続され、ソースが選択MOSトランジスタ(Tsel)505のドレインに接続されている。また、選択MOSトランジスタ(Tsel)505のソースは、同一列で共通な垂直出力線(Vline)506に接続されることで画素出力される。更に、転送MOSトランジスタ(Tx1)502、(Tx2)508の間に画素メモリ(Cm)509が接続されていて、転送MOSトランジスタ(Tx2)508をオンさせることで、画素メモリ(Cm)509が上記フローティングディフュージョン(Cfd)507と並列に接続できるようになっている。また破線で囲まれた部分は1つの画素を構成しており、撮像装置内にはm行×n列の画素が配置されている。

【0093】

つまり図1との差は、転送MOSトランジスタ(Tx2)508、画素メモリ(Cm)509の配置の違いと、フォトダイオード(PD)501のカソード側に専用のリセットMOSトランジスタ(Tres2)510及びその制御線Pres2を配置している点である。

【0094】

図6は上記図5のCMOS型撮像装置で残像効果を出す場合と残像効果を出さない場合(Ptx2破線)の制御を行うタイミングチャートである。

【0095】

図3との差は、図5でフォトダイオード(PD)501のカソード側に専用のリセットMOSトランジスタ(Tres2)510及びその制御線Pres2を配置しているので、Pres2パルスを追加している点であり、その他のパルスは図3と同じ駆動方法なので説明を省略する。

【0096】

Pres2パルスは1stフレームのみPres1_1、Pres1_2と同じタイミングで“L”→“H”→“L”とすることで、PD501、Cm509、Cfd507をそれぞれリセットさせている。

【0097】

このようなタイミングで駆動することで、図1の構成と同様に残像効果を出したり残像効果を出さなかったりすることができる。

【符号の説明】

【0098】

701:撮像素子

702:AFE(アナログフロントエンド)

703:DSP(DigitalSignalProseccer)

704:タイミング発生回路

705:CPU

506:ROM

707:RAM

708:記録媒体

709:電源スイッチ

510:シャッタースイッチSW1

711:シャッタースイッチSW2

712:モードダイアル

713:測距回路

714:測光回路

715:表示装置

101、401、501:フォトダイオード

102、103、104、105、108、402、403、404、405、408、410、412、502、503、404、505、508、510:MOSトランジスタ

107、407、507:フローティングディフュージョン

109、409、411、413、509:画素メモリ

506:垂直出力線

【特許請求の範囲】

【請求項1】

光を受光して光電荷を生成し蓄積するフォトダイオードと、前記フォトダイオードに接続され前記光電荷を転送する転送トランジスタと、前記転送トランジスタに接続された前記光電荷を蓄積する蓄積容量とを備え、

前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを実行する第1の駆動モードと、

前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを非実行する第2の駆動モードとを有することを特徴とする撮像装置。

【請求項2】

前記光電荷を蓄積する容量の異なる複数の蓄積容量を有し、前記複数の蓄積容量を選択する選択手段を有することを特徴とする、請求項1に記載の撮像装置。

【請求項3】

前記撮像装置は、前記フォトダイオードが光電荷を蓄積した信号を読み出すとともに、読み出された信号を画像として表示する手段と、

前記信号のうち1フレームのみを読み出し表示する静止画撮影モードと

前記信号の読み出しと表示を連続した複数のフレームで繰り返す動画撮影モードとを有し

前記動画撮影モードの時に前記第2の駆動モードで駆動することを特徴とする請求項1または請求項2に記載の撮像装置。

【請求項4】

前記撮像装置は、被写体を含む周囲輝度を測定する手段を有し、周囲輝度が所定の輝度よりも暗い場合に前記第2の駆動モードで駆動することを特徴とする請求項1乃至請求項3の何れか1項に記載の撮像装置。

【請求項1】

光を受光して光電荷を生成し蓄積するフォトダイオードと、前記フォトダイオードに接続され前記光電荷を転送する転送トランジスタと、前記転送トランジスタに接続された前記光電荷を蓄積する蓄積容量とを備え、

前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを実行する第1の駆動モードと、

前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを非実行する第2の駆動モードとを有することを特徴とする撮像装置。

【請求項2】

前記光電荷を蓄積する容量の異なる複数の蓄積容量を有し、前記複数の蓄積容量を選択する選択手段を有することを特徴とする、請求項1に記載の撮像装置。

【請求項3】

前記撮像装置は、前記フォトダイオードが光電荷を蓄積した信号を読み出すとともに、読み出された信号を画像として表示する手段と、

前記信号のうち1フレームのみを読み出し表示する静止画撮影モードと

前記信号の読み出しと表示を連続した複数のフレームで繰り返す動画撮影モードとを有し

前記動画撮影モードの時に前記第2の駆動モードで駆動することを特徴とする請求項1または請求項2に記載の撮像装置。

【請求項4】

前記撮像装置は、被写体を含む周囲輝度を測定する手段を有し、周囲輝度が所定の輝度よりも暗い場合に前記第2の駆動モードで駆動することを特徴とする請求項1乃至請求項3の何れか1項に記載の撮像装置。

【図1】

【図2】

【図3(a)】

【図3(b)】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3(a)】

【図3(b)】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−106224(P2013−106224A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−249326(P2011−249326)

【出願日】平成23年11月15日(2011.11.15)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月15日(2011.11.15)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]