放射ノイズ防止プリント基板配置配線処理システム

【課題】配置配線処理時にパスコン追加のEMC設計条件を検出及びパスコンの追加を行い放射ノイズ発生を防止し設計品質を保証するプリント基板配置配線処理システムの提供。

【解決手段】電子部品の電源ピンを抽出する電子部品電源ピン抽出部21、電源ピンから電源のヴィアまでの配線パターンを抽出する配線パターン抽出部22、抽出された配線パターンの線長、線幅を検査する線長、線幅検査部23、パスコンの追加が可能かを検査するパスコン追加可能性検査部24、現状の配線経路でパスコンが追加不可能な場合パスコン追加可能とする配線経路があるか検査する配線経路変更可能性検査部25と、配線経路を変更する配線経路変更実行部26、パスコン追加実行部27、配線経路を変更してもパスコンが追加不可能な場合エラー表示するエラー表示部28を備える。

【解決手段】電子部品の電源ピンを抽出する電子部品電源ピン抽出部21、電源ピンから電源のヴィアまでの配線パターンを抽出する配線パターン抽出部22、抽出された配線パターンの線長、線幅を検査する線長、線幅検査部23、パスコンの追加が可能かを検査するパスコン追加可能性検査部24、現状の配線経路でパスコンが追加不可能な場合パスコン追加可能とする配線経路があるか検査する配線経路変更可能性検査部25と、配線経路を変更する配線経路変更実行部26、パスコン追加実行部27、配線経路を変更してもパスコンが追加不可能な場合エラー表示するエラー表示部28を備える。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、プリント基板配置配線処理システムに関し、特に、多層プリント基板の放射ノイズ(電磁雑音)の発生を防止するEMC(ElectroMagnetic Compatibility)設計条件に対応したCAD(Computer Aided Design;計算機支援型設計)によるプリント基板配置配線処理システムに関する。

【0002】

【従来の技術】従来のプリント基板配置配線処理システムにおいては、パスコン(放射ノイズ低減用コンデンサ;バイパスコンデンサともいう)を追加する場合、目視および人手によりパスコンの追加配置、および配線を行っている。

【0003】なお、例えば特開平9−62717号公報には、電子部品各々の近傍に割り当て配置されるバイパスコンデンサの数が所定の評価関数により最適に決定された後に、電子部品各々へのバイパスコンデンサの仮想接続関係を考慮して電子部品相互接続関係を示す接続マトリクスを生成し、この接続マトリクスを参照しつつ、電子部品相互間での仮想配線長の総和が最小となるべく、電子部品各々の基板上での配置位置を決定するようにした方法が提案されている。

【0004】

【発明が解決しようとする課題】上述した従来のプリント基板配置配線処理システムにおいては、パスコン(放射ノイズ低減用コンデンサ)の追加配置配線を人手に依存して行っていたため、追加もれを生じ易い、という問題点を有している。

【0005】また、配置配線処理時に検出されずに、パスコンを追加せずにそのまま基板が製造された場合には、放射ノイズ(電磁雑音)の発生源となる、という問題点を有している。

【0006】したがって本発明は、上記問題点に鑑みてなされたものであって、その目的は、EMC設計条件違反のパスコン(放射ノイズ低減用コンデンサ)の追加もれを生ずることなく、設計条件の違反による放射ノイズ発生を防止して設計品質を保証するプリント基板配置配線処理システムを提供することにある。

【0007】

【課題を解決するための手段】前記目的を達成する本発明は、電子部品の接続ピン間の回路的接続を示す回路図情報と、電子部品の接続ピン位置を含む部品情報とにもとづいて多層プリント基板に搭載する前記電子部品の接続ピン間の配置と配線を行うCAD方式のプリント基板配置配線処理方式において、電子部品の電源ピンを抽出し、当該電源ピンと電源ヴィアホール間を接続する物理的な配線パターンを抽出する手段と、該手段により抽出された配線パターンの線長、線幅を検査する手段と、現状の配線経路でパスコン(放射ノイズ低減用コンデンサ)の追加が可能であるかを検査する手段と、現状の配線経路ではパスコンの追加が不可能な場合に配線経路を変更する手段と、パスコンの追加が可能な場合にパスコンを追加する手段と、配線経路を変更してもパスコンの追加が不可能な場合にエラーを表示する手段と、を備えたことを特徴とするプリント基板配置配線処理方式を提供する。

【0008】また本発明は、電子部品の接続ピン間の回路的接続を示す回路図情報と、電子部品の接続ピン位置を含む部品情報とにもとづいて多層プリント基板に搭載する前記電子部品の配置と接続ピン間の配線を行うCAD方式のプリント基板配置配線処理方式において、電子部品の接続ピン間の回路的接続を示す回路図情報と電子部品の接続ピン位置を含む部品情報と配置配線処理中に生成した配線パターンのデータを記憶するデータ記憶装置と、表示部と、前記データ記憶装置に記憶したデータとパスコンの追加が不可能であったエラーに関するデータとを前記表示部にグラフィック表示する入出力処理を行う入出力装置と、現状の配置配線経路では放射ノイズ低減用パスコンの追加が不可能であるというエラーの検出を行う配置配線処理部と、全体動作の制御および配置配線処理に関する演算を行う演算処理装置とを備えて構成される。

【0009】

【発明の実施の形態】本発明の実施の形態について以下に説明する。本発明を適用した一実施の形態は、電子部品の接続ピン間の回路的接続を示す回路図情報と、前記電子部品の接続ピン位置を含む部品情報とに基づいて多層プリント基板に搭載する前記電子部品の配置と接続ピン間の配線を行うCAD方式のプリント基板配置配線処理システムにおいて、電子部品の電源ピンを抽出する手段(図1の21)と、前記電源ピンと電源ヴィアホール間を接続する物理的な配線パターンを抽出する手段(図1の22)と、前記抽出された配線パターンの線長、線幅を検査する手段(図1の23)と、放射ノイズ低減用コンデンサ(「パスコン」という)の追加可能性を検査する手段(図1の24)と、現状の配線経路ではパスコンの追加が不可能な場合に配線経路の変更が可能であるか検査する手段(図1の25)と、配線経路の変更を実行する手段(図1の26)と、パスコンの追加が可能な場合にパスコンを追加する手段(図1の27)と、現状の配線経路を変更してもパスコンの追加が不可能な場合にはエラーを表示する手段(図1の28)と、備える。

【0010】本発明の一実施の形態の処理動作について説明すると、(a)まず回路図情報と部品情報を入力し、電子部品の電源ピンを抽出し、(b)前記電源ピンから電源ヴィアまでの配線パターンを抽出し、(c)該配線パターンの線長、線幅を検査し、(d)該配線パターンの線長、線幅の検査結果が適であり、現状の配線パターンにパスコンの追加が可能であればパスコンを追加し、(e)ステップ(c)で該配線パターンの線長、線幅の検査結果が不適であるか、ステップ(d)でパスコンの追加ができない場合、配線経路の変更が可能であるか判定し、(f)配線経路が変更可能な場合に、配線経路を変更して、前記ステップ(b)の処理から開始し、(g)一方、配線経路を変更してもパスコンの追加が不可能な場合にはエラーを表示する。

【0011】本発明の一実施の形態において、上記各手段(図1の21〜28)は、CADシステムを構成するコンピュータ(演算処理装置)で実行されるプログラム制御によって実現され、これらのプログラムを記録した記録媒体からプログラムをロードして実行されるものであり、本発明はこの記録媒体も含む。

【0012】

【実施例】本発明の実施例について図面を参照して詳細に説明する。

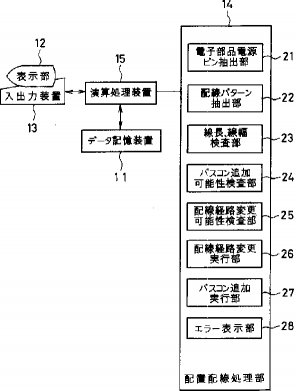

【0013】図1は、本発明の一実施例のプリント基板配置配線処理システムの構成を示すブロック図である。

【0014】図1を参照すると、本実施例に係るプリント基板配置配線処理方式は、プリント基板に搭載する電子部品およびピンデータ,電子部品ピン間の論理的接続データおよび配置配線処理中に生成された配線パターンデータを記憶するデータ記憶装置11と、表示部12と、データ記憶装置の記憶データと、パスコンの追加不可能エラーを表示部12に表示するための入出力処理を行う入出力装置13と、プリント基板にパスコンの追加処理を実行する配置配線処理部14と、プログラムを内蔵し全体の動作制御と配置配線並びに配置配線修正に伴う主たる演算とを行う演算処理装置15と、を備える。

【0015】また、配置配線処理部14は、電子部品の電源ピンを抽出する電子部品電源ピン抽出部21と、電源ピンから電源のヴィアまでの配線パターンを抽出する配線パターン抽出部22と、抽出された配線パターンの線長、線幅を検査する線長、線幅検査部23と、パスコンの追加が可能かを検査するパスコン追加可能検査部24と、現状の配線経路ではパスコンの追加が不可能な場合にパスコンを追加可能にするような配線パターン経路が存在するかを検査する配線経路変更可能性検査部25と、既存の配線経路を前項の配線経路変更可能性検査部25で検出したパスコンの追加が可能な配線経路に変更する配線経路変更実行部26と、パスコンを追加するパスコン追加実行部27と、配線経路を変更してもパスコンの追加が不可能な場合にエラーを表示するエラー表示部28と、を備えて構成されている。

【0016】図2は、本発明の一実施例に係るプリント基板配置配線処理システムの動作を説明するためのフローチャートである。次に図1および図2を参照して、本実施例に係るプリント基板配置配線処理システムの動作について説明する。

【0017】入出力装置13を介して回路図情報と部品情報を入力すると、配置配線処理部14の電子部品電源ピン抽出部21は、データ記憶装置11に記憶されている回路図情報と部品情報を基にして電源ピンの情報を抽出し(ステップS1)、配線パターン抽出部22は、データ記憶装置11に記憶されている回路図情報と部品情報と部品ピン間の配線パターンデータから配線パターン情報を抽出する(ステップS2)。

【0018】抽出した配線パターン情報から、電源ピンから電源ヴィアまでの線長、線幅を検査し、基準値内にあることを検査する(ステップS3)。

【0019】ステップ3における検査がOKであればパスコンの追加が可能であるかを検査する(ステップS4)。

【0020】ステップ4における検査がOKであれば、パスコンを追加する(ステップS5)。

【0021】一方、ステップS3、ステップS4における検査がNG(不適)の場合には、既存の配線経路を変更することによりパスコンの追加が可能であるかを検査する(ステップS6)。

【0022】配線経路の変更が可能であれば配線経路を変更して、ステップ2から再度実行する(ステップS7)。

【0023】一方、配線経路を変更してもパスコンの追加が不可能であれば、パスコンの追加が不可能であったことを、表示部12にエラー表示する(ステップS8)。

【0024】図3は、本発明の一実施例を具体的に説明するための図であり、プリント基板配置配線処理を行う前の電子部品の配線パターンの状態を示す図である。

【0025】図4は、本発明の一実施例によりパスコンの追加及び配線パターン変更の一例を示す図である。図4を参照すると、電源端子と電源ビア間を接続する配線パタンにはパスコンが接続され、また図3の配線パタンではパスコンが追加できないパタンについてはその配線パタンを変更し電源端子2−4から電源ヴィア1−4までの配線にパスコン3−4を追加している。

【0026】

【発明の効果】以上説明したように、本発明によれば、EMC設計条件を満足させてのパスコンの追加及び配線を容易に行うことができ、かつEMC設計条件違反による放射ノイズ(電磁雑音)の発生を防止して設計品質を保証することができる、という効果を奏する。

【図面の簡単な説明】

【図1】本発明の一実施例の構成を示す示すブロック図である。

【図2】本発明の一実施例の動作を説明するためのフローチャートである。

【図3】本発明の一実施例を説明するための図であり、プリント基板配置配線処理を実施する前の電子部品の配線パターンの状態を示す図である。

【図4】本発明の一実施例を説明するための図であり、プリント基板配置配線処理方式におけるパスコンの追加及び配線パターン変更の様子を示す図である。

【符号の説明】

1 線長、線幅検査部

2 パスコン追加可能性検査部

3 配線経路変更可能性検査部

4 配線経路変更実行部

5 パスコン追加実行部

6 エラー表示部

11 データ記憶装置

12 表示部

13 入出力装置

14 配置配線処理部

15 中央演算処理装置

21 電子部品電源ピン抽出部

22 配線パターン抽出部

【0001】

【発明の属する技術分野】本発明は、プリント基板配置配線処理システムに関し、特に、多層プリント基板の放射ノイズ(電磁雑音)の発生を防止するEMC(ElectroMagnetic Compatibility)設計条件に対応したCAD(Computer Aided Design;計算機支援型設計)によるプリント基板配置配線処理システムに関する。

【0002】

【従来の技術】従来のプリント基板配置配線処理システムにおいては、パスコン(放射ノイズ低減用コンデンサ;バイパスコンデンサともいう)を追加する場合、目視および人手によりパスコンの追加配置、および配線を行っている。

【0003】なお、例えば特開平9−62717号公報には、電子部品各々の近傍に割り当て配置されるバイパスコンデンサの数が所定の評価関数により最適に決定された後に、電子部品各々へのバイパスコンデンサの仮想接続関係を考慮して電子部品相互接続関係を示す接続マトリクスを生成し、この接続マトリクスを参照しつつ、電子部品相互間での仮想配線長の総和が最小となるべく、電子部品各々の基板上での配置位置を決定するようにした方法が提案されている。

【0004】

【発明が解決しようとする課題】上述した従来のプリント基板配置配線処理システムにおいては、パスコン(放射ノイズ低減用コンデンサ)の追加配置配線を人手に依存して行っていたため、追加もれを生じ易い、という問題点を有している。

【0005】また、配置配線処理時に検出されずに、パスコンを追加せずにそのまま基板が製造された場合には、放射ノイズ(電磁雑音)の発生源となる、という問題点を有している。

【0006】したがって本発明は、上記問題点に鑑みてなされたものであって、その目的は、EMC設計条件違反のパスコン(放射ノイズ低減用コンデンサ)の追加もれを生ずることなく、設計条件の違反による放射ノイズ発生を防止して設計品質を保証するプリント基板配置配線処理システムを提供することにある。

【0007】

【課題を解決するための手段】前記目的を達成する本発明は、電子部品の接続ピン間の回路的接続を示す回路図情報と、電子部品の接続ピン位置を含む部品情報とにもとづいて多層プリント基板に搭載する前記電子部品の接続ピン間の配置と配線を行うCAD方式のプリント基板配置配線処理方式において、電子部品の電源ピンを抽出し、当該電源ピンと電源ヴィアホール間を接続する物理的な配線パターンを抽出する手段と、該手段により抽出された配線パターンの線長、線幅を検査する手段と、現状の配線経路でパスコン(放射ノイズ低減用コンデンサ)の追加が可能であるかを検査する手段と、現状の配線経路ではパスコンの追加が不可能な場合に配線経路を変更する手段と、パスコンの追加が可能な場合にパスコンを追加する手段と、配線経路を変更してもパスコンの追加が不可能な場合にエラーを表示する手段と、を備えたことを特徴とするプリント基板配置配線処理方式を提供する。

【0008】また本発明は、電子部品の接続ピン間の回路的接続を示す回路図情報と、電子部品の接続ピン位置を含む部品情報とにもとづいて多層プリント基板に搭載する前記電子部品の配置と接続ピン間の配線を行うCAD方式のプリント基板配置配線処理方式において、電子部品の接続ピン間の回路的接続を示す回路図情報と電子部品の接続ピン位置を含む部品情報と配置配線処理中に生成した配線パターンのデータを記憶するデータ記憶装置と、表示部と、前記データ記憶装置に記憶したデータとパスコンの追加が不可能であったエラーに関するデータとを前記表示部にグラフィック表示する入出力処理を行う入出力装置と、現状の配置配線経路では放射ノイズ低減用パスコンの追加が不可能であるというエラーの検出を行う配置配線処理部と、全体動作の制御および配置配線処理に関する演算を行う演算処理装置とを備えて構成される。

【0009】

【発明の実施の形態】本発明の実施の形態について以下に説明する。本発明を適用した一実施の形態は、電子部品の接続ピン間の回路的接続を示す回路図情報と、前記電子部品の接続ピン位置を含む部品情報とに基づいて多層プリント基板に搭載する前記電子部品の配置と接続ピン間の配線を行うCAD方式のプリント基板配置配線処理システムにおいて、電子部品の電源ピンを抽出する手段(図1の21)と、前記電源ピンと電源ヴィアホール間を接続する物理的な配線パターンを抽出する手段(図1の22)と、前記抽出された配線パターンの線長、線幅を検査する手段(図1の23)と、放射ノイズ低減用コンデンサ(「パスコン」という)の追加可能性を検査する手段(図1の24)と、現状の配線経路ではパスコンの追加が不可能な場合に配線経路の変更が可能であるか検査する手段(図1の25)と、配線経路の変更を実行する手段(図1の26)と、パスコンの追加が可能な場合にパスコンを追加する手段(図1の27)と、現状の配線経路を変更してもパスコンの追加が不可能な場合にはエラーを表示する手段(図1の28)と、備える。

【0010】本発明の一実施の形態の処理動作について説明すると、(a)まず回路図情報と部品情報を入力し、電子部品の電源ピンを抽出し、(b)前記電源ピンから電源ヴィアまでの配線パターンを抽出し、(c)該配線パターンの線長、線幅を検査し、(d)該配線パターンの線長、線幅の検査結果が適であり、現状の配線パターンにパスコンの追加が可能であればパスコンを追加し、(e)ステップ(c)で該配線パターンの線長、線幅の検査結果が不適であるか、ステップ(d)でパスコンの追加ができない場合、配線経路の変更が可能であるか判定し、(f)配線経路が変更可能な場合に、配線経路を変更して、前記ステップ(b)の処理から開始し、(g)一方、配線経路を変更してもパスコンの追加が不可能な場合にはエラーを表示する。

【0011】本発明の一実施の形態において、上記各手段(図1の21〜28)は、CADシステムを構成するコンピュータ(演算処理装置)で実行されるプログラム制御によって実現され、これらのプログラムを記録した記録媒体からプログラムをロードして実行されるものであり、本発明はこの記録媒体も含む。

【0012】

【実施例】本発明の実施例について図面を参照して詳細に説明する。

【0013】図1は、本発明の一実施例のプリント基板配置配線処理システムの構成を示すブロック図である。

【0014】図1を参照すると、本実施例に係るプリント基板配置配線処理方式は、プリント基板に搭載する電子部品およびピンデータ,電子部品ピン間の論理的接続データおよび配置配線処理中に生成された配線パターンデータを記憶するデータ記憶装置11と、表示部12と、データ記憶装置の記憶データと、パスコンの追加不可能エラーを表示部12に表示するための入出力処理を行う入出力装置13と、プリント基板にパスコンの追加処理を実行する配置配線処理部14と、プログラムを内蔵し全体の動作制御と配置配線並びに配置配線修正に伴う主たる演算とを行う演算処理装置15と、を備える。

【0015】また、配置配線処理部14は、電子部品の電源ピンを抽出する電子部品電源ピン抽出部21と、電源ピンから電源のヴィアまでの配線パターンを抽出する配線パターン抽出部22と、抽出された配線パターンの線長、線幅を検査する線長、線幅検査部23と、パスコンの追加が可能かを検査するパスコン追加可能検査部24と、現状の配線経路ではパスコンの追加が不可能な場合にパスコンを追加可能にするような配線パターン経路が存在するかを検査する配線経路変更可能性検査部25と、既存の配線経路を前項の配線経路変更可能性検査部25で検出したパスコンの追加が可能な配線経路に変更する配線経路変更実行部26と、パスコンを追加するパスコン追加実行部27と、配線経路を変更してもパスコンの追加が不可能な場合にエラーを表示するエラー表示部28と、を備えて構成されている。

【0016】図2は、本発明の一実施例に係るプリント基板配置配線処理システムの動作を説明するためのフローチャートである。次に図1および図2を参照して、本実施例に係るプリント基板配置配線処理システムの動作について説明する。

【0017】入出力装置13を介して回路図情報と部品情報を入力すると、配置配線処理部14の電子部品電源ピン抽出部21は、データ記憶装置11に記憶されている回路図情報と部品情報を基にして電源ピンの情報を抽出し(ステップS1)、配線パターン抽出部22は、データ記憶装置11に記憶されている回路図情報と部品情報と部品ピン間の配線パターンデータから配線パターン情報を抽出する(ステップS2)。

【0018】抽出した配線パターン情報から、電源ピンから電源ヴィアまでの線長、線幅を検査し、基準値内にあることを検査する(ステップS3)。

【0019】ステップ3における検査がOKであればパスコンの追加が可能であるかを検査する(ステップS4)。

【0020】ステップ4における検査がOKであれば、パスコンを追加する(ステップS5)。

【0021】一方、ステップS3、ステップS4における検査がNG(不適)の場合には、既存の配線経路を変更することによりパスコンの追加が可能であるかを検査する(ステップS6)。

【0022】配線経路の変更が可能であれば配線経路を変更して、ステップ2から再度実行する(ステップS7)。

【0023】一方、配線経路を変更してもパスコンの追加が不可能であれば、パスコンの追加が不可能であったことを、表示部12にエラー表示する(ステップS8)。

【0024】図3は、本発明の一実施例を具体的に説明するための図であり、プリント基板配置配線処理を行う前の電子部品の配線パターンの状態を示す図である。

【0025】図4は、本発明の一実施例によりパスコンの追加及び配線パターン変更の一例を示す図である。図4を参照すると、電源端子と電源ビア間を接続する配線パタンにはパスコンが接続され、また図3の配線パタンではパスコンが追加できないパタンについてはその配線パタンを変更し電源端子2−4から電源ヴィア1−4までの配線にパスコン3−4を追加している。

【0026】

【発明の効果】以上説明したように、本発明によれば、EMC設計条件を満足させてのパスコンの追加及び配線を容易に行うことができ、かつEMC設計条件違反による放射ノイズ(電磁雑音)の発生を防止して設計品質を保証することができる、という効果を奏する。

【図面の簡単な説明】

【図1】本発明の一実施例の構成を示す示すブロック図である。

【図2】本発明の一実施例の動作を説明するためのフローチャートである。

【図3】本発明の一実施例を説明するための図であり、プリント基板配置配線処理を実施する前の電子部品の配線パターンの状態を示す図である。

【図4】本発明の一実施例を説明するための図であり、プリント基板配置配線処理方式におけるパスコンの追加及び配線パターン変更の様子を示す図である。

【符号の説明】

1 線長、線幅検査部

2 パスコン追加可能性検査部

3 配線経路変更可能性検査部

4 配線経路変更実行部

5 パスコン追加実行部

6 エラー表示部

11 データ記憶装置

12 表示部

13 入出力装置

14 配置配線処理部

15 中央演算処理装置

21 電子部品電源ピン抽出部

22 配線パターン抽出部

【特許請求の範囲】

【請求項1】電子部品の接続ピン間の回路的接続を示す回路図情報と、前記電子部品の接続ピン位置を含む部品情報とに基づいて多層プリント基板に搭載する前記電子部品の配置と接続ピン間の配線を行うCAD方式のプリント基板配置配線処理システムにおいて、前記電子部品の電源ピンを抽出し、前記電源ピンと電源ヴィアホール間を接続する物理的な配線パターンを抽出する手段と、前記抽出された配線パターンの線長、線幅を検査する手段と、放射ノイズ低減用コンデンサ(「パスコン」という)の追加可能性を検査する手段と、現状の配線経路ではパスコンの追加が不可能な場合に配線経路を変更する手段と、パスコンの追加が可能な場合にパスコンを追加する手段と、現状の配線経路を変更してもパスコンの追加が不可能な場合にはエラーを表示する手段と、を備えたことを特徴とするプリント基板配置配線処理システム。

【請求項2】電子部品の接続ピン間の回路的接続を示す回路図情報と、前記電子部品の接続ピン位置を含む部品情報とに基づいて多層プリント基板に搭載する前記電子部品の配置と接続ピン間の配線を行うCAD方式のプリント基板配置配線処理方式において、電子部品の接続ピン間の回路的接続を示す回路図情報と電子部品の接続ピン位置を含む部品情報と配置配線処理中に生成した配線パターンのデータを記憶するデータ記憶装置と、表示部と、前記データ記憶装置に記憶されたデータとパスコンの追加不可能エラーに関するデータとを前記表示部にグラフィック表示する入出力処理を行う入出力装置と、放射ノイズ低減用のパスコン追加が不可能であるかエラー検出を行う配置配線処理部と、全体動作の制御および配置配線処理に関する演算を行う演算処理装置と、を備え、前記電子部品の電源ピンと電源ヴィアホール間を接続する物理的な配線パターンを抽出して該配線パターンの線長、線幅を検査し、パスコンの追加可能性を検査しパスコンの追加が不可能な場合に配線経路を変更するとともにパスコンの追加が可能な場合にパスコンを追加し、一方、配線経路を変更してもパスコンの追加が不可能な場合には前記表示部にエラーを表示するように制御する、ことを特徴とするプリント基板配置配線処理装置。

【請求項3】(a)回路図情報と部品情報を入力し、電子部品の電源ピンを抽出し、(b)前記電源ピンから電源ヴィアまでの配線パターンを抽出し、(c)該配線パターンの線長、線幅を検査し、(d)該配線パターンの線長、線幅の検査結果が適であり、現状の配線パターンにパスコンの追加が可能であればパスコンを追加し、(e)ステップ(c)で該配線パターンの線長、線幅の検査結果が不適であるか、ステップ(d)でパスコンの追加ができない場合に、配線経路の変更が可能であるか判定し、(f)配線経路が変更可能な場合に、配線経路を変更して、前記ステップ(b)の処理から開始し、(g)一方、配線経路を変更してもパスコンの追加が不可能な場合には表示部にエラーを表示する、上記ステップ(a)乃至(g)を含むことを特徴とする、プリント基板配置配線方法。

【請求項4】プリント基板配置配線CADシステムにおいて、(a)回路図情報と部品情報を入力し、電子部品の電源ピンを抽出する処理、(b)前記電源ピンから電源ヴィアまでの配線パターンを抽出する処理、(c)該配線パターンの線長、線幅を検査する処理、(d)該配線パターンの線長、線幅の検査結果が適であり、現状の配線パターンにパスコンの追加が可能であればパスコンを追加する処理、(e)該配線パターンの線長、線幅の検査結果が不適であるか、パスコンの追加ができない場合、配線経路の変更が可能であるか判定し、配線経路が変更可能な場合に、配線経路を変更してパスコンの追加が可能な場合にパスコンを追加する処理、(f)配線経路を変更してもパスコンの追加が不可能な場合には表示部にエラーを表示する処理、の上記(a)乃至(g)の処理を、上記CADシステムのコンピュータで実行させるためのプログラムを記録した記録媒体。

【請求項1】電子部品の接続ピン間の回路的接続を示す回路図情報と、前記電子部品の接続ピン位置を含む部品情報とに基づいて多層プリント基板に搭載する前記電子部品の配置と接続ピン間の配線を行うCAD方式のプリント基板配置配線処理システムにおいて、前記電子部品の電源ピンを抽出し、前記電源ピンと電源ヴィアホール間を接続する物理的な配線パターンを抽出する手段と、前記抽出された配線パターンの線長、線幅を検査する手段と、放射ノイズ低減用コンデンサ(「パスコン」という)の追加可能性を検査する手段と、現状の配線経路ではパスコンの追加が不可能な場合に配線経路を変更する手段と、パスコンの追加が可能な場合にパスコンを追加する手段と、現状の配線経路を変更してもパスコンの追加が不可能な場合にはエラーを表示する手段と、を備えたことを特徴とするプリント基板配置配線処理システム。

【請求項2】電子部品の接続ピン間の回路的接続を示す回路図情報と、前記電子部品の接続ピン位置を含む部品情報とに基づいて多層プリント基板に搭載する前記電子部品の配置と接続ピン間の配線を行うCAD方式のプリント基板配置配線処理方式において、電子部品の接続ピン間の回路的接続を示す回路図情報と電子部品の接続ピン位置を含む部品情報と配置配線処理中に生成した配線パターンのデータを記憶するデータ記憶装置と、表示部と、前記データ記憶装置に記憶されたデータとパスコンの追加不可能エラーに関するデータとを前記表示部にグラフィック表示する入出力処理を行う入出力装置と、放射ノイズ低減用のパスコン追加が不可能であるかエラー検出を行う配置配線処理部と、全体動作の制御および配置配線処理に関する演算を行う演算処理装置と、を備え、前記電子部品の電源ピンと電源ヴィアホール間を接続する物理的な配線パターンを抽出して該配線パターンの線長、線幅を検査し、パスコンの追加可能性を検査しパスコンの追加が不可能な場合に配線経路を変更するとともにパスコンの追加が可能な場合にパスコンを追加し、一方、配線経路を変更してもパスコンの追加が不可能な場合には前記表示部にエラーを表示するように制御する、ことを特徴とするプリント基板配置配線処理装置。

【請求項3】(a)回路図情報と部品情報を入力し、電子部品の電源ピンを抽出し、(b)前記電源ピンから電源ヴィアまでの配線パターンを抽出し、(c)該配線パターンの線長、線幅を検査し、(d)該配線パターンの線長、線幅の検査結果が適であり、現状の配線パターンにパスコンの追加が可能であればパスコンを追加し、(e)ステップ(c)で該配線パターンの線長、線幅の検査結果が不適であるか、ステップ(d)でパスコンの追加ができない場合に、配線経路の変更が可能であるか判定し、(f)配線経路が変更可能な場合に、配線経路を変更して、前記ステップ(b)の処理から開始し、(g)一方、配線経路を変更してもパスコンの追加が不可能な場合には表示部にエラーを表示する、上記ステップ(a)乃至(g)を含むことを特徴とする、プリント基板配置配線方法。

【請求項4】プリント基板配置配線CADシステムにおいて、(a)回路図情報と部品情報を入力し、電子部品の電源ピンを抽出する処理、(b)前記電源ピンから電源ヴィアまでの配線パターンを抽出する処理、(c)該配線パターンの線長、線幅を検査する処理、(d)該配線パターンの線長、線幅の検査結果が適であり、現状の配線パターンにパスコンの追加が可能であればパスコンを追加する処理、(e)該配線パターンの線長、線幅の検査結果が不適であるか、パスコンの追加ができない場合、配線経路の変更が可能であるか判定し、配線経路が変更可能な場合に、配線経路を変更してパスコンの追加が可能な場合にパスコンを追加する処理、(f)配線経路を変更してもパスコンの追加が不可能な場合には表示部にエラーを表示する処理、の上記(a)乃至(g)の処理を、上記CADシステムのコンピュータで実行させるためのプログラムを記録した記録媒体。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2000−35976(P2000−35976A)

【公開日】平成12年2月2日(2000.2.2)

【国際特許分類】

【出願番号】特願平10−202569

【出願日】平成10年7月17日(1998.7.17)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

【公開日】平成12年2月2日(2000.2.2)

【国際特許分類】

【出願日】平成10年7月17日(1998.7.17)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

[ Back to top ]