故障検出回路

【課題】RAMマクロ出力回路のテストを効率良く行うことができる故障検出回路を提供すること。

【解決手段】本発明にかかる故障検出回路は、メモリBIST100と、メモリBISTが出力したマクロ試験データ信号S100を選択する複数のRAMマクロ入力選択回路110、111と、選択されたマクロ試験データ信号S100をそれぞれ入力するRAMマクロ120、121と、RAMマクロ120、121の出力信号を選択するBIST入力選択回路200と、RAMマクロ120、121からの出力信号を選択するRAMマクロ出力選択回路130、131と、選択された出力信号を保持するフリップフロップ140、141と、マクロ試験データ信号S100からパリティ信号を生成するパリティ生成回路400と、パリティ信号とフリップフロップが保持している出力信号のパリティチェックを行うパリティチェック回路150、151と、を備える。

【解決手段】本発明にかかる故障検出回路は、メモリBIST100と、メモリBISTが出力したマクロ試験データ信号S100を選択する複数のRAMマクロ入力選択回路110、111と、選択されたマクロ試験データ信号S100をそれぞれ入力するRAMマクロ120、121と、RAMマクロ120、121の出力信号を選択するBIST入力選択回路200と、RAMマクロ120、121からの出力信号を選択するRAMマクロ出力選択回路130、131と、選択された出力信号を保持するフリップフロップ140、141と、マクロ試験データ信号S100からパリティ信号を生成するパリティ生成回路400と、パリティ信号とフリップフロップが保持している出力信号のパリティチェックを行うパリティチェック回路150、151と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は故障検出回路に関する。

【背景技術】

【0002】

RAMマクロを有する故障検出回路において、一般に、フリップフロップ間のロジックの検査はスキャンテストにより行われ、RAMマクロの検査はメモリBIST(build-in self-test)により行われる。

【0003】

図5は、関連する故障検出回路のブロック図である。図5に示す故障検出回路は、メモリBIST100と、RAMマクロ入力選択回路110、111と、RAMマクロ120、121と、RAMマクロ出力選択回路130、131と、フリップフロップ(FF)140、141と、BIST入力選択回路200と、を備えている。

【0004】

RAMマクロ入力選択回路110は、メモリBIST100で生成され出力されたRAMマクロ試験データ信号S100と、外部機器から出力された信号S1を入力し、いずれか選択した信号をRAMマクロ120に出力する。同様に、RAMマクロ入力選択回路111は、RAMマクロ試験データ信号S100と、外部機器から出力された信号S2を入力し、いずれか選択した信号をRAMマクロ121に出力する。

RAMマクロ120、121から、それぞれ出力信号S120、S121が、BIST入力選択回路200に出力される。BIST入力選択回路200は、検査を行いたいRAMマクロに応じて、入力された信号をメモリBIST100に選択的に出力する。例えば、RAMマクロ120の検査を行いたい場合には、BIST入力選択回路200は、出力信号S120をメモリBISTに出力する。

メモリBIST100は、BIST入力選択回路200から入力された信号と、RAMマクロ試験データ信号S100との比較を行うことにより、選択したRAMマクロの故障検出を行う。

【0005】

ここで、RAMマクロ出力選択回路130、131は、RAMマクロ120、121の出力に直接接続されている。この場合、RAMマクロ出力選択回路130、131では、スキャンテスト及びメモリBISTによるテストを行うことができない。そこで、RAMマクロ出力選択回路130、131では、機能テストパターンを多数作成し、これらのパターンをテスター上で実行することにより、故障の検出を行っている。

【0006】

特許文献1では、メモリBISTを用いてRAMマクロ出力ロジックのテストを行う技術が開示されている。図6は、特許文献1に開示された技術について、複数のRAMマクロ及びRAMマクロ出力回路がメモリ出力選択回路により構成されている場合のブロック図である。

【0007】

RAMマクロ入力選択回路110は、メモリBIST100で生成され出力されたRAMマクロ試験データ信号S100と、外部機器から出力された信号S1を入力し、いずれか選択した信号をRAMマクロ120に出力する。同様に、RAMマクロ入力選択回路111は、RAMマクロ試験データ信号S100と、外部機器から出力された信号S2を入力し、いずれか選択した信号をRAMマクロ121に出力する。

RAMマクロ120、121から、それぞれ出力信号S120、S121が、BIST入力選択回路200に出力される。BIST入力選択回路200は、検査を行いたいRAMマクロに応じて、入力された信号をメモリBIST100に選択的に出力する。例えば、RAMマクロ120の検査を行いたい場合には、BIST入力選択回路200は、出力信号S120をメモリBISTに出力する。

メモリBIST100は、BIST入力選択回路200から入力された信号と、RAMマクロ試験データ信号S100との比較を行うことにより、選択したRAMマクロの故障検出を行う。

【0008】

RAMマクロ出力選択回路130は、RAMマクロ120、121から出力された出力信号S120、S121を入力する。また選択信号生成回路300は、選択信号S300を、RAMマクロ出力選択回路130に出力する。RAMマクロ出力選択回路130は、選択信号S300に基づいて、出力信号S120、S121のいずれかを選択し、FF140に信号を出力する。また同様にして、RAMマクロ出力選択回路131は、FF141に信号を出力する。

FF140、141から、それぞれ出力信号S140、S141が、BIST入力選択回路200に出力される。BIST入力選択回路200は、検査を行いたいRAMマクロ出力選択回路に応じて、入力された信号をメモリBIST100に選択的に出力する。例えば、RAMマクロ出力選択回路130の検査を行いたい場合には、BIST入力選択回路200は、出力信号S140をメモリBISTに出力する。

【0009】

これによると、RAMマクロ出力選択回路の出力をメモリBISTに接続し、メモリBISTにおいて期待値比較を行うことで、RAMマクロ出力選択回路のテストを行うことができる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2004−334933号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、特許文献1にかかる回路では、RAMマクロおよびRAMマクロ出力ロジックを検査する際に、RAMマクロ出力とRAMマクロ出力回路とを選択する回路が必要となる。このとき、RAMマクロのビット幅が大きい場合やRAMマクロの数が多い場合には、選択回路のゲート量及び配線数が増加し、回路の収容性が悪化する。さらに、RAMマクロのテストとRAMマクロ出力回路のテストは同時に行うことができないため、テスト時間が増大する。

また、図5に示す回路のように、機能テストパターンを用いる検査方法では、テストパターン作成コスト及びテスト時間増大によりテストのコストが増加するという問題がある。

本発明は、このような問題点を解決するためになされたものであり、RAMマクロ出力回路のテストを効率良く行うことができる故障検出回路を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明にかかる故障検出回路は、メモリBISTと、前記メモリBISTの出力信号である第1の出力信号を入力し当該第1の出力信号を選択する複数のRAMマクロ入力選択回路と、前記複数のRAMマクロ入力選択回路で選択された前記第1の出力信号をそれぞれ入力する複数のRAMマクロと、前記RAMマクロの出力信号である第2の出力信号を入力し、当該第2の出力信号のうちのいずれかを選択し前記メモリBISTに出力するBIST入力選択回路と、前記RAMマクロから出力された前記第2の出力信号のうちのいずれかを選択するRAMマクロ出力選択回路と、前記RAMマクロ出力選択回路で選択された前記第2の出力信号を保持するフリップフロップと、前記メモリBISTの出力信号からパリティ信号を生成するパリティ生成回路と、前記パリティ生成回路から出力されたパリティ信号と前記フリップフロップが保持している前記第2の出力信号のパリティチェックを行うパリティチェック回路と、を備える。

【発明の効果】

【0013】

メモリBISTによりRAMマクロの故障を検出する故障検出回路において、RAMマクロ出力回路のテストを効率良く行うことができる。

【図面の簡単な説明】

【0014】

【図1】実施の形態1にかかる故障検出回路のブロック図である。

【図2】実施の形態1にかかる故障検出回路のブロック図である。

【図3】実施の形態1にかかるパリティチェック回路のブロック図である。

【図4】実施の形態1にかかる選択信号生成回路の動作を示す図である。

【図5】関連する故障検出回路のブロック図である。

【図6】関連する故障検出回路のブロック図である。

【発明を実施するための形態】

【0015】

実施の形態1.

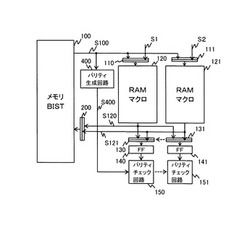

以下、図面を参照して本発明の実施の形態について説明する。図1は、本実施の形態にかかる故障検出回路のブロック図である。

【0016】

故障検出回路は、メモリBIST100と、RAMマクロ入力選択回路110、111と、RAMマクロ120、121と、RAMマクロ出力選択回路130、131と、フリップフロップ(FF)140、141と、パリティチェック回路150、151と、BIST入力選択回路200と、パリティ生成回路400と、を備えている。

【0017】

メモリBIST100は、RAMマクロ試験データ信号S100(第1の出力信号)を生成する。また、メモリBIST100は、RAMマクロ入力選択回路110、111及びパリティ生成回路400と接続されている。メモリBIST100は、RAMマクロ入力選択回路110、111及びパリティ生成回路400に対して、RAMマクロ試験データ信号S100を出力する。

【0018】

パリティ生成回路400には、RAMマクロ試験データ信号S100が入力される。また、パリティ生成回路400は、RAMマクロ試験データ信号S100に基づくパリティ信号S400を生成して、パリティチェック回路150、151に出力する。

【0019】

RAMマクロ入力選択回路110、111には、RAMマクロ試験データ信号S100が入力される。また、RAMマクロ入力選択回路110、111は、外部機器(図示せず)と接続されている。RAMマクロ入力選択回路110には外部機器から信号S1(第3の出力信号)が入力され、RAMマクロ入力選択回路111には外部機器から信号S2(第3の出力信号)が入力される。

RAMマクロ入力選択回路110の出力は、RAMマクロ120と接続されている。RAMマクロ入力選択回路110で選択された信号はRAMマクロ120に出力される。同様に、RAMマクロ入力選択回路111の出力は、RAMマクロ121と接続されている。RAMマクロ入力選択回路111で選択された信号は、RAMマクロ121に出力される。

【0020】

RAMマクロ120、121には、それぞれRAMマクロ入力選択回路110、111で選択された信号が入力される。また、RAMマクロ120の出力は、RAMマクロ出力選択回路130、131及びBIST入力選択回路200と接続されている。RAMマクロ120は、RAMマクロ出力選択回路130、131及びBIST入力選択回路200に出力信号S120(第2の出力信号)を出力する。同様に、RAMマクロ121の出力は、RAMマクロ出力選択回路130、131及びBIST入力選択回路200と接続されている。RAMマクロ121は、RAMマクロ出力選択回路130、131及びBIST入力選択回路200に出力信号S121(第2の出力信号)を出力する。

【0021】

BIST入力選択回路200には、出力信号S120、S121が入力される。また、BIST入力選択回路200の出力は、メモリBIST100と接続されている。BIST入力選択回路200は、選択したデータを、メモリBIST100に出力する。

【0022】

RAMマクロ出力選択回路130には、出力信号S120、S121が入力される。また、RAMマクロ出力選択回路130の出力は、フリップフロップ140と接続されている。RAMマクロ出力選択回路130は、選択したデータを、パリティチェック回路150に出力する。同様に、出力信号S120、S121が入力されたRAMマクロ出力選択回路131は、データをパリティチェック回路151に出力する。

【0023】

図3は、本実施の形態にかかるパリティチェック回路のブロック図である。パリティチェック回路150は、XOR回路150aと、XOR回路150bと、を備えている。

【0024】

XOR回路150aの入力は、フリップフロップ140の出力と接続されている。XOR回路150aには、フリップフロップ140から信号が入力される。XOR回路150aは、XOR回路150aにおける演算(排他的論理和)の結果を出力する。

【0025】

XOR回路150bの一方の入力は、XOR回路150aの出力と接続されている。XOR回路150bには、XOR回路150aによる演算結果が入力される。また、XOR回路150bの他方の入力は、パリティ生成回路400の出力と接続されている。XOR回路150bには、パリティ信号S400が入力される。XOR回路150bは、XOR回路150bにおける演算(排他的論理和)の結果を出力する。

なお、パリティチェック回路151もパリティチェック回路150と同様に構成することができる。

【0026】

すなわちパリティチェック回路150は、通常動作時のパリティチェック回路に、テスト動作時のパリティチェックによるRAMマクロ出力選択回路130の故障検出回路を付加した場合の構成例である。

【0027】

図2は、図1にかかる故障検出回路に、選択信号生成回路310をさらに備えた故障検出回路のブロック図である。本実施の形態では図2に示すように、選択信号生成回路310を備えていてもよい。

【0028】

選択信号生成回路310の出力は、RAMマクロ出力選択回路130、131と接続されている。選択信号生成回路310は、選択信号生成回路310で生成した選択信号S310を、RAMマクロ出力選択回路130、131に出力する。

【0029】

以上詳細に実施の形態の構成を述べたが、メモリBIST100は、当業者にとってよく知られており、また本発明とは直接関係しないので、その詳細な構成は省略する。

なお、上記説明での構成例は一例であり、RAMマクロ入力選択回路の個数、RAMマクロの個数、RAMマクロ出力選択回路の個数、フリップフロップの個数及びパリティチェック回路の個数は限定されない。

【0030】

次に、本実施の形態に係る故障検出回路の動作について説明する。

【0031】

故障検出回路は、メモリBIST100で生成したデータを用いるテスト動作モードと、メモリBIST100で生成したデータを用いない通常動作モードで動作する。

【0032】

メモリBIST100は、RAMマクロ試験データ信号S100を生成して出力する。

【0033】

RAMマクロ入力選択回路110には、メモリBIST100で生成されたRAMマクロ試験データ信号S100と、外部機器から出力された信号S1が入力される。RAMマクロ入力選択回路110は、動作モードに基づいて、いずれの入力信号を用いるかを選択する。すなわちRAMマクロ入力選択回路110は、テスト動作モードの場合にはRAMマクロ試験データ信号S100を選択し、通常動作モードの場合には信号S1を選択する。RAMマクロ入力選択回路110は、選択した信号に応じた書きこみデータをRAMマクロ120に出力する。

同様に、RAMマクロ入力選択回路111は、メモリBIST100で生成されたRAMマクロ試験データ信号S100と、外部機器から出力された信号S2の、いずれの信号を用いるか選択し、選択した信号に応じた書き込みデータをRAMマクロ121に出力する。

【0034】

RAMマクロ120は、入力された書き込みデータに応じて、出力信号S120を出力する。同様にRAMマクロ121は、出力信号S121を出力する。

【0035】

出力信号S120は、RAMマクロ出力選択回路130、131に入力される。同様に出力信号S121は、RAMマクロ出力選択回路130、131に入力される。

RAMマクロ出力選択回路130は、出力信号S120、S121から信号を選択し、選択した信号をFF140に格納する。同様に、RAMマクロ出力選択回路131は、出力信号S120、S121から信号を選択し、選択した信号をFF141に格納する。

【0036】

ここで図2に示したように、本実施の形態にかかる故障検出回路は、例えば選択信号生成回路310を備えていてもよい。選択信号生成回路310は、RAMマクロ出力選択回路130、131を制御するための手段である。選択信号生成回路310は選択信号S310を、RAMマクロ出力選択回路130、131に出力する。

図4は、選択信号生成回路310の動作を示す図である。選択信号生成回路310は、通常動作モードを選択する場合には通常動作時選択信号を送出する。テスト動作モードであって、RAMマクロ120を選択する場合には、RAMマクロ120選択信号を送出し、RAMマクロ121を選択する場合には、RAMマクロ121選択信号を送出する。すなわち、RAMマクロ出力選択回路130、131は、選択信号S310に応じて、RAMマクロ120、121のいずれかの出力信号S120、S121を選択するかを決定し、信号をそれぞれFF140、141に出力する。

【0037】

FF140に格納されたデータは、パリティチェック回路150に入力される。また同様に、FF141に格納されたデータは、パリティチェック回路151に入力される。

【0038】

また、パリティ生成回路400には、メモリBIST100から出力されたRAMマクロ試験データ信号S100が入力され、パリティ信号S400を生成する。パリティ生成回路400は生成したパリティ信号S400を、パリティチェック回路150、151に出力する。

【0039】

ここで図3に示すように、パリティチェック回路150は、XOR回路150aとXOR回路150bを備えている。

ここで、XOR150aは通常動作モードにおける故障検出回路である。XOR150aは、FF140から出力された複数のデータに対して演算を行い、演算結果を出力する。演算は、例えば入力されたデータのそれぞれのパリティビットについて行われる。XOR回路150aの出力は、偶数パリティの場合、RAMマクロ出力選択回路130やFF140が故障していると"1"になり、これにより故障を検出する。

【0040】

XOR150bは、テスト動作モードにおける故障検出回路である。XOR150bは、RAMマクロ試験データ信号S100のパリティであるパリティ信号S400と、XOR150aの出力信号を入力して演算を行い、演算結果を出力する。これによりXOR150bは、RAMマクロ出力選択回路130やFF140の故障検出をおこなう。

パリティチェック回路151は、パリティチェック回路150と同様に動作し、RAMマクロ出力選択回路131やFF141の故障検出を行う。

【0041】

すなわち、通常動作モードにおいて、外部機器からRAMマクロ入力選択回路110に入力された信号S1は、RAMマクロ120に出力される。次に、RAMマクロ120から出力された出力信号S120は、RAMマクロ出力選択回路130及びFF140を介して、パリティチェック回路150に入力される。パリティチェック回路150のXOR回路150aは、FF140から出力された複数のデータについて演算を行い、データのチェックを行う。

同様にして、出力信号S120はRAMマクロ出力選択回路131及びFF141を介して、パリティチェック回路151に入力される。パリティチェック回路151は、XOR(排他的論理和)の演算を行う。また、外部機器からRAMマクロ入力選択回路111に入力された信号S2を用い、RAMマクロ121から出力された信号について、パリティチェック回路150、151において演算を行うことができる。

これにより、通常動作モードにおいて、RAMマクロ120、121及びRAMマクロ出力選択回路130、131の故障検出を行うことができる。

【0042】

また、テスト動作モードにおいて、メモリBIST100から出力され、RAMマクロ入力選択回路110に入力されたRAMマクロ試験データ信号S100は、RAMマクロ120に出力される。次に、RAMマクロ120から出力された出力信号S120は、RAMマクロ出力選択回路130及びFF140を介して、パリティチェック回路150に入力される。パリティチェック回路150のXOR回路150aは、FF140から出力された複数のデータについて演算を行う。この出力を第1の入力信号として、XOR回路150bに出力する。また、メモリBIST100から出力されたRAMマクロ試験データ信号S100は、パリティ生成回路400に入力され、パリティ生成回路400はパリティ信号S400をパリティチェック回路150に出力する。このパリティ信号S400を第2の入力信号としてXOR回路150bは演算を行い、データのチェックを行う。

同様にして、出力信号S120はRAMマクロ出力選択回路131及びFF141を介して、パリティチェック回路151に入力される。パリティチェック回路151は、パリティチェック回路150と同様に動作し、データのチェックを行う。

なお、RAMマクロ入力選択回路110及びRAMマクロ120を用いる代わりに、RAMマクロ入力選択回路111及びRAMマクロ121を用い、RAMマクロ121から出力された信号について、処理を行うことができる。

これによりテスト動作モードにおいて、パリティを用いてRAMマクロ出力選択回路130、131の故障検出を行うことができる。

【0043】

ここで、テスト動作モードにおいて、RAMマクロ120、121から出力された出力信号S120、S121は、それぞれBIST入力選択回路200に入力される。BIST入力選択回路200は、テスト対象となる出力信号S120、S121を選択する。例えば、テスト対象がRAMマクロ120の場合には、出力信号S120を選択し、テスト対象がRAMマクロ121の場合には、出力信号S121を選択する。

BIST入力選択回路200で選択された出力信号S120、S121は、メモリBIST100に入力される。メモリBIST100は、入力されたデータとRAMマクロ試験データ信号S100に応じた期待値との比較を行い、RAMマクロ120、121の故障検出を行う。

【0044】

これにより、メモリBIST100を用いてRAMマクロの故障を検出する回路において、メモリBISTから出力されるRAMマクロ試験データ信号S100を用いて、RAMマクロ120、121の出力からFF140、141に至るまでのテストが可能となる。特に、メモリ出力ロジックが複数のRAMマクロを選択する回路において、選択回路のテストを可能にする。

すなわち、メモリBIST100による比較を行うこと無く、RAMマクロ出力選択回路130、131のテストを行うことができる。したがって、メモリBIST100によるRAMマクロ120、121のテストと同時に、RAMマクロ120、121の出力からFF140、141に至るまでの回路のテストをおこなうことができ、テスト時間の短縮が可能となる。

【0045】

また、データそのものではなく、パリティで期待値比較(パリティチェックによる故障検出)をおこなうことができる。これにより、BIST入力選択回路200の信号数の削減が可能になるとともに、BIST入力選択回路200のゲート量も削減可能となる。RAMマクロ数及びマクロ出力選択回路の数が多い場合に、信号数、ゲート数削減効果が大きくなる。

【0046】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。また、本発明は、RAMマクロ及びメモリBISTを備えた半導体集積回路の故障検出に適用することが可能である。

【符号の説明】

【0047】

100 メモリBIST

110 RAMマクロ入力選択回路

111 RAMマクロ入力選択回路

120 RAMマクロ

121 RAMマクロ

130 RAMマクロ出力選択回路

131 RAMマクロ出力選択回路

140 フリップフロップ

150 パリティチェック回路

151 パリティチェック回路

150a、150b、151a、151b XOR回路

200 BIST入力選択回路

300 選択信号生成回路

310 選択信号生成回路

400 パリティ生成回路

S1、S2 入力信号

S100 マクロ試験データ信号

S120 出力信号

S121 出力信号

S140、S141 出力信号

S300 選択信号

S310 選択信号

S400 パリティ信号

【技術分野】

【0001】

本発明は故障検出回路に関する。

【背景技術】

【0002】

RAMマクロを有する故障検出回路において、一般に、フリップフロップ間のロジックの検査はスキャンテストにより行われ、RAMマクロの検査はメモリBIST(build-in self-test)により行われる。

【0003】

図5は、関連する故障検出回路のブロック図である。図5に示す故障検出回路は、メモリBIST100と、RAMマクロ入力選択回路110、111と、RAMマクロ120、121と、RAMマクロ出力選択回路130、131と、フリップフロップ(FF)140、141と、BIST入力選択回路200と、を備えている。

【0004】

RAMマクロ入力選択回路110は、メモリBIST100で生成され出力されたRAMマクロ試験データ信号S100と、外部機器から出力された信号S1を入力し、いずれか選択した信号をRAMマクロ120に出力する。同様に、RAMマクロ入力選択回路111は、RAMマクロ試験データ信号S100と、外部機器から出力された信号S2を入力し、いずれか選択した信号をRAMマクロ121に出力する。

RAMマクロ120、121から、それぞれ出力信号S120、S121が、BIST入力選択回路200に出力される。BIST入力選択回路200は、検査を行いたいRAMマクロに応じて、入力された信号をメモリBIST100に選択的に出力する。例えば、RAMマクロ120の検査を行いたい場合には、BIST入力選択回路200は、出力信号S120をメモリBISTに出力する。

メモリBIST100は、BIST入力選択回路200から入力された信号と、RAMマクロ試験データ信号S100との比較を行うことにより、選択したRAMマクロの故障検出を行う。

【0005】

ここで、RAMマクロ出力選択回路130、131は、RAMマクロ120、121の出力に直接接続されている。この場合、RAMマクロ出力選択回路130、131では、スキャンテスト及びメモリBISTによるテストを行うことができない。そこで、RAMマクロ出力選択回路130、131では、機能テストパターンを多数作成し、これらのパターンをテスター上で実行することにより、故障の検出を行っている。

【0006】

特許文献1では、メモリBISTを用いてRAMマクロ出力ロジックのテストを行う技術が開示されている。図6は、特許文献1に開示された技術について、複数のRAMマクロ及びRAMマクロ出力回路がメモリ出力選択回路により構成されている場合のブロック図である。

【0007】

RAMマクロ入力選択回路110は、メモリBIST100で生成され出力されたRAMマクロ試験データ信号S100と、外部機器から出力された信号S1を入力し、いずれか選択した信号をRAMマクロ120に出力する。同様に、RAMマクロ入力選択回路111は、RAMマクロ試験データ信号S100と、外部機器から出力された信号S2を入力し、いずれか選択した信号をRAMマクロ121に出力する。

RAMマクロ120、121から、それぞれ出力信号S120、S121が、BIST入力選択回路200に出力される。BIST入力選択回路200は、検査を行いたいRAMマクロに応じて、入力された信号をメモリBIST100に選択的に出力する。例えば、RAMマクロ120の検査を行いたい場合には、BIST入力選択回路200は、出力信号S120をメモリBISTに出力する。

メモリBIST100は、BIST入力選択回路200から入力された信号と、RAMマクロ試験データ信号S100との比較を行うことにより、選択したRAMマクロの故障検出を行う。

【0008】

RAMマクロ出力選択回路130は、RAMマクロ120、121から出力された出力信号S120、S121を入力する。また選択信号生成回路300は、選択信号S300を、RAMマクロ出力選択回路130に出力する。RAMマクロ出力選択回路130は、選択信号S300に基づいて、出力信号S120、S121のいずれかを選択し、FF140に信号を出力する。また同様にして、RAMマクロ出力選択回路131は、FF141に信号を出力する。

FF140、141から、それぞれ出力信号S140、S141が、BIST入力選択回路200に出力される。BIST入力選択回路200は、検査を行いたいRAMマクロ出力選択回路に応じて、入力された信号をメモリBIST100に選択的に出力する。例えば、RAMマクロ出力選択回路130の検査を行いたい場合には、BIST入力選択回路200は、出力信号S140をメモリBISTに出力する。

【0009】

これによると、RAMマクロ出力選択回路の出力をメモリBISTに接続し、メモリBISTにおいて期待値比較を行うことで、RAMマクロ出力選択回路のテストを行うことができる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2004−334933号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、特許文献1にかかる回路では、RAMマクロおよびRAMマクロ出力ロジックを検査する際に、RAMマクロ出力とRAMマクロ出力回路とを選択する回路が必要となる。このとき、RAMマクロのビット幅が大きい場合やRAMマクロの数が多い場合には、選択回路のゲート量及び配線数が増加し、回路の収容性が悪化する。さらに、RAMマクロのテストとRAMマクロ出力回路のテストは同時に行うことができないため、テスト時間が増大する。

また、図5に示す回路のように、機能テストパターンを用いる検査方法では、テストパターン作成コスト及びテスト時間増大によりテストのコストが増加するという問題がある。

本発明は、このような問題点を解決するためになされたものであり、RAMマクロ出力回路のテストを効率良く行うことができる故障検出回路を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明にかかる故障検出回路は、メモリBISTと、前記メモリBISTの出力信号である第1の出力信号を入力し当該第1の出力信号を選択する複数のRAMマクロ入力選択回路と、前記複数のRAMマクロ入力選択回路で選択された前記第1の出力信号をそれぞれ入力する複数のRAMマクロと、前記RAMマクロの出力信号である第2の出力信号を入力し、当該第2の出力信号のうちのいずれかを選択し前記メモリBISTに出力するBIST入力選択回路と、前記RAMマクロから出力された前記第2の出力信号のうちのいずれかを選択するRAMマクロ出力選択回路と、前記RAMマクロ出力選択回路で選択された前記第2の出力信号を保持するフリップフロップと、前記メモリBISTの出力信号からパリティ信号を生成するパリティ生成回路と、前記パリティ生成回路から出力されたパリティ信号と前記フリップフロップが保持している前記第2の出力信号のパリティチェックを行うパリティチェック回路と、を備える。

【発明の効果】

【0013】

メモリBISTによりRAMマクロの故障を検出する故障検出回路において、RAMマクロ出力回路のテストを効率良く行うことができる。

【図面の簡単な説明】

【0014】

【図1】実施の形態1にかかる故障検出回路のブロック図である。

【図2】実施の形態1にかかる故障検出回路のブロック図である。

【図3】実施の形態1にかかるパリティチェック回路のブロック図である。

【図4】実施の形態1にかかる選択信号生成回路の動作を示す図である。

【図5】関連する故障検出回路のブロック図である。

【図6】関連する故障検出回路のブロック図である。

【発明を実施するための形態】

【0015】

実施の形態1.

以下、図面を参照して本発明の実施の形態について説明する。図1は、本実施の形態にかかる故障検出回路のブロック図である。

【0016】

故障検出回路は、メモリBIST100と、RAMマクロ入力選択回路110、111と、RAMマクロ120、121と、RAMマクロ出力選択回路130、131と、フリップフロップ(FF)140、141と、パリティチェック回路150、151と、BIST入力選択回路200と、パリティ生成回路400と、を備えている。

【0017】

メモリBIST100は、RAMマクロ試験データ信号S100(第1の出力信号)を生成する。また、メモリBIST100は、RAMマクロ入力選択回路110、111及びパリティ生成回路400と接続されている。メモリBIST100は、RAMマクロ入力選択回路110、111及びパリティ生成回路400に対して、RAMマクロ試験データ信号S100を出力する。

【0018】

パリティ生成回路400には、RAMマクロ試験データ信号S100が入力される。また、パリティ生成回路400は、RAMマクロ試験データ信号S100に基づくパリティ信号S400を生成して、パリティチェック回路150、151に出力する。

【0019】

RAMマクロ入力選択回路110、111には、RAMマクロ試験データ信号S100が入力される。また、RAMマクロ入力選択回路110、111は、外部機器(図示せず)と接続されている。RAMマクロ入力選択回路110には外部機器から信号S1(第3の出力信号)が入力され、RAMマクロ入力選択回路111には外部機器から信号S2(第3の出力信号)が入力される。

RAMマクロ入力選択回路110の出力は、RAMマクロ120と接続されている。RAMマクロ入力選択回路110で選択された信号はRAMマクロ120に出力される。同様に、RAMマクロ入力選択回路111の出力は、RAMマクロ121と接続されている。RAMマクロ入力選択回路111で選択された信号は、RAMマクロ121に出力される。

【0020】

RAMマクロ120、121には、それぞれRAMマクロ入力選択回路110、111で選択された信号が入力される。また、RAMマクロ120の出力は、RAMマクロ出力選択回路130、131及びBIST入力選択回路200と接続されている。RAMマクロ120は、RAMマクロ出力選択回路130、131及びBIST入力選択回路200に出力信号S120(第2の出力信号)を出力する。同様に、RAMマクロ121の出力は、RAMマクロ出力選択回路130、131及びBIST入力選択回路200と接続されている。RAMマクロ121は、RAMマクロ出力選択回路130、131及びBIST入力選択回路200に出力信号S121(第2の出力信号)を出力する。

【0021】

BIST入力選択回路200には、出力信号S120、S121が入力される。また、BIST入力選択回路200の出力は、メモリBIST100と接続されている。BIST入力選択回路200は、選択したデータを、メモリBIST100に出力する。

【0022】

RAMマクロ出力選択回路130には、出力信号S120、S121が入力される。また、RAMマクロ出力選択回路130の出力は、フリップフロップ140と接続されている。RAMマクロ出力選択回路130は、選択したデータを、パリティチェック回路150に出力する。同様に、出力信号S120、S121が入力されたRAMマクロ出力選択回路131は、データをパリティチェック回路151に出力する。

【0023】

図3は、本実施の形態にかかるパリティチェック回路のブロック図である。パリティチェック回路150は、XOR回路150aと、XOR回路150bと、を備えている。

【0024】

XOR回路150aの入力は、フリップフロップ140の出力と接続されている。XOR回路150aには、フリップフロップ140から信号が入力される。XOR回路150aは、XOR回路150aにおける演算(排他的論理和)の結果を出力する。

【0025】

XOR回路150bの一方の入力は、XOR回路150aの出力と接続されている。XOR回路150bには、XOR回路150aによる演算結果が入力される。また、XOR回路150bの他方の入力は、パリティ生成回路400の出力と接続されている。XOR回路150bには、パリティ信号S400が入力される。XOR回路150bは、XOR回路150bにおける演算(排他的論理和)の結果を出力する。

なお、パリティチェック回路151もパリティチェック回路150と同様に構成することができる。

【0026】

すなわちパリティチェック回路150は、通常動作時のパリティチェック回路に、テスト動作時のパリティチェックによるRAMマクロ出力選択回路130の故障検出回路を付加した場合の構成例である。

【0027】

図2は、図1にかかる故障検出回路に、選択信号生成回路310をさらに備えた故障検出回路のブロック図である。本実施の形態では図2に示すように、選択信号生成回路310を備えていてもよい。

【0028】

選択信号生成回路310の出力は、RAMマクロ出力選択回路130、131と接続されている。選択信号生成回路310は、選択信号生成回路310で生成した選択信号S310を、RAMマクロ出力選択回路130、131に出力する。

【0029】

以上詳細に実施の形態の構成を述べたが、メモリBIST100は、当業者にとってよく知られており、また本発明とは直接関係しないので、その詳細な構成は省略する。

なお、上記説明での構成例は一例であり、RAMマクロ入力選択回路の個数、RAMマクロの個数、RAMマクロ出力選択回路の個数、フリップフロップの個数及びパリティチェック回路の個数は限定されない。

【0030】

次に、本実施の形態に係る故障検出回路の動作について説明する。

【0031】

故障検出回路は、メモリBIST100で生成したデータを用いるテスト動作モードと、メモリBIST100で生成したデータを用いない通常動作モードで動作する。

【0032】

メモリBIST100は、RAMマクロ試験データ信号S100を生成して出力する。

【0033】

RAMマクロ入力選択回路110には、メモリBIST100で生成されたRAMマクロ試験データ信号S100と、外部機器から出力された信号S1が入力される。RAMマクロ入力選択回路110は、動作モードに基づいて、いずれの入力信号を用いるかを選択する。すなわちRAMマクロ入力選択回路110は、テスト動作モードの場合にはRAMマクロ試験データ信号S100を選択し、通常動作モードの場合には信号S1を選択する。RAMマクロ入力選択回路110は、選択した信号に応じた書きこみデータをRAMマクロ120に出力する。

同様に、RAMマクロ入力選択回路111は、メモリBIST100で生成されたRAMマクロ試験データ信号S100と、外部機器から出力された信号S2の、いずれの信号を用いるか選択し、選択した信号に応じた書き込みデータをRAMマクロ121に出力する。

【0034】

RAMマクロ120は、入力された書き込みデータに応じて、出力信号S120を出力する。同様にRAMマクロ121は、出力信号S121を出力する。

【0035】

出力信号S120は、RAMマクロ出力選択回路130、131に入力される。同様に出力信号S121は、RAMマクロ出力選択回路130、131に入力される。

RAMマクロ出力選択回路130は、出力信号S120、S121から信号を選択し、選択した信号をFF140に格納する。同様に、RAMマクロ出力選択回路131は、出力信号S120、S121から信号を選択し、選択した信号をFF141に格納する。

【0036】

ここで図2に示したように、本実施の形態にかかる故障検出回路は、例えば選択信号生成回路310を備えていてもよい。選択信号生成回路310は、RAMマクロ出力選択回路130、131を制御するための手段である。選択信号生成回路310は選択信号S310を、RAMマクロ出力選択回路130、131に出力する。

図4は、選択信号生成回路310の動作を示す図である。選択信号生成回路310は、通常動作モードを選択する場合には通常動作時選択信号を送出する。テスト動作モードであって、RAMマクロ120を選択する場合には、RAMマクロ120選択信号を送出し、RAMマクロ121を選択する場合には、RAMマクロ121選択信号を送出する。すなわち、RAMマクロ出力選択回路130、131は、選択信号S310に応じて、RAMマクロ120、121のいずれかの出力信号S120、S121を選択するかを決定し、信号をそれぞれFF140、141に出力する。

【0037】

FF140に格納されたデータは、パリティチェック回路150に入力される。また同様に、FF141に格納されたデータは、パリティチェック回路151に入力される。

【0038】

また、パリティ生成回路400には、メモリBIST100から出力されたRAMマクロ試験データ信号S100が入力され、パリティ信号S400を生成する。パリティ生成回路400は生成したパリティ信号S400を、パリティチェック回路150、151に出力する。

【0039】

ここで図3に示すように、パリティチェック回路150は、XOR回路150aとXOR回路150bを備えている。

ここで、XOR150aは通常動作モードにおける故障検出回路である。XOR150aは、FF140から出力された複数のデータに対して演算を行い、演算結果を出力する。演算は、例えば入力されたデータのそれぞれのパリティビットについて行われる。XOR回路150aの出力は、偶数パリティの場合、RAMマクロ出力選択回路130やFF140が故障していると"1"になり、これにより故障を検出する。

【0040】

XOR150bは、テスト動作モードにおける故障検出回路である。XOR150bは、RAMマクロ試験データ信号S100のパリティであるパリティ信号S400と、XOR150aの出力信号を入力して演算を行い、演算結果を出力する。これによりXOR150bは、RAMマクロ出力選択回路130やFF140の故障検出をおこなう。

パリティチェック回路151は、パリティチェック回路150と同様に動作し、RAMマクロ出力選択回路131やFF141の故障検出を行う。

【0041】

すなわち、通常動作モードにおいて、外部機器からRAMマクロ入力選択回路110に入力された信号S1は、RAMマクロ120に出力される。次に、RAMマクロ120から出力された出力信号S120は、RAMマクロ出力選択回路130及びFF140を介して、パリティチェック回路150に入力される。パリティチェック回路150のXOR回路150aは、FF140から出力された複数のデータについて演算を行い、データのチェックを行う。

同様にして、出力信号S120はRAMマクロ出力選択回路131及びFF141を介して、パリティチェック回路151に入力される。パリティチェック回路151は、XOR(排他的論理和)の演算を行う。また、外部機器からRAMマクロ入力選択回路111に入力された信号S2を用い、RAMマクロ121から出力された信号について、パリティチェック回路150、151において演算を行うことができる。

これにより、通常動作モードにおいて、RAMマクロ120、121及びRAMマクロ出力選択回路130、131の故障検出を行うことができる。

【0042】

また、テスト動作モードにおいて、メモリBIST100から出力され、RAMマクロ入力選択回路110に入力されたRAMマクロ試験データ信号S100は、RAMマクロ120に出力される。次に、RAMマクロ120から出力された出力信号S120は、RAMマクロ出力選択回路130及びFF140を介して、パリティチェック回路150に入力される。パリティチェック回路150のXOR回路150aは、FF140から出力された複数のデータについて演算を行う。この出力を第1の入力信号として、XOR回路150bに出力する。また、メモリBIST100から出力されたRAMマクロ試験データ信号S100は、パリティ生成回路400に入力され、パリティ生成回路400はパリティ信号S400をパリティチェック回路150に出力する。このパリティ信号S400を第2の入力信号としてXOR回路150bは演算を行い、データのチェックを行う。

同様にして、出力信号S120はRAMマクロ出力選択回路131及びFF141を介して、パリティチェック回路151に入力される。パリティチェック回路151は、パリティチェック回路150と同様に動作し、データのチェックを行う。

なお、RAMマクロ入力選択回路110及びRAMマクロ120を用いる代わりに、RAMマクロ入力選択回路111及びRAMマクロ121を用い、RAMマクロ121から出力された信号について、処理を行うことができる。

これによりテスト動作モードにおいて、パリティを用いてRAMマクロ出力選択回路130、131の故障検出を行うことができる。

【0043】

ここで、テスト動作モードにおいて、RAMマクロ120、121から出力された出力信号S120、S121は、それぞれBIST入力選択回路200に入力される。BIST入力選択回路200は、テスト対象となる出力信号S120、S121を選択する。例えば、テスト対象がRAMマクロ120の場合には、出力信号S120を選択し、テスト対象がRAMマクロ121の場合には、出力信号S121を選択する。

BIST入力選択回路200で選択された出力信号S120、S121は、メモリBIST100に入力される。メモリBIST100は、入力されたデータとRAMマクロ試験データ信号S100に応じた期待値との比較を行い、RAMマクロ120、121の故障検出を行う。

【0044】

これにより、メモリBIST100を用いてRAMマクロの故障を検出する回路において、メモリBISTから出力されるRAMマクロ試験データ信号S100を用いて、RAMマクロ120、121の出力からFF140、141に至るまでのテストが可能となる。特に、メモリ出力ロジックが複数のRAMマクロを選択する回路において、選択回路のテストを可能にする。

すなわち、メモリBIST100による比較を行うこと無く、RAMマクロ出力選択回路130、131のテストを行うことができる。したがって、メモリBIST100によるRAMマクロ120、121のテストと同時に、RAMマクロ120、121の出力からFF140、141に至るまでの回路のテストをおこなうことができ、テスト時間の短縮が可能となる。

【0045】

また、データそのものではなく、パリティで期待値比較(パリティチェックによる故障検出)をおこなうことができる。これにより、BIST入力選択回路200の信号数の削減が可能になるとともに、BIST入力選択回路200のゲート量も削減可能となる。RAMマクロ数及びマクロ出力選択回路の数が多い場合に、信号数、ゲート数削減効果が大きくなる。

【0046】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。また、本発明は、RAMマクロ及びメモリBISTを備えた半導体集積回路の故障検出に適用することが可能である。

【符号の説明】

【0047】

100 メモリBIST

110 RAMマクロ入力選択回路

111 RAMマクロ入力選択回路

120 RAMマクロ

121 RAMマクロ

130 RAMマクロ出力選択回路

131 RAMマクロ出力選択回路

140 フリップフロップ

150 パリティチェック回路

151 パリティチェック回路

150a、150b、151a、151b XOR回路

200 BIST入力選択回路

300 選択信号生成回路

310 選択信号生成回路

400 パリティ生成回路

S1、S2 入力信号

S100 マクロ試験データ信号

S120 出力信号

S121 出力信号

S140、S141 出力信号

S300 選択信号

S310 選択信号

S400 パリティ信号

【特許請求の範囲】

【請求項1】

メモリBISTと、

前記メモリBISTの出力信号である第1の出力信号を入力し当該第1の出力信号を選択する複数のRAMマクロ入力選択回路と、

選択された前記第1の出力信号をそれぞれ入力する複数のRAMマクロと、

前記RAMマクロの出力信号である第2の出力信号を入力し、当該第2の出力信号のうちのいずれかを選択し前記メモリBISTに出力するBIST入力選択回路と、

前記RAMマクロから出力された前記第2の出力信号のうちのいずれかを選択するRAMマクロ出力選択回路と、

前記RAMマクロ出力選択回路で選択された前記第2の出力信号を保持するフリップフロップと、

前記メモリBISTの出力信号からパリティ信号を生成するパリティ生成回路と、

前記パリティ生成回路から出力されたパリティ信号と前記フリップフロップが保持している前記第2の出力信号のパリティチェックを行うパリティチェック回路と、を備える、

故障検出回路。

【請求項2】

前記パリティチェック回路は、

前記フリップフロップから出力された前記第2の出力信号を入力し、演算結果を出力する第1のXOR回路と、

前記第1のXOR回路の出力信号を第1の入力信号とし、前記パリティ生成回路で生成されたパリティ信号を第2の入力信号として、演算結果を出力する第2のXOR回路と、を備える、請求項1に記載の故障検出回路。

【請求項3】

選択信号生成回路をさらに備え、

前記選択信号生成回路は、前記第2の出力信号が前記RAMマクロ出力選択回路を経て前記フリップフロップに入力されるような制御信号を生成する、請求項1または請求項2に記載の故障検出回路。

【請求項4】

前記BIST入力選択回路は、検査を行いたい前記RAMマクロに応じて、前記第2の出力信号を選択して、前記メモリBISTに信号を出力する、

請求項1乃至請求項3のいずれか一項に記載の故障検出回路。

【請求項5】

前記RAMマクロ入力選択回路は、前記メモリBISTの出力信号である第1の出力信号と、外部機器が出力した第3の出力信号とを入力し、いずれかの信号を前記RAMマクロに出力する、

請求項1乃至請求項4のいずれか一項に記載の故障検出回路。

【請求項6】

前記パリティチェック回路は、前記RAMマクロ入力選択回路において前記メモリBISTの出力信号である第1の出力信号が選択された場合に、前記フリップフロップに格納された複数の第2の出力信号について演算を行った演算結果と、前記パリティ生成回路で生成したパリティ信号との演算を行う、

請求項5に記載の故障検出回路。

【請求項7】

前記パリティチェック回路は、前記RAMマクロ入力選択回路において外部機器が出力した第3の出力信号が選択された場合に、前記フリップフロップに格納された複数の第2の出力信号について演算を行う、

請求項5または請求項6に記載の故障検出回路。

【請求項1】

メモリBISTと、

前記メモリBISTの出力信号である第1の出力信号を入力し当該第1の出力信号を選択する複数のRAMマクロ入力選択回路と、

選択された前記第1の出力信号をそれぞれ入力する複数のRAMマクロと、

前記RAMマクロの出力信号である第2の出力信号を入力し、当該第2の出力信号のうちのいずれかを選択し前記メモリBISTに出力するBIST入力選択回路と、

前記RAMマクロから出力された前記第2の出力信号のうちのいずれかを選択するRAMマクロ出力選択回路と、

前記RAMマクロ出力選択回路で選択された前記第2の出力信号を保持するフリップフロップと、

前記メモリBISTの出力信号からパリティ信号を生成するパリティ生成回路と、

前記パリティ生成回路から出力されたパリティ信号と前記フリップフロップが保持している前記第2の出力信号のパリティチェックを行うパリティチェック回路と、を備える、

故障検出回路。

【請求項2】

前記パリティチェック回路は、

前記フリップフロップから出力された前記第2の出力信号を入力し、演算結果を出力する第1のXOR回路と、

前記第1のXOR回路の出力信号を第1の入力信号とし、前記パリティ生成回路で生成されたパリティ信号を第2の入力信号として、演算結果を出力する第2のXOR回路と、を備える、請求項1に記載の故障検出回路。

【請求項3】

選択信号生成回路をさらに備え、

前記選択信号生成回路は、前記第2の出力信号が前記RAMマクロ出力選択回路を経て前記フリップフロップに入力されるような制御信号を生成する、請求項1または請求項2に記載の故障検出回路。

【請求項4】

前記BIST入力選択回路は、検査を行いたい前記RAMマクロに応じて、前記第2の出力信号を選択して、前記メモリBISTに信号を出力する、

請求項1乃至請求項3のいずれか一項に記載の故障検出回路。

【請求項5】

前記RAMマクロ入力選択回路は、前記メモリBISTの出力信号である第1の出力信号と、外部機器が出力した第3の出力信号とを入力し、いずれかの信号を前記RAMマクロに出力する、

請求項1乃至請求項4のいずれか一項に記載の故障検出回路。

【請求項6】

前記パリティチェック回路は、前記RAMマクロ入力選択回路において前記メモリBISTの出力信号である第1の出力信号が選択された場合に、前記フリップフロップに格納された複数の第2の出力信号について演算を行った演算結果と、前記パリティ生成回路で生成したパリティ信号との演算を行う、

請求項5に記載の故障検出回路。

【請求項7】

前記パリティチェック回路は、前記RAMマクロ入力選択回路において外部機器が出力した第3の出力信号が選択された場合に、前記フリップフロップに格納された複数の第2の出力信号について演算を行う、

請求項5または請求項6に記載の故障検出回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2011−108325(P2011−108325A)

【公開日】平成23年6月2日(2011.6.2)

【国際特許分類】

【出願番号】特願2009−262546(P2009−262546)

【出願日】平成21年11月18日(2009.11.18)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成23年6月2日(2011.6.2)

【国際特許分類】

【出願日】平成21年11月18日(2009.11.18)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]