整流回路

【課題】 外部から入力される高周波電力が小さくても整流効率を高くできる整流回路を得る。

【解決手段】 入力した高周波を通過させ、直流を遮断する第1のフィルタと、前記高周波と同じ周波数の周期電圧が印加される第1の端子、前記第1のフィルタに接続された第2の端子、および接地された第3の端子、を有し、前記高周波を整流するトランジスタと、前記第1のフィルタと前記第2の端子との接続点に接続され、前記高周波を遮断し、前記トランジスタで整流された直流を出力する第2のフィルタと、を備える。

【解決手段】 入力した高周波を通過させ、直流を遮断する第1のフィルタと、前記高周波と同じ周波数の周期電圧が印加される第1の端子、前記第1のフィルタに接続された第2の端子、および接地された第3の端子、を有し、前記高周波を整流するトランジスタと、前記第1のフィルタと前記第2の端子との接続点に接続され、前記高周波を遮断し、前記トランジスタで整流された直流を出力する第2のフィルタと、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、RFID(Radio Frequency IDentification)タグやマイクロ波エネルギー伝送などに用いられ、入力された高周波電力を直流電力に変換する整流回路に関するものである。

【背景技術】

【0002】

高周波、特にマイクロ波帯で用いられる整流回路として、従来から非特許文献1(図1)に示される構成が用いられてきた。これは、ダイオードと低域通過フィルタ、及び直流通過フィルタから構成される整流回路である。図7(a)にダイオードの電流−電圧特性を示す。図中、Vは電圧、Iは電流である。ダイオードは非線形素子であり、ON電圧(Von)を超える順方向電圧に対しては電流を流し(ON状態)、ON電圧より低い逆方向電圧に対しては電流を流さない(OFF状態)。

【0003】

ダイオードに正弦波電圧を印加する場合の電圧波形及び電流波形を、それぞれ図7(b)及び図7(c)に示す。図中、tは時間である。正弦波電圧の振幅がVonを上回る間はダイオードに電流が流れ、Vonを下回る間はダイオードに電流が流れない。この電流波形はダイオードの後段に接続される直流通過フィルタで平滑され、直流電流成分が負荷に供給される。

【0004】

ここで、Vonが低いほどダイオードに電流が流れる時間が長くなるため、直流通過フィルタで平滑される直流電力が高くなる。よって、ダイオードのON電圧が低いほど、整流回路に入力される高周波電力と負荷に供給される直流電力との比である整流効率が高くなる。

【0005】

また、整流回路に入力される高周波電力が大きいほど、整流効率は高くなる。整流回路に入力される高周波電力が小さい場合、Vonが高いとダイオードが常にOFF状態となり(図中、Bの状態)整流動作をしないが、Vonが低いとダイオードがON状態になる時間が生じるため(図中、Aの状態)整流動作を行う。よって、特に小電力の高周波入力に対してはダイオードのON電圧が低いほど整流効率が高くなる。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】T. Yoo and K. Chang, “Theoretical and experimental development of 10 and 35 GHz rectennas,” IEEE Trans. Microwave Theory Tech., vol. 40, pp. 1259-1266, June 1992.

【発明の概要】

【発明が解決しようとする課題】

【0007】

整流回路に用いるダイオードとしては、金属と半導体との接合を利用したショットキーダイオードが一般的である。ショットキーダイオードはON電圧が0.3V程度と小さいため、比較的小電力の高周波入力に対しても高効率に整流することが可能である。

【0008】

しかし、ダイオードを含めた整流回路を例えばSiプロセスにより一体化して小形化・低コスト化を図ろうとした場合、ショットキーダイオードを用いると、金属と半導体を接合するための特別なプロセスが必要となり、コストを低減できない問題がある。

【0009】

一般的なSiプロセスで製造可能なダイオードとして、ダイオード接続したMOS(Metal Oxide Semiconductor)トランジスタがある。これはMOSトランジスタのゲート端子とドレイン端子を接続したものであり、ドレイン端子からソース端子へ順方向電流が流れ、逆方向には電流を流さないというダイオードの特性を呈する。

【0010】

しかし、ダイオード接続したMOSトランジスタのON電圧は、0.7V程度とショットキーダイオードより高いため、小電力の高周波入力に対して整流効率が低いという問題がある。

【0011】

この発明は上記のような課題を解決するためになされたもので、小電力からの広い入力電力の範囲で高効率動作を行うことが可能な整流回路を得ることを目的とする。

【課題を解決するための手段】

【0012】

この発明に係る整流回路は、

入力した高周波を通過させ、直流を遮断する第1のフィルタと、

前記高周波と同じ周波数の周期電圧が印加される第1の端子、前記第1のフィルタに接続された第2の端子、および接地された第3の端子、を有し、前記高周波を整流するトランジスタと、

前記第1のフィルタと前記第2の端子との接続点に接続され、前記高周波を遮断し、前記トランジスタで整流された直流を出力する第2のフィルタと、

を備えたことを特徴とするものである。

【発明の効果】

【0013】

この発明によれば、外部から入力され直流に変換される高周波をトランジスタに入力し、このトランジスタをON、OFFするための高周波をトランジスタの第1の端子に印加しているため、特に外部から入力される高周波電力が小さくても整流効率を高くできるという効果がある。

【図面の簡単な説明】

【0014】

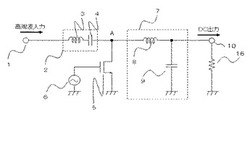

【図1】この発明の実施の形態1による整流回路を示す構成図である。

【図2】高周波入力電力と整流効率との関係を示す図である。

【図3】この発明の実施の形態2による整流回路を示す構成図である。

【図4】この発明の実施の形態2による整流回路の変形例を示す構成図である。

【図5】この発明の実施の形態2による整流回路の変形例を示す構成図である。

【図6】この発明の実施の形態3による整流回路を示す構成図である。

【図7】従来例の動作を説明する説明図である。

【発明を実施するための形態】

【0015】

実施の形態1.

図1は、この発明の実施の形態1による整流回路を示す構成図である。なお、各図において、同一符号は同一または相当部分を示す。図1中、1は入力端子、2は第1のフィルタである帯域通過フィルタ、3はインダクタ、4はキャパシタ、5はトランジスタであるMOS(Metal Oxide Semiconductor)トランジスタ、6は信号源、7は第2のフィルタである低域通過フィルタ、8はインダクタ、9はキャパシタ、10は出力端子、16は負荷抵抗である。

【0016】

入力端子1には高周波が入力される。帯域通過フィルタ2は、入力端子1から入力された高周波を通過し、他の周波数の波の通過を阻止する。図1では、帯域通過フィルタ2をインダクタ3とキャパシタ4を直列接続した直列共振器で構成しているが、同等の特性が得られれば他の構成でも良い。図1に示す帯域通過フィルタ2を用いる場合、入力する高周波の周波数で直列共振するようにインダクタ3及びキャパシタ4の値を決めることで、高周波の通過及び他の周波数の遮断が実現される。

【0017】

MOSトランジスタ5は、第1の端子であるゲート端子、第2の端子であるドレイン端子、第3の端子であるソース端子の3つの端子を有し、高周波の波形を整流する非線形素子である。MOSトランジスタ5のゲート端子には信号源6で生成した周期電圧が印加される。MOSトランジスタ5のドレイン端子は、帯域通過フィルタ2と図中Aで示す接続点において接続される。MOSトランジスタ5のソース端子は接地されている。

【0018】

図1に示すMOSトランジスタ5はNチャネルのMOSトランジスタであり、ゲート端子に閾値電圧を越える正の電圧が印加される場合はドレイン−ソース間に電流が流れ(ON状態)、ゲート端子に印加される電圧が閾値電圧を下回る場合はドレイン−ソース間に電流が流れない(OFF状態)。したがって、ダイオードと同様に整流動作を行うことができる。MOSトランジスタ5により整流された電流波形は、直流成分である直流電流と入力される高周波の周波数成分及びその高調波の成分を含んでいる。

【0019】

信号源6は、入力端子1から入力される高周波に同期した同じ周波数の正弦波の周期電圧を発生し、この周期電圧をMOSトランジスタ5のゲート端子に印加する。

【0020】

低域通過フィルタ7は、帯域通過フィルタ2とMOSトランジスタ5のドレイン端子との接続点(図中A点)に接続されている。低域通過フィルタ7は、MOSトランジスタ5により整流された電流波形を平滑し直流成分のみを出力端子10に出力し、負荷抵抗16に供給するとともに、直流以外の高周波の通過を阻止する。図1では、低域通過フィルタ7を直列接続されたインダクタ8と並列接続されたキャパシタ9とから構成しているが、同等の特性が得られれば他の構成でも良い。図1に示すような低域通過フィルタ7を用いる場合は、その遮断周波数を入力端子1から入力される高周波の周波数よりも低く設定することで、直流以外の高周波の遮断が実現される。

【0021】

次に、より詳細な動作について説明する。

入力端子1に入力された高周波は帯域通過フィルタ2を通過し、その電圧がMOSトランジスタ5のドレイン端子に印加される。低域通過フィルタ7は高周波に対してはハイインピーダンスとなるため、高周波は低域通過フィルタ7で遮断され、負荷抵抗16へは通過しない。

【0022】

一方、MOSトランジスタ5のゲート端子には、信号源6から、入力端子1に入力された高周波に同期した同じ周波数の正弦波の周期電圧が印加される。この周期電圧をMOSトランジスタ5の閾値電圧を上回る振幅でゲート端子に印加することにより、ゲート端子に印加される周期電圧がMOSトランジスタ5の閾値電圧を上回るほぼ半周期の時間ではMOSトランジスタ5はON状態となり、閾値電圧を下回るほぼ半周期の時間ではMOSトランジスタ5はOFF状態となる。

【0023】

ここで、信号源6からMOSトランジスタ5のゲート端子に印加される正弦波電圧の位相を、入力端子1から入力され帯域通過フィルタ2を介してMOSトランジスタ5のドレイン端子に印加される高周波の位相と同相になるように同期すれば、ゲート端子に印加される電圧が閾値電圧を上回り、MOSトランジスタ5がON状態となる間はドレイン端子からソース端子に電流が流れ、MOSトランジスタ5がOFF状態となる間は電流が流れない。したがって、MOSトランジスタ5のドレイン端子に印加する高周波の電圧が正となるほぼ半周期の時間のみ電流が流れ、整流を行うことができる。

【0024】

あるいは、信号源6からMOSトランジスタ5のゲート端子に印加される正弦波の位相を、入力端子1から入力され帯域通過フィルタ2を介してMOSトランジスタ5のドレイン端子に印加される高周波の位相と逆相になるように同期しても良い。この場合、ゲート端子に印加される電圧が閾値電圧を上回り、MOSトランジスタ5がON状態となる間はソース端子からドレイン端子に電流が流れ、MOSトランジスタ5がOFF状態となる間は電流が流れない。したがって、MOSトランジスタ5のドレイン端子に印加する高周波の電圧が負となるほぼ半周期の時間のみ電流が流れ、やはり整流を行うことができる。

【0025】

このようにして、入力端子1に入力された高周波がMOSトランジスタ5により整流される。

【0026】

MOSトランジスタ5により整流された電流波形は、直流成分と入力される高周波成分及びその高調波成分を含む。このうち、低域通過フィルタ7は直流成分のみを出力端子10に通過し、この直流成分の電力を負荷抵抗16に供給する。

【0027】

この直流成分は、帯域通過フィルタ2では遮断されるため、入力端子1に戻ることはない。帯域通過フィルタ2の代わりに高域通過フィルタを用い、入力された高周波成分は通過し直流成分は遮断するようすることもできる。ただし、高調波成分も遮断して、入力端子1に戻さないという点では、高周波成分のみを通過し直流成分と高調波成分を遮断する帯域通過フィルタ2を用いることがより望ましい。

【0028】

図2に、高周波の入力電力と整流効率との関係を示す。図2の横軸は高周波の入力電力、縦軸は整流回路の整流効率である。図2において、点線はダイオード接続されたMOSトランジスタを用いる場合、実線は図1の構成を用いる場合、それぞれの整流効率曲線を示している。

【0029】

MOSトランジスタをダイオード接続してダイオードとして用いる場合は、入力端子1から入力される高周波の電圧自身でダイオードをスイッチングしていることと等価である。このとき、高周波入力電力が大きくダイオードをスイッチングするのに十分な電圧振幅が印加されている場合は、Vonを上回る時間が長いため比較的整流効率が高い。しかし、高周波入力電力が低くなるにしたがって、ダイオードに印加される電圧振幅が小さくなり、Vonを上回る時間が短くなるため整流効率が低くなる。さらに高周波の電圧振幅がVonよりも低くなると、ダイオードがスイッチング動作しなくなるため整流効率が0となる。

【0030】

一方、本実施の形態の図1の構成を用いる場合は、高周波の入力電力の値に関わらず、MOSトランジスタ5は信号源6からゲート端子に印加される正弦波の周期電圧が正の半周期の時間でON状態、負の半周期の時間でOFF状態となる。そのため、高周波入力電力が低い場合においても整流動作が起こり、高周波電力から直流電力への変換効率、すなわち整流効率が高くなるという利点を有する。このため、図2の実線に示すように、ダイオード接続されたMOSトランジスタを用いる場合に比べ、整流効率を高くすることができ、特に入力電力が小さいときに整流効率を高くすることができる。

【0031】

なお、図1の構成では、外部からの高周波入力とは別に信号源6が必要となるが、MOSトランジスタ5のゲート端子はハイインピーダンスであるため、信号源6から出力される正弦波の周期電圧は小さくて良く、信号源6の電力消費は小さくて済む。

【0032】

図1では、信号源6から正弦波を出力するとして説明したが、代わりに矩形波を出力して周期電圧としても良い。矩形波は正弦波より立ち上がり時間及び立下り時間が短いため、MOSトランジスタ5のON状態、OFF状態が瞬時に切り替わり、理想の整流動作に近づくことから、正弦波入力と比べて整流効率がさらに高くなるという利点を有する。

【0033】

なお、本実施の形態においては、非線形素子としてNチャネルのMOSトランジスタ5を用いる構成を示したが、本発明はこれに限らず、非線形素子としてPチャネルのMOSトランジスタを用いてもよい。この場合には、ゲート端子に印加される周期電圧が、ある閾値電圧より低くなったときに、トランジスタがON状態となりドレイン端子とソース端子間に電流が流れる。また、ゲート端子に印加される電圧がこの閾値電圧より高くなったときに、トランジスタがOFF状態になりドレイン端子とソース端子間の電流が流れなくなる。したがって、この場合でも同様に整流動作が行え、整流効率を高くできるという本実施の形態の効果が得られる。

【0034】

また、本実施の形態では、MOSトランジスタ5のソース端子を接地し、ドレイン端子側に高周波電力を印加する構成としたが、ソース端子とドレイン端子は逆に接続してもよく、すなわち第2の端子と第3の端子を入れ替えてもよい。この場合もスイッチング動作が同様に行われ、本実施の形態の効果が得られる。

【0035】

加えて、本実施の形態では、非線形素子として電界効果トランジスタ(FET)の一種であるMOSトランジスタ5を用いたが、これに限らず、他の種類の電界効果トランジスタを用いることもでき、Nチャネル、Pチャネルのどちらのものも用いることができる。さらに、電界効果トランジスタでなくても、バイポーラトランジスタを用いることもできる。いずれの種類のトランジスタでも、Siプロセスにより他の回路と一体化できるトランジスタを用いることがより望ましいが、必ずしもこれに限るものではない。なお、バイポーラトランジスタを用いる場合は、ゲート端子、ドレイン端子、ソース端子のそれぞれに対応する端子として、ベース端子、コレクタ端子、エミッタ端子を用いれば良く、コレクタ端子とエミッタ端子の接続を入れ替えてもよい。バイポーラトランジスタはNPN型、PNP型のいずれのものも使用することができ、本実施の形態の効果を同様に得ることができる。

【0036】

さらに、本実施の形態では、MOSトランジスタ5のゲート端子に印加する周期電圧を、信号源6を用いて発生する構成を示したが、本発明はこれに限らず、入力端子1に入力された高周波と同期した同じ周波数の周期電圧がトランジスタのゲート端子に印加されれば良く、必ずしも信号源6を設ける必要はない。例えば、ゲート端子に印加する周期電圧の周波数情報や位相情報を、入力端子1に入力する高周波を生成する図示していない装置から供給するなどすることもできる。

【0037】

以上のように、本実施の形態に示した整流回路では、整流効率を高くできるという効果を奏し、Siプロセスを用いればさらにコストを低くできるという効果を奏する。

【0038】

実施の形態2.

図3は、この発明の実施の形態2による整流回路を示す構成図である。これは、信号源6を用いる代わりに、高周波入力の一部を用いてMOSトランジスタ5をスイッチングする構成である。図3において、図1と同一符号は同一または相当部分を示すので説明を省略する。11は分配手段である電力分配器、12は昇圧手段である変成器、13は移相手段である移相器である。

【0039】

図3において、電力分配器11は、入力端子1から入力され帯域通過フィルタ2を介して伝送される高周波電力を第1の高周波と第2の高周波2つに分配する。第1の高周波は図中点Aを通過し、MOSトランジスタ5のドレイン端子に印加する。第2の高周波は変成器12に入力する。変成器12は、電力分配器11から出力された第2の高周波の電圧を昇圧する。移相器13は、変成器12から出力される高周波電圧の位相をシフトして周期電圧としてMOSトランジスタ5のゲート端子に印加する。

【0040】

次に動作について説明する。

入力端子1から入力され、帯域通過フィルタ2を介して伝送される高周波電力は電力分配器11により、2つに分配される。電力分配器11により分配される第1の高周波は、その電圧がMOSトランジスタ5のドレイン端子に印加される。高周波電力は、低域通過フィルタ7が高周波に対してはハイインピーダンスとなるため、出力端子10や負荷抵抗16へは通過しない。

【0041】

電力分配器11により分配される第2の高周波の出力は変成器12に入力する。この高周波は、変成器12で昇圧され移相器13を介してMOSトランジスタ5のゲート端子に印加される。

【0042】

昇圧された高周波の電圧振幅がMOSトランジスタ5の閾値電圧を超えると、MOSトランジスタ5はスイッチング動作をする。すなわち、正弦波電圧がMOSトランジスタ5の閾値を上回る正の半周期の時間ではMOSトランジスタ5はON状態となり、正弦波電圧がMOSトランジスタ5の閾値を下回る負の半周期の時間ではMOSトランジスタ5はOFF状態となる。

【0043】

電力分配器11の2つの出力に位相差がなく、また変成器12を通過することによる位相の変化がない場合は、MOSトランジスタ5のドレイン端子及びゲート端子に印加される電圧は同相、すなわち位相差が0度となる。そのため、MOSトランジスタ5がON状態のとき高周波入力の正の半周期の電圧がドレイン端子に印加され、ドレイン端子からソース端子に電流が流れる。MOSトランジスタ5がOFF状態のとき高周波入力の負の半周期の電圧がドレイン端子に印加されるが、ドレイン端子とソース端子の間に電流は流れない。

【0044】

電力分配器11の2つの出力に位相差があったとしても、変成器12を通過することなどによる位相の変化が、これを打ち消すような場合は、同様に、MOSトランジスタ5のドレイン端子及びゲート端子に印加される電圧の位相差が0度となる。いずれにしても、MOSトランジスタ5による整流動作が行われる。

【0045】

一方、電力分配器11の2つの出力に位相差が生じ、また変成器12を通過する高周波の位相が変化するなどし、MOSトランジスタ5のドレイン端子及びゲート端子に印加される電圧が逆相、すなわち位相差が180度となる場合、MOSトランジスタ5がON状態のとき高周波入力の負の半周期の電圧がドレイン端子に印加され、ソース端子からドレイン端子に電流が流れる。MOSトランジスタ5がOFF状態のとき電流は流れない。

【0046】

このようにして、入力端子1に入力された高周波がMOSトランジスタ5により整流される。

【0047】

MOSトランジスタ5により整流された波形は、直流成分と入力される高周波の成分及びその高調波成分を含む。このうち、低域通過フィルタ7は直流成分のみを通過し、出力端子10及び負荷抵抗16に供給する。

【0048】

図3の構成では、入力端子1から入力される高周波の電力が小さい場合においても、変成器12で高周波の電圧が昇圧されるため、この電圧をMOSトランジスタ5のゲート端子に印加することで、MOSトランジスタ5はスイッチング動作を行い整流動作が起こる。そのため、高周波入力電力が低い場合においても高周波電力から直流電力への変換効率が高くなるという利点を有する。

【0049】

また、入力端子1に入力した高周波を電力分配器11で分配し周期電圧としているため、入力した高周波に同期した同じ周波数の周期電圧を容易に作ることができるという利点を有する。

【0050】

よって、図3に示す構成とすることで、信号源6を用いることなく広い入力電力範囲において高い整流効率で整流動作を行うことが可能となる。

【0051】

電力分配器11の2つの出力に位相差があるか、あるいは変成器12を通過することによる位相の変化が生じ、MOSトランジスタ5のドレイン端子とゲート端子に印加される電圧に0度や180度以外の位相のずれが生じる場合は、MOSトランジスタ5がONとなる時間の一部はドレイン端子からソース端子に電流が流れるが、残りの時間は逆にソース端子からドレイン端子に電流が流れるようになる。このため、直流通過フィルタ7で平滑され負荷抵抗16に供給される直流成分の値が低くなり、整流効率が劣化する。

【0052】

そこで、図3に示すように、変成器12とMOSトランジスタ5のドレイン端子の間に移相器13を挿入し、この移相器13により高周波の位相をシフトしてMOSトランジスタ5のドレイン端子とゲート端子に印加される周期電圧を同相にするか逆相にすることで、MOSトランジスタ5がON状態となる間は常にドレイン端子からソース端子、あるいはソース端子からドレイン端子に電流が流れるようにすることができる。そのため、整流効率の劣化を抑制でき、より変換効率の高い整流回路が得られる。

【0053】

変成器12はコイルを用いたトランスなど、種々の回路で構成することができる。また図3では、変成器12を用いて昇圧したが、代わりに増幅器などを用いて昇圧しても良い。

【0054】

なお、図3では、電力分配器11を帯域通過フィルタ2と接続点Aとの間に挿入しているが、電力分配器11を入力端子1と帯域通過フィルタ2との間に挿入してもよい。

【0055】

さらに、図3では、移相器13を変成器12とMOSトランジスタ5のゲート端子との間に接続したが、図4に示すように電力分配器11と図中接続点Aの間に接続しても良く、また図5に示すように図中接続点AとMOSトランジスタ5のドレイン端子の間に接続しても良い。また、移相器13を分配器11と変成器12の間等に接続することもでき、いずれの場合もドレイン端子に印加する高周波とゲート端子に印加する周期電圧との位相差を調整することができるので、本実施の形態の効果を得ることができる。

【0056】

実施の形態3.

図6は、この発明の実施の形態3による整流回路を示す構成図である。図6において、図1及び図3〜図5と同一符号は同一または相当部分を示すので説明を省略する。14は直流電圧印加手段である直流電源、15はキャパシタである。直流電源14は、所定の電圧をMOSトランジスタ5のゲート端子に印加する。キャパシタ15は、直流電源14の電圧が移相器13に印加されないようにDCカットしている。

【0057】

次に動作について説明する。

直流電源14から供給される所定の電圧はMOSトランジスタ5のゲート端子の閾値電圧に近い値としている。このため、直流電源14とキャパシタ15を用いることにより、MOSトランジスタ5のゲート端子には常に閾値電圧に近い値の電圧が印加されている。よって、入力端子1から帯域通過フィルタ2、電力分配器11、変成器12、及び移相器13を介してゲート端子に印加される高周波の周期電圧は、直流電源14で与えられる電圧に重畳して、ゲート端子に印加される。よって、高周波の周期電圧に対してはMOSトランジスタ5のON電圧が0Vに近い値と等価になる。そのため、変成器12により昇圧される高周波電力が小さくても、容易にゲート端子の電圧を閾値電圧の上下に振るようにすることができ、MOSトランジスタ5を理想に近い状態でスイッチング動作させることが可能となる。

【0058】

そこで、電力分配器11の電力分配比を変えて、変成器12へ出力される電力をより小さくし、MOSトランジスタ5に出力される電力を大きくしても、整流動作を行うことができる。その結果、整流効率に直接関与する電力である、電力分配器11からMOSトランジスタ5のドレイン端子に出力される高周波電力を増加させることができるため、整流効率をより高めることができる。

【0059】

なお、直流電源14が印加する電圧が、閾値電圧の一部をMOSトランジスタ5のゲート端子に供給する構成としても良いし、閾値電圧を越えてより高い(低い)電圧を供給する構成としても良い。この場合でも、高周波の周期電圧に対してMOSトランジスタ5のON電圧を、元々の閾値電圧よりも絶対値が低い値と等価にすることができる。したがって、同様に整流回路の整流効率を高めることができる。

【0060】

また、本実施の形態では、電力分配器11を用いて入力した高周波の一部を分岐して周期電圧としてゲート端子に印加する構成を示したが、これに限らず、実施の形態1のように信号源6を設けるなどして、ゲート端子に印加する周期電圧を生成しても良い。

【符号の説明】

【0061】

1 入力端子、2 帯域通過フィルタ、3 インダクタ、4 キャパシタ、5 NチャネルMOSトランジスタ、6 信号源、7 低域通過フィルタ、8 インダクタ、9 キャパシタ、10 出力端子、11 電力分配器、12 変成器、13 移相器、14 直流電源、15 キャパシタ、16 負荷抵抗

【技術分野】

【0001】

この発明は、RFID(Radio Frequency IDentification)タグやマイクロ波エネルギー伝送などに用いられ、入力された高周波電力を直流電力に変換する整流回路に関するものである。

【背景技術】

【0002】

高周波、特にマイクロ波帯で用いられる整流回路として、従来から非特許文献1(図1)に示される構成が用いられてきた。これは、ダイオードと低域通過フィルタ、及び直流通過フィルタから構成される整流回路である。図7(a)にダイオードの電流−電圧特性を示す。図中、Vは電圧、Iは電流である。ダイオードは非線形素子であり、ON電圧(Von)を超える順方向電圧に対しては電流を流し(ON状態)、ON電圧より低い逆方向電圧に対しては電流を流さない(OFF状態)。

【0003】

ダイオードに正弦波電圧を印加する場合の電圧波形及び電流波形を、それぞれ図7(b)及び図7(c)に示す。図中、tは時間である。正弦波電圧の振幅がVonを上回る間はダイオードに電流が流れ、Vonを下回る間はダイオードに電流が流れない。この電流波形はダイオードの後段に接続される直流通過フィルタで平滑され、直流電流成分が負荷に供給される。

【0004】

ここで、Vonが低いほどダイオードに電流が流れる時間が長くなるため、直流通過フィルタで平滑される直流電力が高くなる。よって、ダイオードのON電圧が低いほど、整流回路に入力される高周波電力と負荷に供給される直流電力との比である整流効率が高くなる。

【0005】

また、整流回路に入力される高周波電力が大きいほど、整流効率は高くなる。整流回路に入力される高周波電力が小さい場合、Vonが高いとダイオードが常にOFF状態となり(図中、Bの状態)整流動作をしないが、Vonが低いとダイオードがON状態になる時間が生じるため(図中、Aの状態)整流動作を行う。よって、特に小電力の高周波入力に対してはダイオードのON電圧が低いほど整流効率が高くなる。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】T. Yoo and K. Chang, “Theoretical and experimental development of 10 and 35 GHz rectennas,” IEEE Trans. Microwave Theory Tech., vol. 40, pp. 1259-1266, June 1992.

【発明の概要】

【発明が解決しようとする課題】

【0007】

整流回路に用いるダイオードとしては、金属と半導体との接合を利用したショットキーダイオードが一般的である。ショットキーダイオードはON電圧が0.3V程度と小さいため、比較的小電力の高周波入力に対しても高効率に整流することが可能である。

【0008】

しかし、ダイオードを含めた整流回路を例えばSiプロセスにより一体化して小形化・低コスト化を図ろうとした場合、ショットキーダイオードを用いると、金属と半導体を接合するための特別なプロセスが必要となり、コストを低減できない問題がある。

【0009】

一般的なSiプロセスで製造可能なダイオードとして、ダイオード接続したMOS(Metal Oxide Semiconductor)トランジスタがある。これはMOSトランジスタのゲート端子とドレイン端子を接続したものであり、ドレイン端子からソース端子へ順方向電流が流れ、逆方向には電流を流さないというダイオードの特性を呈する。

【0010】

しかし、ダイオード接続したMOSトランジスタのON電圧は、0.7V程度とショットキーダイオードより高いため、小電力の高周波入力に対して整流効率が低いという問題がある。

【0011】

この発明は上記のような課題を解決するためになされたもので、小電力からの広い入力電力の範囲で高効率動作を行うことが可能な整流回路を得ることを目的とする。

【課題を解決するための手段】

【0012】

この発明に係る整流回路は、

入力した高周波を通過させ、直流を遮断する第1のフィルタと、

前記高周波と同じ周波数の周期電圧が印加される第1の端子、前記第1のフィルタに接続された第2の端子、および接地された第3の端子、を有し、前記高周波を整流するトランジスタと、

前記第1のフィルタと前記第2の端子との接続点に接続され、前記高周波を遮断し、前記トランジスタで整流された直流を出力する第2のフィルタと、

を備えたことを特徴とするものである。

【発明の効果】

【0013】

この発明によれば、外部から入力され直流に変換される高周波をトランジスタに入力し、このトランジスタをON、OFFするための高周波をトランジスタの第1の端子に印加しているため、特に外部から入力される高周波電力が小さくても整流効率を高くできるという効果がある。

【図面の簡単な説明】

【0014】

【図1】この発明の実施の形態1による整流回路を示す構成図である。

【図2】高周波入力電力と整流効率との関係を示す図である。

【図3】この発明の実施の形態2による整流回路を示す構成図である。

【図4】この発明の実施の形態2による整流回路の変形例を示す構成図である。

【図5】この発明の実施の形態2による整流回路の変形例を示す構成図である。

【図6】この発明の実施の形態3による整流回路を示す構成図である。

【図7】従来例の動作を説明する説明図である。

【発明を実施するための形態】

【0015】

実施の形態1.

図1は、この発明の実施の形態1による整流回路を示す構成図である。なお、各図において、同一符号は同一または相当部分を示す。図1中、1は入力端子、2は第1のフィルタである帯域通過フィルタ、3はインダクタ、4はキャパシタ、5はトランジスタであるMOS(Metal Oxide Semiconductor)トランジスタ、6は信号源、7は第2のフィルタである低域通過フィルタ、8はインダクタ、9はキャパシタ、10は出力端子、16は負荷抵抗である。

【0016】

入力端子1には高周波が入力される。帯域通過フィルタ2は、入力端子1から入力された高周波を通過し、他の周波数の波の通過を阻止する。図1では、帯域通過フィルタ2をインダクタ3とキャパシタ4を直列接続した直列共振器で構成しているが、同等の特性が得られれば他の構成でも良い。図1に示す帯域通過フィルタ2を用いる場合、入力する高周波の周波数で直列共振するようにインダクタ3及びキャパシタ4の値を決めることで、高周波の通過及び他の周波数の遮断が実現される。

【0017】

MOSトランジスタ5は、第1の端子であるゲート端子、第2の端子であるドレイン端子、第3の端子であるソース端子の3つの端子を有し、高周波の波形を整流する非線形素子である。MOSトランジスタ5のゲート端子には信号源6で生成した周期電圧が印加される。MOSトランジスタ5のドレイン端子は、帯域通過フィルタ2と図中Aで示す接続点において接続される。MOSトランジスタ5のソース端子は接地されている。

【0018】

図1に示すMOSトランジスタ5はNチャネルのMOSトランジスタであり、ゲート端子に閾値電圧を越える正の電圧が印加される場合はドレイン−ソース間に電流が流れ(ON状態)、ゲート端子に印加される電圧が閾値電圧を下回る場合はドレイン−ソース間に電流が流れない(OFF状態)。したがって、ダイオードと同様に整流動作を行うことができる。MOSトランジスタ5により整流された電流波形は、直流成分である直流電流と入力される高周波の周波数成分及びその高調波の成分を含んでいる。

【0019】

信号源6は、入力端子1から入力される高周波に同期した同じ周波数の正弦波の周期電圧を発生し、この周期電圧をMOSトランジスタ5のゲート端子に印加する。

【0020】

低域通過フィルタ7は、帯域通過フィルタ2とMOSトランジスタ5のドレイン端子との接続点(図中A点)に接続されている。低域通過フィルタ7は、MOSトランジスタ5により整流された電流波形を平滑し直流成分のみを出力端子10に出力し、負荷抵抗16に供給するとともに、直流以外の高周波の通過を阻止する。図1では、低域通過フィルタ7を直列接続されたインダクタ8と並列接続されたキャパシタ9とから構成しているが、同等の特性が得られれば他の構成でも良い。図1に示すような低域通過フィルタ7を用いる場合は、その遮断周波数を入力端子1から入力される高周波の周波数よりも低く設定することで、直流以外の高周波の遮断が実現される。

【0021】

次に、より詳細な動作について説明する。

入力端子1に入力された高周波は帯域通過フィルタ2を通過し、その電圧がMOSトランジスタ5のドレイン端子に印加される。低域通過フィルタ7は高周波に対してはハイインピーダンスとなるため、高周波は低域通過フィルタ7で遮断され、負荷抵抗16へは通過しない。

【0022】

一方、MOSトランジスタ5のゲート端子には、信号源6から、入力端子1に入力された高周波に同期した同じ周波数の正弦波の周期電圧が印加される。この周期電圧をMOSトランジスタ5の閾値電圧を上回る振幅でゲート端子に印加することにより、ゲート端子に印加される周期電圧がMOSトランジスタ5の閾値電圧を上回るほぼ半周期の時間ではMOSトランジスタ5はON状態となり、閾値電圧を下回るほぼ半周期の時間ではMOSトランジスタ5はOFF状態となる。

【0023】

ここで、信号源6からMOSトランジスタ5のゲート端子に印加される正弦波電圧の位相を、入力端子1から入力され帯域通過フィルタ2を介してMOSトランジスタ5のドレイン端子に印加される高周波の位相と同相になるように同期すれば、ゲート端子に印加される電圧が閾値電圧を上回り、MOSトランジスタ5がON状態となる間はドレイン端子からソース端子に電流が流れ、MOSトランジスタ5がOFF状態となる間は電流が流れない。したがって、MOSトランジスタ5のドレイン端子に印加する高周波の電圧が正となるほぼ半周期の時間のみ電流が流れ、整流を行うことができる。

【0024】

あるいは、信号源6からMOSトランジスタ5のゲート端子に印加される正弦波の位相を、入力端子1から入力され帯域通過フィルタ2を介してMOSトランジスタ5のドレイン端子に印加される高周波の位相と逆相になるように同期しても良い。この場合、ゲート端子に印加される電圧が閾値電圧を上回り、MOSトランジスタ5がON状態となる間はソース端子からドレイン端子に電流が流れ、MOSトランジスタ5がOFF状態となる間は電流が流れない。したがって、MOSトランジスタ5のドレイン端子に印加する高周波の電圧が負となるほぼ半周期の時間のみ電流が流れ、やはり整流を行うことができる。

【0025】

このようにして、入力端子1に入力された高周波がMOSトランジスタ5により整流される。

【0026】

MOSトランジスタ5により整流された電流波形は、直流成分と入力される高周波成分及びその高調波成分を含む。このうち、低域通過フィルタ7は直流成分のみを出力端子10に通過し、この直流成分の電力を負荷抵抗16に供給する。

【0027】

この直流成分は、帯域通過フィルタ2では遮断されるため、入力端子1に戻ることはない。帯域通過フィルタ2の代わりに高域通過フィルタを用い、入力された高周波成分は通過し直流成分は遮断するようすることもできる。ただし、高調波成分も遮断して、入力端子1に戻さないという点では、高周波成分のみを通過し直流成分と高調波成分を遮断する帯域通過フィルタ2を用いることがより望ましい。

【0028】

図2に、高周波の入力電力と整流効率との関係を示す。図2の横軸は高周波の入力電力、縦軸は整流回路の整流効率である。図2において、点線はダイオード接続されたMOSトランジスタを用いる場合、実線は図1の構成を用いる場合、それぞれの整流効率曲線を示している。

【0029】

MOSトランジスタをダイオード接続してダイオードとして用いる場合は、入力端子1から入力される高周波の電圧自身でダイオードをスイッチングしていることと等価である。このとき、高周波入力電力が大きくダイオードをスイッチングするのに十分な電圧振幅が印加されている場合は、Vonを上回る時間が長いため比較的整流効率が高い。しかし、高周波入力電力が低くなるにしたがって、ダイオードに印加される電圧振幅が小さくなり、Vonを上回る時間が短くなるため整流効率が低くなる。さらに高周波の電圧振幅がVonよりも低くなると、ダイオードがスイッチング動作しなくなるため整流効率が0となる。

【0030】

一方、本実施の形態の図1の構成を用いる場合は、高周波の入力電力の値に関わらず、MOSトランジスタ5は信号源6からゲート端子に印加される正弦波の周期電圧が正の半周期の時間でON状態、負の半周期の時間でOFF状態となる。そのため、高周波入力電力が低い場合においても整流動作が起こり、高周波電力から直流電力への変換効率、すなわち整流効率が高くなるという利点を有する。このため、図2の実線に示すように、ダイオード接続されたMOSトランジスタを用いる場合に比べ、整流効率を高くすることができ、特に入力電力が小さいときに整流効率を高くすることができる。

【0031】

なお、図1の構成では、外部からの高周波入力とは別に信号源6が必要となるが、MOSトランジスタ5のゲート端子はハイインピーダンスであるため、信号源6から出力される正弦波の周期電圧は小さくて良く、信号源6の電力消費は小さくて済む。

【0032】

図1では、信号源6から正弦波を出力するとして説明したが、代わりに矩形波を出力して周期電圧としても良い。矩形波は正弦波より立ち上がり時間及び立下り時間が短いため、MOSトランジスタ5のON状態、OFF状態が瞬時に切り替わり、理想の整流動作に近づくことから、正弦波入力と比べて整流効率がさらに高くなるという利点を有する。

【0033】

なお、本実施の形態においては、非線形素子としてNチャネルのMOSトランジスタ5を用いる構成を示したが、本発明はこれに限らず、非線形素子としてPチャネルのMOSトランジスタを用いてもよい。この場合には、ゲート端子に印加される周期電圧が、ある閾値電圧より低くなったときに、トランジスタがON状態となりドレイン端子とソース端子間に電流が流れる。また、ゲート端子に印加される電圧がこの閾値電圧より高くなったときに、トランジスタがOFF状態になりドレイン端子とソース端子間の電流が流れなくなる。したがって、この場合でも同様に整流動作が行え、整流効率を高くできるという本実施の形態の効果が得られる。

【0034】

また、本実施の形態では、MOSトランジスタ5のソース端子を接地し、ドレイン端子側に高周波電力を印加する構成としたが、ソース端子とドレイン端子は逆に接続してもよく、すなわち第2の端子と第3の端子を入れ替えてもよい。この場合もスイッチング動作が同様に行われ、本実施の形態の効果が得られる。

【0035】

加えて、本実施の形態では、非線形素子として電界効果トランジスタ(FET)の一種であるMOSトランジスタ5を用いたが、これに限らず、他の種類の電界効果トランジスタを用いることもでき、Nチャネル、Pチャネルのどちらのものも用いることができる。さらに、電界効果トランジスタでなくても、バイポーラトランジスタを用いることもできる。いずれの種類のトランジスタでも、Siプロセスにより他の回路と一体化できるトランジスタを用いることがより望ましいが、必ずしもこれに限るものではない。なお、バイポーラトランジスタを用いる場合は、ゲート端子、ドレイン端子、ソース端子のそれぞれに対応する端子として、ベース端子、コレクタ端子、エミッタ端子を用いれば良く、コレクタ端子とエミッタ端子の接続を入れ替えてもよい。バイポーラトランジスタはNPN型、PNP型のいずれのものも使用することができ、本実施の形態の効果を同様に得ることができる。

【0036】

さらに、本実施の形態では、MOSトランジスタ5のゲート端子に印加する周期電圧を、信号源6を用いて発生する構成を示したが、本発明はこれに限らず、入力端子1に入力された高周波と同期した同じ周波数の周期電圧がトランジスタのゲート端子に印加されれば良く、必ずしも信号源6を設ける必要はない。例えば、ゲート端子に印加する周期電圧の周波数情報や位相情報を、入力端子1に入力する高周波を生成する図示していない装置から供給するなどすることもできる。

【0037】

以上のように、本実施の形態に示した整流回路では、整流効率を高くできるという効果を奏し、Siプロセスを用いればさらにコストを低くできるという効果を奏する。

【0038】

実施の形態2.

図3は、この発明の実施の形態2による整流回路を示す構成図である。これは、信号源6を用いる代わりに、高周波入力の一部を用いてMOSトランジスタ5をスイッチングする構成である。図3において、図1と同一符号は同一または相当部分を示すので説明を省略する。11は分配手段である電力分配器、12は昇圧手段である変成器、13は移相手段である移相器である。

【0039】

図3において、電力分配器11は、入力端子1から入力され帯域通過フィルタ2を介して伝送される高周波電力を第1の高周波と第2の高周波2つに分配する。第1の高周波は図中点Aを通過し、MOSトランジスタ5のドレイン端子に印加する。第2の高周波は変成器12に入力する。変成器12は、電力分配器11から出力された第2の高周波の電圧を昇圧する。移相器13は、変成器12から出力される高周波電圧の位相をシフトして周期電圧としてMOSトランジスタ5のゲート端子に印加する。

【0040】

次に動作について説明する。

入力端子1から入力され、帯域通過フィルタ2を介して伝送される高周波電力は電力分配器11により、2つに分配される。電力分配器11により分配される第1の高周波は、その電圧がMOSトランジスタ5のドレイン端子に印加される。高周波電力は、低域通過フィルタ7が高周波に対してはハイインピーダンスとなるため、出力端子10や負荷抵抗16へは通過しない。

【0041】

電力分配器11により分配される第2の高周波の出力は変成器12に入力する。この高周波は、変成器12で昇圧され移相器13を介してMOSトランジスタ5のゲート端子に印加される。

【0042】

昇圧された高周波の電圧振幅がMOSトランジスタ5の閾値電圧を超えると、MOSトランジスタ5はスイッチング動作をする。すなわち、正弦波電圧がMOSトランジスタ5の閾値を上回る正の半周期の時間ではMOSトランジスタ5はON状態となり、正弦波電圧がMOSトランジスタ5の閾値を下回る負の半周期の時間ではMOSトランジスタ5はOFF状態となる。

【0043】

電力分配器11の2つの出力に位相差がなく、また変成器12を通過することによる位相の変化がない場合は、MOSトランジスタ5のドレイン端子及びゲート端子に印加される電圧は同相、すなわち位相差が0度となる。そのため、MOSトランジスタ5がON状態のとき高周波入力の正の半周期の電圧がドレイン端子に印加され、ドレイン端子からソース端子に電流が流れる。MOSトランジスタ5がOFF状態のとき高周波入力の負の半周期の電圧がドレイン端子に印加されるが、ドレイン端子とソース端子の間に電流は流れない。

【0044】

電力分配器11の2つの出力に位相差があったとしても、変成器12を通過することなどによる位相の変化が、これを打ち消すような場合は、同様に、MOSトランジスタ5のドレイン端子及びゲート端子に印加される電圧の位相差が0度となる。いずれにしても、MOSトランジスタ5による整流動作が行われる。

【0045】

一方、電力分配器11の2つの出力に位相差が生じ、また変成器12を通過する高周波の位相が変化するなどし、MOSトランジスタ5のドレイン端子及びゲート端子に印加される電圧が逆相、すなわち位相差が180度となる場合、MOSトランジスタ5がON状態のとき高周波入力の負の半周期の電圧がドレイン端子に印加され、ソース端子からドレイン端子に電流が流れる。MOSトランジスタ5がOFF状態のとき電流は流れない。

【0046】

このようにして、入力端子1に入力された高周波がMOSトランジスタ5により整流される。

【0047】

MOSトランジスタ5により整流された波形は、直流成分と入力される高周波の成分及びその高調波成分を含む。このうち、低域通過フィルタ7は直流成分のみを通過し、出力端子10及び負荷抵抗16に供給する。

【0048】

図3の構成では、入力端子1から入力される高周波の電力が小さい場合においても、変成器12で高周波の電圧が昇圧されるため、この電圧をMOSトランジスタ5のゲート端子に印加することで、MOSトランジスタ5はスイッチング動作を行い整流動作が起こる。そのため、高周波入力電力が低い場合においても高周波電力から直流電力への変換効率が高くなるという利点を有する。

【0049】

また、入力端子1に入力した高周波を電力分配器11で分配し周期電圧としているため、入力した高周波に同期した同じ周波数の周期電圧を容易に作ることができるという利点を有する。

【0050】

よって、図3に示す構成とすることで、信号源6を用いることなく広い入力電力範囲において高い整流効率で整流動作を行うことが可能となる。

【0051】

電力分配器11の2つの出力に位相差があるか、あるいは変成器12を通過することによる位相の変化が生じ、MOSトランジスタ5のドレイン端子とゲート端子に印加される電圧に0度や180度以外の位相のずれが生じる場合は、MOSトランジスタ5がONとなる時間の一部はドレイン端子からソース端子に電流が流れるが、残りの時間は逆にソース端子からドレイン端子に電流が流れるようになる。このため、直流通過フィルタ7で平滑され負荷抵抗16に供給される直流成分の値が低くなり、整流効率が劣化する。

【0052】

そこで、図3に示すように、変成器12とMOSトランジスタ5のドレイン端子の間に移相器13を挿入し、この移相器13により高周波の位相をシフトしてMOSトランジスタ5のドレイン端子とゲート端子に印加される周期電圧を同相にするか逆相にすることで、MOSトランジスタ5がON状態となる間は常にドレイン端子からソース端子、あるいはソース端子からドレイン端子に電流が流れるようにすることができる。そのため、整流効率の劣化を抑制でき、より変換効率の高い整流回路が得られる。

【0053】

変成器12はコイルを用いたトランスなど、種々の回路で構成することができる。また図3では、変成器12を用いて昇圧したが、代わりに増幅器などを用いて昇圧しても良い。

【0054】

なお、図3では、電力分配器11を帯域通過フィルタ2と接続点Aとの間に挿入しているが、電力分配器11を入力端子1と帯域通過フィルタ2との間に挿入してもよい。

【0055】

さらに、図3では、移相器13を変成器12とMOSトランジスタ5のゲート端子との間に接続したが、図4に示すように電力分配器11と図中接続点Aの間に接続しても良く、また図5に示すように図中接続点AとMOSトランジスタ5のドレイン端子の間に接続しても良い。また、移相器13を分配器11と変成器12の間等に接続することもでき、いずれの場合もドレイン端子に印加する高周波とゲート端子に印加する周期電圧との位相差を調整することができるので、本実施の形態の効果を得ることができる。

【0056】

実施の形態3.

図6は、この発明の実施の形態3による整流回路を示す構成図である。図6において、図1及び図3〜図5と同一符号は同一または相当部分を示すので説明を省略する。14は直流電圧印加手段である直流電源、15はキャパシタである。直流電源14は、所定の電圧をMOSトランジスタ5のゲート端子に印加する。キャパシタ15は、直流電源14の電圧が移相器13に印加されないようにDCカットしている。

【0057】

次に動作について説明する。

直流電源14から供給される所定の電圧はMOSトランジスタ5のゲート端子の閾値電圧に近い値としている。このため、直流電源14とキャパシタ15を用いることにより、MOSトランジスタ5のゲート端子には常に閾値電圧に近い値の電圧が印加されている。よって、入力端子1から帯域通過フィルタ2、電力分配器11、変成器12、及び移相器13を介してゲート端子に印加される高周波の周期電圧は、直流電源14で与えられる電圧に重畳して、ゲート端子に印加される。よって、高周波の周期電圧に対してはMOSトランジスタ5のON電圧が0Vに近い値と等価になる。そのため、変成器12により昇圧される高周波電力が小さくても、容易にゲート端子の電圧を閾値電圧の上下に振るようにすることができ、MOSトランジスタ5を理想に近い状態でスイッチング動作させることが可能となる。

【0058】

そこで、電力分配器11の電力分配比を変えて、変成器12へ出力される電力をより小さくし、MOSトランジスタ5に出力される電力を大きくしても、整流動作を行うことができる。その結果、整流効率に直接関与する電力である、電力分配器11からMOSトランジスタ5のドレイン端子に出力される高周波電力を増加させることができるため、整流効率をより高めることができる。

【0059】

なお、直流電源14が印加する電圧が、閾値電圧の一部をMOSトランジスタ5のゲート端子に供給する構成としても良いし、閾値電圧を越えてより高い(低い)電圧を供給する構成としても良い。この場合でも、高周波の周期電圧に対してMOSトランジスタ5のON電圧を、元々の閾値電圧よりも絶対値が低い値と等価にすることができる。したがって、同様に整流回路の整流効率を高めることができる。

【0060】

また、本実施の形態では、電力分配器11を用いて入力した高周波の一部を分岐して周期電圧としてゲート端子に印加する構成を示したが、これに限らず、実施の形態1のように信号源6を設けるなどして、ゲート端子に印加する周期電圧を生成しても良い。

【符号の説明】

【0061】

1 入力端子、2 帯域通過フィルタ、3 インダクタ、4 キャパシタ、5 NチャネルMOSトランジスタ、6 信号源、7 低域通過フィルタ、8 インダクタ、9 キャパシタ、10 出力端子、11 電力分配器、12 変成器、13 移相器、14 直流電源、15 キャパシタ、16 負荷抵抗

【特許請求の範囲】

【請求項1】

入力した高周波を通過させ、直流を遮断する第1のフィルタと、

前記高周波と同じ周波数の周期電圧が印加される第1の端子、前記第1のフィルタに接続された第2の端子、および接地された第3の端子、を有し、前記高周波を整流するトランジスタと、

前記第1のフィルタと前記第2の端子との接続点に接続され、前記高周波を遮断し、前記トランジスタで整流された直流を出力する第2のフィルタと、

を備えたことを特徴とする整流回路。

【請求項2】

前記第1の端子は、前記トランジスタのゲート端子またはベース端子であることを特徴とする請求項1に記載の整流回路。

【請求項3】

前記第1のフィルタは前記高周波の高調波成分を遮断する帯域通過フィルタであることを特徴とする請求項1または請求項2に記載の整流回路。

【請求項4】

前記第2のフィルタは低域通過フィルタであることを特徴とする請求項1から請求項3のいずれかに記載の整流回路。

【請求項5】

前記第1の端子に直流電圧を印加する直流電圧印加手段を備えたことを特徴とする請求項1から請求項4のいずれかに記載の整流回路。

【請求項6】

入力した前記高周波を第1の高周波と第2の高周波に分配し、前記第1の高周波を前記第2の端子に出力する分配手段と、

前記分配手段で分配された前記第2の高周波の電圧を昇圧する昇圧手段と、を備え、

前記昇圧手段で昇圧された前記第2の高周波を、前記周期電圧として前記第1の端子に印加することを特徴とする請求項1から請求項5のいずれかに記載の整流回路。

【請求項7】

前記分配手段で分配された前記第1の高周波または前記第2の高周波のいずれかの位相を変化させる移相手段を備えたことを特徴とする請求項6に記載の整流回路。

【請求項8】

前記周期電圧を発生する信号源を備えたことを特徴とする請求項1から請求項5のいずれかに記載の整流回路。

【請求項9】

前記周期電圧は、前記第2の端子に印加する前記高周波に対し、同相もしくは逆相となるように同期していることを特徴とする請求項1から請求項8のいずれかに記載の整流回路。

【請求項1】

入力した高周波を通過させ、直流を遮断する第1のフィルタと、

前記高周波と同じ周波数の周期電圧が印加される第1の端子、前記第1のフィルタに接続された第2の端子、および接地された第3の端子、を有し、前記高周波を整流するトランジスタと、

前記第1のフィルタと前記第2の端子との接続点に接続され、前記高周波を遮断し、前記トランジスタで整流された直流を出力する第2のフィルタと、

を備えたことを特徴とする整流回路。

【請求項2】

前記第1の端子は、前記トランジスタのゲート端子またはベース端子であることを特徴とする請求項1に記載の整流回路。

【請求項3】

前記第1のフィルタは前記高周波の高調波成分を遮断する帯域通過フィルタであることを特徴とする請求項1または請求項2に記載の整流回路。

【請求項4】

前記第2のフィルタは低域通過フィルタであることを特徴とする請求項1から請求項3のいずれかに記載の整流回路。

【請求項5】

前記第1の端子に直流電圧を印加する直流電圧印加手段を備えたことを特徴とする請求項1から請求項4のいずれかに記載の整流回路。

【請求項6】

入力した前記高周波を第1の高周波と第2の高周波に分配し、前記第1の高周波を前記第2の端子に出力する分配手段と、

前記分配手段で分配された前記第2の高周波の電圧を昇圧する昇圧手段と、を備え、

前記昇圧手段で昇圧された前記第2の高周波を、前記周期電圧として前記第1の端子に印加することを特徴とする請求項1から請求項5のいずれかに記載の整流回路。

【請求項7】

前記分配手段で分配された前記第1の高周波または前記第2の高周波のいずれかの位相を変化させる移相手段を備えたことを特徴とする請求項6に記載の整流回路。

【請求項8】

前記周期電圧を発生する信号源を備えたことを特徴とする請求項1から請求項5のいずれかに記載の整流回路。

【請求項9】

前記周期電圧は、前記第2の端子に印加する前記高周波に対し、同相もしくは逆相となるように同期していることを特徴とする請求項1から請求項8のいずれかに記載の整流回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−196068(P2012−196068A)

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願番号】特願2011−58696(P2011−58696)

【出願日】平成23年3月17日(2011.3.17)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願日】平成23年3月17日(2011.3.17)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]