整流装置

【課題】従来よりも降圧チョッパに印加される電圧を抑制することが出来る整流装置を提供することを目的とする。

【解決手段】整流装置が、3相交流電圧を整流することによって直流電圧へ変換し、当該直流電圧を出力する整流装置であって、整流した直流電圧が所定のしきい値を超えた場合に、直流電圧の生成に供する相電圧を減らす。

【解決手段】整流装置が、3相交流電圧を整流することによって直流電圧へ変換し、当該直流電圧を出力する整流装置であって、整流した直流電圧が所定のしきい値を超えた場合に、直流電圧の生成に供する相電圧を減らす。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、オルタネータ等の発電機が出力した電圧の整流装置に関する。

【背景技術】

【0002】

従来、航空機では、エンジンによって回転駆動するオルタネータ(発電機)が出力する3相交流電圧を、整流装置によって直流電圧へ変換し、当該直流電圧をスイッチングシャントによって所望の電圧まで降圧することによって、各種負荷装置を稼動する電圧として使用している。しかしながら、このスイッチングシャントでは、余った電圧をオルタネータへ戻している為、この電圧によってオルタネータが発熱してしまうという課題を抱えていた。その為に、スイッチングシャントの代わりに、降圧用DC/DCコンバータとして、降圧チョッパ回路を使用することが検討されている。しかしながら、降圧チョッパ回路では、整流装置からの入力される直流電圧がFET(Field Effect Transistor)等のスイッチング素子に印加される為、高い直流電圧に耐えることが出来るスイッチング素子を搭載しなければならないという課題を抱えている。

【0003】

そして、上記課題を解決する整流装置として、下記特許文献1には、可変電圧交流電源によって発生された電圧の範囲を圧縮するように自動的に動作する整流回路が開示されている。

この整流回路は、交流電源が出力する交流電圧を直流電圧に変換する整流回路であって、電源に接続されると共に整流回路の第1の出力端子に一方の極性の出力電圧を発生する第1の整流手段と、電源に接続されると共に整流回路の第2の出力端子に反対の極性の出力電圧を発生する第2の整流手段と、一端が電源に結合されると共に他端が第2の出力端子に結合されている一方向導電性素子と、第2の整流手段または一方向導電性素子のいずれかを非導通状態にするように選択的に動作するスイッチング手段とを有し、一方向導電性素子が非導通状態にあるときは3相全波整流回路として動作し、また第2の整流手段が非導通状態にあるときは3相半波整流回路として動作することによって、出力する直流電圧の範囲を交流電源の電圧範囲よりも狭くする。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭62−155775号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、上記従来技術では、出力する直流電圧に応じて、3相全波整流回路として動作していた整流回路を、3相半波整流回路として動作させることによって、出力する直流電圧を降圧している。しかしながら、航空機では、オルタネータが出力した交流電圧を、3相半波整流回路として動作する整流回路によって整流しただけでは、直流電圧の降圧が十分ではない為に、高い直流電圧が降圧チョッパ回路に印加されてしまう。この為、降圧チョッパ回路では、スイッチング素子として、高い直流電圧に耐えることが出来る半導体デバイスを搭載しなければならなかった。

【0006】

本発明は、上述した事情に鑑みてなされたものであり、従来よりも降圧チョッパに印加される電圧を抑制することが出来る整流装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明では、整流装置に係る第1の解決手段として、3相交流電圧を整流することによって直流電圧へ変換し、当該直流電圧を出力する整流装置であって、整流した直流電圧が所定のしきい値を超えた場合に、直流電圧の生成に供する相電圧を減らすという手段を採用する。

【0008】

本発明では、整流装置に係る第2の解決手段として、上記第1の解決手段において、3相の交流電圧に応じた3対の整流用ダイオードから構成された整流用ブリッジ回路と、前記整流用ブリッジ回路の正極側の出力端に接続する2個の整流用ダイオードのカソード端子に接続する第1のスイッチング手段と、前記整流用ブリッジ回路の負極側の出力端に接続する3個の整流用ダイオードのアノード端子に接続する第2のスイッチング手段と、3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、前記第1のスイッチン手段及び前記第2のスイッチング手段をOFFにすることによって、前記整流用ブリッジ回路の動作を3相全波整流から単相半波整流へ切り替える制御手段とを、具備するという手段を採用する。

【0009】

本発明では、整流装置に係る第3の解決手段として、上記第1の解決手段において、3相の交流電圧に応じた3対の整流用ダイオードから構成された整流用ブリッジ回路と、前記整流用ブリッジ回路の正極側の出力端に接続する1個の整流用ダイオードのカソード端子に接続する第1のスイッチング手段と、前記整流用ブリッジ回路の負極側の出力端に接続する3個の整流用ダイオードのアノード端子に接続する第2のスイッチング手段と、3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、前記第1のスイッチン手段及び前記第2のスイッチング手段をOFFにすることによって、前記整流用ブリッジ回路の動作を3相全波整流から2相半波整流へ切り替える制御手段とを、具備するという手段を採用する。

【0010】

本発明では、整流装置に係る第4の解決手段として、上記第1の解決手段において、3相の交流電圧に応じた合計6個の整流用ダイオード及び整流用サイリスタから構成され、前記合計6個の内、少なくとも3つは、負極側の出力端にアノード端子が接続する整流用サイリスタである整流用ブリッジ回路と、3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、少なくとも前記整流用ブリッジ回路の負極側の出力端にアノード端子が接続する整流用サイリスタをOFFにする制御手段とを、具備するという手段を採用する。

【発明の効果】

【0011】

本発明によれば、整流装置が、3相交流電圧を整流することによって直流電圧へ変換し、当該直流電圧を出力する整流装置であって、整流した直流電圧が所定のしきい値を超えた場合に、直流電圧の生成に供する相電圧を減らす。

このように、整流装置が、整流した直流電圧がしきい値を超えると、直流電圧の生成に供する相電圧を減らすことによって、従来行われていた3相全波整流から3相半波整流への切り替える方法よりも直流電圧を抑制することが出来る。これにより、従来よりも降圧チョッパに印加される電圧を抑制することが出来る。

【図面の簡単な説明】

【0012】

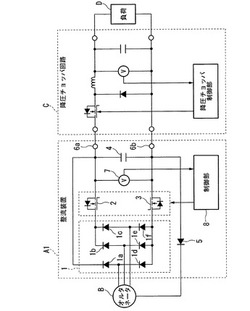

【図1】本発明の第1実施形態に係る整流装置A1の構成を示す回路図である。

【図2】本発明の第1実施形態に係る整流装置A1の入力された3相交流電圧の線間電圧を示す波形図と、直流電圧V1を示す波形図と、第1MOSFET2及び第2MOSFET3のスイッチング周期を示す波形図である。

【図3】本発明の第2実施形態に係る整流装置A2の構成を示す回路図である。

【図4】本発明の第2実施形態に係る整流装置A2の入力された3相交流電圧の線間電圧を示す波形図と、直流電圧V11を示す波形図と、第1MOSFET12及び第2MOSFET13のスイッチング周期を示す波形図である。

【図5】本発明の第2第3実施形態に係る整流装置A3の構成を示す回路図である。

【発明を実施するための形態】

【0013】

以下、図面を参照して、本発明の実施形態について説明する。

〔第1実施形態〕

まず、第1実施形態に係る整流装置A1について、説明する。

第1実施形態に係る整流装置A1の回路構成について、図1を参照して、説明する。図1は、第1実施形態に係る整流装置A1の構成を示す回路図である。

【0014】

整流装置A1は、オルタネータBが発生させた交流電圧を直流電圧に変換し、当該直流電圧を降圧チョッパ回路Cを介して負荷Dへ出力するものであり、図1に示すように、整流用ブリッジ回路1、第1MOSFET2、第2MOSFET3、コンデンサ4、ダイオード5、出力端子6a,6b、電圧センサ7及び制御部8を備えている。

なお、第1MOSFET2は、第1実施形態における第1のスイッチング手段であり、第2MOSFET3は、第1実施形態における第2のスイッチング手段である。また、電圧センサ7及び制御部8が、第1実施形態における制御手段を構成する。

【0015】

整流用ブリッジ回路1は、オルタネータBが出力する3相交流電圧を整流することによって直流電圧に変換するブリッジ回路であり、整流用ダイオード1a〜1fを備えている。

整流用ダイオード1aは、カソード端子が、正極側の出力端子6aに接続され、アノード端子が、オルタネータBのU相巻線及び整流用ダイオード1dのカソード端子に接続されている。

【0016】

整流用ダイオード1bは、カソード端子が、第1MOSFET2のドレイン端子に接続され、アノード端子が、オルタネータBのV相巻線及び整流用ダイオード1eのカソード端子に接続されている。

整流用ダイオード1cは、カソード端子が、第1MOSFET2のドレイン端子に接続され、アノード端子が、オルタネータBのW相巻線及び整流用ダイオード1fのカソード端子に接続されている。

【0017】

整流用ダイオード1dは、カソード端子が、オルタネータBのU相巻線及び整流用ダイオード1aのアノード端子に接続され、アノード端子が、第2MOSFET3のソース端子に接続されている。

整流用ダイオード1eは、カソード端子が、オルタネータBのV相巻線及び整流用ダイオード1bのアノード端子に接続され、アノード端子が、第2MOSFET3のソース端子に接続されている。

【0018】

整流用ダイオード1fは、カソード端子が、オルタネータBのW相巻線及び整流用ダイオード1cのアノード端子に接続され、アノード端子が、第2MOSFET3のソース端子に接続されている。

【0019】

第1MOSFET2では、ドレイン端子が整流用ダイオード1bのカソード端子及び整流用ダイオード1cのカソード端子に接続され、ソース端子が、コンデンサ4の一端及び一方の出力端子6aに接続され、さらにゲート端子が制御部8に接続されている。

第2MOSFET3では、ドレイン端子がコンデンサ4の他端及び負極側の出力端子6bに接続され、ソース端子が整流用ダイオード1dのアノード端子、整流用ダイオード1eのアノード端子及び整流用ダイオード1fのアノード端子に接続され、さらにゲート端子が制御部8にされている。

【0020】

コンデンサ4は、降圧チョッパ回路Cへ出力する直流電圧の平滑化、すなわち直流電圧のリップルを低減することを目的として設けられたものであり、一端が、整流用ダイオード1aのカソード端子、第1第1MOSFET2のソース端子及び一方の出力端子6aに接続され、他端が、第2第1MOSFET3のドレイン端子、ダイオード5のアノード端子及び他方の出力端子6bに接続されている。

ダイオード5は、アノード端子がコンデンサ4の他端及び他方の出力端子6bに接続され、カソード端子がオルタネータBに接続されている。

【0021】

出力端子6a,6bは、整流装置A1が交流電圧を整流することによって変換した直流電圧を降圧チョッパ回路Cへ出力するための一対の接続端子であり、一方の正極側の出力端子6aが、整流用ダイオード1aのカソード端子、第1MOSFET2のソース端子及びコンデンサ4の一端に接続され、他方の負極側の出力端子6bが、コンデンサ4の他端、第2MOSFET3のドレイン端子及びダイオード5のアノード端子に接続されている。

【0022】

電圧センサ7は、整流装置A1が出力端子6a,6bから降圧チョッパ回路Cへ出力する直流電圧を検出するセンサであり、図1に示すように、一方の端子が一方の出力端子6aに接続され、他方の端子が他方の出力端子6bに接続されている。そして、この電圧センサ7は、検出結果に基づいて、出力端子6a,6bから出力する直流電圧を示す検出信号Sv1を制御部8へ出力する。

【0023】

制御部8は、第1MOSFET2と第2MOSFET3と信号の入出力を行うインタフェース回路等から構成されており、上記電圧センサ7から入力される検出信号Sv1に基づいて、第1MOSFET2及び第2MOSFET3を制御する。なお、制御部8は、半導体デバイス等のハードウェアのみによって制御を行う制御回路であってもよいし、またCPU(Central Processing Unit)、ROM(Read Only Memory)及びRAM(Random Access Memory)から構成され、上記ROMに記憶された制御プログラムに基づいて制御を行うソフトウェアを用いた制御回路であってもよい。

【0024】

次に、このように構成された第1実施形態に係る整流装置A1の動作について、詳しく説明する。

整流装置A1では、オルタネータBが回転によって3相交流電圧の出力を開始すると、整流用ブリッジ回路1が交流電圧を直流電圧V1へ変換し、当該直流電圧V1を出力端子6a,6bから降圧チョッパ回路Cへ出力する。電圧センサ7は、直流電圧V1の出力動作の開始に伴って、制御部8への検出信号Sv1の出力を開始する。そして、オルタネータBの回転数の上昇に伴って、整流装置A1では、オルタネータBから入力される3相交流電圧が上昇する。

【0025】

制御部8は、電圧センサ7から検出信号Sv1が入力されると、当該検出信号Sv1に基づいて、出力端子6a,6bから出力する直流電圧V1が、降圧チョッパ回路Cの耐電圧を示すしきい値Va1を超えたか否か判断する。そして、制御部8は、直流電圧V1がしきい値Va1を超えると、第1MOSFET2及び第2MOSFET3をOFFにする。

【0026】

そして、整流装置A1では、第1MOSFET2及び第2MOSFET3がOFFになることによって、整流用ダイオード1aのみが整流に使用される為に、3相全波整流から単相半波整流に切り替わる。その為、整流装置A1の出力端子6a,6bから出力する直流電圧V1が低下する。

【0027】

整流装置A1の上記動作について、図2を参照して、詳しく説明する。

図2は、第1実施形態に係る整流装置A1の入力された3相交流電圧の線間電圧を示す波形図と、直流電圧V1を示す波形図と、第1MOSFET2及び第2MOSFET3のスイッチング周期を示す波形図である。

【0028】

なお、図2の(a)では、3相交流電圧の線間電圧が電圧Vb1まで変化した場合の波形を示し、図2の(b)では、3相交流電圧の線間電圧が電圧Vb1まで変化した場合の直流電圧V1の波形を示し、図2の(c)では、3相交流電圧の線間電圧が電圧Vb1まで変化した場合の第1MOSFET2及び第2MOSFET3のスイッチング周期の波形を示している。そして、図2の(a),(b),(c)では、縦軸が電圧を示し、横軸が時間を示す。

【0029】

整流装置A1では、第1MOSFET2及び第2MOSFET3がONの場合、すなわち3相全波整流を行っている場合、図2の(a)に示す3相交流電圧の線間電圧のピーク電圧と、図2の(b)に示す直流電圧V1とが等しくなる。

そして、制御部8は、直流電圧V1がしきい値Va1を超えると、第1MOSFET2及び第2MOSFET3をOFFすることによって、3相全波整流から単相半波整流に切り替え、これにより、図2の(b)に示すように、直流電圧V1がしきい値Va1を下回る電圧、すなわち降圧チョッパ回路Cの耐電圧を下回る電圧まで降圧させる。

【0030】

整流装置A1では、単相半波整流を行っている場合に、直流電圧V1が、3相交流電圧の線間電圧のピーク電圧の(1/√3)に等しくなる。なお、図2の(b)には、比較の為に、整流装置A1が3相全波整流のみを行った場合の直流電圧V2と、整流装置A1が単相半波整流のみを行った場合の直流電圧V3との波形を示す。

【0031】

そして、制御部8は、直流電圧V1がしきい値Va1を下回る電圧まで降圧すると、第1MOSFET2及び第2MOSFET3をONにし、再び、直流電圧V1がしきい値Va1を超えると、第1MOSFET2及び第2MOSFET3をOFFにする。制御部8は、第1MOSFET2及び第2MOSFET3のONとOFFの切り替えを、図2の(c)に示すように、何度も繰り返すことによって、直流電圧V1をしきい値Va1を下回る電圧になるように制御する。

【0032】

以上のように、第1実施形態に係る整流装置A1では、制御部8が、出力端子6a,6bから出力する直流電圧V1がしきい値Va1を超えると、第1MOSFET2及び第2MOSFET3をOFFにすることによって、3相全波整流から単相半波整流に切り替える為に、降圧チョッパ回路Cへ出力する直流電圧V1を抑制することが出来る。これによって、降圧チョッパ回路Cに高耐圧の半導体デバイスを搭載しなくてもよい為に、降圧チョッパ回路の生産経費を抑制することが出来る。

【0033】

以上、本発明の第1実施形態について説明したが、本発明は上記第1実施形態に限定されることなく、例えば以下のような変形が考えられる。

(1)上記第1実施形態に係る整流装置A1では、直流電圧V1がしきい値Va1を超えると、第1MOSFET2及び第2MOSFET3をOFFにすることによって、3相全波整流から単相半波整流に切り替え、これによって直流電圧V1を抑制したが、本発明はこれに限定されない。

【0034】

例えば、制御部8が、電圧センサ7から入力される検出信号Sv1に基づいて、直流電圧V1がしきい値Va1を超えたと判断すると、オルタネータBの回転数を低下させることによって、しきい値Va1を下回る電圧まで直流電圧V1を降圧するようにしてもよい。

【0035】

〔第2実施形態〕

次に、第2実施形態に係る整流装置A2について、説明する。

第2実施形態に係る整流装置A2の回路構成について、図3を参照して、説明する。図3は、第2実施形態に係る整流装置A2の構成を示す回路図である。

【0036】

整流装置A2は、第1実施形態に係る整流装置A1と同様に、オルタネータBが発生させた交流電圧を直流電圧に変換し、当該直流電圧を降圧チョッパ回路Cを介して負荷Dへ出力するものであり、ブリッジ回路の結線が異なる点において、第1実施形態に係る整流装置A1と相違する。

【0037】

整流装置A2は、図3に示すように、整流用ブリッジ回路11、第1MOSFET12、第2MOSFET13、コンデンサ14、ダイオード15、出力端子16a,16b、電圧センサ17及び制御部18を備えている。なお、第1MOSFET12は、第2実施形態における第1のスイッチング手段であり、第2MOSFET13は、第2実施形態における第2のスイッチング手段である。また、電圧センサ17及び制御部18が、第2実施形態における制御手段を構成する。

【0038】

整流用ブリッジ回路11は、オルタネータBが出力する3相交流電圧を整流することによって直流電圧に変換するブリッジ回路であり、整流用ダイオード11a〜11fを備えている。

整流用ダイオード11aは、カソード端子が、正極側の出力端子16aに接続され、アノード端子が、オルタネータBのU相巻線及び整流用ダイオード11dのカソード端子に接続されている。

【0039】

整流用ダイオード11bは、カソード端子が、正極側の出力端子16aに接続され、アノード端子が、オルタネータBのV相巻線及び整流用ダイオード11eのカソード端子に接続されている。

整流用ダイオード11cは、カソード端子が、第1MOSFET12のドレイン端子に接続され、アノード端子が、オルタネータBのW相巻線及び整流用ダイオード11fのカソード端子に接続されている。

【0040】

整流用ダイオード11dは、カソード端子が、オルタネータBのU相巻線及び整流用ダイオード11aのアノード端子に接続され、アノード端子が、第2MOSFET13のソース端子に接続されている。

整流用ダイオード11eは、カソード端子が、オルタネータBのV相巻線及び整流用ダイオード11bのアノード端子に接続され、アノード端子が、第2MOSFET13のソース端子に接続されている。

【0041】

整流用ダイオード11fは、カソード端子が、オルタネータBのW相巻線及び整流用ダイオード11cのアノード端子に接続され、アノード端子が、第2MOSFET13のソース端子に接続されている。

【0042】

第1MOSFET12では、ドレイン端子が整流用ダイオード11cのカソード端子に接続され、ソース端子が、コンデンサ14の一端及び一方の出力端子16aに接続され、さらにゲート端子が制御部18に接続されている。

第2MOSFET13では、ドレイン端子がコンデンサ14の他端及び負極側の出力端子16bに接続され、ソース端子が整流用ダイオード11dのアノード端子、整流用ダイオード11eのアノード端子及び整流用ダイオード11fのアノード端子に接続され、さらにゲート端子が制御部18にされている。

【0043】

コンデンサ14は、降圧チョッパ回路Cへ出力する直流電圧の平滑化、すなわち直流電圧のリップルを低減することを目的として設けられたものであり、一端が、整流用ダイオード11aのカソード端子、整流用ダイオード11bのカソード端子、第1第1MOSFET12のソース端子及び一方の出力端子16aに接続され、他端が、第2第1MOSFET3のドレイン端子、ダイオード15のアノード端子及び他方の出力端子16bに接続されている。

ダイオード15は、アノード端子がコンデンサ14の他端及び他方の出力端子16bに接続され、カソード端子がオルタネータBに接続されている。

【0044】

出力端子16a,16bは、整流装置A2が交流電圧を整流することによって変換した直流電圧を降圧チョッパ回路Cへ出力するための一対の接続端子であり、一方の正極側の出力端子16aが、整流用ダイオード11aのカソード端子、整流用ダイオード11bのカソード端子、第1MOSFET12のソース端子及びコンデンサ14の一端に接続され、他方の負極側の出力端子16bが、コンデンサ14の他端、第2MOSFET13のドレイン端子及びダイオード15のアノード端子に接続されている。

【0045】

電圧センサ17は、整流装置A2が出力端子16a,16bから降圧チョッパ回路Cへ出力する直流電圧を検出するセンサであり、図3に示すように、一方の端子が一方の出力端子16aに接続され、他方の端子が他方の出力端子16bに接続されている。そして、この電圧センサ17は、検出結果に基づいて、出力端子16a,16bから出力する直流電圧を示す検出信号Sv11を制御部18へ出力する。

【0046】

制御部18は、第1MOSFET12と第2MOSFET13と信号の入出力を行うインタフェース回路等から構成されており、上記電圧センサ17から入力される検出信号Sv11に基づいて、第1MOSFET12及び第2MOSFET13を制御する。

【0047】

次に、このように構成された第2実施形態に係る整流装置A2の動作について、詳しく説明する。

整流装置A2では、オルタネータBが回転によって3相交流電圧の出力を開始すると、整流用ブリッジ回路11が交流電圧を直流電圧V11へ変換し、当該直流電圧V11を出力端子16a,16bから降圧チョッパ回路Cへ出力する。電圧センサ17は、直流電圧V11の出力動作の開始に伴って、制御部18への検出信号Sv11の出力を開始する。そして、オルタネータBの回転数の上昇に伴って、整流装置A2では、オルタネータBから入力される3相交流電圧が上昇する。

【0048】

制御部18は、電圧センサ17から検出信号Sv11が入力されると、当該検出信号Sv11に基づいて、出力端子16a,16bから出力する直流電圧V11が、降圧チョッパ回路Cの耐電圧を示すしきい値Va11を超えたか否か判断する。そして、制御部18は、直流電圧V11がしきい値Va11を超えると、第1MOSFET12及び第2MOSFET13をOFFにする。

【0049】

そして、整流装置A2では、第1MOSFET12及び第2MOSFET13がOFFになることによって、整流用ダイオード11a,11bのみが整流に使用される為に、3相全波整流から2相半波整流に切り替わる。その為、整流装置A2の出力端子16a,6bから出力する直流電圧V11が低下する。

【0050】

整流装置A2の上記動作について、図4を参照して、詳しく説明する。

図4は、第2実施形態に係る整流装置A2の入力された3相交流電圧の線間電圧を示す波形図と、直流電圧V11を示す波形図と、第1MOSFET12及び第2MOSFET13のスイッチング周期を示す波形図である。

【0051】

なお、図4の(a)では、3相交流電圧の線間電圧が電圧Vb11まで変化した場合の波形を示し、図4の(b)では、3相交流電圧の線間電圧が電圧Vb11まで変化した場合の直流電圧V11の波形を示し、図4の(c)では、3相交流電圧の線間電圧が電圧Vb11まで変化した場合の第1MOSFET12及び第2MOSFET13のスイッチング周期の波形を示している。そして、図4の(a),(b),(c)では、縦軸が電圧を示し、横軸が時間を示す。

【0052】

整流装置A2では、第1MOSFET12及び第2MOSFET13がONの場合、すなわち3相全波整流を行っている場合、図4の(a)に示す3相交流電圧の線間電圧のピーク電圧と、図4の(b)に示す直流電圧V11とが等しくなる。

【0053】

そして、制御部18は、直流電圧V11がしきい値Va11を超えると、第1MOSFET12及び第2MOSFET13をOFFすることによって、3相全波整流から2相半波整流に切り替え、これにより、図4の(b)に示すように、直流電圧V11がしきい値Va11を下回る電圧、すなわち降圧チョッパ回路Cの耐電圧を下回る電圧まで降圧させる。なお、図4の(b)には、比較の為に、整流装置A2が3相全波整流のみを行った場合の直流電圧V12と、整流装置A2が2相半波整流のみを行った場合の直流電圧V13との波形を示す。

【0054】

そして、制御部18は、直流電圧V11がしきい値Va11を下回る電圧まで降圧すると、第1MOSFET12及び第2MOSFET113をONにし、再び、直流電圧V11がしきい値Va11を超えると、第1MOSFET12及び第2MOSFET13をOFFにする。制御部18は、第1MOSFET12及び第2MOSFET13のONとOFFの切り替えを、図4の(c)に示すように、何度も繰り返すことによって、直流電圧V11をしきい値Va11を下回る電圧になるように制御する。

【0055】

以上のように、第2実施形態に係る整流装置A2では、制御部18が、出力端子16a,16bから出力する直流電圧V11がしきい値Va11を超えると、第1MOSFET12及び第2MOSFET13をOFFにすることによって、3相全波整流から2相半波整流に切り替える為に、降圧チョッパ回路Cへ出力する直流電圧V11を抑制することが出来る。これによって、降圧チョッパ回路Cに高耐圧の半導体デバイスを搭載しなくてもよい為に、降圧チョッパ回路の生産経費を抑制することが出来る。

【0056】

〔第3実施形態〕

次に、第3実施形態に係る整流装置A3について、説明する。

第3実施形態に係る整流装置A3の回路構成について、図5を参照して、説明する。図5は、第3実施形態に係る整流装置A3の構成を示す回路図である。

【0057】

整流装置A3は、第1実施形態に係る整流装置A1及び第2実施形態に係る整流装置A2と同様に、オルタネータBが発生させた交流電圧を直流電圧に変換し、当該直流電圧を降圧チョッパ回路Cを介して負荷Dへ出力するものであり、ブリッジ回路をサイリスタによって構成することによって、スイッチング素子であるMOSFETを搭載しない点において、第1実施形態に係る整流装置A1及び第2実施形態に係る整流装置A2と相違する。

【0058】

整流装置A3は、図5に示すように、整流用ブリッジ回路21、コンデンサ22、ダイオード23、出力端子24a,24b、電圧センサ25及び制御部26を備えている。なお、電圧センサ25及び制御部26が、第2実施形態における制御手段を構成する。

【0059】

整流用ブリッジ回路21は、オルタネータBが出力する3相交流電圧を整流することによって直流電圧に変換するブリッジ回路であり、整流用ダイオード21a及び整流用サイリスタ21b〜21fを備えている。

整流用ダイオード21aは、カソード端子が、正極側の出力端子24aに接続され、アノード端子が、オルタネータBのU相巻線及び整流用サイリスタ21dのカソード端子に接続されている。

【0060】

整流用サイリスタ21bは、カソード端子が、正極側の出力端子24aに接続され、アノード端子が、オルタネータBのV相巻線及び整流用サイリスタ21eのカソード端子に接続され、ゲート端子が制御部26に接続されている。

整流用サイリスタ21cは、カソード端子が、正極側の出力端子24aに接続され、アノード端子が、オルタネータBのW相巻線及び整流用サイリスタ21fのカソード端子に接続され、ゲート端子が制御部26に接続されている。

【0061】

整流用サイリスタ21dは、カソード端子が、オルタネータBのU相巻線及び整流用ダイオード21aのアノード端子に接続され、アノード端子が、負極側の出力端子24bに接続され、ゲート端子が制御部26に接続されている。

整流用サイリスタ21eは、カソード端子が、オルタネータBのV相巻線及び整流用サイリスタ21bのアノード端子に接続され、アノード端子が、負極側の出力端子24bに接続され、ゲート端子が制御部26に接続されている。

【0062】

整流用サイリスタ21fは、カソード端子が、オルタネータBのW相巻線及び整流用サイリスタ21cのアノード端子に接続され、アノード端子が、負極側の出力端子24bに接続され、ゲート端子が制御部26に接続されている。

【0063】

コンデンサ22は、降圧チョッパ回路Cへ出力する直流電圧の平滑化、すなわち直流電圧のリップルを低減することを目的として設けられたものであり、一端が、整流用ダイオード21aのカソード端子、整流用サイリスタ21bのカソード端子、整流用サイリスタ21cのカソード端子及び一方の出力端子24aに接続され、他端が、整流用サイリスタ21dのアノード端子、整流用サイリスタ21eのアノード端子、整流用サイリスタ21fのアノード端子及びダイオード23のアノード端子及び他方の出力端子24bに接続されている。

ダイオード23は、アノード端子がコンデンサ22の他端及び他方の出力端子24bに接続され、カソード端子がオルタネータBに接続されている。

【0064】

出力端子24a,24bは、整流装置A3が交流電圧を整流することによって変換した直流電圧を降圧チョッパ回路Cへ出力するための一対の接続端子であり、一方の正極側の出力端子24aが、整流用ダイオード21aのカソード端子、整流用サイリスタ21bのカソード端子、整流用サイリスタ21cのカソード端子及びコンデンサ22の一端に接続され、他方の負極側の出力端子24bが、整流用サイリスタ21dのアノード端子、整流用サイリスタ21eのアノード端子、整流用サイリスタ21fのアノード端子、コンデンサ22の他端及びダイオード23のアノード端子に接続されている。

【0065】

電圧センサ25は、整流装置A3が出力端子24a,24bから降圧チョッパ回路Cへ出力する直流電圧を検出するセンサであり、図5に示すように、一方の端子が一方の出力端子24aに接続され、他方の端子が他方の出力端子24bに接続されている。そして、この電圧センサ25は、検出結果に基づいて、出力端子24a,24bから出力する直流電圧を示す検出信号Sv21を制御部26へ出力する。

【0066】

制御部26は、整流用サイリスタ21b〜21fの各ゲート端子とと信号の入出力を行うインタフェース回路等から構成されており、上記電圧センサ25から入力される検出信号Sv11に基づいて、整流用サイリスタ21b〜21fを制御する。

【0067】

次に、このように構成された第2実施形態に係る整流装置A3の動作について、詳しく説明する。

整流装置A3では、オルタネータBが回転によって3相交流電圧の出力を開始すると、整流用ブリッジ回路21が交流電圧を直流電圧V21へ変換し、当該直流電圧V21を出力端子24a,24bから降圧チョッパ回路Cへ出力する。電圧センサ25は、直流電圧V21の出力動作の開始に伴って、制御部26への検出信号Sv21の出力を開始する。そして、オルタネータBの回転数の上昇に伴って、整流装置A3では、オルタネータBから入力される3相交流電圧が上昇する。

【0068】

制御部26は、電圧センサ25から検出信号Sv21が入力されると、当該検出信号Sv21に基づいて、出力端子24a,24bから出力する直流電圧V21が、降圧チョッパ回路Cの耐電圧を示すしきい値Va21を超えたか否か判断する。そして、制御部26は、直流電圧V21がしきい値Va21を超えると、整流用サイリスタ21b〜21fをOFFにする。

【0069】

そして、整流装置A3では、整流用サイリスタ21b〜21fがOFFになることによって、整流用ダイオード21aのみが整流に使用される為に、3相全波整流から単相半波整流に切り替わる。その為、整流装置A3の出力端子24a,24bから出力する直流電圧V21が低下する。

【0070】

そして、制御部26は、直流電圧V21がしきい値Va21を下回る電圧まで降圧するとと、整流用サイリスタ21b〜21fをONにし、再び、直流電圧V21がしきい値Va21を超えると、整流用サイリスタ21b〜21fをOFFにする。制御部18は、整流用サイリスタ21b〜21fのONとOFFの切り替えを、何度も繰り返すことによって、直流電圧V21をしきい値Va21を下回る電圧になるように制御する。

【0071】

以上のように、第3実施形態に係る整流装置A3では、制御部26が、出力端子24a,24bから出力する直流電圧V21がしきい値Va21を超えると、整流用サイリスタ21b〜21fをOFFにすることによって、3相全波整流から単相半波整流に切り替える為に、降圧チョッパ回路Cへ出力する直流電圧V21を抑制することが出来る。これによって、降圧チョッパ回路Cに高耐圧の半導体デバイスを搭載しなくてもよい為に、降圧チョッパ回路の生産経費を抑制することが出来る。

【0072】

以上、本発明の第3実施形態について説明したが、本発明は上記第3実施形態に限定されることなく、例えば以下のような変形が考えられる。

(1)上記第3実施形態に係る整流装置A3では、整流用ブリッジ回路21を、1個の整流用ダイオード21aと、5個の整流用サイリスタ21b〜21fによって構成したが、本発明はこれに限定されない。

【0073】

例えば、整流用サイリスタ21bを整流用ダイオードに置き換え、制御部26が、直流電圧V21がしきい値Va21を超えると、整流用サイリスタ21c〜21fをOFFにすることによって、3相全波整流から2相半波整流に切り替えるようにすれば、第2実施形態の整流装置A2と同じ動作を行うことが出来る。

【0074】

また、整流用サイリスタ21b,21cを整流用ダイオードに置き換え、制御部26が、直流電圧V21がしきい値Va21を超えると、整流用サイリスタ21d〜21fをOFFにすることによって、3相全波整流から単相全波整流に切り替えるようにしてもよい。

さらに、整流用ダイオード21aを整流用サイリスタに置き換え、制御部26が、直流電圧V21に応じて、各整流用サイリスタのON/OFFを制御することによって、直流電圧V21を0ボルト〜ピーク電圧までの間で段階的に変化させる、すなわち直流電圧V21の出力制御をするようにしてもよい。

【符号の説明】

【0075】

A1,A2,Å3…整流装置、B…オルタネータ、C…降圧チョッパ回路、D…負荷、1…整流用ブリッジ回路、1a〜1f…整流用ダイオード、2…第1MOSFET、3…第2MOSFET、4…コンデンサ、5…ダイオード、6a,6b…出力端子、7…電圧センサ、8…制御部、11…整流用ブリッジ回路、11a〜11f…整流用ダイオード、12…第1MOSFET、13…第2MOSFET、14…コンデンサ、15…ダイオード、16a,16b…出力端子、17…電圧センサ、18…制御部、21…整流用ブリッジ回路、21a…整流用ダイオード、21b〜21f…整流用サイリスタ、22…コンデンサ、23…ダイオード、24a,24b…出力端子、25…電圧センサ、26…制御部

【技術分野】

【0001】

本発明は、オルタネータ等の発電機が出力した電圧の整流装置に関する。

【背景技術】

【0002】

従来、航空機では、エンジンによって回転駆動するオルタネータ(発電機)が出力する3相交流電圧を、整流装置によって直流電圧へ変換し、当該直流電圧をスイッチングシャントによって所望の電圧まで降圧することによって、各種負荷装置を稼動する電圧として使用している。しかしながら、このスイッチングシャントでは、余った電圧をオルタネータへ戻している為、この電圧によってオルタネータが発熱してしまうという課題を抱えていた。その為に、スイッチングシャントの代わりに、降圧用DC/DCコンバータとして、降圧チョッパ回路を使用することが検討されている。しかしながら、降圧チョッパ回路では、整流装置からの入力される直流電圧がFET(Field Effect Transistor)等のスイッチング素子に印加される為、高い直流電圧に耐えることが出来るスイッチング素子を搭載しなければならないという課題を抱えている。

【0003】

そして、上記課題を解決する整流装置として、下記特許文献1には、可変電圧交流電源によって発生された電圧の範囲を圧縮するように自動的に動作する整流回路が開示されている。

この整流回路は、交流電源が出力する交流電圧を直流電圧に変換する整流回路であって、電源に接続されると共に整流回路の第1の出力端子に一方の極性の出力電圧を発生する第1の整流手段と、電源に接続されると共に整流回路の第2の出力端子に反対の極性の出力電圧を発生する第2の整流手段と、一端が電源に結合されると共に他端が第2の出力端子に結合されている一方向導電性素子と、第2の整流手段または一方向導電性素子のいずれかを非導通状態にするように選択的に動作するスイッチング手段とを有し、一方向導電性素子が非導通状態にあるときは3相全波整流回路として動作し、また第2の整流手段が非導通状態にあるときは3相半波整流回路として動作することによって、出力する直流電圧の範囲を交流電源の電圧範囲よりも狭くする。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭62−155775号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、上記従来技術では、出力する直流電圧に応じて、3相全波整流回路として動作していた整流回路を、3相半波整流回路として動作させることによって、出力する直流電圧を降圧している。しかしながら、航空機では、オルタネータが出力した交流電圧を、3相半波整流回路として動作する整流回路によって整流しただけでは、直流電圧の降圧が十分ではない為に、高い直流電圧が降圧チョッパ回路に印加されてしまう。この為、降圧チョッパ回路では、スイッチング素子として、高い直流電圧に耐えることが出来る半導体デバイスを搭載しなければならなかった。

【0006】

本発明は、上述した事情に鑑みてなされたものであり、従来よりも降圧チョッパに印加される電圧を抑制することが出来る整流装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明では、整流装置に係る第1の解決手段として、3相交流電圧を整流することによって直流電圧へ変換し、当該直流電圧を出力する整流装置であって、整流した直流電圧が所定のしきい値を超えた場合に、直流電圧の生成に供する相電圧を減らすという手段を採用する。

【0008】

本発明では、整流装置に係る第2の解決手段として、上記第1の解決手段において、3相の交流電圧に応じた3対の整流用ダイオードから構成された整流用ブリッジ回路と、前記整流用ブリッジ回路の正極側の出力端に接続する2個の整流用ダイオードのカソード端子に接続する第1のスイッチング手段と、前記整流用ブリッジ回路の負極側の出力端に接続する3個の整流用ダイオードのアノード端子に接続する第2のスイッチング手段と、3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、前記第1のスイッチン手段及び前記第2のスイッチング手段をOFFにすることによって、前記整流用ブリッジ回路の動作を3相全波整流から単相半波整流へ切り替える制御手段とを、具備するという手段を採用する。

【0009】

本発明では、整流装置に係る第3の解決手段として、上記第1の解決手段において、3相の交流電圧に応じた3対の整流用ダイオードから構成された整流用ブリッジ回路と、前記整流用ブリッジ回路の正極側の出力端に接続する1個の整流用ダイオードのカソード端子に接続する第1のスイッチング手段と、前記整流用ブリッジ回路の負極側の出力端に接続する3個の整流用ダイオードのアノード端子に接続する第2のスイッチング手段と、3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、前記第1のスイッチン手段及び前記第2のスイッチング手段をOFFにすることによって、前記整流用ブリッジ回路の動作を3相全波整流から2相半波整流へ切り替える制御手段とを、具備するという手段を採用する。

【0010】

本発明では、整流装置に係る第4の解決手段として、上記第1の解決手段において、3相の交流電圧に応じた合計6個の整流用ダイオード及び整流用サイリスタから構成され、前記合計6個の内、少なくとも3つは、負極側の出力端にアノード端子が接続する整流用サイリスタである整流用ブリッジ回路と、3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、少なくとも前記整流用ブリッジ回路の負極側の出力端にアノード端子が接続する整流用サイリスタをOFFにする制御手段とを、具備するという手段を採用する。

【発明の効果】

【0011】

本発明によれば、整流装置が、3相交流電圧を整流することによって直流電圧へ変換し、当該直流電圧を出力する整流装置であって、整流した直流電圧が所定のしきい値を超えた場合に、直流電圧の生成に供する相電圧を減らす。

このように、整流装置が、整流した直流電圧がしきい値を超えると、直流電圧の生成に供する相電圧を減らすことによって、従来行われていた3相全波整流から3相半波整流への切り替える方法よりも直流電圧を抑制することが出来る。これにより、従来よりも降圧チョッパに印加される電圧を抑制することが出来る。

【図面の簡単な説明】

【0012】

【図1】本発明の第1実施形態に係る整流装置A1の構成を示す回路図である。

【図2】本発明の第1実施形態に係る整流装置A1の入力された3相交流電圧の線間電圧を示す波形図と、直流電圧V1を示す波形図と、第1MOSFET2及び第2MOSFET3のスイッチング周期を示す波形図である。

【図3】本発明の第2実施形態に係る整流装置A2の構成を示す回路図である。

【図4】本発明の第2実施形態に係る整流装置A2の入力された3相交流電圧の線間電圧を示す波形図と、直流電圧V11を示す波形図と、第1MOSFET12及び第2MOSFET13のスイッチング周期を示す波形図である。

【図5】本発明の第2第3実施形態に係る整流装置A3の構成を示す回路図である。

【発明を実施するための形態】

【0013】

以下、図面を参照して、本発明の実施形態について説明する。

〔第1実施形態〕

まず、第1実施形態に係る整流装置A1について、説明する。

第1実施形態に係る整流装置A1の回路構成について、図1を参照して、説明する。図1は、第1実施形態に係る整流装置A1の構成を示す回路図である。

【0014】

整流装置A1は、オルタネータBが発生させた交流電圧を直流電圧に変換し、当該直流電圧を降圧チョッパ回路Cを介して負荷Dへ出力するものであり、図1に示すように、整流用ブリッジ回路1、第1MOSFET2、第2MOSFET3、コンデンサ4、ダイオード5、出力端子6a,6b、電圧センサ7及び制御部8を備えている。

なお、第1MOSFET2は、第1実施形態における第1のスイッチング手段であり、第2MOSFET3は、第1実施形態における第2のスイッチング手段である。また、電圧センサ7及び制御部8が、第1実施形態における制御手段を構成する。

【0015】

整流用ブリッジ回路1は、オルタネータBが出力する3相交流電圧を整流することによって直流電圧に変換するブリッジ回路であり、整流用ダイオード1a〜1fを備えている。

整流用ダイオード1aは、カソード端子が、正極側の出力端子6aに接続され、アノード端子が、オルタネータBのU相巻線及び整流用ダイオード1dのカソード端子に接続されている。

【0016】

整流用ダイオード1bは、カソード端子が、第1MOSFET2のドレイン端子に接続され、アノード端子が、オルタネータBのV相巻線及び整流用ダイオード1eのカソード端子に接続されている。

整流用ダイオード1cは、カソード端子が、第1MOSFET2のドレイン端子に接続され、アノード端子が、オルタネータBのW相巻線及び整流用ダイオード1fのカソード端子に接続されている。

【0017】

整流用ダイオード1dは、カソード端子が、オルタネータBのU相巻線及び整流用ダイオード1aのアノード端子に接続され、アノード端子が、第2MOSFET3のソース端子に接続されている。

整流用ダイオード1eは、カソード端子が、オルタネータBのV相巻線及び整流用ダイオード1bのアノード端子に接続され、アノード端子が、第2MOSFET3のソース端子に接続されている。

【0018】

整流用ダイオード1fは、カソード端子が、オルタネータBのW相巻線及び整流用ダイオード1cのアノード端子に接続され、アノード端子が、第2MOSFET3のソース端子に接続されている。

【0019】

第1MOSFET2では、ドレイン端子が整流用ダイオード1bのカソード端子及び整流用ダイオード1cのカソード端子に接続され、ソース端子が、コンデンサ4の一端及び一方の出力端子6aに接続され、さらにゲート端子が制御部8に接続されている。

第2MOSFET3では、ドレイン端子がコンデンサ4の他端及び負極側の出力端子6bに接続され、ソース端子が整流用ダイオード1dのアノード端子、整流用ダイオード1eのアノード端子及び整流用ダイオード1fのアノード端子に接続され、さらにゲート端子が制御部8にされている。

【0020】

コンデンサ4は、降圧チョッパ回路Cへ出力する直流電圧の平滑化、すなわち直流電圧のリップルを低減することを目的として設けられたものであり、一端が、整流用ダイオード1aのカソード端子、第1第1MOSFET2のソース端子及び一方の出力端子6aに接続され、他端が、第2第1MOSFET3のドレイン端子、ダイオード5のアノード端子及び他方の出力端子6bに接続されている。

ダイオード5は、アノード端子がコンデンサ4の他端及び他方の出力端子6bに接続され、カソード端子がオルタネータBに接続されている。

【0021】

出力端子6a,6bは、整流装置A1が交流電圧を整流することによって変換した直流電圧を降圧チョッパ回路Cへ出力するための一対の接続端子であり、一方の正極側の出力端子6aが、整流用ダイオード1aのカソード端子、第1MOSFET2のソース端子及びコンデンサ4の一端に接続され、他方の負極側の出力端子6bが、コンデンサ4の他端、第2MOSFET3のドレイン端子及びダイオード5のアノード端子に接続されている。

【0022】

電圧センサ7は、整流装置A1が出力端子6a,6bから降圧チョッパ回路Cへ出力する直流電圧を検出するセンサであり、図1に示すように、一方の端子が一方の出力端子6aに接続され、他方の端子が他方の出力端子6bに接続されている。そして、この電圧センサ7は、検出結果に基づいて、出力端子6a,6bから出力する直流電圧を示す検出信号Sv1を制御部8へ出力する。

【0023】

制御部8は、第1MOSFET2と第2MOSFET3と信号の入出力を行うインタフェース回路等から構成されており、上記電圧センサ7から入力される検出信号Sv1に基づいて、第1MOSFET2及び第2MOSFET3を制御する。なお、制御部8は、半導体デバイス等のハードウェアのみによって制御を行う制御回路であってもよいし、またCPU(Central Processing Unit)、ROM(Read Only Memory)及びRAM(Random Access Memory)から構成され、上記ROMに記憶された制御プログラムに基づいて制御を行うソフトウェアを用いた制御回路であってもよい。

【0024】

次に、このように構成された第1実施形態に係る整流装置A1の動作について、詳しく説明する。

整流装置A1では、オルタネータBが回転によって3相交流電圧の出力を開始すると、整流用ブリッジ回路1が交流電圧を直流電圧V1へ変換し、当該直流電圧V1を出力端子6a,6bから降圧チョッパ回路Cへ出力する。電圧センサ7は、直流電圧V1の出力動作の開始に伴って、制御部8への検出信号Sv1の出力を開始する。そして、オルタネータBの回転数の上昇に伴って、整流装置A1では、オルタネータBから入力される3相交流電圧が上昇する。

【0025】

制御部8は、電圧センサ7から検出信号Sv1が入力されると、当該検出信号Sv1に基づいて、出力端子6a,6bから出力する直流電圧V1が、降圧チョッパ回路Cの耐電圧を示すしきい値Va1を超えたか否か判断する。そして、制御部8は、直流電圧V1がしきい値Va1を超えると、第1MOSFET2及び第2MOSFET3をOFFにする。

【0026】

そして、整流装置A1では、第1MOSFET2及び第2MOSFET3がOFFになることによって、整流用ダイオード1aのみが整流に使用される為に、3相全波整流から単相半波整流に切り替わる。その為、整流装置A1の出力端子6a,6bから出力する直流電圧V1が低下する。

【0027】

整流装置A1の上記動作について、図2を参照して、詳しく説明する。

図2は、第1実施形態に係る整流装置A1の入力された3相交流電圧の線間電圧を示す波形図と、直流電圧V1を示す波形図と、第1MOSFET2及び第2MOSFET3のスイッチング周期を示す波形図である。

【0028】

なお、図2の(a)では、3相交流電圧の線間電圧が電圧Vb1まで変化した場合の波形を示し、図2の(b)では、3相交流電圧の線間電圧が電圧Vb1まで変化した場合の直流電圧V1の波形を示し、図2の(c)では、3相交流電圧の線間電圧が電圧Vb1まで変化した場合の第1MOSFET2及び第2MOSFET3のスイッチング周期の波形を示している。そして、図2の(a),(b),(c)では、縦軸が電圧を示し、横軸が時間を示す。

【0029】

整流装置A1では、第1MOSFET2及び第2MOSFET3がONの場合、すなわち3相全波整流を行っている場合、図2の(a)に示す3相交流電圧の線間電圧のピーク電圧と、図2の(b)に示す直流電圧V1とが等しくなる。

そして、制御部8は、直流電圧V1がしきい値Va1を超えると、第1MOSFET2及び第2MOSFET3をOFFすることによって、3相全波整流から単相半波整流に切り替え、これにより、図2の(b)に示すように、直流電圧V1がしきい値Va1を下回る電圧、すなわち降圧チョッパ回路Cの耐電圧を下回る電圧まで降圧させる。

【0030】

整流装置A1では、単相半波整流を行っている場合に、直流電圧V1が、3相交流電圧の線間電圧のピーク電圧の(1/√3)に等しくなる。なお、図2の(b)には、比較の為に、整流装置A1が3相全波整流のみを行った場合の直流電圧V2と、整流装置A1が単相半波整流のみを行った場合の直流電圧V3との波形を示す。

【0031】

そして、制御部8は、直流電圧V1がしきい値Va1を下回る電圧まで降圧すると、第1MOSFET2及び第2MOSFET3をONにし、再び、直流電圧V1がしきい値Va1を超えると、第1MOSFET2及び第2MOSFET3をOFFにする。制御部8は、第1MOSFET2及び第2MOSFET3のONとOFFの切り替えを、図2の(c)に示すように、何度も繰り返すことによって、直流電圧V1をしきい値Va1を下回る電圧になるように制御する。

【0032】

以上のように、第1実施形態に係る整流装置A1では、制御部8が、出力端子6a,6bから出力する直流電圧V1がしきい値Va1を超えると、第1MOSFET2及び第2MOSFET3をOFFにすることによって、3相全波整流から単相半波整流に切り替える為に、降圧チョッパ回路Cへ出力する直流電圧V1を抑制することが出来る。これによって、降圧チョッパ回路Cに高耐圧の半導体デバイスを搭載しなくてもよい為に、降圧チョッパ回路の生産経費を抑制することが出来る。

【0033】

以上、本発明の第1実施形態について説明したが、本発明は上記第1実施形態に限定されることなく、例えば以下のような変形が考えられる。

(1)上記第1実施形態に係る整流装置A1では、直流電圧V1がしきい値Va1を超えると、第1MOSFET2及び第2MOSFET3をOFFにすることによって、3相全波整流から単相半波整流に切り替え、これによって直流電圧V1を抑制したが、本発明はこれに限定されない。

【0034】

例えば、制御部8が、電圧センサ7から入力される検出信号Sv1に基づいて、直流電圧V1がしきい値Va1を超えたと判断すると、オルタネータBの回転数を低下させることによって、しきい値Va1を下回る電圧まで直流電圧V1を降圧するようにしてもよい。

【0035】

〔第2実施形態〕

次に、第2実施形態に係る整流装置A2について、説明する。

第2実施形態に係る整流装置A2の回路構成について、図3を参照して、説明する。図3は、第2実施形態に係る整流装置A2の構成を示す回路図である。

【0036】

整流装置A2は、第1実施形態に係る整流装置A1と同様に、オルタネータBが発生させた交流電圧を直流電圧に変換し、当該直流電圧を降圧チョッパ回路Cを介して負荷Dへ出力するものであり、ブリッジ回路の結線が異なる点において、第1実施形態に係る整流装置A1と相違する。

【0037】

整流装置A2は、図3に示すように、整流用ブリッジ回路11、第1MOSFET12、第2MOSFET13、コンデンサ14、ダイオード15、出力端子16a,16b、電圧センサ17及び制御部18を備えている。なお、第1MOSFET12は、第2実施形態における第1のスイッチング手段であり、第2MOSFET13は、第2実施形態における第2のスイッチング手段である。また、電圧センサ17及び制御部18が、第2実施形態における制御手段を構成する。

【0038】

整流用ブリッジ回路11は、オルタネータBが出力する3相交流電圧を整流することによって直流電圧に変換するブリッジ回路であり、整流用ダイオード11a〜11fを備えている。

整流用ダイオード11aは、カソード端子が、正極側の出力端子16aに接続され、アノード端子が、オルタネータBのU相巻線及び整流用ダイオード11dのカソード端子に接続されている。

【0039】

整流用ダイオード11bは、カソード端子が、正極側の出力端子16aに接続され、アノード端子が、オルタネータBのV相巻線及び整流用ダイオード11eのカソード端子に接続されている。

整流用ダイオード11cは、カソード端子が、第1MOSFET12のドレイン端子に接続され、アノード端子が、オルタネータBのW相巻線及び整流用ダイオード11fのカソード端子に接続されている。

【0040】

整流用ダイオード11dは、カソード端子が、オルタネータBのU相巻線及び整流用ダイオード11aのアノード端子に接続され、アノード端子が、第2MOSFET13のソース端子に接続されている。

整流用ダイオード11eは、カソード端子が、オルタネータBのV相巻線及び整流用ダイオード11bのアノード端子に接続され、アノード端子が、第2MOSFET13のソース端子に接続されている。

【0041】

整流用ダイオード11fは、カソード端子が、オルタネータBのW相巻線及び整流用ダイオード11cのアノード端子に接続され、アノード端子が、第2MOSFET13のソース端子に接続されている。

【0042】

第1MOSFET12では、ドレイン端子が整流用ダイオード11cのカソード端子に接続され、ソース端子が、コンデンサ14の一端及び一方の出力端子16aに接続され、さらにゲート端子が制御部18に接続されている。

第2MOSFET13では、ドレイン端子がコンデンサ14の他端及び負極側の出力端子16bに接続され、ソース端子が整流用ダイオード11dのアノード端子、整流用ダイオード11eのアノード端子及び整流用ダイオード11fのアノード端子に接続され、さらにゲート端子が制御部18にされている。

【0043】

コンデンサ14は、降圧チョッパ回路Cへ出力する直流電圧の平滑化、すなわち直流電圧のリップルを低減することを目的として設けられたものであり、一端が、整流用ダイオード11aのカソード端子、整流用ダイオード11bのカソード端子、第1第1MOSFET12のソース端子及び一方の出力端子16aに接続され、他端が、第2第1MOSFET3のドレイン端子、ダイオード15のアノード端子及び他方の出力端子16bに接続されている。

ダイオード15は、アノード端子がコンデンサ14の他端及び他方の出力端子16bに接続され、カソード端子がオルタネータBに接続されている。

【0044】

出力端子16a,16bは、整流装置A2が交流電圧を整流することによって変換した直流電圧を降圧チョッパ回路Cへ出力するための一対の接続端子であり、一方の正極側の出力端子16aが、整流用ダイオード11aのカソード端子、整流用ダイオード11bのカソード端子、第1MOSFET12のソース端子及びコンデンサ14の一端に接続され、他方の負極側の出力端子16bが、コンデンサ14の他端、第2MOSFET13のドレイン端子及びダイオード15のアノード端子に接続されている。

【0045】

電圧センサ17は、整流装置A2が出力端子16a,16bから降圧チョッパ回路Cへ出力する直流電圧を検出するセンサであり、図3に示すように、一方の端子が一方の出力端子16aに接続され、他方の端子が他方の出力端子16bに接続されている。そして、この電圧センサ17は、検出結果に基づいて、出力端子16a,16bから出力する直流電圧を示す検出信号Sv11を制御部18へ出力する。

【0046】

制御部18は、第1MOSFET12と第2MOSFET13と信号の入出力を行うインタフェース回路等から構成されており、上記電圧センサ17から入力される検出信号Sv11に基づいて、第1MOSFET12及び第2MOSFET13を制御する。

【0047】

次に、このように構成された第2実施形態に係る整流装置A2の動作について、詳しく説明する。

整流装置A2では、オルタネータBが回転によって3相交流電圧の出力を開始すると、整流用ブリッジ回路11が交流電圧を直流電圧V11へ変換し、当該直流電圧V11を出力端子16a,16bから降圧チョッパ回路Cへ出力する。電圧センサ17は、直流電圧V11の出力動作の開始に伴って、制御部18への検出信号Sv11の出力を開始する。そして、オルタネータBの回転数の上昇に伴って、整流装置A2では、オルタネータBから入力される3相交流電圧が上昇する。

【0048】

制御部18は、電圧センサ17から検出信号Sv11が入力されると、当該検出信号Sv11に基づいて、出力端子16a,16bから出力する直流電圧V11が、降圧チョッパ回路Cの耐電圧を示すしきい値Va11を超えたか否か判断する。そして、制御部18は、直流電圧V11がしきい値Va11を超えると、第1MOSFET12及び第2MOSFET13をOFFにする。

【0049】

そして、整流装置A2では、第1MOSFET12及び第2MOSFET13がOFFになることによって、整流用ダイオード11a,11bのみが整流に使用される為に、3相全波整流から2相半波整流に切り替わる。その為、整流装置A2の出力端子16a,6bから出力する直流電圧V11が低下する。

【0050】

整流装置A2の上記動作について、図4を参照して、詳しく説明する。

図4は、第2実施形態に係る整流装置A2の入力された3相交流電圧の線間電圧を示す波形図と、直流電圧V11を示す波形図と、第1MOSFET12及び第2MOSFET13のスイッチング周期を示す波形図である。

【0051】

なお、図4の(a)では、3相交流電圧の線間電圧が電圧Vb11まで変化した場合の波形を示し、図4の(b)では、3相交流電圧の線間電圧が電圧Vb11まで変化した場合の直流電圧V11の波形を示し、図4の(c)では、3相交流電圧の線間電圧が電圧Vb11まで変化した場合の第1MOSFET12及び第2MOSFET13のスイッチング周期の波形を示している。そして、図4の(a),(b),(c)では、縦軸が電圧を示し、横軸が時間を示す。

【0052】

整流装置A2では、第1MOSFET12及び第2MOSFET13がONの場合、すなわち3相全波整流を行っている場合、図4の(a)に示す3相交流電圧の線間電圧のピーク電圧と、図4の(b)に示す直流電圧V11とが等しくなる。

【0053】

そして、制御部18は、直流電圧V11がしきい値Va11を超えると、第1MOSFET12及び第2MOSFET13をOFFすることによって、3相全波整流から2相半波整流に切り替え、これにより、図4の(b)に示すように、直流電圧V11がしきい値Va11を下回る電圧、すなわち降圧チョッパ回路Cの耐電圧を下回る電圧まで降圧させる。なお、図4の(b)には、比較の為に、整流装置A2が3相全波整流のみを行った場合の直流電圧V12と、整流装置A2が2相半波整流のみを行った場合の直流電圧V13との波形を示す。

【0054】

そして、制御部18は、直流電圧V11がしきい値Va11を下回る電圧まで降圧すると、第1MOSFET12及び第2MOSFET113をONにし、再び、直流電圧V11がしきい値Va11を超えると、第1MOSFET12及び第2MOSFET13をOFFにする。制御部18は、第1MOSFET12及び第2MOSFET13のONとOFFの切り替えを、図4の(c)に示すように、何度も繰り返すことによって、直流電圧V11をしきい値Va11を下回る電圧になるように制御する。

【0055】

以上のように、第2実施形態に係る整流装置A2では、制御部18が、出力端子16a,16bから出力する直流電圧V11がしきい値Va11を超えると、第1MOSFET12及び第2MOSFET13をOFFにすることによって、3相全波整流から2相半波整流に切り替える為に、降圧チョッパ回路Cへ出力する直流電圧V11を抑制することが出来る。これによって、降圧チョッパ回路Cに高耐圧の半導体デバイスを搭載しなくてもよい為に、降圧チョッパ回路の生産経費を抑制することが出来る。

【0056】

〔第3実施形態〕

次に、第3実施形態に係る整流装置A3について、説明する。

第3実施形態に係る整流装置A3の回路構成について、図5を参照して、説明する。図5は、第3実施形態に係る整流装置A3の構成を示す回路図である。

【0057】

整流装置A3は、第1実施形態に係る整流装置A1及び第2実施形態に係る整流装置A2と同様に、オルタネータBが発生させた交流電圧を直流電圧に変換し、当該直流電圧を降圧チョッパ回路Cを介して負荷Dへ出力するものであり、ブリッジ回路をサイリスタによって構成することによって、スイッチング素子であるMOSFETを搭載しない点において、第1実施形態に係る整流装置A1及び第2実施形態に係る整流装置A2と相違する。

【0058】

整流装置A3は、図5に示すように、整流用ブリッジ回路21、コンデンサ22、ダイオード23、出力端子24a,24b、電圧センサ25及び制御部26を備えている。なお、電圧センサ25及び制御部26が、第2実施形態における制御手段を構成する。

【0059】

整流用ブリッジ回路21は、オルタネータBが出力する3相交流電圧を整流することによって直流電圧に変換するブリッジ回路であり、整流用ダイオード21a及び整流用サイリスタ21b〜21fを備えている。

整流用ダイオード21aは、カソード端子が、正極側の出力端子24aに接続され、アノード端子が、オルタネータBのU相巻線及び整流用サイリスタ21dのカソード端子に接続されている。

【0060】

整流用サイリスタ21bは、カソード端子が、正極側の出力端子24aに接続され、アノード端子が、オルタネータBのV相巻線及び整流用サイリスタ21eのカソード端子に接続され、ゲート端子が制御部26に接続されている。

整流用サイリスタ21cは、カソード端子が、正極側の出力端子24aに接続され、アノード端子が、オルタネータBのW相巻線及び整流用サイリスタ21fのカソード端子に接続され、ゲート端子が制御部26に接続されている。

【0061】

整流用サイリスタ21dは、カソード端子が、オルタネータBのU相巻線及び整流用ダイオード21aのアノード端子に接続され、アノード端子が、負極側の出力端子24bに接続され、ゲート端子が制御部26に接続されている。

整流用サイリスタ21eは、カソード端子が、オルタネータBのV相巻線及び整流用サイリスタ21bのアノード端子に接続され、アノード端子が、負極側の出力端子24bに接続され、ゲート端子が制御部26に接続されている。

【0062】

整流用サイリスタ21fは、カソード端子が、オルタネータBのW相巻線及び整流用サイリスタ21cのアノード端子に接続され、アノード端子が、負極側の出力端子24bに接続され、ゲート端子が制御部26に接続されている。

【0063】

コンデンサ22は、降圧チョッパ回路Cへ出力する直流電圧の平滑化、すなわち直流電圧のリップルを低減することを目的として設けられたものであり、一端が、整流用ダイオード21aのカソード端子、整流用サイリスタ21bのカソード端子、整流用サイリスタ21cのカソード端子及び一方の出力端子24aに接続され、他端が、整流用サイリスタ21dのアノード端子、整流用サイリスタ21eのアノード端子、整流用サイリスタ21fのアノード端子及びダイオード23のアノード端子及び他方の出力端子24bに接続されている。

ダイオード23は、アノード端子がコンデンサ22の他端及び他方の出力端子24bに接続され、カソード端子がオルタネータBに接続されている。

【0064】

出力端子24a,24bは、整流装置A3が交流電圧を整流することによって変換した直流電圧を降圧チョッパ回路Cへ出力するための一対の接続端子であり、一方の正極側の出力端子24aが、整流用ダイオード21aのカソード端子、整流用サイリスタ21bのカソード端子、整流用サイリスタ21cのカソード端子及びコンデンサ22の一端に接続され、他方の負極側の出力端子24bが、整流用サイリスタ21dのアノード端子、整流用サイリスタ21eのアノード端子、整流用サイリスタ21fのアノード端子、コンデンサ22の他端及びダイオード23のアノード端子に接続されている。

【0065】

電圧センサ25は、整流装置A3が出力端子24a,24bから降圧チョッパ回路Cへ出力する直流電圧を検出するセンサであり、図5に示すように、一方の端子が一方の出力端子24aに接続され、他方の端子が他方の出力端子24bに接続されている。そして、この電圧センサ25は、検出結果に基づいて、出力端子24a,24bから出力する直流電圧を示す検出信号Sv21を制御部26へ出力する。

【0066】

制御部26は、整流用サイリスタ21b〜21fの各ゲート端子とと信号の入出力を行うインタフェース回路等から構成されており、上記電圧センサ25から入力される検出信号Sv11に基づいて、整流用サイリスタ21b〜21fを制御する。

【0067】

次に、このように構成された第2実施形態に係る整流装置A3の動作について、詳しく説明する。

整流装置A3では、オルタネータBが回転によって3相交流電圧の出力を開始すると、整流用ブリッジ回路21が交流電圧を直流電圧V21へ変換し、当該直流電圧V21を出力端子24a,24bから降圧チョッパ回路Cへ出力する。電圧センサ25は、直流電圧V21の出力動作の開始に伴って、制御部26への検出信号Sv21の出力を開始する。そして、オルタネータBの回転数の上昇に伴って、整流装置A3では、オルタネータBから入力される3相交流電圧が上昇する。

【0068】

制御部26は、電圧センサ25から検出信号Sv21が入力されると、当該検出信号Sv21に基づいて、出力端子24a,24bから出力する直流電圧V21が、降圧チョッパ回路Cの耐電圧を示すしきい値Va21を超えたか否か判断する。そして、制御部26は、直流電圧V21がしきい値Va21を超えると、整流用サイリスタ21b〜21fをOFFにする。

【0069】

そして、整流装置A3では、整流用サイリスタ21b〜21fがOFFになることによって、整流用ダイオード21aのみが整流に使用される為に、3相全波整流から単相半波整流に切り替わる。その為、整流装置A3の出力端子24a,24bから出力する直流電圧V21が低下する。

【0070】

そして、制御部26は、直流電圧V21がしきい値Va21を下回る電圧まで降圧するとと、整流用サイリスタ21b〜21fをONにし、再び、直流電圧V21がしきい値Va21を超えると、整流用サイリスタ21b〜21fをOFFにする。制御部18は、整流用サイリスタ21b〜21fのONとOFFの切り替えを、何度も繰り返すことによって、直流電圧V21をしきい値Va21を下回る電圧になるように制御する。

【0071】

以上のように、第3実施形態に係る整流装置A3では、制御部26が、出力端子24a,24bから出力する直流電圧V21がしきい値Va21を超えると、整流用サイリスタ21b〜21fをOFFにすることによって、3相全波整流から単相半波整流に切り替える為に、降圧チョッパ回路Cへ出力する直流電圧V21を抑制することが出来る。これによって、降圧チョッパ回路Cに高耐圧の半導体デバイスを搭載しなくてもよい為に、降圧チョッパ回路の生産経費を抑制することが出来る。

【0072】

以上、本発明の第3実施形態について説明したが、本発明は上記第3実施形態に限定されることなく、例えば以下のような変形が考えられる。

(1)上記第3実施形態に係る整流装置A3では、整流用ブリッジ回路21を、1個の整流用ダイオード21aと、5個の整流用サイリスタ21b〜21fによって構成したが、本発明はこれに限定されない。

【0073】

例えば、整流用サイリスタ21bを整流用ダイオードに置き換え、制御部26が、直流電圧V21がしきい値Va21を超えると、整流用サイリスタ21c〜21fをOFFにすることによって、3相全波整流から2相半波整流に切り替えるようにすれば、第2実施形態の整流装置A2と同じ動作を行うことが出来る。

【0074】

また、整流用サイリスタ21b,21cを整流用ダイオードに置き換え、制御部26が、直流電圧V21がしきい値Va21を超えると、整流用サイリスタ21d〜21fをOFFにすることによって、3相全波整流から単相全波整流に切り替えるようにしてもよい。

さらに、整流用ダイオード21aを整流用サイリスタに置き換え、制御部26が、直流電圧V21に応じて、各整流用サイリスタのON/OFFを制御することによって、直流電圧V21を0ボルト〜ピーク電圧までの間で段階的に変化させる、すなわち直流電圧V21の出力制御をするようにしてもよい。

【符号の説明】

【0075】

A1,A2,Å3…整流装置、B…オルタネータ、C…降圧チョッパ回路、D…負荷、1…整流用ブリッジ回路、1a〜1f…整流用ダイオード、2…第1MOSFET、3…第2MOSFET、4…コンデンサ、5…ダイオード、6a,6b…出力端子、7…電圧センサ、8…制御部、11…整流用ブリッジ回路、11a〜11f…整流用ダイオード、12…第1MOSFET、13…第2MOSFET、14…コンデンサ、15…ダイオード、16a,16b…出力端子、17…電圧センサ、18…制御部、21…整流用ブリッジ回路、21a…整流用ダイオード、21b〜21f…整流用サイリスタ、22…コンデンサ、23…ダイオード、24a,24b…出力端子、25…電圧センサ、26…制御部

【特許請求の範囲】

【請求項1】

3相交流電圧を整流することによって直流電圧へ変換し、当該直流電圧を出力する整流装置であって、

整流した直流電圧が所定のしきい値を超えた場合に、直流電圧の生成に供する相電圧を減らすことを特徴とする整流装置。

【請求項2】

3相の交流電圧に応じた3対の整流用ダイオードから構成された整流用ブリッジ回路と、

前記整流用ブリッジ回路の正極側の出力端に接続する2個の整流用ダイオードのカソード端子に接続する第1のスイッチング手段と、

前記整流用ブリッジ回路の負極側の出力端に接続する3個の整流用ダイオードのアノード端子に接続する第2のスイッチング手段と、

3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、前記第1のスイッチン手段及び前記第2のスイッチング手段をOFFにすることによって、前記整流用ブリッジ回路の動作を3相全波整流から単相半波整流へ切り替える制御手段とを、

具備することを特徴とする請求項1に記載の整流装置。

【請求項3】

3相の交流電圧に応じた3対の整流用ダイオードから構成された整流用ブリッジ回路と、

前記整流用ブリッジ回路の正極側の出力端に接続する1個の整流用ダイオードのカソード端子に接続する第1のスイッチング手段と、

前記整流用ブリッジ回路の負極側の出力端に接続する3個の整流用ダイオードのアノード端子に接続する第2のスイッチング手段と、

3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、前記第1のスイッチン手段及び前記第2のスイッチング手段をOFFにすることによって、前記整流用ブリッジ回路の動作を3相全波整流から2相半波整流へ切り替える制御手段とを、

具備することを特徴とする請求項1に記載の整流装置。

【請求項4】

3相の交流電圧に応じた合計6個の整流用ダイオード及び整流用サイリスタから構成され、前記合計6個の内、少なくとも3つは、負極側の出力端にアノード端子が接続する整流用サイリスタである整流用ブリッジ回路と、

3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、少なくとも前記整流用ブリッジ回路の負極側の出力端にアノード端子が接続する整流用サイリスタをOFFにする制御手段とを、

具備することを特徴とする請求項1に記載の整流装置。

【請求項1】

3相交流電圧を整流することによって直流電圧へ変換し、当該直流電圧を出力する整流装置であって、

整流した直流電圧が所定のしきい値を超えた場合に、直流電圧の生成に供する相電圧を減らすことを特徴とする整流装置。

【請求項2】

3相の交流電圧に応じた3対の整流用ダイオードから構成された整流用ブリッジ回路と、

前記整流用ブリッジ回路の正極側の出力端に接続する2個の整流用ダイオードのカソード端子に接続する第1のスイッチング手段と、

前記整流用ブリッジ回路の負極側の出力端に接続する3個の整流用ダイオードのアノード端子に接続する第2のスイッチング手段と、

3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、前記第1のスイッチン手段及び前記第2のスイッチング手段をOFFにすることによって、前記整流用ブリッジ回路の動作を3相全波整流から単相半波整流へ切り替える制御手段とを、

具備することを特徴とする請求項1に記載の整流装置。

【請求項3】

3相の交流電圧に応じた3対の整流用ダイオードから構成された整流用ブリッジ回路と、

前記整流用ブリッジ回路の正極側の出力端に接続する1個の整流用ダイオードのカソード端子に接続する第1のスイッチング手段と、

前記整流用ブリッジ回路の負極側の出力端に接続する3個の整流用ダイオードのアノード端子に接続する第2のスイッチング手段と、

3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、前記第1のスイッチン手段及び前記第2のスイッチング手段をOFFにすることによって、前記整流用ブリッジ回路の動作を3相全波整流から2相半波整流へ切り替える制御手段とを、

具備することを特徴とする請求項1に記載の整流装置。

【請求項4】

3相の交流電圧に応じた合計6個の整流用ダイオード及び整流用サイリスタから構成され、前記合計6個の内、少なくとも3つは、負極側の出力端にアノード端子が接続する整流用サイリスタである整流用ブリッジ回路と、

3相全波整流によって整流した直流電圧が前記しきい値を超えた場合に、少なくとも前記整流用ブリッジ回路の負極側の出力端にアノード端子が接続する整流用サイリスタをOFFにする制御手段とを、

具備することを特徴とする請求項1に記載の整流装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2010−273451(P2010−273451A)

【公開日】平成22年12月2日(2010.12.2)

【国際特許分類】

【出願番号】特願2009−123147(P2009−123147)

【出願日】平成21年5月21日(2009.5.21)

【出願人】(000000099)株式会社IHI (5,014)

【Fターム(参考)】

【公開日】平成22年12月2日(2010.12.2)

【国際特許分類】

【出願日】平成21年5月21日(2009.5.21)

【出願人】(000000099)株式会社IHI (5,014)

【Fターム(参考)】

[ Back to top ]