昇圧回路

【課題】従来の昇圧回路は、低耐圧トランジスタにより構成することができなかった。

【解決手段】本発明は、第1の電源電圧を昇圧する昇圧回路であって、第1のノードに接続される第1のトランジスタと、一端が第1のノードに接続され、第1のトランジスタの活性化時に第1のノードの電圧で充電される第1の容量素子と、第1のトランジスタの制御端子に第1の制御信号を出力する第1の制御信号生成回路を有し、第1の容量素子は、第1のトランジスタの非活性化時に、他端に印加される第1の電源電圧の1/2以下の電圧により第1のノードの電位を、第2の電圧に昇圧し、第1の制御信号生成回路は、第1のトランジスタの非活性化時の第1の制御信号の電位を、第2の電位とし、第1のトランジスタの活性化時の第1の制御信号の電位を、第2の電位との差が第1の電源電圧以内となる電位とする昇圧回路である。

【解決手段】本発明は、第1の電源電圧を昇圧する昇圧回路であって、第1のノードに接続される第1のトランジスタと、一端が第1のノードに接続され、第1のトランジスタの活性化時に第1のノードの電圧で充電される第1の容量素子と、第1のトランジスタの制御端子に第1の制御信号を出力する第1の制御信号生成回路を有し、第1の容量素子は、第1のトランジスタの非活性化時に、他端に印加される第1の電源電圧の1/2以下の電圧により第1のノードの電位を、第2の電圧に昇圧し、第1の制御信号生成回路は、第1のトランジスタの非活性化時の第1の制御信号の電位を、第2の電位とし、第1のトランジスタの活性化時の第1の制御信号の電位を、第2の電位との差が第1の電源電圧以内となる電位とする昇圧回路である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、昇圧回路に関するものである。

【背景技術】

【0002】

従来の正電位の昇圧回路1を図14に示す。図14に示すように、昇圧回路1は、PMOSトランジスタMP1、MP2と、コンデンサC1と、レベルシフタLS1、LS2と、アンプAMP1を有する。PMOSトランジスタMP1は、電源電圧端子VDDとノードN1との間に接続される。また、ゲートにレベルシフタLS1の出力信号が入力される。PMOSトランジスタMP2は、ノードN1とノードN2との間に接続される。また、ゲートにレベルシフタLS2の出力信号が入力される。

【0003】

レベルシフタLS1は、クロック信号CLK1を入力し、出力クロック信号をPMOSトランジスタMP1のゲートへ出力する。レベルシフタLS1の電源電圧は、高電位側がノードN1、低電位側が接地端子GNDから供給される。レベルシフタLS2は、クロック信号CLK2を入力し、出力クロック信号をPMOSトランジスタMP2のゲートへ出力する。レベルシフタLS2の電源電圧は、高電位側が出力端子OUT1、低電位側が接地端子GNDから供給される。なお、便宜上、符号「VDD」「GND」は、端子名を示すと同時に、その端子が供給する電圧を示すものとする。また、出力端子OUT1の電圧をVOUTとする。

【0004】

コンデンサC1は、一端がアンプAMP1の出力、他端がノードN1に接続される。アンプAMP1は、クロック信号CLK3を入力し、出力クロック信号をコンデンサC1の一端に出力する。なお、アンプAMP1の電源電圧は、高電位側が電源電圧端子VDD、低電位側が接地端子GNDから供給される。

【0005】

図15に昇圧回路1の動作を示すタイミングチャートを示す。図15に示すように、時刻t1〜t2の期間、クロック信号CLK1はロウレベルとなり、PMOSトランジスタMP1がオン状態となる。よって、電源電圧端子VDDとノードN1が電気的に接続され、ノードN1の電位が電源電圧VDDとなる。一方、この期間において、クロック信号CLK3はロウレベルであるためコンデンサC1の一端の電位は接地電圧GNDであり、コンデンサC1が充電される。

【0006】

時刻t3〜t6の期間、クロック信号CLK3はハイレベルとなり、コンデンサC1の他端の電位が電源電圧VDDとなる。このため、充電されたコンデンサC1の一端の電位が昇圧され、ノードN1の電位が2VDDとなる。また、時刻t4〜t5の期間、クロック信号CLK2がロウレベルとなり、PMOSトランジスタMP2がオン状態となる。よって、ノードN1と出力端子OUT1が電気的に接続され、出力電圧VOUTが2VDDとなる。

【0007】

ここで、時刻t3〜t6の期間、ノードN1の電位が2VDDとなる。このため、電源電圧端子VDDに電流の逆流を防ぐため、時刻t2〜t6の期間、PMOSトランジスタMP1をオフさせる必要がある。よって、時刻t2〜t6の期間、PMOSトランジスタMP1をオフさせるため、図16に示すような構成のレベルシフタLS1を用いる。

【0008】

図16にレベルシフタLS1の詳細な回路構成を示す。なお、レベルシフタLS2も同様の構成である。レベルシフタLS1は、PMOSトランジスタMP11、MP12と、NMOSトランジスタMN11、MN12と、入力端子IN10と、出力端子OUT10、OUT10Bと、インバータ回路IV10とを有する。

【0009】

PMOSトランジスタMP11は、電源電圧端子VDDと出力端子OUT10Bとの間に接続される。また、ゲートが出力端子OUT10に接続される。PMOSトランジスタMP12は、電源電圧端子VDDと出力端子OUT10との間に接続される。また、ゲートが出力端子OUT10Bに接続される。NMOSトランジスタMN11は、出力端子OUT10Bと接地端子GNDとの間に接続される。また、ゲートが入力端子IN10に接続される。NMOSトランジスタMN12は、出力端子OUT10と接地端子GNDとの間に接続される。また、ゲートがインバータ回路IV10の出力端子に接続される。

【0010】

図17に、レベルシフタLS1の入力端子INに入力するクロック信号CLK1と、出力端子OUT10(及び反転出力端子OUT10B)の電位の関係をまとめた表を示す。このように、クロック信号CLK1がロウレベル(図の「L」)のとき、レベルシフタLS1の出力は接地電圧GND、クロック信号CLK1がハイレベル(図の「H」)のとき、レベルシフタLS1の出力は2VDDの電位となる。

【0011】

ここで、レベルシフタLS1の電源電圧のハイレベル側とロウレベル側の電位差は、2×VDDとなる。このため、PMOSトランジスタMP11、MP12及びNMOSトランジスタMN11、MN12は、電源電圧VDDの2倍の電位差に耐えられる高耐圧トランジスタで構成する必要がある。但し、高耐圧トランジスタは、ゲート酸化膜を厚くする必要があり、ゲート酸化膜が厚いほど大きなチャンネル長が必要となるため、厚膜トランジスタは、レイアウト面積を大きくとる問題を有する。

【0012】

また、図18に負電圧−VDDを生成する昇圧回路2の構成を示す。図18に示すように、昇圧回路2は、NMOSトランジスタMN1、MN2と、コンデンサC1と、レベルシフタLS3、LS4と、アンプAMP1を有する。昇圧回路2の動作タイミングチャートは、図15の昇圧回路1のタイミングチャートの極性が異なる以外は、基本的に同様であるため省略する。更に、レベルシフタLS3(及びLS4)の構成を図19に示す。また、図20にレベルシフタLS3の入力端子INに入力するクロック信号CLK1と、出力端子OUT10(及び反転出力端子OUT10B)の電位の関係をまとめた表を示す。レベルシフタLS3も、レベルシフタLS1と同様、電源電圧のハイレベル側とロウレベル側の電位差は、2×VDDとなる。このため、PMOSトランジスタMP11、MP12及びNMOSトランジスタMN11、MN12は、高耐圧トランジスタで構成する必要がある。

【0013】

なお、昇圧回路の例として特許文献1のような技術が開示されている。しかし、この技術でも、昇圧回路1と同様に、高耐圧トランジスタの使用が前提となっている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2005−129815号公報

【発明の概要】

【発明が解決しようとする課題】

【0015】

ワンチップ化された集積装置において、図16のレベルシフタLS1や図19のレベルシフタLS3のような高耐圧トランジスタを使用した回路は、耐圧が電源電圧VDD程度の低耐圧トランジスタを使用した回路と製造プロセスを分けて作成される。このため、製造工程が複雑化し、製造期間や製造コストの増大要因となる。また、ゲート酸化膜が厚膜となる高耐圧トランジスタは、レイアウト面積が大きくなるため、チップ面積の増大の要因にもなる。

【0016】

このため、レベルシフタLS1のように厚膜トランジスタを使用せず、低耐圧トランジスタでレベルシフタを構成するのに電界緩和回路技術を用いることが考えられる。このような電界緩和回路技術を用いて構成したレベルシフタLS10を図21に示す。

【0017】

図21に示すように、レベルシフタLS10は、PMOSトランジスタMP11、MP12、MP21、MP22と、NMOSトランジスタMN11、MN12、MN21、MN22と、入力端子IN10と、出力端子OUT10、OUT10Bと、インバータ回路IV10とを有する。

【0018】

PMOSトランジスタMP11は、電源電圧端子VDDとノードN11との間に接続される。また、ゲートがノードN12に接続される。PMOSトランジスタMP12は、電源電圧端子VDDとノードN12との間に接続される。また、ゲートがノードN11に接続される。PMOSトランジスタMP21は、ノードN11と出力端子OUT10Bとの間に接続される。PMOSトランジスタMP22は、ノードN12と出力端子OUT10との間に接続される。PMOSトランジスタMP21、MP22のゲートは、電源電圧端子VDDが接続される。

【0019】

NMOSトランジスタMN11は、ノードN21と接地端子GNDとの間に接続される。また、ゲートが入力端子IN10に接続される。NMOSトランジスタMN12は、ノードN22と接地端子GNDとの間に接続される。また、ゲートがインバータ回路IV10の出力端子に接続される。NMOSトランジスタMN21は、出力端子OUT10BとノードN21との間に接続される。NMOSトランジスタMN22は、出力端子OUT10とノードN22との間に接続される。また、NMOSトランジスタMN21、MN22は、ゲートが電源電圧端子VDDに接続される。

【0020】

図22に、レベルシフタLS10の入力端子IN10に入力するクロック信号と、出力端子OUT10(及び反転出力端子OUT10B)の電位及び各ノードの電位の関係をまとめた表を示す。但し、「Vtp」はPMOSトランジスタのスレッショルド電圧、「Vtn」はNMOSトランジスタのスレッショルド電圧である。

【0021】

図22の表に示すように、入力端子IN10に入力するクロック信号がロウレベル(図の「L」)のとき、レベルシフタLS1と同様、出力端子OUT10、OUT10Bの電位がそれぞれ接地電圧GND、2VDDとなる。しかし、各ノードの電位は図22の表に示すようになり、各トランジスタのゲート−ドレイン間もしくはゲート−ソース間の電位差は、電源電圧VDD以内に収まる。このことは、入力端子IN10に入力するクロック信号がハイレベル(図の「H」)のときも同様である。この電界緩和回路技術を用いたレベルシフタLS10を、昇圧回路1のLS1と交換することで、昇圧回路1で使用するトランジスタを全て低耐圧トランジスタとすることができる。

【0022】

なお、負電圧を生成する昇圧回路2に、昇圧回路1と同様、電界緩和回路技術を用いて構成した場合のレベルシフタLS30の回路構成を図23に示す。また、図24に、レベルシフタLS30の入力端子IN10に入力するクロック信号と、出力端子OUT10(及び反転出力端子OUT10B)の電位及び各ノードの電位の関係をまとめた表を示す。

【0023】

ここで、例えばレベルシフタLS10の場合、高電位側の電源電圧は、図14のノードN1の電位を利用している。このため、昇圧回路1の動作開始時の初期状態では、ノードN1の電位が昇圧されておらず2VDDではなくVDDである。よって、入力端子IN10に入力するクロック信号CLK1がハイレベルの場合であっても、図21のPMOSトランジスタMP22がオンせず、出力端子OUT10からの出力電位が不定となる。このため、図14のPMOSトランジスタMP1をオフさせることができない。結果として、昇圧回路1が昇圧動作を行うことができず、出力電圧VOUTを2VDDとすることができない。このため、電界緩和回路技術を用いて構成したレベルシフタを使用することができず、低耐圧トランジスタで昇圧回路1を構成することができない問題があった。

【0024】

更に、昇圧回路2においても、レベルシフタLS30の低電位側の電源電圧は、図18のノードN1の電位を利用している。このため、昇圧回路2の動作開始時の初期状態では、ノードN1の電位が負側に昇圧されておらず−VDDではなく接地電圧GNDとなっている。よって、入力端子IN10に入力するクロック信号CLK1がロウレベルの場合であっても、図23のNMOSトランジスタMN22がオンせず、出力端子OUT10からの出力電位が不定となる。このため、図18のNMOSトランジスタMN1をオフさせることができない。結果として、昇圧回路2が負電位側に昇圧動作を行うことができず、出力電圧VOUTを−VDDとすることができない。このため、電界緩和回路技術を用いて構成したレベルシフタを使用することができず、昇圧回路1と同様、低耐圧トランジスタで昇圧回路2を構成することができない問題があった。

【課題を解決するための手段】

【0025】

本発明は、第1の電源電圧を、正側または負側の所定の電圧に昇圧する昇圧回路であって、第1のノードに接続される第1のトランジスタと、一端が前記第1のノードに接続され、前記第1のトランジスタの活性化時に前記第1のノードの電圧で充電される第1の容量素子と、前記第1のトランジスタの制御端子に第1の制御信号を出力する第1の制御信号生成回路を有し、前記第1の容量素子は、前記第1のトランジスタの非活性化時に、他端に印加される前記第1の電源電圧の1/2以下の電圧により前記第1のノードの電位を、正側または負側の第2の電圧に昇圧し、前記第1の制御信号生成回路は、前記第1のトランジスタの非活性化時の前記第1の制御信号の電位を、前記第2の電位とし、前記第1のトランジスタの活性化時の前記第1の制御信号の電位を、前記第2の電位との差が前記第1の電源電圧以内となる電位とする昇圧回路である。

【0026】

本発明にかかる昇圧回路は、制御信号生成回路の動作電圧の範囲を、第2の電位から第1の電源電圧以内とする。このため、当該昇圧回路の初期状態で、第1のノードが昇圧されていなくても、制御信号生成回路から不定な電圧の制御信号生成回路が出力されない。このため、耐圧が第1の電源電圧以内であるトランジスタで制御信号生成回路を構成することができる。

【発明の効果】

【0027】

本発明にかかる昇圧回路は、耐圧が第1の電源電圧以内の低耐圧トランジスタを使用して構成することができ、回路規模の削減、製造工程の簡素化が行える。

【図面の簡単な説明】

【0028】

【図1】実施の形態1にかかる半導体記憶装置のブロック図である。

【図2】実施の形態1にかかる正電位の昇圧回路100の回路構成である。

【図3】実施の形態1にかかる昇圧回路100の動作タイミングチャートである。

【図4】実施の形態1にかかるレベルシフタLS101の回路構成である。

【図5】実施の形態1にかかるレベルシフタLS103の回路構成である。

【図6】実施の形態1にかかるレベルシフタLS101の入出力信号と、各ノードの電位の関係をまとめた表である。

【図7】実施の形態1にかかるレベルシフタLS103の入出力信号と、各ノードの電位の関係をまとめた表である。

【図8】実施の形態2にかかる負電位の昇圧回路200の回路構成である。

【図9】実施の形態2にかかる昇圧回路200の動作タイミングチャートである。

【図10】実施の形態2にかかるレベルシフタLS201の回路構成である。

【図11】実施の形態2にかかるレベルシフタLS203の回路構成である。

【図12】実施の形態2にかかるレベルシフタLS201の入出力信号と、各ノードの電位の関係をまとめた表である。

【図13】実施の形態2にかかるレベルシフタLS203の入出力信号と、各ノードの電位の関係をまとめた表である。

【図14】従来の正電位の昇圧回路1の回路構成である。

【図15】従来の昇圧回路1の動作タイミングチャートである。

【図16】従来のレベルシフタLS1の回路構成である。

【図17】従来のレベルシフタLS1の入出力信号の電位の関係をまとめた表である。

【図18】従来の負電位の昇圧回路2の回路構成である。

【図19】従来のレベルシフタLS3の回路構成である。

【図20】従来のレベルシフタLS3の入出力信号の電位の関係をまとめた表である。

【図21】従来のレベルシフタLS10の回路構成である。

【図22】従来のレベルシフタLS10の入出力信号と、各ノードの電位の関係をまとめた表である。

【図23】従来のレベルシフタLS30の回路構成である。

【図24】従来のレベルシフタLS30の入出力信号と、各ノードの電位の関係をまとめた表である。

【発明を実施するための形態】

【0029】

発明の実施の形態1

【0030】

以下、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。この実施の形態は、本発明をフラッシュメモリ等の半導体記憶装置における正の昇圧回路に適用したものである。

【0031】

図1に本実施の形態1にかかる半導体記憶装置MEM1のブロック構成図を示す。図1に示すように、半導体記憶装置MEM1は、メモリセルアレイCELLと、アドレスバッファADDBと、ロウレコーダLDECと、カラムデコーダCDECと、カラムセレクタCSELと、消去回路RSETと、スイッチ回路SWと、高電圧生成回路PCHRGEと、負電圧生成回路NCHRGEとを有する。

【0032】

メモリセルアレイCELLは、マトリクス状に記憶素子が配置されている。各記憶素子には、ビット線、ワード線が接続されている。ロウデコーダLDECは、アドレスバッファADDBから送られてくるロウアドレスデータに応じて、1つのワード線を選択する。カラムデコーダCDECは、アドレスバッファADDBから送られてくるカラムアドレスデータに応じて、1つのビット線を選択する。カラムセレクタCSELは、カラムデコーダCDECが選択したビット線をデータ線と接続する。

【0033】

高電圧生成回路PCHRGEは、電源電圧VDDよりも高い電圧VPPを生成する。負電圧生成回路NCHRGEは、接地電圧GNDよりも低い負電圧VKKを生成する。スイッチ回路SWは、高電圧生成回路PCHRGEもしくは負電圧生成回路NCHRGEが生成した電圧を必要に応じて、ロウデコーダLDECや、消去回路RSETに供給する。

【0034】

例えば、高電圧生成回路PCHRGEが生成した高電位の電圧VPPは、ロウデコーダLDECのワード線ドライバに供給され、ハイレベルのワード信号に利用される。また、負電圧生成回路NCHRGEが生成した負電位の電圧VKKは、ロウデコーダLDECのワード線ドライバに供給され、ロウレベルのワード信号に利用される。

【0035】

消去回路RSETは、半導体記憶装置MEM1がフラッシュメモリである場合、メモリセルアレイCELLの記憶素子が記憶しているデータを消去する機能を有する。このデータ消去時に、高電圧生成回路PCHRGE、負電圧生成回路NCHRGEが生成した高電位電圧VPP、負電圧VKKを利用する。この高電位電圧VPPを記憶素子のフローティングゲートの一方、負電圧VKKを他方にかけることで、フローティングゲートに蓄えられた電荷を抜く作業を行う。

【0036】

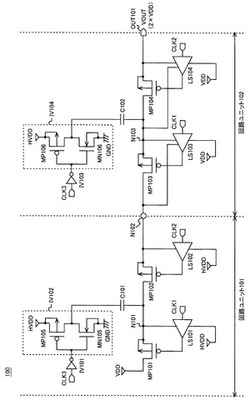

図2に本実施の形態1にかかる高電圧生成回路PCHRGEが有する昇圧回路100の構成の一例を示す。図2に示すように、昇圧回路100は、PMOSトランジスタMP101、MP102、MP103、MP104と、レベルシフタLS101、LS102、LS103、LS104と、コンデンサC101、C102と、インバータ回路IV101、IV102、IV103、IV104とを有する。

【0037】

PMOSトランジスタMP101(第1のトランジスタ)は、ソースもしくはドレインの一端が電源電圧VDD(第1の電源電圧)を供給する電源電圧端子VDD(第1の電源端子)、ソースもしくはドレインの他端がノードN101(第1のノード)に接続される。また、PMOSトランジスタMP101は、ゲートにレベルシフタLS101の出力信号が入力される。PMOSトランジスタMP102(第2のトランジスタ)は、ソースもしくはドレインの一端がノードN101、ソースもしくはドレインの他端がノードN102(第2のノード)に接続される。また、PMOSトランジスタMP102は、ゲートにレベルシフタLS102の出力信号が入力される。なお、便宜上、符号「VDD」は、電源電圧端子名を示すと同時に、電源電圧VDDを示すものとする。また、符号「GND」は、接地端子名を示すと同時に、接地電圧GNDを示すものとする。

【0038】

レベルシフタLS101(第1の制御信号生成回路)は、クロック信号CLK1を入力し、出力信号(第1の制御信号)をPMOSトランジスタMP101のゲートへ出力する。レベルシフタLS101の電源電圧は、高電位側がノードN101、低電位側がHVDD電圧端子から供給される。なお、HVDD電圧端子は、電源電圧VDDの1/2の電圧(以下、1/2VDDと称す)を供給する。また、このHVDD電圧端子からの1/2VDDの電圧は、電源電圧VDDを同じ抵抗値の抵抗で分圧した電位から生成してもよい。

【0039】

レベルシフタLS102(第2の制御信号生成回路)は、クロック信号CLK2を入力し、出力信号(第2の制御信号)をPMOSトランジスタMP102のゲートへ出力する。レベルシフタLS102の電源電圧は、高電位側がノードN102、低電位側がHVDD電圧端子から供給される。

【0040】

インバータ回路IV101は、クロック信号CLK3を入力し、その反転信号をインバータ回路IV102の入力へ出力する。インバータ回路IV102は、図2に示すように、PMOSトランジスタMP105と、NMOSトランジスタMN105とを有する。PMOSトランジスタMP105、NMOSトランジスタMN105は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP105、NMOSトランジスタMN105の共通ノードがインバータ回路IV102の出力端となる。また、PMOSトランジスタMP105、NMOSトランジスタMN105のゲートには、インバータ回路IV101の出力信号が入力される。このため、インバータ回路IV102からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0041】

コンデンサC101(第1の容量素子)は、一端がインバータ回路IV102の出力端、他端がノードN101に接続される。

【0042】

PMOSトランジスタMP103(第9のトランジスタ)は、ソースもしくはドレインの一端がノードN102、ソースもしくはドレインの他端がノードN103(第7のノード)に接続される。また、PMOSトランジスタMP103は、ゲートにレベルシフタLS103の出力信号が入力される。PMOSトランジスタMP104(第10のトランジスタ)は、ソースもしくはドレインの一端がノードN103、ソースもしくはドレインの他端が出力端子OUT101(第8のノード)に接続される。また、PMOSトランジスタMP104は、ゲートにレベルシフタLS104の出力信号が入力される。

【0043】

レベルシフタLS103(第3の制御信号生成回路)は、クロック信号CLK1を入力し、出力信号(第3の制御信号)をPMOSトランジスタMP103のゲートへ出力する。レベルシフタLS103の詳細な構成は後述するが、高電位側の電源電圧がノードN102及びN103、低電位側が電源電圧端子VDDから供給される。レベルシフタLS104(第4の制御信号生成回路)は、クロック信号CLK2を入力し、出力信号(第4の制御信号)をPMOSトランジスタMP104のゲートへ出力する。レベルシフタLS104の詳細な構成は後述するが、高電位側の電源電圧がノードN103及び出力端子OUT101、低電位側が電源電圧端子VDDから供給される。

【0044】

インバータ回路IV103は、クロック信号CLK3を入力し、その反転信号をインバータ回路IV104の入力へ出力する。インバータ回路IV104は、図2に示すように、PMOSトランジスタMP106と、NMOSトランジスタMN106とを有する。PMOSトランジスタMP106、NMOSトランジスタMN106は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP106、NMOSトランジスタMN106の共通ノードがインバータ回路IV104の出力端となる。また、PMOSトランジスタMP106、NMOSトランジスタMN106のゲートには、インバータ回路IV103の出力信号が入力される。このため、インバータ回路IV104からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0045】

コンデンサC102(第2の容量素子)は、一端がインバータ回路IV104の出力端、他端がノードN103に接続される。

【0046】

なお、上記PMOSトランジスタ、NMOSトランジスタは、ゲート酸化膜の耐圧が電源電圧VDD以下の低耐圧トランジスタであるものとする。また、PMOSトランジスタのスレッショルド電圧Vtp及びNMOSトランジスタのスレッショルド電圧Vtnは、それぞれ1/2VDD以下であるものとする。

【0047】

図3に昇圧回路100の動作を説明するタイミングチャートを示す。なお、本説明では、図2の回路ユニット101と、回路ユニット102に分けて動作の説明を行う。回路ユニット101の動作を時刻t1〜t6、回路ユニット102の動作を時刻t6〜t11に説明する。

【0048】

まず、回路ユニット101の動作は、図3に示すように、時刻t1〜t2の期間、クロック信号CLK1はロウレベルとなり、PMOSトランジスタMP101がオン状態となる。よって、電源電圧端子VDDとノードN101が電気的に接続され、ノードN101の電位が電源電圧VDDとなる。一方、この期間において、クロック信号CLK3はロウレベルであり、インバータ回路IV102から出力される電位は接地電圧GNDである。このため、コンデンサC101の一端の電位は接地電圧GNDとなり、コンデンサC101は、電位差VDDで充電される。

【0049】

時刻t2で、クロック信号CLK1はハイレベルに立ち上がる。このため、電源電圧端子VDDとノードN101が電気的に遮断される。また、クロック信号CLK2によりPMOSトランジスタMP102もオフ状態のため、ノードN101はハイインピーダンスとなる。但し、コンデンサC101が充電されているため、ノードN101の電位はVDDで保持される。

【0050】

時刻t3で、クロック信号CLK3がハイレベルに立ち上がる。このため、インバータ回路IV102から出力される電位が1/2VDDとなる。よって、コンデンサC101の一端に1/2VDDの電位が印加され、コンデンサC101の他端の電位が1/2VDD分昇圧される。よって、ノードN101の電位が3/2VDD(=VDD+1/2VDD)となる。

【0051】

時刻t4〜t5の期間、クロック信号CLK2はロウレベルとなり、PMOSトランジスタMP102がオン状態となる。よって、ノードN101とノードN102が電気的に接続され、ノードN102の電位が3/2VDDとなる。

【0052】

時刻t5で、クロック信号CLK2はハイレベルに立ち上がる。このため、ノードN101とノードN102が電気的に遮断される。

【0053】

次に、回路ユニット102の動作は、図3に示すように、時刻6〜t7の期間、クロック信号CLK1はロウレベルとなり、PMOSトランジスタMP103がオン状態となる。よって、ノードN102とノードN103が電気的に接続され、ノードN103の電位が3/2VDDとなる。一方、この期間において、クロック信号CLK3はロウレベルであり、インバータ回路IV104から出力される電位は接地電圧GNDである。このため、コンデンサC102の一端の電位は接地電圧GNDとなり、コンデンサC102は、電位差3/2VDDで充電される。

【0054】

時刻t7で、クロック信号CLK1はハイレベルに立ち上がる。このため、ノードN102とノードN103が電気的に遮断される。また、クロック信号CLK2によりPMOSトランジスタMP104もオフ状態のため、ノードN103はハイインピーダンスとなる。但し、コンデンサC102が充電されているため、ノードN103の電位は3/2VDDで保持される。

【0055】

時刻t8で、クロック信号CLK3がハイレベルに立ち上がる。このため、インバータ回路IV102から出力される電位が1/2VDDとなる。よって、コンデンサC102の一端に1/2VDDの電位が印加され、コンデンサC102の他端の電位が1/2VDD分昇圧される。よって、ノードN103の電位が2VDD(=3/2VDD+1/2VDD)となる。

【0056】

時刻t9〜t10の期間、クロック信号CLK2はロウレベルとなり、PMOSトランジスタMP104がオン状態となる。よって、ノードN103と出力端子OUT101が電気的に接続され、出力端子の電位が2VDDとなる。

【0057】

時刻t11で、クロック信号CLK2はハイレベルに立ち上がる。このため、ノードN103と出力端子OUT101が電気的に遮断される。

【0058】

ここで、時刻t3〜t6、t8〜t11の期間、ノードN101、N103の電位が、それぞれ電源電圧VDD、ノードN102の電位3/2VDDより大きくなる。このため、電源電圧端子VDD、ノードN102への電流の逆流を防ぐため、時刻t2〜t6、t7〜t11の期間、PMOSトランジスタMP101、MP103をオフさせる必要がある。このため、回路ユニット101では、図4に示すような構成のレベルシフタLS101、LS102、回路ユニット102では、図5に示すような構成のレベルシフタLS103、LS104を用いる。

【0059】

図4にレベルシフタLS101の構成を示す。なお、レベルシフタLS102は、レベルシフタLS101とほぼ同様の構成のため、特に断らない限り説明は省略する。図4に示すように、レベルシフタLS101は、PMOSトランジスタMP111、MP112と、NMOSトランジスタMN111、MN112、MN121、MN122と、入力端子IN110と、出力端子OUT110、OUT110Bと、インバータ回路IV110とを有する。この入力端子IN110にクロック信号CLK1が入力される。また、出力端子OUT110からの出力信号が図2のPMOSトランジスタMP101のゲートに出力される。

【0060】

なお、レベルシフタLS102では、入力端子IN110にクロック信号CLK2が入力される。また、出力端子OUT110からの出力信号が図2のPMOSトランジスタMP102のゲートに出力される。

【0061】

PMOSトランジスタMP111(第3のトランジスタ)は、ソースが電源端子VA(第1の電圧供給端子)、ドレインが出力端子OUT110B(第3のノード)、ゲートが出力端子OUT110(第4のノード)に接続される。PMOSトランジスタMP112(第4のトランジスタ)は、ソースが電源端子VA、ドレインが出力端子OUT110、ゲートが出力端子OUT110Bに接続される。ここで、電源端子VAは、図2のノードN101と接続されている。なお、レベルシフタLS102では、この電源端子VAは図2のノードN102と接続されることになる。

【0062】

NMOSトランジスタMN111(第7のトランジスタ)は、ドレインがノードN111(第5のノード)、ソースがHVDD端子(第3の電圧供給端子)、ゲートが入力端子IN110に接続される。NMOSトランジスタMN112(第8のトランジスタ)は、ドレインがノードN112(第6のノード)、ソースがHVDD端子、ゲートがインバータ回路IV110の出力端に接続される。NMOSトランジスタMN121(第5のトランジスタ)は、ドレインが出力端子OUT110、ソースがノードN111、ゲートが電源電圧端子VDD(第2の電圧供給端子)に接続される。NMOSトランジスタMN122(第6のトランジスタ)は、ドレインが出力端子OUT110B、ソースがノードN112、ゲートが電源電圧端子VDDに接続される。

【0063】

インバータ回路IV110は、入力端が入力端子IN110、出力端がNMOSトランジスタMN112のゲートに接続される。

【0064】

次に、図5にレベルシフタLS103の構成を示す。なお、レベルシフタLS104は、レベルシフタLS103とほぼ同様の構成のため、特に断らない限り説明は省略する。図5に示すように、レベルシフタLS103は、PMOSトランジスタMP121、MP122、MP131、MP132と、NMOSトランジスタMN131、MN132、MN141、MN142、MN151、MN152、MN161、MN162と、入力端子IN111と、出力端子OUT111、OUT111Bと、インバータ回路IV111とを有する。この入力端子IN111にクロック信号CLK1が入力される。また、出力端子OUT111からの出力信号が図2のPMOSトランジスタMP103のゲートに出力される。

【0065】

なお、レベルシフタLS104では、入力端子IN111にクロック信号CLK2が入力される。また、出力端子OUT111からの出力信号が図2のPMOSトランジスタMP104のゲートに出力される。

【0066】

PMOSトランジスタMP121(第11のトランジスタ)は、ソースが電源端子VB(第4の電圧供給端子)、ドレインがノードN131(第9のノード)、ゲートがノードN132(第10のノード)に接続される。PMOSトランジスタMP122(第12のトランジスタ)は、ソースが電源端子VB、ドレインがノードN132、ゲートがノードN131に接続される。ここで、電源端子VBは、図2のノードN102と接続されている。なお、レベルシフタLS104では、この電源端子VBは図2のノードN103と接続されることになる。

【0067】

NMOSトランジスタMN141(第17のトランジスタ)は、ドレインがノードN121(第11のノード)、ソースがHVDD端子(第6の電圧供給端子)、ゲートが入力端子IN111に接続される。NMOSトランジスタMN142(第18のトランジスタ)は、ドレインがノードN122(第12のノード)、ソースがHVDD端子、ゲートがインバータ回路IV111の出力端に接続される。NMOSトランジスタMN131(第15のトランジスタ)は、ドレインがノードN131、ソースがノードN121、ゲートが電源電圧端子VDD(第5の電圧供給端子)に接続される。NMOSトランジスタMN132(第16のトランジスタ)は、ドレインがノードN132、ソースがノードN122、ゲートが電源電圧端子VDDに接続される。

【0068】

インバータ回路IV111は、入力端が入力端子IN111、出力端がNMOSトランジスタMN142のゲートに接続される。

【0069】

PMOSトランジスタMP131(第13のトランジスタ)は、ソースが電源端子VC(第7の電圧供給端子)、ドレインが出力端子OUT111B(第13のノード)、ゲートが出力端子OUT111(第14のノード)に接続される。PMOSトランジスタMP132(第14のトランジスタ)は、ソースが電源端子VC、ドレインが出力端子OUT111、ゲートが出力端子OUT111Bに接続される。ここで、電源端子VCは、図2のノードN103と接続されている。なお、レベルシフタLS104では、この電源端子VCは図2の出力端子OUT101と接続されることになる。

【0070】

NMOSトランジスタMN161(第21のトランジスタ)は、ドレインがノードN141(第15のノード)、ソースが電源電圧端子VDD、ゲートがノードN132に接続される。NMOSトランジスタMN162(第22のトランジスタ)は、ドレインがノードN142(第16のノード)、ソースが電源電圧端子VDD、ゲートがノードN131に接続される。NMOSトランジスタMN151(第19のトランジスタ)は、ドレインが出力端子OUT111B、ソースがノードN141、ゲートが電源端子VBに接続される。NMOSトランジスタMN152(第20のトランジスタ)は、ドレインが出力端子OUT111、ソースがノードN142、ゲートが電源端子VBに接続される。

【0071】

なお、上記レベルシフタLS101、LS102、LS103、LS104を構成する全てのPMOSトランジスタ、NMOSトランジスタは、ゲート酸化膜の耐圧が電源電圧VDD以下の低耐圧トランジスタであるものとする。また、PMOSトランジスタのスレッショルド電圧Vtp及びNMOSトランジスタのスレッショルド電圧Vtnは、それぞれ1/2VDD以下であるものとする。また、図5からもわかるようにレベルシフタLS103(及びLS104)は、ノードN131、N132で接続される2つのレベルシフタで構成されているとみなすこともできる。そして、この2つのレベルシフタにおいても高電側位電源電圧と低電位側電源電圧の電位差がVDD以内となっている。

【0072】

ここで、レベルシフタLS101の動作を中心に回路ユニット101ついて、説明する。なお、レベルシフタLS102の動作は、入力クロック信号がCLK2である以外は、レベルシフタLS101と同様なため説明は省略する。図6に、レベルシフタLS101の入力端子IN110に入力するクロック信号CLK1と、出力端子OUT110(及び反転出力端子OUT110B)、及び、ノードN111、N112の電位の関係をまとめた表を示す。但し、「Vtn」はNMOSトランジスタのスレッショルド電圧である。

【0073】

図6の表に示すように、入力端子IN110に入力するクロック信号CLK1がロウレベル(接地電圧GND)のとき、出力端子OUT110、OUT110Bの電位がそれぞれ1/2VDD、3/2VDDとなる。また、ノードN111、N112の電位がそれぞれVDD−Vtn、1/2VDDとなる。

【0074】

逆に、入力端子IN110に入力するクロック信号CLK1がハイレベル(電源電圧VDD)のとき、出力端子OUT110、OUT110Bの電位がそれぞれ3/2VDD、1/2VDDとなる。また、ノードN111、N112の電位がそれぞれ1/2VDD、VDD−Vtnとなる。

【0075】

なお、レベルシフタLS102もクロック信号CLK2に応じて同様の動作を行う。このように、レベルシフタLS101、LS102の各トランジスタのゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。

【0076】

また、上述のようにクロック信号CLK1がロウレベルのとき1/2VDD、ハイレベルのとき3/2VDDが、レベルシフタLS101から出力される。そして、このレベルシフタLS101からの出力に応じて、図2のPMOSトランジスタMP101のオン、オフが制御される。なお、レベルシフタLS102も、クロック信号CLK2がロウレベルのとき1/2VDD、ハイレベルのとき3/2VDDを出力する。そして、このレベルシフタLS102からの出力に応じて、図2のPMOSトランジスタMP102のオン、オフが制御される。このように、PMOSトランジスタMP101、MP102のゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。よって、回路ユニット101で使用するトランジスタを全て低耐圧トランジスタとすることができる。

【0077】

ここで更に、昇圧回路100の初期状態を考える。昇圧回路100の初期状態では、コンデンサC101が充電されておらず、クロック信号CLK1がハイレベルであっても、ノードN101が昇圧されない。このため、ノードN101の電位が3/2VDDではなく、VDDである。よって、レベルシフタLS101の高電位側の電源電圧である電源端子VAの電位もVDDとなる。

【0078】

ここで、図21に示した電界緩和回路技術を用いた従来のレベルシフタLS10では高電位側の電源電圧がVDDの場合、PMOSトランジスタMP22もしくはMP21がオンしないため、出力端子OUT10の電位が不定となっていた。

【0079】

しかし、本実施の形態1のレベルシフタLS101では、電源端子VAの電位がVDDであっても、PMOSトランジスタMP112もしくはMP111のソース−ゲート間の電位差を1/2VDDとすることができ、PMOSトランジスタMP112もしくはMP111をオンさせることができる。よって、出力端子OUT110の電位が不定となることがなく、レベルシフタLS101が初期状態においても正常に動作する。このため、PMOSトランジスタMP101を確実にオフさせることができ、回路ユニット101の正常動作が可能となる。

【0080】

次に、レベルシフタLS103の動作を中心に回路ユニット102について説明する。なお、レベルシフタLS104の動作は、入力クロック信号がCLK2である以外は、レベルシフタLS103と同様なため説明は省略する。図7に、レベルシフタLS103の入力端子IN111に入力するクロック信号CLK1と、出力端子OUT111(及び反転出力端子OUT111B)、及び、ノードN121、N122、N131、N132、N141、N142の電位の関係をまとめた表を示す。

【0081】

図7の表に示すように、入力端子IN111に入力するクロック信号CLK1がロウレベル(接地電圧GND)のとき、出力端子OUT111、OUT111Bの電位がそれぞれVDD、2VDDとなる。また、ノードN121、N122の電位がそれぞれVDD−Vtn、1/2VDDとなる。ノードN131、N132の電位がそれぞれ3/2VDD、1/2VDDとなる。ノードN141、N142の電位がそれぞれ3/2VDD−Vtn、VDDとなる。

【0082】

逆に、入力端子IN111に入力するクロック信号CLK1がハイレベル(電源電圧VDD)のとき、出力端子OUT111、OUT111Bの電位がそれぞれ2VDD、VDDとなる。また、ノードN121、N122の電位がそれぞれ1/2VDD、VDD−Vtnとなる。ノードN131、N132の電位がそれぞれ1/2VDD、3/2VDDとなる。ノードN141、N142の電位がそれぞれVDD、3/2VDD−Vtnとなる。

【0083】

なお、レベルシフタLS104もクロック信号CLK2に応じて同様の動作を行う。このように、レベルシフタLS103、LS104の各トランジスタのゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。

【0084】

また、上述のようにクロック信号CLK1がロウレベルのとき3/2VDD、ハイレベルのとき2VDDが、レベルシフタLS103から出力される。そして、このレベルシフタLS103からの出力に応じて、図2のPMOSトランジスタMP103のオン、オフが制御される。なお、レベルシフタLS104も、クロック信号CLK2がロウレベルのとき3/2VDD、ハイレベルのとき2VDDを出力する。そして、このレベルシフタLS104からの出力に応じて、図2のPMOSトランジスタMP104のオン、オフが制御される。このように、PMOSトランジスタMP103、MP104のゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。よって、回路ユニット102で使用するトランジスタを全て低耐圧トランジスタとすることができる。

【0085】

以上、昇圧回路100では、使用するトランジスタを全て低耐圧トランジスタとしても、出力電圧VOUTを2×VDDとすることができる。また、図21に示した電界緩和回路技術を用いた従来のレベルシフタを用いた場合、動作開始時の初期状態でレベルシフタが不定な電位を出力するため、昇圧動作を行えなかった。しかし、本実施の形態1の昇圧回路100のレベルシフタLS101は、動作開始時の初期状態であって不定な電圧を出力しない。このため、昇圧回路100が正常に昇圧動作を開始することができる。

【0086】

発明の実施の形態2

【0087】

以下、本発明を適用した具体的な実施の形態2について、図面を参照しながら詳細に説明する。この実施の形態2は、本発明をフラッシュメモリ等の半導体記憶装置における負の昇圧回路に適用したものである。つまり、図1の負電圧生成昇圧回路NCHRGEが有する昇圧回路に適用する。

【0088】

図8に本実施の形態2にかかる負電圧生成昇圧回路NCHRGEが有する昇圧回路200の構成の一例を示す。

【0089】

図8に示すように、昇圧回路200は、NMOSトランジスタMN201、MN202、MN203、MN204と、レベルシフタLS201、LS202、LS203、LS204と、コンデンサC201、C202と、インバータ回路IV201、IV202、IV203、IV204とを有する。

【0090】

NMOSトランジスタMN201(第1のトランジスタ)は、ソースもしくはドレインの一端が接地電圧GNDを供給する接地端子GND(第2の電源端子)、ソースもしくはドレインの他端がノードN201(第1のノード)に接続される。また、NMOSトランジスタMN201は、ゲートにレベルシフタLS201の出力信号が入力される。NMOSトランジスタMN202(第2のトランジスタ)は、ソースもしくはドレインの一端がノードN201、ソースもしくはドレインの他端がノードN202に接続される。また、NMOSトランジスタMN202(第2のノード)は、ゲートにレベルシフタLS202の出力信号が入力される。

【0091】

レベルシフタLS201(第1の制御信号生成回路)は、クロック信号CLK1を入力し、出力信号(第1の制御信号)をNMOSトランジスタMN201のゲートへ出力する。レベルシフタLS201の電源電圧は、高電位側がHVDD端子、低電位側がノードN201から供給される。

【0092】

レベルシフタLS202(第2の制御信号生成回路)は、クロック信号CLK2を入力し、出力信号(第2の制御信号)をNMOSトランジスタMN202のゲートへ出力する。レベルシフタLS202の電源電圧は、高電位側がHVDD端子、低電位側がノードN202から供給される。

【0093】

インバータ回路IV201は、クロック信号CLK3を入力し、その反転信号をインバータ回路IV202の入力へ出力する。インバータ回路IV202は、図8に示すように、PMOSトランジスタMP205と、NMOSトランジスタMN205とを有する。PMOSトランジスタMP205、NMOSトランジスタMN205は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP205、NMOSトランジスタMN205の共通ノードがインバータ回路IV202の出力端となる。また、PMOSトランジスタMP205、NMOSトランジスタMN205のゲートには、インバータ回路IV201の出力信号が入力される。このため、インバータ回路IV202からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0094】

コンデンサC201(第2の容量素子)は、一端がインバータ回路IV202の出力端、他端がノードN201に接続される。

【0095】

NMOSトランジスタMN203(第7のトランジスタ)は、ソースもしくはドレインの一端がノードN202、ソースもしくはドレインの他端がノードN203(第5のノード)に接続される。また、NMOSトランジスタMN203は、ゲートにレベルシフタLS203の出力信号が入力される。NMOSトランジスタMN204(第8のトランジスタ)は、ソースもしくはドレインの一端がノードN203、ソースもしくはドレインの他端が出力端子OUT201(第6のノード)に接続される。また、NMOSトランジスタMN204は、ゲートにレベルシフタLS204の出力信号が入力される。

【0096】

レベルシフタLS203は、クロック信号CLK1を入力し、出力信号をNMOSトランジスタMN203のゲートへ出力する。レベルシフタLS203の詳細な構成は後述するが、高電位側の電源電圧が接地端子GND、低電位側がノードN202及びN203から供給される。レベルシフタLS204は、クロック信号CLK2を入力し、出力信号をNMOSトランジスタMN204のゲートへ出力する。レベルシフタLS204の詳細な構成は後述するが、高電位側の電源電圧が接地端子GND、低電位側がノードN203及び出力端子OUT201から供給される。

【0097】

インバータ回路IV203は、クロック信号CLK3を入力し、その反転信号をインバータ回路IV204の入力へ出力する。インバータ回路IV204は、図8に示すように、PMOSトランジスタMP206と、NMOSトランジスタMN206とを有する。PMOSトランジスタMP206、NMOSトランジスタMN206は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP206、NMOSトランジスタMN206の共通ノードがインバータ回路IV204の出力端となる。また、PMOSトランジスタMP206、NMOSトランジスタMN206のゲートには、インバータ回路IV203の出力信号が入力される。このため、インバータ回路IV204からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0098】

コンデンサC202は、一端がインバータ回路IV204の出力端、他端がノードN203に接続される。

【0099】

なお、上記PMOSトランジスタ、NMOSトランジスタは、ゲート酸化膜の耐圧が電源電圧VDD以下の低耐圧トランジスタであるものとする。また、PMOSトランジスタのスレッショルド電圧Vtp及びNMOSトランジスタのスレッショルド電圧Vtnは、それぞれ1/2VDD以下であるものとする。

【0100】

図9に昇圧回路200の動作を説明するタイミングチャートを示す。なお、本説明では、図9の回路ユニット201と、回路ユニット202に分けて動作の説明を行う。回路ユニット201の動作を時刻t1〜t6、回路ユニット202の動作を時刻t6〜t11に説明する。

【0101】

まず、回路ユニット201の動作は、図10に示すように、時刻t1〜t2の期間、クロック信号CLK1はハイレベルとなり、NMOSトランジスタMN201がオン状態となる。よって、接地端子VDDとノードN201が電気的に接続され、ノードN201の電位が接地電圧GNDとなる。一方、この期間において、クロック信号CLK3はハイレベルであり、インバータ回路IV202から出力される電位は1/2VDDである。このため、コンデンサC201の一端の電位は接地電圧GNDとなり、コンデンサC101は、電位差1/2VDDで充電される。

【0102】

時刻t2で、クロック信号CLK1はロウレベルに立ち下がる。このため、接地電圧GNDとノードN201が電気的に遮断される。また、クロック信号CLK2によりNMOSトランジスタMN202もオフ状態のため、ノードN201はハイインピーダンスとなる。但し、コンデンサC201が充電されているため、ノードN101の電位は接地電圧GNDで保持される。

【0103】

時刻t3で、クロック信号CLK3がロウレベルに立ち下がる。このため、インバータ回路IV202から出力される電位が接地電圧GNDとなる。よって、コンデンサC201の一端の電位が接地電圧GNDとなり、コンデンサC201の他端の電位が1/2VDD分降下する。よって、ノードN201の電位が−1/2VDDとなる。

【0104】

時刻t4〜t5の期間、クロック信号CLK2はハイレベルとなり、NMOSトランジスタMN202がオン状態となる。よって、ノードN201とノードN202が電気的に接続され、ノードN202の電位が−1/2VDDとなる。

【0105】

時刻t5で、クロック信号CLK2はロウレベルに立ち下がる。このため、ノードN201とノードN202が電気的に遮断される。

【0106】

次に、回路ユニット202の動作は、図10に示すように、時刻6〜t7の期間、クロック信号CLK1はロウレベルとなり、NMOSトランジスタMN203がオン状態となる。よって、ノードN202とノードN203が電気的に接続され、ノードN203の電位が−1/2VDDとなる。一方、この期間において、クロック信号CLK3はハイレベルであり、インバータ回路IV204から出力される電位は1/2VDDである。このため、コンデンサC202の一端の電位は−1/2VDDとなり、コンデンサC202は、電位差VDDで充電される。

【0107】

時刻t7で、クロック信号CLK1はロウレベルに立ち下がる。このため、ノードN202とノードN203が電気的に遮断される。また、クロック信号CLK2によりNMOSトランジスタMN204もオフ状態のため、ノードN203はハイインピーダンスとなる。但し、コンデンサC202が充電されているため、ノードN203の電位は−1/2VDDで保持される。

【0108】

時刻t8で、クロック信号CLK3がロウレベルに立ち下がる。このため、インバータ回路IV202から出力される電位が接地電圧GNDとなる。よって、コンデンサC202の一端に接地電圧GNDの電位が印加され、コンデンサC102の他端の電位が1/2VDD分降下する。よって、ノードN203の電位が−VDD(=−1/2VDD−1/2VDD)となる。

【0109】

時刻t9〜t10の期間、クロック信号CLK2はハイレベルとなり、NMOSトランジスタMN204がオン状態となる。よって、ノードN203と出力端子OUT201が電気的に接続され、出力端子の電位が−VDDとなる。

【0110】

時刻t11で、クロック信号CLK2はロウレベルに立ち下がる。このため、ノードN203と出力端子OUT201が電気的に遮断される。

【0111】

ここで、時刻t3〜t6、t8〜t11の期間、ノードN201、N203の電位が、それぞれ接地電圧GND、ノードN202の電位−1/2VDDより低くなる。このため、接地端子GND、ノードN202から電流の逆流を防ぐため、時刻t2〜t6、t7〜t11の期間、NMOSトランジスタMN201、MN203をオフさせる必要がある。このため、回路ユニット201では、図10に示すような構成のレベルシフタLS201、LS202、回路ユニット202では、図11に示すような構成のレベルシフタLS203、LS204を用いる。

【0112】

図10にレベルシフタLS201の構成を示す。なお、レベルシフタLS202は、レベルシフタLS201とほぼ同様の構成のため、特に断らない限り説明は省略する。図10に示すように、レベルシフタLS201は、PMOSトランジスタMP211、MP212と、NMOSトランジスタMN211、MN212と、入力端子IN210と、出力端子OUT210、OUT210Bと、インバータ回路IV210、IV211、IV212とを有する。この入力端子IN210にクロック信号CLK1が入力される。また、出力端子OUT210からの出力信号が図2のNMOSトランジスタMN201のゲートに出力される。

【0113】

なお、レベルシフタLS202では、入力端子IN210にクロック信号CLK2が入力される。また、出力端子OUT210からの出力信号が図2のNMOSトランジスタMN202のゲートに出力される。

【0114】

PMOSトランジスタMP211(第3のトランジスタ)は、ソースがHVDD電源端子(第3の電圧供給端子)、ドレインが出力端子OUT210B(第3のノード)、ゲートがノードN211に接続される。PMOSトランジスタMP212(第4のトランジスタ)は、ソースがHVDD電源端子、ドレインが出力端子OUT210(第4のノード)、ゲートがノードN212に接続される。

【0115】

NMOSトランジスタMN211(第5のトランジスタ)は、ドレインが出力端子OUT210B、ソースが電源端子VD、ゲートが出力端子OUT210に接続される。NMOSトランジスタMN212(第6のトランジスタ)は、ドレインが出力端子OUT210、ソースが電源端子VD、ゲートが出力端子OUT210Bに接続される。ここで、電源端子VDは、図8のノードN201と接続されている。なお、レベルシフタLS202では、この電源端子VDは図8のノードN202と接続されることになる。

【0116】

インバータ回路IV210は、入力端が入力端子IN210、出力端がインバータ回路IV211の入力端に接続される。インバータ回路IV211は、入力端がインバータ回路IV210の出力端、出力端がノードN211に接続される。インバータ回路IV212は、入力端がノードN211、出力端がノードN212に接続される。

【0117】

インバータ回路IV211(第1のインバータ回路)は、図10に示すように、PMOSトランジスタMP213と、NMOSトランジスタMN213とを有する。PMOSトランジスタMP213、NMOSトランジスタMN213は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP213、NMOSトランジスタMN213の共通ノードがインバータ回路IV211の出力端(ノードN211)となる。また、PMOSトランジスタMP213、NMOSトランジスタMN213のゲートには、インバータ回路IV210の出力信号が入力される。このため、インバータ回路IV211からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0118】

また、インバータ回路IV212(第2のインバータ回路)は、図10に示すように、PMOSトランジスタMP214と、NMOSトランジスタMN214とを有する。PMOSトランジスタMP214、NMOSトランジスタMN214は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP214、NMOSトランジスタMN214の共通ノードがインバータ回路IV212の出力端(ノードN212)となる。また、PMOSトランジスタMP214、NMOSトランジスタMN214のゲートには、インバータ回路IV211の出力信号が入力される。このため、インバータ回路IV212からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0119】

次に、図11にレベルシフタLS203の構成を示す。なお、レベルシフタLS204は、レベルシフタLS203とほぼ同様の構成のため、特に断らない限り説明は省略する。図11に示すように、レベルシフタLS203は、PMOSトランジスタMP221、MP222、MP231、MP232、MP241、MP242と、NMOSトランジスタMN221、MN222、MN231、MN232と、入力端子IN211と、出力端子OUT211、OUT211Bと、インバータ回路IV220、IV221、IV222とを有する。この入力端子IN211にクロック信号CLK1が入力される。また、出力端子OUT211からの出力信号が図8のNMOSトランジスタMN203のゲートに出力される。

【0120】

なお、レベルシフタLS204では、入力端子IN211にクロック信号CLK2が入力される。また、出力端子OUT211からの出力信号が図8のNMOSトランジスタMN204のゲートに出力される。

【0121】

PMOSトランジスタMP221(第9のトランジスタ)は、ソースがHVDD端子、ドレインがノードN231(第7のノード)、ゲートがノードN221に接続される。PMOSトランジスタMP222(第10のトランジスタ)は、ソースがHVDD端子、ドレインがノードN232(第8のノード)、ゲートがノードN222に接続される。

【0122】

NMOSトランジスタMN221(第15のトランジスタ)は、ドレインがノードN231、ソースが電源端子VD(第4の電圧供給端子)、ゲートがノードN232に接続される。NMOSトランジスタMN222(第16のトランジスタ)は、ドレインがノードN232、ソースが電源端子VD、ゲートがノードN231に接続される。ここで、電源端子VDは、図8のノードN202と接続されている。なお、レベルシフタLS204では、この電源端子VDは図8のノードN203と接続されることになる。

【0123】

インバータ回路IV220は、入力端が入力端子IN211、出力端がインバータ回路IV221の入力端に接続される。インバータ回路IV221は、入力端がインバータ回路IV220の出力端、出力端がノードN221に接続される。インバータ回路IV222は、入力端がノードN221、出力端がノードN222に接続される。

【0124】

インバータ回路IV221(第3のインバータ回路)は、図11に示すように、PMOSトランジスタMP223と、NMOSトランジスタMN223とを有する。PMOSトランジスタMP223、NMOSトランジスタMN223は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP223、NMOSトランジスタMN223の共通ノードがインバータ回路IV221の出力端(ノードN221)となる。また、PMOSトランジスタMP223、NMOSトランジスタMN223のゲートには、インバータ回路IV220の出力信号が入力される。このため、インバータ回路IV221からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0125】

また、インバータ回路IV222(第4のインバータ回路)は、図11に示すように、PMOSトランジスタMP224と、NMOSトランジスタMN224とを有する。PMOSトランジスタMP224、NMOSトランジスタMN224は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP224、NMOSトランジスタMN224の共通ノードがインバータ回路IV222の出力端(ノードN222)となる。また、PMOSトランジスタMP224、NMOSトランジスタMN224のゲートには、インバータ回路IV221の出力信号が入力される。このため、インバータ回路IV222からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0126】

PMOSトランジスタMP231(第11のトランジスタ)は、ソースが接地端子GND(第5の電圧供給端子)、ドレインがノードN241(第9のノード)、ゲートがノードN232に接続される。PMOSトランジスタMP232(第12のトランジスタ)は、ソースが接地端子GND、ドレインがノードN242(第10のノード)、ゲートがノードN231に接続される。PMOSトランジスタMP241(第13のトランジスタ)は、ソースがノードN241、ドレインが出力端子OUT211B(第11のノード)、ゲートが電源端子VDに接続される。PMOSトランジスタMP242(第14のトランジスタ)は、ソースがノードN242、ドレインが出力端子OUT211(第12のノード)、ゲートが電源端子VDに接続される。

【0127】

NMOSトランジスタMN231(第17のトランジスタ)は、ドレインが出力端子OUT211B、ソースが電源端子VE(第6の電圧供給端子)、ゲートが出力端子OUT211に接続される。NMOSトランジスタMN232(第18のトランジスタ)は、ドレインが出力端子OUT211、ソースが電源端子VE、ゲートが出力端子OUT211Bに接続される。ここで、電源端子VEは、図8のノードN203と接続されている。なお、レベルシフタLS204では、この電源端子VCは図8の出力端子OUT201と接続されることになる。

【0128】

なお、上記レベルシフタLS201、LS202、LS203、LS204を構成する全てのPMOSトランジスタ、NMOSトランジスタは、ゲート酸化膜の耐圧が電源電圧VDD以下の低耐圧トランジスタであるものとする。また、PMOSトランジスタのスレッショルド電圧Vtp及びNMOSトランジスタのスレッショルド電圧Vtnは、それぞれ1/2VDD以下であるものとする。また、図11からもわかるようにレベルシフタLS203(及びLS204)は、ノードN231、N232で接続される2つのレベルシフタで構成されているとみなすこともできる。そして、この2つのレベルシフタにおいても高電側位電源電圧と低電位側の電位差がVDD以内となっている。

【0129】

ここで、レベルシフタLS201の動作を中心に回路ユニット201について説明する。なお、レベルシフタLS202の動作は、入力クロック信号がCLK2である以外は、レベルシフタLS201と同様なため説明は省略する。図12に、レベルシフタLS201の入力端子IN210に入力するクロック信号CLK1と、出力端子OUT210(及び反転出力端子OUT210B)、及び、ノードN211、N212の電位の関係をまとめた表を示す。

【0130】

図12の表に示すように、入力端子IN210に入力するクロック信号CLK1がロウレベル(接地電圧GND)のとき、出力端子OUT210、OUT210Bの電位がそれぞれ−1/2VDD、1/2VDDとなる。また、ノードN211、N212の電位がそれぞれ接地電圧GND、1/2VDDとなる。逆に、入力端子IN210に入力するクロック信号CLK1がハイレベル(電源電圧VDD)のとき、出力端子OUT210、OUT210Bの電位がそれぞれ1/2VDD、−1/2VDDとなる。また、ノードN211、N212の電位がそれぞれ1/2VDD、接地電圧GNDとなる。

【0131】

なお、レベルシフタLS202もクロック信号CLK2に応じて同様の動作を行う。このように、レベルシフタLS201、LS202の各トランジスタのゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。

【0132】

また、上述のようにクロック信号CLK1がロウレベルのとき−1/2VDD、ハイレベルのとき1/2VDDが、レベルシフタLS201から出力される。そして、このレベルシフタLS201からの出力に応じて、図8のNMOSトランジスタMN201のオン、オフが制御される。なお、レベルシフタLS202も、クロック信号CLK2がロウレベルのとき−1/2VDD、ハイレベルのとき1/2VDDを出力する。そして、このレベルシフタLS102からの出力に応じて、図8のNMOSトランジスタMN202のオン、オフが制御される。このように、NMOSトランジスタMN201、MN202のゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。よって、回路ユニット201で使用するトランジスタを全て低耐圧トランジスタとすることができる。

【0133】

ここで更に、昇圧回路200の初期状態を考える。昇圧回路200の初期状態では、コンデンサC201が充電されておらず、クロック信号CLK3がロウレベルであっても、ノードN201が負電位側に昇圧されない。このため、ノードN201の電位が−1/2VDDではなく、GNDである。よって、レベルシフタLS201の低電位側の電源電圧である電源端子VDの電位もGNDとなる。

【0134】

ここで、図23に示した電界緩和回路技術を用いた従来のレベルシフタLS30では低電位側の電源電圧がGNDの場合、NMOSトランジスタMN22もしくはMN21がオンしないため、出力端子OUT10の電位が不定となっていた。

【0135】

しかし、本実施の形態2のレベルシフタLS201では、電源端子VDの電位がGNDであっても、NMOSトランジスタMP212もしくはMP211のソース−ゲート間の電位差を1/2VDDとすることができ、NMOSトランジスタMN212もしくはMN211をオンさせることができる。よって、出力端子OUT210の電位が不定となることがなく、レベルシフタLS201が初期状態においても正常に動作する。このため、NMOSトランジスタMN201を確実にオフさせることができ、回路ユニット201の正常動作が可能となる。

【0136】

次に、レベルシフタLS203の動作を中心に回路ユニット202について説明する。なお、レベルシフタLS204の動作は、入力クロック信号がCLK2である以外は、レベルシフタLS203と同様なため説明は省略する。図13に、レベルシフタLS203の入力端子IN211に入力するクロック信号CLK1と、出力端子OUT211(及び反転出力端子OUT211B)、及び、ノードN221、N222、N231、N232、N241、N242の電位の関係をまとめた表を示す。但し、「Vtp」はPMOSトランジスタのスレッショルド電圧である。

【0137】

図13の表に示すように、入力端子IN211に入力するクロック信号CLK1がロウレベル(接地電圧GND)のとき、出力端子OUT211、OUT211Bの電位がそれぞれ−VDD、GNDとなる。また、ノードN221、N222の電位がそれぞれGND、1/2VDDとなる。ノードN231、N232の電位がそれぞれ1/2VDD、−1/2VDDとなる。ノードN241、N242の電位がそれぞれGND、−VDD+Vtpとなる。

【0138】

逆に、入力端子IN211に入力するクロック信号CLK1がハイレベル(電源電圧VDD)のとき、出力端子OUT211、OUT211Bの電位がそれぞれGND、−VDDとなる。また、ノードN221、N222の電位がそれぞれ1/2VDD、GNDとなる。ノードN231、N232の電位がそれぞれ−1/2VDD、1/2VDDとなる。ノードN241、N242の電位がそれぞれ−VDD+Vtp、GNDとなる。

【0139】

なお、レベルシフタLS204もクロック信号CLK2に応じて同様の動作を行う。このように、レベルシフタLS203、LS204の各トランジスタのゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。

【0140】

また、上述のようにクロック信号CLK1がロウレベルのとき−VDD、ハイレベルのときGNDが、レベルシフタLS203から出力される。そして、このレベルシフタLS203からの出力に応じて、図8のNMOSトランジスタMN203のオン、オフが制御される。なお、レベルシフタLS204も、クロック信号CLK2がロウレベルのとき−VDD、ハイレベルのときGNDが、レベルシフタLS203から出力される。そして、このレベルシフタLS204からの出力に応じて、図8のNMOSトランジスタMN204のオン、オフが制御される。このように、NMOSトランジスタMN203、MN204のゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。よって、回路ユニット202で使用するトランジスタを全て低耐圧トランジスタとすることができる。

【0141】

以上、昇圧回路200では、使用するトランジスタを全て低耐圧トランジスタとしても、出力電圧VOUTを−VDDとすることができる。また、図23に示した電界緩和回路技術を用いた従来のレベルシフタを用いた場合、動作開始時の初期状態でレベルシフタが不定な電位を出力するため、負電位側の昇圧動作を行えなかった。しかし、本実施の形態2の昇圧回路200のレベルシフタLS201は、動作開始時の初期状態であって不定な電圧を出力しない。このため、昇圧回路200が正常に昇圧動作を開始することができる。

【0142】

なお、本発明は上記実施の形態に限られたものでなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、昇圧回路100または200を更に多段構成にして、出力電圧を2VDDより高電位側、または−VDDより負電位側に昇圧してもよい。

【0143】

また、実施の形態1、2では、各コンデンサの一端に印加されるインバータ回路が出力する出力信号の振幅レベルを1/2VDDとしている。しかし、この振幅レベルを、1/2VDD以下としてもよい。例えば、実施の形態1で、回路ユニット101のインバータ回路IV102のHVDD端子の電位を1/2VDDから電位ΔV1分低くする。但し、この場合、コンデンサC101の他端に接続されるノードの電位の昇圧レベルも、1/2VDDよりΔV1分低下することになる。よって、レベルシフタLS101、LS102のHVDD端子の電位も同様に1/2VDDからΔV1低くする。また、NMOSトランジスタMN121、122のゲートに印加される電位、および、インバータ回路IV110の高電位側の電源電圧を、そのHVDD端子の電位の2倍の電位とする。

【符号の説明】

【0144】

100、200 昇圧回路

MP101〜MP104、MP111、MP112、MP121、MP122、MP131、MP132、MP211、MP212、MP221、MP222、MP231、MP232、MP241、MP242 PMOSトランジスタ

MN201〜MN204、MN111、MN112、MN121、MN122、MN131、MN132、MN141、MN142、MN151、MN152、MN161、MN162、MN211、MN212、MN221、MN222、MN231、MN232 NMOSトランジスタ

LS101〜LS104、LS201〜LS204 レベルシフタ

IV101〜IV104、IV110、IV111、IV201〜IV204、IV210、IV211、IV212、IV220、IV221、IV222 インバータ回路

C101、C102、C201、C202 コンデンサ

【技術分野】

【0001】

本発明は、昇圧回路に関するものである。

【背景技術】

【0002】

従来の正電位の昇圧回路1を図14に示す。図14に示すように、昇圧回路1は、PMOSトランジスタMP1、MP2と、コンデンサC1と、レベルシフタLS1、LS2と、アンプAMP1を有する。PMOSトランジスタMP1は、電源電圧端子VDDとノードN1との間に接続される。また、ゲートにレベルシフタLS1の出力信号が入力される。PMOSトランジスタMP2は、ノードN1とノードN2との間に接続される。また、ゲートにレベルシフタLS2の出力信号が入力される。

【0003】

レベルシフタLS1は、クロック信号CLK1を入力し、出力クロック信号をPMOSトランジスタMP1のゲートへ出力する。レベルシフタLS1の電源電圧は、高電位側がノードN1、低電位側が接地端子GNDから供給される。レベルシフタLS2は、クロック信号CLK2を入力し、出力クロック信号をPMOSトランジスタMP2のゲートへ出力する。レベルシフタLS2の電源電圧は、高電位側が出力端子OUT1、低電位側が接地端子GNDから供給される。なお、便宜上、符号「VDD」「GND」は、端子名を示すと同時に、その端子が供給する電圧を示すものとする。また、出力端子OUT1の電圧をVOUTとする。

【0004】

コンデンサC1は、一端がアンプAMP1の出力、他端がノードN1に接続される。アンプAMP1は、クロック信号CLK3を入力し、出力クロック信号をコンデンサC1の一端に出力する。なお、アンプAMP1の電源電圧は、高電位側が電源電圧端子VDD、低電位側が接地端子GNDから供給される。

【0005】

図15に昇圧回路1の動作を示すタイミングチャートを示す。図15に示すように、時刻t1〜t2の期間、クロック信号CLK1はロウレベルとなり、PMOSトランジスタMP1がオン状態となる。よって、電源電圧端子VDDとノードN1が電気的に接続され、ノードN1の電位が電源電圧VDDとなる。一方、この期間において、クロック信号CLK3はロウレベルであるためコンデンサC1の一端の電位は接地電圧GNDであり、コンデンサC1が充電される。

【0006】

時刻t3〜t6の期間、クロック信号CLK3はハイレベルとなり、コンデンサC1の他端の電位が電源電圧VDDとなる。このため、充電されたコンデンサC1の一端の電位が昇圧され、ノードN1の電位が2VDDとなる。また、時刻t4〜t5の期間、クロック信号CLK2がロウレベルとなり、PMOSトランジスタMP2がオン状態となる。よって、ノードN1と出力端子OUT1が電気的に接続され、出力電圧VOUTが2VDDとなる。

【0007】

ここで、時刻t3〜t6の期間、ノードN1の電位が2VDDとなる。このため、電源電圧端子VDDに電流の逆流を防ぐため、時刻t2〜t6の期間、PMOSトランジスタMP1をオフさせる必要がある。よって、時刻t2〜t6の期間、PMOSトランジスタMP1をオフさせるため、図16に示すような構成のレベルシフタLS1を用いる。

【0008】

図16にレベルシフタLS1の詳細な回路構成を示す。なお、レベルシフタLS2も同様の構成である。レベルシフタLS1は、PMOSトランジスタMP11、MP12と、NMOSトランジスタMN11、MN12と、入力端子IN10と、出力端子OUT10、OUT10Bと、インバータ回路IV10とを有する。

【0009】

PMOSトランジスタMP11は、電源電圧端子VDDと出力端子OUT10Bとの間に接続される。また、ゲートが出力端子OUT10に接続される。PMOSトランジスタMP12は、電源電圧端子VDDと出力端子OUT10との間に接続される。また、ゲートが出力端子OUT10Bに接続される。NMOSトランジスタMN11は、出力端子OUT10Bと接地端子GNDとの間に接続される。また、ゲートが入力端子IN10に接続される。NMOSトランジスタMN12は、出力端子OUT10と接地端子GNDとの間に接続される。また、ゲートがインバータ回路IV10の出力端子に接続される。

【0010】

図17に、レベルシフタLS1の入力端子INに入力するクロック信号CLK1と、出力端子OUT10(及び反転出力端子OUT10B)の電位の関係をまとめた表を示す。このように、クロック信号CLK1がロウレベル(図の「L」)のとき、レベルシフタLS1の出力は接地電圧GND、クロック信号CLK1がハイレベル(図の「H」)のとき、レベルシフタLS1の出力は2VDDの電位となる。

【0011】

ここで、レベルシフタLS1の電源電圧のハイレベル側とロウレベル側の電位差は、2×VDDとなる。このため、PMOSトランジスタMP11、MP12及びNMOSトランジスタMN11、MN12は、電源電圧VDDの2倍の電位差に耐えられる高耐圧トランジスタで構成する必要がある。但し、高耐圧トランジスタは、ゲート酸化膜を厚くする必要があり、ゲート酸化膜が厚いほど大きなチャンネル長が必要となるため、厚膜トランジスタは、レイアウト面積を大きくとる問題を有する。

【0012】

また、図18に負電圧−VDDを生成する昇圧回路2の構成を示す。図18に示すように、昇圧回路2は、NMOSトランジスタMN1、MN2と、コンデンサC1と、レベルシフタLS3、LS4と、アンプAMP1を有する。昇圧回路2の動作タイミングチャートは、図15の昇圧回路1のタイミングチャートの極性が異なる以外は、基本的に同様であるため省略する。更に、レベルシフタLS3(及びLS4)の構成を図19に示す。また、図20にレベルシフタLS3の入力端子INに入力するクロック信号CLK1と、出力端子OUT10(及び反転出力端子OUT10B)の電位の関係をまとめた表を示す。レベルシフタLS3も、レベルシフタLS1と同様、電源電圧のハイレベル側とロウレベル側の電位差は、2×VDDとなる。このため、PMOSトランジスタMP11、MP12及びNMOSトランジスタMN11、MN12は、高耐圧トランジスタで構成する必要がある。

【0013】

なお、昇圧回路の例として特許文献1のような技術が開示されている。しかし、この技術でも、昇圧回路1と同様に、高耐圧トランジスタの使用が前提となっている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2005−129815号公報

【発明の概要】

【発明が解決しようとする課題】

【0015】

ワンチップ化された集積装置において、図16のレベルシフタLS1や図19のレベルシフタLS3のような高耐圧トランジスタを使用した回路は、耐圧が電源電圧VDD程度の低耐圧トランジスタを使用した回路と製造プロセスを分けて作成される。このため、製造工程が複雑化し、製造期間や製造コストの増大要因となる。また、ゲート酸化膜が厚膜となる高耐圧トランジスタは、レイアウト面積が大きくなるため、チップ面積の増大の要因にもなる。

【0016】

このため、レベルシフタLS1のように厚膜トランジスタを使用せず、低耐圧トランジスタでレベルシフタを構成するのに電界緩和回路技術を用いることが考えられる。このような電界緩和回路技術を用いて構成したレベルシフタLS10を図21に示す。

【0017】

図21に示すように、レベルシフタLS10は、PMOSトランジスタMP11、MP12、MP21、MP22と、NMOSトランジスタMN11、MN12、MN21、MN22と、入力端子IN10と、出力端子OUT10、OUT10Bと、インバータ回路IV10とを有する。

【0018】

PMOSトランジスタMP11は、電源電圧端子VDDとノードN11との間に接続される。また、ゲートがノードN12に接続される。PMOSトランジスタMP12は、電源電圧端子VDDとノードN12との間に接続される。また、ゲートがノードN11に接続される。PMOSトランジスタMP21は、ノードN11と出力端子OUT10Bとの間に接続される。PMOSトランジスタMP22は、ノードN12と出力端子OUT10との間に接続される。PMOSトランジスタMP21、MP22のゲートは、電源電圧端子VDDが接続される。

【0019】

NMOSトランジスタMN11は、ノードN21と接地端子GNDとの間に接続される。また、ゲートが入力端子IN10に接続される。NMOSトランジスタMN12は、ノードN22と接地端子GNDとの間に接続される。また、ゲートがインバータ回路IV10の出力端子に接続される。NMOSトランジスタMN21は、出力端子OUT10BとノードN21との間に接続される。NMOSトランジスタMN22は、出力端子OUT10とノードN22との間に接続される。また、NMOSトランジスタMN21、MN22は、ゲートが電源電圧端子VDDに接続される。

【0020】

図22に、レベルシフタLS10の入力端子IN10に入力するクロック信号と、出力端子OUT10(及び反転出力端子OUT10B)の電位及び各ノードの電位の関係をまとめた表を示す。但し、「Vtp」はPMOSトランジスタのスレッショルド電圧、「Vtn」はNMOSトランジスタのスレッショルド電圧である。

【0021】

図22の表に示すように、入力端子IN10に入力するクロック信号がロウレベル(図の「L」)のとき、レベルシフタLS1と同様、出力端子OUT10、OUT10Bの電位がそれぞれ接地電圧GND、2VDDとなる。しかし、各ノードの電位は図22の表に示すようになり、各トランジスタのゲート−ドレイン間もしくはゲート−ソース間の電位差は、電源電圧VDD以内に収まる。このことは、入力端子IN10に入力するクロック信号がハイレベル(図の「H」)のときも同様である。この電界緩和回路技術を用いたレベルシフタLS10を、昇圧回路1のLS1と交換することで、昇圧回路1で使用するトランジスタを全て低耐圧トランジスタとすることができる。

【0022】

なお、負電圧を生成する昇圧回路2に、昇圧回路1と同様、電界緩和回路技術を用いて構成した場合のレベルシフタLS30の回路構成を図23に示す。また、図24に、レベルシフタLS30の入力端子IN10に入力するクロック信号と、出力端子OUT10(及び反転出力端子OUT10B)の電位及び各ノードの電位の関係をまとめた表を示す。

【0023】

ここで、例えばレベルシフタLS10の場合、高電位側の電源電圧は、図14のノードN1の電位を利用している。このため、昇圧回路1の動作開始時の初期状態では、ノードN1の電位が昇圧されておらず2VDDではなくVDDである。よって、入力端子IN10に入力するクロック信号CLK1がハイレベルの場合であっても、図21のPMOSトランジスタMP22がオンせず、出力端子OUT10からの出力電位が不定となる。このため、図14のPMOSトランジスタMP1をオフさせることができない。結果として、昇圧回路1が昇圧動作を行うことができず、出力電圧VOUTを2VDDとすることができない。このため、電界緩和回路技術を用いて構成したレベルシフタを使用することができず、低耐圧トランジスタで昇圧回路1を構成することができない問題があった。

【0024】

更に、昇圧回路2においても、レベルシフタLS30の低電位側の電源電圧は、図18のノードN1の電位を利用している。このため、昇圧回路2の動作開始時の初期状態では、ノードN1の電位が負側に昇圧されておらず−VDDではなく接地電圧GNDとなっている。よって、入力端子IN10に入力するクロック信号CLK1がロウレベルの場合であっても、図23のNMOSトランジスタMN22がオンせず、出力端子OUT10からの出力電位が不定となる。このため、図18のNMOSトランジスタMN1をオフさせることができない。結果として、昇圧回路2が負電位側に昇圧動作を行うことができず、出力電圧VOUTを−VDDとすることができない。このため、電界緩和回路技術を用いて構成したレベルシフタを使用することができず、昇圧回路1と同様、低耐圧トランジスタで昇圧回路2を構成することができない問題があった。

【課題を解決するための手段】

【0025】

本発明は、第1の電源電圧を、正側または負側の所定の電圧に昇圧する昇圧回路であって、第1のノードに接続される第1のトランジスタと、一端が前記第1のノードに接続され、前記第1のトランジスタの活性化時に前記第1のノードの電圧で充電される第1の容量素子と、前記第1のトランジスタの制御端子に第1の制御信号を出力する第1の制御信号生成回路を有し、前記第1の容量素子は、前記第1のトランジスタの非活性化時に、他端に印加される前記第1の電源電圧の1/2以下の電圧により前記第1のノードの電位を、正側または負側の第2の電圧に昇圧し、前記第1の制御信号生成回路は、前記第1のトランジスタの非活性化時の前記第1の制御信号の電位を、前記第2の電位とし、前記第1のトランジスタの活性化時の前記第1の制御信号の電位を、前記第2の電位との差が前記第1の電源電圧以内となる電位とする昇圧回路である。

【0026】

本発明にかかる昇圧回路は、制御信号生成回路の動作電圧の範囲を、第2の電位から第1の電源電圧以内とする。このため、当該昇圧回路の初期状態で、第1のノードが昇圧されていなくても、制御信号生成回路から不定な電圧の制御信号生成回路が出力されない。このため、耐圧が第1の電源電圧以内であるトランジスタで制御信号生成回路を構成することができる。

【発明の効果】

【0027】

本発明にかかる昇圧回路は、耐圧が第1の電源電圧以内の低耐圧トランジスタを使用して構成することができ、回路規模の削減、製造工程の簡素化が行える。

【図面の簡単な説明】

【0028】

【図1】実施の形態1にかかる半導体記憶装置のブロック図である。

【図2】実施の形態1にかかる正電位の昇圧回路100の回路構成である。

【図3】実施の形態1にかかる昇圧回路100の動作タイミングチャートである。

【図4】実施の形態1にかかるレベルシフタLS101の回路構成である。

【図5】実施の形態1にかかるレベルシフタLS103の回路構成である。

【図6】実施の形態1にかかるレベルシフタLS101の入出力信号と、各ノードの電位の関係をまとめた表である。

【図7】実施の形態1にかかるレベルシフタLS103の入出力信号と、各ノードの電位の関係をまとめた表である。

【図8】実施の形態2にかかる負電位の昇圧回路200の回路構成である。

【図9】実施の形態2にかかる昇圧回路200の動作タイミングチャートである。

【図10】実施の形態2にかかるレベルシフタLS201の回路構成である。

【図11】実施の形態2にかかるレベルシフタLS203の回路構成である。

【図12】実施の形態2にかかるレベルシフタLS201の入出力信号と、各ノードの電位の関係をまとめた表である。

【図13】実施の形態2にかかるレベルシフタLS203の入出力信号と、各ノードの電位の関係をまとめた表である。

【図14】従来の正電位の昇圧回路1の回路構成である。

【図15】従来の昇圧回路1の動作タイミングチャートである。

【図16】従来のレベルシフタLS1の回路構成である。

【図17】従来のレベルシフタLS1の入出力信号の電位の関係をまとめた表である。

【図18】従来の負電位の昇圧回路2の回路構成である。

【図19】従来のレベルシフタLS3の回路構成である。

【図20】従来のレベルシフタLS3の入出力信号の電位の関係をまとめた表である。

【図21】従来のレベルシフタLS10の回路構成である。

【図22】従来のレベルシフタLS10の入出力信号と、各ノードの電位の関係をまとめた表である。

【図23】従来のレベルシフタLS30の回路構成である。

【図24】従来のレベルシフタLS30の入出力信号と、各ノードの電位の関係をまとめた表である。

【発明を実施するための形態】

【0029】

発明の実施の形態1

【0030】

以下、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。この実施の形態は、本発明をフラッシュメモリ等の半導体記憶装置における正の昇圧回路に適用したものである。

【0031】

図1に本実施の形態1にかかる半導体記憶装置MEM1のブロック構成図を示す。図1に示すように、半導体記憶装置MEM1は、メモリセルアレイCELLと、アドレスバッファADDBと、ロウレコーダLDECと、カラムデコーダCDECと、カラムセレクタCSELと、消去回路RSETと、スイッチ回路SWと、高電圧生成回路PCHRGEと、負電圧生成回路NCHRGEとを有する。

【0032】

メモリセルアレイCELLは、マトリクス状に記憶素子が配置されている。各記憶素子には、ビット線、ワード線が接続されている。ロウデコーダLDECは、アドレスバッファADDBから送られてくるロウアドレスデータに応じて、1つのワード線を選択する。カラムデコーダCDECは、アドレスバッファADDBから送られてくるカラムアドレスデータに応じて、1つのビット線を選択する。カラムセレクタCSELは、カラムデコーダCDECが選択したビット線をデータ線と接続する。

【0033】

高電圧生成回路PCHRGEは、電源電圧VDDよりも高い電圧VPPを生成する。負電圧生成回路NCHRGEは、接地電圧GNDよりも低い負電圧VKKを生成する。スイッチ回路SWは、高電圧生成回路PCHRGEもしくは負電圧生成回路NCHRGEが生成した電圧を必要に応じて、ロウデコーダLDECや、消去回路RSETに供給する。

【0034】

例えば、高電圧生成回路PCHRGEが生成した高電位の電圧VPPは、ロウデコーダLDECのワード線ドライバに供給され、ハイレベルのワード信号に利用される。また、負電圧生成回路NCHRGEが生成した負電位の電圧VKKは、ロウデコーダLDECのワード線ドライバに供給され、ロウレベルのワード信号に利用される。

【0035】

消去回路RSETは、半導体記憶装置MEM1がフラッシュメモリである場合、メモリセルアレイCELLの記憶素子が記憶しているデータを消去する機能を有する。このデータ消去時に、高電圧生成回路PCHRGE、負電圧生成回路NCHRGEが生成した高電位電圧VPP、負電圧VKKを利用する。この高電位電圧VPPを記憶素子のフローティングゲートの一方、負電圧VKKを他方にかけることで、フローティングゲートに蓄えられた電荷を抜く作業を行う。

【0036】

図2に本実施の形態1にかかる高電圧生成回路PCHRGEが有する昇圧回路100の構成の一例を示す。図2に示すように、昇圧回路100は、PMOSトランジスタMP101、MP102、MP103、MP104と、レベルシフタLS101、LS102、LS103、LS104と、コンデンサC101、C102と、インバータ回路IV101、IV102、IV103、IV104とを有する。

【0037】

PMOSトランジスタMP101(第1のトランジスタ)は、ソースもしくはドレインの一端が電源電圧VDD(第1の電源電圧)を供給する電源電圧端子VDD(第1の電源端子)、ソースもしくはドレインの他端がノードN101(第1のノード)に接続される。また、PMOSトランジスタMP101は、ゲートにレベルシフタLS101の出力信号が入力される。PMOSトランジスタMP102(第2のトランジスタ)は、ソースもしくはドレインの一端がノードN101、ソースもしくはドレインの他端がノードN102(第2のノード)に接続される。また、PMOSトランジスタMP102は、ゲートにレベルシフタLS102の出力信号が入力される。なお、便宜上、符号「VDD」は、電源電圧端子名を示すと同時に、電源電圧VDDを示すものとする。また、符号「GND」は、接地端子名を示すと同時に、接地電圧GNDを示すものとする。

【0038】

レベルシフタLS101(第1の制御信号生成回路)は、クロック信号CLK1を入力し、出力信号(第1の制御信号)をPMOSトランジスタMP101のゲートへ出力する。レベルシフタLS101の電源電圧は、高電位側がノードN101、低電位側がHVDD電圧端子から供給される。なお、HVDD電圧端子は、電源電圧VDDの1/2の電圧(以下、1/2VDDと称す)を供給する。また、このHVDD電圧端子からの1/2VDDの電圧は、電源電圧VDDを同じ抵抗値の抵抗で分圧した電位から生成してもよい。

【0039】

レベルシフタLS102(第2の制御信号生成回路)は、クロック信号CLK2を入力し、出力信号(第2の制御信号)をPMOSトランジスタMP102のゲートへ出力する。レベルシフタLS102の電源電圧は、高電位側がノードN102、低電位側がHVDD電圧端子から供給される。

【0040】

インバータ回路IV101は、クロック信号CLK3を入力し、その反転信号をインバータ回路IV102の入力へ出力する。インバータ回路IV102は、図2に示すように、PMOSトランジスタMP105と、NMOSトランジスタMN105とを有する。PMOSトランジスタMP105、NMOSトランジスタMN105は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP105、NMOSトランジスタMN105の共通ノードがインバータ回路IV102の出力端となる。また、PMOSトランジスタMP105、NMOSトランジスタMN105のゲートには、インバータ回路IV101の出力信号が入力される。このため、インバータ回路IV102からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0041】

コンデンサC101(第1の容量素子)は、一端がインバータ回路IV102の出力端、他端がノードN101に接続される。

【0042】

PMOSトランジスタMP103(第9のトランジスタ)は、ソースもしくはドレインの一端がノードN102、ソースもしくはドレインの他端がノードN103(第7のノード)に接続される。また、PMOSトランジスタMP103は、ゲートにレベルシフタLS103の出力信号が入力される。PMOSトランジスタMP104(第10のトランジスタ)は、ソースもしくはドレインの一端がノードN103、ソースもしくはドレインの他端が出力端子OUT101(第8のノード)に接続される。また、PMOSトランジスタMP104は、ゲートにレベルシフタLS104の出力信号が入力される。

【0043】

レベルシフタLS103(第3の制御信号生成回路)は、クロック信号CLK1を入力し、出力信号(第3の制御信号)をPMOSトランジスタMP103のゲートへ出力する。レベルシフタLS103の詳細な構成は後述するが、高電位側の電源電圧がノードN102及びN103、低電位側が電源電圧端子VDDから供給される。レベルシフタLS104(第4の制御信号生成回路)は、クロック信号CLK2を入力し、出力信号(第4の制御信号)をPMOSトランジスタMP104のゲートへ出力する。レベルシフタLS104の詳細な構成は後述するが、高電位側の電源電圧がノードN103及び出力端子OUT101、低電位側が電源電圧端子VDDから供給される。

【0044】

インバータ回路IV103は、クロック信号CLK3を入力し、その反転信号をインバータ回路IV104の入力へ出力する。インバータ回路IV104は、図2に示すように、PMOSトランジスタMP106と、NMOSトランジスタMN106とを有する。PMOSトランジスタMP106、NMOSトランジスタMN106は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP106、NMOSトランジスタMN106の共通ノードがインバータ回路IV104の出力端となる。また、PMOSトランジスタMP106、NMOSトランジスタMN106のゲートには、インバータ回路IV103の出力信号が入力される。このため、インバータ回路IV104からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0045】

コンデンサC102(第2の容量素子)は、一端がインバータ回路IV104の出力端、他端がノードN103に接続される。

【0046】

なお、上記PMOSトランジスタ、NMOSトランジスタは、ゲート酸化膜の耐圧が電源電圧VDD以下の低耐圧トランジスタであるものとする。また、PMOSトランジスタのスレッショルド電圧Vtp及びNMOSトランジスタのスレッショルド電圧Vtnは、それぞれ1/2VDD以下であるものとする。

【0047】

図3に昇圧回路100の動作を説明するタイミングチャートを示す。なお、本説明では、図2の回路ユニット101と、回路ユニット102に分けて動作の説明を行う。回路ユニット101の動作を時刻t1〜t6、回路ユニット102の動作を時刻t6〜t11に説明する。

【0048】

まず、回路ユニット101の動作は、図3に示すように、時刻t1〜t2の期間、クロック信号CLK1はロウレベルとなり、PMOSトランジスタMP101がオン状態となる。よって、電源電圧端子VDDとノードN101が電気的に接続され、ノードN101の電位が電源電圧VDDとなる。一方、この期間において、クロック信号CLK3はロウレベルであり、インバータ回路IV102から出力される電位は接地電圧GNDである。このため、コンデンサC101の一端の電位は接地電圧GNDとなり、コンデンサC101は、電位差VDDで充電される。

【0049】

時刻t2で、クロック信号CLK1はハイレベルに立ち上がる。このため、電源電圧端子VDDとノードN101が電気的に遮断される。また、クロック信号CLK2によりPMOSトランジスタMP102もオフ状態のため、ノードN101はハイインピーダンスとなる。但し、コンデンサC101が充電されているため、ノードN101の電位はVDDで保持される。

【0050】

時刻t3で、クロック信号CLK3がハイレベルに立ち上がる。このため、インバータ回路IV102から出力される電位が1/2VDDとなる。よって、コンデンサC101の一端に1/2VDDの電位が印加され、コンデンサC101の他端の電位が1/2VDD分昇圧される。よって、ノードN101の電位が3/2VDD(=VDD+1/2VDD)となる。

【0051】

時刻t4〜t5の期間、クロック信号CLK2はロウレベルとなり、PMOSトランジスタMP102がオン状態となる。よって、ノードN101とノードN102が電気的に接続され、ノードN102の電位が3/2VDDとなる。

【0052】

時刻t5で、クロック信号CLK2はハイレベルに立ち上がる。このため、ノードN101とノードN102が電気的に遮断される。

【0053】

次に、回路ユニット102の動作は、図3に示すように、時刻6〜t7の期間、クロック信号CLK1はロウレベルとなり、PMOSトランジスタMP103がオン状態となる。よって、ノードN102とノードN103が電気的に接続され、ノードN103の電位が3/2VDDとなる。一方、この期間において、クロック信号CLK3はロウレベルであり、インバータ回路IV104から出力される電位は接地電圧GNDである。このため、コンデンサC102の一端の電位は接地電圧GNDとなり、コンデンサC102は、電位差3/2VDDで充電される。

【0054】

時刻t7で、クロック信号CLK1はハイレベルに立ち上がる。このため、ノードN102とノードN103が電気的に遮断される。また、クロック信号CLK2によりPMOSトランジスタMP104もオフ状態のため、ノードN103はハイインピーダンスとなる。但し、コンデンサC102が充電されているため、ノードN103の電位は3/2VDDで保持される。

【0055】

時刻t8で、クロック信号CLK3がハイレベルに立ち上がる。このため、インバータ回路IV102から出力される電位が1/2VDDとなる。よって、コンデンサC102の一端に1/2VDDの電位が印加され、コンデンサC102の他端の電位が1/2VDD分昇圧される。よって、ノードN103の電位が2VDD(=3/2VDD+1/2VDD)となる。

【0056】

時刻t9〜t10の期間、クロック信号CLK2はロウレベルとなり、PMOSトランジスタMP104がオン状態となる。よって、ノードN103と出力端子OUT101が電気的に接続され、出力端子の電位が2VDDとなる。

【0057】

時刻t11で、クロック信号CLK2はハイレベルに立ち上がる。このため、ノードN103と出力端子OUT101が電気的に遮断される。

【0058】

ここで、時刻t3〜t6、t8〜t11の期間、ノードN101、N103の電位が、それぞれ電源電圧VDD、ノードN102の電位3/2VDDより大きくなる。このため、電源電圧端子VDD、ノードN102への電流の逆流を防ぐため、時刻t2〜t6、t7〜t11の期間、PMOSトランジスタMP101、MP103をオフさせる必要がある。このため、回路ユニット101では、図4に示すような構成のレベルシフタLS101、LS102、回路ユニット102では、図5に示すような構成のレベルシフタLS103、LS104を用いる。

【0059】

図4にレベルシフタLS101の構成を示す。なお、レベルシフタLS102は、レベルシフタLS101とほぼ同様の構成のため、特に断らない限り説明は省略する。図4に示すように、レベルシフタLS101は、PMOSトランジスタMP111、MP112と、NMOSトランジスタMN111、MN112、MN121、MN122と、入力端子IN110と、出力端子OUT110、OUT110Bと、インバータ回路IV110とを有する。この入力端子IN110にクロック信号CLK1が入力される。また、出力端子OUT110からの出力信号が図2のPMOSトランジスタMP101のゲートに出力される。

【0060】

なお、レベルシフタLS102では、入力端子IN110にクロック信号CLK2が入力される。また、出力端子OUT110からの出力信号が図2のPMOSトランジスタMP102のゲートに出力される。

【0061】

PMOSトランジスタMP111(第3のトランジスタ)は、ソースが電源端子VA(第1の電圧供給端子)、ドレインが出力端子OUT110B(第3のノード)、ゲートが出力端子OUT110(第4のノード)に接続される。PMOSトランジスタMP112(第4のトランジスタ)は、ソースが電源端子VA、ドレインが出力端子OUT110、ゲートが出力端子OUT110Bに接続される。ここで、電源端子VAは、図2のノードN101と接続されている。なお、レベルシフタLS102では、この電源端子VAは図2のノードN102と接続されることになる。

【0062】

NMOSトランジスタMN111(第7のトランジスタ)は、ドレインがノードN111(第5のノード)、ソースがHVDD端子(第3の電圧供給端子)、ゲートが入力端子IN110に接続される。NMOSトランジスタMN112(第8のトランジスタ)は、ドレインがノードN112(第6のノード)、ソースがHVDD端子、ゲートがインバータ回路IV110の出力端に接続される。NMOSトランジスタMN121(第5のトランジスタ)は、ドレインが出力端子OUT110、ソースがノードN111、ゲートが電源電圧端子VDD(第2の電圧供給端子)に接続される。NMOSトランジスタMN122(第6のトランジスタ)は、ドレインが出力端子OUT110B、ソースがノードN112、ゲートが電源電圧端子VDDに接続される。

【0063】

インバータ回路IV110は、入力端が入力端子IN110、出力端がNMOSトランジスタMN112のゲートに接続される。

【0064】

次に、図5にレベルシフタLS103の構成を示す。なお、レベルシフタLS104は、レベルシフタLS103とほぼ同様の構成のため、特に断らない限り説明は省略する。図5に示すように、レベルシフタLS103は、PMOSトランジスタMP121、MP122、MP131、MP132と、NMOSトランジスタMN131、MN132、MN141、MN142、MN151、MN152、MN161、MN162と、入力端子IN111と、出力端子OUT111、OUT111Bと、インバータ回路IV111とを有する。この入力端子IN111にクロック信号CLK1が入力される。また、出力端子OUT111からの出力信号が図2のPMOSトランジスタMP103のゲートに出力される。

【0065】

なお、レベルシフタLS104では、入力端子IN111にクロック信号CLK2が入力される。また、出力端子OUT111からの出力信号が図2のPMOSトランジスタMP104のゲートに出力される。

【0066】

PMOSトランジスタMP121(第11のトランジスタ)は、ソースが電源端子VB(第4の電圧供給端子)、ドレインがノードN131(第9のノード)、ゲートがノードN132(第10のノード)に接続される。PMOSトランジスタMP122(第12のトランジスタ)は、ソースが電源端子VB、ドレインがノードN132、ゲートがノードN131に接続される。ここで、電源端子VBは、図2のノードN102と接続されている。なお、レベルシフタLS104では、この電源端子VBは図2のノードN103と接続されることになる。

【0067】

NMOSトランジスタMN141(第17のトランジスタ)は、ドレインがノードN121(第11のノード)、ソースがHVDD端子(第6の電圧供給端子)、ゲートが入力端子IN111に接続される。NMOSトランジスタMN142(第18のトランジスタ)は、ドレインがノードN122(第12のノード)、ソースがHVDD端子、ゲートがインバータ回路IV111の出力端に接続される。NMOSトランジスタMN131(第15のトランジスタ)は、ドレインがノードN131、ソースがノードN121、ゲートが電源電圧端子VDD(第5の電圧供給端子)に接続される。NMOSトランジスタMN132(第16のトランジスタ)は、ドレインがノードN132、ソースがノードN122、ゲートが電源電圧端子VDDに接続される。

【0068】

インバータ回路IV111は、入力端が入力端子IN111、出力端がNMOSトランジスタMN142のゲートに接続される。

【0069】

PMOSトランジスタMP131(第13のトランジスタ)は、ソースが電源端子VC(第7の電圧供給端子)、ドレインが出力端子OUT111B(第13のノード)、ゲートが出力端子OUT111(第14のノード)に接続される。PMOSトランジスタMP132(第14のトランジスタ)は、ソースが電源端子VC、ドレインが出力端子OUT111、ゲートが出力端子OUT111Bに接続される。ここで、電源端子VCは、図2のノードN103と接続されている。なお、レベルシフタLS104では、この電源端子VCは図2の出力端子OUT101と接続されることになる。

【0070】

NMOSトランジスタMN161(第21のトランジスタ)は、ドレインがノードN141(第15のノード)、ソースが電源電圧端子VDD、ゲートがノードN132に接続される。NMOSトランジスタMN162(第22のトランジスタ)は、ドレインがノードN142(第16のノード)、ソースが電源電圧端子VDD、ゲートがノードN131に接続される。NMOSトランジスタMN151(第19のトランジスタ)は、ドレインが出力端子OUT111B、ソースがノードN141、ゲートが電源端子VBに接続される。NMOSトランジスタMN152(第20のトランジスタ)は、ドレインが出力端子OUT111、ソースがノードN142、ゲートが電源端子VBに接続される。

【0071】

なお、上記レベルシフタLS101、LS102、LS103、LS104を構成する全てのPMOSトランジスタ、NMOSトランジスタは、ゲート酸化膜の耐圧が電源電圧VDD以下の低耐圧トランジスタであるものとする。また、PMOSトランジスタのスレッショルド電圧Vtp及びNMOSトランジスタのスレッショルド電圧Vtnは、それぞれ1/2VDD以下であるものとする。また、図5からもわかるようにレベルシフタLS103(及びLS104)は、ノードN131、N132で接続される2つのレベルシフタで構成されているとみなすこともできる。そして、この2つのレベルシフタにおいても高電側位電源電圧と低電位側電源電圧の電位差がVDD以内となっている。

【0072】

ここで、レベルシフタLS101の動作を中心に回路ユニット101ついて、説明する。なお、レベルシフタLS102の動作は、入力クロック信号がCLK2である以外は、レベルシフタLS101と同様なため説明は省略する。図6に、レベルシフタLS101の入力端子IN110に入力するクロック信号CLK1と、出力端子OUT110(及び反転出力端子OUT110B)、及び、ノードN111、N112の電位の関係をまとめた表を示す。但し、「Vtn」はNMOSトランジスタのスレッショルド電圧である。

【0073】

図6の表に示すように、入力端子IN110に入力するクロック信号CLK1がロウレベル(接地電圧GND)のとき、出力端子OUT110、OUT110Bの電位がそれぞれ1/2VDD、3/2VDDとなる。また、ノードN111、N112の電位がそれぞれVDD−Vtn、1/2VDDとなる。

【0074】

逆に、入力端子IN110に入力するクロック信号CLK1がハイレベル(電源電圧VDD)のとき、出力端子OUT110、OUT110Bの電位がそれぞれ3/2VDD、1/2VDDとなる。また、ノードN111、N112の電位がそれぞれ1/2VDD、VDD−Vtnとなる。

【0075】

なお、レベルシフタLS102もクロック信号CLK2に応じて同様の動作を行う。このように、レベルシフタLS101、LS102の各トランジスタのゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。

【0076】

また、上述のようにクロック信号CLK1がロウレベルのとき1/2VDD、ハイレベルのとき3/2VDDが、レベルシフタLS101から出力される。そして、このレベルシフタLS101からの出力に応じて、図2のPMOSトランジスタMP101のオン、オフが制御される。なお、レベルシフタLS102も、クロック信号CLK2がロウレベルのとき1/2VDD、ハイレベルのとき3/2VDDを出力する。そして、このレベルシフタLS102からの出力に応じて、図2のPMOSトランジスタMP102のオン、オフが制御される。このように、PMOSトランジスタMP101、MP102のゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。よって、回路ユニット101で使用するトランジスタを全て低耐圧トランジスタとすることができる。

【0077】

ここで更に、昇圧回路100の初期状態を考える。昇圧回路100の初期状態では、コンデンサC101が充電されておらず、クロック信号CLK1がハイレベルであっても、ノードN101が昇圧されない。このため、ノードN101の電位が3/2VDDではなく、VDDである。よって、レベルシフタLS101の高電位側の電源電圧である電源端子VAの電位もVDDとなる。

【0078】

ここで、図21に示した電界緩和回路技術を用いた従来のレベルシフタLS10では高電位側の電源電圧がVDDの場合、PMOSトランジスタMP22もしくはMP21がオンしないため、出力端子OUT10の電位が不定となっていた。

【0079】

しかし、本実施の形態1のレベルシフタLS101では、電源端子VAの電位がVDDであっても、PMOSトランジスタMP112もしくはMP111のソース−ゲート間の電位差を1/2VDDとすることができ、PMOSトランジスタMP112もしくはMP111をオンさせることができる。よって、出力端子OUT110の電位が不定となることがなく、レベルシフタLS101が初期状態においても正常に動作する。このため、PMOSトランジスタMP101を確実にオフさせることができ、回路ユニット101の正常動作が可能となる。

【0080】

次に、レベルシフタLS103の動作を中心に回路ユニット102について説明する。なお、レベルシフタLS104の動作は、入力クロック信号がCLK2である以外は、レベルシフタLS103と同様なため説明は省略する。図7に、レベルシフタLS103の入力端子IN111に入力するクロック信号CLK1と、出力端子OUT111(及び反転出力端子OUT111B)、及び、ノードN121、N122、N131、N132、N141、N142の電位の関係をまとめた表を示す。

【0081】

図7の表に示すように、入力端子IN111に入力するクロック信号CLK1がロウレベル(接地電圧GND)のとき、出力端子OUT111、OUT111Bの電位がそれぞれVDD、2VDDとなる。また、ノードN121、N122の電位がそれぞれVDD−Vtn、1/2VDDとなる。ノードN131、N132の電位がそれぞれ3/2VDD、1/2VDDとなる。ノードN141、N142の電位がそれぞれ3/2VDD−Vtn、VDDとなる。

【0082】

逆に、入力端子IN111に入力するクロック信号CLK1がハイレベル(電源電圧VDD)のとき、出力端子OUT111、OUT111Bの電位がそれぞれ2VDD、VDDとなる。また、ノードN121、N122の電位がそれぞれ1/2VDD、VDD−Vtnとなる。ノードN131、N132の電位がそれぞれ1/2VDD、3/2VDDとなる。ノードN141、N142の電位がそれぞれVDD、3/2VDD−Vtnとなる。

【0083】

なお、レベルシフタLS104もクロック信号CLK2に応じて同様の動作を行う。このように、レベルシフタLS103、LS104の各トランジスタのゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。

【0084】

また、上述のようにクロック信号CLK1がロウレベルのとき3/2VDD、ハイレベルのとき2VDDが、レベルシフタLS103から出力される。そして、このレベルシフタLS103からの出力に応じて、図2のPMOSトランジスタMP103のオン、オフが制御される。なお、レベルシフタLS104も、クロック信号CLK2がロウレベルのとき3/2VDD、ハイレベルのとき2VDDを出力する。そして、このレベルシフタLS104からの出力に応じて、図2のPMOSトランジスタMP104のオン、オフが制御される。このように、PMOSトランジスタMP103、MP104のゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。よって、回路ユニット102で使用するトランジスタを全て低耐圧トランジスタとすることができる。

【0085】

以上、昇圧回路100では、使用するトランジスタを全て低耐圧トランジスタとしても、出力電圧VOUTを2×VDDとすることができる。また、図21に示した電界緩和回路技術を用いた従来のレベルシフタを用いた場合、動作開始時の初期状態でレベルシフタが不定な電位を出力するため、昇圧動作を行えなかった。しかし、本実施の形態1の昇圧回路100のレベルシフタLS101は、動作開始時の初期状態であって不定な電圧を出力しない。このため、昇圧回路100が正常に昇圧動作を開始することができる。

【0086】

発明の実施の形態2

【0087】

以下、本発明を適用した具体的な実施の形態2について、図面を参照しながら詳細に説明する。この実施の形態2は、本発明をフラッシュメモリ等の半導体記憶装置における負の昇圧回路に適用したものである。つまり、図1の負電圧生成昇圧回路NCHRGEが有する昇圧回路に適用する。

【0088】

図8に本実施の形態2にかかる負電圧生成昇圧回路NCHRGEが有する昇圧回路200の構成の一例を示す。

【0089】

図8に示すように、昇圧回路200は、NMOSトランジスタMN201、MN202、MN203、MN204と、レベルシフタLS201、LS202、LS203、LS204と、コンデンサC201、C202と、インバータ回路IV201、IV202、IV203、IV204とを有する。

【0090】

NMOSトランジスタMN201(第1のトランジスタ)は、ソースもしくはドレインの一端が接地電圧GNDを供給する接地端子GND(第2の電源端子)、ソースもしくはドレインの他端がノードN201(第1のノード)に接続される。また、NMOSトランジスタMN201は、ゲートにレベルシフタLS201の出力信号が入力される。NMOSトランジスタMN202(第2のトランジスタ)は、ソースもしくはドレインの一端がノードN201、ソースもしくはドレインの他端がノードN202に接続される。また、NMOSトランジスタMN202(第2のノード)は、ゲートにレベルシフタLS202の出力信号が入力される。

【0091】

レベルシフタLS201(第1の制御信号生成回路)は、クロック信号CLK1を入力し、出力信号(第1の制御信号)をNMOSトランジスタMN201のゲートへ出力する。レベルシフタLS201の電源電圧は、高電位側がHVDD端子、低電位側がノードN201から供給される。

【0092】

レベルシフタLS202(第2の制御信号生成回路)は、クロック信号CLK2を入力し、出力信号(第2の制御信号)をNMOSトランジスタMN202のゲートへ出力する。レベルシフタLS202の電源電圧は、高電位側がHVDD端子、低電位側がノードN202から供給される。

【0093】

インバータ回路IV201は、クロック信号CLK3を入力し、その反転信号をインバータ回路IV202の入力へ出力する。インバータ回路IV202は、図8に示すように、PMOSトランジスタMP205と、NMOSトランジスタMN205とを有する。PMOSトランジスタMP205、NMOSトランジスタMN205は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP205、NMOSトランジスタMN205の共通ノードがインバータ回路IV202の出力端となる。また、PMOSトランジスタMP205、NMOSトランジスタMN205のゲートには、インバータ回路IV201の出力信号が入力される。このため、インバータ回路IV202からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0094】

コンデンサC201(第2の容量素子)は、一端がインバータ回路IV202の出力端、他端がノードN201に接続される。

【0095】

NMOSトランジスタMN203(第7のトランジスタ)は、ソースもしくはドレインの一端がノードN202、ソースもしくはドレインの他端がノードN203(第5のノード)に接続される。また、NMOSトランジスタMN203は、ゲートにレベルシフタLS203の出力信号が入力される。NMOSトランジスタMN204(第8のトランジスタ)は、ソースもしくはドレインの一端がノードN203、ソースもしくはドレインの他端が出力端子OUT201(第6のノード)に接続される。また、NMOSトランジスタMN204は、ゲートにレベルシフタLS204の出力信号が入力される。

【0096】

レベルシフタLS203は、クロック信号CLK1を入力し、出力信号をNMOSトランジスタMN203のゲートへ出力する。レベルシフタLS203の詳細な構成は後述するが、高電位側の電源電圧が接地端子GND、低電位側がノードN202及びN203から供給される。レベルシフタLS204は、クロック信号CLK2を入力し、出力信号をNMOSトランジスタMN204のゲートへ出力する。レベルシフタLS204の詳細な構成は後述するが、高電位側の電源電圧が接地端子GND、低電位側がノードN203及び出力端子OUT201から供給される。

【0097】

インバータ回路IV203は、クロック信号CLK3を入力し、その反転信号をインバータ回路IV204の入力へ出力する。インバータ回路IV204は、図8に示すように、PMOSトランジスタMP206と、NMOSトランジスタMN206とを有する。PMOSトランジスタMP206、NMOSトランジスタMN206は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP206、NMOSトランジスタMN206の共通ノードがインバータ回路IV204の出力端となる。また、PMOSトランジスタMP206、NMOSトランジスタMN206のゲートには、インバータ回路IV203の出力信号が入力される。このため、インバータ回路IV204からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0098】

コンデンサC202は、一端がインバータ回路IV204の出力端、他端がノードN203に接続される。

【0099】

なお、上記PMOSトランジスタ、NMOSトランジスタは、ゲート酸化膜の耐圧が電源電圧VDD以下の低耐圧トランジスタであるものとする。また、PMOSトランジスタのスレッショルド電圧Vtp及びNMOSトランジスタのスレッショルド電圧Vtnは、それぞれ1/2VDD以下であるものとする。

【0100】

図9に昇圧回路200の動作を説明するタイミングチャートを示す。なお、本説明では、図9の回路ユニット201と、回路ユニット202に分けて動作の説明を行う。回路ユニット201の動作を時刻t1〜t6、回路ユニット202の動作を時刻t6〜t11に説明する。

【0101】

まず、回路ユニット201の動作は、図10に示すように、時刻t1〜t2の期間、クロック信号CLK1はハイレベルとなり、NMOSトランジスタMN201がオン状態となる。よって、接地端子VDDとノードN201が電気的に接続され、ノードN201の電位が接地電圧GNDとなる。一方、この期間において、クロック信号CLK3はハイレベルであり、インバータ回路IV202から出力される電位は1/2VDDである。このため、コンデンサC201の一端の電位は接地電圧GNDとなり、コンデンサC101は、電位差1/2VDDで充電される。

【0102】

時刻t2で、クロック信号CLK1はロウレベルに立ち下がる。このため、接地電圧GNDとノードN201が電気的に遮断される。また、クロック信号CLK2によりNMOSトランジスタMN202もオフ状態のため、ノードN201はハイインピーダンスとなる。但し、コンデンサC201が充電されているため、ノードN101の電位は接地電圧GNDで保持される。

【0103】

時刻t3で、クロック信号CLK3がロウレベルに立ち下がる。このため、インバータ回路IV202から出力される電位が接地電圧GNDとなる。よって、コンデンサC201の一端の電位が接地電圧GNDとなり、コンデンサC201の他端の電位が1/2VDD分降下する。よって、ノードN201の電位が−1/2VDDとなる。

【0104】

時刻t4〜t5の期間、クロック信号CLK2はハイレベルとなり、NMOSトランジスタMN202がオン状態となる。よって、ノードN201とノードN202が電気的に接続され、ノードN202の電位が−1/2VDDとなる。

【0105】

時刻t5で、クロック信号CLK2はロウレベルに立ち下がる。このため、ノードN201とノードN202が電気的に遮断される。

【0106】

次に、回路ユニット202の動作は、図10に示すように、時刻6〜t7の期間、クロック信号CLK1はロウレベルとなり、NMOSトランジスタMN203がオン状態となる。よって、ノードN202とノードN203が電気的に接続され、ノードN203の電位が−1/2VDDとなる。一方、この期間において、クロック信号CLK3はハイレベルであり、インバータ回路IV204から出力される電位は1/2VDDである。このため、コンデンサC202の一端の電位は−1/2VDDとなり、コンデンサC202は、電位差VDDで充電される。

【0107】

時刻t7で、クロック信号CLK1はロウレベルに立ち下がる。このため、ノードN202とノードN203が電気的に遮断される。また、クロック信号CLK2によりNMOSトランジスタMN204もオフ状態のため、ノードN203はハイインピーダンスとなる。但し、コンデンサC202が充電されているため、ノードN203の電位は−1/2VDDで保持される。

【0108】

時刻t8で、クロック信号CLK3がロウレベルに立ち下がる。このため、インバータ回路IV202から出力される電位が接地電圧GNDとなる。よって、コンデンサC202の一端に接地電圧GNDの電位が印加され、コンデンサC102の他端の電位が1/2VDD分降下する。よって、ノードN203の電位が−VDD(=−1/2VDD−1/2VDD)となる。

【0109】

時刻t9〜t10の期間、クロック信号CLK2はハイレベルとなり、NMOSトランジスタMN204がオン状態となる。よって、ノードN203と出力端子OUT201が電気的に接続され、出力端子の電位が−VDDとなる。

【0110】

時刻t11で、クロック信号CLK2はロウレベルに立ち下がる。このため、ノードN203と出力端子OUT201が電気的に遮断される。

【0111】

ここで、時刻t3〜t6、t8〜t11の期間、ノードN201、N203の電位が、それぞれ接地電圧GND、ノードN202の電位−1/2VDDより低くなる。このため、接地端子GND、ノードN202から電流の逆流を防ぐため、時刻t2〜t6、t7〜t11の期間、NMOSトランジスタMN201、MN203をオフさせる必要がある。このため、回路ユニット201では、図10に示すような構成のレベルシフタLS201、LS202、回路ユニット202では、図11に示すような構成のレベルシフタLS203、LS204を用いる。

【0112】

図10にレベルシフタLS201の構成を示す。なお、レベルシフタLS202は、レベルシフタLS201とほぼ同様の構成のため、特に断らない限り説明は省略する。図10に示すように、レベルシフタLS201は、PMOSトランジスタMP211、MP212と、NMOSトランジスタMN211、MN212と、入力端子IN210と、出力端子OUT210、OUT210Bと、インバータ回路IV210、IV211、IV212とを有する。この入力端子IN210にクロック信号CLK1が入力される。また、出力端子OUT210からの出力信号が図2のNMOSトランジスタMN201のゲートに出力される。

【0113】

なお、レベルシフタLS202では、入力端子IN210にクロック信号CLK2が入力される。また、出力端子OUT210からの出力信号が図2のNMOSトランジスタMN202のゲートに出力される。

【0114】

PMOSトランジスタMP211(第3のトランジスタ)は、ソースがHVDD電源端子(第3の電圧供給端子)、ドレインが出力端子OUT210B(第3のノード)、ゲートがノードN211に接続される。PMOSトランジスタMP212(第4のトランジスタ)は、ソースがHVDD電源端子、ドレインが出力端子OUT210(第4のノード)、ゲートがノードN212に接続される。

【0115】

NMOSトランジスタMN211(第5のトランジスタ)は、ドレインが出力端子OUT210B、ソースが電源端子VD、ゲートが出力端子OUT210に接続される。NMOSトランジスタMN212(第6のトランジスタ)は、ドレインが出力端子OUT210、ソースが電源端子VD、ゲートが出力端子OUT210Bに接続される。ここで、電源端子VDは、図8のノードN201と接続されている。なお、レベルシフタLS202では、この電源端子VDは図8のノードN202と接続されることになる。

【0116】

インバータ回路IV210は、入力端が入力端子IN210、出力端がインバータ回路IV211の入力端に接続される。インバータ回路IV211は、入力端がインバータ回路IV210の出力端、出力端がノードN211に接続される。インバータ回路IV212は、入力端がノードN211、出力端がノードN212に接続される。

【0117】

インバータ回路IV211(第1のインバータ回路)は、図10に示すように、PMOSトランジスタMP213と、NMOSトランジスタMN213とを有する。PMOSトランジスタMP213、NMOSトランジスタMN213は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP213、NMOSトランジスタMN213の共通ノードがインバータ回路IV211の出力端(ノードN211)となる。また、PMOSトランジスタMP213、NMOSトランジスタMN213のゲートには、インバータ回路IV210の出力信号が入力される。このため、インバータ回路IV211からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0118】

また、インバータ回路IV212(第2のインバータ回路)は、図10に示すように、PMOSトランジスタMP214と、NMOSトランジスタMN214とを有する。PMOSトランジスタMP214、NMOSトランジスタMN214は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP214、NMOSトランジスタMN214の共通ノードがインバータ回路IV212の出力端(ノードN212)となる。また、PMOSトランジスタMP214、NMOSトランジスタMN214のゲートには、インバータ回路IV211の出力信号が入力される。このため、インバータ回路IV212からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0119】

次に、図11にレベルシフタLS203の構成を示す。なお、レベルシフタLS204は、レベルシフタLS203とほぼ同様の構成のため、特に断らない限り説明は省略する。図11に示すように、レベルシフタLS203は、PMOSトランジスタMP221、MP222、MP231、MP232、MP241、MP242と、NMOSトランジスタMN221、MN222、MN231、MN232と、入力端子IN211と、出力端子OUT211、OUT211Bと、インバータ回路IV220、IV221、IV222とを有する。この入力端子IN211にクロック信号CLK1が入力される。また、出力端子OUT211からの出力信号が図8のNMOSトランジスタMN203のゲートに出力される。

【0120】

なお、レベルシフタLS204では、入力端子IN211にクロック信号CLK2が入力される。また、出力端子OUT211からの出力信号が図8のNMOSトランジスタMN204のゲートに出力される。

【0121】

PMOSトランジスタMP221(第9のトランジスタ)は、ソースがHVDD端子、ドレインがノードN231(第7のノード)、ゲートがノードN221に接続される。PMOSトランジスタMP222(第10のトランジスタ)は、ソースがHVDD端子、ドレインがノードN232(第8のノード)、ゲートがノードN222に接続される。

【0122】

NMOSトランジスタMN221(第15のトランジスタ)は、ドレインがノードN231、ソースが電源端子VD(第4の電圧供給端子)、ゲートがノードN232に接続される。NMOSトランジスタMN222(第16のトランジスタ)は、ドレインがノードN232、ソースが電源端子VD、ゲートがノードN231に接続される。ここで、電源端子VDは、図8のノードN202と接続されている。なお、レベルシフタLS204では、この電源端子VDは図8のノードN203と接続されることになる。

【0123】

インバータ回路IV220は、入力端が入力端子IN211、出力端がインバータ回路IV221の入力端に接続される。インバータ回路IV221は、入力端がインバータ回路IV220の出力端、出力端がノードN221に接続される。インバータ回路IV222は、入力端がノードN221、出力端がノードN222に接続される。

【0124】

インバータ回路IV221(第3のインバータ回路)は、図11に示すように、PMOSトランジスタMP223と、NMOSトランジスタMN223とを有する。PMOSトランジスタMP223、NMOSトランジスタMN223は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP223、NMOSトランジスタMN223の共通ノードがインバータ回路IV221の出力端(ノードN221)となる。また、PMOSトランジスタMP223、NMOSトランジスタMN223のゲートには、インバータ回路IV220の出力信号が入力される。このため、インバータ回路IV221からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0125】

また、インバータ回路IV222(第4のインバータ回路)は、図11に示すように、PMOSトランジスタMP224と、NMOSトランジスタMN224とを有する。PMOSトランジスタMP224、NMOSトランジスタMN224は、HVDD電源端子と接地端子GND間に直列に接続される。PMOSトランジスタMP224、NMOSトランジスタMN224の共通ノードがインバータ回路IV222の出力端(ノードN222)となる。また、PMOSトランジスタMP224、NMOSトランジスタMN224のゲートには、インバータ回路IV221の出力信号が入力される。このため、インバータ回路IV222からは、クロック信号CLK3に応じた、ハイレベルの電位が1/2VDD、ロウレベルの電位が接地電圧GNDの出力信号が出力される。

【0126】

PMOSトランジスタMP231(第11のトランジスタ)は、ソースが接地端子GND(第5の電圧供給端子)、ドレインがノードN241(第9のノード)、ゲートがノードN232に接続される。PMOSトランジスタMP232(第12のトランジスタ)は、ソースが接地端子GND、ドレインがノードN242(第10のノード)、ゲートがノードN231に接続される。PMOSトランジスタMP241(第13のトランジスタ)は、ソースがノードN241、ドレインが出力端子OUT211B(第11のノード)、ゲートが電源端子VDに接続される。PMOSトランジスタMP242(第14のトランジスタ)は、ソースがノードN242、ドレインが出力端子OUT211(第12のノード)、ゲートが電源端子VDに接続される。

【0127】

NMOSトランジスタMN231(第17のトランジスタ)は、ドレインが出力端子OUT211B、ソースが電源端子VE(第6の電圧供給端子)、ゲートが出力端子OUT211に接続される。NMOSトランジスタMN232(第18のトランジスタ)は、ドレインが出力端子OUT211、ソースが電源端子VE、ゲートが出力端子OUT211Bに接続される。ここで、電源端子VEは、図8のノードN203と接続されている。なお、レベルシフタLS204では、この電源端子VCは図8の出力端子OUT201と接続されることになる。

【0128】

なお、上記レベルシフタLS201、LS202、LS203、LS204を構成する全てのPMOSトランジスタ、NMOSトランジスタは、ゲート酸化膜の耐圧が電源電圧VDD以下の低耐圧トランジスタであるものとする。また、PMOSトランジスタのスレッショルド電圧Vtp及びNMOSトランジスタのスレッショルド電圧Vtnは、それぞれ1/2VDD以下であるものとする。また、図11からもわかるようにレベルシフタLS203(及びLS204)は、ノードN231、N232で接続される2つのレベルシフタで構成されているとみなすこともできる。そして、この2つのレベルシフタにおいても高電側位電源電圧と低電位側の電位差がVDD以内となっている。

【0129】

ここで、レベルシフタLS201の動作を中心に回路ユニット201について説明する。なお、レベルシフタLS202の動作は、入力クロック信号がCLK2である以外は、レベルシフタLS201と同様なため説明は省略する。図12に、レベルシフタLS201の入力端子IN210に入力するクロック信号CLK1と、出力端子OUT210(及び反転出力端子OUT210B)、及び、ノードN211、N212の電位の関係をまとめた表を示す。

【0130】

図12の表に示すように、入力端子IN210に入力するクロック信号CLK1がロウレベル(接地電圧GND)のとき、出力端子OUT210、OUT210Bの電位がそれぞれ−1/2VDD、1/2VDDとなる。また、ノードN211、N212の電位がそれぞれ接地電圧GND、1/2VDDとなる。逆に、入力端子IN210に入力するクロック信号CLK1がハイレベル(電源電圧VDD)のとき、出力端子OUT210、OUT210Bの電位がそれぞれ1/2VDD、−1/2VDDとなる。また、ノードN211、N212の電位がそれぞれ1/2VDD、接地電圧GNDとなる。

【0131】

なお、レベルシフタLS202もクロック信号CLK2に応じて同様の動作を行う。このように、レベルシフタLS201、LS202の各トランジスタのゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。

【0132】

また、上述のようにクロック信号CLK1がロウレベルのとき−1/2VDD、ハイレベルのとき1/2VDDが、レベルシフタLS201から出力される。そして、このレベルシフタLS201からの出力に応じて、図8のNMOSトランジスタMN201のオン、オフが制御される。なお、レベルシフタLS202も、クロック信号CLK2がロウレベルのとき−1/2VDD、ハイレベルのとき1/2VDDを出力する。そして、このレベルシフタLS102からの出力に応じて、図8のNMOSトランジスタMN202のオン、オフが制御される。このように、NMOSトランジスタMN201、MN202のゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。よって、回路ユニット201で使用するトランジスタを全て低耐圧トランジスタとすることができる。

【0133】

ここで更に、昇圧回路200の初期状態を考える。昇圧回路200の初期状態では、コンデンサC201が充電されておらず、クロック信号CLK3がロウレベルであっても、ノードN201が負電位側に昇圧されない。このため、ノードN201の電位が−1/2VDDではなく、GNDである。よって、レベルシフタLS201の低電位側の電源電圧である電源端子VDの電位もGNDとなる。

【0134】

ここで、図23に示した電界緩和回路技術を用いた従来のレベルシフタLS30では低電位側の電源電圧がGNDの場合、NMOSトランジスタMN22もしくはMN21がオンしないため、出力端子OUT10の電位が不定となっていた。

【0135】

しかし、本実施の形態2のレベルシフタLS201では、電源端子VDの電位がGNDであっても、NMOSトランジスタMP212もしくはMP211のソース−ゲート間の電位差を1/2VDDとすることができ、NMOSトランジスタMN212もしくはMN211をオンさせることができる。よって、出力端子OUT210の電位が不定となることがなく、レベルシフタLS201が初期状態においても正常に動作する。このため、NMOSトランジスタMN201を確実にオフさせることができ、回路ユニット201の正常動作が可能となる。

【0136】

次に、レベルシフタLS203の動作を中心に回路ユニット202について説明する。なお、レベルシフタLS204の動作は、入力クロック信号がCLK2である以外は、レベルシフタLS203と同様なため説明は省略する。図13に、レベルシフタLS203の入力端子IN211に入力するクロック信号CLK1と、出力端子OUT211(及び反転出力端子OUT211B)、及び、ノードN221、N222、N231、N232、N241、N242の電位の関係をまとめた表を示す。但し、「Vtp」はPMOSトランジスタのスレッショルド電圧である。

【0137】

図13の表に示すように、入力端子IN211に入力するクロック信号CLK1がロウレベル(接地電圧GND)のとき、出力端子OUT211、OUT211Bの電位がそれぞれ−VDD、GNDとなる。また、ノードN221、N222の電位がそれぞれGND、1/2VDDとなる。ノードN231、N232の電位がそれぞれ1/2VDD、−1/2VDDとなる。ノードN241、N242の電位がそれぞれGND、−VDD+Vtpとなる。

【0138】

逆に、入力端子IN211に入力するクロック信号CLK1がハイレベル(電源電圧VDD)のとき、出力端子OUT211、OUT211Bの電位がそれぞれGND、−VDDとなる。また、ノードN221、N222の電位がそれぞれ1/2VDD、GNDとなる。ノードN231、N232の電位がそれぞれ−1/2VDD、1/2VDDとなる。ノードN241、N242の電位がそれぞれ−VDD+Vtp、GNDとなる。

【0139】

なお、レベルシフタLS204もクロック信号CLK2に応じて同様の動作を行う。このように、レベルシフタLS203、LS204の各トランジスタのゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。

【0140】

また、上述のようにクロック信号CLK1がロウレベルのとき−VDD、ハイレベルのときGNDが、レベルシフタLS203から出力される。そして、このレベルシフタLS203からの出力に応じて、図8のNMOSトランジスタMN203のオン、オフが制御される。なお、レベルシフタLS204も、クロック信号CLK2がロウレベルのとき−VDD、ハイレベルのときGNDが、レベルシフタLS203から出力される。そして、このレベルシフタLS204からの出力に応じて、図8のNMOSトランジスタMN204のオン、オフが制御される。このように、NMOSトランジスタMN203、MN204のゲート−ドレイン間もしくはゲート−ソース間の電位差を、電源電圧VDD以内に収めることができる。よって、回路ユニット202で使用するトランジスタを全て低耐圧トランジスタとすることができる。

【0141】

以上、昇圧回路200では、使用するトランジスタを全て低耐圧トランジスタとしても、出力電圧VOUTを−VDDとすることができる。また、図23に示した電界緩和回路技術を用いた従来のレベルシフタを用いた場合、動作開始時の初期状態でレベルシフタが不定な電位を出力するため、負電位側の昇圧動作を行えなかった。しかし、本実施の形態2の昇圧回路200のレベルシフタLS201は、動作開始時の初期状態であって不定な電圧を出力しない。このため、昇圧回路200が正常に昇圧動作を開始することができる。

【0142】

なお、本発明は上記実施の形態に限られたものでなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、昇圧回路100または200を更に多段構成にして、出力電圧を2VDDより高電位側、または−VDDより負電位側に昇圧してもよい。

【0143】

また、実施の形態1、2では、各コンデンサの一端に印加されるインバータ回路が出力する出力信号の振幅レベルを1/2VDDとしている。しかし、この振幅レベルを、1/2VDD以下としてもよい。例えば、実施の形態1で、回路ユニット101のインバータ回路IV102のHVDD端子の電位を1/2VDDから電位ΔV1分低くする。但し、この場合、コンデンサC101の他端に接続されるノードの電位の昇圧レベルも、1/2VDDよりΔV1分低下することになる。よって、レベルシフタLS101、LS102のHVDD端子の電位も同様に1/2VDDからΔV1低くする。また、NMOSトランジスタMN121、122のゲートに印加される電位、および、インバータ回路IV110の高電位側の電源電圧を、そのHVDD端子の電位の2倍の電位とする。

【符号の説明】

【0144】

100、200 昇圧回路

MP101〜MP104、MP111、MP112、MP121、MP122、MP131、MP132、MP211、MP212、MP221、MP222、MP231、MP232、MP241、MP242 PMOSトランジスタ

MN201〜MN204、MN111、MN112、MN121、MN122、MN131、MN132、MN141、MN142、MN151、MN152、MN161、MN162、MN211、MN212、MN221、MN222、MN231、MN232 NMOSトランジスタ

LS101〜LS104、LS201〜LS204 レベルシフタ

IV101〜IV104、IV110、IV111、IV201〜IV204、IV210、IV211、IV212、IV220、IV221、IV222 インバータ回路

C101、C102、C201、C202 コンデンサ

【特許請求の範囲】

【請求項1】

第1の電源電圧を、正側または負側の所定の電圧に昇圧する昇圧回路であって、

第1のノードに接続される第1のトランジスタと、

一端が前記第1のノードに接続され、前記第1のトランジスタの活性化時に前記第1のノードの電圧で充電される第1の容量素子と、

前記第1のトランジスタの制御端子に第1のクロック信号に応じた第1の制御信号を出力する第1の制御信号生成回路を有し、

前記第1の容量素子は、前記第1のトランジスタの非活性化時に、他端に印加される前記第1の電源電圧の1/2以下の電圧により前記第1のノードの電位を、正側または負側の第1の電圧に昇圧し、

前記第1の制御信号生成回路は、

前記第1のトランジスタの非活性化時の前記第1の制御信号の電位を、前記第1の電位とし、

前記第1のトランジスタの活性化時の前記第1の制御信号の電位を、前記第1の電位との差が前記第1の電源電圧以内となる電位とする

昇圧回路。

【請求項2】

前記第1のノードと、第2のノードとの間に接続される第2のトランジスタと、

前記第2のトランジスタの制御端子に第2のクロック信号に応じた第2の制御信号を出力し、前記第1のトランジスタが非活性化時に前記第2のトランジスタを活性化させる第2の制御信号生成回路を有し、

前記第2の制御信号生成回路は、

前記第2のトランジスタの非活性化時の前記第2の制御信号の電位を、前記第2のノードの第2の電位とし、

前記第2のトランジスタの活性化時の前記第2の制御信号の電位を、前記第2の電位との差が前記第1の電源電圧以内となる電位とする

請求項1に記載の昇圧回路。

【請求項3】

前記第1、第2のトランジスタは、第1導電型であり、前記第1のトランジスタが前記第1の電源電圧を供給する第1の電源端子と前記第1のノードとの間に接続される

請求項1または請求項2に記載の昇圧回路。

【請求項4】

前記第1の制御信号生成回路は、第1導電型の第3、第4のトランジスタと、第2導電型の第5〜第8のトランジスタと、第1〜第3の電圧供給端子とを有し、

前記第1の電圧供給端子は、前記第1のノードの電位を供給し、

前記第2の電圧供給端子は、前記第1の電源電圧を供給し、

前記第3の電圧供給端子は、前記第1の電源電圧の1/2の電位を供給し、

前記第3のトランジスタは、前記第1の電圧供給端子と第3のノードとの間に接続され、制御端子が第4のノードと接続され、

前記第4のトランジスタは、前記第1の電圧供給端子と前記第4のノードとの間に接続され、制御端子が前記第3のノードと接続され、

前記第5のトランジスタは、前記第3のノードと第5のノードとの間に接続され、制御端子が前記第2の電圧供給端子と接続され、

前記第6のトランジスタは、前記第4のノードと第6のノードとの間に接続され、制御端子が前記第2の電圧供給端子と接続され、

前記第7のトランジスタは、前記第5のノードと前記第3の電圧供給端子との間に接続され、制御端子に前記第1の電源電圧の振幅レベルを有する前記第1のクロック信号を入力し、

前記第8のトランジスタは、前記第6のノードと前記第3の電圧供給端子との間に接続され、制御端子に前記第1のクロック信号の反転信号を入力し、

前記第4のノードが当該第1の制御信号生成回路の出力端である

請求項3に記載の昇圧回路。

【請求項5】

前記第2の制御信号生成回路は、

前記第1の電圧供給端子は、前記第2のノードの電位を供給し、

前記第7のトランジスタの制御端子に前記第1の電源電圧の振幅レベルを有する前記第2のクロック信号を入力し、

前記第8のトランジスタの制御端子に前記第2のクロック信号の反転信号を入力し、

前記第4のノードが当該第2の制御信号生成回路の出力端である以外は、前記第1の制御信号生成回路と同様の回路構成を備える

請求項4に記載の昇圧回路。

【請求項6】

前記第2のノードと、第7のノードとの間に接続される第1導電型の第9のトランジスタと

一端が前記第7のノードに接続され、前記第9のトランジスタの活性化時に前記第7のノードの電圧で充電される第2の容量素子と、

前記第9のトランジスタの制御端子に前記第1のクロック信号に応じた第3の制御信号を出力する第3の制御信号生成回路を有し、

前記第2の容量素子は、前記第9のトランジスタの非活性化時に、他端に印加される前記第1の電源電圧の1/2以下の電圧により前記第7のノードの電位を、正側の第3の電圧に昇圧し、

前記第3の制御信号生成回路は、

前記第9のトランジスタの非活性化時の前記第3の制御信号の電位を、前記第3の電位とし、

前記第9のトランジスタの活性化時の前記第3の制御信号の電位を、前記第3の電位との差が前記第1の電源電圧以内となる電位とする

請求項4もしくは請求項5に記載の昇圧回路。

【請求項7】

前記第7のノードと、第8のノードとの間に接続される第1導電型の第10のトランジスタと、

前記第10のトランジスタの制御端子に第2のクロック信号に応じた第4の制御信号を出力し、前記第9のトランジスタが非活性化時に前記第10のトランジスタを活性化させる第4の制御信号生成回路を有し、

前記第4の制御信号生成回路は、

前記第10のトランジスタの非活性化時の前記第4の制御信号の電位を、前記第8のノードの第4の電位とし、

前記第10のトランジスタの活性化時の前記第4の制御信号の電位を、前記第4の電位との差が前記第1の電源電圧以内となる電位とする

請求項6に記載の昇圧回路。

【請求項8】

前記第3の制御信号生成回路は、第1導電型の第11〜第14のトランジスタと、第2導電型の第15〜第22のトランジスタと、第4〜第7の電圧供給端子とを有し、

前記第4の電圧供給端子は、前記第2のノードの電位を供給し、

前記第5の電圧供給端子は、前記第1の電源電圧を供給し、

前記第6の電圧供給端子は、前記第1の電源電圧の1/2の電位を供給し、

前記第7の電圧供給端子は、前記第7のノードの電位を供給し、

前記第11のトランジスタは、前記第4の電圧供給端子と第9のノードとの間に接続され、制御端子が第10のノードと接続され、

前記第12のトランジスタは、前記第4の電圧供給端子と前記第10のノードとの間に接続され、制御端子が前記第9のノードと接続され、

前記第15のトランジスタは、前記第9のノードと第11のノードとの間に接続され、制御端子が前記第5の電圧供給端子と接続され、

前記第16のトランジスタは、前記第10のノードと第12のノードとの間に接続され、制御端子が前記第5の電圧供給端子と接続され、

前記第17のトランジスタは、前記第11のノードと前記第6の電圧供給端子との間に接続され、制御端子に前記第1のクロック信号を入力し、

前記第18のトランジスタは、前記第12のノードと前記第6の電圧供給端子との間に接続され、制御端子に前記第1のクロック信号の反転信号を入力し、

前記第13のトランジスタは、前記第7の電圧供給端子と第13のノードとの間に接続され、制御端子が第14のノードと接続され、

前記第14のトランジスタは、前記第7の電圧供給端子と前記第14のノードとの間に接続され、制御端子が前記第13のノードと接続され、

前記第19のトランジスタは、前記第13のノードと第15のノードとの間に接続され、制御端子が前記第4の電圧供給端子と接続され、

前記第20のトランジスタは、前記第14のノードと第16のノードとの間に接続され、制御端子が前記第4の電圧供給端子と接続され、

前記第21のトランジスタは、前記第15のノードと前記第5の電圧供給端子との間に接続され、制御端子が前記第10のノードと接続され、

前記第22のトランジスタは、前記第16のノードと前記第5の電圧供給端子との間に接続され、制御端子が前記第9のノードと接続され、

前記第14のノードが当該第3の制御信号生成回路の出力端である

請求項7に記載の昇圧回路。

【請求項9】

前記第4の制御信号生成回路は、

前記第4の電圧供給端子は、前記第2のノードの電位を供給し、

前記第7の電圧供給端子は、前記第7のノードの電位を供給し、

前記第17のトランジスタの制御端子に前記第2のクロック信号を入力し、

前記第18のトランジスタの制御端子に前記第2のクロック信号の反転信号を入力し、

前記第14のノードが当該第4の制御信号生成回路の出力端である以外は、前記第3の制御信号生成回路と同様の回路構成を備える

請求項8に記載の昇圧回路。

【請求項10】

前記第1、第2のトランジスタは、第2の導電性を有し、前記第1のトランジスタが、接地電圧を供給する第2の電源端子と前記第1のノードとの間に接続される

請求項1または請求項2に記載の昇圧回路。

【請求項11】

前記第1の制御信号生成回路は、第1導電型の第3、第4のトランジスタと、第2導電型の第5、第6のトランジスタと、第1、第2のインバータ回路と、第1、第2の電圧供給端子とを有し、

前記第1の電圧供給端子は、前記第1の電源電圧の1/2の電位を供給し、

前記第2の電圧供給端子は、前記第1のノードの電位を供給し、

前記第1のインバータ回路は、高電位側の電源電圧を前記第1の電圧供給端子の電位、低電圧側の電源電圧を接地電圧とし、入力に前記第1のクロック信号に応じた信号が入力され、

前記第2のインバータ回路は、高電位側の電源電圧を前記第1の電圧供給端子の電位、低電圧側の電源電圧を接地電圧とし、入力に前記第1のインバータ回路の出力が入力され、

前記第3のトランジスタは、前記第1の電圧供給端子と第3のノードとの間に接続され、制御端子に前記第1のインバータ回路の出力を入力し、

前記第4のトランジスタは、前記第1の電圧供給端子と第4のノードとの間に接続され、制御端子に前記第2のインバータ回路の出力を入力し、

前記第5のトランジスタは、前記第3のノードと前記第2の電圧供給端子との間に接続され、制御端子が前記第4のノードに接続され、

前記第6のトランジスタは、前記第4のノードと前記第2の電圧供給端子との間に接続され、制御端子が前記第3のノードに接続され、

前記第4のノードが当該第1の制御信号生成回路の出力端である

請求項10に記載の昇圧回路。

【請求項12】

前記第2の制御信号生成回路は、

前記第2の電圧供給端子は、前記第2のノードの電位を供給し、

前記第1のインバータ回路は、入力に前記第2のクロック信号に応じた信号が入力され、

前記第4のノードが当該第2の制御信号生成回路の出力端である以外は、前記第1の制御信号生成回路と同様の回路構成を備える

請求項11に記載の昇圧回路。

【請求項13】

前記第2のノードと、第5のノードとの間に接続される第2導電型の第7のトランジスタと

一端が前記第5のノードに接続され、前記第7のトランジスタの活性化時に前記第5のノードの電圧で充電される第2の容量素子と、

前記第7のトランジスタの制御端子に前記第1のクロック信号に応じた第3の制御信号を出力する第3の制御信号生成回路を有し、

前記第2の容量素子は、前記第7のトランジスタの非活性化時に、他端に印加される前記第1の電源電圧の1/2以下の電圧により前記第5のノードの電位を、負側の第3の電圧に昇圧し、

前記第3の制御信号生成回路は、

前記第7のトランジスタの非活性化時の前記第3の制御信号の電位を、前記第3の電位とし、

前記第7のトランジスタの活性化時の前記第3の制御信号の電位を、前記第3の電位との差が前記第1の電源電圧以内となる電位とする

請求項11もしくは請求項12に記載の昇圧回路。

【請求項14】

前記第5のノードと、第6のノードとの間に接続される第2導電型の第8のトランジスタと、

前記第8のトランジスタの制御端子に第2のクロック信号に応じた第4の制御信号を出力し、前記第7のトランジスタが非活性化時に前記第8のトランジスタを活性化させる第4の制御信号生成回路を有し、

前記第4の制御信号生成回路は、

前記第8のトランジスタの非活性化時の前記第4の制御信号の電位を、前記第6のノードの第4の電位とし、

前記第8のトランジスタの活性化時の前記第4の制御信号の電位を、前記第4の電位との差が前記第1の電源電圧以内となる電位とする

請求項13に記載の昇圧回路。

【請求項15】

前記第3の制御信号生成回路は、第1導電型の第9〜第14のトランジスタと、第2導電型の第15〜第18のトランジスタと、第3、第4のインバータ回路と、第3〜第6の電圧供給端子とを有し、

前記第3の電圧供給端子は、前記第1の電源電圧の1/2の電位を供給し、

前記第4の電圧供給端子は、前記第2のノードの電位を供給し、

前記第5の電圧供給端子は、接地電圧を供給し、

前記第6の電圧供給端子は、前記第5のノードの電位を供給し、

前記第3のインバータ回路は、高電位側の電源電圧を前記第1の電圧供給端子の電位、低電圧側の電源電圧を接地電圧とし、入力に前記第2のクロック信号に応じた信号が入力され、

前記第4のインバータ回路は、高電位側の電源電圧を前記第1の電圧供給端子の電位、低電圧側の電源電圧を接地電圧とし、入力に前記第3のインバータ回路の出力が入力され、

前記第9のトランジスタは、前記第3の電圧供給端子と第7のノードとの間に接続され、制御端子に前記第3のインバータ回路の出力を入力し、

前記第10のトランジスタは、前記第3の電圧供給端子と第8のノードとの間に接続され、制御端子に前記第4のインバータ回路の出力を入力し、

前記第15のトランジスタは、前記第7のノードと前記第4の電圧供給端子との間に接続され、制御端子が第8のノードと接続され、

前記第16のトランジスタは、前記第8のノードと前記第4の電圧供給端子との間に接続され、制御端子が第7のノードと接続され、

前記第11のトランジスタは、前記第5の電圧供給端子と第9のノードとの間に接続され、制御端子が前記第8のノードと接続され、

前記第12のトランジスタは、前記第5の電圧供給端子と第10のノードとの間に接続され、制御端子が前記第7のノードと接続され、

前記第13のトランジスタは、前記第9のノードと第11のノードとの間に接続され、制御端子が前記第4の電圧供給端子と接続され、

前記第14のトランジスタは、前記第10のノードと第12のノードとの間に接続され、制御端子が前記第4

の電圧供給端子と接続され、

前記第17のトランジスタは、前記第11のノードと前記第6の電圧供給端子との間に接続され、制御端子が前記第12のノードと接続され、

前記第18のトランジスタは、前記第12のノードと前記第6の電圧供給端子との間に接続され、制御端子が前記第11のノードと接続され、

前記第12のノードが当該第3の制御信号生成回路の出力端である

請求項14に記載の昇圧回路。

【請求項16】

前記第4の制御信号生成回路は、

前記第4の電圧供給端子は、前記第5のノードの電位を供給し、

前記第6の電圧供給端子は、前記第6のノードの電位を供給し、

前記第3のインバータ回路は、入力に前記第2のクロック信号に応じた信号が入力され、

前記第12のノードが当該第4の制御信号生成回路の出力端である以外は、前記第3の制御信号生成回路と同様の回路構成を備える

請求項15に記載の昇圧回路。

【請求項1】

第1の電源電圧を、正側または負側の所定の電圧に昇圧する昇圧回路であって、

第1のノードに接続される第1のトランジスタと、

一端が前記第1のノードに接続され、前記第1のトランジスタの活性化時に前記第1のノードの電圧で充電される第1の容量素子と、

前記第1のトランジスタの制御端子に第1のクロック信号に応じた第1の制御信号を出力する第1の制御信号生成回路を有し、

前記第1の容量素子は、前記第1のトランジスタの非活性化時に、他端に印加される前記第1の電源電圧の1/2以下の電圧により前記第1のノードの電位を、正側または負側の第1の電圧に昇圧し、

前記第1の制御信号生成回路は、

前記第1のトランジスタの非活性化時の前記第1の制御信号の電位を、前記第1の電位とし、

前記第1のトランジスタの活性化時の前記第1の制御信号の電位を、前記第1の電位との差が前記第1の電源電圧以内となる電位とする

昇圧回路。

【請求項2】

前記第1のノードと、第2のノードとの間に接続される第2のトランジスタと、

前記第2のトランジスタの制御端子に第2のクロック信号に応じた第2の制御信号を出力し、前記第1のトランジスタが非活性化時に前記第2のトランジスタを活性化させる第2の制御信号生成回路を有し、

前記第2の制御信号生成回路は、

前記第2のトランジスタの非活性化時の前記第2の制御信号の電位を、前記第2のノードの第2の電位とし、

前記第2のトランジスタの活性化時の前記第2の制御信号の電位を、前記第2の電位との差が前記第1の電源電圧以内となる電位とする

請求項1に記載の昇圧回路。

【請求項3】

前記第1、第2のトランジスタは、第1導電型であり、前記第1のトランジスタが前記第1の電源電圧を供給する第1の電源端子と前記第1のノードとの間に接続される

請求項1または請求項2に記載の昇圧回路。

【請求項4】

前記第1の制御信号生成回路は、第1導電型の第3、第4のトランジスタと、第2導電型の第5〜第8のトランジスタと、第1〜第3の電圧供給端子とを有し、

前記第1の電圧供給端子は、前記第1のノードの電位を供給し、

前記第2の電圧供給端子は、前記第1の電源電圧を供給し、

前記第3の電圧供給端子は、前記第1の電源電圧の1/2の電位を供給し、

前記第3のトランジスタは、前記第1の電圧供給端子と第3のノードとの間に接続され、制御端子が第4のノードと接続され、

前記第4のトランジスタは、前記第1の電圧供給端子と前記第4のノードとの間に接続され、制御端子が前記第3のノードと接続され、

前記第5のトランジスタは、前記第3のノードと第5のノードとの間に接続され、制御端子が前記第2の電圧供給端子と接続され、

前記第6のトランジスタは、前記第4のノードと第6のノードとの間に接続され、制御端子が前記第2の電圧供給端子と接続され、

前記第7のトランジスタは、前記第5のノードと前記第3の電圧供給端子との間に接続され、制御端子に前記第1の電源電圧の振幅レベルを有する前記第1のクロック信号を入力し、

前記第8のトランジスタは、前記第6のノードと前記第3の電圧供給端子との間に接続され、制御端子に前記第1のクロック信号の反転信号を入力し、

前記第4のノードが当該第1の制御信号生成回路の出力端である

請求項3に記載の昇圧回路。

【請求項5】

前記第2の制御信号生成回路は、

前記第1の電圧供給端子は、前記第2のノードの電位を供給し、

前記第7のトランジスタの制御端子に前記第1の電源電圧の振幅レベルを有する前記第2のクロック信号を入力し、

前記第8のトランジスタの制御端子に前記第2のクロック信号の反転信号を入力し、

前記第4のノードが当該第2の制御信号生成回路の出力端である以外は、前記第1の制御信号生成回路と同様の回路構成を備える

請求項4に記載の昇圧回路。

【請求項6】

前記第2のノードと、第7のノードとの間に接続される第1導電型の第9のトランジスタと

一端が前記第7のノードに接続され、前記第9のトランジスタの活性化時に前記第7のノードの電圧で充電される第2の容量素子と、

前記第9のトランジスタの制御端子に前記第1のクロック信号に応じた第3の制御信号を出力する第3の制御信号生成回路を有し、

前記第2の容量素子は、前記第9のトランジスタの非活性化時に、他端に印加される前記第1の電源電圧の1/2以下の電圧により前記第7のノードの電位を、正側の第3の電圧に昇圧し、

前記第3の制御信号生成回路は、

前記第9のトランジスタの非活性化時の前記第3の制御信号の電位を、前記第3の電位とし、

前記第9のトランジスタの活性化時の前記第3の制御信号の電位を、前記第3の電位との差が前記第1の電源電圧以内となる電位とする

請求項4もしくは請求項5に記載の昇圧回路。

【請求項7】

前記第7のノードと、第8のノードとの間に接続される第1導電型の第10のトランジスタと、

前記第10のトランジスタの制御端子に第2のクロック信号に応じた第4の制御信号を出力し、前記第9のトランジスタが非活性化時に前記第10のトランジスタを活性化させる第4の制御信号生成回路を有し、

前記第4の制御信号生成回路は、

前記第10のトランジスタの非活性化時の前記第4の制御信号の電位を、前記第8のノードの第4の電位とし、

前記第10のトランジスタの活性化時の前記第4の制御信号の電位を、前記第4の電位との差が前記第1の電源電圧以内となる電位とする

請求項6に記載の昇圧回路。

【請求項8】

前記第3の制御信号生成回路は、第1導電型の第11〜第14のトランジスタと、第2導電型の第15〜第22のトランジスタと、第4〜第7の電圧供給端子とを有し、

前記第4の電圧供給端子は、前記第2のノードの電位を供給し、

前記第5の電圧供給端子は、前記第1の電源電圧を供給し、

前記第6の電圧供給端子は、前記第1の電源電圧の1/2の電位を供給し、

前記第7の電圧供給端子は、前記第7のノードの電位を供給し、

前記第11のトランジスタは、前記第4の電圧供給端子と第9のノードとの間に接続され、制御端子が第10のノードと接続され、

前記第12のトランジスタは、前記第4の電圧供給端子と前記第10のノードとの間に接続され、制御端子が前記第9のノードと接続され、

前記第15のトランジスタは、前記第9のノードと第11のノードとの間に接続され、制御端子が前記第5の電圧供給端子と接続され、

前記第16のトランジスタは、前記第10のノードと第12のノードとの間に接続され、制御端子が前記第5の電圧供給端子と接続され、

前記第17のトランジスタは、前記第11のノードと前記第6の電圧供給端子との間に接続され、制御端子に前記第1のクロック信号を入力し、

前記第18のトランジスタは、前記第12のノードと前記第6の電圧供給端子との間に接続され、制御端子に前記第1のクロック信号の反転信号を入力し、

前記第13のトランジスタは、前記第7の電圧供給端子と第13のノードとの間に接続され、制御端子が第14のノードと接続され、

前記第14のトランジスタは、前記第7の電圧供給端子と前記第14のノードとの間に接続され、制御端子が前記第13のノードと接続され、

前記第19のトランジスタは、前記第13のノードと第15のノードとの間に接続され、制御端子が前記第4の電圧供給端子と接続され、

前記第20のトランジスタは、前記第14のノードと第16のノードとの間に接続され、制御端子が前記第4の電圧供給端子と接続され、

前記第21のトランジスタは、前記第15のノードと前記第5の電圧供給端子との間に接続され、制御端子が前記第10のノードと接続され、

前記第22のトランジスタは、前記第16のノードと前記第5の電圧供給端子との間に接続され、制御端子が前記第9のノードと接続され、

前記第14のノードが当該第3の制御信号生成回路の出力端である

請求項7に記載の昇圧回路。

【請求項9】

前記第4の制御信号生成回路は、

前記第4の電圧供給端子は、前記第2のノードの電位を供給し、

前記第7の電圧供給端子は、前記第7のノードの電位を供給し、

前記第17のトランジスタの制御端子に前記第2のクロック信号を入力し、

前記第18のトランジスタの制御端子に前記第2のクロック信号の反転信号を入力し、

前記第14のノードが当該第4の制御信号生成回路の出力端である以外は、前記第3の制御信号生成回路と同様の回路構成を備える

請求項8に記載の昇圧回路。

【請求項10】

前記第1、第2のトランジスタは、第2の導電性を有し、前記第1のトランジスタが、接地電圧を供給する第2の電源端子と前記第1のノードとの間に接続される

請求項1または請求項2に記載の昇圧回路。

【請求項11】

前記第1の制御信号生成回路は、第1導電型の第3、第4のトランジスタと、第2導電型の第5、第6のトランジスタと、第1、第2のインバータ回路と、第1、第2の電圧供給端子とを有し、

前記第1の電圧供給端子は、前記第1の電源電圧の1/2の電位を供給し、

前記第2の電圧供給端子は、前記第1のノードの電位を供給し、

前記第1のインバータ回路は、高電位側の電源電圧を前記第1の電圧供給端子の電位、低電圧側の電源電圧を接地電圧とし、入力に前記第1のクロック信号に応じた信号が入力され、

前記第2のインバータ回路は、高電位側の電源電圧を前記第1の電圧供給端子の電位、低電圧側の電源電圧を接地電圧とし、入力に前記第1のインバータ回路の出力が入力され、

前記第3のトランジスタは、前記第1の電圧供給端子と第3のノードとの間に接続され、制御端子に前記第1のインバータ回路の出力を入力し、

前記第4のトランジスタは、前記第1の電圧供給端子と第4のノードとの間に接続され、制御端子に前記第2のインバータ回路の出力を入力し、

前記第5のトランジスタは、前記第3のノードと前記第2の電圧供給端子との間に接続され、制御端子が前記第4のノードに接続され、

前記第6のトランジスタは、前記第4のノードと前記第2の電圧供給端子との間に接続され、制御端子が前記第3のノードに接続され、

前記第4のノードが当該第1の制御信号生成回路の出力端である

請求項10に記載の昇圧回路。

【請求項12】

前記第2の制御信号生成回路は、

前記第2の電圧供給端子は、前記第2のノードの電位を供給し、

前記第1のインバータ回路は、入力に前記第2のクロック信号に応じた信号が入力され、

前記第4のノードが当該第2の制御信号生成回路の出力端である以外は、前記第1の制御信号生成回路と同様の回路構成を備える

請求項11に記載の昇圧回路。

【請求項13】

前記第2のノードと、第5のノードとの間に接続される第2導電型の第7のトランジスタと

一端が前記第5のノードに接続され、前記第7のトランジスタの活性化時に前記第5のノードの電圧で充電される第2の容量素子と、

前記第7のトランジスタの制御端子に前記第1のクロック信号に応じた第3の制御信号を出力する第3の制御信号生成回路を有し、

前記第2の容量素子は、前記第7のトランジスタの非活性化時に、他端に印加される前記第1の電源電圧の1/2以下の電圧により前記第5のノードの電位を、負側の第3の電圧に昇圧し、

前記第3の制御信号生成回路は、

前記第7のトランジスタの非活性化時の前記第3の制御信号の電位を、前記第3の電位とし、

前記第7のトランジスタの活性化時の前記第3の制御信号の電位を、前記第3の電位との差が前記第1の電源電圧以内となる電位とする

請求項11もしくは請求項12に記載の昇圧回路。

【請求項14】

前記第5のノードと、第6のノードとの間に接続される第2導電型の第8のトランジスタと、