昇圧型DC/DCコンバータ

【課題】 昇圧型DC/DCコンバータの出力電圧を低電圧レベルから高電圧レベルに切り替えたときの突入電流を最小限に抑える。

【解決手段】 LED6の輝度を低輝度から高輝度に切り替え設定すると、制御回路81は、現設定データより1ステップ高い設定データをD/Aコンバータ84に出力し、D/Aコンバータ84は、該設定データに対応する電圧を基準電圧としてコンパレータ85へ出力する。コンパレータ85は、ドライバ制御回路86に対して昇圧動作を指示し、ドライバ制御回路86はFET3をオン/オフ制御することにより昇圧動作を開始する。DC/DCコンバータの出力電圧が設定データに相当する電圧に達すると、コンパレータ85の指示によりドライバ制御回路86は昇圧動作を停止する。制御回路81は、この動作を所定時間毎に前回よりも1ステップ高い設定データをD/Aコンバータ84に出力する動作を、高輝度電圧レベルとなるまで繰り返す。

【解決手段】 LED6の輝度を低輝度から高輝度に切り替え設定すると、制御回路81は、現設定データより1ステップ高い設定データをD/Aコンバータ84に出力し、D/Aコンバータ84は、該設定データに対応する電圧を基準電圧としてコンパレータ85へ出力する。コンパレータ85は、ドライバ制御回路86に対して昇圧動作を指示し、ドライバ制御回路86はFET3をオン/オフ制御することにより昇圧動作を開始する。DC/DCコンバータの出力電圧が設定データに相当する電圧に達すると、コンパレータ85の指示によりドライバ制御回路86は昇圧動作を停止する。制御回路81は、この動作を所定時間毎に前回よりも1ステップ高い設定データをD/Aコンバータ84に出力する動作を、高輝度電圧レベルとなるまで繰り返す。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、昇圧型DC/DCコンバータに関し、特にその出力電圧を調整することが可能な昇圧型DC/DCコンバータに関する。

【背景技術】

【0002】

直流電源と直列にインダクタ(コイル)及びスイッチング素子を接続し、該インダクタとスイッチング素子の接続点をダイオードのアノードに接続するとともに該ダイオードのカソードをコンデンサの一端及び出力端子に接続し、パルス幅変調回路等からなるデューティ比制御回路によりスイッチング素子のオン/オフ時間を制御することによって、昇圧された電圧を出力する昇圧型DC/DCコンバータは、例えば特許文献1等に示されているように、従来から知られている。

【0003】

このデューティ制御回路によりそのデューティ比が制御された所定周期Tのパルスをスイッチング素子に入力する構成の昇圧型DC/DCコンバータでは、TONとなるパルス幅の区間、TONに対応する電圧をスイッチング素子に入力してスイッチング素子をオン状態とすることにより、直流電源からの電流をインダクタ及びスイッチング素子を介して流し、その後、TOFFとなるパルス幅の区間、TOFFに対応する電圧をスイッチング素子に入力してスイッチング素子をオフに切り替え、それまでインダクタに流れていた電流の過渡応答により、インダクタ及びスイッチング素子の接続点の電圧を直流電源電圧以上に上昇させる。

【0004】

この上昇した電圧による電流は、インダクタ及びスイッチング素子の接続点にそのアノードが接続されたダイオードを介して出力されるとともに、該ダイオードのカソードに接続されたコンデンサに充電される。また、スイッチング素子がオンのときにはダイオードのアノード側は接地電位となりダイオードはオフとなって、コンデンサに充電された電荷による電流は負荷へ出力される。これにより、直流電源電圧以上に昇圧された直流出力電圧が得られる。昇圧される出力電圧の値は、デューティ制御回路によって所定周期Tのパルスのデューティ比を変更することにより調整できる。

【0005】

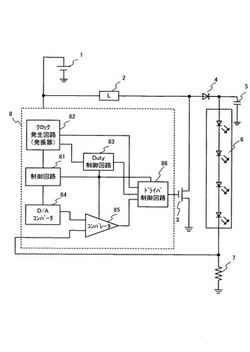

図1は、上記構成の昇圧型DC/DCコンバータで昇圧された出力電圧をLEDに供給し、昇圧される電圧の値を切り替えてLEDの輝度を調整することができるようにした回路構成を示しており、図6は、図1に示す回路を用いて、LEDの輝度を低輝度(暗い状態)から高輝度(明るい状態)に変更する場合の出力電圧調整動作を示すタイムチャートを示している。

【0006】

この昇圧型DC/DCコンバータは、本回路が適用される装置の電源であるとともに本回路の昇圧電圧を得るための入力電圧となる電池1と、入力電圧を昇圧する動作を行うための回路であるインダクタ2、スイッチング素子として動作するFET3、ダイオード4、コンデンサ5と、負荷であるLED6と、昇圧された電圧の分圧された電圧を発生するための抵抗7と、FET3のオン/オフ動作を制御するスイッチング制御部8により構成される。

【0007】

また、スイッチング制御部8は、外部から設定された出力電圧値に対応する昇圧値データを設定するとともにスイッチング制御部8の動作を制御する制御回路81と、昇圧動作に使用されるクロックを発生するクロック発生回路82と、制御回路81で設定されている昇圧値データに従ってクロック発生回路81のクロックのDuty比を制御する信号を発生するDuty制御回路83と、制御回路81で設定された昇圧値データに対応する基準電圧を発生するD/Aコンバータ84と、昇圧された出力電圧とD/Aコンバータ84から出力される基準電圧とを比較し、その大小関係に応じて昇圧動作を制御する信号を発生するコンパレータ85と、クロック発生回路82、Duty制御回路83及びコンパレータ85からの信号を入力してFET3のオン/オフ動作を制御するドライバ制御回路86とにより構成される。

【0008】

LED6の輝度を低輝度(暗い状態)から高輝度(明るい状態)に変更するときに、LED6を高輝度状態にする出力電圧値が制御回路81に設定されると、制御回路81は、高電圧レベル切り替え動作を起動するとともに、D/Aコンバータ84に対して、高電圧レベルに対応して設定された昇圧値データを出力する。また、Duty制御回路83は、制御回路81から高電圧レベル切り替え動作起動信号を受けて、昇圧値データに対応する昇圧電圧が得られるようにクロック発生回路82のクロックのDuty比を制御する信号を発生してドライバ制御回路86へ出力する。特許文献1に記載されているように、このDuty比は、高い出力電圧が設定される程スイッチング素子として動作するFET3のオン時間が長くなるように制御される。

【0009】

D/Aコンバータ84は、制御回路81で設定された昇圧値データに対応するアナログ電圧を基準電圧としてコンパレータ85へ出力する。例えば図6に示すように、制御回路81が現設定データである“0011”データ(低輝度設定データ)を、高輝度出力電圧値となる設定データである“1011”に切り替えると、D/Aコンバータ84から出力される基準電圧は“1011”データに対応する電圧となる。DC/DCコンバータの現出力電圧は“0011”に対応する電圧であり、LED6と抵抗7で分圧された出力電圧はD/Aコンバータ84から出力される設定基準電圧よりも低いので、コンパレータ85は、ドライバ制御回路86に対して、昇圧動作(スイッチング動作)を指示する信号を出力する。

【0010】

ドライバ制御回路86は、コンパレータ85からの昇圧動作指示を受けると、クロック発生回路82のクロック信号をDuty制御回路83により設定された高輝度出力電圧に対応するDuty比でパルス幅変調した信号をFET3のゲートに供給し、FET3をオン/オフ制御することにより昇圧動作を開始する。DC/DCコンバータの出力電圧(LED6と抵抗7で分圧された出力電圧)がD/Aコンバータ84から出力されている高輝度出力電圧値に達すると、コンパレータ85は、ドライバ制御回路86に対して昇圧動作(スイッチング動作)の停止を指示する信号を出力する。

【0011】

以降、コンパレータ85は、DC/DCコンバータ出力を分圧した電圧とD/Aコンバータ84で設定されている基準電圧とを比較することによってこのDC/DCコンバータの出力電圧を監視し、DC/DCコンバータ出力を分圧した電圧がD/Aコンバータ84で設定されている基準電圧よりも低下したことを検出するとドライバ制御回路86に対して昇圧動作の開始を指示し、DC/DCコンバータ出力を分圧した電圧がD/Aコンバータ84で設定されている基準電圧に達したことを検出すると昇圧動作の停止を指示することを繰り返すことにより、DC/DCコンバータの出力電圧を“1011”データに相当する高輝度出力電圧値に保持する。

【0012】

【特許文献1】特開平11−136929号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

上記出力電圧調整可能な昇圧型DC/DCコンバータにおいて、負荷LEDを暗い状態から明るい状態に調整するには、その駆動電圧(出力電圧)を、低輝度状態に対応する低い電圧から高輝度状態に対応する高い電圧に変化する必要があり、そのため、Duty制御回路83から出力されるDuty比の制御データは、低い出力電圧に対応するDuty比データから高い出力電圧に対応するDuty比データに切り替えられ、また、D/Aコンバータ84へ出力する設定データは、暗い状態に対応する低輝度設定データ“0011”から明るい状態に対応する高輝度設定データ“1011”に切り替えられる。

【0014】

このDuty比は、出力電圧が高い電圧に設定される程スイッチング素子として動作するFET3のオン時間が長くなるように設定されるため、高輝度状態に設定されると、FET3のゲート制御によりGNDへの短絡時間が長くなる。而も、低輝度状態に対応する低い電圧と高輝度状態に対応する高い電圧との差が大きい(D/Aコンバータ6の出力電圧と昇圧電圧の分圧であるフィードバック電圧との電圧差が大きい)と、低輝度状態から高輝度状態に切り替えられた後、設定された高電圧に達するまで時間が掛かる。

【0015】

この低電圧から高電圧に達するまでの間、FET3は短絡時間が長いDuty比のクロックパルスによりオン/オフ動作が継続して実行されるため、図6に示すように、その間、突入電流として過電流が流れる。この過電流は電源(電池1)から供給されるため、電源(電池1)出力に大きな電圧変動(電圧ドロップ)を生じる。この電源(電池1)は、通常このLED輝度調整回路を備えている装置(例えば携帯電話機等)全体の電源としても使用されるので、この電圧変動により装置に誤動作が発生することがある。

【0016】

本発明は、上記問題点に鑑み、少なくとも低電圧レベルと高電圧レベルの2つの電圧を出力可能な昇圧型DC/DCコンバータにおいて、出力電圧を低電圧レベルから高電圧レベルに切り替えたときの突入電流を最小限に抑え、過電流を抑制する手段を提供することにある。

【課題を解決するための手段】

【0017】

本発明の昇圧型DC/DCコンバータは、直流電源と、該直流電源の正極にインダクタを介してその一方の端子が接続され、他方の端子が前記直流電源の負極に接続されたスイッチング素子と、前記インダクタとスイッチング素子の接続点にアノードが接続されたダイオードと、該ダイオードのカソードと前記直流電源の負極の間に接続されたコンデンサと、前記スイッチング素子をオン/オフ制御するスイッチング制御部とからなり、前記コンデンサの両端から前記直流電源電圧を昇圧した低電圧レベル及び高電圧レベルの少なくとも2つの電圧レベルを切り替えて出力することを可能に構成された出力電圧調整可能な昇圧型DC/DCコンバータであって、前記スイッチング制御部には、前記低電圧レベルと高電圧レベルに対応する昇圧値データをデジタルデータとして設定する手段と、前記低電圧レベルに対応する昇圧値データが設定されている状態において前記高電圧レベルへの切り替え指示を受けたとき、切り替え動作を起動するとともに、前記低電圧レベルから前記高電圧レベルまで所定のレベル差で階段状に上昇するデジタル昇圧値データを、所定時間間隔で順次設定して出力する手段を有する制御回路と、昇圧動作に使用されるクロックを発生するクロック発生回路と、前記制御回路から切り替え動作を起動する信号を受けて、前記クロック発生回路のクロックのDuty比を制御するDuty制御信号を発生するDuty制御回路と、前記制御回路から出力される前記所定のレベル差で上昇するデジタル昇圧値データを入力して、該デジタル昇圧値データに対応する基準電圧を前記所定時間間隔で順次発生するD/Aコンバータと、昇圧された出力電圧レベルと前記D/Aコンバータから出力される基準電圧とを比較し、前記出力電圧レベルが前記基準電圧以上か、または基準電圧より低いかを判定するコンパレータと、前記クロック発生回路、Duty制御回路およびコンパレータからの信号を受け、前記昇圧された出力電圧レベルが前記基準電圧よりも低いと判定されている間、前記Duty制御信号によりそのDuty比が変調された前記クロック信号を用いて前記スイッチング素子のオン/オフ動作を制御するドライバ制御回路とを備えたことを特徴としている。

【0018】

前記制御回路は、低い電圧から高い電圧への出力電圧調整時に、前記クロック発生回路のクロックを所定数カウントすることにより前記所定時間を設定し、この所定時間毎に1コード分増加する昇圧値データを発生し、前記D/Aコンバータの出力電圧を一定の時間間隔で1コード分の電圧づつ増加させるように制御する構成とすることができる。

【0019】

また、本発明は、上記記載の出力電圧調整可能な昇圧型DC/DCコンバータの出力電圧が供給され、前記低電圧レベルと高電圧レベルに対応する低輝度状態と高輝度状態に調整されるLEDを備えることにより、LED輝度調整回路を構成したことを特徴とする。

【発明の効果】

【0020】

本発明によれば、昇圧型DC/DCコンバータの出力電圧を低い状態から高い状態に変化させるときに(例えばLED等を暗い状態から明るい状態に調整するとき)、基準電圧を発生するD/Aコンバータの出力電圧値を、所定時間間隔で現状の低電圧値から設定高電圧値まで例えば1コード分の電圧づつ順次上昇させて設定するので、D/Aコンバータの出力電圧を使用しているコンパレータの基準電圧と昇圧電圧の分圧であるフィードバック電圧との電圧差が小さいため、各ステップにおける昇圧動作時間が短くなるとともに突入電流が時間方向に分散された小さな値に抑えられる。そのため、過大な突入電流を抑制することができる。

【0021】

また、Duty制御回路が、制御回路が発生する昇圧設定データに対応したDuty制御信号を出力するように設定すれば、昇圧設定データが低い時にはFET3は短絡時間が短いDuty比のクロックパルスによりオン/オフ動作されるので、FETのゲート制御によるGNDへの短絡時間は、高電圧レベルに切り替え当初はより短くなるため、突入電流を最小限に抑えることが可能となる。

【発明を実施するための最良の形態】

【0022】

図1は、本発明の第1の実施形態を示す出力電圧調整可能な昇圧型DC/DCコンバータのブロック図である。本実施形態は、上記背景技術で説明した構成例と同様のブロック構成となっているが、本実施形態では、制御回路81における制御手段、およびDuty制御回路から出力されるDuty制御信号が上記背景技術で説明した構成とは異なっている。

【0023】

本実施形態においても、昇圧型DC/DCコンバータは、本回路が適用される装置の電源であるとともに本回路の昇圧電圧を得るための入力電圧となる電池1と、入力電圧を昇圧する動作を行うための回路であるインダクタ2、スイッチング素子として動作するFET3、ダイオード4、コンデンサ5と、負荷であるLED6と、昇圧された電圧を分圧した電圧を発生するための抵抗7と、FET3のオン/オフ動作を制御するスイッチング制御部8とにより構成されている。

【0024】

また、スイッチング制御部8は、昇圧動作に使用されるクロックを発生するクロック発生回路82と、クロック発生回路82のクロックのDuty比を制御する信号を発生するDuty制御回路83と、制御回路81で設定された昇圧値データに対応する基準電圧を発生するD/Aコンバータ84と、昇圧された出力電圧とD/Aコンバータ84から出力される基準電圧とを比較し、その大小関係に応じて昇圧動作を制御する信号を発生するコンパレータ85と、クロック発生回路82、Duty制御回路83及びコンパレータ85からの信号を入力してFET3のオン/オフ動作を制御するドライバ制御回路86を備えている点では、上記背景技術で説明した構成と同様であるが、本実施形態の制御回路81は、以下に説明する本発明特有の制御動作を行うための手段を有しており、また、Duty制御回路83は、制御回路81で設定された昇圧値データに対応したDuty比制御信号を発生する。

【0025】

図2は、本実施形態の制御回路81の動作を示すフローチャートであり、図3は、本実施形態の出力電圧調整動作を示すタイムチャートである。以下、本実施形態の動作について、図1〜図3を参照して説明する。

【0026】

LED6の輝度を低輝度(暗い状態)から高輝度(明るい状態)に変更するときに、LED6が高輝度となる出力電圧設定値“1011”が制御回路81に設定される(S1)と、制御回路81は、高輝度となる出力電圧への切り替え動作を起動するとともに、現設定データ“0011”より1コード高い設定データ“0100”を設定して(S2)、D/Aコンバータ84に出力する。Duty制御回路83は、制御回路81から高輝度となる出力電圧への切り替え動作を起動する信号を受けて、制御回路81で設定された昇圧値データ“0100”に対応する昇圧電圧が得られるようにクロック発生回路81のクロックのDuty比を制御する信号を発生してドライバ制御回路86へ出力する。

【0027】

D/Aコンバータ84は、制御回路81で設定された昇圧値データ“0100”に対応するアナログ電圧を基準電圧としてコンパレータ85へ出力する。DC/DCコンバータの現出力電圧は“0011”に対応する電圧であり、その分圧値はD/Aコンバータ84から出力される“0100”に対応する設定基準電圧よりも低いので、コンパレータ85は、ドライバ制御回路86に対して、昇圧動作(スイッチング動作)を指示する信号を出力する。

【0028】

ドライバ制御回路86は、コンパレータ85からの昇圧動作指示を受けると、クロック発生回路82のクロック信号をDuty制御回路83により設定されたDuty比でパルス幅変調した信号をFET3のゲートに供給し、FET3をオン/オフ制御することにより昇圧動作を開始する。DC/DCコンバータの出力電圧が設定された昇圧値データ“0100”に相当する電圧に達すると、コンパレータ85は、ドライバ制御回路86に対して昇圧動作(スイッチング動作)の停止を指示する信号を出力する。

【0029】

一方、制御回路81は、設定した昇圧値データ“0100”をD/Aコンバータ84に出力した後、この設定データ“0100”(設定昇圧値データ)と高輝度の設定データ“1011”とを比較し(S3)、設定昇圧値データが低ければクロック発生回路82のクロックを所定数カウント(S4)した後、更に1コード高い設定昇圧値データ“0101”を設定(S1)してD/Aコンバータ84に出力するとともに、Duty制御回路83に対して設定変更したことを示す信号を出力する。制御回路81における前記クロックのカウント数は、カウント時間がDC/DCコンバータの出力電圧が設定された昇圧値データ“0100”に相当する電圧に達する時間よりも少し長くなるようにその所定カウント数の値が設定される。

【0030】

Duty制御回路83は、制御回路81から設定変更したことを示す信号を受けて、制御回路81で設定された昇圧値データ“0101”に対応する昇圧電圧が得られるようにクロック発生回路81のクロックのDuty比を制御する信号を発生してドライバ制御回路86へ出力する。また、D/Aコンバータ84は、制御回路81で設定された昇圧値データ“0101”に対応するアナログ電圧を基準電圧としてコンパレータ85へ出力する。

【0031】

DC/DCコンバータの現出力電圧は“0100”に対応する電圧であり、その分圧値はD/Aコンバータ84から出力される“0101”に対応する設定基準電圧よりも低いので、コンパレータ85は、ドライバ制御回路86に対して、昇圧動作(スイッチング動作)を指示する信号を出力する。ドライバ制御回路86は、コンパレータ85からの昇圧動作指示を受けると、クロック発生回路82のクロック信号をDuty制御回路83により設定されたDuty比でパルス幅変調した信号をFET3のゲートに供給し、FET3をオン/オフ制御することにより昇圧動作を開始する。

【0032】

DC/DCコンバータの出力電圧が設定された昇圧値データ“0101”に相当する電圧に達すると、コンパレータ85は、ドライバ制御回路86に対して昇圧動作(スイッチング動作)の停止を指示する信号を出力する。この一連の動作を、低輝度である現設定データ“0011”から高輝度の設定データ“1011”になるまで一定時間(前記クロックを所定数カウントする時間)間隔で1コードづつ上昇させながら繰り返す。そして、設定昇圧値データが高輝度の設定データ“1011”と同じになったら設定データの上昇を停止(S5)し、以降、設定データ“1011”に対応する出力電圧を維持するようにコンパレータ85で監視制御する。

【0033】

本実施形態によれば、スイッチ素子であるFET3のゲートに供給されるクロックパルスのDuty比は、GNDへの短絡時間が最も長くなる高輝度状態にいきなり設定されることはなく、而も、D/Aコンバータ6の出力電圧と昇圧電圧の分圧であるフィードバック電圧との電圧差が小さいので、各ステップにおける昇圧動作時間は短くなる。そのため、LEDを高輝度に切り替えた時に、電源(電池1)出力に大きな電圧変動(電圧ドロップ)を生じるような過大な突入電流を抑えることができる。

【0034】

LED6を高輝度状態から低輝度状態に切り替え設定するために、DC/DCコンバータの出力電圧を高電圧から低電圧へ下げるばあいには、スイッチング制御パルスのDuty比はFET3の短絡時間が短くなる値に設定される。また、コンパレータ85に入力される比較電圧が低電圧設定値に下がるまで昇圧動作は停止され、コンパレータ85に入力される比較電圧が低電圧設定値より低下した後に制御回路83により設定されたDuty比により、FET3がオン/オフ制御されて低電圧設定値を維持するように動作する。

【0035】

従ってこの場合は、D/Aコンバータ84に対して、直接低電圧値データ“0011”が設定されても、過大な突入電流が流れるような動作が行われることはないので、LED6を高輝度状態から低輝度状態に切り替え設定する場合には、制御回路81は、低輝度状態への切り替えと同時に、D/Aコンバータ84に対して低電圧値データ“0011”が設定され、Duty制御回路83は低電圧値データ“0011”に対応するDuty制御信号を発生する。

【0036】

なお、上記実施形態では、制御回路81からDuty制御回路83へ出力されるデジタル昇圧値データ切り替え信号を受けて、Duty制御回路83が、低電圧レベル“0011”から所定のレベル差で階段状に上昇する昇圧値データ“0100”,“0101”,…,“1011”に対応するDuty制御信号を順次発生するように構成したが、Duty制御回路83が制御回路81から高電圧レベルへの切り替え動作を起動する信号を受けた時点から、昇圧値データ“1011”に対応するDuty制御信号を出力するように構成してもよい。

【0037】

この場合、低輝度状態から高輝度状態へ切り替え直後から、スイッチ素子であるFET3のゲートに供給されるクロックパルスのDuty比は、GNDへの短絡時間が最も長くなる高輝度状態に直ちに設定されるため、上記実施形態の場合よりは突入電流は多くなるが、D/Aコンバータ6の出力電圧と昇圧電圧の分圧であるフィードバック電圧との電圧差は小さいので、各ステップにおける昇圧動作時間は短くなり、突入電流は時間方向に分散されるため、図6に示すような過大な突入電流とはならない。

【0038】

図4は、本発明の第2の実施形態を示す出力電圧調整可能な昇圧型DC/DCコンバータのブロック図である。本実施形態では、CPU9及びタイマー10が備えられており、D/Aコンバータ84に対する設定データを所定時間毎に1コードづつ上昇させる手段として、タイマー10のタイミングでCPU9がソフト処理により上昇させている点で、第1の実施形態と異なるが、同様の効果を得ることができる。この場合、制御回路81は、出力電圧切り替え動作起動信号を各ブロックに出力する機能を果す。なお、タイマー10を制御回路81に接続し、制御回路81がタイマー10のタイミングでソフト処理により設定データを上昇させるように構成することもできる。

【0039】

図5は、本発明の第3の実施形態を示す出力電圧調整可能な昇圧型DC/DCコンバータのブロック図である。本実施形態では、D/Aコンバータ84の出力にコンデンサ10を備えることで、高輝度設定データ設定に対するD/Aコンバータ84の出力電圧をコンデンサ10の充電により遅延させることにより、図3に示すD/Aコンバータ出力電圧の各ステップ電圧での立ち上がり特性を緩やかにしている。その結果、各ステップにおいてFET3がオンとなるスイッチングの間隔を伸ばす効果が生じ、突入電流をより小さくする効果が得られる。

【図面の簡単な説明】

【0040】

【図1】本発明が適用される昇圧型DC/DCコンバータを示すブロック図である。

【図2】本発明の実施形態の制御動作を示すフローチャートである。

【図3】本発明の実施形態の出力電圧調整動作を示すタイムチャートである。

【図4】本発明が適用される昇圧型DC/DCコンバータの他の例を示すブロック図である。

【図5】本発明が適用される昇圧型DC/DCコンバータの他の例を示すブロック図である。

【図6】従来例の出力電圧調整動作を示すタイムチャートである。

【符号の説明】

【0041】

1 直流電源(電池)

2 インダクタ

3 FET

4 ダイオード

5、11 コンデンサ

6 LED

7 抵抗

8 スイッチング制御部

9 タイマー

10 CPU

81 制御回路

82 クロック発生回路

83 Duty制御回路

84 D/Aコンバータ

85 コンパレータ

86 ドライバ制御回路

【技術分野】

【0001】

本発明は、昇圧型DC/DCコンバータに関し、特にその出力電圧を調整することが可能な昇圧型DC/DCコンバータに関する。

【背景技術】

【0002】

直流電源と直列にインダクタ(コイル)及びスイッチング素子を接続し、該インダクタとスイッチング素子の接続点をダイオードのアノードに接続するとともに該ダイオードのカソードをコンデンサの一端及び出力端子に接続し、パルス幅変調回路等からなるデューティ比制御回路によりスイッチング素子のオン/オフ時間を制御することによって、昇圧された電圧を出力する昇圧型DC/DCコンバータは、例えば特許文献1等に示されているように、従来から知られている。

【0003】

このデューティ制御回路によりそのデューティ比が制御された所定周期Tのパルスをスイッチング素子に入力する構成の昇圧型DC/DCコンバータでは、TONとなるパルス幅の区間、TONに対応する電圧をスイッチング素子に入力してスイッチング素子をオン状態とすることにより、直流電源からの電流をインダクタ及びスイッチング素子を介して流し、その後、TOFFとなるパルス幅の区間、TOFFに対応する電圧をスイッチング素子に入力してスイッチング素子をオフに切り替え、それまでインダクタに流れていた電流の過渡応答により、インダクタ及びスイッチング素子の接続点の電圧を直流電源電圧以上に上昇させる。

【0004】

この上昇した電圧による電流は、インダクタ及びスイッチング素子の接続点にそのアノードが接続されたダイオードを介して出力されるとともに、該ダイオードのカソードに接続されたコンデンサに充電される。また、スイッチング素子がオンのときにはダイオードのアノード側は接地電位となりダイオードはオフとなって、コンデンサに充電された電荷による電流は負荷へ出力される。これにより、直流電源電圧以上に昇圧された直流出力電圧が得られる。昇圧される出力電圧の値は、デューティ制御回路によって所定周期Tのパルスのデューティ比を変更することにより調整できる。

【0005】

図1は、上記構成の昇圧型DC/DCコンバータで昇圧された出力電圧をLEDに供給し、昇圧される電圧の値を切り替えてLEDの輝度を調整することができるようにした回路構成を示しており、図6は、図1に示す回路を用いて、LEDの輝度を低輝度(暗い状態)から高輝度(明るい状態)に変更する場合の出力電圧調整動作を示すタイムチャートを示している。

【0006】

この昇圧型DC/DCコンバータは、本回路が適用される装置の電源であるとともに本回路の昇圧電圧を得るための入力電圧となる電池1と、入力電圧を昇圧する動作を行うための回路であるインダクタ2、スイッチング素子として動作するFET3、ダイオード4、コンデンサ5と、負荷であるLED6と、昇圧された電圧の分圧された電圧を発生するための抵抗7と、FET3のオン/オフ動作を制御するスイッチング制御部8により構成される。

【0007】

また、スイッチング制御部8は、外部から設定された出力電圧値に対応する昇圧値データを設定するとともにスイッチング制御部8の動作を制御する制御回路81と、昇圧動作に使用されるクロックを発生するクロック発生回路82と、制御回路81で設定されている昇圧値データに従ってクロック発生回路81のクロックのDuty比を制御する信号を発生するDuty制御回路83と、制御回路81で設定された昇圧値データに対応する基準電圧を発生するD/Aコンバータ84と、昇圧された出力電圧とD/Aコンバータ84から出力される基準電圧とを比較し、その大小関係に応じて昇圧動作を制御する信号を発生するコンパレータ85と、クロック発生回路82、Duty制御回路83及びコンパレータ85からの信号を入力してFET3のオン/オフ動作を制御するドライバ制御回路86とにより構成される。

【0008】

LED6の輝度を低輝度(暗い状態)から高輝度(明るい状態)に変更するときに、LED6を高輝度状態にする出力電圧値が制御回路81に設定されると、制御回路81は、高電圧レベル切り替え動作を起動するとともに、D/Aコンバータ84に対して、高電圧レベルに対応して設定された昇圧値データを出力する。また、Duty制御回路83は、制御回路81から高電圧レベル切り替え動作起動信号を受けて、昇圧値データに対応する昇圧電圧が得られるようにクロック発生回路82のクロックのDuty比を制御する信号を発生してドライバ制御回路86へ出力する。特許文献1に記載されているように、このDuty比は、高い出力電圧が設定される程スイッチング素子として動作するFET3のオン時間が長くなるように制御される。

【0009】

D/Aコンバータ84は、制御回路81で設定された昇圧値データに対応するアナログ電圧を基準電圧としてコンパレータ85へ出力する。例えば図6に示すように、制御回路81が現設定データである“0011”データ(低輝度設定データ)を、高輝度出力電圧値となる設定データである“1011”に切り替えると、D/Aコンバータ84から出力される基準電圧は“1011”データに対応する電圧となる。DC/DCコンバータの現出力電圧は“0011”に対応する電圧であり、LED6と抵抗7で分圧された出力電圧はD/Aコンバータ84から出力される設定基準電圧よりも低いので、コンパレータ85は、ドライバ制御回路86に対して、昇圧動作(スイッチング動作)を指示する信号を出力する。

【0010】

ドライバ制御回路86は、コンパレータ85からの昇圧動作指示を受けると、クロック発生回路82のクロック信号をDuty制御回路83により設定された高輝度出力電圧に対応するDuty比でパルス幅変調した信号をFET3のゲートに供給し、FET3をオン/オフ制御することにより昇圧動作を開始する。DC/DCコンバータの出力電圧(LED6と抵抗7で分圧された出力電圧)がD/Aコンバータ84から出力されている高輝度出力電圧値に達すると、コンパレータ85は、ドライバ制御回路86に対して昇圧動作(スイッチング動作)の停止を指示する信号を出力する。

【0011】

以降、コンパレータ85は、DC/DCコンバータ出力を分圧した電圧とD/Aコンバータ84で設定されている基準電圧とを比較することによってこのDC/DCコンバータの出力電圧を監視し、DC/DCコンバータ出力を分圧した電圧がD/Aコンバータ84で設定されている基準電圧よりも低下したことを検出するとドライバ制御回路86に対して昇圧動作の開始を指示し、DC/DCコンバータ出力を分圧した電圧がD/Aコンバータ84で設定されている基準電圧に達したことを検出すると昇圧動作の停止を指示することを繰り返すことにより、DC/DCコンバータの出力電圧を“1011”データに相当する高輝度出力電圧値に保持する。

【0012】

【特許文献1】特開平11−136929号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

上記出力電圧調整可能な昇圧型DC/DCコンバータにおいて、負荷LEDを暗い状態から明るい状態に調整するには、その駆動電圧(出力電圧)を、低輝度状態に対応する低い電圧から高輝度状態に対応する高い電圧に変化する必要があり、そのため、Duty制御回路83から出力されるDuty比の制御データは、低い出力電圧に対応するDuty比データから高い出力電圧に対応するDuty比データに切り替えられ、また、D/Aコンバータ84へ出力する設定データは、暗い状態に対応する低輝度設定データ“0011”から明るい状態に対応する高輝度設定データ“1011”に切り替えられる。

【0014】

このDuty比は、出力電圧が高い電圧に設定される程スイッチング素子として動作するFET3のオン時間が長くなるように設定されるため、高輝度状態に設定されると、FET3のゲート制御によりGNDへの短絡時間が長くなる。而も、低輝度状態に対応する低い電圧と高輝度状態に対応する高い電圧との差が大きい(D/Aコンバータ6の出力電圧と昇圧電圧の分圧であるフィードバック電圧との電圧差が大きい)と、低輝度状態から高輝度状態に切り替えられた後、設定された高電圧に達するまで時間が掛かる。

【0015】

この低電圧から高電圧に達するまでの間、FET3は短絡時間が長いDuty比のクロックパルスによりオン/オフ動作が継続して実行されるため、図6に示すように、その間、突入電流として過電流が流れる。この過電流は電源(電池1)から供給されるため、電源(電池1)出力に大きな電圧変動(電圧ドロップ)を生じる。この電源(電池1)は、通常このLED輝度調整回路を備えている装置(例えば携帯電話機等)全体の電源としても使用されるので、この電圧変動により装置に誤動作が発生することがある。

【0016】

本発明は、上記問題点に鑑み、少なくとも低電圧レベルと高電圧レベルの2つの電圧を出力可能な昇圧型DC/DCコンバータにおいて、出力電圧を低電圧レベルから高電圧レベルに切り替えたときの突入電流を最小限に抑え、過電流を抑制する手段を提供することにある。

【課題を解決するための手段】

【0017】

本発明の昇圧型DC/DCコンバータは、直流電源と、該直流電源の正極にインダクタを介してその一方の端子が接続され、他方の端子が前記直流電源の負極に接続されたスイッチング素子と、前記インダクタとスイッチング素子の接続点にアノードが接続されたダイオードと、該ダイオードのカソードと前記直流電源の負極の間に接続されたコンデンサと、前記スイッチング素子をオン/オフ制御するスイッチング制御部とからなり、前記コンデンサの両端から前記直流電源電圧を昇圧した低電圧レベル及び高電圧レベルの少なくとも2つの電圧レベルを切り替えて出力することを可能に構成された出力電圧調整可能な昇圧型DC/DCコンバータであって、前記スイッチング制御部には、前記低電圧レベルと高電圧レベルに対応する昇圧値データをデジタルデータとして設定する手段と、前記低電圧レベルに対応する昇圧値データが設定されている状態において前記高電圧レベルへの切り替え指示を受けたとき、切り替え動作を起動するとともに、前記低電圧レベルから前記高電圧レベルまで所定のレベル差で階段状に上昇するデジタル昇圧値データを、所定時間間隔で順次設定して出力する手段を有する制御回路と、昇圧動作に使用されるクロックを発生するクロック発生回路と、前記制御回路から切り替え動作を起動する信号を受けて、前記クロック発生回路のクロックのDuty比を制御するDuty制御信号を発生するDuty制御回路と、前記制御回路から出力される前記所定のレベル差で上昇するデジタル昇圧値データを入力して、該デジタル昇圧値データに対応する基準電圧を前記所定時間間隔で順次発生するD/Aコンバータと、昇圧された出力電圧レベルと前記D/Aコンバータから出力される基準電圧とを比較し、前記出力電圧レベルが前記基準電圧以上か、または基準電圧より低いかを判定するコンパレータと、前記クロック発生回路、Duty制御回路およびコンパレータからの信号を受け、前記昇圧された出力電圧レベルが前記基準電圧よりも低いと判定されている間、前記Duty制御信号によりそのDuty比が変調された前記クロック信号を用いて前記スイッチング素子のオン/オフ動作を制御するドライバ制御回路とを備えたことを特徴としている。

【0018】

前記制御回路は、低い電圧から高い電圧への出力電圧調整時に、前記クロック発生回路のクロックを所定数カウントすることにより前記所定時間を設定し、この所定時間毎に1コード分増加する昇圧値データを発生し、前記D/Aコンバータの出力電圧を一定の時間間隔で1コード分の電圧づつ増加させるように制御する構成とすることができる。

【0019】

また、本発明は、上記記載の出力電圧調整可能な昇圧型DC/DCコンバータの出力電圧が供給され、前記低電圧レベルと高電圧レベルに対応する低輝度状態と高輝度状態に調整されるLEDを備えることにより、LED輝度調整回路を構成したことを特徴とする。

【発明の効果】

【0020】

本発明によれば、昇圧型DC/DCコンバータの出力電圧を低い状態から高い状態に変化させるときに(例えばLED等を暗い状態から明るい状態に調整するとき)、基準電圧を発生するD/Aコンバータの出力電圧値を、所定時間間隔で現状の低電圧値から設定高電圧値まで例えば1コード分の電圧づつ順次上昇させて設定するので、D/Aコンバータの出力電圧を使用しているコンパレータの基準電圧と昇圧電圧の分圧であるフィードバック電圧との電圧差が小さいため、各ステップにおける昇圧動作時間が短くなるとともに突入電流が時間方向に分散された小さな値に抑えられる。そのため、過大な突入電流を抑制することができる。

【0021】

また、Duty制御回路が、制御回路が発生する昇圧設定データに対応したDuty制御信号を出力するように設定すれば、昇圧設定データが低い時にはFET3は短絡時間が短いDuty比のクロックパルスによりオン/オフ動作されるので、FETのゲート制御によるGNDへの短絡時間は、高電圧レベルに切り替え当初はより短くなるため、突入電流を最小限に抑えることが可能となる。

【発明を実施するための最良の形態】

【0022】

図1は、本発明の第1の実施形態を示す出力電圧調整可能な昇圧型DC/DCコンバータのブロック図である。本実施形態は、上記背景技術で説明した構成例と同様のブロック構成となっているが、本実施形態では、制御回路81における制御手段、およびDuty制御回路から出力されるDuty制御信号が上記背景技術で説明した構成とは異なっている。

【0023】

本実施形態においても、昇圧型DC/DCコンバータは、本回路が適用される装置の電源であるとともに本回路の昇圧電圧を得るための入力電圧となる電池1と、入力電圧を昇圧する動作を行うための回路であるインダクタ2、スイッチング素子として動作するFET3、ダイオード4、コンデンサ5と、負荷であるLED6と、昇圧された電圧を分圧した電圧を発生するための抵抗7と、FET3のオン/オフ動作を制御するスイッチング制御部8とにより構成されている。

【0024】

また、スイッチング制御部8は、昇圧動作に使用されるクロックを発生するクロック発生回路82と、クロック発生回路82のクロックのDuty比を制御する信号を発生するDuty制御回路83と、制御回路81で設定された昇圧値データに対応する基準電圧を発生するD/Aコンバータ84と、昇圧された出力電圧とD/Aコンバータ84から出力される基準電圧とを比較し、その大小関係に応じて昇圧動作を制御する信号を発生するコンパレータ85と、クロック発生回路82、Duty制御回路83及びコンパレータ85からの信号を入力してFET3のオン/オフ動作を制御するドライバ制御回路86を備えている点では、上記背景技術で説明した構成と同様であるが、本実施形態の制御回路81は、以下に説明する本発明特有の制御動作を行うための手段を有しており、また、Duty制御回路83は、制御回路81で設定された昇圧値データに対応したDuty比制御信号を発生する。

【0025】

図2は、本実施形態の制御回路81の動作を示すフローチャートであり、図3は、本実施形態の出力電圧調整動作を示すタイムチャートである。以下、本実施形態の動作について、図1〜図3を参照して説明する。

【0026】

LED6の輝度を低輝度(暗い状態)から高輝度(明るい状態)に変更するときに、LED6が高輝度となる出力電圧設定値“1011”が制御回路81に設定される(S1)と、制御回路81は、高輝度となる出力電圧への切り替え動作を起動するとともに、現設定データ“0011”より1コード高い設定データ“0100”を設定して(S2)、D/Aコンバータ84に出力する。Duty制御回路83は、制御回路81から高輝度となる出力電圧への切り替え動作を起動する信号を受けて、制御回路81で設定された昇圧値データ“0100”に対応する昇圧電圧が得られるようにクロック発生回路81のクロックのDuty比を制御する信号を発生してドライバ制御回路86へ出力する。

【0027】

D/Aコンバータ84は、制御回路81で設定された昇圧値データ“0100”に対応するアナログ電圧を基準電圧としてコンパレータ85へ出力する。DC/DCコンバータの現出力電圧は“0011”に対応する電圧であり、その分圧値はD/Aコンバータ84から出力される“0100”に対応する設定基準電圧よりも低いので、コンパレータ85は、ドライバ制御回路86に対して、昇圧動作(スイッチング動作)を指示する信号を出力する。

【0028】

ドライバ制御回路86は、コンパレータ85からの昇圧動作指示を受けると、クロック発生回路82のクロック信号をDuty制御回路83により設定されたDuty比でパルス幅変調した信号をFET3のゲートに供給し、FET3をオン/オフ制御することにより昇圧動作を開始する。DC/DCコンバータの出力電圧が設定された昇圧値データ“0100”に相当する電圧に達すると、コンパレータ85は、ドライバ制御回路86に対して昇圧動作(スイッチング動作)の停止を指示する信号を出力する。

【0029】

一方、制御回路81は、設定した昇圧値データ“0100”をD/Aコンバータ84に出力した後、この設定データ“0100”(設定昇圧値データ)と高輝度の設定データ“1011”とを比較し(S3)、設定昇圧値データが低ければクロック発生回路82のクロックを所定数カウント(S4)した後、更に1コード高い設定昇圧値データ“0101”を設定(S1)してD/Aコンバータ84に出力するとともに、Duty制御回路83に対して設定変更したことを示す信号を出力する。制御回路81における前記クロックのカウント数は、カウント時間がDC/DCコンバータの出力電圧が設定された昇圧値データ“0100”に相当する電圧に達する時間よりも少し長くなるようにその所定カウント数の値が設定される。

【0030】

Duty制御回路83は、制御回路81から設定変更したことを示す信号を受けて、制御回路81で設定された昇圧値データ“0101”に対応する昇圧電圧が得られるようにクロック発生回路81のクロックのDuty比を制御する信号を発生してドライバ制御回路86へ出力する。また、D/Aコンバータ84は、制御回路81で設定された昇圧値データ“0101”に対応するアナログ電圧を基準電圧としてコンパレータ85へ出力する。

【0031】

DC/DCコンバータの現出力電圧は“0100”に対応する電圧であり、その分圧値はD/Aコンバータ84から出力される“0101”に対応する設定基準電圧よりも低いので、コンパレータ85は、ドライバ制御回路86に対して、昇圧動作(スイッチング動作)を指示する信号を出力する。ドライバ制御回路86は、コンパレータ85からの昇圧動作指示を受けると、クロック発生回路82のクロック信号をDuty制御回路83により設定されたDuty比でパルス幅変調した信号をFET3のゲートに供給し、FET3をオン/オフ制御することにより昇圧動作を開始する。

【0032】

DC/DCコンバータの出力電圧が設定された昇圧値データ“0101”に相当する電圧に達すると、コンパレータ85は、ドライバ制御回路86に対して昇圧動作(スイッチング動作)の停止を指示する信号を出力する。この一連の動作を、低輝度である現設定データ“0011”から高輝度の設定データ“1011”になるまで一定時間(前記クロックを所定数カウントする時間)間隔で1コードづつ上昇させながら繰り返す。そして、設定昇圧値データが高輝度の設定データ“1011”と同じになったら設定データの上昇を停止(S5)し、以降、設定データ“1011”に対応する出力電圧を維持するようにコンパレータ85で監視制御する。

【0033】

本実施形態によれば、スイッチ素子であるFET3のゲートに供給されるクロックパルスのDuty比は、GNDへの短絡時間が最も長くなる高輝度状態にいきなり設定されることはなく、而も、D/Aコンバータ6の出力電圧と昇圧電圧の分圧であるフィードバック電圧との電圧差が小さいので、各ステップにおける昇圧動作時間は短くなる。そのため、LEDを高輝度に切り替えた時に、電源(電池1)出力に大きな電圧変動(電圧ドロップ)を生じるような過大な突入電流を抑えることができる。

【0034】

LED6を高輝度状態から低輝度状態に切り替え設定するために、DC/DCコンバータの出力電圧を高電圧から低電圧へ下げるばあいには、スイッチング制御パルスのDuty比はFET3の短絡時間が短くなる値に設定される。また、コンパレータ85に入力される比較電圧が低電圧設定値に下がるまで昇圧動作は停止され、コンパレータ85に入力される比較電圧が低電圧設定値より低下した後に制御回路83により設定されたDuty比により、FET3がオン/オフ制御されて低電圧設定値を維持するように動作する。

【0035】

従ってこの場合は、D/Aコンバータ84に対して、直接低電圧値データ“0011”が設定されても、過大な突入電流が流れるような動作が行われることはないので、LED6を高輝度状態から低輝度状態に切り替え設定する場合には、制御回路81は、低輝度状態への切り替えと同時に、D/Aコンバータ84に対して低電圧値データ“0011”が設定され、Duty制御回路83は低電圧値データ“0011”に対応するDuty制御信号を発生する。

【0036】

なお、上記実施形態では、制御回路81からDuty制御回路83へ出力されるデジタル昇圧値データ切り替え信号を受けて、Duty制御回路83が、低電圧レベル“0011”から所定のレベル差で階段状に上昇する昇圧値データ“0100”,“0101”,…,“1011”に対応するDuty制御信号を順次発生するように構成したが、Duty制御回路83が制御回路81から高電圧レベルへの切り替え動作を起動する信号を受けた時点から、昇圧値データ“1011”に対応するDuty制御信号を出力するように構成してもよい。

【0037】

この場合、低輝度状態から高輝度状態へ切り替え直後から、スイッチ素子であるFET3のゲートに供給されるクロックパルスのDuty比は、GNDへの短絡時間が最も長くなる高輝度状態に直ちに設定されるため、上記実施形態の場合よりは突入電流は多くなるが、D/Aコンバータ6の出力電圧と昇圧電圧の分圧であるフィードバック電圧との電圧差は小さいので、各ステップにおける昇圧動作時間は短くなり、突入電流は時間方向に分散されるため、図6に示すような過大な突入電流とはならない。

【0038】

図4は、本発明の第2の実施形態を示す出力電圧調整可能な昇圧型DC/DCコンバータのブロック図である。本実施形態では、CPU9及びタイマー10が備えられており、D/Aコンバータ84に対する設定データを所定時間毎に1コードづつ上昇させる手段として、タイマー10のタイミングでCPU9がソフト処理により上昇させている点で、第1の実施形態と異なるが、同様の効果を得ることができる。この場合、制御回路81は、出力電圧切り替え動作起動信号を各ブロックに出力する機能を果す。なお、タイマー10を制御回路81に接続し、制御回路81がタイマー10のタイミングでソフト処理により設定データを上昇させるように構成することもできる。

【0039】

図5は、本発明の第3の実施形態を示す出力電圧調整可能な昇圧型DC/DCコンバータのブロック図である。本実施形態では、D/Aコンバータ84の出力にコンデンサ10を備えることで、高輝度設定データ設定に対するD/Aコンバータ84の出力電圧をコンデンサ10の充電により遅延させることにより、図3に示すD/Aコンバータ出力電圧の各ステップ電圧での立ち上がり特性を緩やかにしている。その結果、各ステップにおいてFET3がオンとなるスイッチングの間隔を伸ばす効果が生じ、突入電流をより小さくする効果が得られる。

【図面の簡単な説明】

【0040】

【図1】本発明が適用される昇圧型DC/DCコンバータを示すブロック図である。

【図2】本発明の実施形態の制御動作を示すフローチャートである。

【図3】本発明の実施形態の出力電圧調整動作を示すタイムチャートである。

【図4】本発明が適用される昇圧型DC/DCコンバータの他の例を示すブロック図である。

【図5】本発明が適用される昇圧型DC/DCコンバータの他の例を示すブロック図である。

【図6】従来例の出力電圧調整動作を示すタイムチャートである。

【符号の説明】

【0041】

1 直流電源(電池)

2 インダクタ

3 FET

4 ダイオード

5、11 コンデンサ

6 LED

7 抵抗

8 スイッチング制御部

9 タイマー

10 CPU

81 制御回路

82 クロック発生回路

83 Duty制御回路

84 D/Aコンバータ

85 コンパレータ

86 ドライバ制御回路

【特許請求の範囲】

【請求項1】

直流電源と、該直流電源の正極にインダクタを介してその一方の端子が接続され、他方の端子が前記直流電源の負極に接続されたスイッチング素子と、前記インダクタとスイッチング素子の接続点にアノードが接続されたダイオードと、該ダイオードのカソードと前記直流電源の負極の間に接続されたコンデンサと、前記スイッチング素子をオン/オフ制御するスイッチング制御部とからなり、前記コンデンサの両端から前記直流電源の電圧を昇圧した少なくとも2つの電圧レベル(低電圧レベル及び高電圧レベル)を切り替えて出力することを可能に構成された昇圧型DC/DCコンバータにおいて、

前記スイッチング制御部は、

前記低電圧レベルと高電圧レベルに対応する昇圧値データをデジタルデータとして設定する手段と、前記低電圧レベルに対応する昇圧値データが設定されている状態において前記高電圧レベルへの切り替え指示を受けたとき、切り替え動作を起動するとともに、前記低電圧レベルから前記高電圧レベルまで所定のレベル差で階段状に上昇するデジタル昇圧値データを、所定時間間隔で順次設定して出力する手段を有する制御回路と、

昇圧動作に使用されるクロックを発生するクロック発生回路と、

前記制御回路から切り替え動作を起動する信号を受けて、前記クロック発生回路のクロックのDuty比を制御するDuty制御信号を発生するDuty制御回路と、

前記制御回路から出力される前記所定のレベル差で上昇するデジタル昇圧値データを入力して、該デジタル昇圧値データに対応する基準電圧を前記所定時間間隔で順次発生するD/Aコンバータと、

昇圧された出力電圧レベルと前記D/Aコンバータから出力される基準電圧とを比較し、前記出力電圧レベルが前記基準電圧以上か、または基準電圧より低いかを判定するコンパレータと、

前記クロック発生回路、Duty制御回路およびコンパレータからの信号を受け、前記昇圧された出力電圧レベルが前記基準電圧よりも低いと判定されている間、前記Duty制御信号によりそのDuty比が変調された前記クロック信号を用いて前記スイッチング素子のオン/オフ動作を制御するドライバ制御回路とを備えている、

ことを特徴とする出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項2】

前記Duty制御回路は、前記高電圧レベルへの切り替え動作を起動する信号を受けて、前記クロック発生回路のクロックのDuty比を、前記高電圧レベルが発生可能なDuty比に設定するDuty制御信号を発生する手段を有していることを特徴とする請求項1に記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項3】

前記Duty制御回路は、前記高電圧レベルへの切り替え動作を起動する信号を受けて、前記クロック発生回路のクロックのDuty比を、前記低電圧レベルから所定のレベル差で階段状に上昇する電圧レベルを発生可能な各Duty比に前記所定時間間隔で順次設定するDuty制御信号を発生する手段を有していることを特徴とする請求項1に記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項4】

前記制御回路は、前記クロック発生回路のクロックを所定数計数することによって前記所定時間を設定する手段を有していることを特徴とする請求項1〜3のいずれかに記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項5】

タイマーが備えられており、前記制御回路は、前記所定時間を該タイマーにより設定する手段を有していることを特徴とする請求項1〜3のいずれかに記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項6】

前記D/Aコンバータの出力端に、前記コンパレータに入力する該D/Aコンバータの出力電圧を遅延させるためのコンデンサが接続されていることを特徴とする請求項1〜5のいずれかに記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項7】

前記制御回路は、前記高電圧レベルに対応する昇圧値データが設定されている状態において、前記低電圧レベルへの切り替え指示を受けたとき、該切り替え指示と同時に前記低電圧レベルに対応する昇圧値データを設定する手段を有していることを特徴とする請求項1に記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項8】

請求項1〜8のいずれかに記載の出力電圧調整可能な昇圧型DC/DCコンバータの出力電圧が供給され、前記低電圧レベルと高電圧レベルに対応する低輝度状態と高輝度状態に調整されるLEDを備えていることを特徴とするLED輝度調整回路。

【請求項1】

直流電源と、該直流電源の正極にインダクタを介してその一方の端子が接続され、他方の端子が前記直流電源の負極に接続されたスイッチング素子と、前記インダクタとスイッチング素子の接続点にアノードが接続されたダイオードと、該ダイオードのカソードと前記直流電源の負極の間に接続されたコンデンサと、前記スイッチング素子をオン/オフ制御するスイッチング制御部とからなり、前記コンデンサの両端から前記直流電源の電圧を昇圧した少なくとも2つの電圧レベル(低電圧レベル及び高電圧レベル)を切り替えて出力することを可能に構成された昇圧型DC/DCコンバータにおいて、

前記スイッチング制御部は、

前記低電圧レベルと高電圧レベルに対応する昇圧値データをデジタルデータとして設定する手段と、前記低電圧レベルに対応する昇圧値データが設定されている状態において前記高電圧レベルへの切り替え指示を受けたとき、切り替え動作を起動するとともに、前記低電圧レベルから前記高電圧レベルまで所定のレベル差で階段状に上昇するデジタル昇圧値データを、所定時間間隔で順次設定して出力する手段を有する制御回路と、

昇圧動作に使用されるクロックを発生するクロック発生回路と、

前記制御回路から切り替え動作を起動する信号を受けて、前記クロック発生回路のクロックのDuty比を制御するDuty制御信号を発生するDuty制御回路と、

前記制御回路から出力される前記所定のレベル差で上昇するデジタル昇圧値データを入力して、該デジタル昇圧値データに対応する基準電圧を前記所定時間間隔で順次発生するD/Aコンバータと、

昇圧された出力電圧レベルと前記D/Aコンバータから出力される基準電圧とを比較し、前記出力電圧レベルが前記基準電圧以上か、または基準電圧より低いかを判定するコンパレータと、

前記クロック発生回路、Duty制御回路およびコンパレータからの信号を受け、前記昇圧された出力電圧レベルが前記基準電圧よりも低いと判定されている間、前記Duty制御信号によりそのDuty比が変調された前記クロック信号を用いて前記スイッチング素子のオン/オフ動作を制御するドライバ制御回路とを備えている、

ことを特徴とする出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項2】

前記Duty制御回路は、前記高電圧レベルへの切り替え動作を起動する信号を受けて、前記クロック発生回路のクロックのDuty比を、前記高電圧レベルが発生可能なDuty比に設定するDuty制御信号を発生する手段を有していることを特徴とする請求項1に記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項3】

前記Duty制御回路は、前記高電圧レベルへの切り替え動作を起動する信号を受けて、前記クロック発生回路のクロックのDuty比を、前記低電圧レベルから所定のレベル差で階段状に上昇する電圧レベルを発生可能な各Duty比に前記所定時間間隔で順次設定するDuty制御信号を発生する手段を有していることを特徴とする請求項1に記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項4】

前記制御回路は、前記クロック発生回路のクロックを所定数計数することによって前記所定時間を設定する手段を有していることを特徴とする請求項1〜3のいずれかに記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項5】

タイマーが備えられており、前記制御回路は、前記所定時間を該タイマーにより設定する手段を有していることを特徴とする請求項1〜3のいずれかに記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項6】

前記D/Aコンバータの出力端に、前記コンパレータに入力する該D/Aコンバータの出力電圧を遅延させるためのコンデンサが接続されていることを特徴とする請求項1〜5のいずれかに記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項7】

前記制御回路は、前記高電圧レベルに対応する昇圧値データが設定されている状態において、前記低電圧レベルへの切り替え指示を受けたとき、該切り替え指示と同時に前記低電圧レベルに対応する昇圧値データを設定する手段を有していることを特徴とする請求項1に記載の出力電圧調整可能な昇圧型DC/DCコンバータ。

【請求項8】

請求項1〜8のいずれかに記載の出力電圧調整可能な昇圧型DC/DCコンバータの出力電圧が供給され、前記低電圧レベルと高電圧レベルに対応する低輝度状態と高輝度状態に調整されるLEDを備えていることを特徴とするLED輝度調整回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2006−141184(P2006−141184A)

【公開日】平成18年6月1日(2006.6.1)

【国際特許分類】

【出願番号】特願2004−331180(P2004−331180)

【出願日】平成16年11月15日(2004.11.15)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

【公開日】平成18年6月1日(2006.6.1)

【国際特許分類】

【出願日】平成16年11月15日(2004.11.15)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

[ Back to top ]